Texas Instruments UC5612PWPTR, UC5612PWP, UC5612N, UC5612DPTR, UC5612DP Datasheet

• Complies with SCSI, SCSI-2

and SPI-2 Standards

• 5pF Channel Capacitance

during Disconnect

• Meets SCSI Hot Plugging

•−400mA Sourcing Current for

Termination

• +100mA Sinking Current for

Active Negation

• 1V Dropout Voltage Regulator

• Logic High Command

Disconnects all Termination

Lines

• 100µA Supply Current in

Disconnect Mode

• Trimmed Termination Current

to 5%

• Trimmed Impedance to 5%

• Low Thermal Resistance

Surface Mount Packages

The UC5612 provides 9 lines of acti ve term ination for a SCSI (Small Co mputer

Systems Interfac e) parallel bus. The SCSI standard recommends active termi nation at both ends of the cable segment.

The only functional differences between the UC5603 and UC5612 is the absence of the negative clamps on the out put lines. Parametrically, the UC5612

has a 5% tol er anc e on impedance and current com par ed t o a 3% tol erance on

the UC5603. Custom power packages are utilized to al low nor mal oper ati on at

full power (2 Watts).

The UC5612 provi des a disconnect feature which, when opened or driven high,

disconnect s all terminating resistors , disables the regulator and greatly reduces

standby power consumption. The output channels remain high impedance even

without Termpwr applied. A low channel capacitance of 5pF allows interim

points of the bus to have little to no effect on the signal integrity.

Internal circuit trimming is utilized, first to trim the impedance to a 5% tolerance,

and then most importantly, to trim the output current to a 5% tolerance, as close

to the maximum SCS I speci f ication as possible. This maximizes the noise margin in fast SCSI operation. Other features include therm al shutdown and current limit.

This device is offered in low ther mal resistanc e versions of the industry standard 16 pin narrow body SOIC, 16 pin ZIP (zig-zag in line package) and 24 pin

TSSOP.

UC5612

9-Line Low Capacitance SCSI Active Terminator

FEATURES DESCRIPTION

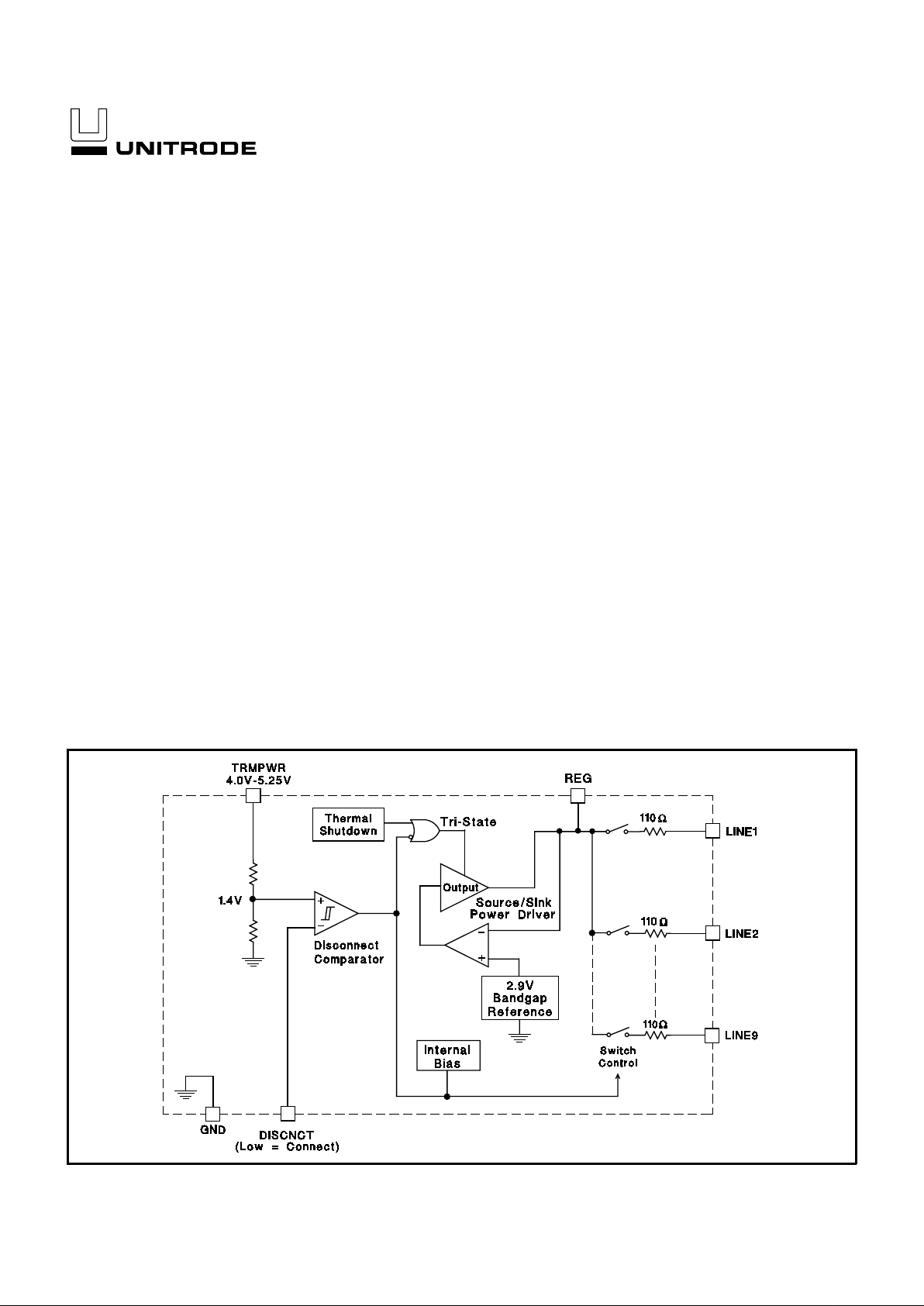

BLOCK DIAGRAM

Circuit Design Patented

3/97

UDG-94133

ABSOLUTE MAXIMUM RATIN GS

Termpwr Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +7V

Signal Line Voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . 0V to +7V

Regulator Output Current . . . . . . . . . . . . . . . . . . . . . . . . . . 0.6A

Storage Temperature . . . . . . . . . . . . . . . . . . . −65°C to +150°C

Operating Temperature . . . . . . . . . . . . . . . . . −55°C to +150°C

Lead Temperature (Soldering, 10 Sec.). . . . . . . . . . . . . +300°C

RECOMMENDED OPERATIN G CONDITIONS

Termpwr Voltage . . . . . . . . . . . . . . . . . . . . . . . . . 3.8V to 5.25V

Signal Line Voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . 0V to +5V

Disconnect Input Voltage . . . . . . . . . . . . . . . . . . 0V to Termpwr

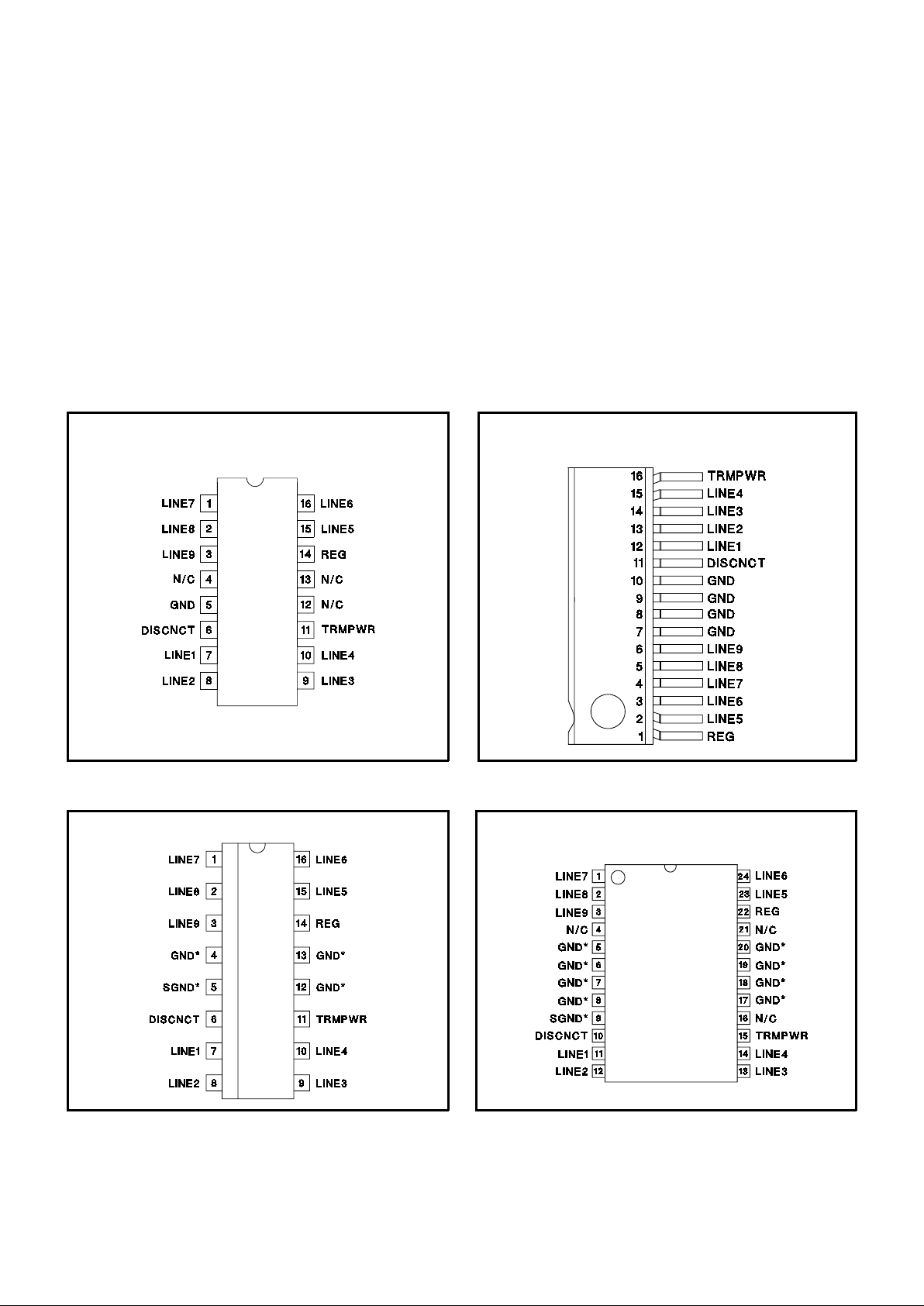

CONNECTION DIAG RAMS

DIL-16 (Top View)

N or J Package

UC5612

* DP package pin 5 serves as signal ground; pins 4, 12, 13

serve as heatsink/ground.

* PWP package pin 9 serves as signal ground; pins 5, 6, 7, 8,

17, 18, 19, and 20 serve as heatsink/ground.

ZIP-16 (Top View)

Z Package

SOIC-16 (Top View)

DP Package

TSSOP-24 (Top View)

PWP Package

Note: Drawings are not to scale.

Unless otherwise specified all voltages are with respect to

Ground. Currents are positive into, negative out of the specified terminal.

Consult Packaging Section of Unitrode Integrated Circuits databook for thermal limitations and considerations of packages.

2

Loading...

Loading...