TVP5158, TVP5157, TVP5156

Four-Channel NTSC/PAL Video Decoders

With Independent Scalers, Noise Reduction, Auto

Contrast, and Flexible Output Formatter for Security and

Other Multi-Channel Video Applications

Data Manual

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Literature Number: SLES243D

July 2009–Revised October 2010

TVP5158, TVP5157, TVP5156

SLES243D–JULY 2009–REVISED OCTOBER 2010

www.ti.com

Contents

1 Introduction ........................................................................................................................ 9

1.1 Features ...................................................................................................................... 9

1.2 Applications ................................................................................................................ 10

1.3 Related Products .......................................................................................................... 10

1.4 Trademarks ................................................................................................................. 10

1.5 Document Conventions ................................................................................................... 10

1.6 Description ................................................................................................................. 10

1.7 Ordering Information ...................................................................................................... 11

1.8 Functional Block Diagram ................................................................................................ 12

2 Terminal Assignments ....................................................................................................... 13

2.1 Pinout ....................................................................................................................... 13

3 Functional Description ....................................................................................................... 16

3.1 Analog Video Processing and A/D Converters ........................................................................ 16

3.1.1 Analog Video Input ............................................................................................. 16

3.1.2 Analog Video Input Clamping ................................................................................. 17

3.1.3 A/D Converter ................................................................................................... 17

3.2 Digital Video Processing .................................................................................................. 17

3.2.1 2x Decimation Filter ............................................................................................ 17

3.2.2 Automatic Gain Control ........................................................................................ 17

3.2.3 Composite Processor .......................................................................................... 17

3.2.3.1 Color Low-Pass Filter .............................................................................. 18

3.2.3.2 Y/C Separation ..................................................................................... 19

3.2.4 Luminance Processing ......................................................................................... 20

3.3 AVID Cropping ............................................................................................................. 21

3.4 Embedded Syncs .......................................................................................................... 21

3.5 Scaler ....................................................................................................................... 22

3.6 Noise Reduction ........................................................................................................... 22

3.7 Auto Contrast .............................................................................................................. 22

3.8 Output Formatter .......................................................................................................... 23

3.8.1 Non-Interleaved Mode ......................................................................................... 23

3.8.2 Pixel-Interleaved Mode ......................................................................................... 23

3.8.2.1 2-Ch Pixel-Interleaved Mode ..................................................................... 24

3.8.2.2 4-Ch Pixel-Interleaved Mode ..................................................................... 24

3.8.2.3 Metadata Insertion for Non-Interleave Mode and Pixel-Interleaved Mode ................. 25

3.8.3 Line-Interleaved Mode Support (TVP5158 only) ........................................................... 26

3.8.3.1 2-Ch Line-Interleaved Mode ...................................................................... 26

3.8.3.2 4-Ch Line-Interleaved Mode ...................................................................... 26

3.8.3.3 8-Ch Line-Interleaved Mode ...................................................................... 27

3.8.3.4 Hybrid Modes ....................................................................................... 29

3.8.3.5 Metadata Insertion for Line-Interleaved Mode ................................................. 29

3.9 Audio Sub-System (TVP5157 and TVP5158 Only) ................................................................... 32

3.9.1 Features ......................................................................................................... 32

3.9.2 Audio Sub-System Functional Diagram ..................................................................... 33

3.9.3 Serial Audio Interface .......................................................................................... 33

3.9.4 Analog Audio Input Clamping ................................................................................. 34

2 Contents Copyright © 2009–2010, Texas Instruments Incorporated

TVP5158, TVP5157, TVP5156

www.ti.com

SLES243D–JULY 2009–REVISED OCTOBER 2010

3.9.5 Audio Cascade Connection ................................................................................... 35

3.10 I

2

C Host Interface .......................................................................................................... 36

3.10.1 I

3.10.2 I

2

C Write Operation ............................................................................................. 38

2

C Read Operation ............................................................................................ 38

3.10.3 VBUS Access ................................................................................................... 40

3.11 Clock Circuits .............................................................................................................. 41

3.12 Reset Mode ................................................................................................................ 42

4 Internal Control Registers ................................................................................................... 43

4.1 Overview .................................................................................................................... 43

4.2 Register Definitions ........................................................................................................ 46

5 Electrical Specifications ..................................................................................................... 88

5.1 Absolute Maximum Ratings .............................................................................................. 88

5.2 Recommended Operating Conditions .................................................................................. 88

5.3 Reference Clock Specifications .......................................................................................... 89

5.4 Electrical Characteristics ................................................................................................. 89

5.5 DC Electrical Characteristics ............................................................................................. 89

5.6 Video A/D Converters Electrical Characteristics ...................................................................... 90

5.7 Audio A/D Converters Electrical Characteristics ...................................................................... 90

5.8 Video Output Clock and Data Timing ................................................................................... 91

5.8.1 Video Input Clock and Data Timing .......................................................................... 91

5.9 I

2

C Host Port Timing ...................................................................................................... 92

5.9.1 I

2

S Port Timing .................................................................................................. 93

5.10 Miscellaneous Timings .................................................................................................... 93

5.11 Power Dissipation Ratings ............................................................................................... 93

6 Application Information ...................................................................................................... 94

6.1 4-Ch D1 Applications ..................................................................................................... 94

6.2 8-Ch CIF Applications ..................................................................................................... 94

6.3 16-Ch CIF Applications ................................................................................................... 95

6.4 Application Circuit Examples ............................................................................................. 96

6.5 Designing with PowerPAD™ Devices .................................................................................. 97

7 Revison History ................................................................................................................. 98

Copyright © 2009–2010, Texas Instruments Incorporated Contents 3

TVP5158, TVP5157, TVP5156

SLES243D–JULY 2009–REVISED OCTOBER 2010

www.ti.com

List of Figures

1-1 Functional Block Diagram....................................................................................................... 12

3-1 Video Analog Processing and ADC Block Diagram ......................................................................... 16

3-2 Anti-Aliasing Filter Frequency Response ..................................................................................... 17

3-3 Composite Processor Block Diagram.......................................................................................... 18

3-4 Color Low-Pass Filter Frequency Response ................................................................................. 19

3-5 Color Low-Pass Filter with Filter Characteristics, NTSC/PAL ITU-R BT.601 Sampling................................. 19

3-6 Chroma Trap Filter Frequency Response, NTSC ITU-R BT.601 Sampling .............................................. 20

3-7 Chroma Trap Filter Frequency Response, PAL ITU-R BT.601 Sampling ................................................ 20

3-8 Luminance Edge-Enhancer Peaking Block Diagram........................................................................ 21

3-9 Peaking Filter Response, NTSC/PAL ITU-R BT.601 Sampling............................................................ 21

3-10 2-Ch Pixel-Interleaved Mode Timing Diagram................................................................................ 24

3-11 4-Ch Pixel-Interleaved Mode Timing Diagram................................................................................ 25

3-12 Cascade Connection for 16-Ch CIF Recoding and Multi-Ch CIF Preview ............................................... 28

3-13 Cascade Connection for 16-Ch CIF Recoding and Multi-Ch Half-D1 Preview........................................... 28

3-14 Cascade Connection for 16-Ch CIF Recoding and 2-Ch D1/Multi-Ch CIF Preview..................................... 29

3-15 Start Code in 8-Bit BT.656 Interface........................................................................................... 30

3-16 Start Code in 16-Bit YCbCr 4:2:2 Interface................................................................................... 30

3-17 Audio Sub-System Functional Diagram ....................................................................................... 33

3-18 Serial Audio Interface Timing Diagram........................................................................................ 34

3-19 Audio Cascade Connection..................................................................................................... 35

3-20 VBUS Access..................................................................................................................... 40

3-21 Clock and Crystal Connectivity ................................................................................................. 41

3-22 Reset Timing...................................................................................................................... 42

5-1 Video Output Clock and Data Timing.......................................................................................... 91

5-2 I

6-1 4-Ch D1 Application (Single BT.656 Interface)............................................................................... 94

6-2 4-Ch D1 Application (16-Bit YCbCr 4:2:2 Interface)......................................................................... 94

6-3 8-Ch CIF Real Time Encoding and Multi-Ch D1 Preview Application..................................................... 95

6-4 8-Ch CIF Real Time Encoding and Multi-Ch D1 Preview Application..................................................... 95

6-5 Video Input Connectivity......................................................................................................... 97

6-6 Audio Input Connectivity......................................................................................................... 97

2

C Host Port Timing ............................................................................................................. 92

4 List of Figures Copyright © 2009–2010, Texas Instruments Incorporated

TVP5158, TVP5157, TVP5156

www.ti.com

SLES243D–JULY 2009–REVISED OCTOBER 2010

List of Tables

1-1 Device Options ................................................................................................................... 11

2-1 Terminal Functions .............................................................................................................. 14

3-1 EAV and SAV Sequence........................................................................................................ 21

3-2 Standard Video Resolutions .................................................................................................... 22

3-3 Video Resolutions Converted by the Scaler.................................................................................. 22

3-4 Summary of Line Frequencies, Data Rates and Pixel Counts for Different Standards................................. 23

3-5 Output Ports Configuration for Non-Interleaved Mode ...................................................................... 23

3-6 Output Ports Configuration for Pixel-Interleaved Mode ..................................................................... 24

3-7 VDET Statues Insertion in SAV/EAV Codes.................................................................................. 25

3-8 Channel ID Insertion in Horizontal Blanking Code........................................................................... 25

3-9 Channel ID Insertion in SAV/EAV Code Sequence.......................................................................... 25

3-10 Output Ports Configuration for Line-Interleaved Mode...................................................................... 26

3-11 Default Super-Frame Format and Timing..................................................................................... 29

3-12 Bit Assignment of 4-Byte Start Code for Active Video Line................................................................. 30

3-13 Bit Field Definition of 4-Byte Start Code for Active Video Line............................................................. 30

3-14 Bit Assignment of 4-Byte Start Code for the Dummy Line.................................................................. 31

3-15 Serial Audio Output Channel Assignment..................................................................................... 36

3-16 I

3-17 I

3-18 Reset Mode ....................................................................................................................... 42

3-19 Reset Sequence.................................................................................................................. 42

4-1 Registers Summary .............................................................................................................. 43

4-2 Status 1 ........................................................................................................................... 46

4-3 Status 2 ........................................................................................................................... 47

4-4 Color Subcarrier Phase Status ................................................................................................ 47

4-5 ROM Version ..................................................................................................................... 47

4-6 Chip ID MSB ..................................................................................................................... 48

4-7 Chip ID LSB ...................................................................................................................... 48

4-8 Video Standard Status .......................................................................................................... 48

4-9 Video Standard Select .......................................................................................................... 49

4-10 CVBS Autoswitch Mask ......................................................................................................... 49

4-11 Auto Contrast Mode ............................................................................................................. 49

4-12 Luminance Brightness .......................................................................................................... 50

4-13 Luminance Contrast ............................................................................................................. 50

4-14 Brightness and Contrast Range Extender .................................................................................... 50

4-15 Chrominance Saturation ........................................................................................................ 51

4-16 Chrominance Hue ............................................................................................................... 51

4-17 Color Killer ........................................................................................................................ 51

4-18 Luminance Processing Control 1 .............................................................................................. 52

4-19 Luminance Processing Control 2 .............................................................................................. 52

4-20 Power Control .................................................................................................................... 53

4-21 Chrominance Processing Control 1 ........................................................................................... 54

4-22 Chrominance Processing Control 2 ........................................................................................... 54

4-23 AGC Gain Status ................................................................................................................ 55

4-24 Back-End AGC Status .......................................................................................................... 55

4-25 Status Request .................................................................................................................. 55

4-26 AFE Gain Control ................................................................................................................ 55

Copyright © 2009–2010, Texas Instruments Incorporated List of Tables 5

2

C Terminal Description ........................................................................................................ 37

2

C Host Interface Device Addresses.......................................................................................... 37

TVP5158, TVP5157, TVP5156

SLES243D–JULY 2009–REVISED OCTOBER 2010

4-27 Luma ALC Freeze Upper Threshold .......................................................................................... 56

4-28 Chroma ALC Freeze Upper Threshold ....................................................................................... 56

4-29 AGC Increment Speed .......................................................................................................... 56

4-30 AGC Increment Delay ........................................................................................................... 56

4-31 AGC Decrement Speed ......................................................................................................... 57

4-32 AGC Decrement Delay ......................................................................................................... 57

4-33 AGC White Peak Processing .................................................................................................. 58

4-34 Back-End AGC Control ......................................................................................................... 59

4-35 AFE Fine Gain ................................................................................................................... 59

4-36 AVID Start Pixel .................................................................................................................. 60

4-37 AVID Pixel Width ................................................................................................................ 60

4-38 Noise Reduction Max Noise .................................................................................................... 60

4-39 Noise Reduction Control ........................................................................................................ 61

4-40 Noise Reduction Noise Filter Beta ............................................................................................ 61

4-41 Operation Mode Control ........................................................................................................ 62

4-42 Color PLL Speed Control ....................................................................................................... 62

4-43 Sync Height Low Threshold .................................................................................................... 62

4-44 Sync Height High Threshold ................................................................................................... 63

4-45 Clear Lost Lock Detect .......................................................................................................... 63

4-46 VSYNC Filter Shift ............................................................................................................... 63

4-47 656 Version/F-bit Control ....................................................................................................... 63

4-48 F-Bit and V-Bit Decode Control ................................................................................................ 64

4-49 F-Bit and V-Bit Control .......................................................................................................... 65

4-50 Output Timing Delay ............................................................................................................ 65

4-51 Auto Contrast User Table Index ............................................................................................... 66

4-52 Blue Screen Y Control .......................................................................................................... 66

4-53 Blue Screen Cb Control ........................................................................................................ 66

4-54 Blue Screen Cr Control ......................................................................................................... 66

4-55 Blue Screen LSB Control ....................................................................................................... 67

4-56 Noise Measurement ............................................................................................................. 67

4-57 Weak Signal High Threshold ................................................................................................... 67

4-58 Weak Signal Low Threshold ................................................................................................... 67

4-59 Noise Reduction Y/U/V T0 ..................................................................................................... 68

4-60 Vertical Line Count Status ...................................................................................................... 68

4-61 Output Formatter Control 1 ..................................................................................................... 68

4-62 Output Formatter Control 2 ..................................................................................................... 69

4-63 Interrupt Control ................................................................................................................. 69

4-64 Embedded Sync Offset Control 1 ............................................................................................. 69

4-65 Embedded Sync Offset Control 2 ............................................................................................. 70

4-66 AVD Output Control 1 ........................................................................................................... 71

4-67 AVD Output Control 2 ........................................................................................................... 72

4-68 OFM Mode Control .............................................................................................................. 73

4-69 OFM Channel Select 1 .......................................................................................................... 74

4-70 OFM Channel Select 2 .......................................................................................................... 75

4-71 OFM Channel Select 3 .......................................................................................................... 75

4-72 OFM Super-Frame Size ........................................................................................................ 76

4-73 OFM H-Blank Duration .......................................................................................................... 76

4-74 Misc OFM Control ............................................................................................................... 76

www.ti.com

6 List of Tables Copyright © 2009–2010, Texas Instruments Incorporated

TVP5158, TVP5157, TVP5156

www.ti.com

SLES243D–JULY 2009–REVISED OCTOBER 2010

4-75 Audio Sample Rate Control .................................................................................................... 77

4-76 Analog Audio Gain Control 1 ................................................................................................... 77

4-77 Analog Audio Gain Control 2 ................................................................................................... 78

4-78 Audio Mode Control ............................................................................................................. 79

4-79 Audio Mixer Select .............................................................................................................. 80

4-80 Audio Mute Control .............................................................................................................. 81

4-81 Analog Mixing Ratio Control 1 ................................................................................................. 81

4-82 Analog Mixing Ratio Control 2 ................................................................................................. 82

4-83 Audio Cascade Mode Control .................................................................................................. 82

4-84 Super-Frame EAV2SAV Duration Status ..................................................................................... 82

4-85 Super-Frame SAV2EAV Duration Status ..................................................................................... 83

4-86 VBUS Data Access With No VBUS Address Increment ................................................................... 83

4-87 VBUS Data Access With VBUS Address Increment ........................................................................ 83

4-88 VBUS Address Access ......................................................................................................... 83

4-89 Interrupt Status .................................................................................................................. 84

4-90 Interrupt Mask .................................................................................................................... 85

4-91 Interrupt Clear .................................................................................................................... 86

4-92 Decoder Write Enable .......................................................................................................... 86

4-93 Decoder Read Enable .......................................................................................................... 87

7-1 Revison History................................................................................................................... 98

Copyright © 2009–2010, Texas Instruments Incorporated List of Tables 7

TVP5158, TVP5157, TVP5156

SLES243D–JULY 2009–REVISED OCTOBER 2010

www.ti.com

8 List of Tables Copyright © 2009–2010, Texas Instruments Incorporated

TVP5158, TVP5157, TVP5156

www.ti.com

SLES243D–JULY 2009–REVISED OCTOBER 2010

Four-Channel NTSC/PAL Video Decoders

Check for Samples: TVP5158, TVP5157, TVP5156

1 Introduction

1.1 Features

1234

• Common Device Features

(TVP5156, TVP5157, TVP5158)

– Four separate video decoder channels

having the following features for each

channel – Internal phase-locked loop (PLL) for

• Accepts NTSC (J, M, 4.43) and PAL (B, D,

G, H, I, M, N, Nc, 60) video data

• Composite video inputs,

Pseudo-differential video inputs to • ITU-R BT.656, 8-bit 4:2:2 with embedded

improved noise immunity syncs

• High-speed 10-bit ADC • YCbCr 16-bit 4:2:2 with embedded syncs

• Fully differential CMOS analog – Macrovision™ copy protection detection

preprocessing channels with clamping

• Integrated Anti-Aliasing filter

• 2D 5-line (5H) adaptive comb filter

• Noise reduction and auto contrast temperature range

• Robust automatic video standard • Additional TVP5158/TVP5157 Specific Features

detection (NTSC/PAL) and switching

• Programmable hue, saturation, audio sample rate of 8 kHz or 16 kHz

sharpness, brightness and contrast

• Luma-peaking processing

• Patented architecture for locking to weak,

noisy, or unstable signals

– Four independent scalers support horizontal

and/or vertical 2:1 downscaling

– Channel multiplexing capabilities with

metadata insertion

• Pixel-interleaved mode supports up to

four-channel D1 multiplexed 8-bit output

at 108 MHz

• Supports concurrent NTSC and PAL

inputs

– Support crystal interface with on-chip

oscillator and single clock input mode

– Single 27-MHz clock input or crystal for all

standards and all channels

line-locked clock (separate for each channel)

and sampling

– Standard programmable video output format

– 3.3-V compatible I/O

– 128-pin TQFP package

– Available in commercial (0°C to 70°C)

– Integrated four-channel audio ADC with

– Support Master and Slave mode I2S Output

– Support audio cascade connection

• Additional TVP5158 Specific Features

– Enhanced channel multiplexing capability –

Line-interleaved mode

– Four-channel D1 multiplexed output at 8 bit

at 108 MHz

– Video cascade connection for 8-Ch CIF, 8-Ch

Half-D1, and 8-Ch CIF + 1-Ch D1 outputs

– Also available in Industrial (-40°C to 85°C)

temperature range

• Qualified for Automotive Applications

(AEC-Q100 Rev G – TVP5158IPNPQ1,

TVP5158IPNPRQ1)

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

2DaVinci is a trademark of Texas Instruments.

3Macrovision is a trademark of Macrovision Corporation.

4All other trademarks are the property of their respective owners.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Copyright © 2009–2010, Texas Instruments Incorporated

TVP5158, TVP5157, TVP5156

SLES243D–JULY 2009–REVISED OCTOBER 2010

1.2 Applications

• Security/surveillance digital video recorders/servers and PCI products

• Automotive infotainment video hub

• Large format video wall displays

• Game systems

1.3 Related Products

• TVP5154A

• TVP5150AM1

• TVP5146M2

• TVP5147M1

1.4 Trademarks

DaVinci, PowerPAD are trademarks of Texas Instruments.

Macrovision is a trademark of Macrovision Corporation.

Other trademarks are the property of their respective owners.

1.5 Document Conventions

Throughout this data manual, several conventions are used to convey information. These conventions are

as follows:

• To identify a binary number or field, a lower case b follows the numbers. For example: 000b is a 3-bit

binary field.

• To identify a hexadecimal number or field, a lower case h follows the numbers. For example: 8AFh is a

12-bit hexadecimal field.

• All other numbers that appear in this document that do not have either a b or h following the number

are assumed to be decimal format.

• If the signal or terminal name has a bar above the name (for example, RESETB), then this indicates

the logical NOT function. When asserted, this signal is a logic low, 0, or 0b.

• RSVD indicates that the referenced item is reserved.

www.ti.com

1.6 Description

The TVP5158, TVP5157, and TVP5156 devices are 4-channel, high-quality NTSC/PAL video decoder that

digitizes and decodes all popular base-band analog video formats into digital video output. Each channel

of this decoder includes 10-bit 27-MSPS A/D converter (ADC). Preceding each ADC in the device, the

corresponding analog channel contains an analog circuit that clamps the input to a reference voltage and

applies the gain.

Composite input signal is sampled at 2x the ITU-R BT.601 clock frequency, line-locked alignment, and is

then decimated to the 1x pixel rate. CVBS decoding uses five-line adaptive comb filtering for both the

luma and chroma data paths to reduce both cross-luma and cross-chroma artifacts. A chroma trap filter is

also available. On CVBS inputs, the user can control video characteristics such as contrast, brightness,

saturation, and hue via an I2C host port interface. Furthermore, luma peaking (sharpness) with

programmable gain is included.

All 4 channels are independently controllable. These decoders share a single clock input for all channels

and for all supported standards.

10 Introduction Copyright © 2009–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TVP5158 TVP5157 TVP5156

TVP5158, TVP5157, TVP5156

www.ti.com

TVP5158 provides a glueless audio and video interface to TI DaVinci™ video processors. Video output

ports support 8-bit ITU-R BT.656 and 16-bit 4:2:2 YCbCr with embedded synchronization. TVP5158

supports multiplexed pixel-interleaved and line-interleaved mode video outputs with metadata insertion.

TVP5158 and TVP5157 integrate 4-Ch audio ADCs to reduce the BOM cost for surveillance market.

Multiple TVP5158 devices can be cascade connected to support up to 8-Ch Video or 16-Ch audio

processing.

Noise reduction and auto contrast functions improve the video quality under low light condition which is

very critical for surveillance products.

The TVP5158, TVP5157, and TVP5156 can be programmed by using a single I2C serial interface. I2C

commands can be sent to one or more decoder cores simultaneously, reducing the amount of I2C activity

necessary to configure each core. This is especially useful for fast downloading modified firmware to the

decoder cores.

TVP5158, TVP5157, and TVP5156 use 1.1-V, 1.8-V, and 3.3-V power supplies for the analog/digital core

and I/O. These devices are available in a 128-pin TQFP package.

SLES243D–JULY 2009–REVISED OCTOBER 2010

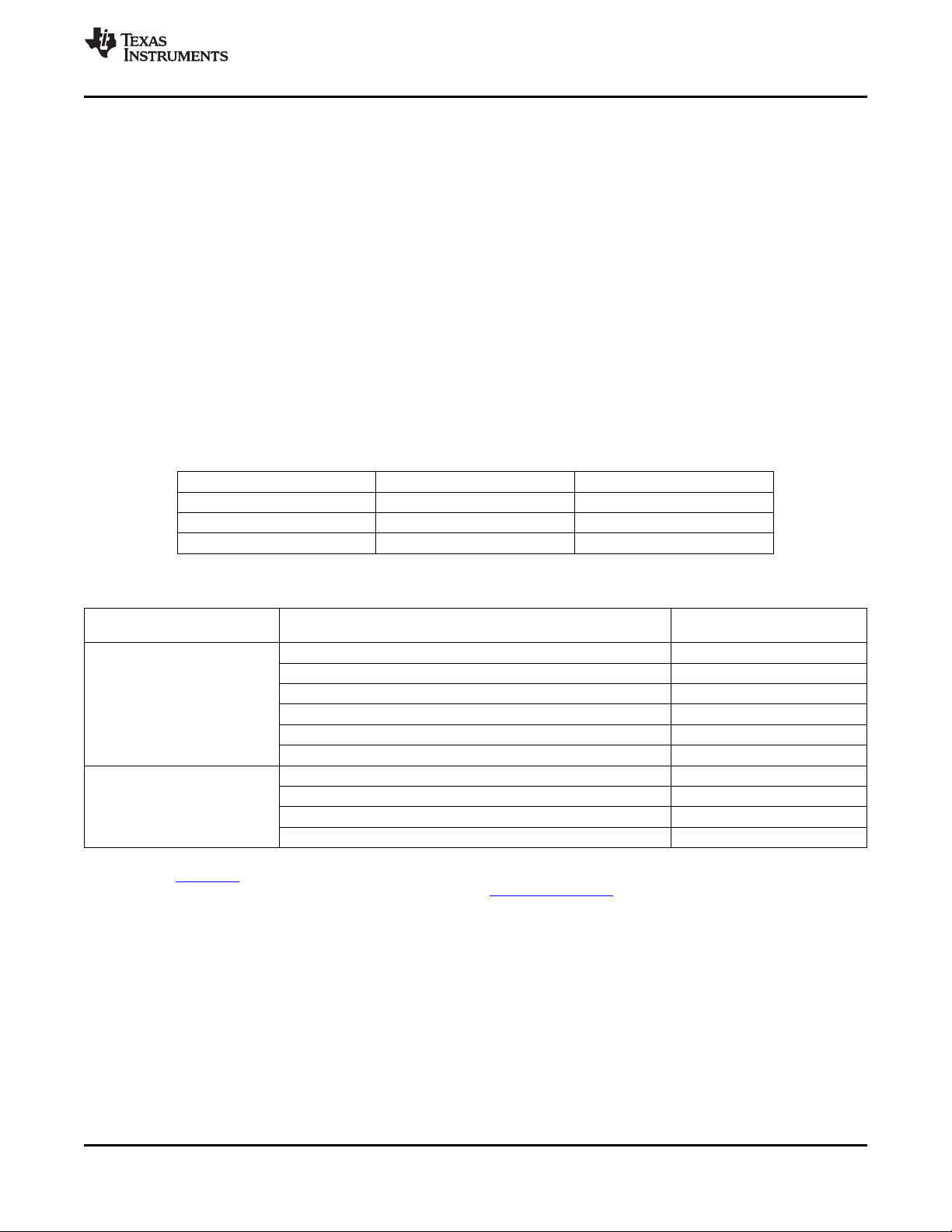

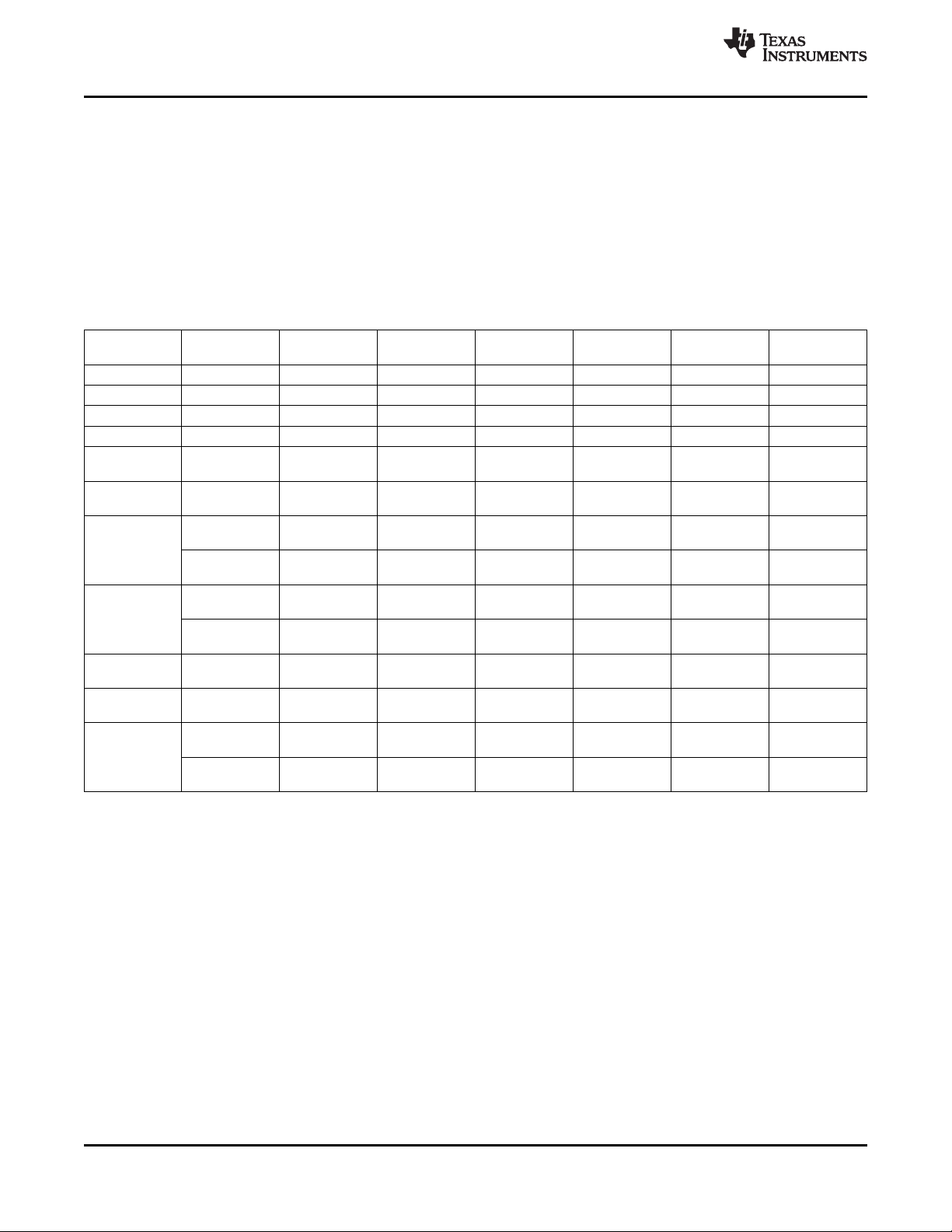

Table 1-1. Device Options

Device Name 4-Ch Audio ADC Line-Interleaved Modes

TVP5156 No No

TVP5157 Yes No

TVP5158 Yes Yes

1.7 Ordering Information

(3)

(3)

(1) (2)

PACKAGE OPTION

Tray

Tape and reel

T

A

0°C to 70°C

-40°C to 85°C

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI

web site at www.ti.com.

(2) Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

(3) AEC-Q100 Rev G certified

PACKAGED DEVICES

TQFP 128-Pin PowerPADTMPackage

TVP5156PNP Tray

TVP5156PNPR Tape and reel

TVP5157PNP Tray

TVP5157PNPR Tape and reel

TVP5158PNP Tray

TVP5158PNPR Tape and reel

TVP5158IPNP Tray

TVP5158IPNPR Tape and reel

TVP5158IPNPQ1

TVP5158IPNPRQ1

Copyright © 2009–2010, Texas Instruments Incorporated Introduction 11

Submit Documentation Feedback

Product Folder Link(s): TVP5158 TVP5157 TVP5156

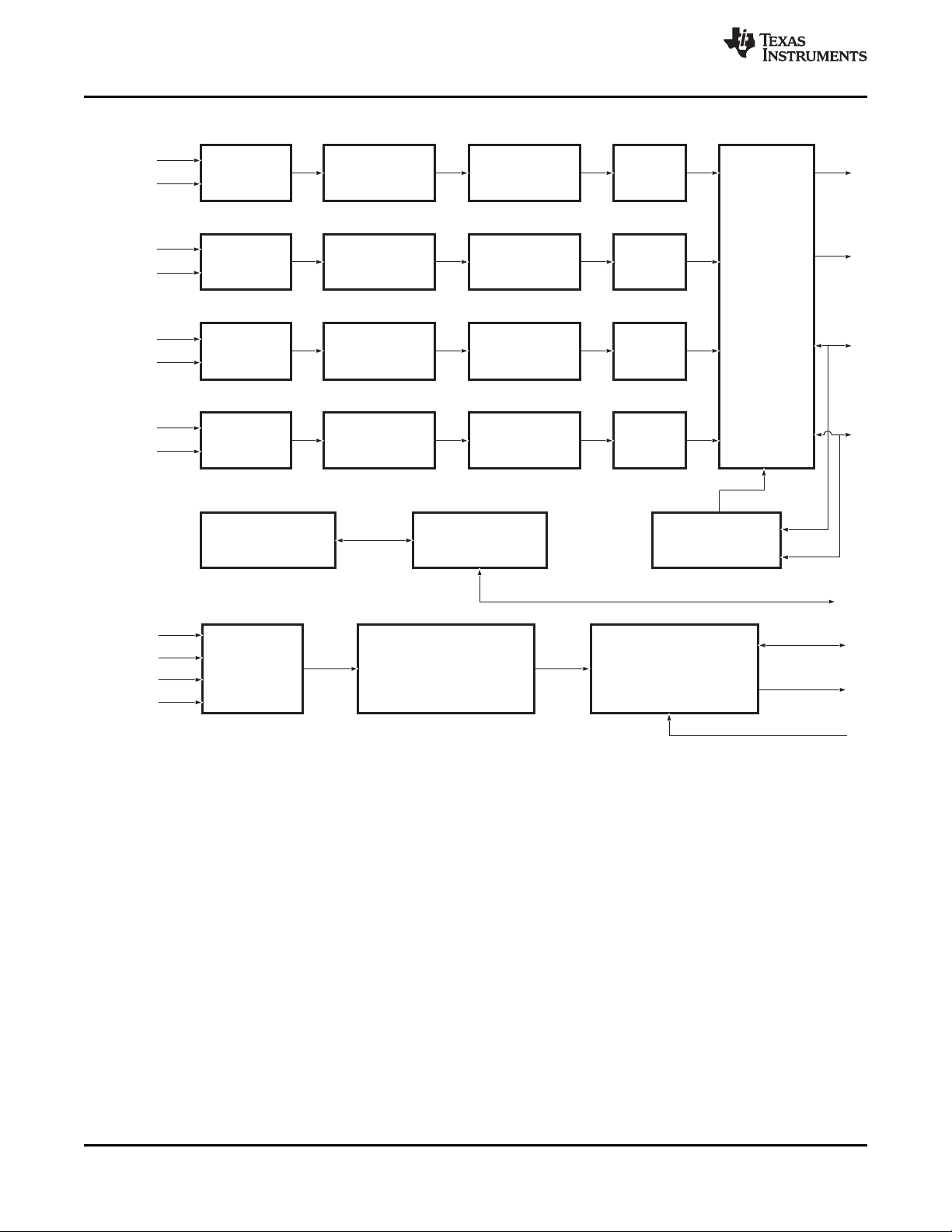

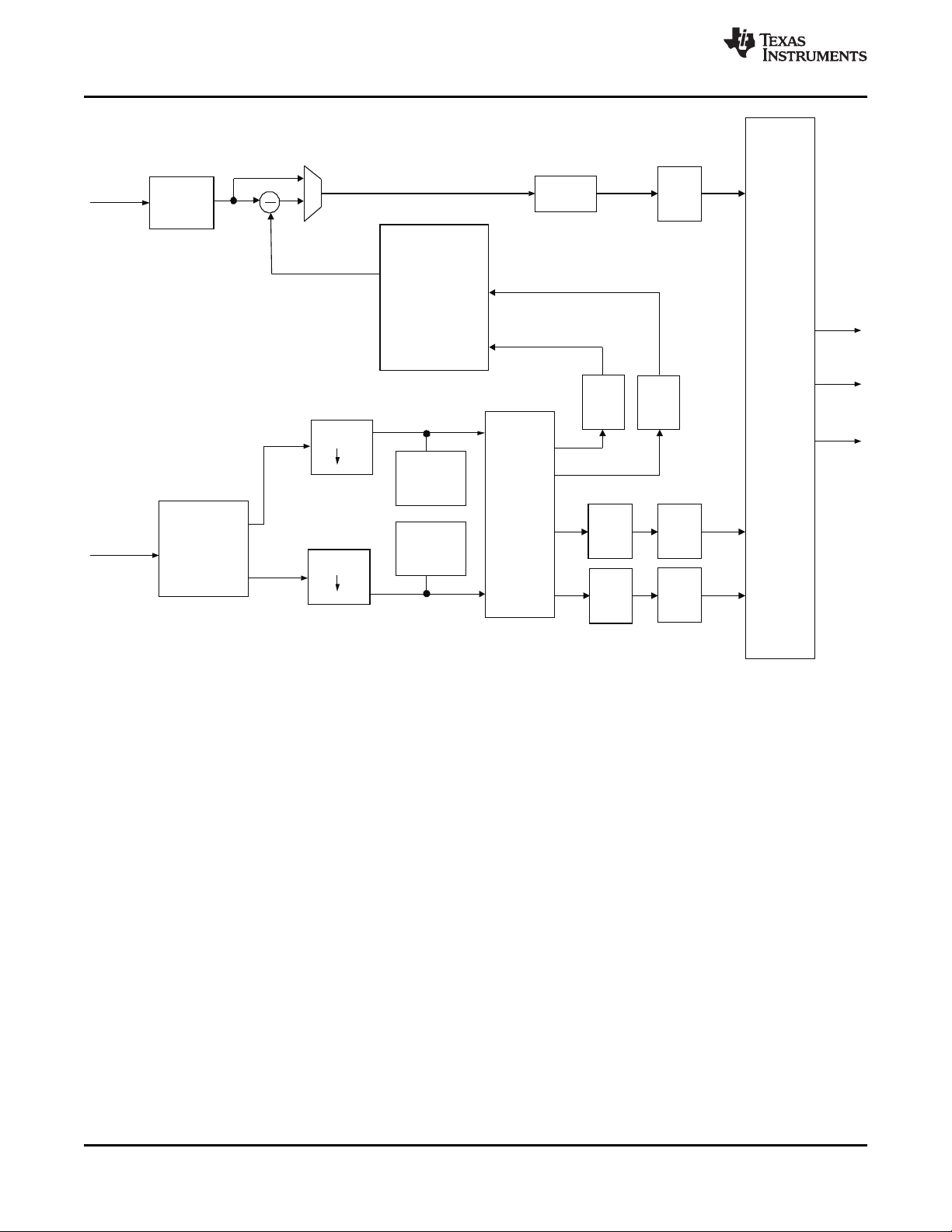

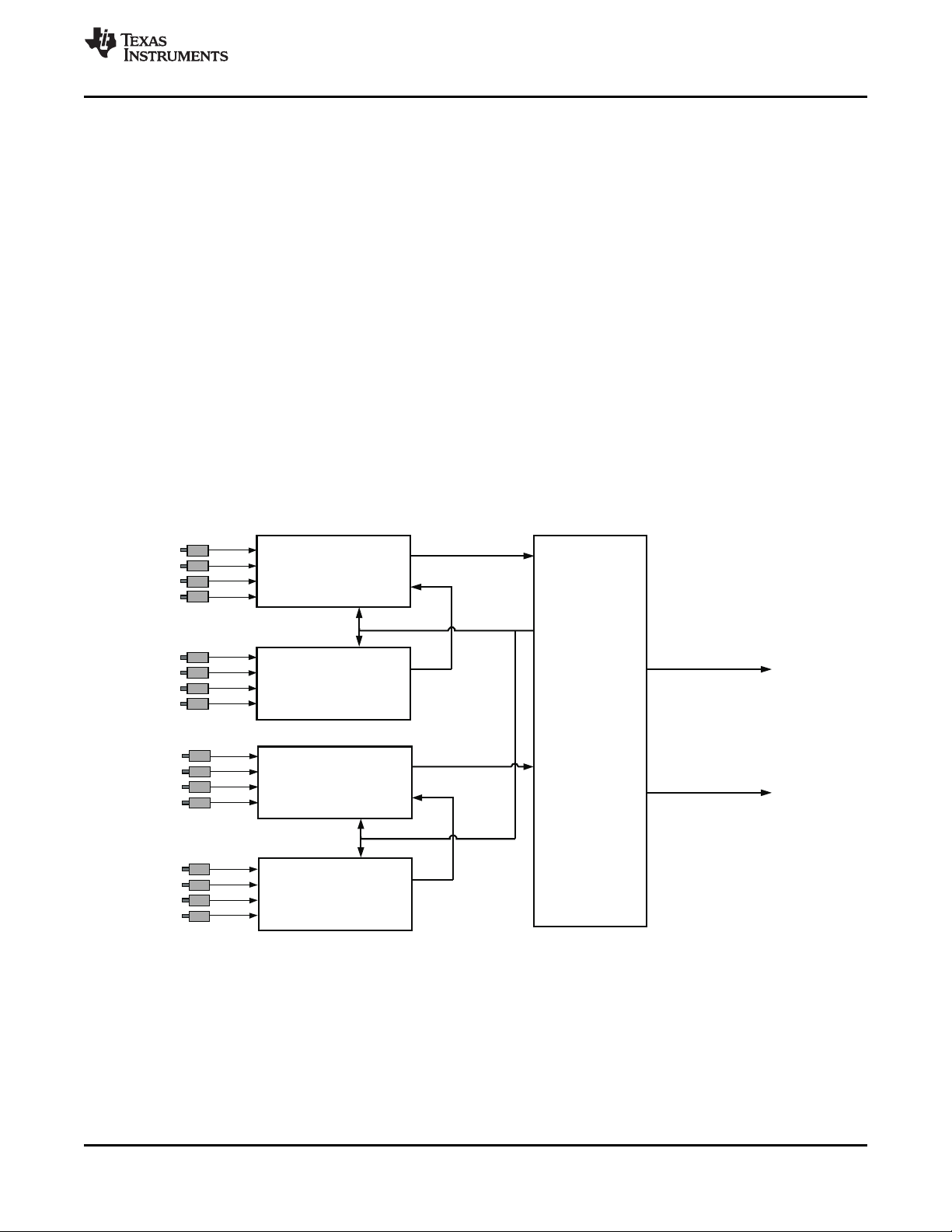

10-Bit

ADC

VIN_1_P

VIN_1_N

Y/C

Separation

Noise Reduction/

Auto Contrast

Scaler

VIN_2_P

VIN_2_N

VIN_3_P

VIN_3_N

VIN_4_P

VIN_4_N

Output

Formattor

DVO_A_[7:0]

Delay Match

and Re-Sync

Cascade

Input

ARM/Memory

Registers

I C Host port

2

Audio

ADC

AIN_1

AIN_2

AIN_3

AIN_4

Decimation Filter

and Mixer

I C

2

I S Encoder

2

Audio Cascade Input

BCLK_R

LRCLK_R

SD_R/SD_M

SD_CO

Y/C

Separation

Y/C

Separation

10-Bit

ADC

10-Bit

ADC

Y/C

Separation

10-Bit

ADC

Scaler

Scaler

Scaler

Noise Reduction/

Auto Contrast

Noise Reduction/

Auto Contrast

Noise Reduction/

Auto Contrast

DVO_B_[7:0]

DVO_C_[7:0]

DVO_D_[7:0]

TVP5158, TVP5157, TVP5156

SLES243D–JULY 2009–REVISED OCTOBER 2010

1.8 Functional Block Diagram

www.ti.com

Figure 1-1. Functional Block Diagram

12 Introduction Copyright © 2009–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TVP5158 TVP5157 TVP5156

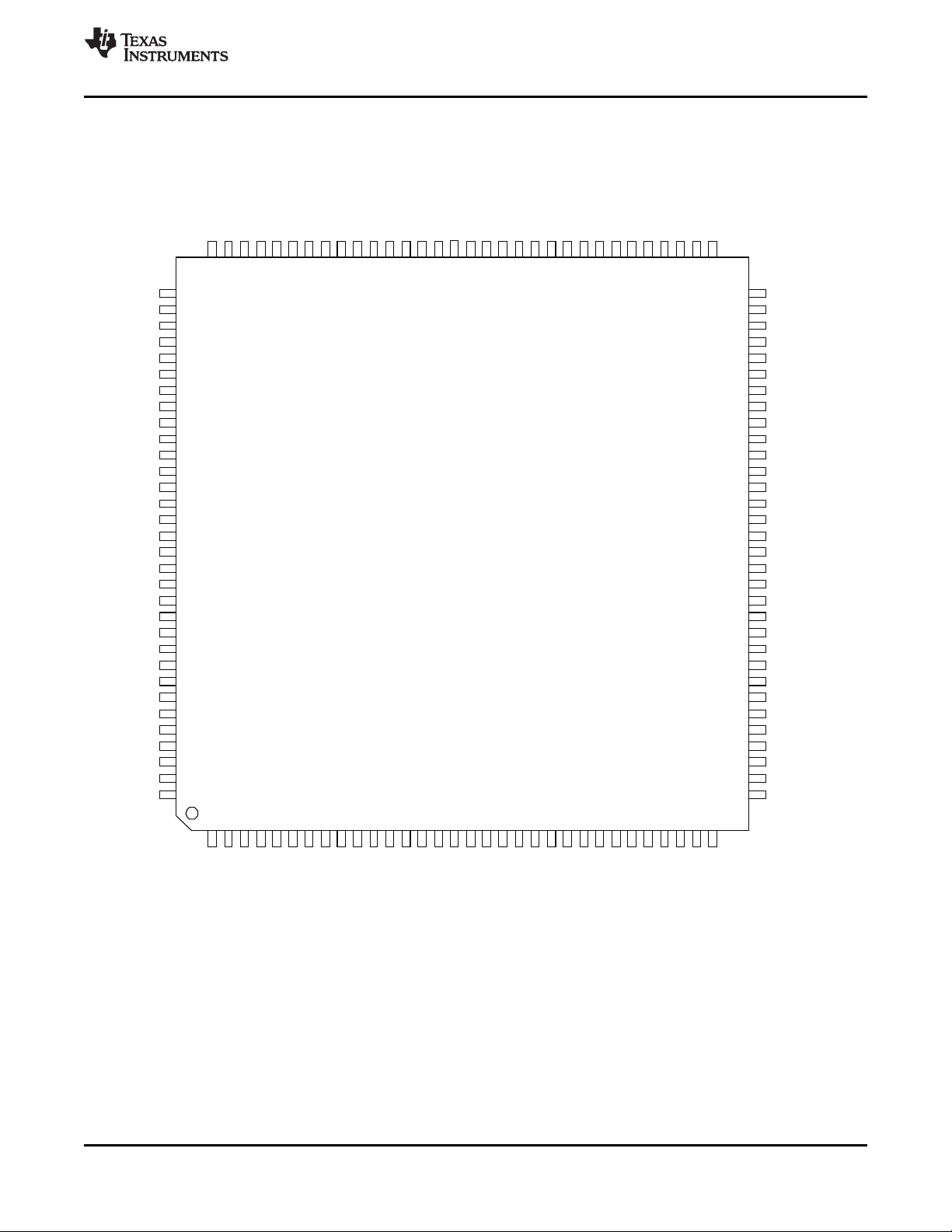

96

VSSA95AIN_194AIN_2

93 AIN_3

92

AIN_491VDDA_1_890VSS

89 SD_M

88

SD_R

87

VSS

86

LRCLK_R85BCLK_R

84 VDD_1_1

83

SD_CO

82

VSS81VDD_3_3

80 I2CA0

79

VSS

78

DVO_A_0

77

DVO_A_176VDD_1_1

75 DVO_A_2

74

DVO_A_373VSS

72

DVO_A_4

71 DVO_A_5

70

VDD_3_369DVO_A_6

68

DVO_A_767VDD_1_1

66 I2CA1

65

VSS

64

VDD_1_1

63

DVO_B_0

62

DVO_B_1

61 VSS

60

DVO_B_2

59

DVO_B_3

58

VDD_3_3

57 DVO_B_4

56

DVO_B_5

55

VSS

54

DVO_B_6

53 DVO_B_7

52

VDD_1_1

51

OCLK_N/CLKIN

50

OCLK_P

49 VSS

48

I2CA2

47

VSS

46

DVO_C_0

45 DVO_C_1

44

VDD_1_1

43

DVO_C_2

42

DVO_C_3

41 VDD_3_3

40

DVO_C_4

39

DVO_C_5

38

VSS

37 DVO_C_6

36

DVO_C_7

35

VDD_1_1

34

NC

33 VSS

1VSS

2

INTREQ3RESETB

4SCL

5

SDA

6

VSS

7

T1

8T2

9

T310T411T5

12

VSS

13VDD_1_1

14

VSS

15

VDD_3_3

16

LRCLK_CI

17BCLK_CI

18

VDD_1_1

19

SD_CI

20

VSS

21

DVO_D_722DVO_D_623VDD_1_124DVO_D_525DVO_D_4

26VSS

27

DVO_D_328DVO_D_229VDD_3_330DVO_D_131DVO_D_032VDD_1_1

97

OSC_OUT

98

VSSA

99XTAL_IN

100XTAL_REF

101

XTAL_OUT

102

VDDA_1_8

103VDDA_1_1

104

VSSA

105

VSSA

106VDDA_1_1

107VDDA_1_8

108VIN_1_P

109VIN_1_N

110

VSSA

111

VSSA

112VIN_2_P

113VIN_2_N

114VDDA_1_8

115VDDA_1_8

116REXT_2K

117

VSSA

118

VSSA

119VDDA_1_1

120VDDA_1_8

121VIN_3_P

122VIN_3_N

123

VSSA

124

VSSA

125VIN_4_P

126VIN_4_N

127VDDA_1_8

128VDAA_3_3

TVP5158

128-Pin TQFP Package

TVP5158, TVP5157, TVP5156

www.ti.com

2 Terminal Assignments

2.1 Pinout

SLES243D–JULY 2009–REVISED OCTOBER 2010

Copyright © 2009–2010, Texas Instruments Incorporated Terminal Assignments 13

Submit Documentation Feedback

Product Folder Link(s): TVP5158 TVP5157 TVP5156

TVP5158, TVP5157, TVP5156

SLES243D–JULY 2009–REVISED OCTOBER 2010

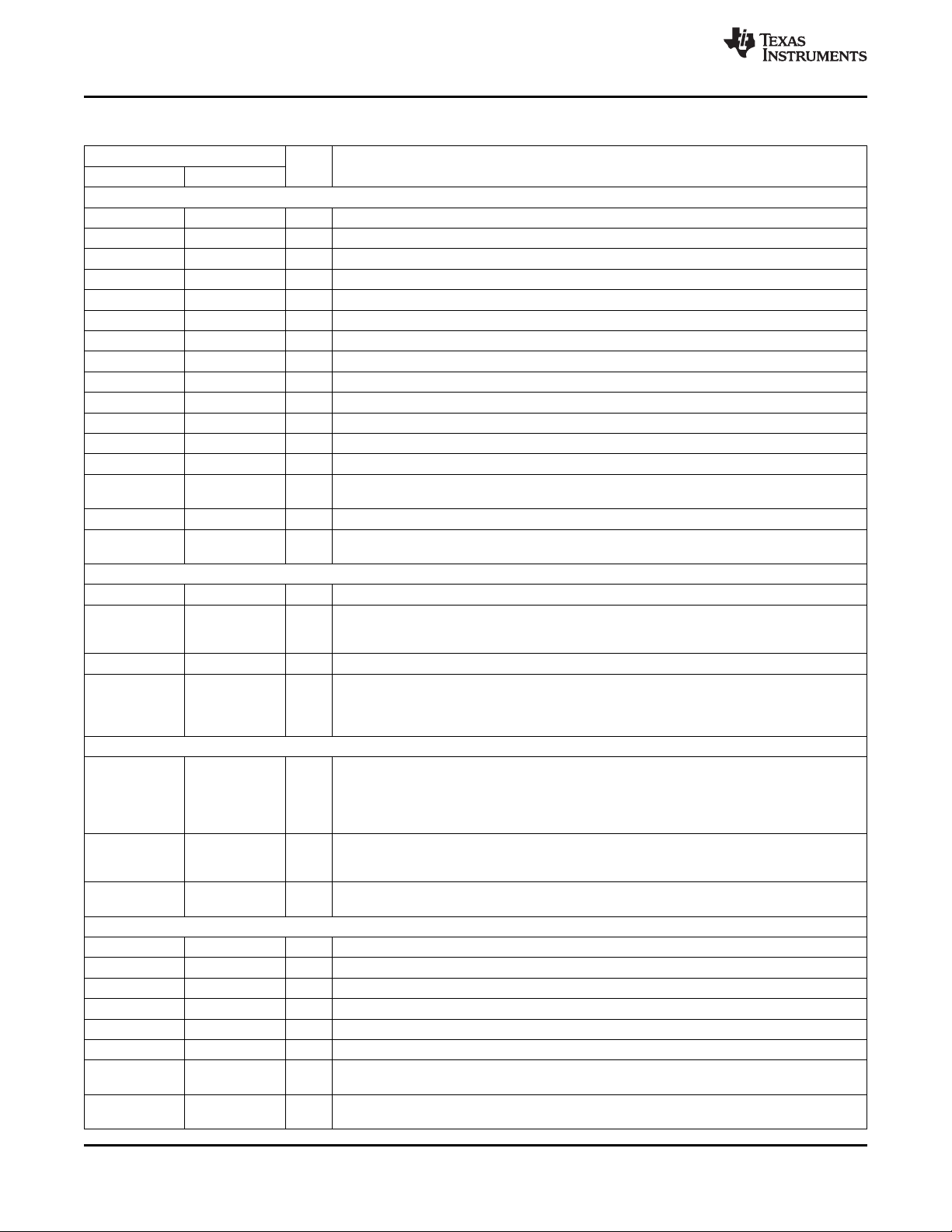

Table 2-1. Terminal Functions

TERMINAL

NAME NO.

Analog Section

VIN_1_P 108 I Analog video input for ADC channel 1.

VIN_1_N 109 I Common-mode reference input for ADC channel 1.

VIN_2_P 112 I Analog video input for ADC channel 2.

VIN_2_N 113 I Common-mode reference input for ADC channel 2.

VIN_3_P 121 I Analog video input for ADC channel 3.

VIN_3_N 122 I Common-mode reference input for ADC channel 3.

VIN_4_P 125 I Analog video input for ADC channel 4.

VIN_4_N 126 I Common-mode reference input for ADC channels.

REXT_2K 116 I External resistor for AFE bias generator. Connect external 1.8kΩ resistor to ground.

AIN_1 95 I Analog audio input for channel 1 (No Connect for TVP5156 Only)

AIN_2 94 I Analog audio input for channel 2 (No Connect for TVP5156 Only)

AIN_3 93 I Analog audio input for channel 3 (No Connect for TVP5156 Only)

AIN_4 92 I Analog audio input for channel 4 (No Connect for TVP5156 Only)

XTAL_IN 99 I

XTAL_REF 100 G Crystal reference. Connected to analog ground internally.

XTAL_OUT 101 O

Analog Power

VDDA_1_1 103, 106, 119 P 1.1V analog supply

VDDA_1_8 114, 115, 120, P 1.8V analog supply

VDDA_3_3 128 P 3.3V analog supply for all 4 video channels

VSSA G Analog ground

Digital Power

VSS 49, 55, 61, 65, G Digital ground

VDD_1_1 35, 44, 52, 64, P Digital core supply. Connect to 1.1-V digital supply.

VDD_3_3 P Digital I/O supply. Connect to 3.3-V digital supply.

Digital Section

INTREQ 2 O Interrupt request. Interrupt signal to host processor.

RESETB 3 I Reset. An active low signal that controls the reset state.

SCL 4 I/O I2C serial clock (open drain)

SDA 5 I/O I2C serial data (open drain)

OSC_OUT 97 O Buffered crystal oscillator output. 1.8-V compatible.

OCLK_P 51 O Output data clock+. All 4 digital video output ports are synchronized to this clock.

OCLK_N/CLKIN 50 I/O

DVO_A_[7:0] O Digital video output data bus.

91, 102, 107,

127

96, 98, 104,

105, 110, 111,

117, 118, 123,

124

1, 6, 12, 14, 20,

26, 33, 38, 47,

73, 79, 82, 87,

90

13, 18, 23, 32,

67, 76, 84

15, 29, 41, 58,

70, 81

68, 69, 71, 72,

74, 75, 77, 78

I/O DESCRIPTION

External clock reference input. It may be connected to external oscillator with 1.8-V compatible

clock signal or 27.0-MHz crystal oscillator.

External clock reference output. Not connected if XTAL_IN is driven by an external

single-ended oscillator.

Output data clock- for 2-Ch time-multiplexed mode or data clock input for 8-Ch video cascade

mode

www.ti.com

14 Terminal Assignments Copyright © 2009–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TVP5158 TVP5157 TVP5156

TVP5158, TVP5157, TVP5156

www.ti.com

SLES243D–JULY 2009–REVISED OCTOBER 2010

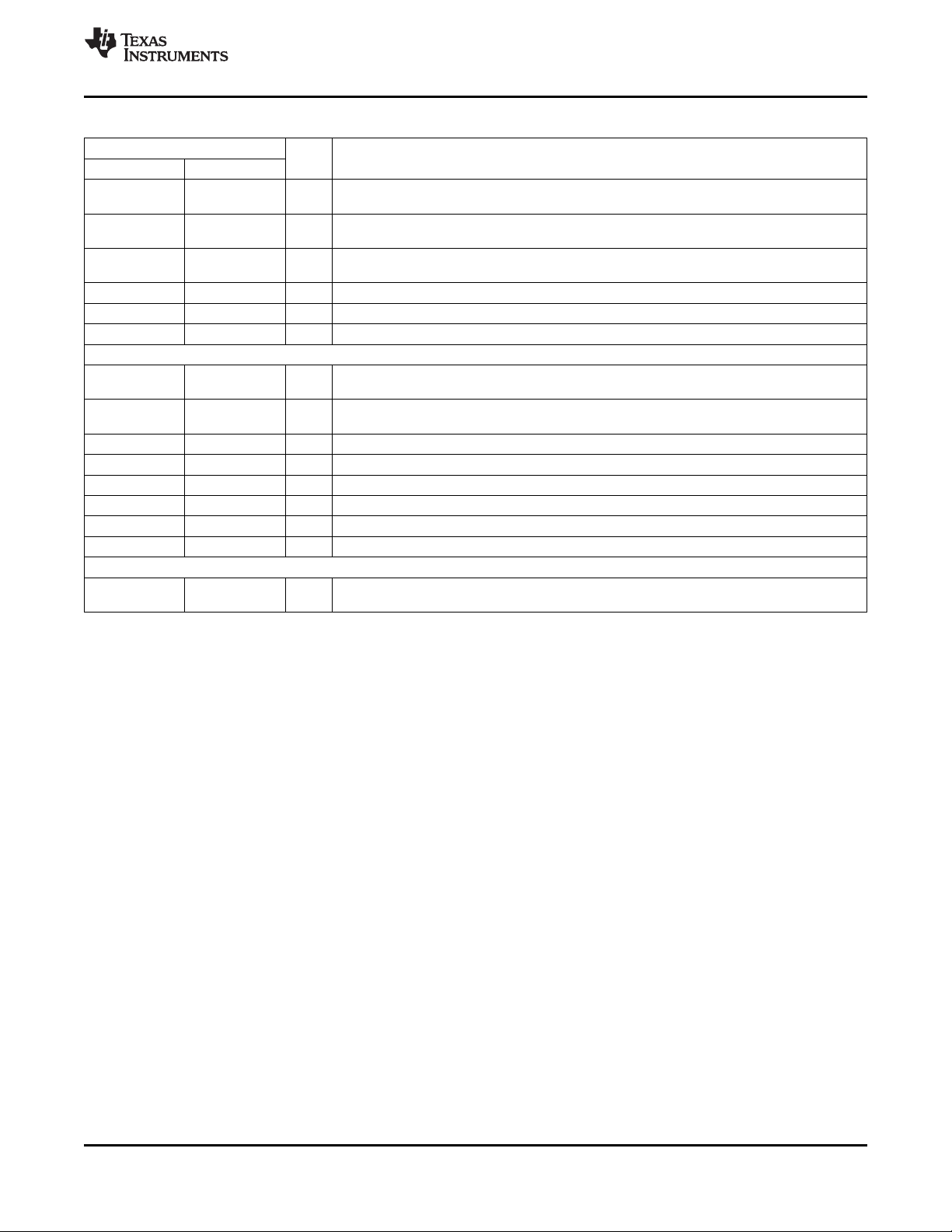

Table 2-1. Terminal Functions (continued)

TERMINAL

NAME NO.

DVO_B_[7:0] O Digital video output data bus.

DVO_C_[7:0] I/O

DVO_D_[7:0] I/O

I2CA0 80 I I2C slave address bit 0

I2CA1 66 I I2C slave address bit 1

I2CA2 48 I I2C slave address bit 2

Digital Audio Section (Not supported on TVP5156)

BCLK_R 85 I/O

LRCLK_R 86 I/O

SD_R 88 O I2S serial data output for recording.

SD_M 89 O I2S serial data output for mixed audio or recording.

SD_CO 83 O Audio serial data output for cascade mode

LRCLK_CI 16 I I2S left/right clock input for cascade mode. Also known as I2S word select (WS).

BCLK_CI 17 I I2S bit clock input for cascade mode. Also known as I2S serial clock (SCK).

SD_CI 19 I Audio serial data input for cascade mode.

No Connect Pins

T1, T2, T3, T4, 7, 8, 9, 10, 11,

T5, NC 34

53, 54, 56, 57,

59, 60, 62, 63

36, 37, 39, 40, Digital video output data bus. In cascade mode, all pins operate as input from another

42, 43, 45, 46 TVP5158 device.

21, 22, 24, 25, Digital video output data bus. In cascade mode, all pins operate as input from another

27, 28, 30, 31 TVP5158 device.

I/O DESCRIPTION

I2S bit clock for recording. Also known as I2S serial clock (SCK). Supports master and slave

modes.

I2S left/right clock for recording. Also known as I2S word select (WS). Supports master and

slave modes.

NC For normal operation, no connect

Copyright © 2009–2010, Texas Instruments Incorporated Terminal Assignments 15

Submit Documentation Feedback

Product Folder Link(s): TVP5158 TVP5157 TVP5156

Anti-Aliasing

Filter

Analog

CVBS Input

Clamp

ADC

Reference & Bias

Output to

Digital

Processing

Frequency Response

-35

-30

-25

-20

-15

-10

-5

0

5

- 5 1 0 1 5 2 0 25

Freq uency ( MHz)

Gain(dB)

TVP5158, TVP5157, TVP5156

SLES243D–JULY 2009–REVISED OCTOBER 2010

3 Functional Description

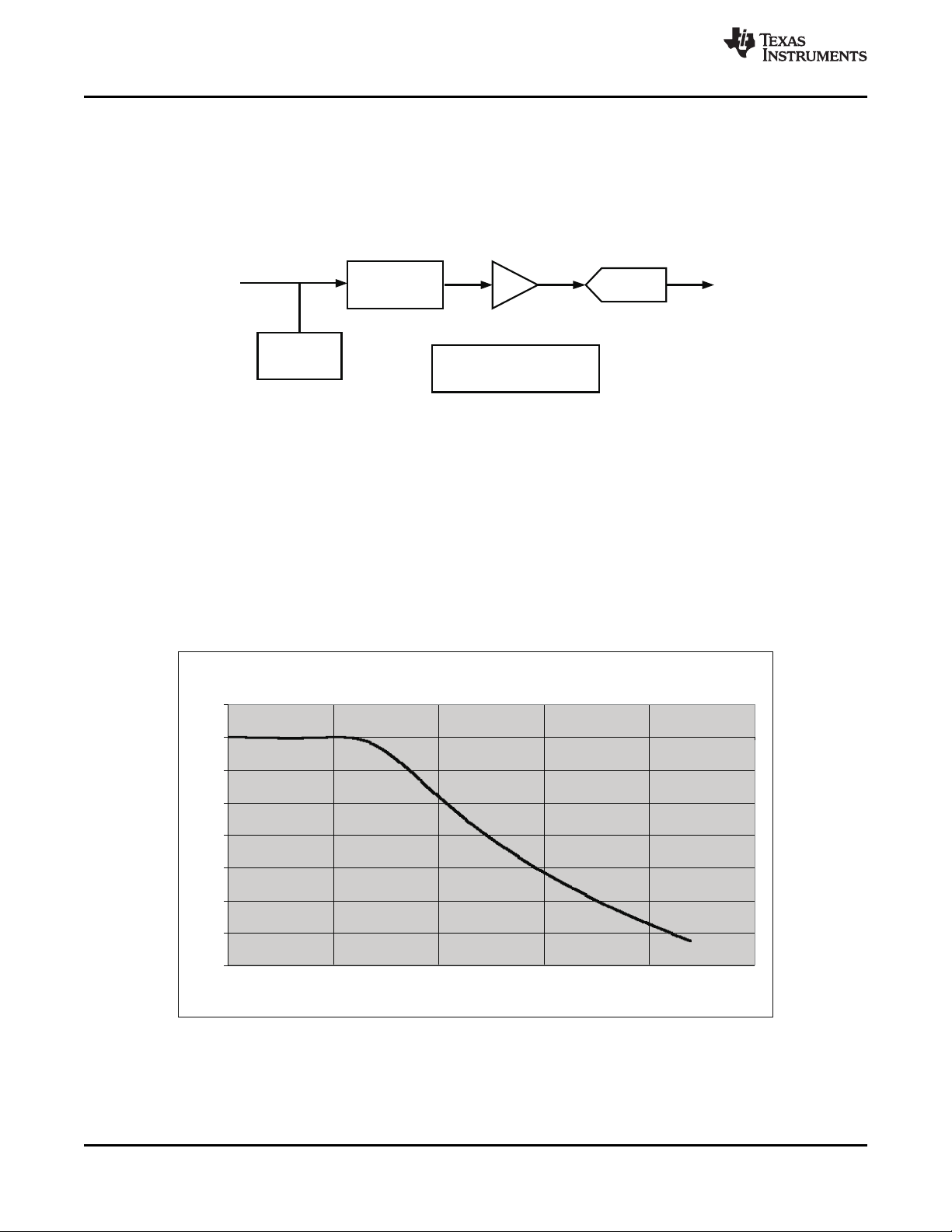

3.1 Analog Video Processing and A/D Converters

Each video decoder accepts one composite video input and performs video clamping, anti-aliasing

filtering, video amplification, A/D conversion, and gain and offset adjustments to center the digitized video

signal. Figure 3-1 shows the video analog processing and ADC block diagram.

Figure 3-1. Video Analog Processing and ADC Block Diagram

3.1.1 Analog Video Input

Supports NTSC (J, M, 4.43) and PAL (B, D, G, H, I, M, N, Nc, 60) video standards. Each video decoder

channel supports a composite video input with a pseudo-differential pin which improves the noise

immunity and analog performance.

www.ti.com

Each video decoder input should be ac-coupled through a 0.1-µF capacitor. The nominal parallel

termination resistor before the input to the device is 75 Ω.

Each video decoder integrates an anti-aliasing filter to provide good stop-band rejection on the analog

video input signal. Figure 3-2 shows the frequency response of the anti-aliasing filter.

Figure 3-2. Anti-Aliasing Filter Frequency Response

16 Functional Description Copyright © 2009–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TVP5158 TVP5157 TVP5156

TVP5158, TVP5157, TVP5156

www.ti.com

3.1.2 Analog Video Input Clamping

An internal clamping circuit provides dc restoration for all four analog composite video inputs. The dc

restoration circuit (sync-tip clamp) restores sync-tip level of the ac-coupled composite video signal to a

fixed dc level near the bottom of the A/D converter range.

3.1.3 A/D Converter

All ADCs have a resolution of 10 bits and can operate at 27 MSPS. Each A/D channel receives a clock

from the on-chip phase-locked loop (PLL) at a nominal frequency of 27 MHz. All ADC reference voltages

are generated internally.

3.2 Digital Video Processing

Digital Video Processing block receives digitized video signals from the ADCs and performs composite

processing and YCbCr signal enhancements. The digital data output can be programmed to two formats:

ITU-R BT.656 8-bit 4:2:2 with embedded syncs or 16-bit 4:2:2 with embedded syncs. The circuit also

detects pseudo-sync pulses, AGC pulses, and color striping in Macrovision-encoded copy-protected

material.

3.2.1 2x Decimation Filter

All input signals are over-sampled by a factor of 2 (by 27-MHz clock). The A/D outputs initially pass

through decimation filters that reduce the data rate to 1x the pixel rate. The decimation filter is a half-band

filter. Over-sampling and decimation filtering can effectively increase the overall signal-to-noise ratio by

3 dB.

SLES243D–JULY 2009–REVISED OCTOBER 2010

3.2.2 Automatic Gain Control

The automatic gain control (AGC) can be enabled and can adjust the signal amplitude controlled by 14-bit

digital gain stage after the ADC. The AGC algorithms can use up to four amplitude references: sync

height, color burst amplitude, composite peak, and luma peak.

The specific amplitude references being used by the AGC algorithms can be controlled using the AGC

white peak processing register located at sub-address 2Dh. The gain increment speed and gain increment

delay can be controlled using the AGC increment speed register located at sub-address 29h and the AGC

increment delay register located at sub-address 2Ah. The gain decrement speed and gain decrement

delay can be controlled using the AGC decrement speed register located at sub-address 2Bh and the

AGC decrement delay register located at sub-address 2Ch.

3.2.3 Composite Processor

This Composite Processor circuit receives a digitized composite signal from the ADCs and performs sync

and Y/C separation, chroma demodulation for PAL/NTSC, and YUV signal enhancements. The slice levels

of the sync separator are adaptive. The slice levels continually adapt to changes in the back-porch and

sync-tip levels. The 10-bit composite video is multiplied by the sub carrier signals in the quadrature

demodulator to generate U and V color difference signals. The U and V signals are then sent to low-pass

filters to achieve the desired bandwidth. An adaptive 5-line comb filter separates UV from Y based on the

unique property of color phase shifts from line to line. The chroma is re-modulated through a quadrature

modulator and subtracted from line-delayed composite video to generate luma. This form of Y/C

separation is completely complementary, thus there is no loss of information. However, in some

applications, it is desirable to limit the U/V bandwidth to avoid crosstalk. In that case, notch filters can be

turned on. To accommodate some viewing preferences, a peaking filter is also available in the luma path.

Contrast, brightness, sharpness, hue, and saturation controls are programmable through the I2C host port.

Figure 3-3 shows the block diagram of Composite Processor.

Copyright © 2009–2010, Texas Instruments Incorporated Functional Description 17

Submit Documentation Feedback

Product Folder Link(s): TVP5158 TVP5157 TVP5156

Color LPF

2

5 Line

Adaptive

Comb Filter

Notch

Filter

Notch

Filter

Delay

Delay

Contrast

Brightness

Saturation

Adjust

Color LPF

2

Y

Cb

Cr

U

V

Notch

Notch

Delay

Y

Peaking

NTSC/PAL

Remodulation

NTSC/PAL

Demodulation

Line

Delay

CVBS

CVBS

Burst

Accumulator

(U)

Burst

Accumulator

(V)

Filter

Filter

TVP5158, TVP5157, TVP5156

SLES243D–JULY 2009–REVISED OCTOBER 2010

www.ti.com

Figure 3-3. Composite Processor Block Diagram

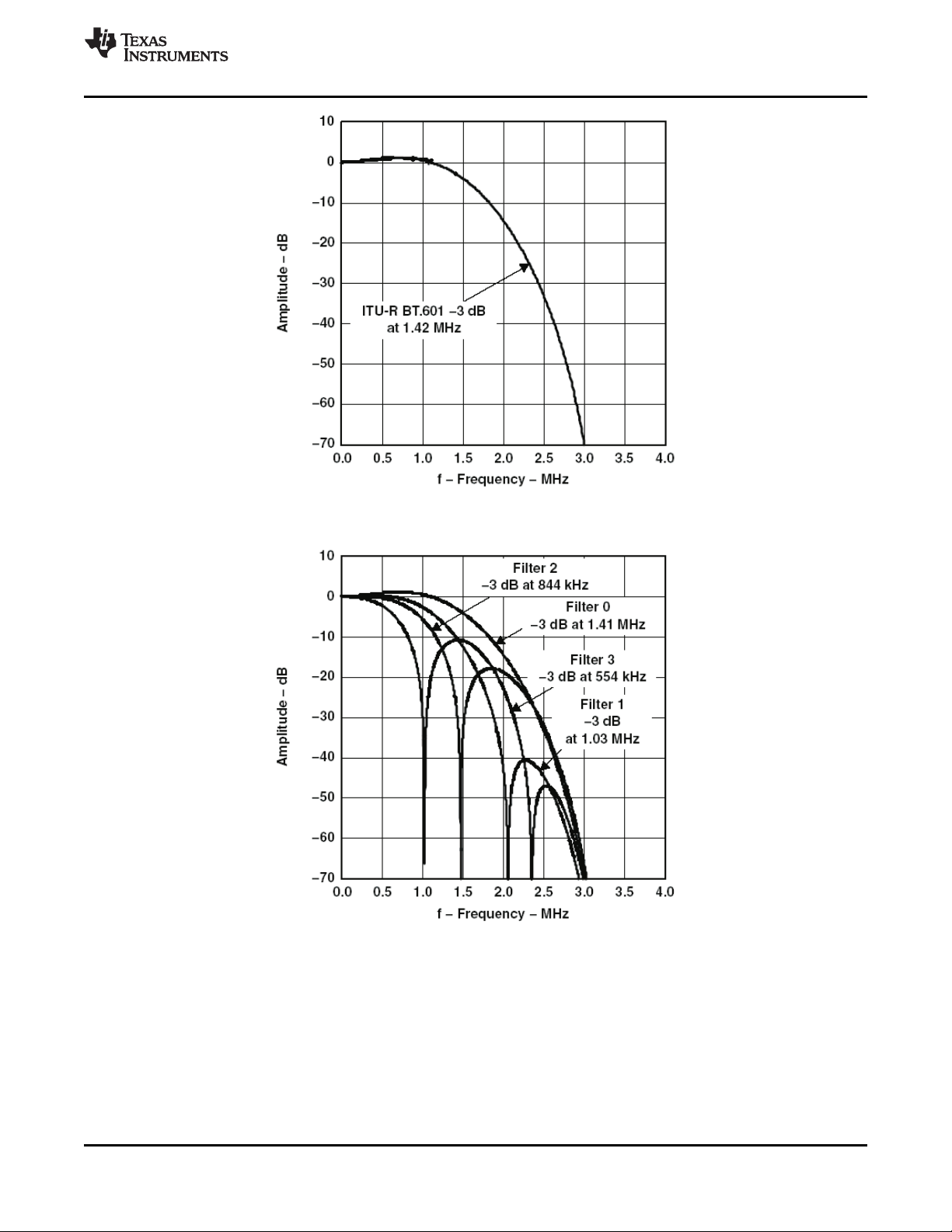

3.2.3.1 Color Low-Pass Filter

High filter bandwidth preserves sharp color transitions and produces crisp color boundaries. However, for

nonstandard video sources that have asymmetrical U and V side bands, it is desirable to limit the filter

bandwidth to avoid UV crosstalk. The color low-pass filter bandwidth is programmable to enable one of the

three notch filters. Figure 3-4 and Figure 3-5 represent the frequency responses of the wideband color

low-pass filters.

18 Functional Description Copyright © 2009–2010, Texas Instruments Incorporated

Product Folder Link(s): TVP5158 TVP5157 TVP5156

Submit Documentation Feedback

TVP5158, TVP5157, TVP5156

www.ti.com

SLES243D–JULY 2009–REVISED OCTOBER 2010

Figure 3-4. Color Low-Pass Filter Frequency Response

Figure 3-5. Color Low-Pass Filter with Filter Characteristics, NTSC/PAL ITU-R BT.601 Sampling

3.2.3.2 Y/C Separation

Y/C separation can be done using adaptive 5-line (5-H delay) comb filters or a chroma trap filter. The

comb filter can be selectively bypassed in the luma or chroma path. If the comb filter is bypassed in the

luma path, then chroma trap filters are used which are shown in Figure 3-6 and Figure 3-7. The TI

patented adaptive comb filter algorithm reduces artifacts such as hanging dots at color boundaries. It

detects and properly handles false colors in high-frequency luminance images such as a multiburst pattern

or circle pattern.

Copyright © 2009–2010, Texas Instruments Incorporated Functional Description 19

Submit Documentation Feedback

Product Folder Link(s): TVP5158 TVP5157 TVP5156

Peak

Detector

Bandpass

Filter

Peaking

Filter

Delay

IN

Gain

OUT

+

x

TVP5158, TVP5157, TVP5156

SLES243D–JULY 2009–REVISED OCTOBER 2010

Figure 3-6. Chroma Trap Filter Frequency Response, NTSC ITU-R BT.601 Sampling

www.ti.com

Figure 3-7. Chroma Trap Filter Frequency Response, PAL ITU-R BT.601 Sampling

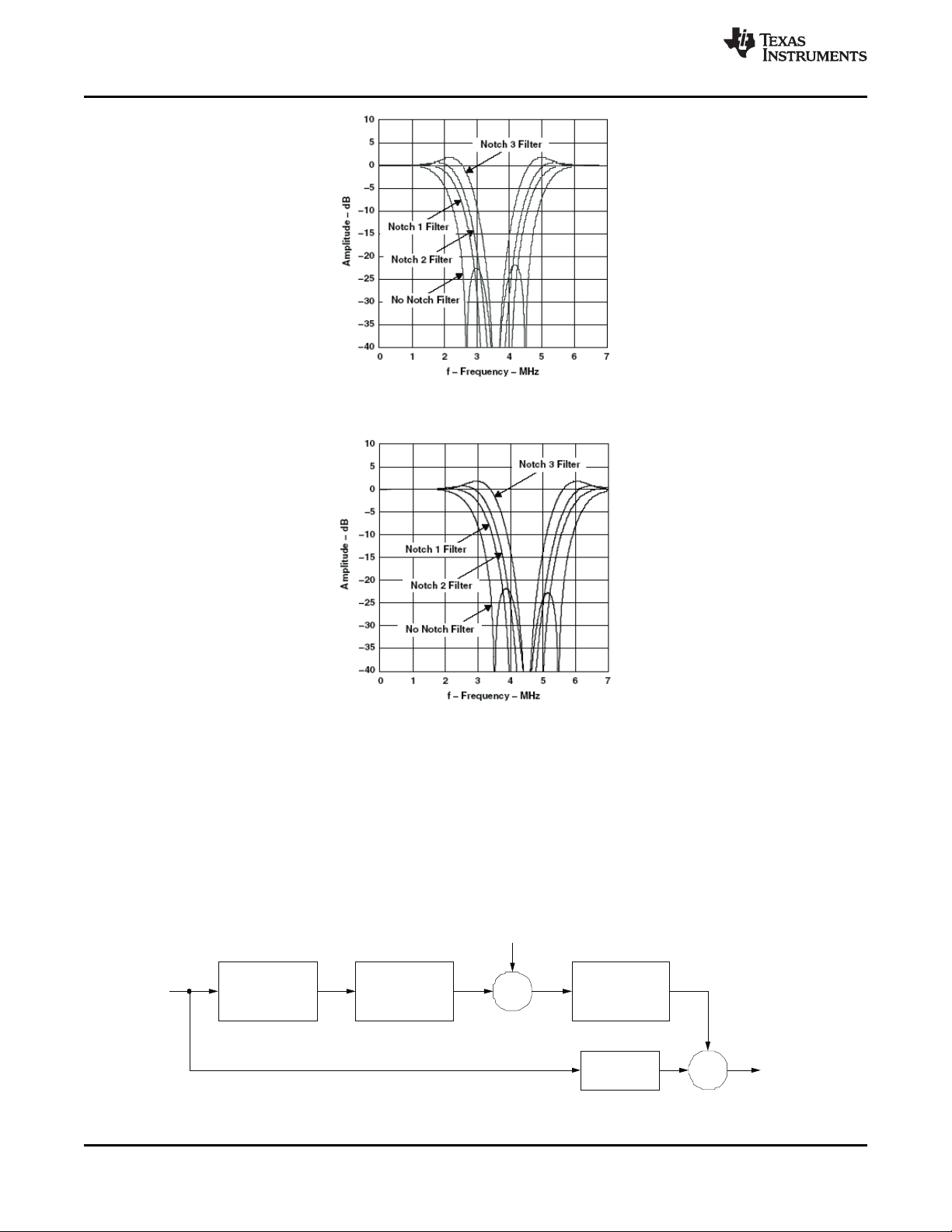

3.2.4 Luminance Processing

The digitized composite video signal passes through either a luminance comb filter or a chroma trap filter,

either of which removes chrominance information from the composite signal to generate a luminance

signal. The luminance signal is then fed into the input of a peaking circuit. Figure 3-8 shows the basic

functions of the luminance data path. A peaking filter (edge enhancer) amplifies high-frequency

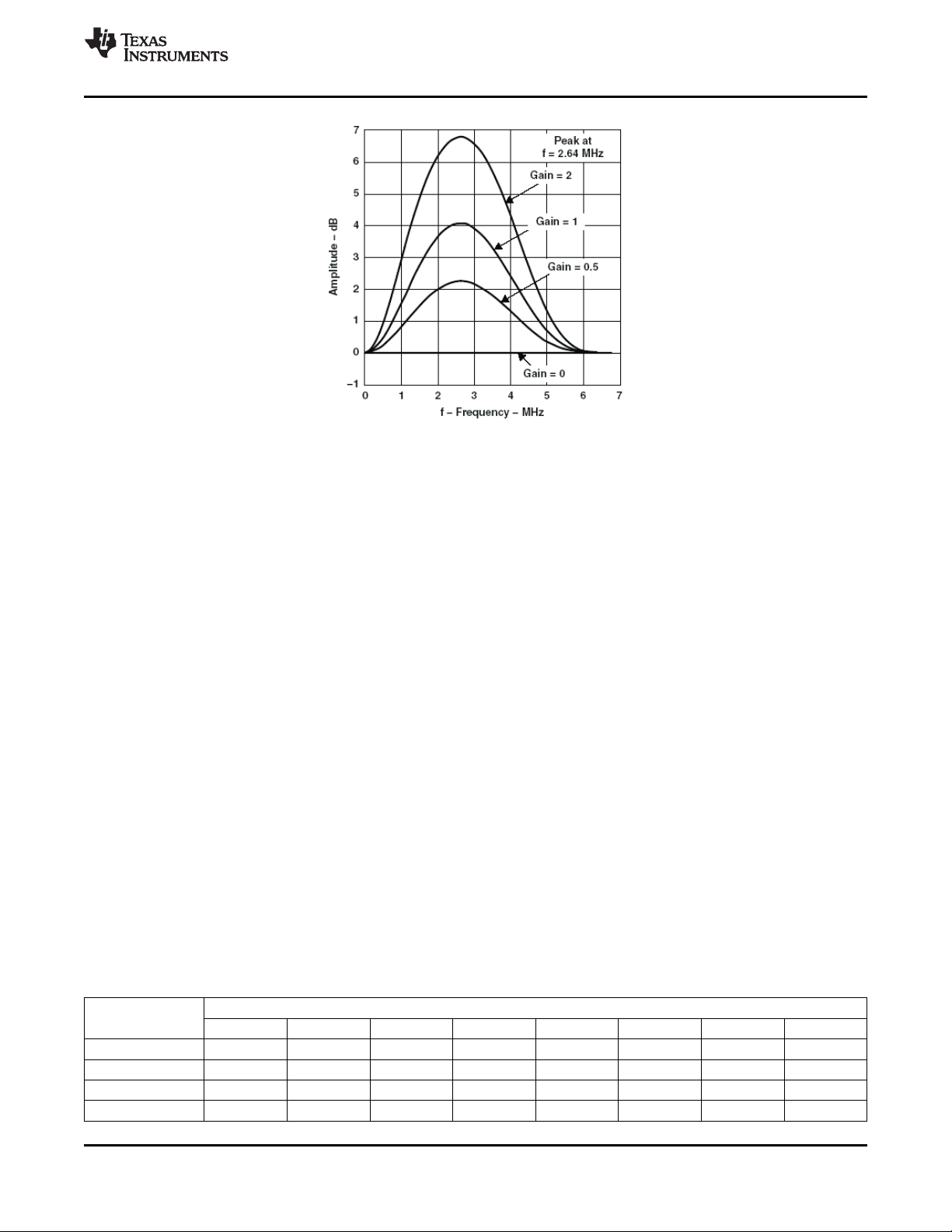

components of the luminance signal. Figure 3-9 shows the characteristics of the peaking filter at four

different gain settings that are user-programmable via the I2C interface.

20 Functional Description Copyright © 2009–2010, Texas Instruments Incorporated

Figure 3-8. Luminance Edge-Enhancer Peaking Block Diagram

Submit Documentation Feedback

Product Folder Link(s): TVP5158 TVP5157 TVP5156

TVP5158, TVP5157, TVP5156

www.ti.com

Figure 3-9. Peaking Filter Response, NTSC/PAL ITU-R BT.601 Sampling

3.3 AVID Cropping

AVID or active video cropping provides a means to decrease the amount of video data output. This is

accomplished by horizontally blanking a number of AVID pulses and by vertically blanking a number of

lines per frame. Horizontal cropping can be enabled/disabled using bit-6 of address B1h. When line

cropping is enabled, active video will be reduced from 720 to 704 pixels for unscaled video and from 360

to 352 pixels for down-scaled video.

SLES243D–JULY 2009–REVISED OCTOBER 2010

When line cropping is enabled, the TVP5158 crops an equal amount from both the start and end of active

video. Register 8Ch can be used to delay both the start and end of active video. It allows selecting which

704 pixels out of 720 are actually being used for active video when line cropping is enabled.

3.4 Embedded Syncs

Standards with embedded syncs insert SAV and EAV codes into the data stream at the beginning and end

of horizontal blanking. These codes contain the V and F bits which also define vertical timing. F and V

change on EAV. Table 3-1 gives the format of the SAV and EAV codes.

H equals 1 always indicates EAV. H equals 0 always indicates SAV. The alignment of V and F to the line

and field counter varies depending on the standard. Please refer to ITU-R BT.656 for more information on

embedded syncs.

The P bits are protection bits:

P3 = V xor H

P2 = F xor H

P1 = F xor V

P0 = F xor V xor H

Table 3-1. EAV and SAV Sequence

8-BIT DATA

D7 (MSB) D6 D5 D4 D3 D2 D1 D0

Preamble 1 1 1 1 1 1 1 1

Preamble 0 0 0 0 0 0 0 0

Preamble 0 0 0 0 0 0 0 0

Status word 1 F V H P3 P2 P1 P0

Copyright © 2009–2010, Texas Instruments Incorporated Functional Description 21

Submit Documentation Feedback

Product Folder Link(s): TVP5158 TVP5157 TVP5156

TVP5158, TVP5157, TVP5156

SLES243D–JULY 2009–REVISED OCTOBER 2010

3.5 Scaler

Each video decoder has an independent horizontal and vertical scaler, which supports D1 to half-D1 or

CIF conversion. Table 3-2 gives the details of video resolution including un-cropped and cropped.

Table 3-3 shows the video resolutions converted by the scaler.

Table 3-2. Standard Video Resolutions

Format

D1 720 x 480 720 x 576 704 x 480 704 x 576

Half-D1 360 x 480 360 x 576 352 x 480 352 x 576

CIF 360 x 240 360 x 288 352 x 240 352 x 288

Table 3-3. Video Resolutions Converted by the Scaler

Scaling Ratio Format Horizontal Scaling Vertical Scaling Total Pixel

D1

D1 to Half-D1

D1 to CIF

NTSC 1:1 1:1 858 x 525 720 x 480

PAL 1:1 1:1 864 x 625 720 x 576

NTSC 2:1 1:1 429 x 525 360 x 480

PAL 2:1 1:1 432 x 625 360 x 576

NTSC 2:1 2:1 429 x 262 360 x 240

PAL 2:1 2:1 432 x 312 360 x 288

Uncropped Cropped

NTSC PAL NTSC PAL

www.ti.com

Active Output

Resolution

3.6 Noise Reduction

A video sequence shot under low light condition, which is typical of video surveillance applications, can

contain lots of noise. Human eyes are very sensitive to oscillating signals, the visual quality degenerates

significantly even when the noise level is small.

Each video decoder uses a TI proprietary spatial filter to reduce video noise. For each frame of image, the

video noise filter (VNF) produces an estimate of the Y/U/V noise. Based on the noise estimates, the

firmware adjusts the threshold for Y/U/V filtering. The filtered video shows improved video quality and

lower compression bit-rate. The firmware can also utilize the Y/U/V noise estimates to make decisions to

disable color if the video noise is determined to be too high. This "color killer" decision bit can be used to

control another module that implements the color killing function.

The Noise Reduction can be controlled using I2C registers from 50h to 5Fh. This module can also be set

to bypass mode by I2C register 5Dh (Bit 0).

3.7 Auto Contrast

The Auto Contrast (AC) module can adjust the picture brightness automatically or manually (user

programmable) for better image quality. The goal of AC processing is to make the dark area brighter and

high-light area dimmer. This makes it possible for the viewer to see details hidden in the shadows. It also

prevents loss of details in the washed-out high light area. The AC processing is mostly for video

surveillance applications.

For each frame of image, the auto contrast module collects the statistics of its Y (luminance) values. The

AC algorithm implemented in the firmware processes the statistics and generates a look-up table (LUT).

This LUT is used to map each incoming pixel Y value to an output pixel Y value for the next frame of

image. The LUT is updated during the blanking period between two frames.

The Auto Contrast Mode can be controlled by using I2C registers 0Fh. This module can also be set to

disable mode by I2C register 0Fh (Bit 1:0).

22 Functional Description Copyright © 2009–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TVP5158 TVP5157 TVP5156

TVP5158, TVP5157, TVP5156

www.ti.com

SLES243D–JULY 2009–REVISED OCTOBER 2010

3.8 Output Formatter

The output formatter is responsible for generating the output digital video stream. Table 3-4 provides a

summary of line frequencies, data rates, and pixel counts for different input standards. TVP5158 supports

non-interleaved output mode, pixel-interleaved output mode and line-interleaved output mode. The

non-interleaved mode is similar to the TVP5154A device, except that a single fixed clock output is used. In

the interleaved modes, the video output data from multiple decoder channels are multiplexed together and

then output to a single 8-bit or 16-bit port. The video output data from selected channels can be

interleaved on a pixel or line basis.

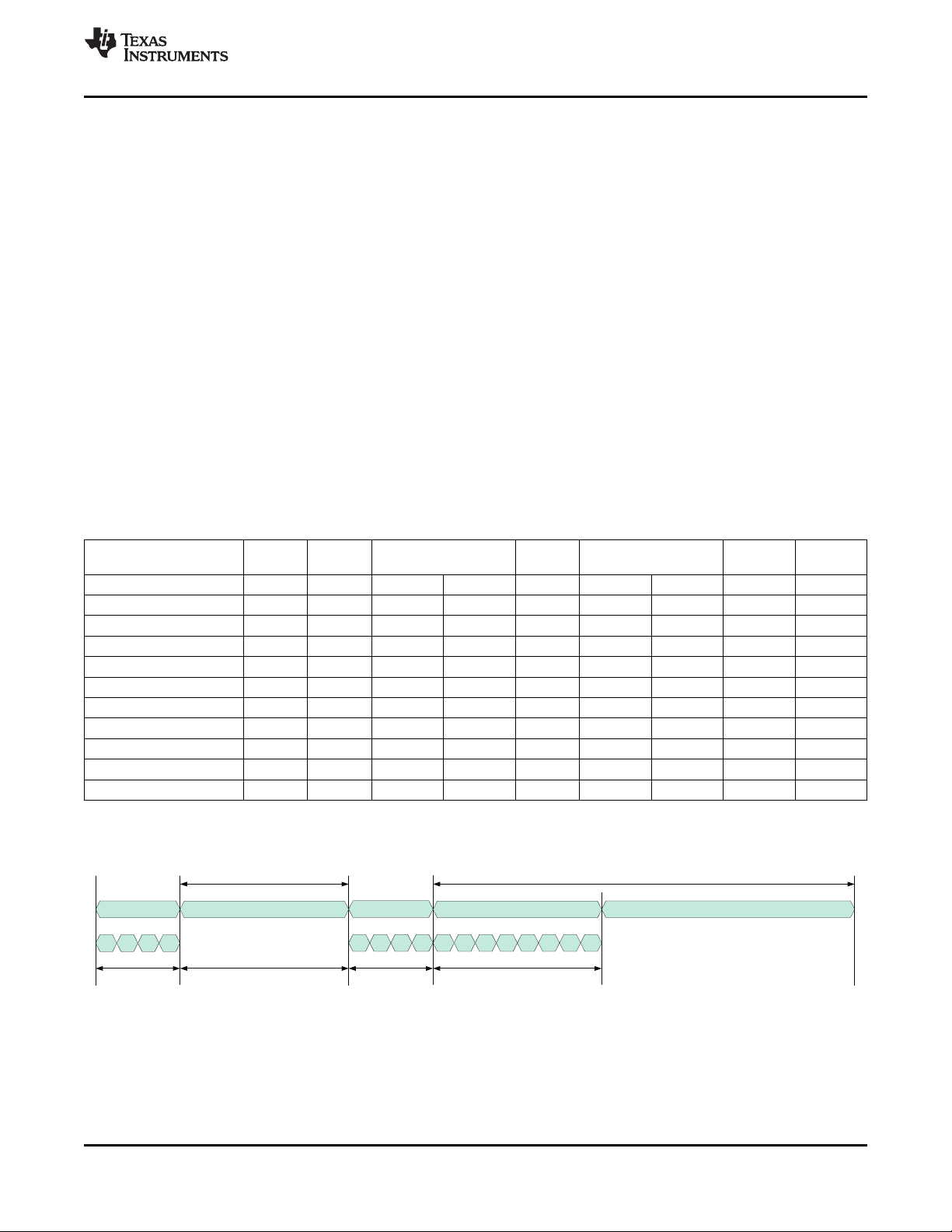

Table 3-4. Summary of Line Frequencies, Data Rates and Pixel Counts for Different Standards

Standards Active Pixels Lines per

(ITU-R BT.601) per Line Frame

NTSC-J, M 858 720 525 13.5 3.579545 15.73426

NTSC-4.43 858 720 525 13.5 4.43361875 15.73426

PAL-M 858 720 525 13.5 3.57561149 15.73426

PAL-60 858 720 525 13.5 4.43361875 15.73426

PAL-B, D, G, H, I 864 720 625 13.5 4.43361875 15.625

PAL-N 864 720 625 13.5 4.43361875 15.625

PAL-Nc 864 720 625 13.5 3.58205625 15.625

Pixels per Line Frequency Frequency Rate

Pixel Color Subcarrier Horizontal Line

(MHz) (MHz) (kHz)

3.8.1 Non-Interleaved Mode

In the non-interleaved mode, the YCbCr digital output is programmed as 8-bit ITU-R BT.656 parallel

interface standard. Depending on which output mode is selected, the output for each channel can be

un-scaled data or scaled data. Also each video output port can be selected to output the video data from

any 1 of 4 video decoders. Table 3-5 shows the detailed information about non-interleaved mode.

Table 3-5. Output Ports Configuration for Non-Interleaved Mode

Video Output Cascade I2C Address: OCLK

Format Stage B0h (MHz)

1-Ch D1 n/a 00h 27 Any 1 of 4 Ch Any 1 of 4 Ch Any 1 of 4 Ch Any 1 of 4 Ch

1-Ch Half-D1 n/a 02h 27 Any 1 of 4 Ch Any 1 of 4 Ch Any 1 of 4 Ch Any 1 of 4 Ch

1-Ch CIF n/a 03h 27 Any 1 of 4 Ch Any 1 of 4 Ch Any 1 of 4 Ch Any 1 of 4 Ch

Port A Port B Port C Port D

3.8.2 Pixel-Interleaved Mode

Each video decoder supports multiplexing two or four channels ITU-R BT.656 format data together on a

pixel basis. The output from each video decoder channel is still ITU-R BT.656 format. After the processing

in output formatter, two or four channels video data has been interleaved together by strictly one pixel

from each channel.

The pixel-interleaved mode is dedicated for the backend chip which has limited video input ports.

Table 3-6 gives the output port configuration for pixel-interleaved mode.

Copyright © 2009–2010, Texas Instruments Incorporated Functional Description 23

Submit Documentation Feedback

Product Folder Link(s): TVP5158 TVP5157 TVP5156

FF 00 Y0 Y1 Y2 Y3

CLK_P

(27MHz)

CH1_D

00 XY

CH2_D

DVO_A_

[7:0]

Cb0 C r0 Cb2 Cr2

Cb20 Y20 Cr 20 Y21 Cb22 Y22 C r22 Y23 Cb 24 Y24 Cr24 Y25

FF 00 Y0 Y1 Y2 Y300 XY Cb0 C r0 Cb2 Cr2Cb20 Y20 Cr 20 Y21 Cb22 Y22 C r22 Y23 Cb 24 Y24 Cr24 Y25

CLK_N

(27MHz)

FF 00 Y0

CLK (108MHz)

CH1_D

00 XY

CH2_D

Cb0

Cr50 Cb52 Cr52

Cb20 Y20 Cr20 Y21

Cb22 Y22

Cr92 Y93 Cb94 Y94

Cr 94

Y95

Y51 Y52 Y53

FF 00 Y000 XY Cb0Cb20 Y 20 Cr20 Y21 C b22 Y22Cr50 Cb52 Cr52Y51 Y52 Y53Cr92 Y93 Cb94 Y94

Cr 94

Y95

CH3_D

CH4_D

DVO_A_

[7:0]

TVP5158, TVP5157, TVP5156

SLES243D–JULY 2009–REVISED OCTOBER 2010

Table 3-6. Output Ports Configuration for Pixel-Interleaved Mode

Video Output Cascade I2C Address: OCLK

Format Stage B0h (MHz)

2-Ch D1 n/a 50h 54 Any 2 of 4 Ch Any 2 of 4 Ch Hi-Z Hi-Z

4-Ch D1 n/a 60h 108 All 4 Ch Hi-Z Hi-Z Hi-Z

4-Ch Half-D1 n/a 62h 54 All 4 Ch Hi-Z Hi-Z Hi-Z

4-Ch CIF n/a 63h 54 All 4 Ch Hi-Z Hi-Z Hi-Z

Port A Port B Port C Port D

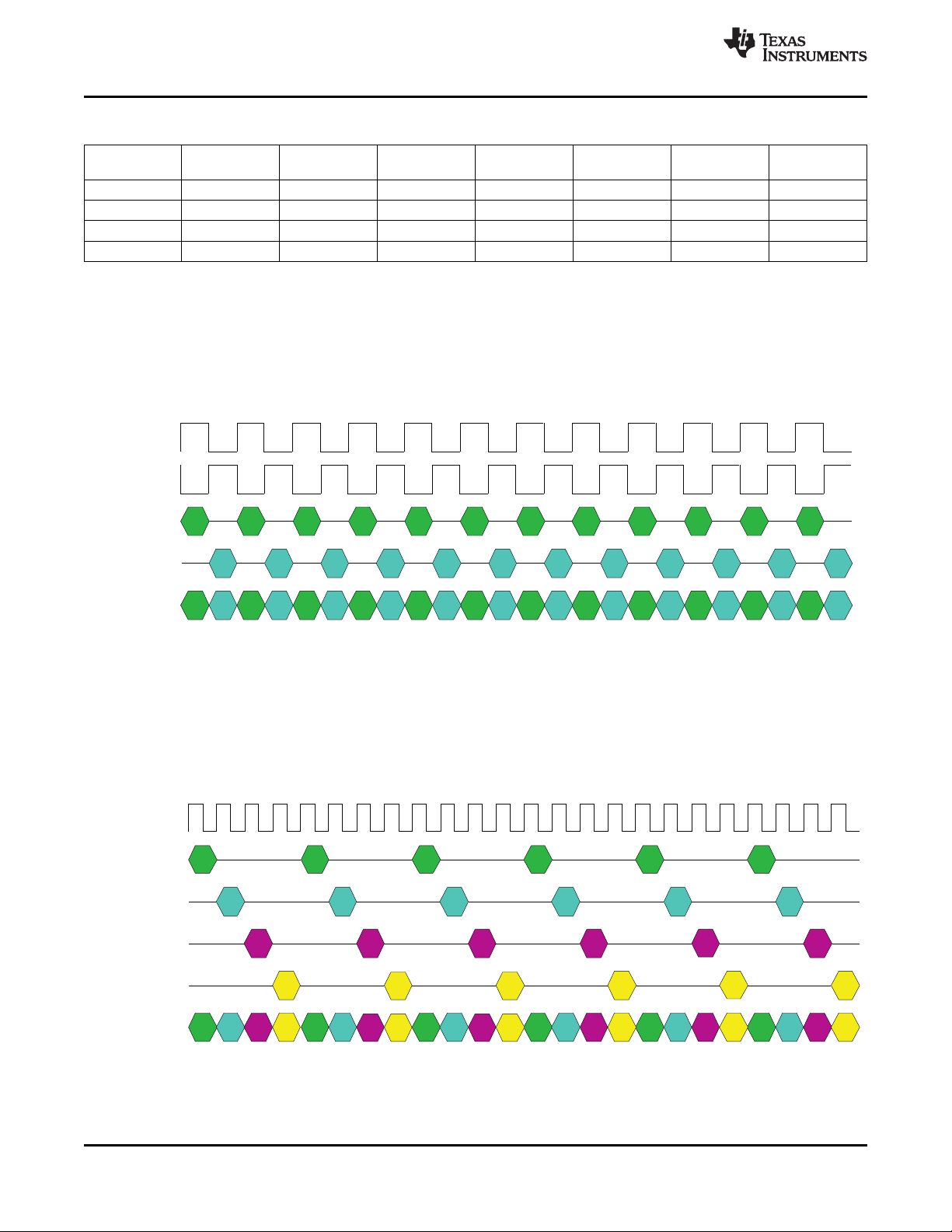

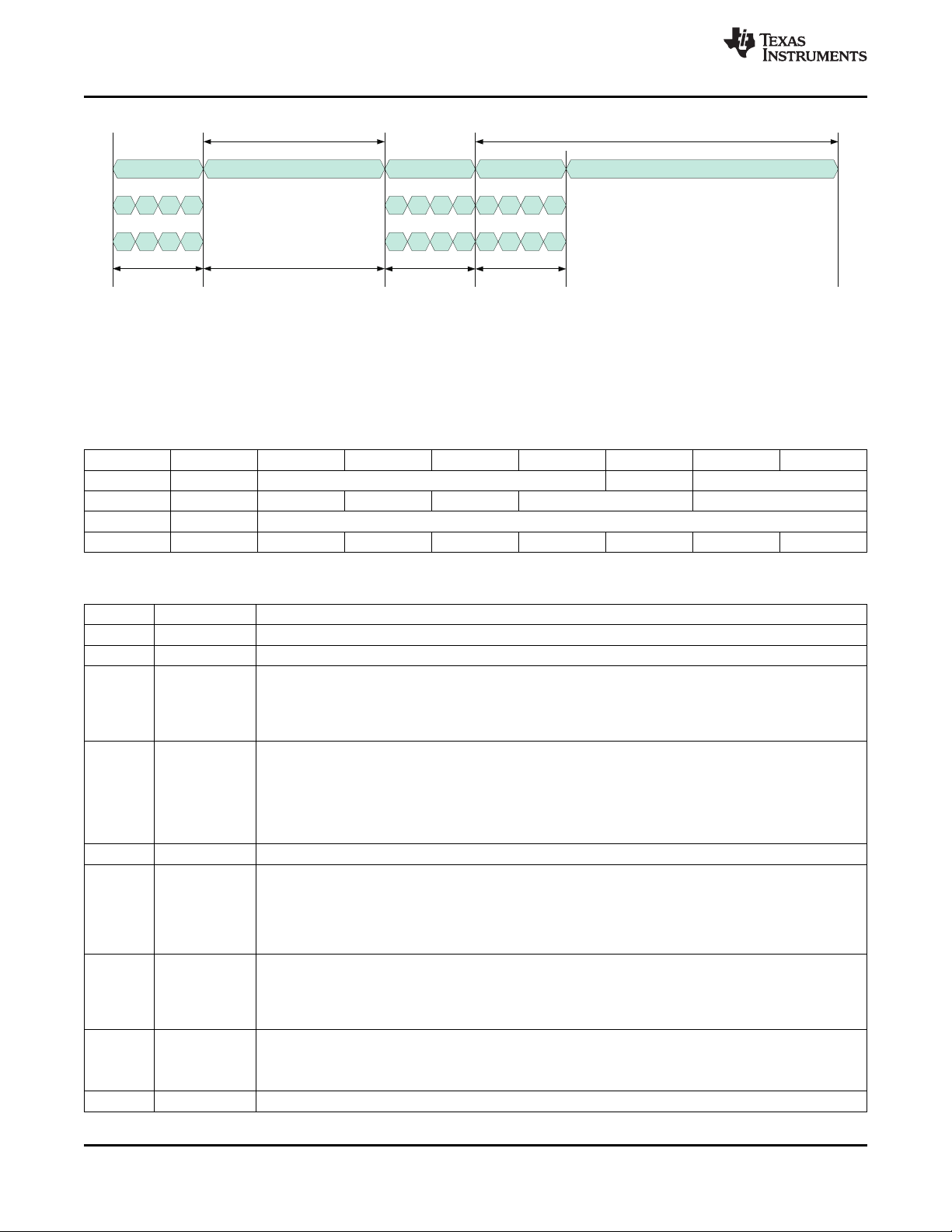

3.8.2.1 2-Ch Pixel-Interleaved Mode

In 2-Ch pixel-interleaved mode, the video output data with D1 resolution from two video channels is

multiplexed pixel by pixel at 54 MHz. The output ports DVO_A and DVO_B are used in this mode. The

output clocks OCLK_P and OCLK_N are synchronized with each channel so that the backend chip can

de-multiplexed each video channel data easily. The video output from each channel is compatible with

ITU-R BT.656 format. Figure 3-10 shows the timing diagram for 2-Ch pixel-interleaved mode.

www.ti.com

Figure 3-10. 2-Ch Pixel-Interleaved Mode Timing Diagram

3.8.2.2 4-Ch Pixel-Interleaved Mode

In 4-Ch pixel-interleaved mode, the video output data with D1 resolution from four video channels is

multiplexed pixel by pixel at 108 MHz. The output DVO_A is used in this mode. The output clock OCLK_P

is synchronized with all four channels data. Each channel video data is compatible with ITU-R BT.656

format. Figure 3-11 shows the timing diagram for 4-Ch pixel-interleaved mode.

Figure 3-11. 4-Ch Pixel-Interleaved Mode Timing Diagram

24 Functional Description Copyright © 2009–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TVP5158 TVP5157 TVP5156

TVP5158, TVP5157, TVP5156

www.ti.com

SLES243D–JULY 2009–REVISED OCTOBER 2010

In 4-Ch pixel-interleaved mode, TVP5158 also supports Half-D1 and CIF format data multiplexed at 54

MHz. The output DVO_A is used in this mode. The output clock OCLK_P is synchronized with all four

channels data.

3.8.2.3 Metadata Insertion for Non-Interleave Mode and Pixel-Interleaved Mode

In non-interleaved mode and pixel-interleaved mode, the video detection status (VDET) has also been

inserted in MSB of SAV/EAV control byte. Table 3-7 shows VDET status insertion in SAV/EAV codes.

Table 3-7. VDET Statues Insertion in SAV/EAV Codes

CONDITION FVH VALUE SAV/EAV CODE SEQUENCE

FIELD V TIME H TIME F V H 1st 2nd 3rd

1 Active SAV 0 0 0 FFh 00h 00h 80h 00h

1 Active EAV 0 0 1 FFh 00h 00h 9Dh 1Dh

1 Blank SAV 0 1 0 FFh 00h 00h ABh 2Bh

1 Blank EAV 0 1 1 FFh 00h 00h B6h 36h

2 Active SAV 1 0 0 FFh 00h 00h C7h 47h

2 Active EAV 1 0 1 FFh 00h 00h DAh 5Ah

2 Blank SAV 1 1 0 FFh 00h 00h ECh 6Ch

2 Blank EAV 1 1 1 FFh 00h 00h F1h 71h

VDET = 1 VDET = 0

4th

In the pixel-interleaved mode, Channel ID is inserted in the horizontal blanking code as Table 3-8. The

backend chip can easily identify the video data from which video decoder channel by inserted Channel ID.

Table 3-8. Channel ID Insertion in Horizontal Blanking Code

CHANNEL

Ch1 10h 80h 80h

Ch2 11h 81h 81h

Ch3 12h 82h 82h

Ch4 13h 83h 83h

H BLANKING CODE WITH CHANNEL ID

Y Cb Cr

In the pixel-interleaved mode, Channel ID can also be inserted in 4 LSBs of SAV/EAV control byte

replacing protection bits as Table 3-9.

Table 3-9. Channel ID Insertion in SAV/EAV Code Sequence

CONDITION FVH VALUE SAV/EAV CODE SEQUENCE

FIELD V TIME H TIME F V H 1st 2nd 3rd

1 Active SAV 0 0 0 FFh 00h 00h 80h 81h 82h 83h

1 Active EAV 0 0 1 FFh 00h 00h 90h 91h 92h 93h

1 Blank SAV 0 1 0 FFh 00h 00h A0h A1h A2h A3h

1 Blank EAV 0 1 1 FFh 00h 00h B0h B1h B2h B3h

2 Active SAV 1 0 0 FFh 00h 00h C0h C1h C2h C3h

2 Active EAV 1 0 1 FFh 00h 00h D0h D1h D2h D3h

2 Blank SAV 1 1 0 FFh 00h 00h E0h E1h E2h E3h

2 Blank EAV 1 1 1 FFh 00h 00h F0h F1h F2h F3h

Ch1 Ch2 Ch3 Ch4

4th

Copyright © 2009–2010, Texas Instruments Incorporated Functional Description 25

Submit Documentation Feedback

Product Folder Link(s): TVP5158 TVP5157 TVP5156

TVP5158, TVP5157, TVP5156

SLES243D–JULY 2009–REVISED OCTOBER 2010

3.8.3 Line-Interleaved Mode Support (TVP5158 only)

The TVP5158 supports 2-Ch, 4-Ch, and 8-Ch line-interleaved modes. In the line-interleaved mode, the

video channels are multiplexed together on a line-by-line basis. Compared to the pixel-interleaved mode,

the line-interleaved mode significantly reduces the code complexity and MIPS consumption of the backend

processor. The 8-Ch modes require connecting two TVP5158 devices together using a video cascade

interface (see Section 3.8.3.3). The TVP5158 also supports different image resolutions (for example, D1,

Half-D1, and CIF) in the line-interleaved mode. All supported line-interleaved modes are shown in

Table 3-10.

Table 3-10. Output Ports Configuration for Line-Interleaved Mode

Video Output Cascade I2C Address: OCLK

Format Stage B0h (MHz)

2-Ch D1 n/a 90h 54 Any 2 of 4 Ch Any 2 of 4 Ch Hi-Z Hi-Z

4-Ch D1 n/a A0h 108 All 4 Ch Hi-Z Hi-Z Hi-Z

4-Ch Half-D1 n/a A2h 54 All 4 Ch Hi-Z Hi-Z Hi-Z

4-Ch CIF n/a A3h 27 All 4 Ch Hi-Z Hi-Z Hi-Z

4-Ch D1 All 4 Ch All 4 Ch

(16-bit) (Y data) (C data)

4-Ch Half-D1 All 4 Ch All 4 Ch

(16-bit) (Y data) (C data)

8-Ch Half-D1

8-Ch CIF

4-Ch Half-D1 + 4 Ch Half-D1 +

1-Ch D1 Any 1 of 4 D1

4-Ch CIF + 4-Ch CIF + Any

1-Ch D1 1 of 4 D1

8-Ch CIF +

1-Ch D1

n/a A8h 54 Hi-Z Hi-Z

n/a AAh 27 Hi-Z Hi-Z

1st B2h 108 Hi-Z Hi-Z

2nd B6h 54 Hi-Z Hi-Z Hi-Z

1st B3h 54 Hi-Z Hi-Z 4-Ch CIF Input

2nd B7h 27 Hi-Z Hi-Z Hi-Z

n/a E2h 108 Hi-Z Hi-Z Hi-Z

n/a E3h 54 Hi-Z Hi-Z Hi-Z

1st F3h 108 Hi-Z 1-Ch D1 Input 4-Ch CIF Input

2nd F7h 27 1-Ch D1 Output Hi-Z Hi-Z

Port A Port B Port C Port D

8-Ch Half-D1 4-Ch Half-D1

Output Input

4-Ch Half-D1

Output

8-Ch CIF

Output

4-Ch CIF

Output

8-Ch CIF + Any

1 of 8 D1

4-Ch CIF

Output

www.ti.com

3.8.3.1 2-Ch Line-Interleaved Mode

TVP5158 supports 2-Ch line-interleaved mode at 54 MHz. The video output data with D1 resolution from

any two video channels is multiplexed together on a line basis. The output ports DVO_A and DVO_B are

used in this mode. The output clock OCLK_P is synchronized with both output ports.

3.8.3.2 4-Ch Line-Interleaved Mode

In 4-Ch line-interleaved mode, the video output data from all 4 channels is multiplexed together on a line

basis. The output resolution of video data can be D1, Half-D1 or CIF. For D1 and Half-D1 output

resolutions, the video output port can be configured to support 8-bit BT.656 or 16-Bit YCbCr 4:2:2 data

with embedded sync. Port DVO_A is used for 8-bit output. Ports DVO_A and DVO_B are used for 16-Bit

output. The output clock OCLK_P is synchronized with all four output ports.

TVP5158 supports multiplexing 4-Ch CIF and 1-Ch D1 data together and then output through DVO_A at

54 MHz. 1-Ch D1 can be from any one of 4 video channels. In typical surveillance applications, CIF

resolution is used for recording and D1 resolution is used for video preview.

26 Functional Description Copyright © 2009–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TVP5158 TVP5157 TVP5156

DM6467

DaVinci HD

DVO_A_[7:0]

VPIF_A

I2C

H.264

DVO_D_[7:0]

4-C h CIF

8Bit@27MHz

8Bit@54MH z

DVO_A_[7:0]

VPIF_B

8-C h CIF

Multi-C h CIF

Preview

16-Ch CIF Recording

TVP5158

TVP5158

OCLK_P

OCLKN/CLKIN

OCLK_P

DVO_A_[7:0]

DVO_D_[7:0]

4-C h CIF

8Bit@ 27MHz

8Bit @54MH z

DVO_A_[7:0]

8-C h CIF

OCLK_P

OCLKN/CLKIN

OCLK_P

I2C

TVP5158

TVP5158

VIN_1

VIN_2

VIN_3

VIN_4

VIN_1

VIN_2

VIN_3

VIN_4

VIN_1

VIN_2

VIN_3

VIN_4

VIN_1

VIN_2

VIN_3

VIN_4

TVP5158, TVP5157, TVP5156

www.ti.com

TVP5158 also supports multiplexing 4-Ch Half-D1 and 1-Ch D1 data together and then output through

DVO_A at 108 MHz. The backend chip can use Half-D1 to generate CIF format by dropped one field.

Pleas note that the line-interleaved mode does NOT strictly output one line from each decoder channel

sequentially. The order of multiplexed the video line data is based on the availability of video output data

from each decoder channel. Therefore, it is possible to output two consecutive lines from the same

decoder channel or to skip one decoder channel output.

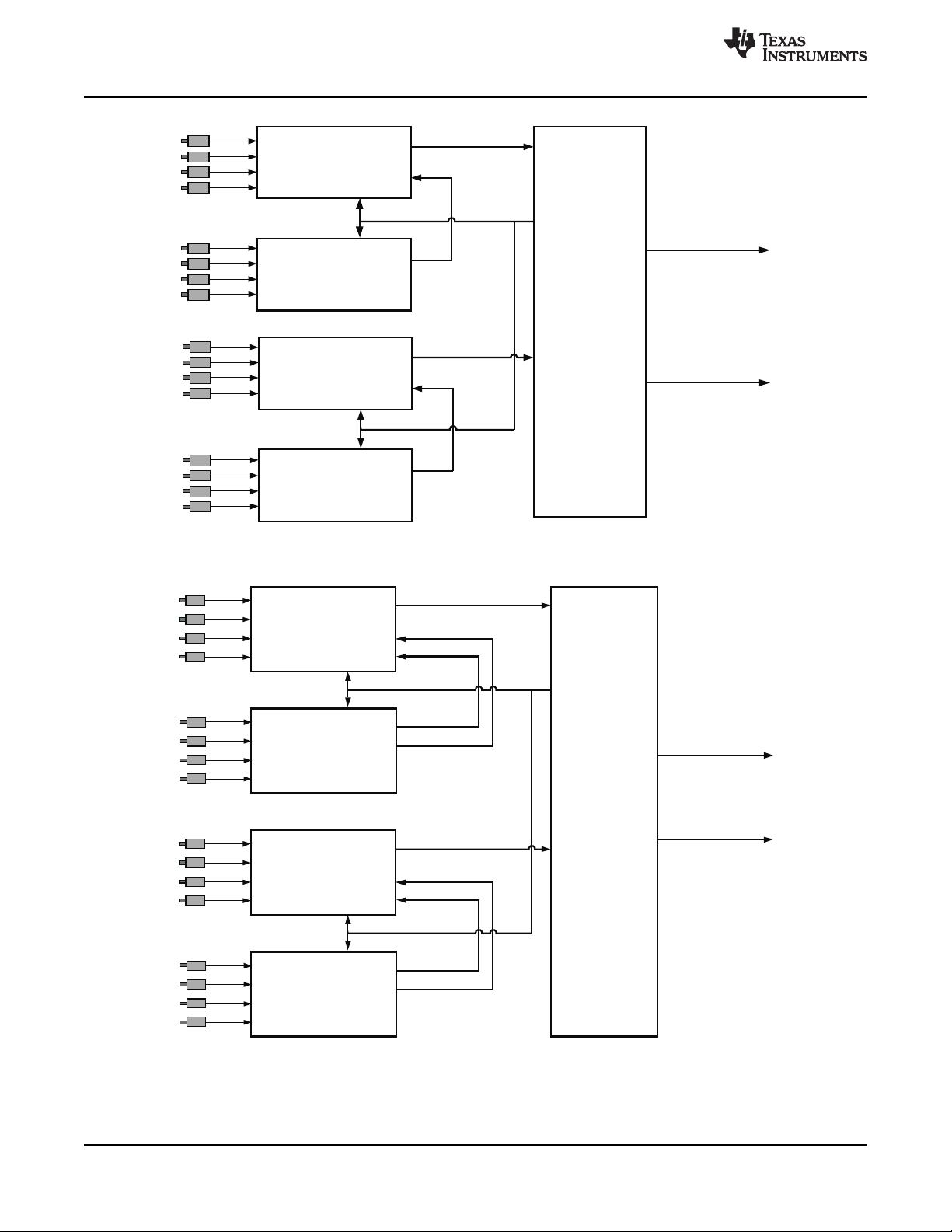

3.8.3.3 8-Ch Line-Interleaved Mode

Two TVP5158 devices can be cascade connected and work as single 8-Ch video decoder. In cascade

mode, the port DVO_C and DVO_D of master TVP5158 (first stage) can be configured as the video input

interface. The DVO_A and DVO_B of master TVP5158 are configured as the output interface for two

devices. This mode is dedicated for the backend chip with extremely limited input ports.

In the video cascade mode, the open-drain interrupt request (INTREQ) outputs from the first and second

stages can be combined using a wired-OR connection.

Typical applications with cascade mode show in the following diagrams.

Figure 3-12 shows the Cascade Connection for 16-Ch CIF Recoding and Multi-Ch CIF Preview.

Figure 3-13 shows the Cascade Connection for 16-Ch CIF Recoding and Multi-Ch Half-D1 Preview.

Figure 3-14 shows the Cascade Connection for 16-Ch CIF Recoding and 2-Ch D1/Multi-Ch CIF

Preview.

SLES243D–JULY 2009–REVISED OCTOBER 2010

Figure 3-12. Cascade Connection for 16-Ch CIF Recoding and Multi-Ch CIF Preview

Copyright © 2009–2010, Texas Instruments Incorporated Functional Description 27

Submit Documentation Feedback

Product Folder Link(s): TVP5158 TVP5157 TVP5156

DM6467

DaVinci HD

DVO_A_[7:0]

VPIF_A

I2C

H.264

DVO_D_[7:0]

4-Ch H alf-D1

8Bit@54MHz

8Bit@108MHz

DVO_A_[7:0]

VPIF_B

8-Ch Half-D1

Multi-Ch H alf-D1

Preview

16 -Ch CIF R ecording

TVP5158

TVP5158

OCLK_P

OCLKN/CLKIN

OCLK_P

DVO_A_[7:0]

DVO_D_[7:0]

4-Ch H alf- D1

8Bit@ 54MHz

8Bit@ 108MHz

DVO_A_[7:0]

8-Ch Half-D1

OCLK_P

OCLKN/CLKIN

OCLK_P

I2C

TVP5158

TVP5158

VIN_1

VIN_2

VIN_3