TSB12LV42 (DVLynx)

IEEE 1394-1995 Link-Layer Controller

for Digital Video

SLLS293

December 1998

Printed on Recycled Paper

IMPORTANT NOTICE

T exas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue

any product or service without notice, and advise customers to obtain the latest version of relevant information

to verify, before placing orders, that information being relied on is current and complete. All products are sold

subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those

pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent

TI deems necessary to support this warranty . Specific testing of all parameters of each device is not necessarily

performed, except those mandated by government requirements.

CERT AIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MA Y INVOLVE POTENTIAL RISKS OF

DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL

APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR

WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER

CRITICAL APPLICA TIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERST OOD TO

BE FULLY AT THE CUSTOMER’S RISK.

In order to minimize risks associated with the customer’s applications, adequate design and operating

safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent

that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other

intellectual property right of TI covering or relating to any combination, machine, or process in which such

semiconductor products or services might be or are used. TI’s publication of information regarding any third

party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.

Copyright 1998, Texas Instruments Incorporated

Contents

Section Title Page

1 Introduction 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1 TSB12L V42 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2 TSB12LV42 Features 1–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3 DVLynx Pinout 1–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4 Ordering Information 1–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

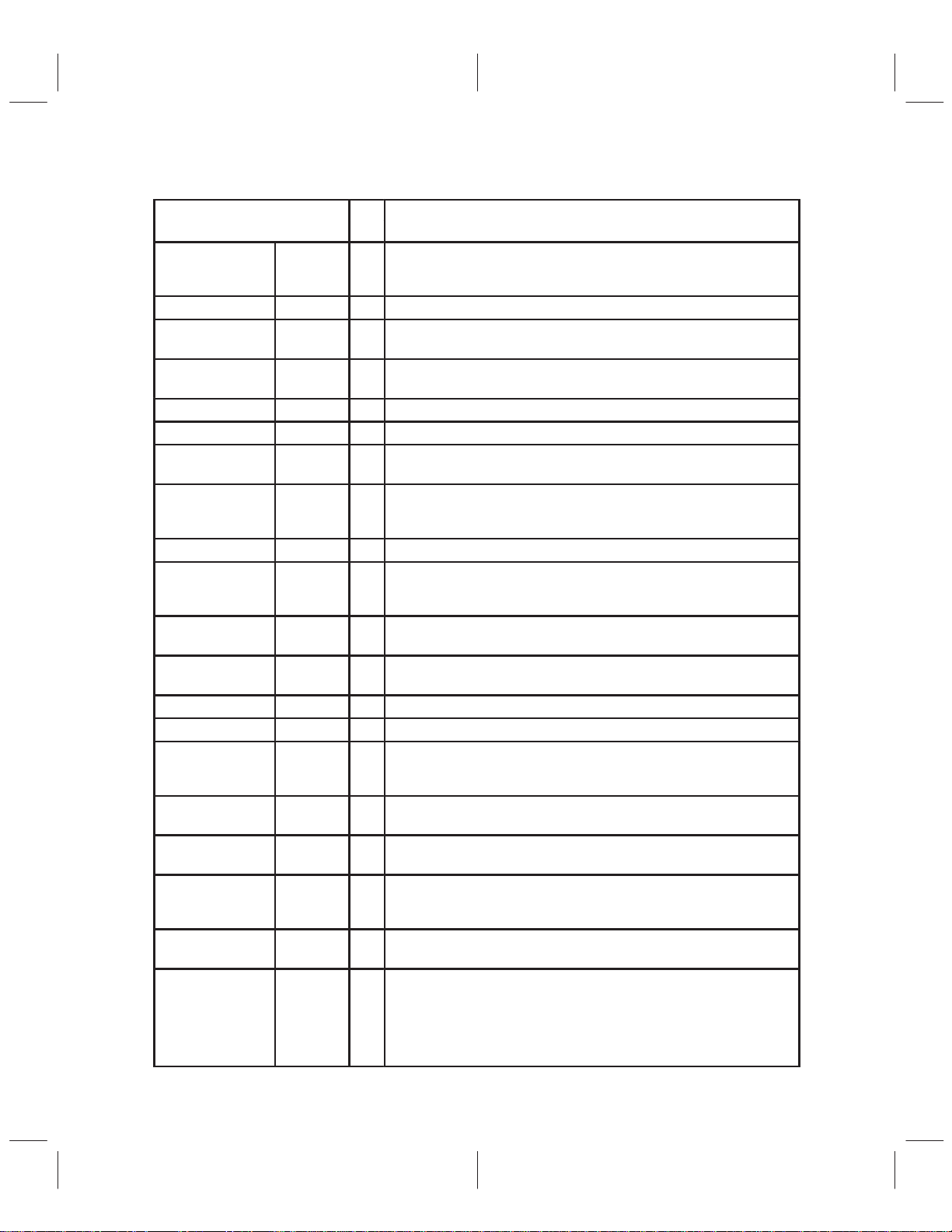

1.5 TSB12LV42 Terminal Functions 1–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.5 TSB12LV42 Terminal Functions (Continued) 1–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2 Architecture 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1 Bulky Data Interface 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2 Bulky Data FIFO 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.1 Bulky DV Transmit FIFO (BDTX) 2–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.2 Bulky DV Receive FIFO (BDRX) 2–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.3 Bulky Asynchronous Transmit FIFO (BATX) 2–2. . . . . . . . . . . . . . . . . . . . . . . . .

2.2.4 Bulky Asynchronous Receive FIFO (BARX) 2–2. . . . . . . . . . . . . . . . . . . . . . . . .

2.2.5 Bulky Isochronous Transmit FIFO (BITX) 2–2. . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.6 Bulky Isochronous Receive FIFO (BIRX) 2–2. . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3 DV Transmit and Receive Control 2–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4 Microprocessor/Microcontroller Interface 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5 Control FIFO 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5.1 Asynchronous Control Transmit FIFO (ACTX) 2–3. . . . . . . . . . . . . . . . . . . . . . .

2.5.2 Asynchronous Control Receive FIFO (ACRX) 2–3. . . . . . . . . . . . . . . . . . . . . . . .

2.5.3 Broadcast Write Receive FIFO (BWRX) 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6 Physical Layer 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.7 Configuration Register (CFR) 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3 Functional Description and Data Formats 3–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1 Overview 3–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2 DV on 1394 Overview 3–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.1 DV interface 3–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.2 DV Bandwidth on IEEE1394 3–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.3 DV Transmission over IEEE1394 3–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.4 Source Packet/DIF Block Format 3–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.5 DV Packets CIP Header Calculations 3–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3 Transmit Operation 3–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.1 Transmitting Asynchronous Control Packets 3–6. . . . . . . . . . . . . . . . . . . . . . . . .

3.3.2 Transmitting Asynchronous Data Packets 3–7. . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.4 Byte Padding 3–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.5 Transmitting DV Formatted Isochronous Packets 3–12. . . . . . . . . . . . . . . . . . .

3.4 Receive Operation 3–17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4.1 Receiving Asynchronous Packets 3–17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

iii

3.5 Time Stamps 3–27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.1 Time Stamp Encoding/Decoding for DV Transmit and Receive 3–27. . . . . . . .

3.5.2 Time Stamp Calculation on Transmit 3–28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.3 Time Stamp Determination on Receive 3–29. . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6 Asynchronous Transmit Data Formats (Host Bus to TSB12LV42) 3–29. . . . . . . . . . . .

3.6.1 Quadlet Transmit 3–29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.2 Block Transmit 3–30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.3 Quadlet Receive 3–31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.4 Block Receive 3–33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.7 Isochronous Transmit and Receive (Host Bus to TSB12LV42) Data Formats 3–35. .

3.7.1 Isochronous Transmit 3–35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.7.2 Isochronous Receive Data Formats 3–35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8 Snoop 3–36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.9 CycleMark 3–37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.10 Phy Configuration 3–37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.11 Receive Self-ID Packet 3–38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4 External Interfaces 4–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1 Bulky Data Interface 4–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1.1 BDIF Control Register (D8h) Configuration 4–4. . . . . . . . . . . . . . . . . . . . . . . . . .

4.1.2 Modes of the Bulky Data Interface (BDIF) 4–6. . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1.3 Mode A – 8 Bit Parallel I/O 4–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1.4 Mode B – 8-Bit Parallel I/O with No Read Control 4–8. . . . . . . . . . . . . . . . . . . .

4.1.5 Mode C – 8 Bit Parallel Asynchronous Input/8 Bit Parallel Asynchronous

Output 4–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1.6 Mode D– 8 Bit Parallel Bidirectional Mode 4–10. . . . . . . . . . . . . . . . . . . . . . . . . .

4.1.7 Bulky Data Interface Timing 4–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1.8 Bidirectional Modes 4–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2 Microprocessor Interface 4–16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.1 Microprocessors Supported 4–16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.2 Microprocessor Interface Control 4–19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.3 Handshake and Blind Access modes 4–20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.4 General Read Instructions 4–20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.5 General Write Instructions 4–21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.6 TMS320AV7100 Mode Timing Diagrams 4–22. . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.7 68000 Mode Timing Diagrams 4–27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.8 8051 Mode Timing Diagrams 4–31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.9 Blind Access Mode Specific Issues 4–35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.10 Endianness 4–36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.11 Use of Interrupts with DVLynx 4–38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3 TSB12LV42 to 1394 Phy Interface Specification 4–39. . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.1 Introduction 4–39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.2 Assumptions 4–40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.3 Block Diagram 4–40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.4 Operational Overview 4–40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.5 Request 4–41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.6 Status 4–43. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.7 TSB12LV42 to Phy Bus Timing 4–45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

iv

5 Detailed Operation and Programmers Reference 5–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1 TSB12LV42 Configuration Register 5–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2 Version Register (VERS at Addr 000h) 5–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3 C Acknowledge Register (CACK at Addr 004h) 5–6. . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.4 B Acknowledge Register (BACK at Addr 008h) 5–6. . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.5 Link Control Register (LCTRL at Addr 00Ch) 5–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6 Interrupt Register (IR at Addr 010h) 5–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.7 Interrupt Register Enable Register (IMR at Addr 014h) 5–11. . . . . . . . . . . . . . . . . . . . .

5.8 Extended Interrupt Register (EIR at Addr 018h) 5–13. . . . . . . . . . . . . . . . . . . . . . . . . . .

5.9 Extended Interrupt Mask Register (EIMR at Addr 01Ch) 5–15. . . . . . . . . . . . . . . . . . . .

5.10 Isochronous Receive Comparators Register 0 (IRPR0 at Addr 020h) 5–16. . . . . . . .

5.11 Isochronous Receive Comparators Register 1 (IRPR1 at Addr 024h) 5–17. . . . . . . .

5.12 Cycle Timer Register (CLKTIM at Addr 028h) 5–18. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.13 Extended Cycle Time Register (EXTTIM at Addr 02Ch) 5–18. . . . . . . . . . . . . . . . . . . .

5.14 Link Diagnostics Register (DIAG at Addr 030h) 5–19. . . . . . . . . . . . . . . . . . . . . . . . . . .

5.15 Phy Access Register (PHYAR at Addr 034h) 5–19. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.16 Expected Response (PHYSR at Addr 038h) 5–20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.17 Reserved Register (at Addr 03Ch – 040h) 5–20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.18 Asynchronous Control Data Transmit FIFO Status (ACTFS at Addr 044h) 5–20. . . .

5.19 Bus Reset Data Register (BRD at Addr 048h) 5–21. . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.20 Bus Reset Error Register (BRERR at Addr 04Ch) 5–22. . . . . . . . . . . . . . . . . . . . . . . . .

5.21 Asynchronous Control Data Receive FIFO Status (ACRXS at Addr 050h) 5–22. . . .

5.22 Read Write Test Register (UCRWTEST at Addr 054h) 5–23. . . . . . . . . . . . . . . . . . . . .

5.23 Reserved Register (at Addr 058h – 07Ch) 5–23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.24 Asynchronous Control Data Transmit FIFO First (ACTXF at Addr 080h) 5–23. . . . . .

5.25 Asynchronous Control Data Transmit FIFO Continue (ACTXC at Addr084h) 5–23. .

5.26 Asynchronous Control Data Transmit FIFO First and Update

(ACTXFU at Addr 088h) 5–23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.27 Asynchronous Control Data Transmit FIFO Continue and Update

(ACTXCU at Addr 08Ch) 5–24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.28 Reserved Register (at Addr 090h – 0BCh) 5–24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.29 Asynchronous Control Data Receive FIFO (ACRX at Addr 0C0h) 5–24. . . . . . . . . . .

5.30 Broadcast Write Receive FIFO (BWRX at Addr 0C4h) 5–24. . . . . . . . . . . . . . . . . . . . .

5.31 Reserved Register (at 0C8 – 0D4) 5–24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.32 Bulky Data Interface Control (BIF at Addr 0D8h) 5–24. . . . . . . . . . . . . . . . . . . . . . . . . .

5.33 Transmit Timestamp Offset Register (XTO at Addr 0DCh) 5–25. . . . . . . . . . . . . . . . . .

5.34 Reserved Register (at Addr 0E0h) 5–25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.35 Receive Timestamp Offset (RTO at Addr 0E4h) 5–25. . . . . . . . . . . . . . . . . . . . . . . . . . .

5.36 Reserved Register (at Addr 0E8h) 5–25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.37 Asynchronous/Isochronous Application Data Control Register

(AICR at Addr 0ECh) 5–25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.38 DV Formatter Control Register (DCR at Addr 0F0h) 5–27. . . . . . . . . . . . . . . . . . . . . . .

5.39 Reserved Register (at Addr 0F4h) 5–29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.40 FIFO Misc (FMISC at Addr 0F8h) 5–29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.41 Reserved Register (at Addr 0FCh – 100h) 5–29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.42 Bulky A Size Register (BASZ at Addr 104h) 5–30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.43 Bulky A Avail Register (BAAVAL at Addr 108h) 5–30. . . . . . . . . . . . . . . . . . . . . . . . . . . .

v

5.44 Asynchronous Application Data Transmit FIFO First and Continue

(BATXFC at Addr 10Ch) 5–30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.45 Asynchronous Application Data Transmit FIFO Last and Send

(BATXLS at Addr 110h) 5–30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.46 Asynchronous Application Data Receive FIFO (BARX at Addr 114h) 5–30. . . . . . . . .

5.47 Asynchronous Application Data Receive Header Register 0

(ARH0 at Addr 118h) 5–31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.48 Asynchronous Application Data Receive Header Register 1

(ARH1 at Addr 11Ch) 5–31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.49 Asynchronous Application Data Receive Header Register 2

(ARH2 at Addr 120h) 5–31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.50 Asynchronous Application Data Receive Header Register 3

(ARH3 at Addr 124h) 5–31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.51 Asynchronous Application Data Receive Trailer (ART at Addr 128h) 5–31. . . . . . . . .

5.52 Bulky Isochronous Size Register (BISZ at Addr 12Ch) 5–32. . . . . . . . . . . . . . . . . . . . .

5.53 Bulky Isochronous Avail Register (BIAVAL at Addr 130h) 5–32. . . . . . . . . . . . . . . . . . .

5.54 Isochronous Transmit First and Continue (BITXFC at Addr 134h) 5–32. . . . . . . . . . .

5.55 Isochronous Transmit Last and Send (BITXLS at Addr 138h) 5–32. . . . . . . . . . . . . . .

5.56 Isochronous Receive FIFO (BIRX at Addr 13Ch) 5–33. . . . . . . . . . . . . . . . . . . . . . . . . .

5.57 Isochronous Packed Received Header (IRH at Addr 140h) 5–33. . . . . . . . . . . . . . . . .

5.58 Isochronous Packet Received Trailer (IRT at Addr 144h) 5–33. . . . . . . . . . . . . . . . . . .

5.59 Receive Packet Router (RMISC at Addr 148h) 5–34. . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.60 Bulky Asynchronous Retry (BARTRY at Addr 14Ch) 5–35. . . . . . . . . . . . . . . . . . . . . . .

5.61 Bulky DV Size Register (BDSZ at Addr 150h) 5–35. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.62 Bulky DV Avail Register (BDAVAL at Addr 154h) 5–36. . . . . . . . . . . . . . . . . . . . . . . . . .

5.63 Reserved Register (at Addr 158h) 5–36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.64 Reserved Register (at Addr 15Ch) 5–36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.65 DV Transmit FIFO First and Continue (BDTXFC at Addr 160h) 5–36. . . . . . . . . . . . . .

5.66 DV Transmit FIFO Last & Send (BDTXLS at Addr 164h) 5–36. . . . . . . . . . . . . . . . . . .

5.67 DV Formatted Packet Receive FIFO (BDRX at Addr 168h) 5–36. . . . . . . . . . . . . . . . .

5.68 Reserved Register (at Addr 16Ch) 5–36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.69 Reserved Register (at Addr 170h) 5–36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.70 Reserved Register (at Addr 174h) 5–36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.71 DV Receive Header (DRH at Addr 178h) 5–36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.72 DV CIP Receive Header 0 (DCIPR0 at Addr 17Ch) 5–37. . . . . . . . . . . . . . . . . . . . . . . .

5.73 DV CIP Receive Header 1 (DCIPR1 at Addr 180h) 5–37. . . . . . . . . . . . . . . . . . . . . . . .

5.74 DV Receive Trailer Register (DRT at Addr 184h) 5–37. . . . . . . . . . . . . . . . . . . . . . . . . .

5.75 Reserved Register (at Addr 188h – 194h) 5–38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.76 DV Receive Cell Header Register 0 (DRX0 at Addr 198h) 5–38. . . . . . . . . . . . . . . . . .

5.77 DV Receive Cell Header Register 1 (DRX1 at Addr 19Ch) 5–38. . . . . . . . . . . . . . . . . .

5.78 Reserved Register (at Addr 1A0h) 5–38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.79 DV Transmit Cell Header Register 0 (DTX0 at Addr 1A4h) 5–38. . . . . . . . . . . . . . . . .

5.80 DV Transmit Cell Header Register 1 (DTX1 at Addr 1A8h) 5–38. . . . . . . . . . . . . . . . .

5.81 Reserved Register (at Addr 1ACh) 5–39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.82 Asynchronous Header 0 for Auto Transmit (AHEAD 0) at Addr 1B0h) 5–39. . . . . . . .

5.83 Asynchronous Header 1 for Auto Transmit (AHEAD1) at Addr 1B4h) 5–39. . . . . . . .

5.84 Asynchronous Header 2 for Auto Transmit (AHEAD2) at Addr 1B8h) 5–39. . . . . . . .

vi

5.85 Asynchronous Header 3 for Auto Transmit (AHEAD3) at Addr 1BCh) 5–39. . . . . . . .

5.86 Isochronous Header for Auto Transmit (IHEAD0 at Addr 1C0h) 5–39. . . . . . . . . . . . .

5.87 Packetizer Control (PKTCTL at Addr 1C4h) 5–40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.88 DV Transmit Header Register (DXH at Addr 1C8h) 5–41. . . . . . . . . . . . . . . . . . . . . . . .

5.89 DV CIP Transmit Header 0 (DCIPX0 at Addr 1CCh) 5–41. . . . . . . . . . . . . . . . . . . . . . .

5.90 DV CIP Transmit Header 1 (DCIPX1 at Addr 1D0h) 5–42. . . . . . . . . . . . . . . . . . . . . . .

5.91 Reserved Register (at Addr 1D4h) 5–42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.92 Reserved Register(at Addr 1D8h) 5–42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.93 Reserved Register (at Addr 1DCh) 5–42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.94 MDAltCont (MDALT at Addr 1E0h) 5–42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.95 Reserved Register (at Addr 1E4h) 5–42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.96 Reserved Register (at Addr 1E8h) 5–42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.97 Microinterface Input/Output Control Register (IOCR at Addr 1ECh) 5–42. . . . . . . . . .

5.98 Blind Access Status Register (BASTAT at Addr 1F0h) 5–43. . . . . . . . . . . . . . . . . . . . .

5.99 Blind Access Holding Register (BAHR at Addr 1F4h) 5–44. . . . . . . . . . . . . . . . . . . . . .

5.100 Reserved Register (at Addr 1F8h) 5–44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.101 Software Reset Register (SRES at Addr 1FCh) 5–44. . . . . . . . . . . . . . . . . . . . . . . . . .

6 Electrical Characteristics 6–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.1 Absolute Maximum Ratings Over Free-Air Temperature Range 6–1. . . . . . . . . . . . . .

6.2 Recommended Operating Conditions 6–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3 Electrical Characteristics Over Recommended Ranges of Supply Voltage

and Operating Free-Air Temperature 6–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.4 DVLynx Power 6–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7 Mechanical Information 7–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A Receive Operation Examples A–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.1 Asynchronous Receive A–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.1.1 Receiving Asynchronous Data to the Bulky Asynchronous FIFO

(Bulky Data Interface) A–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.1.2 Receiving Asynchronous Data to the Asynchronous Control FIFO

(Microprocessor Port) A–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.2 Unformatted Isochronous Receive A–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.2.1 Receiving Isochronous Data to the Bulky Isochronous FIFO

(Bulky Data Interface) A–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.2.2 Receiving Isochronous Data to the Bulky Isochronous FIFO

(Microprocessor Interface) A–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.3 DV Receive A–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.3.1 Receiving DV Data to the Bulky DV FIFO (Bulky Data Interface) A–4. . . . . . . .

A.3.2 Receiving DV Data to the Bulky DV FIFO (Microprocessor Interface) A–4. . . .

vii

B Transmit Operation Examples B–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.1 Asynchronous Transmit B–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.1.1 Transmitting Asynchronous Data Packets (Bulky Data Interface) B–1. . . . . . .

B.1.2 Transmitting Asynchronous Control Packets B–2. . . . . . . . . . . . . . . . . . . . . . . . .

B.2 Unformatted Isochronous Transmit B–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.2.1 Transmitting Isochronous Data, Headers Auto Inserted

(Bulky Data Interface) B–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.2.2 Transmitting Fully Formatted Isochronous Data

(Microprocessor Interface) B–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.3 DV Transmit B–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.3.1 Transmitting DV Data from Bulky Data Interface, Headers Auto-Inserted B–4

B.3.2 Transmitting Fully Formatted Data Fully Formatted with 1394 Isochronous,

CIP, and H0 Headers (Microprocessor Interface) B–5. . . . . . . . . . . . . . . . . . . . .

C Isolation Considerations for TSB12LV42 C–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

viii

List of Illustrations

Figure Title Page

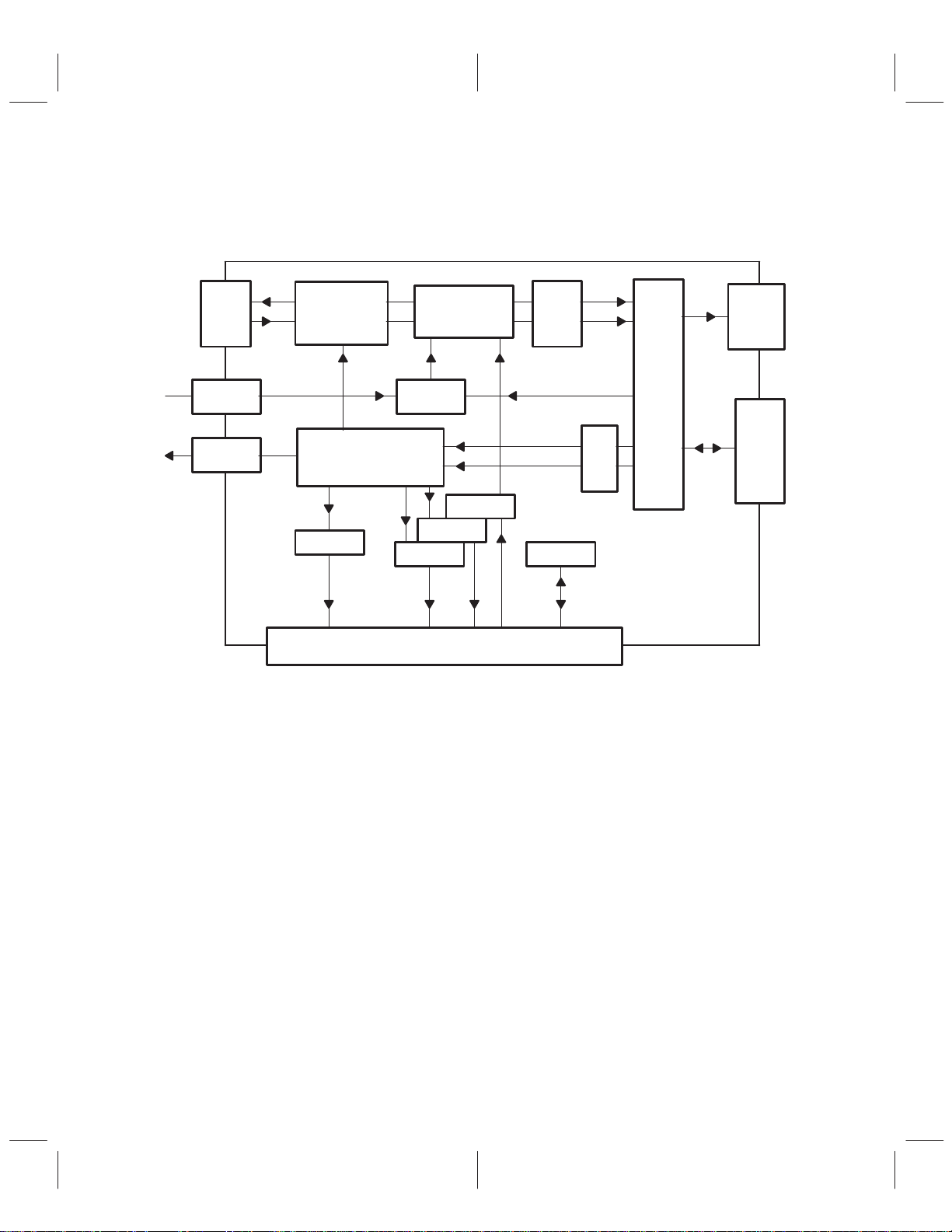

2–1 Functional Block Diagram 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–1 Example of a Source Packet Transmit Event 3–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–2 Source Packet Transmit Event Timing 3–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–3 DV Packet on 1394 Bus 3–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–4 DIF Block H0 3–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–5 ID Data In DIF Block 3–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–6 ID Data in DIF Block 3–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–7 DV Source Packet Format 3–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–8 CIP Header Format 3–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–9 Transmit from the Asynchronous Control Transmit FIFO (ACTX) 3–7. . . . . . . . . . . . . . . . . .

3–10 Transmit Asynchronous/Isochronous Data from BATX

by the Bulky Data Interface with Auto-Packetization 3–8. . . . . . . . . . . . . . . . . . . . . . . . .

3–11 T ransmit Asynchronous/Isochronous Data from BATX

by the MP/MC Interface with Auto-Packetization 3–9. . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–12 Transmit Asynchronous/Isochronous Data from BATX

by the Bulky Data Interface, No Auto-Packetization 3–9. . . . . . . . . . . . . . . . . . . . . . . . . .

3–13 Transmit Asynchronous/Isochronous Data from BATX

by the MP/MC Interface, No Auto-Packetization 3–10. . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–14 Data from Bulky Data Interface, Headers/Timestamp/H0 Automatically Inserted 3–14. .

3–15 Data and H0 Header from Bulky Data Interface,

Headers/Timestamp Automatically Inserted 3–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–16 Data 1394 Isochronous and CIP Headers 3–15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–17 All Data from BDIF, including 1394 Isochronous Header 3–15. . . . . . . . . . . . . . . . . . . . . . .

3–18 DBC Example 3–17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–19 Receive Asynchronous/Isochronous Data to Bulky Data Interface 3–20. . . . . . . . . . . . . .

3–20 Receive Asynchronous/Isochronous Data to Microprocessor Interface 3–20. . . . . . . . . .

3–21 Header, Data, and Trailer Received at BDIF 3–24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–22 Header, Data, and Trailer Received at MP/MC 3–24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–23 Header, Trailer Stripped, Data only sent to BDIF 3–25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–24 Header, Trailer Stripped, Data only set to MP/MC 3–25. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–25 DV Sub Mode Header, Trailer Saved to Registers, Data Discarded 3–26. . . . . . . . . . . . .

3–26 Determination of High Add and Low Add 3–28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–27 Time Stamp Value for LowAdd <3072 3–28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–28 Time Stamp Value for LowAdd . 3072 3–29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–29 Time Stamp Determination on Receive 3–29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–30 Quadlet-Transmit Format 3–29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–31 Block-Transmit Format 3–30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–32 Quadlet-Receive Format for Control FIFO 3–31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–33 Quadlet-Receive Format for Bulky Data FIFO 3–32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–34 Block-Receive Format for Control FIFO 3–33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

ix

3–35 Block-Receive Format for Bulky Data FIFO 3–33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–36 Isochronous-Transmit Format 3–35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–37 Isochronous-Receive Format for Bulky Data FIFO 3–35. . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–38 Snoop Format 3–36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–39 CycleMark Format 3–37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–40 Phy Configuration Format 3–37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–41 Receive Self-ID Format for Broadcast Write Receive FIFO 3–38. . . . . . . . . . . . . . . . . . . . .

3–42 Receive Self-ID Format for Bulky Asynchronous Receive FIFO 3–38. . . . . . . . . . . . . . . . .

3–43 Phy Self-ID Packet #0 Format 3–39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–44 Phy Self-ID Packet #1, Packet #2, and Packet #3 Format 3–40. . . . . . . . . . . . . . . . . . . . . .

4–1 Bulky Data Interface 4–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–2 BDIF Control Register 4–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–3 Bulky Data Interface Mode A Typical Application 4–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–4 Bulky Data Interface Mode B Typical Application 4–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–5 Bulky Data Interface Mode C Typical Application 4–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–6 Bulky Data Interface Mode D Typical Application 4–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–7 Functional Timing for Write Operations in the Unidirectional Modes 4–11. . . . . . . . . . . . . .

4–8 Critical Timing for Write Operations in Unidirectional Mode 4–11. . . . . . . . . . . . . . . . . . . . . .

4–9 Functional Timing for Write Operations in the Asynchronous Mode 4–12. . . . . . . . . . . . . . .

4–10 Functional Timing for Read Operations in Unidirectional Mode 4–12. . . . . . . . . . . . . . . . .

4–11 Critical Timing for Read Operations in Unidirectional Mode 4–13. . . . . . . . . . . . . . . . . . . . .

4–12 Functional Timing for Read Operations in Asynchronous Mode 4–13. . . . . . . . . . . . . . . . .

4–13 Functional Timing for Write Operations in Bidirectional Mode 4–14. . . . . . . . . . . . . . . . . . .

4–14 Critical Timing for Write Operations in Bidirectional Mode 4–14. . . . . . . . . . . . . . . . . . . . . .

4–15 Functional Timing for Read Operations in Bidirectional Mode 4–15. . . . . . . . . . . . . . . . . . .

4–16 Critical Timing for Read Operations in Bidirectional Mode 4–15. . . . . . . . . . . . . . . . . . . . . .

4–17 DVLynx Connections for 68000 Microcontroller 4–17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–18 DVLynx Connections for 8051 Microcontroller 4–18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–19 DVLynx Connections for TMS320AV7100 ARM Processor 4–18. . . . . . . . . . . . . . . . . . . . .

4–20 TSB12LV42 IOCR Register 4–19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–21 TMS320AV7100 ARM Read/Write Critial Timing 4–19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–22 TMS320AV7100 Handshake Mode Read Timing 4–24. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–23 TMS320AV7100 Handshake Mode Write Timing 4–24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–24 TMS320AV7100 ARM Blind Access Mode Read Timing 4–25. . . . . . . . . . . . . . . . . . . . . . .

4–25 TMS320AV7100 ARM Blind Access Mode Write Timing 4–25. . . . . . . . . . . . . . . . . . . . . . .

4–26 Motorola 68000 Read Timing 4–28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–27 Motorola 68000 Write Timing 4–28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–28 Motorola 68000 Read Critical Timing 4–29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–29 Motorola 68000 Write Critical Timing 4–30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–30 Intel 8051 Read Timing (Blind Access Read) 4–32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–31 Intel 8051 Write Timing (Blind Access Write) 4–32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–32 Intel 8051 Read Critial Timing 4–33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–33 Intel 8051 Write Critial Timing 4–34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–34 Big Endian Illustration chart 4–36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–35 Little Endian Illustration chart 4–36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–36 Little Endian Data Invariant System Design Illustration Chart 4–37. . . . . . . . . . . . . . . . . . .

4–37 Little Endian Address Invariant System Design Illustration Chart 4–38. . . . . . . . . . . . . . . .

x

4–38 Interrupt Hierarchy 4–39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–39 Functional Block Diagram of the TSB12LV42 to Phy Layer 4–40. . . . . . . . . . . . . . . . . . . . .

4–40 LREQ Timing 4–45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–41 Status-Transfer Timing 4–45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–42 Transmit Timing 4–46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–43 Receiver Timing 4–46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–1 Internal Register Map 5–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xi

List of Tables

Table Title Page

3–1 DV Bandwidth on IEEE 1394 3–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–2 DHIM/H0INST Settings for Different Header Insertion Schemes 3–13. . . . . . . . . . . . . . . . .

3–3 Asynchronous Receive Modes 3–19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–4 Receiving Isochronous data to the BIRX FIFO 3–22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–5 DV Receive Modes 3–23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–6 Time Stamp Field of Source Packet 3–27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–7 Quadlet-Transmit Format Functions 3–30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–8 Block-Transmit Format Functions 3–31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–9 Quadlet-Receive Format Functions 3–32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–10 Block-Receive Format Functions 3–34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–11 Isochronous-Transmit Functions 3–35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–12 Isochronous-Receive Functions 3–36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–13 Snoop Functions 3–36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–14 CycleMark Function 3–37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–15 Phy Configuration Functions 3–37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–16 Receive Self-ID Function 3–38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–17 Broadcast Write Receive FIFO Contents With Three Nodes on a Bus 3–39. . . . . . . . . . .

3–18 Bulky Data Asynchronous Receive FIFO (BARX FIFO) Contents 3–39. . . . . . . . . . . . . . .

3–19 Phy Self-ID Functions 3–40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–1 Modes of the BDIF 4–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–2 MCSEL Settings for Various Microprocessors 4–16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–3 TSB12LV42 MP/MC Interface Pin Function Matrix 4–16. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–4 TSB12LV42 IOCR Bit/Function Correlation Table and Power–up Default Setting 4–19. . .

4–5 TMS320AV7100 Critical Timing Characteristics 4–22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–6 Motorola 68000 Critical Timing Characteristics 4–27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–7 Intel 8051 Critical Timing Characteristics 4–31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–8 Phy Interface Control of Bus Functions 4–40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–9 TSB12LV42 Control of Bus Functions 4–41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–10 Request Functions 4–41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–11 Bus-Request Functions (Length of Stream: 7 Bits) 4–41. . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–12 Read-Register Request Functions (Length of Stream: 9 Bits) 4–41. . . . . . . . . . . . . . . . . .

4–13 Write-Register Request (Length of Stream: 17 Bits) 4–42. . . . . . . . . . . . . . . . . . . . . . . . . . .

4–14 TSB12LV42 Request Functions 4–42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–15 Request-Speed Functions 4–42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–16 Status-Request Functions (Length of Stream: 16 Bits) 4–44. . . . . . . . . . . . . . . . . . . . . . . .

4–17 Speed Code for Receive 4–45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xii

A–1 Receiving Asynchronous Data to the Bulky Asynchronous FIFO A–1. . . . . . . . . . . . . . . . . .

A–2 Receiving Asynchronous Data to the Asynchronous Control FIFO A–2. . . . . . . . . . . . . . . .

A–3 Receiving Isochronous Data to the Bulky Isochronous FIFO A–2. . . . . . . . . . . . . . . . . . . . .

A–4 Receiving Isochronous Data to the Bulky Isochronous FIFO A–3. . . . . . . . . . . . . . . . . . . . .

A–5 Receiving DV Data to the Bulky DV FIFO A–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–6 Receiving DV Data to the Bulky DV FIFO A–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B–1 Transmitting Asynchronous Data Packets B–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B–2 Transmitting Asynchronous Control Packets B–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B–3 Transmitting Isochronous Data, Headers Auto Inserted B–3. . . . . . . . . . . . . . . . . . . . . . . . . .

B–4 Transmitting Fully Formatted Isochronous Data B–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B–5 Transmitting DV Data from Bulky Data Interface, Headers Auto-Inserted B–4. . . . . . . . . .

B–6 Transmitting Fully Formatted Data Fully Formatted B–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xiii

xiv

1 Introduction

1.1 TSB12LV42

• Supports Provisions of IEEE 1394-1995 Standard for High-Performance Serial Bus

• Fully Interoperable with FireWire Implementation of IEEE-1394 (1995)

• Interfaces Directly to Texas Instruments TSB11LV01 and TSB21LV03A Physical Layer Devices

(100/200 Mbits/s)

• Single 3.3-V Supply Operation with 5-V Tolerance using 5-V Bias T erminals.

• High-Performance 100-Pin PZ (S-PQFP-G100) Package

• Multi-Microcontroller/Microprocessor Interface Supports TMS320AV7xxx, 680xx, 650x, 80x86,

Z8x Processors

• 64 Quadlet (256 byte) Control FIFO Accessed through Microcontroller Interface Supports

Command/Status Operations

• 8K-Byte FIFO Supports Standard-Definition Digital-Video Cassette Recorder (SD-DVCR),

Asynchronous, and Isochronous Modes

• Bus Reset Functions and Automatic IEEE-1394 Self-ID Verification

• Supports IEC61883 standard formats for transmitting SD-DVCR data over 1394.

FireWire is a trademark of Apple Computer, Incorporated.

1–1

1.2 TSB12LV42 Features

• Complies with IEEE 1394-1995 Standard

• Transmits and Receives Correctly Formatted 1394 Packets

• Supports SD-DVCR (DV) Formatted Isochronous Data Transfer

• Supports Isochronous Data Transfer

• Cycle Master (CM), Isochronous Resource Manager (IRM) and Bus Manager(BM) Capable

• Generates and Checks 32-Bit CRC

• Detects Lost Cycle-Start Packets

• 8K-Byte Bulky Data Interface (BDIF) for DV, Isochronous, and Asynchronous Data Transfer

• Multimode BDIF programmable for bytewide and memory mapped modes (independent for RX

and TX)

• Implements a 256-Byte Control FIFO (Control FIFO) and an 8K-Byte Bulky Data FIFO

• 8K-Byte BDIF FIFO Implements Six Independent Logical FIFOs for DV, Isochronous, and

Asynchronous Data Receive and Transmit through the BDIF

• Performs Bulky Asynchronous FIFO Packet Retry for Transmit (up to 256 Retries with Intervals

Up to 256 × 125 µs)

• 256-Byte Control FIFO for Control Packets

• Interfaces Directly to 100-Mbits/s and 200-Mb/s Physical Layer Devices Conforming to Annex

J of 1394-1995

• Chip Control with Directly Addressable Configuration Registers (CFRs)

• Interrupt Driven to Minimize Host Polling

• Multimode 8-/16-Bit Microcontroller/Microprocessor Interface

• Supports 16-Bit Width Timestamp Offsets for DV Receive and Transmit.

• Optimized Pinout for Easy Board Layout

• Includes Texas Instruments Bus Holder Circuitry for Phy-Link Isolation

• Automatic CIP Header Insertion

• Automatic H0 DIF Block Insertion

• Automatic Empty Packet Insertion

• Supports both NTSC and P AL Formats

• Generates Output Frame Pulse

1–2

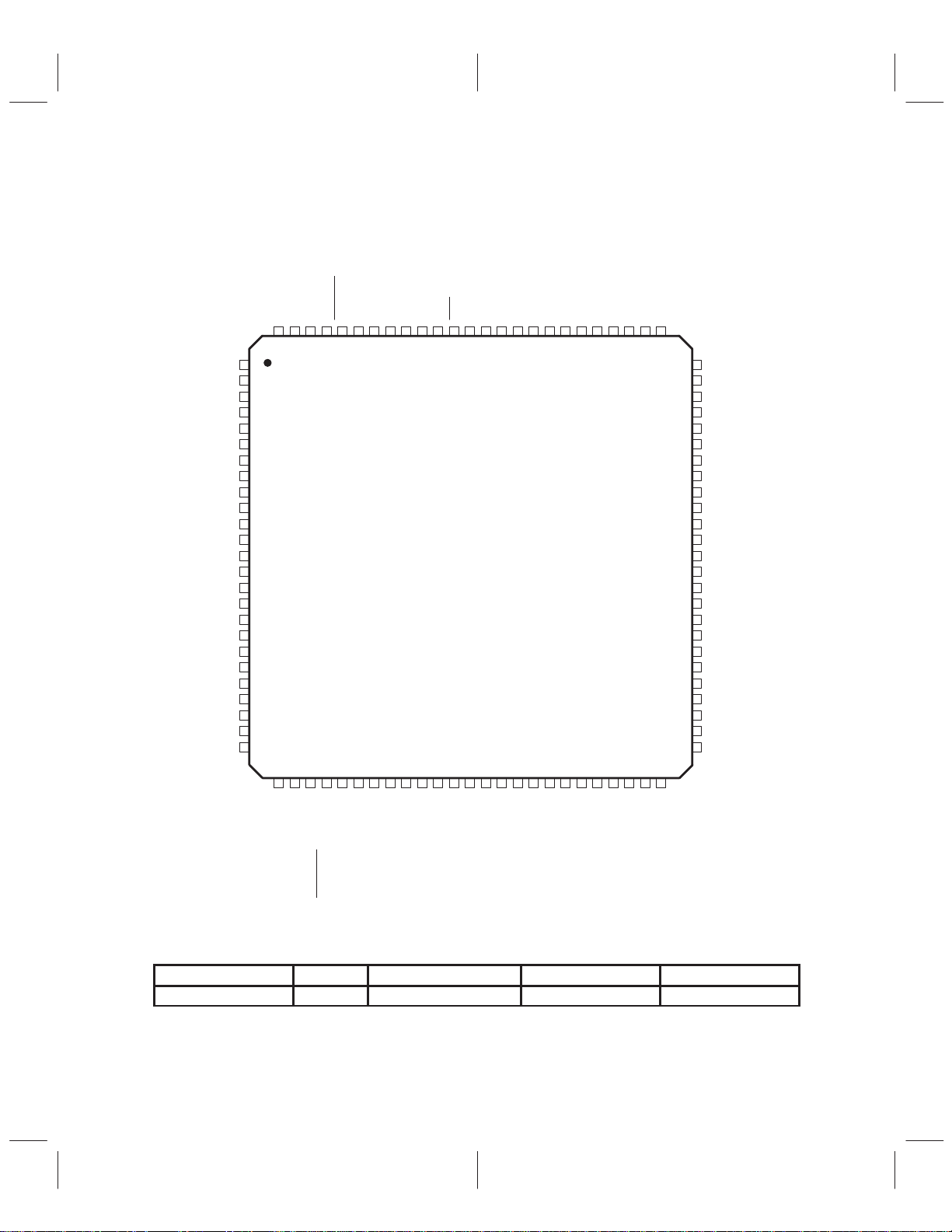

1.3 DVLynx Pinout

BDIF2

BDIF1

99

100

CC

+5V

CC

NC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

BDI/O0

BDI/O1

BDI/O2

BDI/O3

V

BDI/O4

BDI/O5

BDI/O6

BDI/O7

GND

CNTNDR

TEST1

TEST2

TEST3

V

CC

BDOCLK

V

BDO0

BDO1

BDO2

BDO3

GND

BDO4

BDO5

BDIF0

GND

97

98

29

28

RESET

BDO_FR

BDI_FR

94

95

96

32

31

30

BDIEN

LPS (STAT0)

92

93

34

33

PZ PACKAGE

(TOP VIEW)

+5V

CC

INT

BDICLK

91

35

RDY

V

88

89

90

TSB12LV42

38

37

36

GND

86

87

40

39

CS1

MCSEL1

85

41

MCSEL0

MCCTL1

MCCTL0

82

83

84

44

43

42

CC

V

81

45

DATA0

80

46

DATA8

79

47

DATA1

DATA9

DATA2

76

77

78

48

49

50

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

DATA10

DATA3

DATA11

GND

DATA4

DATA12

DATA5

DATA13

V

CC

BCLK

+5V

V

CC

DATA6

DATA14

DATA7

DATA15

GND

ADR8

ADR7

V

CC

ADR6

ADR5

ADR4

ADR3

ADR2

ADR1

D3D1D0

BDO6

BDO7

TEST4

CC

V

CYCLEIN

GND

D2

CTL1

CTL0

+5V

CC

V

CC

V

SCLK

LREQ

BDOF0

GND

BDOF2

BDOF1

ADR0

BDOEN

ISOLAT (STAT1)

BDIBUSY (STAT3)

BDOAVAIL (STAT2)

1.4 Ordering Information

ORDERING NUMBER NAME VOLTAGE DATA RATE PACKAGE

TSB12LV42PZ DVLynx 3.3 V – 5 V Tolerant I/O’s Up to 200 Mbits/s 100 pin PQFP

1–3

1.5 TSB12LV42 Terminal Functions

I/O

DESCRIPTION

TERMINAL

NAME NO.

ADR0 – ADR8 50, 51, 52,

53 54, 55,

56, 58 59

BCLK 66 I Host bus clock

BDI_FR 94 I Frame pulse input. The frame pulse input signal for PAL is 25 Hz and for

BDIBUSY(STAT3) 31 O BDIF is busy or status output 3. STAT3 is programmable at DIAG register

BDICLK 91 I Bulky data I/O clock. This terminal operates at up to 40 MHz.

BDIEN 93 I BDIO bus enable. If BDIEN is low, accesses to BDIO-bus are ignored.

BDIF2 – BDIF0 100, 99,

98

BDIO7 – BDIO0 9, 8, 7, 6,

4, 3 2, 1

BDO_FR 95 O Frame pulse output.

BDO7 – BDO0 27, 26, 25,

24 22, 21,

20, 19

BDOAVAIL(STAT2) 30 O Bulky data output available or status output 2. STAT2 is programmable at

BDOCLK 16 I Bulky data output clock. The bulky data output clock operates at up to

BDOEN 49 I BDO bus enable. If BDOEN is low, accesses to BDO-bus are ignored.

BDOF2 – BDOF0 47, 46, 45 O BDIF format bus for BDO Port. BDOF2 is the MSB.

CNTNDR 11 I/O Contender . The CNTNDR tells the Link when the local node is a contender

CS1 86 I Chip select. CS1 needs to be low when the device is to be selected for reads

CTL0, CTL1 40, 39 I/O Control 0 and control 1 of the Phy-Link control bus. CTL0 and CTL1 indicate

CYCLEIN 33 I Cycle In. CYCLEIN is an optional external 8-kHz clock used as the cycle

D0 – D3 38, 37, 36,35I/O Data 0 – 3 of the Phy-Link data bus. Data is expected on D0 – D1 for 100

DATA0 – DATA15 80, 78, 76,

74 71, 69,

64, 62 79,

77, 75, 73

70, 68, 63,

61

I MP/MC address lines. ADR0 is the MSB.

NTSC is 29.97 Hz at 50% duty cycle.

(reg 30h).

I/O BDIF format bus for BDIO port. BDIF2 is MSB.

I/O BDIF I/O data lines. BDIO7 – BDIO0 are high-speed I/O data lines for the

BDIF bus. They are primarily used for audio/data/video applications. These

lines can also be configured for input only. BDIO7 is the MSB.

O BDIF output data lines. BDO7 – BDO0 are data lines for high-speed output

on the BDIF bus for audio/data/video applications. These lines are

compliant with several standard interfaces. BDO7 is the MSB.

DIAG register (reg 30h).

40 MHz.

for IRM. This terminal can also be driven by the Link. The default status of

this terminal is input.

and writes.

the four operations that can occur in this interface.

clock. It should only be used when attached to the cycle master node. It is

enabled by the cycle source bit and should be tied high when not used.

Mbits/s and D0 – D3 for 200 Mbits/s. Data0 is the MSB.

I/O Data 0 – 15 of MC/MP host processor. Some of the DATAx terminals have

second functions depending on the status of the MCSEL terminals. DATA0

is the MSB.

1–4

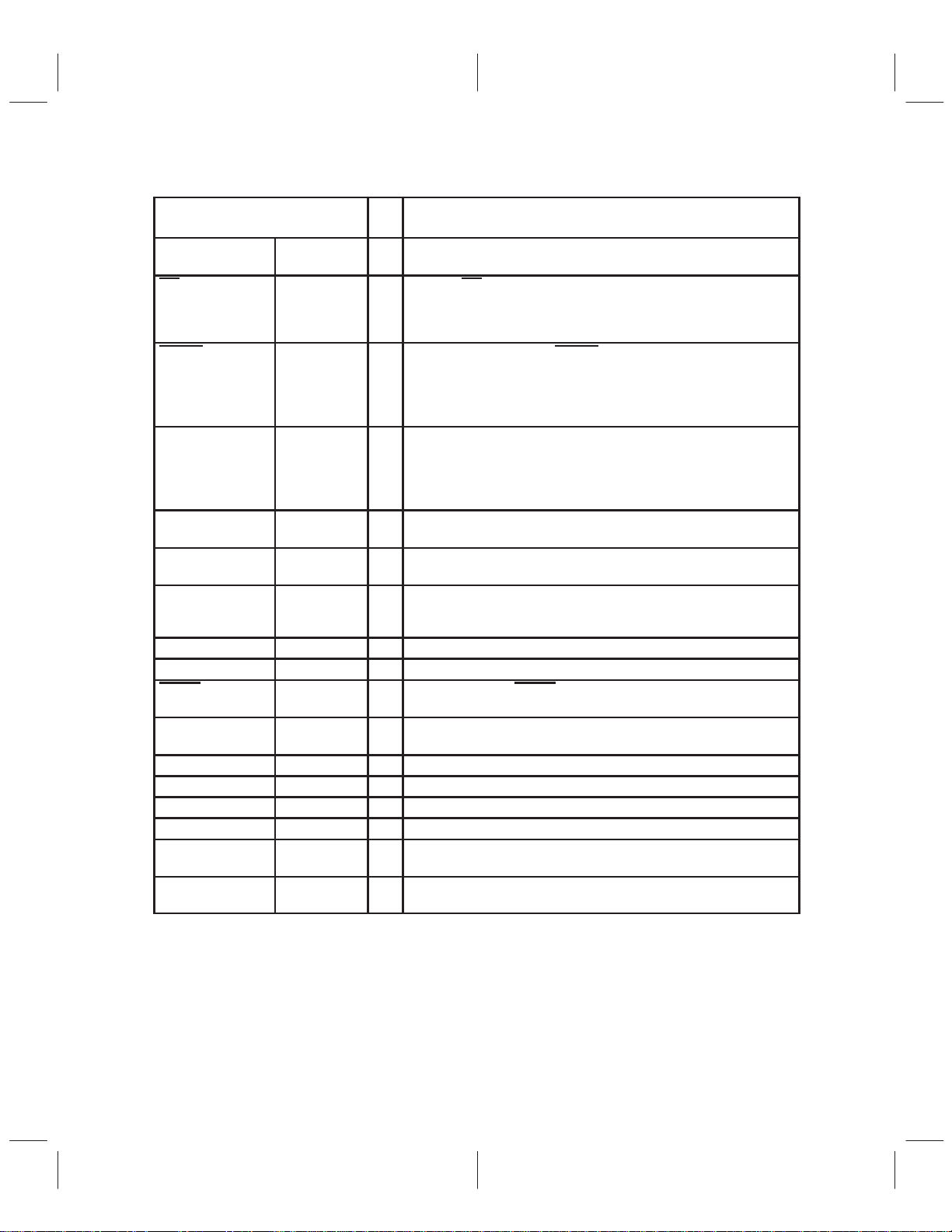

1.5 TSB12LV42 Terminal Functions (Continued)

I/O

DESCRIPTION

TERMINAL

NAME NO.

GND 10, 23, 34, 48

INT 89 O Interrupt. INT is used to notify the host that an interrupt has occurred.

ISOLAT(STAT1) 29 I/O Isolation or status output 1. ISOLA T is sampled during hardware reset to

LPS/STAT0 92 O Link power status or status output 0. LPS is used to drive the LPS input to

LREQ 44 O Link request. LREQ is a DVLynx output that makes bus request and

MCCTL0/1 82, 83 I Control lines for bus access. MCCTL0 and MCCTL1 function depends

MCSEL0/1 84, 85 I Select lines for MP/MC. MCSEL0 and MCSEL1 are selection lines for

NC 18 O No connect

RDY 88 O Ready line. When high, RDY indicates the end of an MP/MC access.

RESET 96 I Reset (active low). RESET is the asynchronous power on reset to the

SCLK 42 I System clock. SCLK is a 49.152-MHz clock from the Phy. This terminal

TEST1 12 I Test pin should be tied to VCC.

TEST2 13 I Test should be tied to GND.

TEST3 14 I Test pin should be tied to VCC.

TEST4 28 I Test pin should be tied to GND.

V

CC

VCC5V 15, 41, 65, 90 5-V ±5% power supplies for 5V tolerant I/O terminals. These terminals

60, 72, 87, 97

5, 17, 32, 43

57, 67, 81

Ground

This terminal can be active low or active high depending on the status of

the INTPOL bit in IOCR register. It is high-impedance when no interrupt

is pending.

determine if isolation is present. When this terminal is high, this indicates

NO isolation is being used. STA T1 is driven as an output after hardware

reset and used as a status output. STAT1 is programmable in the DIAG

register (reg 30h)

the Phy. This signal indicates that the LLC is powered up and active. This

output toggles at 1/32 of BCLK or SYSCLK depending on the

microprocessor used. STA T0 is used to MUX out internal signals. ST AT0

is programmable in the DIAG register (reg 30h).

accesses the Phy layer.

on MP/MC type being used.

the MP/MC-type being used. These terminals have an impact on the

function MCTRL,ADR, RDY and DA TA terminals.

device.

generates the 24.576-MHz clock (NCLK).

3.3 V (3 V – 3.6 V) supply voltage

can be tied to 3.3 V if no 5 V devices interface to the TSB12LV42.

1–5

1–6

2 Architecture

BDIF

8K Byte

6-Queue

Bulky FIFO

DV/A/I

Packetizer

FrP In TS Gen

Rx/Router/

FrP Out

Time Stamp

Recovery

ATF

BusRST

BRF

ARF

MC/MP Interface

Conventions:

Asynchronous packet = Async packet

Isochronous packet = Isoc packet

Asynchronous Transmit FIFO = ATF

Broadcast Receive FIFO = BRF

Asynchronous Receive FIFO = ARF

Configuration registers = CFR

SD-DVCR 480 byte source packet = DV-packet

MP/MC = Microprocessor/Microcontroller

Tx

CFR

Rx

Link

Core

CM/

CT

Status

Pins

PhyLink

IF

Figure 2–1. Functional Block Diagram

2.1 Bulky Data Interface

The bulky data interface (BDIF) enables the TSB12L V42 to provide sustained data rates up to 160 Mbits/s.

The bulky data FIFO supports DV compressed data as defined by the Blue Book standard for digital video,

asynchronous, and isochronous data for both transmit and receive.

2.2 Bulky Data FIFO

The bulky data FIFO is where the BDIF buffers the transmit or receive data. The bulky data FIFO is

partitioned into six logical divisions. Each of these logical FIFO sizes are programmable on four quadlet

boundaries. These six FIFOs are:

• Bulky DV transmit FIFO (BDTX)

• Bulky DV receive FIFO (BDRX)

• Bulky asynchronous transmit FIFO (BATX)

2–1

• Bulky asynchronous receive FIFO (BARX)

• Bulky isochronous transmit FIFO (BITX)

• Bulky isochronous receive FIFO (BIRX)

The following sections give functional descriptions to these logical FIFOs. See Section 4.1,

Interface

, for more detail on using this FIFO to transmit/receive data.

Bulky Data

2.2.1 Bulky DV Transmit FIFO (BDTX)

The BDTX FIFO is used to transmit DV data according to the Blue Book standard. Data is typically written

to this FIFO for the BDIF or microcontroller interface in quadlets (four bytes). The TSB12LV42 can be

configured to automatically insert 1394 isochronous headers, CIP (or common isochronous packet)

headers, and H0 DIF blocks. The TSB12L V42 can also be configured to automatically insert empty packets

to smooth out the bursty data rates. This is necessary to accommodate receiving nodes whose FIFO’s are

sized to receive evenly distributed data.

2.2.2 Bulky DV Receive FIFO (BDRX)

The BDRX FIFO is typically used to store DV data received from the link layer core and then forward it on

to a high speed application via the BDIF . Only isochronous port 0 of the link layer core can access the BDRX

FIFO.

2.2.3 Bulky Asynchronous Transmit FIFO (BATX)

The BATX FIFO is typically used to transmit asynchronous data packets from high-speed applications.

Either the BDI or the microcontroller can load data into this FIFO.

2.2.4 Bulky Asynchronous Receive FIFO (BARX)

The BARX FIFO is typically used to store received asynchronous data packets to be forwarded to a

high-speed application via the BDIF. The microcontroller can also read data from the BARX FIFO one

quadlet at a time. This FIFO is the default location for self-IDs.

2.2.5 Bulky Isochronous Transmit FIFO (BITX)

The BITX FIFO is typically used to transmit isochronous data packets from high-speed applications. Data

can be loaded into the FIFO by either the BDIF or by the microcontroller one quadlet at a time.

2.2.6 Bulky Isochronous Receive FIFO (BIRX)

The BIRX FIFO is typically used for receiving isochronous data and forwarding it to a high-speed application

via the BDIF . Data can also be forwarded to the microcontroller interface one quadlet at a time. Isochronous

ports 1 through 7 have access to this FIFO. Each port can be programmed to filter incoming packets

according to the isochronous channel and/or isochronous header T AG value.

2.3 DV Transmit and Receive Control

The DVLynx transmit and receive circuitry controls automatic insertion of the common isochronous packet

(CIP) header information as defined by the IEC 61883 standard. This circuitry also controls the automatic

insertion of the H0 DIF block header as defined by the Blue Book standard for SD-DVCR. The transmit

circuitry also includes automatic timestamp insertion. The TSB12LV42 has an empty packet insertion

function that will automatically insert a number of empty packets within a frame. These empty packets

smooth out bursty data so that it is easier to handle for the receiving node, whose FIFOs are designed for

evenly distributed data.

2–2

2.4 Microprocessor/Microcontroller Interface

The microprocessor/microcontroller interface (MP/MC) is used as the host controller port. It is designed to

work with several standard MP/MCs including Motorola 68000, Intel 8051, and ARM processors. The

interface supports both 8-bit and 16-bit wide data busses as well as both little endian and big endian

microcontrollers. This interface has two basic modes of operation: handshake Mode and blind access mode.

See Section 4.2,

Microprocessor Interface

, for more details.

2.5 Control FIFO

The control FIFO is partitioned into three logical FIFOs. The size of each of these logical FIFOs is

programmable on quadlet boundaries. These three FIFOs are called:

• Asynchronous control transmit FIFO (ACTX)

• Asynchronous control receive FIFO (ACRX)

• Broadcast write receive FIFO (BWRX)

2.5.1 Asynchronous Control Transmit FIFO (ACTX)

The ACTX FIFO is typically used to transmit small asynchronous control packets sent by the

microprocessor/microcontroller. The ACTX FIFO can also be used to support asynchronous traffic at very

low data rates. Asynchronous packets are written into the FIFO and transmitted using the ACRXF , ACTXC,

and ACTXCU registers. See Section 3.3.1,

concerning the ACTX.

Transmitting Asynchronous Control Packets

2.5.2 Asynchronous Control Receive FIFO (ACRX)

The ACRX FIFO is typically used to receive asynchronous control packets other than self-ID packets.

Regular asynchronous control packets are usually received to the ACRX FIFO. This FIFO is accessible by

the microcontroller port through the ACRX register. See Section 3.4.1,

for more details concerning the ACRX.

Receiving Asynchronous Packets

, for more details

,

2.5.3 Broadcast Write Receive FIFO (BWRX)

The BWRX FIFO is typically used to receive asynchronous broadcast write request packets. See

Section 3.4.1,

Receiving Asynchronous Packets

, for more detail concerning the BWRX.

2.6 Physical Layer

The physical layer interface provides phy-level services to the transmitter and receiver. This includes

gaining access to the serial bus, sending packets, receiving packets, and sending/receiving acknowledges.

The TSB12LV42 supports Texas Instruments bus-holder circuitry on the Phy-link interface terminals. By

using the internal bus holders, the user avoids the need for the complex Annex J isolation method. The bus

holders are enabled by connecting the ISOLA T

terminal to ground.

2.7 Configuration Register (CFR)

The TSB12L V42 is configured for various modes of operation using CFRs. These registers are accessed

via the host microprocessor/microcontroller. The CFR space is 512 bytes, thus the need for a 9-bit address

bus. All CFRs are 32-bits wide. Since the microcontroller interface is either 8 or 16-bits wide, it must perform

a byte stacking/unstacking operation internally on the incoming (write) or outgoing (read) microcontroller

data. Chapter 5 gives a map of all the registers and detailed descriptions of all the register bits.

2–3

2–4

3 Functional Description and Data Formats

3.1 Overview

The TSB12L V42 is a 1394 interface for high-speed audio, video, and data applications at up to 200 Mb/s.

For these high-speed applications a bulky data interface (BDIF) has been implemented that supports long

term data rates up to 60 Mb/s. Burst data rates, however, can go up to 160 Mb/s.

The TSB12L V42 contains two FIFOs that are a 256-byte control FIFO (Control FIFO) and an 8K-byte BDIF

FIFO. These two FIFOs are further subdivided into smaller logical FIFOs.

Bulky data is usually buffered in the BDIF FIFO. The BDIF FIFO supports DV, asynchronous, and

isochronous formatted traffic for receive and transmit.

Asynchronous packets (for 1394 bus control/status) are usually written to or read from the Control FIFO.

For lower data rates the Control FIFO can also be used to buffer asynchronous application data. Based on

destination address, received asynchronous request packets may be steered into either the Control FIFO

or the BDIF FIFO.

A separate self-ID-FIFO allows faster BUS setup and reduces software complexity . The 256-Byte Control

FIFO (Control FIFO) is partitioned into three logical FIFOs. The size of these three logical FIFOs is

programmable on quadlet boundaries. These FIFOs are called:

1. Asynchronous control transmit (ACTX) FIFO

2. Asynchronous control receive (ACRX) FIFO

3. Broadcast write receive (BWRX) FIFO.

The 8K-Byte BDIF FIFO is partitioned into six logical FIFOs. The size of these FIFOs is programmable on

four quadlet (hexlet) boundaries. These FIFOs are called:

1. BDIF DV transmit (BDTX) FIFO

2. BDIF DV receive (BDRX) FIFO

3. BDIF asynchronous transmit (BATX) FIFO

4. BDIF asynchronous receive (BARX) FIFO

5. BDIF isochronous transmit (BITX) FIFO

6. BDIF isochronous receive (BIRX ) FIFO

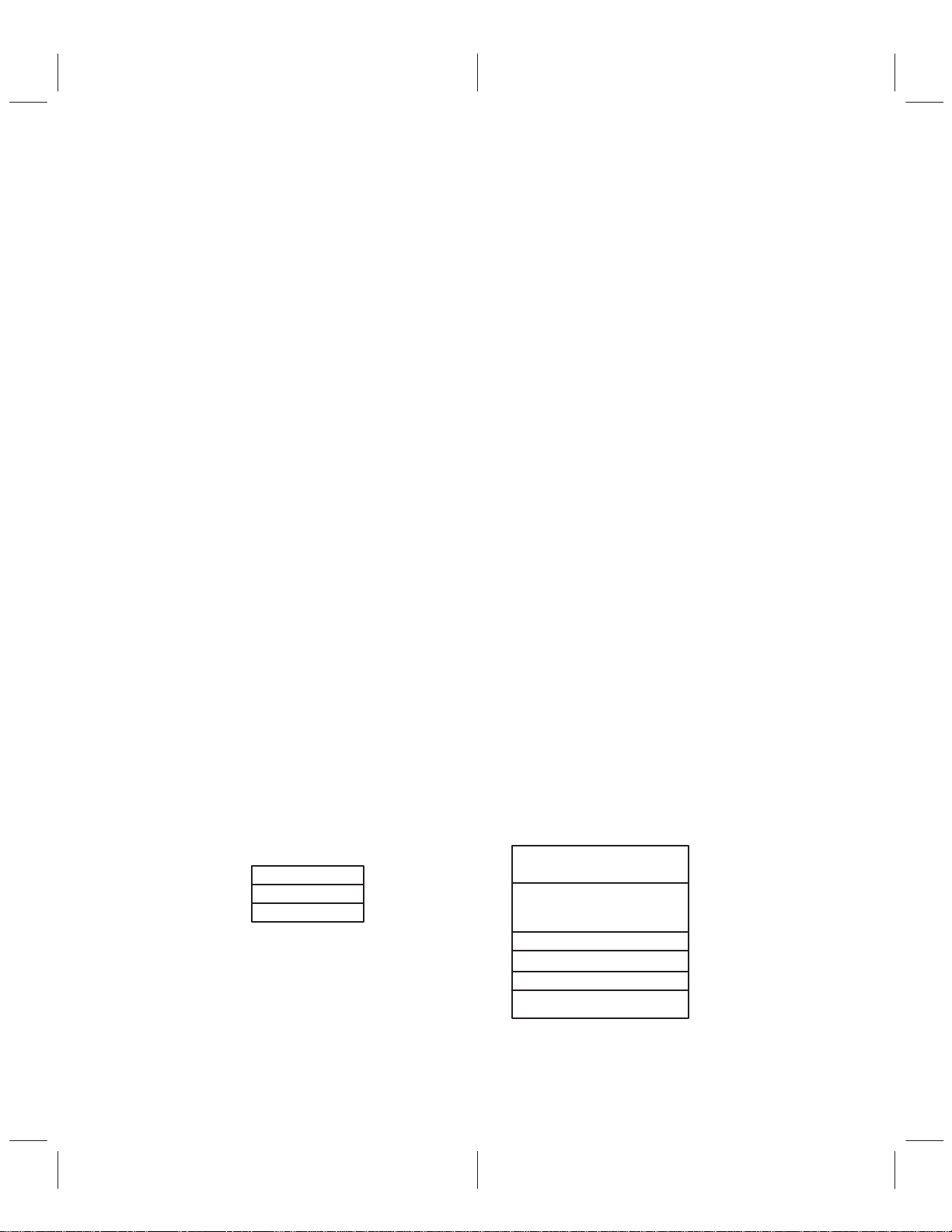

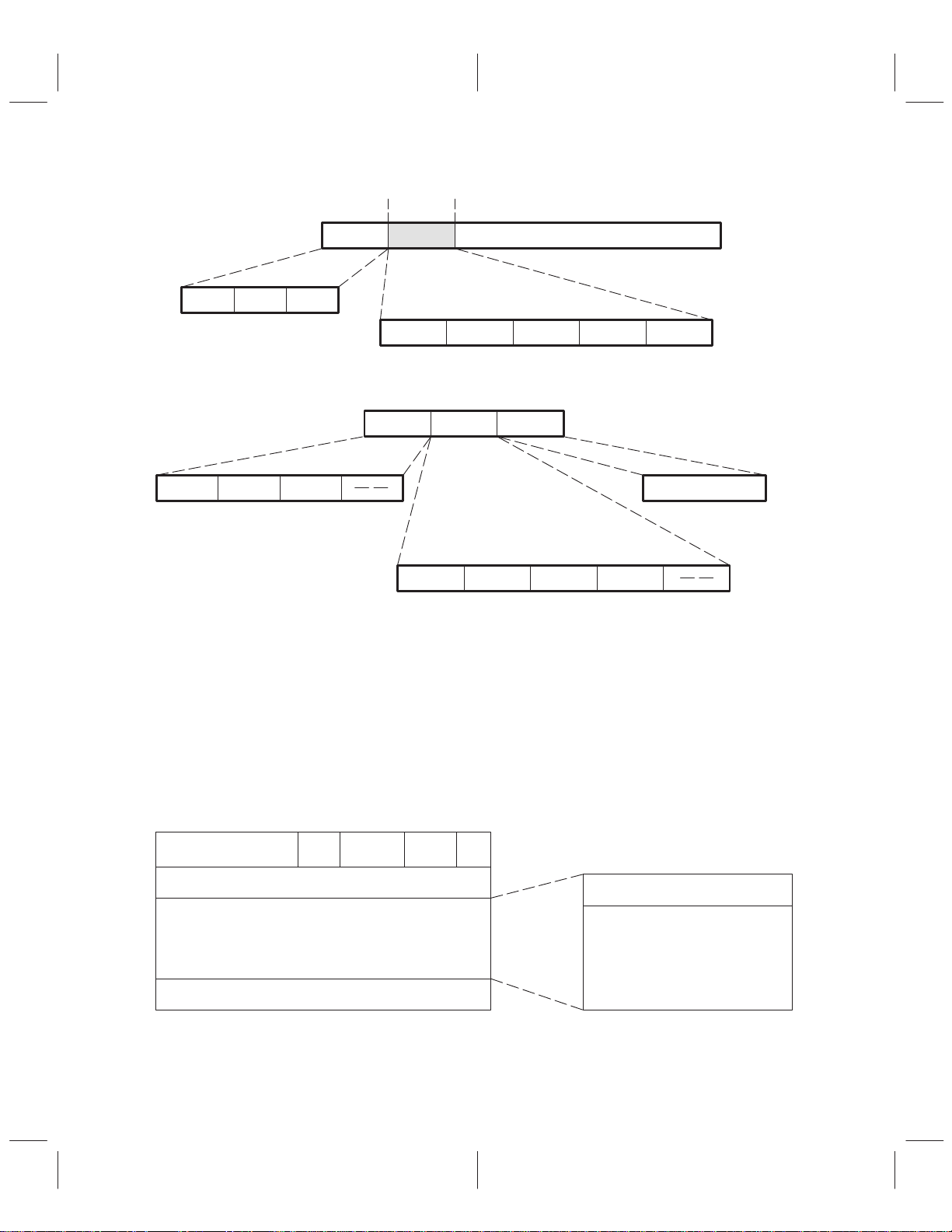

The Control and BDIF FIFOs are structured are as follows:

8K-Byte BDIF FIFO Structure

256-Byte Control

FIFO Structure

00h

FFh

ACTX

ACRX

BWRX

0000h

1FFFh

DV TX Buffer

DV RX Buffer

Async TX Buffer

Async RX Buffer

Isoch TX Buffer

Isoch RX Buffer

The TSB12L V42 (with built-in programmable Endianness) interfaces directly to most microprocessors and

microcontrollers.

3–1

3.2 DV on 1394 Overview

3.2.1 DV interface

NCLK

820020 Clocks

250 Source Packets NTSC

BDI_Fr

NTSC PAL

3280 Clks for 249 SPs

3300 Clks for Last SP

983040 Clocks

300 Source Packets PAL

3277 Clks for 299 SPs

3217 Clks for Last SP

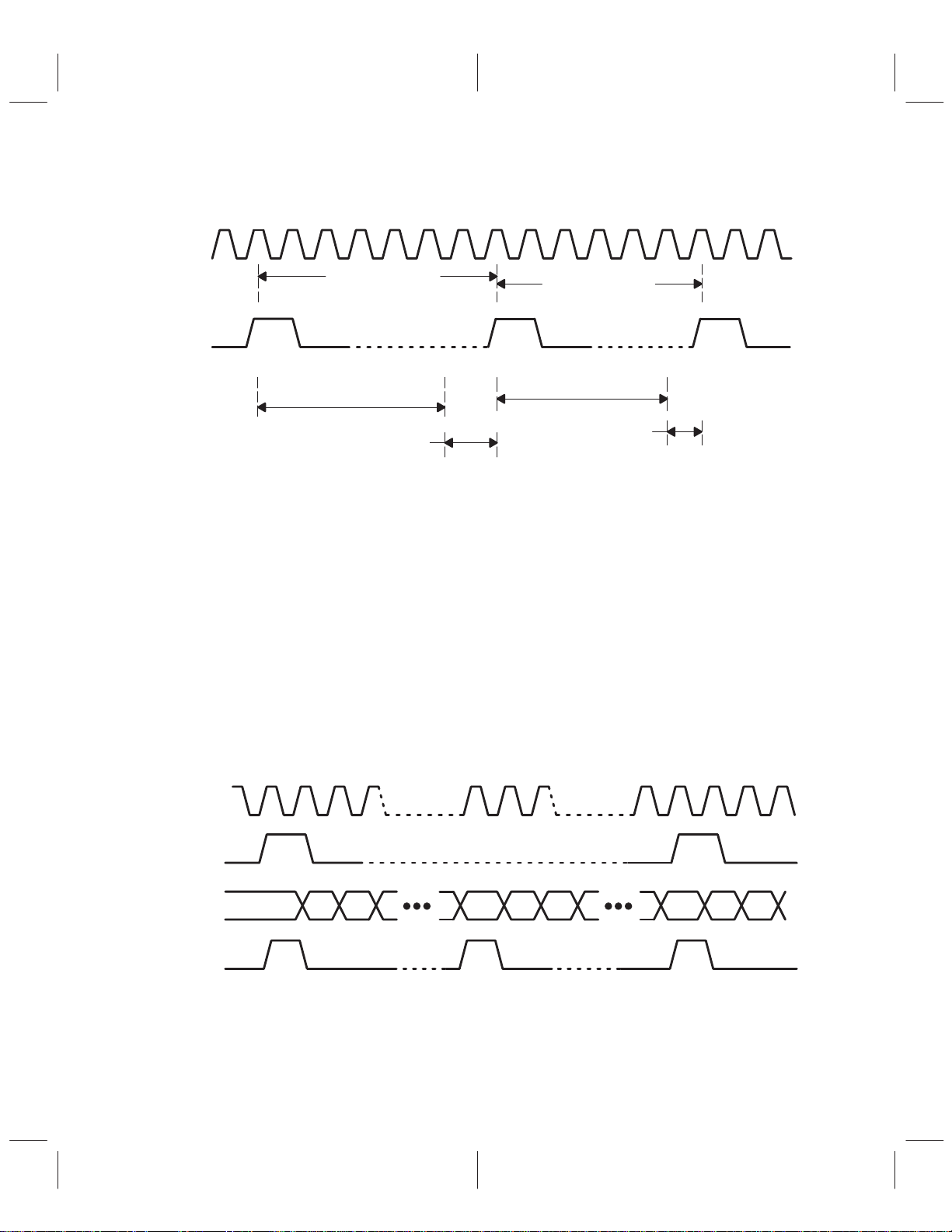

Figure 3–1. Example of a Source Packet Transmit Event

A source packet (SP) event occurs 250 times in 1 NTSC frame or 300 times in 1 PAL frame. NCLK is an

internal 24.576-MHz clock derived from the 49.152-MHz SCLK. The first BDI_FR pulse starts the source

packet counter used to generate the empty packet insertion algorithm. The TSB12L V42 provides automatic

empty packet insertion on transmit to evenly distribute the 250/300 source packets within a frame. Turning

off the appropriate bit in the MDCR Register can turn off this feature. In one NTSC frame, there are 820020.0

NCLKs and therefore 3280.08 NCLKs per source packet. That is equivalent to 249 source packets of 3280

NCLKs and one source packet of 3300 NCLKs. For NTSC a SP event is signaled every 3280 clocks for the

first 249 SP event and the last SP event is signaled after 3300 clocks following the 249th event. This yields

a 33.367-ms frame rate (40.69 ((3280 × 249) + 3300)). For PAL the time for 1 frame is 40.00 ms

(40.69 ((3277 × 299) + 3217)).

Cycle synchronous (CS) events occurs every 125 µs ( this is the isochronous cycle base rate). During each

isochronous cycle a complete SP is transmitted or an empty packet (EP) is transmitted. If two contiguous

CS events occur without an SP event occurring, then an empty packet is forced in the current isochronous

cycle regardless if a complete source packet is available in the FIFO. If a SP event occurs between two CS

events but a complete source packet is not available in the FIFO, then an empty packet is transmitted in the

current isochronous cycle.

NCLK

BDI_Fr

CLK_cntr

SPevent

Valid

001 002 3280 001 002 3300 001 002

Figure 3–2. Source Packet Transmit Event Timing

NOTE: BDI_Fr has already been synchronized with NCLK.

3–2

3.2.2 DV Bandwidth on IEEE1394

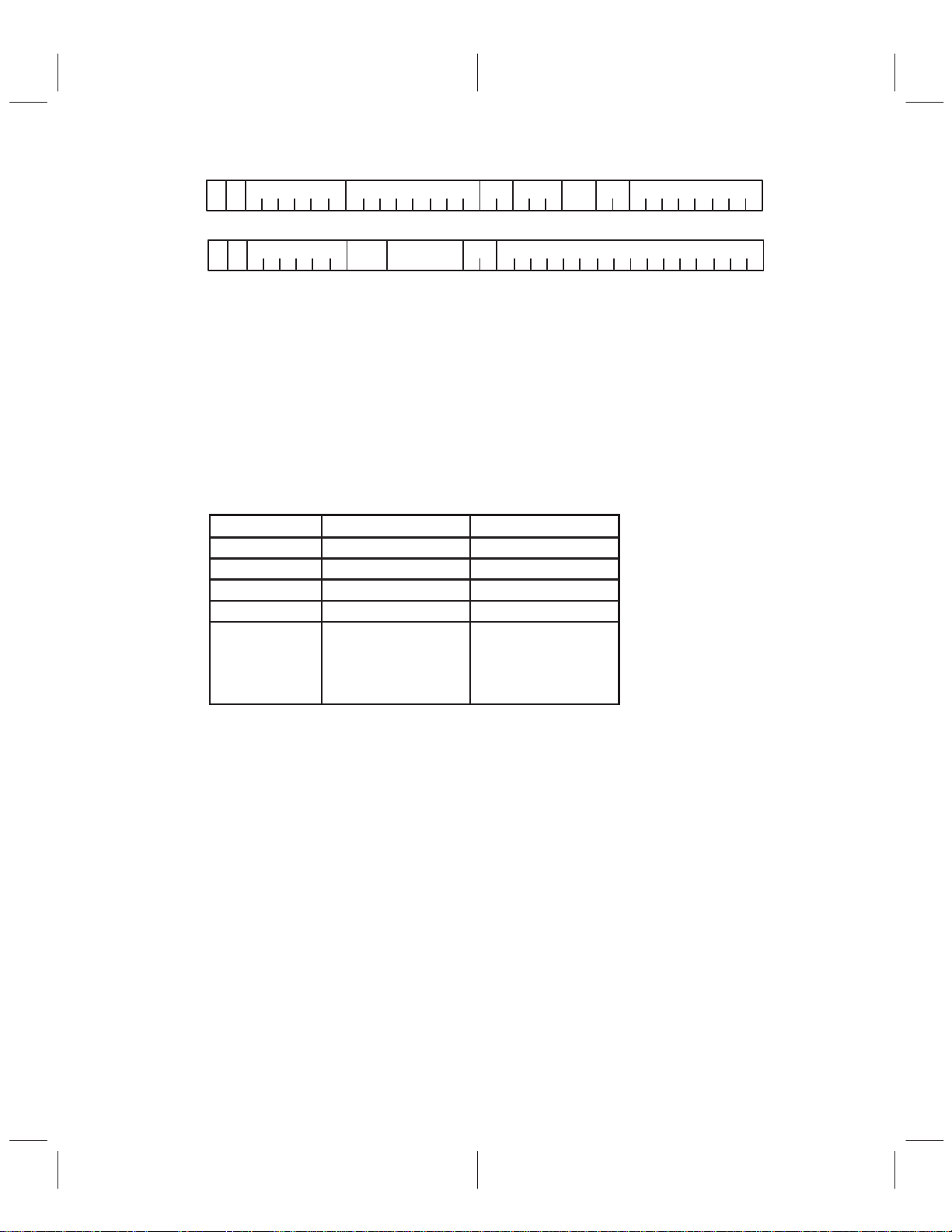

Table 3–1. DV Bandwidth on IEEE 1394

MAX SP-BW

(Mbits/s)

30.72 32 20/500

†

SP-BW: Source package bandwidth (based on 480 byte DV).

‡

1394-BW: Overall bandwidth of 1394 bus on physical medium (includes 4-byte 1394

packet transmit header, 4-byte packet header CRC, 8-byte CIP header, actual

payload, and 4-byte payload CRC. This bandwidth should be allocated by the DV

transfer initiator.

†

MAX 1394-BW

(Mbits/s)

‡

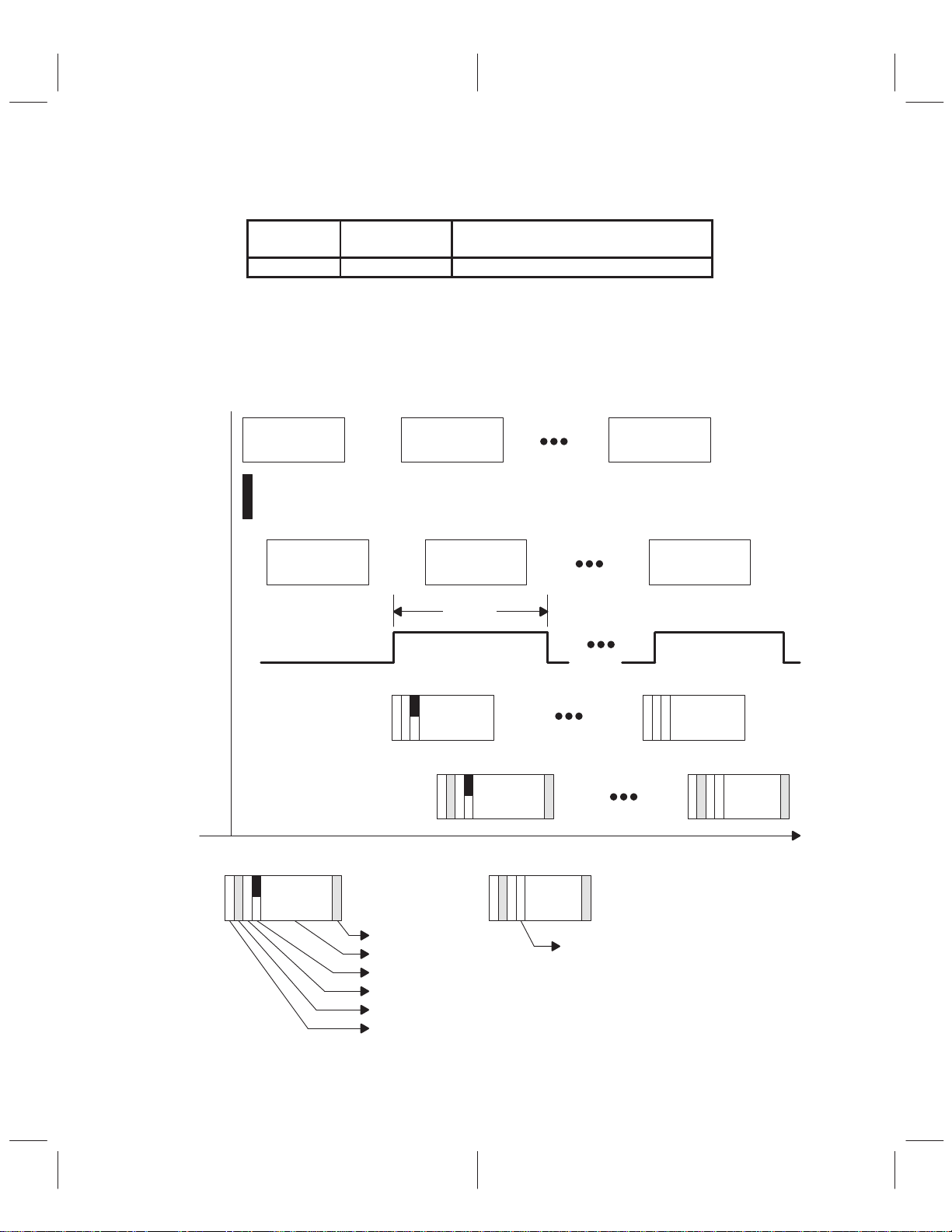

3.2.3 DV Transmission over IEEE1394

A DV-packet on the 1394 bus:

POSSIBLE DV BUS PACKET SIZE IN-

CLUDING CIP, 1394-Hdr, CRCs (Bytes)

Data from

DV Appl.

Data from

TS Gen.

Input to

Transmitter

Internal

I-slot

Enable

Data to

Linkcore

Data on

1394 Bus

A DV-packet on the 1394 bus:

1st DV-cell

480 Bytes

480 Bytes

2nd DV-cell

125 µs

492 Bytes

500 Bytes

250/300th

DV-cell

Time

Payload CRC

DV-cell

CIP1 with timestamp

CIP0 Header

Header CRC

1394 Header

CIP1 without timestamp

Figure 3–3. DV Packet on 1394 Bus

3–3

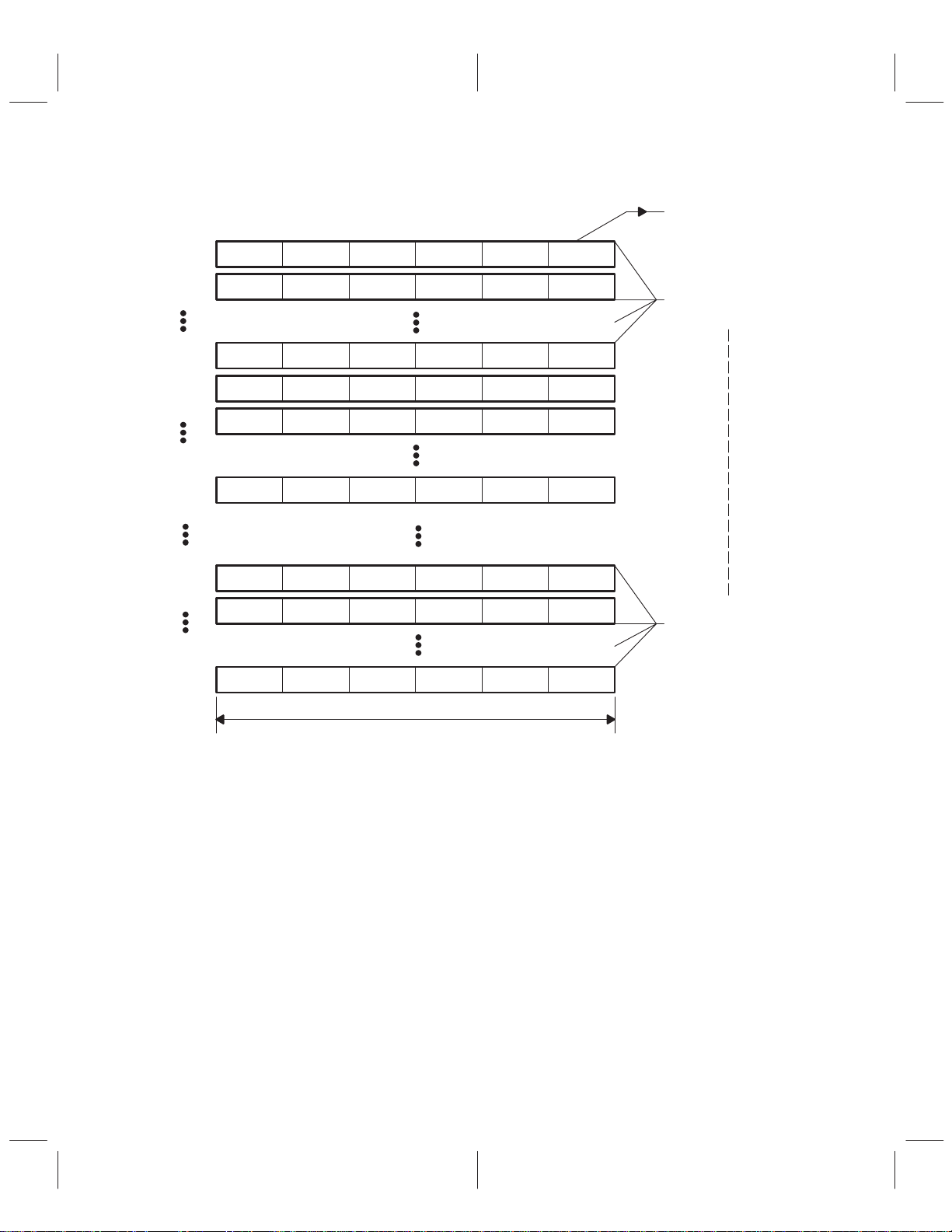

3.2.4 Source Packet/DIF Block Format

Source

Packets

80 Bytes DIF Block

0

1

24

25

49

225

249

H0 SC0 SC1 VA0 VA1 VA2

A0 V0 V1 V2 V3 V4

V129 V130 V131 V132 V133 V134

H0 SC0 SC1 VA0 VA1 VA2

A0 V0 V1 V2 V3 V4

V129 V130 V131 V132 V133 V134

H0 SC0 SC1 VA0 VA1 VA2

A0 V0 V1 V2 V3 V4

V129 V130 V131 V132 V133 V134

DIF Sequence 0

DIF Sequence 9

480 Bytes (120 Quadlets) Data Block

NOTES: A. SD-DVCR 525-50 System is identical to 525-60 system except the number of source packets is 300

B. H0 = Header DIF block

SCi = Subcode DIF block (i = 0, 1)

VAi = VAUX DIF block i (i = 0, 1, 2)

Vi = Video DIF block (i = 0 – 134)

Ai = Audio DIF block (i = 0 – 8)

Figure 3–4. DIF Block H0

The H0 DIF block is inserted into the first 80 bytes every 25th packet. The TSB12LV42 gives the system

designer the option to automatically insert the 80 byte DIF block before transmit. The value of the H0 header

DIF block is programmable via internal registers 1A4h and 1A8h.

Figure 3–5 shows the H0 header DIF block. Bytes 0–7 can be inserted by the link core or can be provided

by the application with the data.

3–4

ID0 ID1 ID2

Byte Position

0 1 2 8 . . . . .. . . . . . . . . . . . . . . . . . . . . . . . . . 793 7

ID FF_FF_FF_ . . . . . . . . . . . . . . _FFH0

H0R3 H0R4 H0R5 H0R6 H0R7

Figure 3–5. ID Data In DIF Block

ID0

SCT2 SCT1 SCT0

MSB

MSB

ID1 ID2

DBN7 . . . DBN0

DSEQ3 DSEQ2 DSEQ1 DSEQ0

Figure 3–6. ID Data in DIF Block

3.2.5 DV Packets CIP Header Calculations

The TSB12LV42 has an option to automatically insert CIP headers and timestamps during transmission.

The CIP headers, or common isochronous packet headers, follow the format of the IEC 61883-2 standard

for transmitting SD-DVCR data over 1394. The values of the CIP headers are programmable in registers

1CCh and 1D0h. The TSB12L V42 also has the option to automatically calculate and insert timestamp values

into the CIP1 header. The timestamp is inserted either into the first transmitted packet in the next

isochronous cycle (register F0h, bit 1 1 INTSSP=0) or into the first full data packet of the next frame (register

F0h, bit 1 1 INTSSP=1).

Data_Length

T ag Channel Tcode Sy

Header_CRC

Data Field

Data_CRC

Length field is either 488 bytes (DV-Source Packet) or 8 bytes (empty packet).

Figure 3–7. DV Source Packet Format

CIP Header

Real Time Data

3–5

DCIP0 00

SID

DBS FN QPC rsv DBC

SPH

DCIP1 01

static values:

DXH: tag,chanNum, spd, sy (1394 Isochronous Header)

DCIPX0:SID, DBS, FN, QPC, SPH, DBC

DCIPX1:FMT, 50/60, STYPE

calculated values:

DXH: length (1394 Isochronous Header)

DCIPX1: SYT

DCIPX0: DBC

STYPE 50/60 50/60

00000 525–60 System

00001 Reserved Reserved

00010 1125–60 System 1250–50 System

0001 1

11111

†

525-60 system: The 525-line system with a frame frequency of 29.97 Hz

625-50 system: The 625-line system with a frame frequency of 25.00 Hz

SD-DVCR: Standard-definition digital-video cassette recorder

FMT

50/60

STYPE

rsv SYT

Figure 3–8. CIP Header Format

0 1

†

.

.

.

Reserved Reserved

625–50 System

†

3.3 Transmit Operation

The functional description for transmission is shown in the following sections. The transmit format describes

the expected organization of data presented to the TSB12L V42 at the host-bus interface.

3.3.1 Transmitting Asynchronous Control Packets

Asynchronous control packets are typically transmitted by the microprocessor (host) using the

Asynchronous Control Transmit FIFO (ACTX). This FIFO is part of the 256 bytes Control FIFO. It is

configurable in register 44h (Asynchronous Control Data Transmit FIFO Status). The ACTX FIFO can also

be used for asynchronous data traffic at low data rates.

For transmit, the 1394 asynchronous headers and the data are loaded into the ACTX by the microprocessor.

The microprocessor has access to the ACTX FIFO through registers 80h – 8Ch. The asynchronous header

must fit the format described in Section 3.6,

TSB12LV42)

3–6

.

Asynchronous Transmit Data Formats (Host Bus to

Loading...

Loading...