Texas Instruments TSB12LV41APZ Datasheet

TSB12LV41A (MPEG2Lynx)

e

IEEE 1394-1995 Link-Layer Controller

for Consumer Applications

SLLS339

MARCH 1999

Printed on Recycl

IMPORTANT NOTICE

T exas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue

any product or service without notice, and advise customers to obtain the latest version of relevant information

to verify, before placing orders, that information being relied on is current and complete. All products are sold

subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those

pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent

TI deems necessary to support this warranty . Specific testing of all parameters of each device is not necessarily

performed, except those mandated by government requirements.

CERT AIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MA Y INVOLVE POTENTIAL RISKS OF

DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL

APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR

WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER

CRITICAL APPLICA TIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERST OOD TO

BE FULLY AT THE CUSTOMER’S RISK.

In order to minimize risks associated with the customer’s applications, adequate design and operating

safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent

that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other

intellectual property right of TI covering or relating to any combination, machine, or process in which such

semiconductor products or services might be or are used. TI’s publication of information regarding any third

party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.

Copyright 1999, Texas Instruments Incorporated

Contents

Section Title Page

1 Introduction 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1 Description 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2 Features 1–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3 Related Documents 1–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4 Ordering Information 1–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.5 Terminal Assignments 1–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2 Architecture 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1 Bulky Data Interface 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2 Bulky Data FIFO 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.1 BDI MPEG2 (DVB)/DSS Transmit FIFO (BMDTX) 2–3. . . . . . . . . . . . . . . . . . . .

2.2.2 BDI MPEG2 (DVB)/DSS Receive FIFO (BMDRX) 2–3. . . . . . . . . . . . . . . . . . . .

2.2.3 BDI Asynchronous Transmit FIFO (BATX) 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.4 BDI Asynchronous Receive FIFO (BARX) 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.5 BDI Isochronous Transmit FIFO (BITX) 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.6 BDI Isochronous Receive FIFO (BIRX) 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3 MPEG2 (DVB)/DSS Transmit and Receive Control 2–3. . . . . . . . . . . . . . . . . . . . . . . .

2.3.1 Local Time Register 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3.2 MPEG2 (DVB)/DSS Transmit and Receive Control/Aging 2–4. . . . . . . . . . . . .

2.4 Microprocessor/Microcontroller Interface 2–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5 Control FIFO 2–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5.1 Asynchronous Control Transmit FIFO (ACTX) 2–4. . . . . . . . . . . . . . . . . . . . . . .

2.5.2 Asynchronous Control Receive FIFO (ACRX) 2–4. . . . . . . . . . . . . . . . . . . . . . . .

2.5.3 Broadcast Write Receive FIFO (BWRX) 2–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6 Physical Layer Interface 2–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.7 Configuration Register (CFR) 2–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3 TSB12LV41A Data Formats 3–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1 Transmit Operation 3–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.1 Transmitting Asynchronous Control Packets 3–1. . . . . . . . . . . . . . . . . . . . . . . . .

3.1.2 Transmitting Asynchronous Data Packets 3–2. . . . . . . . . . . . . . . . . . . . . . . . . . .

General Asynchronous Transmit Notes 3–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.3 Transmitting Isochronous Packets 3–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.4 Notes on Byte Padding 3–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.5 MPEG2(DVB)/DSS Transmit 3–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2 Receive Operation 3–21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.1 Receiving Asynchronous Packets 3–21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.2 Receiving Isochronous Packets 3–26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.3 MPEG2(DVB)/DSS Receive 3–27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

iii

3.3 Timestamps and Aging 3–30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.1 Timestamp Calculation on Transmit 3–31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.2 Timestamp Determination on Receive 3–32. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4 Asynchronous Transmit (Host Bus to TSB12LV41A) 3–32. . . . . . . . . . . . . . . . . . . . . .

3.4.1 Quadlet Transmit 3–32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4.2 Block Transmit 3–33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4.3 Quadlet Receive 3–34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4.4 Block Receive 3–36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5 Isochronous Transmit and Receive (Host Bus to ’12LV41A) Data Formats 3–38. . .

3.5.1 Isochronous Transmit 3–38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.2 Isochronous Receive 3–38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6 Snoop 3–39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.7 Cyclemark 3–40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8 Phy Configuration 3–40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.9 Receive Self-ID Packet 3–41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4 External Interfaces 4–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1 Bulky Data Interface (BDIF) 4–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1.1 Introduction 4–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1.2 Modes of the Bulky Data Interface (BDIF) 4–5. . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2 Bulky Data Interface Timing 4–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.1 Unidirectional and Asynchronous Modes 4–11. . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.2 Bidirectional Modes 4–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3 Microprocessor Interface 4–19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.1 Microprocessors Supported 4–19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.2 Microprocessor Interface Control 4–22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.3 Handshake and Blind Access modes 4–23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.4 General Read Instructions 4–23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.5 General Write Instructions 4–24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.6 TMS320AV7100 Mode Timing Diagrams 4–24. . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.7 68000 Mode Timing Diagrams 4–30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.8 8051 Mode Timing Diagrams 4–34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.9 Blind Access Mode Specific Issues 4–38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.10 Endianness 4–39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.11 Use of Interrupts with MPEG2Lynx 4–41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4 TSB12LV41A to 1394 Phy Interface Specification 4–42. . . . . . . . . . . . . . . . . . . . . . . .

4.4.1 Introduction 4–42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.2 Assumptions 4–42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.3 Block Diagram 4–42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.4 Operational Overview 4–43. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.5 Request 4–44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.6 Status 4–46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.7 TSB12LV41A to Phy Bus Timing 4–48. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

iv

5 Detailed Operation and Programmers Reference 5–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1 TSB12LV41A Configuration Register 5–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2 Version Register (VERS @ Addr 0h) 5–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3 C Acknowledge Register (CACK @ Addr 4h) 5–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.4 B Acknowledge Register (BACK @ Addr 8h) 5–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.5 Link Control Register (LCTRL @ Addr Ch) 5–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6 Interrupt Register/Interrupt Mask Register (IR @ Addr 10h/14h) 5–11. . . . . . . . . . . .

5.7 Extended Interrupt Register/Extended Interrupt Mask Register

(EIR @ Addr 18h/1Ch) 5–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.8 Isochronous Receive Comparators Register 0 (IRPR0 @ Addr 20h) 5–16. . . . . . . .

5.9 Isochronous Receive Comparators Register 1 (IRPR1 @ Addr 24h) 5–17. . . . . . . .

5.10 Cycle Timer Register (CYCTIM @ Addr 28h) 5–18. . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.11 Bus Time Register (BUSTIM @ Addr 2Ch) 5–18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.12 Link Diagnostics Register (DIAG @ Addr 30h) 5–19. . . . . . . . . . . . . . . . . . . . . . . . . . .

5.13 Phy Access Register (PHYAR @ Addr 34h) 5–20. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.14 Expected Response (PHYSR @ Addr 38h) 5–21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.15 Reserved Register (RESERVED @ Addr 3ch–40h) 5–21. . . . . . . . . . . . . . . . . . . . . . .

5.16 Reserved Register (RESERVED @ Addr 3Ch) 5–21. . . . . . . . . . . . . . . . . . . . . . . . . . .

5.17 Reserved Register (RESERVED @ Addr 40h) 5–21. . . . . . . . . . . . . . . . . . . . . . . . . . .

5.18 Asynchronous Control Data Transmit FIFO Status (ACTFS @ Addr 44h) 5–22. . . .

5.19 Bus Reset Data Register (BRD @ Addr 48h) 5–23. . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.20 Bus Reset Error Register (BRERR @ Addr 4Ch) 5–23. . . . . . . . . . . . . . . . . . . . . . . . .

5.21 Asynchronous Control Data Receive FIFO Status (ACRXS @ Addr 50h) 5–24. . . .

5.22 Reserved Register (RESERVED @ Addr 54h) 5–25. . . . . . . . . . . . . . . . . . . . . . . . . . .

5.23 Reserved Register (RESERVED @ Addr 55h – 7Fh) 5–25. . . . . . . . . . . . . . . . . . . . .

5.24 Asynchronous Control Data Transmit FIFO First (ACTXF @ Addr 80h) 5–25. . . . . .

5.25 Asynchronous Control Data Transmit FIFO Continue (ACTXC @ Addr 84h) 5–25.

5.26 Asynchronous Control Data Transmit FIFO First & Update

(ACTXFU @ Addr 88h) 5–25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.27 Asynchronous Control Data Transmit FIFO Last & Send

(ACTXCU @ Addr 8ch) 5–25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.28 Reserved Register (RESERVED @ Addr 90h–BCh) 5–25. . . . . . . . . . . . . . . . . . . . . .

5.29 Asynchronous Control Data Receive FIFO (ACRX @ Addr C0h) 5–26. . . . . . . . . . .

5.30 Broadcast Write Receive FIFO (BWRX @ Addr 0C4h) 5–26. . . . . . . . . . . . . . . . . . . .

5.31 Reserved Register (RESERVED @ Addr C8h) 5–26. . . . . . . . . . . . . . . . . . . . . . . . . . .

5.32 Reserved Register (RESERVED @ Addr CCh) 5–26. . . . . . . . . . . . . . . . . . . . . . . . . .

5.33 Reserved Register (RESERVED @ Addr D0h) 5–26. . . . . . . . . . . . . . . . . . . . . . . . . . .

5.34 Reserved Register (RESERVED @ Addr D4h) 5–26. . . . . . . . . . . . . . . . . . . . . . . . . . .

5.35 Bulky Data Interface Control (BIF @ Addr D8h) 5–27. . . . . . . . . . . . . . . . . . . . . . . . . .

5.36 MPEG2 (DVB) Transmit Timestamp Offset Register (MXTO @ Addr DCh) 5–28

5.37 DSS Transmit Timestamp Offset Register (DXT0 @ Addr E0h) 5–28. . . . . . . . . . . . .

5.38 MPEG2 (DVB)/DSS Receive Timestamp Offset (MRTO @ Addr E4h) 5–29. . . . . . .

5.39 DSS Receive Timestamp Offset Register (DRT0 @ Addr E8h) 5–29. . . . . . . . . . . . .

5.40 Asynchronous/Isochronous Application Data Control Register

(AICR @ Addr ECh) 5–29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.41 MPEG2 (DVB)/DSS Formatter Control Register (MCR @ Addr F0h) 5–32. . . . . . . .

5.42 DSS Formatter Control Register (DCR @ Addr F4h) 5–34. . . . . . . . . . . . . . . . . . . . . .

v

5.43 Bulky Data FIFO Miscellaneous Control and Status

(BDFMISC @ Addr F8h) 5–36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.44 SRAM Address (SRAMA @ Addr FCh) 5–36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.45 SRAM Data (SRAMD @ Addr 100h) 5–37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.46 Bulky Asynchronous Size register (BASZ @ Addr 104h) 5–37. . . . . . . . . . . . . . . . . .

5.47 Bulky Asynchronous Avail register (BAAVAL @ Addr 108h) 5–37. . . . . . . . . . . . . . . .

5.48 Asynchronous Application Data Transmit FIFO First and Continue

(BATX @ Addr 10ch) 5–37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.49 Asynchronous Application Data Transmit FIFO Last & Send

(BATXLS @ Addr 110h) 5–38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.50 Asynchronous Application Data Receive FIFO (BARX @ Addr 114h) 5–38. . . . . . .

5.51 Asynchronous Application Data Receive Header Register 0

(ARH0 @ Addr 118h) 5–38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.52 Asynchronous Application Data Receive Header Register 1

(ARH1 @ Addr 11ch) 5–38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.53 Asynchronous Application Data Receive Header Register 2

(ARH2 @ Addr 120h) 5–38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.54 Asynchronous Application Data Receive Header Register 3

(ARH3 @ Addr 124h) 5–38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.55 Asynchronous Application Data Receive Trailer (ART @ Addr 128h) 5–39. . . . . . . .

5.56 Bulky Isochronous Size register (BISZ @ Addr 12Ch) 5–40. . . . . . . . . . . . . . . . . . . . .

5.57 Bulky Isochronous Avail register (BIAVAL @ Addr 130h) 5–40. . . . . . . . . . . . . . . . . .

5.58 Isochronous Transmit First & Continue (BITXFC @ Addr 134h) 5–40. . . . . . . . . . . .

5.59 Isochronous Transmit Last & Send (BITXLS @ Addr 138h) 5–40. . . . . . . . . . . . . . . .

5.60 Isochronous Receive FIFO (BIRX @ Addr 13ch) 5–40. . . . . . . . . . . . . . . . . . . . . . . . .

5.61 Isochronous Packet Received Header (IRH @ Addr 140h) 5–41. . . . . . . . . . . . . . . .

5.62 Isochronous Packet received Trailer (IRT @ Addr 144h) 5–41. . . . . . . . . . . . . . . . . .

5.63 Receive Packet Routing Control Register (RPRC @ Addr 148h) 5–42. . . . . . . . . . .

5.64 Bulky Asynchrounous Retry (BARTRY@ Addr 14Ch) 5–43. . . . . . . . . . . . . . . . . . . . .

5.65 Bulky MPEG2 (DVB) Size register (BMSZ @ Addr 150h) 5–43. . . . . . . . . . . . . . . . . .

5.66 Bulky MPEG2 (DVB) Avail register (BMAVAL @ Addr 154h) 5–44. . . . . . . . . . . . . . .

5.67 Bulky DSS Size register (BDSZ @ Addr 158h) 5–44. . . . . . . . . . . . . . . . . . . . . . . . . . .

5.68 Bulky DSS Avail register (BDAVAL @ Addr 15ch) 5–44. . . . . . . . . . . . . . . . . . . . . . . .

5.69 MPEG2 (DVB) Transmit FIFO first & continue (BMTXFC @ Addr 160h) 5–44. . . . .

5.70 MPEG2 (DVB) Transmit FIFO last & send (BMTXLS @ Addr 164h) 5–45. . . . . . . . .

5.71 MPEG2 (DVB) Formatted Packet Receive FIFO (BMRX @ Addr 168h) 5–45. . . . .

5.72 DSS Transmit FIFO first & continue (BDTXFC @ Addr 16ch) 5–45. . . . . . . . . . . . . .

5.73 DSS Transmit FIFO last & send (BDTXLS @ Addr 170h) 5–45. . . . . . . . . . . . . . . . . .

5.74 DSS Formatted Packet Receive FIFO (BDRX @ Addr 174h) 5–45. . . . . . . . . . . . . . .

5.75 MPEG2 (DVB) Receive Header (MRH @ Addr 178h) 5–46. . . . . . . . . . . . . . . . . . . . .

5.76 MPEG2 (DVB) CIP Receive Header 0 (MCIPR0 @ Addr 17ch) 5–46. . . . . . . . . . . . .

5.77 MPEG2 (DVB) CIP Receive Header 1 (MCIPR1 @ Addr 180h) 5–46. . . . . . . . . . . .

5.78 MPEG2 (DVB) Receive Trailer Register (MRT @ Addr 184h) 5–47. . . . . . . . . . . . . .

5.79 DSS Formatted Packet Received Header (DRH @ Addr 188h) 5–47. . . . . . . . . . . . .

5.80 DSS Formatter CIP 0 receive Register (DCIPR0 @ Addr 18ch) 5–47. . . . . . . . . . . .

5.81 DSS Formatter CIP 1 receive Register (DCIPR1 @ Addr 190h) 5–48. . . . . . . . . . . .

5.82 DSS Formatted Packet Received Trailer (DRT @ Addr 194h) 5–48. . . . . . . . . . . . . .

vi

5.83 DSS Receive Cell Header Register 0 (DRX0 @ Addr 198h) 5–48. . . . . . . . . . . . . . .

5.84 DSS Receive Cell Header Register 1 (DRX1 @ Addr 19Ch) 5–49. . . . . . . . . . . . . . .

5.85 DSS Receive Cell Header Register 2 (DRX2 @ Addr 1A0h) 5–49. . . . . . . . . . . . . . .

5.86 DSS Transmit Cell Header Register 0 (DTX0 @ Addr 1A4h) 5–49. . . . . . . . . . . . . . .

5.87 DSS Transmit Cell Header Register 1 (DTX1 @ Addr 1A8h) 5–49. . . . . . . . . . . . . . .

5.88 DSS Transmit Cell Header Register 2 (DTX2 @ Addr 1ACh) 5–50. . . . . . . . . . . . . . .

5.89 Asychronous Header 0 for Auto Tx (AHEAD 0) @ Addr 1B0h) 5–50. . . . . . . . . . . . .

5.90 Asychronous Header 1 for Auto Tx (AHEAD(1) @ Addr 1B4h) 5–50. . . . . . . . . . . . .

5.91 Asychronous Header 2 for Auto Tx (AHEAD(2) @ Addr 1B8h) 5–50. . . . . . . . . . . . .

5.92 Asynchrous Header 3 for Auto Tx (AHEAD(3) @ Addr 1BCh) 5–51. . . . . . . . . . . . . .

5.93 Isochronous Header for Auto Tx (IHEAD0 @ Addr 1C0h) 5–51. . . . . . . . . . . . . . . . . .

5.94 Packetizer Control (PKTCTL @ Addr 1C4h) 5–51. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.95 MPEG2 (DVB) Transmit Header Register (MXH @ Addr 1C8h) 5–53. . . . . . . . . . . .

5.96 MPEG2 (DVB) CIP Transmit Header 0 (MCIPX0 @ Addr 1CCh) 5–54. . . . . . . . . . .

5.97 MPEG2 (DVB) CIP Transmit Header 1 (MCIPX1 @ Addr 1D0h) 5–54. . . . . . . . . . . .

5.98 DSS Formatted Isochronous Data Transmit Header (DXH @ Addr 1D4h) 5–54. . .

5.99 DSS Formatter CIP 0 transmit Register (DCIPX0 @ Addr 1D8h) 5–54. . . . . . . . . . .

5.100 DSS Formatter CIP 1 transmit Register (DCIPX1 @ Addr 1DCh) 5–54. . . . . . . . . . .

5.101 MDAltCont (MDALT @ Addr 1E0h) 5–55. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.102 Microprocessor Control Register (MDCTL @ Addr 1E4) 5–55. . . . . . . . . . . . . . . . . . .

5.103 Reserved (RSVD @ Addr 1e8h) 5–55. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.104 Microprocessor Input / Output Control Register (IOCR @ Addr 1ECh) 5–56. . . . . . .

5.105 Blind Access Status Register (BASTAT @ Addr 1F0h) 5–57. . . . . . . . . . . . . . . . . . . .

5.106 Blind Access Holding Register (BAHR @ Addr 1F4h) 5–57. . . . . . . . . . . . . . . . . . . . .

5.107 Reserved Register (RESERVED @ Addr 1F8h) 5–57. . . . . . . . . . . . . . . . . . . . . . . . . .

5.108 Software Reset Register (SRES @ Addr 1FCh) 5–57. . . . . . . . . . . . . . . . . . . . . . . . . .

6 Electrical Characteristics 6–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.1 Absolute Maximum Ratings Over Free-Air Temperature Range 6–1. . . . . . . . . . . . .

6.2 Recommended Operating Conditions 6–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3 Electrical Characteristics Over Recommended Ranges of Supply Voltage

and Operating Free-Air Temperature 6–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7 MPEG2Lynx Power Consumption 7–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8 Mechanical Information 8–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A Receive Operation Examples A–1

A.1 Asynchronous Receive A–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.1.1 Receiving Asynchronous Data to the Bulky Asynchronous FIFO

(Bulky Data Interface) A–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.1.2 Receiving Asynchronous Data to the Asynchronous Control FIFO

A.2 Unformatted Isochronous Receive A–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.2.1 Receiving Isochronous Data to the Bulky Isochronous FIFO

(Bulky Data Interface) A–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.2.2 Receiving Isochronous Data to the Bulky Isochronous FIFO

(Microprocessor Interface) A–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.3 MPEG2/DSS Formatted Isochronous Receive A–3. . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.3.1 Receiving MPEG2 (DVB) Data to the Bulky MPEG2 FIFO

(Bulky Data Interface) A–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

vii

A.3.2 Receiving DSS Data to the Bulky DSS FIFO (Bulky Data Interface) A–4. . . . .

A.3.3 Receiving MPEG2 (DVB) Data to the Bulky MPEG2 (DVB) FIFO

(Microprocessor Interface) A–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.3.4 Receiving DSS Data to the Bulky DSS FIFO (Microprocessor Interface) A–6.

B Transmit Operation Examples B–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.1 Asynchronous Transmit B–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.1.1 Transmitting Asynchronous Data Packets (Bulky Data Interface) B–1. . . . . . .

B.1.2 Transmitting Asynchronous Control Packets B–1. . . . . . . . . . . . . . . . . . . . . . . . .

B.2 Unformatted Isochronous Transmit B–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.2.1 Transmitting Isochronous Data, Headers Auto Inserted (Bulky Data

Interface) B–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.2.2 Transmitting Fully-Formatted Isochronous Data (Microprocessor

Interface) B–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.3 MPEG2/DSS Formatted Isochronous Transmit B–4. . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.3.1 Transmitting MPEG2 (DVB) Data from Bulky Data Interface, Headers

Auto-Inserted B–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.3.2 Transmitting DSS Data from Bulky Data Interface, Headers Auto-InsertedB–5

B.3.3 Transmitting Fully-Formatted MPEG2 (DVB) Data with 1394 Isochronous

Header, CIP Headers, and Timestamps (Microprocessor Interface) B–6. . . . .

B.3.4 Transmitting Fully-Formatted DSS 130 Data with 1394 Isochronous and

CIP headers included. (Microprocessor Interface) B–7. . . . . . . . . . . . . . . . . . . .

C Isolation Considerations for TSB12LV41A C–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

viii

List of Illustrations

Figure Title Page

2–1 Functional Block Diagram 2–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–1 Transmit from the Asynchronous Control Transmit FIFO (ACTX) 3–1. . . . . . . . . . . . . .

3–2 Transmit Asynchronous/Isochronous Data from BATX by the Bulky Data Interface

with Auto-Packetization 3–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–3 Transmit Asynchronous/Isochronous Data from BATX by the MP/MC Interface with

Auto-Packetization 3–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–4 Transmit Asynchronous/Isochronous Data from BATX by the Bulky Data Interface,

No Auto-Packetization 3–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–5 Transmit Asynchronous/Isochronous Data from BATX by the MP/MC Interface,

No Auto-Packetization 3–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–6 MPEG2 (DVB)/DSS Data from Bulky Data Interface, All Headers and Timestamps

Automatically Inserted 3–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–7 MPEG2 (DVB)/DSS Data from Bulky Data Interface All Headers Automatically

Inserted, Timestamp Supplied by Application 3–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–8 MPEG2 (DVB)/DSS Data from Bulky Data Interface, All Headers and Timestamps

Supplied by Application 3–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–9 MPEG2 (DVB)/DSS Data from Microprocessor, All Headers and Timestamps

Automatically Inserted 3–1 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–10 MPEG2 (DVB)/DSS Data from Microprocessor All Headers Automatically Inserted

Timestamp Supplied by Application. 3–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–11 MPEG2 (DVB)/DSS Data from Microprocessor, All Headers and Timestamps

Supplied by Application 3–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–12 Simple MPEG-2 Transmission Over 1394 3–16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–13 Simple DSS Transmission Over 1394 3–20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–14 DSS130 Packets 3–21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–15 Receive Asynchronous/Isochronous Data to Bulky Data Interface 3–24. . . . . . . . . . . .

3–16 Receive Asynchronous/Isochronous Data to Microprocessor Interface 3–25. . . . . . . .

3–17 Receive All Data, Including Headers and Trailer, to Bulky Data Interface 3–28. . . . . .

3–18 Receive MPEG2(DVB)/DSS Cell Data Only to Bulky Data Interface 3–28. . . . . . . . . . .

3–19 Receive All Data, Including Headers and Trailer, to Microprocessor Interface 3–29. .

3–20 Receive MPEG2(DVB)/DSS Cell Data Only to Microprocessor Interface 3–30. . . . . . .

3–21 Determination of Transmit Timestamp 3–31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–22 Quadlet-Transmit Format 3–32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–23 Block-Transmit Format 3–33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–24 Quadlet-Receive Format for Control FIFO 3–34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–25 Quadlet-Receive Format for Bulky Data FIFO 3–35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–26 Block-Receive Format for Control FIFO 3–36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–27 Block-Receive Format for Bulky Data FIFO 3–36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–28 Isochronous-Transmit Format 3–38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–29 Isochronous-Receive Format for Bulky Data FIFO 3–38. . . . . . . . . . . . . . . . . . . . . . . . . .

ix

List of Illustrations (continued)

Figure Title Page

3–30 Snoop Format 3–39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–31 Cyclemark Format 3–40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–32 Phy Configuration Format 3–40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–33 Receive Self-ID Format for Broadcast Write Receive FIFO 3–41. . . . . . . . . . . . . . . . . .

3–34 Receive Self-ID Format for Bulky Asynchronous Receive FIFO 3–41. . . . . . . . . . . . . .

3–35 Phy Self-ID Packet #0 Format 3–42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–36 Phy Self-ID Packet #1, Packet #2, and Packet #3 Format 3–43. . . . . . . . . . . . . . . . . . .

4–1 TSB12LV41A System Application Diagram 4–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–2 Bulky Data Interface 4–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–3 BDIF Control Register 4–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–4 Bulky Data Interface Mode A Typical Application 4–7. . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–5 Bulky Data Interface Mode B Typical Application 4–8. . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–6 Bulky Data Interface Mode C Typical Application 4–9. . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–7 Bulky Data Interface Mode D Typical Application 4–10. . . . . . . . . . . . . . . . . . . . . . . . . . .

4–8 Functional Timing for Write Operations in the Unidirectional Modes 4–11. . . . . . . . . . .

4–9 Critical Timing for Write Operations in Unidirectional Mode 4–12. . . . . . . . . . . . . . . . . .

4–10 Functional Timing for Write Operations in the Asynchronous Mode 4–12. . . . . . . . . . .

4–11 Functional Timing for Read Operations in Unidirectional Mode 4–13. . . . . . . . . . . . . . .

4–12 Read from Bulky Interface Unidirectional Mode 4–13. . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–13 Functional Timing for Read Operations in Asynchronous Mode 4–14. . . . . . . . . . . . . . .

4–14 Functional Timing for Write Operations in Bidirectional Mode 4–15. . . . . . . . . . . . . . . .

4–15 Critical Timing for Write Operations in Bidirectional Mode 4–15. . . . . . . . . . . . . . . . . . . .

4–16 Functional Timing for Read Operations in Bidirectional Mode 4–16. . . . . . . . . . . . . . . .

4–17 Critical Timing for Read Operations in Bidirectional Mode 4–17. . . . . . . . . . . . . . . . . . .

4–18 Functional Timing for Read/Write Interleave Operations in Bidirectional Mode 4–18. .

4–19 MPEG2Lynx Connections for 68000 Microcontroller 4–20. . . . . . . . . . . . . . . . . . . . . . . .

4–20 MPEG2Lynx Connections for 8051 Microcontroller 4–21. . . . . . . . . . . . . . . . . . . . . . . . .

4–21 MPEG2Lynx Connections for TMS320AV7100 ARM Processor 4–21. . . . . . . . . . . . . .

4–22 TSB12LV41A IOCR Register 4–22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–23 TMS320AV7100 ARM Read/Write Critial Timing 4–26. . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–24 TMS320AV7100 Handshake Mode Read Timing 4–27. . . . . . . . . . . . . . . . . . . . . . . . . . .

4–25 TMS320AV7100 Handshake Mode Write Timing 4–27. . . . . . . . . . . . . . . . . . . . . . . . . . .

4–26 TMS320AV7100 ARM Blind Access Mode Read Timing 4–28. . . . . . . . . . . . . . . . . . . . .

4–27 TMS320AV7100 ARM Blind Access Mode W rite Timing 4–28. . . . . . . . . . . . . . . . . . . . .

4–28 Motorola 68000 Read Critical Timing 4–31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–29 Motorola 68000 Write Critical Timing 4–32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–30 Motorola 68000 Read Timing 4–33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–31 Motorola 68000 Write Timing 4–33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–32 Intel 8051 Read Critial Timing 4–35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–33 Intel 8051 Write Critial Timing 4–36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–34 Intel 8051 Read Timing (Blind Access Read) 4–37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–35 Intel 8051 Write Timing (Blind Access Write) 4–37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–36 Big Endian Illustration chart 4–39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–37 Little Endian Illustration chart 4–39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

x

List of Illustrations (continued)

Figure Title Page

4–38 Little Endian Data Invariant System Design Illustration Chart 4–40. . . . . . . . . . . . . . . . .

4–39 Little Endian Address Invariant System Design Illustration Chart 4–41. . . . . . . . . . . . .

4–40 Interrupt Hierarchy 4–42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–41 Functional Block Diagram of the TSB12LV41A to Phy Layer 4–43. . . . . . . . . . . . . . . . .

4–42 LREQ Timing 4–48. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–43 Status-Transfer Timing 4–48. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–44 Transmit Timing 4–49. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–45 Receiver Timing 4–49. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–1 Configuration Register (CFR) Map 5–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xi

List of Tables

Table Title Page

1–1 Terminal Functions 1–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–1 Initial values for the CIP headers (to be set by SW)† 3–14. . . . . . . . . . . . . . . . . . . . . . . .

3–2 DBC Incremental Numbers, DBS Value and Length Values for

MPEG-2 Packets 3–15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–3 MPEG2 on 1394 Bandwidth 3–15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–4 Initial Values for the DCIP Headers (to be Set By SW) 3–18. . . . . . . . . . . . . . . . . . . . . .

3–5 DBC Incremental Numbers, DBS Value and Length Values for DSS Packets 3–18. . .

3–6 DSS on 1394 Bandwidth 3–18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–7 Quadlet-Transmit Format Functions 3–33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–8 Block-Transmit Format Functions 3–34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–9 Quadlet-Receive Format Functions 3–35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–10 Block-Receive Format Functions 3–37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–11 Isochronous-Transmit Functions 3–38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–12 Isochronous-Receive Functions 3–39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–13 Snoop Functions 3–39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–14 Cyclemark Functions 3–40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–15 Phy Configuration Functions 3–40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–16 Receive Self-ID Function 3–41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–17 Broadcast Write Receive FIFO Contents With Three Nodes on a Bus 3–42. . . . . . . . .

3–18 Bulky Data Asynchronous Receive FIFO (BARX FIFO) Contents 3–42. . . . . . . . . . . . .

3–19 Phy Self-ID Functions 3–43. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–1 BDIO Bidirectional Port Signals 4–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–2 BDO Unidirectional Port Signals 4–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–3 MODES of the BDIF 4–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–4 MCSEL Settings for Various Microprocessors 4–19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–5 TSB12LV41A MP/MC Interface Pin Function Matrix 4–19. . . . . . . . . . . . . . . . . . . . . . . . .

4–6 TSB12LV41A IOCR Bit/Function Correlation Table and Power-Up

Default Setting 4–22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–7 TMS320AV7100 Critical Timing Characteristics 4–25. . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–8 Motorola 68000 Critical Timing Characteristics 4–30. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–9 Intel 8051 Critical Timing Characteristics 4–34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–10 Phy Interface Control of Bus Functions 4–43. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–11 TSB12LV41A Control of Bus Functions 4–43. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–12 Request Functions 4–44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–13 Bus-Request Functions (Length of Stream: 7 Bits) 4–44. . . . . . . . . . . . . . . . . . . . . . . . . .

4–14 Read-Register Request Functions (Length of Stream: 9 Bits) 4–44. . . . . . . . . . . . . . . .

4–15 Write-Register Request (Length of Stream: 17 Bits) 4–44. . . . . . . . . . . . . . . . . . . . . . . . .

4–16 TSB12LV41A Request Functions 4–45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–17 Request-Speed Functions 4–45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–18 Status-Request Functions (Length of Stream: 16 Bits) 4–46. . . . . . . . . . . . . . . . . . . . . .

xii

List of Tables (continued)

Table Title Page

4–19 Speed Code for Receive 4–47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–1 Cycle Timer Program Function 5–18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–2 Cycle Time Register 5–18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–1 Receiving Asynchronous Data to the Bulky Asynchronous FIFO

(Bulky Data Interface) A–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–2 Receiving Asynchronous Data to the Asynchronous Control FIFO A–2. . . . . . . . . . . . .

A–3 Receiving Isochronous Data to the Bulky Isochronous FIFO

(Bulky Data Interface) A–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–4 Receiving Isochronous Data to the Bulky Isochronous FIFO

(Microprocessor Interface) A–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–5 Receiving MPEG2 (DVB) Data to the Bulky MPEG2 FIFO (Bulky Data Interface) A–4

A–6 Receiving DSS Data to the Bulky DSS FIFO (Bulky Data Interface) A–4. . . . . . . . . . . .

A–7 Receiving MPEG2 (DVB) Data to the Bulky MPEG2 (DVB) FIFO

(Microprocessor Interface) A–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–8 Receiving DSS Data to the Bulky DSS FIFO (Microprocessor Interface) A–6. . . . . . . .

B–1 Transmitting Asynchronous Data Packets (Bulky Data Interface) B–1. . . . . . . . . . . . . .

B–2 Transmitting Asynchronous Control Packets B–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B–3 Transmitting Isochronous Data, Headers Auto-Inserted (Bulky Data Interface) B–3. .

B–4 Transmitting Fully-Formatted Isochronous Data (Microprocessor Interface) B–3. . . . .

B–5 Transmitting MPEG2 (DVB) Data from Bulky Data Interface,

Headers Auto-Inserted B–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B–6 Transmitting DSS Data from Bulky Data Interface, Headers Auto-Inserted B–5. . . . . .

B–7 Transmitting Fully-Formatted MPEG2 (DVB) Data B–6. . . . . . . . . . . . . . . . . . . . . . . . . . .

B–8 Transmitting Fully-Formatted DSS 130 Data B–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xiii

xiv

1 Introduction

1.1 Description

The T exas Instruments TSB12L V41A link-layer controller (LLC) (also called MPEG2Lynx) complies with the

IEEE 1394-1995 (from here on referred to as 1394) specification for high-performance serial bus, transmits

and receives correctly-formatted 1394 packets, detects lost cycle-start packets, and generates and inspects

the 32-bit cyclic redundancy check (CRC). The TSB12LV41A is also capable of performing the functions

of cycle master (CM), isochronous resource manager (IRM), and bus manager (BM). Support is provided

for the IEC61883 standard for transmitting MPEG2 compressed video on 1394, with automatic generation

of the common isochronous packet headers and timestamping as required by the IEC 61883 standard.

The TSB12L V41A provides a 1394 interface for high-performance audio, video, and data applications at up

to 200 Mbits/s. It is suitable for set-top boxes, multimedia tape, disk drives, and other consumer electronic

devices requiring MPEG-2 formatted isochronous data transfer according to the IEC61883 specification.

The TSB12LV41A also supports non-MPEG-2/DSS isochronous and asynchronous data transfer with an

auto-packetization feature.

The TSB12L V41A interfaces directly to several microprocessors and microcontrollers, including embedded

ARM processor, Intel 8051 and the Motorola 68000. The microprocessor interface supports both 8-bit and

16-bit data busses. It can also automatically transform addresses to interface to either big endian or little

endian type processors.

The bulky data interface (BDIF) is a 16-bit wide I/O port that enables both transmit and receive of DVB/DSS,

isochronous, and asynchronous data. This port is full-duplex, meaning it is capable of transmitting and

receiving 1394 packets simultaneously . A separate 8K-byte FIFO, accessible via the bulky data interface,

provides logically independent FIFOs for transmit and receive of isochronous, asynchronous, and MPEG2

compressed DVB/DSS data. The 8K-byte FIFO or bulky data FIFO can perform asynchronous packet

transmit retry up to 256 times with intervals up to 256 × 125 µs. The TSB12LV41A supports full-width

time-stamped offsets for MPEG2 compressed DVB/DSS transmit and receive, and also performs age

filtering functions. A 256-byte FIFO is used to transmit and receive asynchronous control packets.

1–1

1.2 Features

The TSB12L V41A supports the following features:

• Provisions of IEEE 1394-1995 Standard for High-Performance Serial Bus

• Interoperable with FireWire implementation of the 1394 standard

• Interfaces directly to Texas Instruments TSB11LV01 and TSB21LV03A physical layer (Phy)

devices (100/200Mbits/s)

• Multimode 8-/16-bit microcontroller/microprocessor interface supports many processors

• Interrupt driven to minimize host polling

• 8K-byte FIFO supports fully bidirectional MPEG2/DSS, asynchronous, and isochronous modes

for transmit and receive

• 64 quadlet (256-Byte) control FIFO accessed through microcontroller interface supports

command/status operations

• Bus functions and automatic 1394 Self-ID verification

• Single 3.3-V supply operation with 5-V tolerance using 5-V bias terminals

• High-performance 100-Pin PZ (S-PQFP-G100) package

1.3 Related Documents

• IEEE STD IEEE 1394-1995 High-Performance Serial Bus

• IEC 61883 Digital Interface for Consumer Electronic Audio/Video Equipment

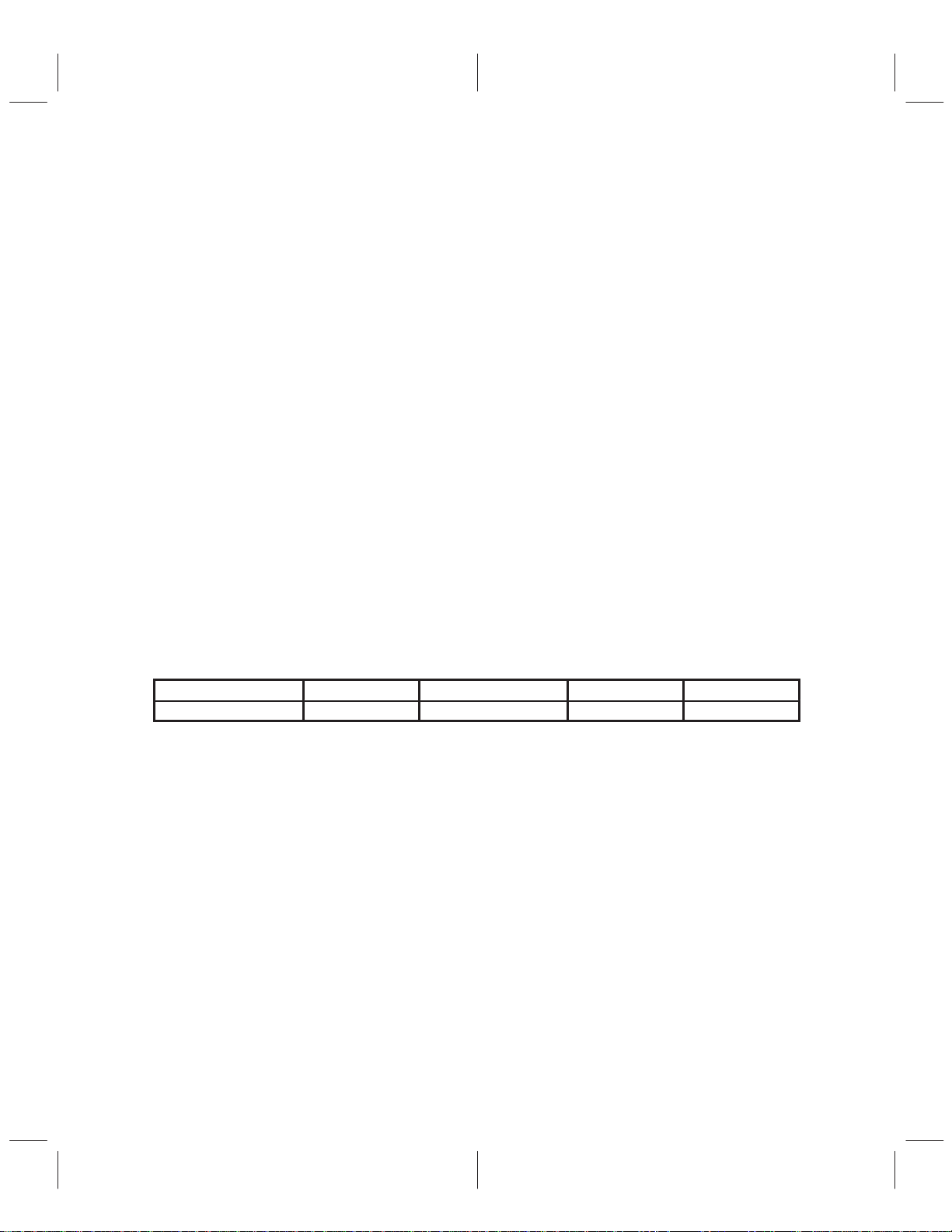

1.4 Ordering Information

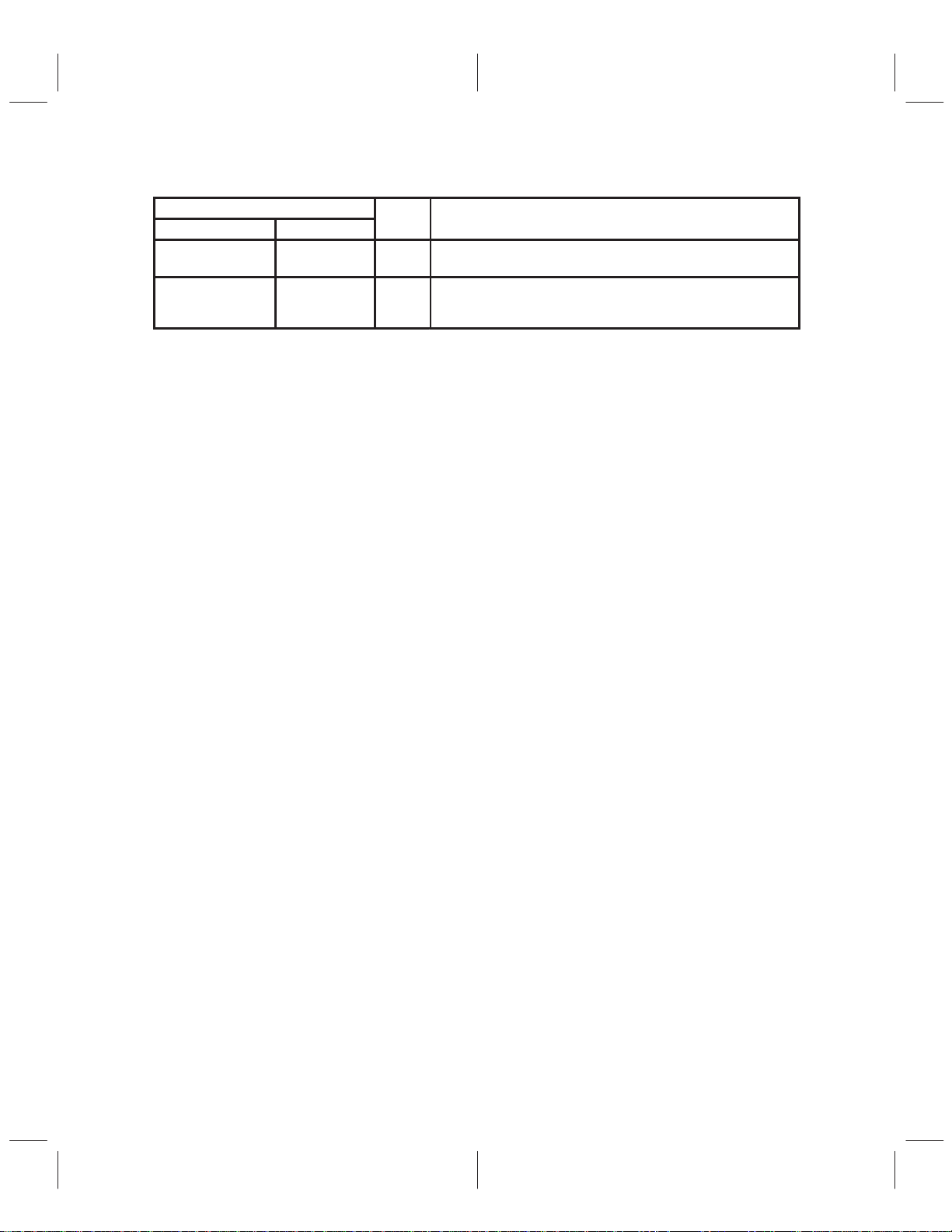

ORDERING NUMBER NAME VOLTAGE DATA RATE PACKAGE

TSB12LV41APZ MPEG2LYNX 3.3 V, 5-V Tolerant I/Os Up to 200 Mbits/s 100-Pin PQFP

FireWire is a trademark of Apple Computer, Incorporated.

1–2

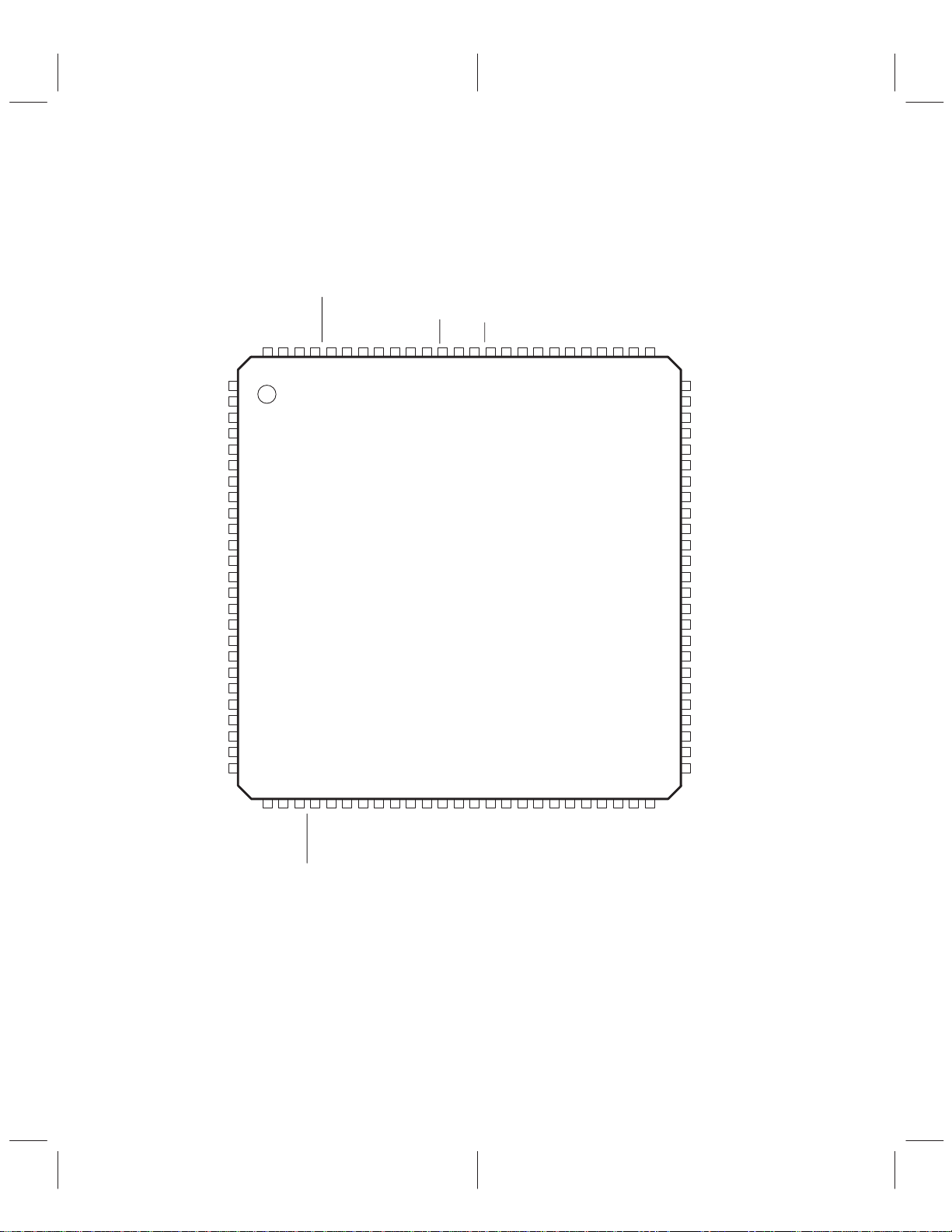

1.5 Terminal Assignments

BDIF2

BDIF1

BDIF0

RESET

CYCLEIN/SE

GND

95

96

97

98

99

100

CC

TDI

CC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

BDI/O0

BDI/O1

BDI/O2

BDI/O3

V

BDI/O4

BDI/O5

BDI/O6

BDI/O7

GND

CNTNDR

TMS

TCK

V

+5V

CC

BDOCLK

V

TDO

BDO0

BDO1

BDO2

BDO3

GND

BDO4

BDO5

CC

SCKEN

BDIEN

V

92

93

94

34

33

32

PZ PACKAGE

(TOP VIEW)

+5V

CC

INT

BDICLK

91

35

RDY

V

88

89

90

TSB12LV41A

38

37

36

GND

86

87

40

39

CS

MCSEL1

85

41

MCSEL0

MCCTL1

MCCTL0

82

83

84

44

43

42

CC

V

81

45

DATA0

80

46

DATA8

79

47

DATA1

DATA9

DATA2

76

77

78

48

49

50

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

DATA10

DATA3

DATA11

GND

DATA4

DATA12

DATA5

DATA13

V

CC

BCLK

+5V

V

CC

DATA6

DATA14

DATA7

DATA15

GND

ADR8

ADR7

V

CC

ADR6

ADR5

ADR4

ADR3

ADR2

ADR1

BDO6

BDO7

LPS (STAT0)

D3

D1

D0

GND

D2

CTL1

CTL0

+5V

CC

V

CC

V

SCLK

LREQ

BDOF0

GND

BDOF2

BDOF1

ADR0

BDOEN

1–3

CC

V

TRST

ISOLAT

BDIBUSY (STAT3)

BDOAVAIL (STAT2)

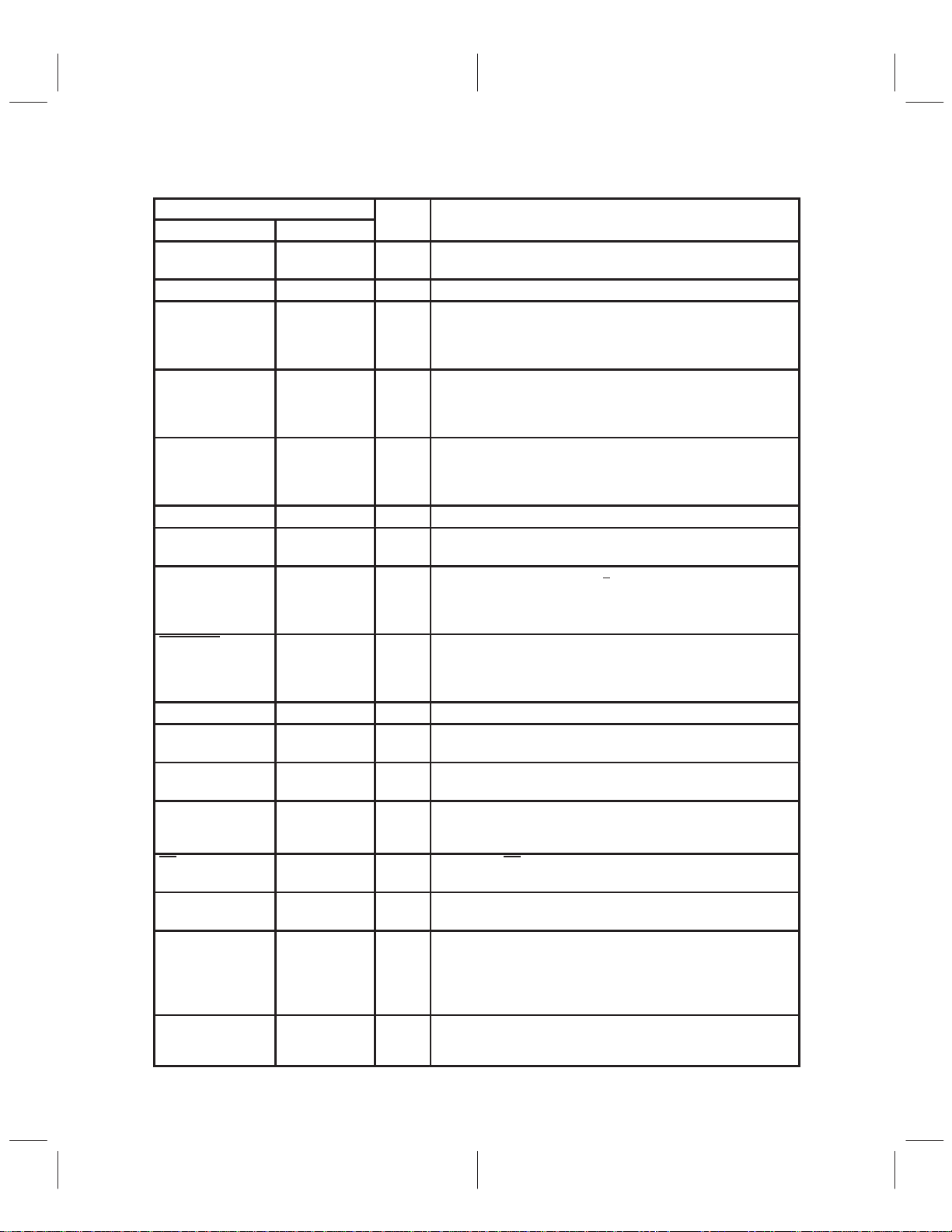

T able 1–1. Terminal Functions

I/O

DESCRIPTION

TERMINAL

NAME NO.

ADR0 – ADR8 50,51,52,53,54,

55,56,58,59

BCLK 66 I Host bus clock

BDIF2 – BDIF0 100,99,98 I/O Indicator lines for BDIF. BDIF2 – BDIF0 are used to select the type

BDI/O7 – BDI/O0 9,8,7,6,4,3,2,1 I/O Bidirectional bulky data I/O port . BDI/O7 – BDI/O0 are data lines

BDIBUSY (STAT3) 31 O Bulky data interface busy status. When high, BDIBUSY indicates

BDICLK 91 I Bulky data clock

BDIEN 93 I BDI bus enable. When low, BDIEN causes accesses to BDI-bus

BDO7 – BDO0 27,26,25,24,22,

21,20,19

BDOAVAIL(STAT2) 30 O Bulky data output available/status output 2. BDOAVAIL indicates

BDOCLK 16 I Bulky data output clock

BDOF2 – BDOF0 47,46,45 O Indicator lines BDO. BDOF2 – BDOF0 are used to select the

BDOEN 49 I BDO bus enable. When BDOEN is asserted low, accesses to

CNTNDR 11 I/O Bus manager contender. CNTNDR indicates to the LLC when

CS 86 I Chip select. CS must be asserted low when the device is to be

CTL0,CTL1 40,39 I/O Control 0 and control 1 of the Phy-link control bus. CTL0 and

CYCLEIN/SE 95 I Cycle in. CYCLEIN is an optional external 8-kHz clock used as

D0 – D3 38,37,36,35 I/O Phy-link data. D0 – D3 is data input from the Phy-link data bus.

I Microprocessor interface address lines. ADR0 is the most

significant bit.

of data to be written to or read from the BDIF . These terminals can

also be used for an application-specific purpose depending on the

bulky data interface mode selected.

for high-speed I/O bus for audio/data/video applications. BDIO7

is the most significant bit and BDIO0 is the least significant bit on

this bus.

that the FIFO being written to from the BDIF is full. This terminal

can also be used to MUX out internal signals for debug purposes

(STAT3).

to be ignored.

O Output Bulky data port. BDO7 – BDO0 are data lines for the

high-speed output bus and are used in audio/data/video

applications. BDO7 is the most significant bit and BDO0 is the

least significant bit on this bus.

that a complete packet (or packets) is available in the bulky data

receive FIFO. This terminal can also be used to MUX out internal

signals for debug purposes (STAT2).

type of data to be read from the BDO.

BDO bus are ignored.

the local node is a contender for IRM. This signal can also be

driven by the LLC. The default state of this signal is input.

selected for reads and writes.

CTL1 control the four operations that can occur in this interface.

the cycle clock. It should only be used when attached to the

cycle master node. CYCLEIN is enabled by the cycle source bit

and should be tied high when not used. This terminal is used for

testing purposes only (SE).

Data is expected on D0 – D1 for 100 Mbits/s and D0 – D3 for

200 Mbits/s.

1–4

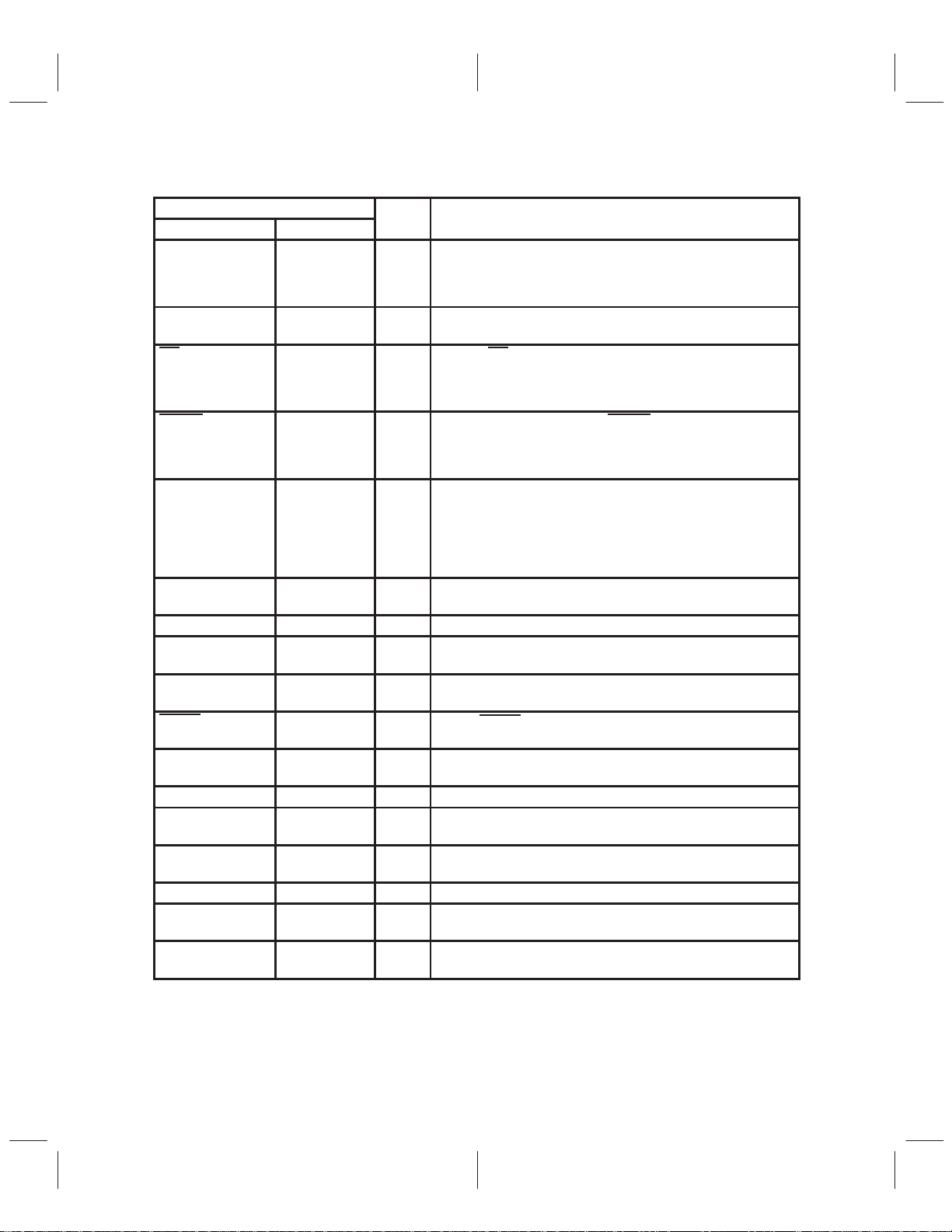

T able 1–1. Terminal Functions (Continued)

I/O

DESCRIPTION

TERMINAL

NAME NO.

DATA0 – DATA15 80,78,76,74,71,

69,64,62,79,77,

75,73,70,68,63,

61

GND 10,23,34,48,60,

72,87,97

INT 89 O Interrupt. INT signals the host that an interrupt has occurred.

ISOLAT 29 I/O Isolation mode/status output 1. ISOLAT is sampled during a

LPS (STAT0) 28 O Link power status/status output 0. This terminal is used to drive

LREQ 44 O Link request. LREQ is an output that makes bus request and

MCCTL0, MCCTL1 82,83 I Control lines for bus access function depend on MP/MC-type.

MCSEL0, MCSEL1 84,85 I Select lines for MP/MC-type used. Has impact on function

RDY 88 O Ready line. When asserted high, RDY indicates the end of an

RESET 96 I

SCKEN 94 I Scan clock enable. This signal is for test purposes only. This

SCLK 42 I System clock. SCLK is a 49.152-MHz clock from the Phy.

TCK 14 I JTAG clock. Used for test purposes only . During normal

TDI 13 I JTAG data in. Used for test purposes only . During normal

TDO 18 O JTAG data out. Used for test purposes only.

TRST 33 I JTAG mode reset. Used for test purposes only. During normal

TMS 12 I JTAG mode select. TMS is used for JTAG. During normal

I/O Microprocessor interface data bus. DATA0 is the most significant

bit. Some of these terminals may have different functions

depending on the microprocessor mode selected.

Ground reference

This line can be active low or active high dependent on the

INTPOL bit in the IOCR register. It is in a high-impedance state

when no interrupt has occurred.

hardware reset to determine if isolation is present. When this

input signal is high, the internal bus holders on the Phy-link

interface are disabled.

the LPS input of the Phy to indicate when the LLC is powered up

and active. This output toggles at 1/32 of either the BCLK rate or

the SYSCLK rate, depending on the type of microprocessor

used. This terminal can also be programmed to MUX out internal

signals for debug purposes (STAT0).

accesses to the Phy.

MCTRL,ADR, RDY, and DATA terminals.

microprocessor access.

Reset. RESET is the asynchronous power on reset to the

TSB12L V41A and is active low.

signal should be tied low during normal operation.

operation this terminal should be pulled up to VCC.

operation this terminal should be pulled down to ground.

operation this terminal should be pulled down to ground.

operation this terminal should be pulled up to VCC.

1–5

T able 1–1. Terminal Functions (Continued)

I/O

DESCRIPTION

TERMINAL

NAME NO.

V

CC

VCC+5V 15,41,65,90 5 V ± 5% power supplies for 5-V tolerant I/O terminals. These

5,17,32,43,57,

67,81,92

3.3 V (3.0 V – 3.6 V) power supplies

terminals can be tied to 3.3 V if no 5-V devices interface to the

TSB12LV41A.

1–6

2 Architecture

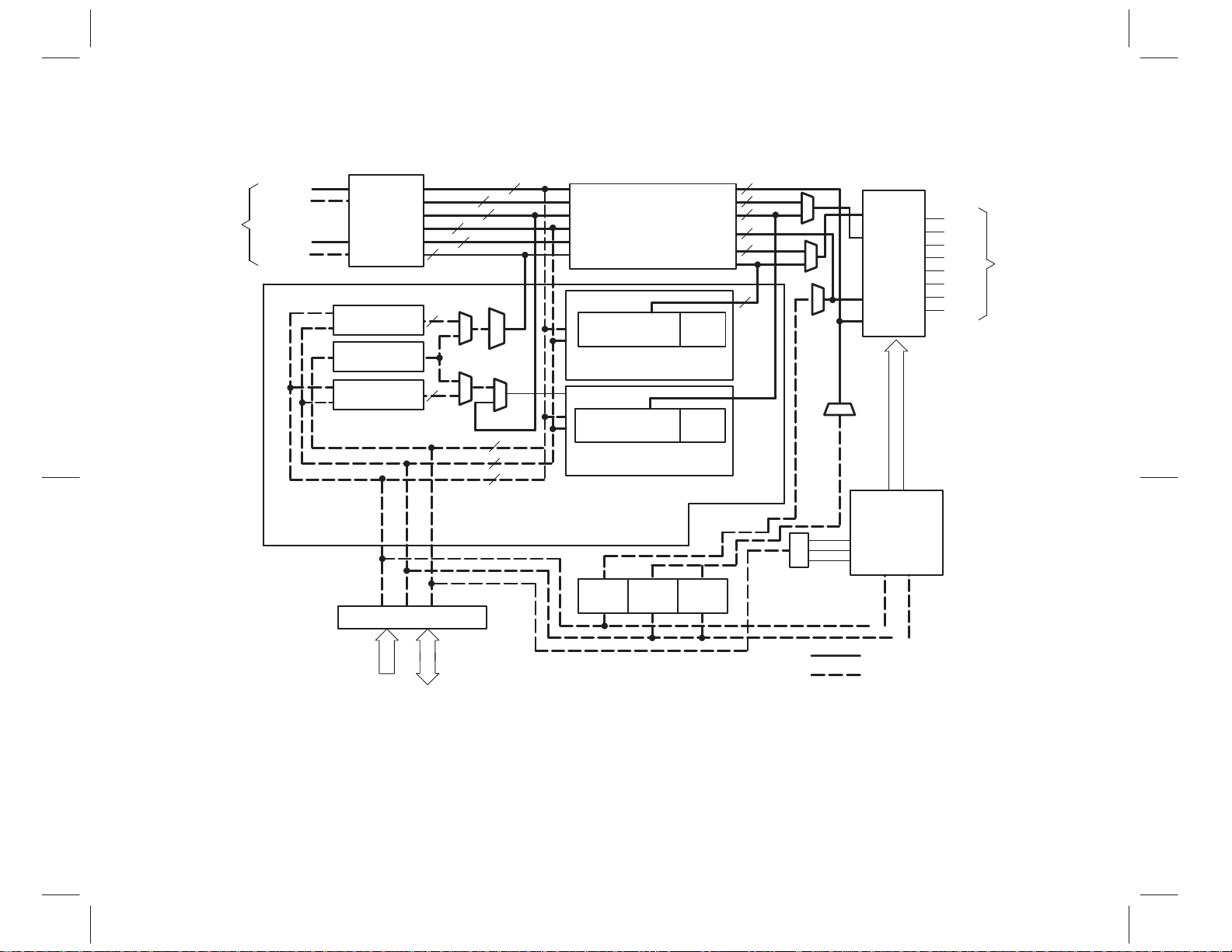

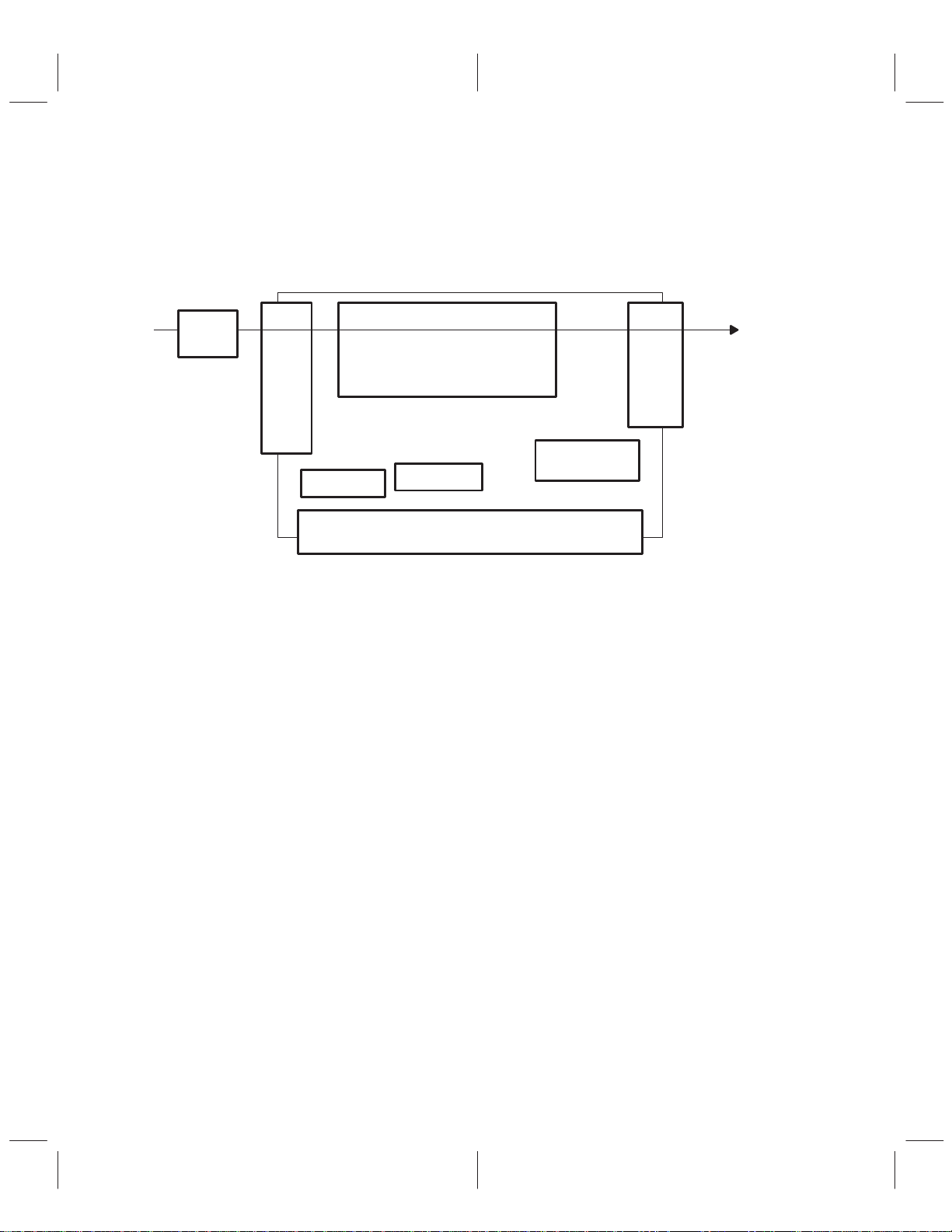

The following sections give an overview of the TSB12L V41A. Figure 2–1 shows a functional block diagram

of the TSB12L V41A.

2–1

2–2

AVD-Layer

BDIN

CONTROL

BDOUT

CONTROL

Bulky Data

Interface

MPEG2/DSS

Time Offset Tx

Loc. Time Reg.

MPEG2/DSS

RX Time Offset

Microprocessor Interface

32

32

32

32

32

32

25

+

+

25

=

32

32

32

MPEG2/DSS Transmit and Receive Control

Bulky Data FIFO

6 Queue Virtual Buffer

MX

Control

MPEG2/DSS Transmit

Control/Aging

MR

Control

MPEG2/DSS Receive

Control/Aging

ACX

FIFO

ACR

FIFO

Aging

Aging

BWR

FIFO

32

32

32

32

32

32

IX

IR

Physical

Layer

Interface

AX

AR

Configuration

Register

(CFRs)

SCLK

CTL0

CTL1

LREQ

LD0

LD1

LD2

LD3

PHY -Chip

8A’ s

8/16D’s

Control Processor

Payload Data Busses

Control Data Busses

Figure 2–1. Functional Block Diagram

2.1 Bulky Data Interface

The bulky data interface (BDI) enables the TSB12L V41A to provide sustained data rates up to 160 Mbits/s.

The bulky data FIFO supports MPEG2 compressed DVB/DSS, asynchronous, and isochronous packets for

receive and transmit.

2.2 Bulky Data FIFO

The bulky data FIFO is where transmit and receive data is buffered via the bulky data interface (BDI). The

bulky data FIFO is partitioned into six logical FIFOs. Each logical FIFO size is programmable on four quadlet

boundaries. These six FIFOs are called:

• BDI MPEG2 (DVB)/DSS Transmit (BMDTX)

• BDI MPEG2 (DVB)/DSS Receive (BMDRX)

• BDI Asynchronous Transmit (BATX)

• BDI Asynchronous Receive (BARX)

• BDI Isochronous Transmit (BITX)

• BDI Isochronous Receive (BIRX)

The following sections give functional descriptions of these logical FIFOs.

2.2.1 BDI MPEG2 (DVB)/DSS Transmit FIFO (BMDTX)

The BMDTX FIFO is used to transmit either MPEG2 (DVB) or DSS data. Data is typically written to this FIFO

from the BDI or microcontroller in quadlets (four bytes). See the Bulky Data Interface section (Section 4)

for more detail on using this FIFO to transmit MPEG2 (DVB)/DSS data.

2.2.2 BDI MPEG2 (DVB)/DSS Receive FIFO (BMDRX)

The BMDRX FIFO is typically used to store MPEG2 (DVB)/DSS data received from the link-layer core to

be forwarded to a high-speed application via the BDI. Data can be written to this FIFO by either the link layer

core or the microcontroller. Note that only isochronous port 0 can access this FIFO. See the Bulky Data

Interface section (Section 4) for more details.

2.2.3 BDI Asynchronous Transmit FIFO (BATX)

The BATX FIFO is typically used to transmit asynchronous data packets from high-speed applications. Data

can be loaded into this FIFO with the BDI or the microcontroller.

2.2.4 BDI Asynchronous Receive FIFO (BARX)

The BARX FIFO is typically used to store received asynchronous data packets to be forwarded to a

high-speed application via the BDI. Data is provided to the BDI or the microcontroller interface. This FIFO

is also the default location for storing incoming Self-ID packets.

2.2.5 BDI Isochronous Transmit FIFO (BITX)

The BITX FIFO is typically used to transmit isochronous data packets from high-speed applications. Data

can be loaded into this FIFO with the BDI or the microcontroller.

2.2.6 BDI Isochronous Receive FIFO (BIRX)

The BIRX FIFO is typically used for receiving isochronous data and forwarding it to a high-speed application.

Data is provided to the BDI or microcontroller interface. Isochronous Ports 1 through 7 have access to this

FIFO. Each port can be programmed to filter incoming packets according to the Isochronous channel and/or

the isochronous header tag value.

2.3 MPEG2 (DVB)/DSS Transmit and Receive Control

The following sections give information on MPEG2 (DVB) and DSS transmit and receive control.

2.3.1 Local Time Register

This register is typically called the cycle timer. It contains the synchronized 1394 cycle timer as specified

by the IEEE 1394-1995 standard. The local time register is used to timestamp packets, which determines

2–3

when to release outgoing packets to either the packetizer for transmission on 1394 or release incoming

packets to the BDI. Section 5.10 describes the cycle timer register in more detail.

2.3.2 MPEG2 (DVB)/DSS Transmit and Receive Control/Aging

This circuitry controls automatic insertion of the common isochronous packet (CIP) header information as

defined by the IEC61883 standard. Timestamping is also used for both transmitted and received MPEG2

(DVB)/DSS packets to determine when a packet gets released from the FIFO. The aging algorithm is used

to invalidate packets based on the timestamp encapsulated in the MPEG2 (DVB)/DSS header (see

Section 3.3).

2.4 Microprocessor/Microcontroller Interface

The microprocessor/microcontroller (MP/MC) interface used as the host controller port, is designed to work

with several standard MP/MCs including Motorola 68000, Intel 8051, and embedded ARM processors. This

interface supports both 8-bit and 16-bit wide data busses as well as both little endian and big endian

microprocessors. This interface has two basic modes of operation, handshake mode and blind access

mode. See the Microprocessor section (Section 4) for more details.

2.5 Control FIFO

The control FIFO is partitioned into three logical FIFOs. The size of each of these logical FIFOs is

programmable on quadlet boundaries. These three FIFOs are called:

• Asynchronous Control Transmit FIFO (ACTX)

• Asynchronous Control Receive FIFO (ACRX)

• Broadcast Write Receive FIFO (BWRX)

2.5.1 Asynchronous Control Transmit FIFO (ACTX)

The ACTX FIFO is typically used to transmit small asynchronous control packets as sent by the

microprocessor/microcontroller. The ACTX FIFO can also be used to support asynchronous traffic at very

low data rates. Asynchronous packets are generated by using the ACTXF, ACTXC, ACTXFU, and the

ACTXCU registers, all of which access the ACTX FIFO (see Section 3.1.1).

2.5.2 Asynchronous Control Receive FIFO (ACRX)

The ACRX FIFO is typically used to receive asynchronous control packets other than the Self-ID packet.

Regular asynchronous control packets typically go to the ACRX FIFO. This FIFO is mapped to the ACRX

register. A read from this register accesses the ACRX FIFO (see Section 3.2.1.1).

2.5.3 Broadcast Write Receive FIFO (BWRX)

The BWRX FIFO is typically used to receive asynchronous broadcast write request packets.

2.6 Physical Layer Interface

The physical layer interface provides phy-level services to the transmitter and receiver. This includes

gaining access to the serial bus, sending packets, receiving packets, and sending and receiving

acknowledgement packets. The TSB12LV41A supports Texas Instruments bus-holder circuity on the

Phy-link interface terminals. By using the internal bus holders, the user avoids the need for the high device

count 1394 Annex J method of isolation. The bus holders are enabled by connecting the ISOLA T

to ground.

terminal

2.7 Configuration Register (CFR)

The TSB12L V41A is configured for various modes of operation using CFRs. These registers are accessed

via the host microprocessor/microcontroller. The CFR space is 512 bytes, thus the need for a 9-bit address

bus. All CFRs are 32-bits wide, and since the microprocessor interface is only 8- or 16-bits wide, it must

perform a byte stacking/unstacking operation of the incoming (write) or outgoing (read) microprocessor

data. Section 5 gives a map of all the registers and detailed descriptions of all register bits.

2–4

3 TSB12LV41A Data Formats

The data formats for transmission and reception of data are shown in the following sections. The transmit

format describes the expected organization of data presented to the TSB12L V41A at the host-bus interface.

The receive formats describe the data format that the TSB12L V41A presents to the host-bus interface.

3.1 Transmit Operation

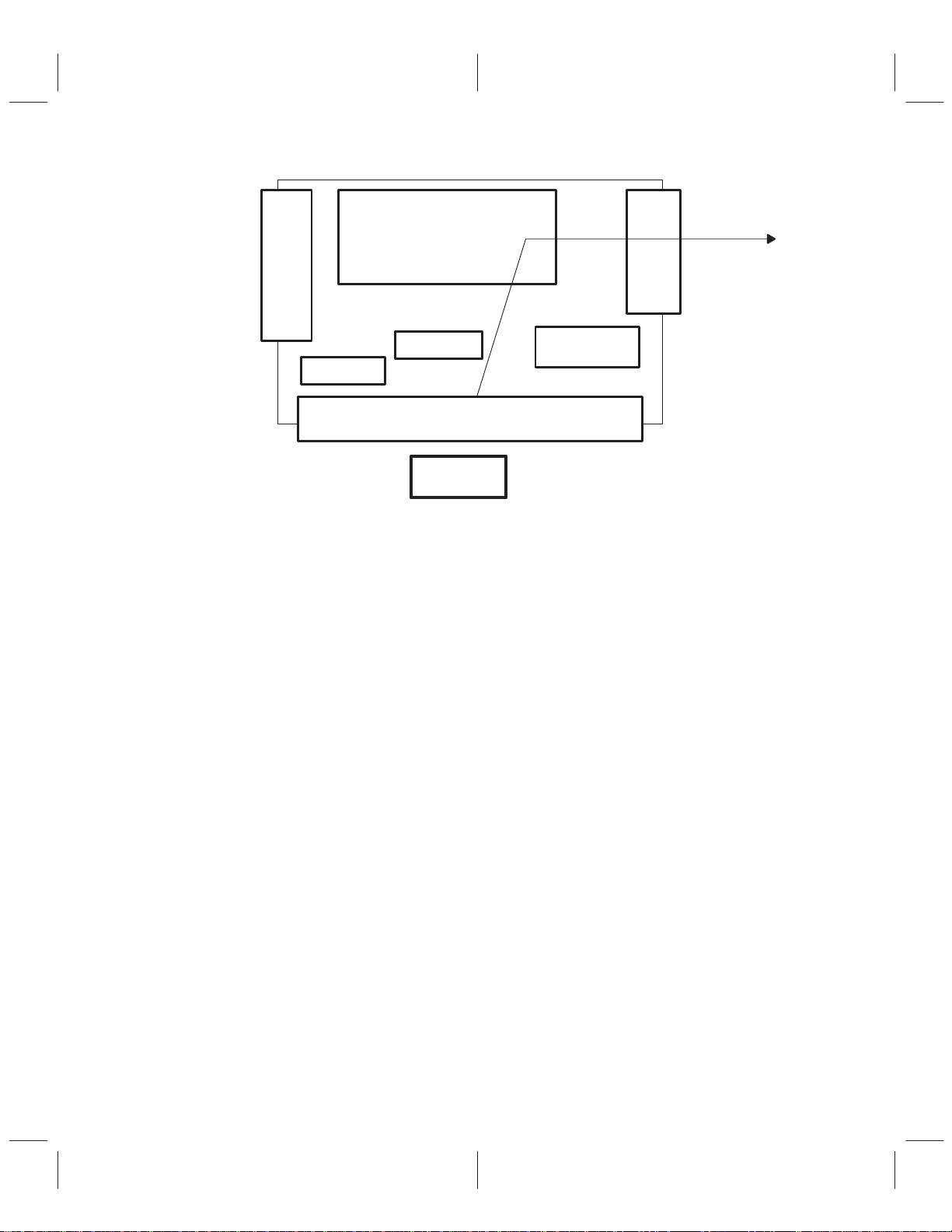

3.1.1 Transmitting Asynchronous Control Packets

Asynchronous control packets are typically transmitted by the microprocessor (host) using the

asynchronous control transmit FIFO (ACTX). This FIFO is part of the 256 bytes Control FIFO. It is

configurable in register 44h (Asynchronous Control Data Transmit FIFO Status.) The ACTX FIFO can also

be used for asynchronous data traffic at low data rates.

For transmit the 1394 asynchronous headers and the data are loaded into the ACTX by the microprocessor.

The microprocessor has access to the ACTX FIFO through registers 80h – 8Ch. The asynchronous header

must fit the format described in Section 3.4.

Bulky FIFO

BD–IF

Control FIFO

CFR

Phy–IF

MPMC–IF

Header, Data

Figure 3–1. Transmit from the Asynchronous Control Transmit FIFO (ACTX)

To transmit an asynchronous packet from the ACTX:

• Register 80h (Asynchronous Control Data Transmit FIFO First): The first quadlet of an

asynchronous packet is written to this register by the application software for transmit.

• Register 84h (Asynchronous Control Data Transmit FIFO Continue): All remaining quadlets of

an asynchronous packet except the last are written to this register by the application software for

transmit.

• Register 8Ch (Asynchronous Control Data Transmit FIFO Last and Send): The last quadlet of

an asynchronous packet is written to this register by the application software. Once the last

quadlet is written into the ACTX FIFO using this register, the entire packet is transmitted.

3–1

NOTE:Register 88h (Asynchronous Control Data Transmit FIFO First and

Update) can be used in conjunction with register 8Ch (Asynchronous Control Data

Transmit FIFO Last And Send) as an alternative method for transmitting

asynchronous control packets from ACTX. The first quadlet and all continuing

quadlets except the last are written to register 88h one quadlet at a time. Each

quadlet is transmitted immediately . The last quadlet is written to register 8Ch and

also transmitted immediately. This method of transmit should only be used in

systems where the microprocessor can keep up with the 1394 bus speed.

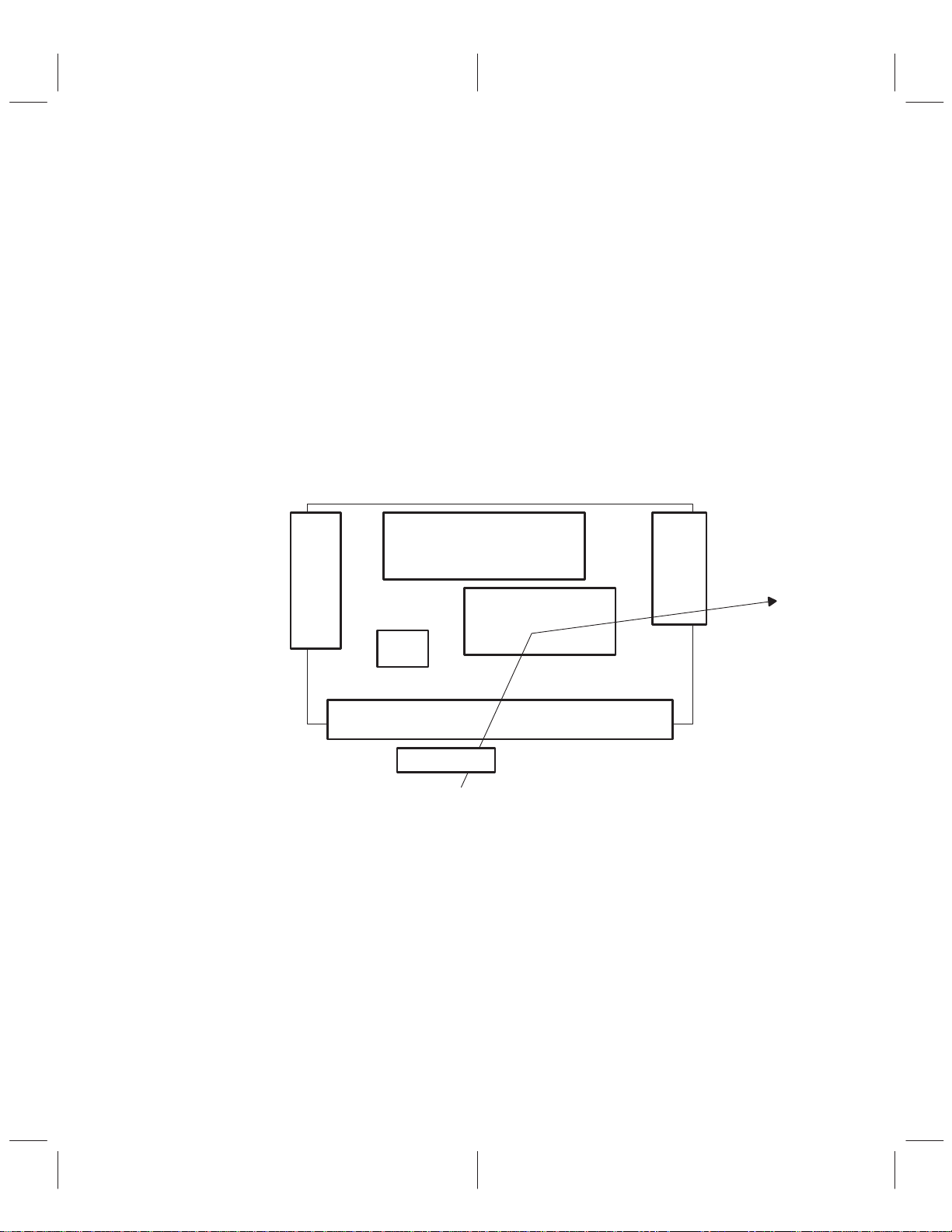

3.1.2 Transmitting Asynchronous Data Packets

Asynchronous data packets are typically transmitted from the bulky asynchronous transmit FIFO (BATX)

using either the bulky data interface (BDIF) or the microprocessor/microcontroller interface (MP/MC IF). The

BATX size is configurable in multiples of four quadlets in register 104h (bulky asynchronous size register.)

The number of empty quadlet locations available in the BATX is provided in register 108h (bulky

asynchronous available register). The transmit operation for the BA TX FIFO is configurable in register EC

(asynchronous/isochronous application data control register).

The BATX has an auto-packetization feature. This allows the user to program header registers within the

MPEG2Lynx CFR’s and supply raw data to the MPEG2Lynx for transmit. The MPEG2Lynx automatically

inserts the appropriate 1394 headers for transmit. The asynchronous packet is transmitted once the last

byte is indicated on bulky data interface or microprocessor interface. If the number of quadlets in the FIFO

is not a multiple of 4, then some byte padding is performed (see Section 3.1.4,

Byte Padding

headers for auto-packetization are available in registers 1B0 – 1BCh. Please note that the headers

programmed in registers 1B0 – 1BCh for auto packetization must match the formats described in Section

Asynchronous Data Formats

3.3,

. The MPEG2Lynx uses the information from these header registers to

create the 1394 asynchronous headers. Please note that automatic header insertion is only supported for

write request operations (tcode 0 and 1). If the number of bytes in the transmitted packet is different from

the datalength field in the header, then receiving node receives the packet with errors.

There are four methods of transmitting asynchronous data from the BATX. The control signals located in

register EC that are necessary for these four modes are summarized in the following text. A detailed

description is included for each mode.

). These

MODE ATENABLE BDAXE AHIM DATA SOURCE HEADER SOURCE

1 1 1 1 Bulky data interface Configuration registers

2 1 0 1 Microprocessor interface Configuration registers

3 1 1 0 Bulky data interface Bulky data interface

4 1 0 0 Microprocessor interface Microprocessor interface

Mode 1: Transmit Asynchronous Data from BATX Using The BDIF, Data Is

Auto-Packetized

The BDIF writes data to the BA TX. This data does not include any asynchronous header bytes. Registers

1B0 – 1BCh (AHEAD0 – AHEAD3) are programmed with the 1394 asynchronous header information. The

packet is transmitted once the last byte is written into the BA TX. The last byte is signaled by the bulky data

interface format lines (BDIF[2..0]). (settings for register EC in this mode: ATENABLE=1, BDAXE=1,

AHIM=1) Please reference Figure 3–2.

3–2

Data

BD–IF

Bulky FIFO

Headers

Phy–IF

Asynchronous,

Isochronous Tx

Control FIFO

Cycle Timer

CFR

MPMC–IF

Figure 3–2. Transmit Asynchronous/Isochronous Data from BATX by the Bulky Data Interface

with Auto-Packetization

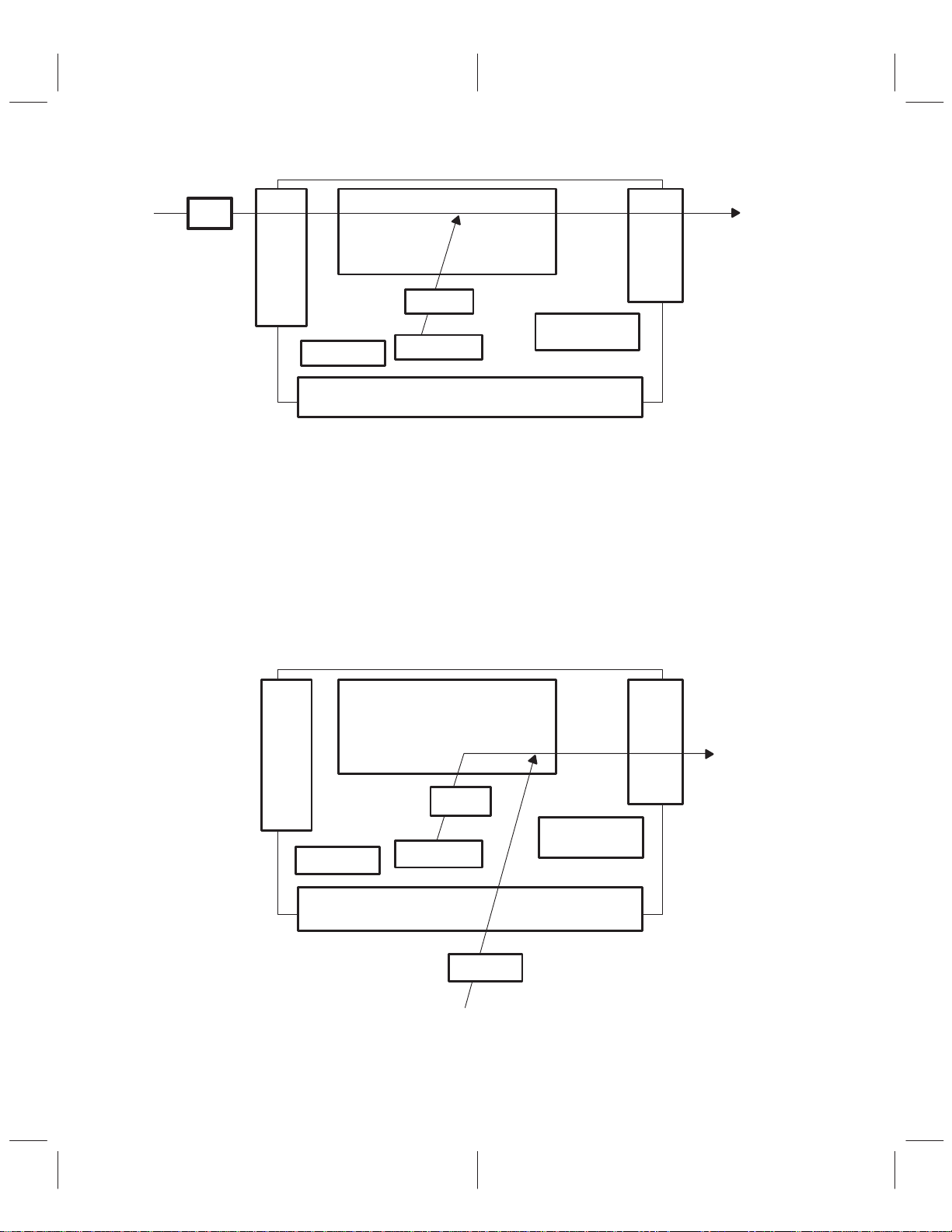

Mode 2: Transmit Asynchronous Data from BATX Using the MP/MC IF, Data Is

Auto-Packetized

The MP/MC IF writes data to the BATX using registers 10Ch and 110h. This data does not include any

asynchronous header bytes. Registers 1B0 – 1BCh (AHEAD0 – AHEAD3) are programmed with the 1394

asynchronous header information. Register 10Ch (Asynchronous Application Data Transmit FIFO First And

Continue) allows the MP/MC to write the all quadlets of the packet to be sent except for the last into the BA TX.

The last quadlet of the asynchronous packet is written into register 1 10h (Asynchronous Application Data

Transmit FIFO Last and Send.) The data is transmitted once the last quadlet is written into register 110h.

(Settings for register EC in this mode: A TENABLE=1, BDAXE=0, AHIM=1) (See Figure 3–3).

Asynchronous,

Bulky FIFO

Phy–IF

BD–IF

Isochronous Tx

Headers

Control FIFO

Cycle Timer

CFR

MPMC–IF

Data

Figure 3–3. Transmit Asynchronous/Isochronous Data from BATX by the MP/MC Interface with

Auto-Packetization

3–3

Mode 3: Transmit Asynchronous Data from BATX Using the BDIF, Data Is Fully

Formatted from the Application

The BDIF writes data to the BA TX. This data includes all asynchronous header and data bytes. The header

quadlets must match the same format as shown in Section 3.3. The packet is transmitted once the last byte

is written into the BATX. The last byte is signaled by the bulky data interface format lines (BDIF[2..0]).

(Settings for register EC in this mode: ATENABLE=1, BDAXE=1, AHIM=0) (See Figure 3–4).

Headers

and Data

BD–IF

Cycle Timer

Bulky FIFO

CFR

MPMC–IF

Control FIFO

Phy–IF

Asynchronous,

Isochronous Tx

Figure 3–4. Transmit Asynchronous/Isochronous Data from BATX by the Bulky Data Interface,

No Auto-Packetization

Mode 4: Transmit Asynchronous Data from BATX Using the MP/MC IF, Data Is Fully

Formatted from the Application

The MP/MC IF writes data to the BA TX using registers 10Ch and 1 10h. This data includes all asynchronous

header and data bytes. The header quadlets must match the same format as shown in Section 3.3. Register

10Ch (Asynchronous Application Data Transmit FIFO First and Continue) allows the MP/MC to write the

all quadlets of the packet to be sent except for the last into the BA TX. The last quadlet of the asynchronous

packet is written into register 1 10h (Asynchronous Application Data Transmit FIFO Last and Send.) The data

is transmitted once the last quadlet is written into register 110h (Settings for register EC in this mode:

A TENABLE=1, BDAXE=0, AHIM=0) (see Figure 3–5).

3–4

BD–IF

Bulky FIFO

Phy–IF

Asynchronous,

Isochronous Tx

CFR

Cycle Timer

MPMC–IF

Headers

and Data

Control FIFO

Figure 3–5. Transmit Asynchronous/Isochronous Data from BATX by the MP/MC Interface, No

Auto-Packetization

General Asynchronous Transmit Notes

• Packet Flush: The entire BATX FIFO can be flushed by setting the AXFLSH bit in the AICR

register (register EC).

• Packet Retries: Bulky asynchronous packets may be automatically retried up to 256 times

(BATxRetryNum in register 14Ch, BARTRY) in up to 256 isochronous cycles (BATxRetryInt in

register 14Ch, BARTRY). Packet retries for the asynchronous control transmit FIFO are manual.

• Retry Protocol: The MPEG2Lynx uses single phase retries only.

• Auto-packetization: For the bulky data interface, if the data from the host is a multiple of four

bytes, then there is no need to indicate

last byte

interface. Similarly , if data from the microprocessor interface is a multiple of four bytes, then all

of the data can be written to register 10Ch only. The packet is transmitted on the bus once the

number of bytes in the FIFO is equal to the data length field of the asynchronous header.

• Acknowledges received for an asynchronous packet transmitted from the bulky asynchronous

transmit FIFO (BATX) are available in register 8h (B Ack register). Bit 23 indicates if the ack

received was normal, BATACK[23] = 0, or if it was an error, BATACK[23] = 1. BATACK[24:27]

gives the acknowledge error if one occurred.

• Acknowledges received for an asynchronous packet transmitted from the asynchronous control

transmit FIFO (ACTX) are available in register 4 (C acknowledge register). Bit 23 indicates if the

ack received was normal, CATACK[23] = 0, or if there was an error, CATACK[23] = 1.

CATACK[24:27] gives the acknowledge error if one occurred.

of an asynchronous packet to the bulky data

3–5

3.1.3 Transmitting Isochronous Packets

Isochronous data is transmitted from the bulky isochronous transmit FIFO (BITX) using either the bulky data

interface (BDIF) or the microprocessor/microcontroller interface (MP/MC IF). The BITX size is configurable

in multiples of four quadlets in register 12Ch (bulky isochronous size register.) The number of empty quadlet

locations available in the BITX is provided in register 130h (bulky isochronous available register). The

transmit operation for the BITX FIFO is configurable in register EC (asynchronous/isochronous application

data control register).

The BITX has an auto-packetization feature which allows the user to program header registers within the

MPEG2Lynx CFR’s. The application can then supply raw data to the MPEG2Lynx for transmit, and the

MPEG2Lynx automatically packetizes the data and insert the appropriate 1394 header for transmit. The

amount of data in the transmit FIFO should match the datalength field in the isochronous header. Some byte

padding is performed when the data does not end on a quadlet boundary. See Section 3.4.1 for more