TSB12LV01A / TSB12LV01AI

Data Manual

IEEE 1394-1995

High-Speed Serial-Bus

Link-Layer Controller

Sourced from: SLLS332A

February 2000

Printed on Recycled Paper

IMPORTANT NOTICE

T exas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue

any product or service without notice, and advise customers to obtain the latest version of relevant information

to verify, before placing orders, that information being relied on is current and complete. All products are sold

subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those

pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent

TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily

performed, except those mandated by government requirements.

CERT AIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MA Y INVOLVE POTENTIAL RISKS OF

DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL

APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR

WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER

CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICA TIONS IS UNDERSTOOD T O

BE FULLY AT THE CUSTOMER’S RISK.

In order to minimize risks associated with the customer’s applications, adequate design and operating

safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent

that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other

intellectual property right of TI covering or relating to any combination, machine, or process in which such

semiconductor products or services might be or are used. TI’s publication of information regarding any third

party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.

Copyright 2000, Texas Instruments Incorporated

iii

Contents

Section Title Page

1 Overview 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1 Description 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2 Features 1–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2.1 Link 1–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2.2 Physical-Link Interface 1–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2.3 Host Bus Interface 1–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2.4 General 1–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3 Terminal Assignments 1–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4 Terminal Functions 1–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2 Architecture 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1 Functional Block Diagram 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.1 Physical Interface 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.2 Transmitter 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.3 Receiver 2–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.4 Transmit and Receive FIFOs 2–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.5 Cycle Timer 2–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.6 Cycle Monitor 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.7 Cyclic Redundancy Check (CRC) 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.8 Internal Registers 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.9 Host Bus Interface 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3 Internal Registers 3–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1 General 3–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2 Internal Register Definitions 3–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.1 Version/Revision Register (@00h) 3–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.2 Node-Address/Transmitter Acknowledge Register (@04h) 3–3. . . . . . . . . . . .

3.2.3 Control Register (@08h) 3–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.4 Interrupt and Interrupt-Mask Registers (@0Ch, @10h) 3–6. . . . . . . . . . . . . . . .

3.2.5 Cycle-Timer Register (@14h) 3–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.6 Isochronous Receive-Port Number Register (@18h) 3–9. . . . . . . . . . . . . . . . . .

3.2.7 FIFO Control Register (@1Ch) 3–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.8 Diagnostic Control Register (@20h) 3–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.9 Phy-Chip Access Register (@24h) 3–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.10 Asynchronous Transmit-FIFO (ATF) Status Register (@30h) 3–11. . . . . . . . .

3.2.11 ITF Status Register (@34h) 3–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.12 GRF Status Register (@3Ch) 3–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

iv

3.3 FIFO Access 3–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.1 General 3–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.2 ATF Access 3–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.3 ITF Access 3–15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.4 General-Receive FIFO (GRF) 3–17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.5 RAM Test Mode 3–18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4 TSB12LV01A Data Formats 4–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1 Asynchronous Transmit (Host Bus to TSB12LV01A) 4–1. . . . . . . . . . . . . . . . . . . . . . . .

4.1.1 Quadlet Transmit 4–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1.2 Block Transmit 4–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1.3 Quadlet Receive 4–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1.4 Block Receive 4–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2 Isochronous Transmit (Host Bus to TSB12LV01A) 4–6. . . . . . . . . . . . . . . . . . . . . . . . . .

4.3 Isochronous Receive (TSB12L V01A to Host Bus) 4–6. . . . . . . . . . . . . . . . . . . . . . . . . .

4.4 Snoop Receive 4–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5 Phy Configuration Transmit 4–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.6 Link-On Transmit 4–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.7 Receive Self-ID 4–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.8 Received Phy Configuration and Link–On Packet 4–10. . . . . . . . . . . . . . . . . . . . . . . . .

5 Electrical Characteristics 5–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1 Absolute Maximum Ratings Over Free-Air Temperature Range 5–1. . . . . . . . . . . . . .

5.2 Recommended Operating Conditions 5–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3 Electrical Characteristics Over Recommended Ranges of Supply Voltage

and Operating Free-Air Temperature 5–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.4 Host-Interface Timing Requirements 5–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.5 Host-Interface Switching Characteristics Over Operating Free-Air

Temperature Range 5–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6 Phy-Interface Timing Requirements Over Operating Free-Air

Temperature Range 5–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.7 Phy-Interface Switching Characteristics Over Operating Free-Air

Temperature Range 5–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.8 Miscellaneous Timing Requirements Over Operating Free-Air

Temperature Range 5–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.9 Miscellaneous Signal Switching Characteristics Over Operating Free-Air

Temperature Range 5–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6 Parameter Measurement Information 6–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

v

7 TSB12LV01A to 1394 Phy Interface Specification 7–1. . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.1 Introduction 7–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2 Assumptions 7–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.3 Block Diagram 7–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.4 Operational Overview 7–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.4.1 Phy Interface Has Control of the Bus 7–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.4.2 TSB12LV01A Has Control of the Bus 7–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.5 Request 7–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.5.1 LREQ Transfer 7–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.5.2 Bus Request 7–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.5.3 Read/Write Requests 7–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.6 Status 7–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.6.1 Status Request 7–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.6.2 Transmit 7–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.6.3 Receive 7–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.7 TSB12LV01A to Phy Bus Timing 7–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8 Mechanical Data 8–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

vi

List of Illustrations

Figure Title Page

1–1 TSB12LV01A Terminal Functions 1–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–1 TSB12LV01A Block Diagram 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–1 Internal Register Map 3–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–2 Interrupt Logic Diagram Example 3–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–3 TSB12LV01A Controller-FIFO-Access Address Map 3–13. . . . . . . . . . . . . . . . . . . . . . . .

4–1 Quadlet-Transmit Format 4–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–2 Block-Transmit Format 4–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–3 Quadlet-Receive Format 4–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–4 Block-Receive Format 4–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–5 Isochronous-Transmit Format 4–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–6 Isochronous-Receive Format 4–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–7 Snoop Format 4–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–8 Phy Configuration Format 4–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–9 Link-On Format 4–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–10 Receive Self-ID Format 4–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–1 BCLK Waveform 6–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–2 Host-Interface Write-Cycle Waveforms (Address: 00h – 2Ch) 6–1. . . . . . . . . . . . . . . . .

6–3 Host-Interface Read-Cycle Waveforms (Address: 00h – 2Ch) 6–2. . . . . . . . . . . . . . . . .

6–4 Host-Interface Quick Write-Cycle Waveforms (ADDR0 – ADDR7 . 30h) 6–2. . . . . . . .

6–5 Host-Interface Quick Read-Cycle Waveforms (ADDR0 – ADDR7 . 30h) 6–3. . . . . . . .

6–6 Burst Write Waveforms 6–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–7 Burst Read Waveforms 6–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–8 SCLK Waveform 6–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–9 TSB12LV01A-to-Phy-Layer Transfer Waveforms 6–5. . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–10 Phy Layer-to-TSB12LV01A Transfer Waveforms 6–6. . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–11 TSB12LV01A Link-Request-to-Phy-Layer Waveforms 6–6. . . . . . . . . . . . . . . . . . . . . . . .

6–12 Interrupt Waveform 6–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–13 CYCLEIN Waveform 6–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–14 CYCLEIN and CYCLEOUT Waveforms 6–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–1 Functional Block Diagram of the TSB12LV01A to Phy Layer 7–1. . . . . . . . . . . . . . . . . .

7–2 LREQ Timing 7–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–3 Status-Transfer Timing 7–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–4 Transmit Timing 7–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–5 Receiver Timing 7–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

vii

List of Tables

Table Title Page

1–1 Terminal Functions 1–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–1 Version/Revision Register Field Descriptions 3–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–2 Node-Address/Transmitter Acknowledge Register Field Descriptions 3–3. . . . . . . . . .

3–3 Control-Register Field Descriptions 3–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–4 Interrupt- and Mask-Register Field Descriptions 3–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–5 Cycle-Timer Register Field Descriptions 3–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–6 Isochronous Receive-Port Number Register Field Descriptions 3–9. . . . . . . . . . . . . . . .

3–7 Node-Address/ Transmitter Acknowledge Register Field Descriptions 3–9. . . . . . . . . .

3–8 Diagnostic Control and Status-Register Field Descriptions 3–10. . . . . . . . . . . . . . . . . . .

3–9 Phy-Chip Access Register 3–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–10 ATF Status Register 3–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–11 ITF Status Register 3–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–12 GRF Status Register 3–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–13 Control Bit Value 3–19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–1 Quadlet-Transmit Format 4–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–2 Block-Transmit Format Functions 4–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–3 Quadlet-Receive Format Functions 4–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–4 Block-Receive Format Functions 4–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–5 Isochronous-Transmit Functions 4–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–6 Isochronous-Receive Functions 4–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–7 Snoop Functions 4–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–8 Phy Configuration Functions 4–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–9 Link-On Functions 4–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–10 Isochronous-Receive Functions 4–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–1 Phy Interface Control of Bus Functions 7–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–2 TSB12LV01A Control of Bus Functions 7–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–3 Request Functions 7–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–4 Bus-Request Functions (Length of Stream: 7 Bits) 7–2. . . . . . . . . . . . . . . . . . . . . . . . . . .

7–5 Read-Register Request Functions (Length of Stream: 9 Bits) 7–3. . . . . . . . . . . . . . . . .

7–6 Write-Register Request (Length of Stream: 17 Bits) 7–3. . . . . . . . . . . . . . . . . . . . . . . . . .

7–7 TSB12LV01A Request Functions 7–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–8 TSB12LV01A Request-Speed Functions 7–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–9 Status-Request Functions (Length of Stream: 16 Bits) 7–5. . . . . . . . . . . . . . . . . . . . . . .

7–10 Speed Code for Receive 7–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

viii

1–1

1 Overview

1.1 Description

The TSB12LV01A is an IEEE 1394-1995 standard (from now on referred to only as 1394) high-speed

serial-bus link-layer controller that allows for easy integration into an I/O subsystem. The TSB12LV01A

provides a high-performance IEEE 1394-1995 interface with the capability of transferring data between the

32-bit host bus, the 1394 PHY -link interface, and external devices connected to the local bus interface. The

1394 PHY -link interface provides the connection to the 1394 physical (PHY) layer device and is supported

by the link-layer controller (LLC). The LLC provides the control for transmitting and receiving 1394 packet

data between the FIFO and PHY-link interface at rates of 100Mbit/s, 200Mbit/s, and 400Mbit/s. The

TSB12LV01A transmits and receives correctly-formatted 1394 packets and generates and inspects the

32-bit cyclic redundancy check (CRC). The TSB12LV01A is capable of being cycle master and supports

reception of isochronous data on two channels or all isochronous channels. TSB12LV01A has a generic

32-bit host bus interface, which connects to most 32-bit hosts. The LLC also provides the capability to

receive status from the physical layer device and to access the physical layer control and status registers

by the application software. An internal 2K-byte memory can be configured as multiple variable-size FIFOs

and eliminates the need for external FIFOs. Separate FIFOs can be user-configured to support general 1394

receive, asynchronous transmit, and isochronous transmit transfer operations. These functions are

accomplished by appropriately sizing the general receive FIFO (GRF), asynchronous transmit FIFO (ATF),

and isochronous transmit FIFO (ITF).

The TSB12LV01A provides bus holding buffers on the PHY interface for simple and cost effective

single-capacitor isolation.

The TSB12LV01A is a revision of the TSB12C01A, with feature enhancements and corrections. All errata

items to the TSB12C01A have been corrected, and the following feature enhancements have been made:

• Cycle start packets can be stored in the GRF.

• Isochronous and asynchronous packet transmit and receive can be enabled/disabled

independently. Asynchronous transmit is disabled upon reset, while isochronous transmit and

receive is unaffected.

• One, two, or all isochronous channels can be received.

• When receiving packets, RxDta can be programmed to interrupt the host processor on

programmable block boundaries, so the host can retrieve data from the GRF when each block

is available.

This is especially useful if the GRF is smaller than the expected receive packet size. RxDta can

also be programmed to interrupt the host processor when each packet is received.

• Host bus burst mode data transfer is supported, at the peak rate of one quadlet (four bytes) per

BClk cycle for ATF write, ITF write, and GRF read.

• A FIFO status read can be accomplished in three BClk cycles: 1. Address cycle 2. Data cycle

3. Idle cycle

• Several changes in the register map have been made to improve host bus data throughput and

reduce status read and interrupt overhead. ATF status (30h), ITF status (34h) and GRF status

(3Ch) contains only status information. FIFO control (1Ch) is defined to control ATF size, ITF size,

clear FIFO function, and block size for GRF received packet. ATF status register and ITF status

register will report flags: full, empty and available space for host bus burst write. GRF status

register will report flags: empty, total stored data count, and next received block size.

1–2

• Maximum data burst throughput on the host bus interface is 200 Mbyte/s, if Bclk is run at 50 MHz.

• Received packet formats now include the packet error status in the first quadlet of the packet in

the receive FIFO.

• Provides bus-hold buffers on physical interface for low-cost single capacitor isolation

This document is not intended to serve as a tutorial on 1394; users are referred to the IEEE 1394-1995 serial

bus standard for detailed information regarding the 1394 high-speed serial bus.

1.2 Features

The following are features of the TSB12LV01A.

1.2.1 Link

• Supports Provision of IEEE 1394-1995 (1394) Standard for High-Performance Serial Bus

• Transmits and Receives Correctly Formatted 1394 Packets

• Supports Isochronous Data Transfer

• Performs Function of 1394 Cycle Master

• Generates and Checks 32-Bit CRC

• Detects Lost Cycle-Start Messages

• Contains Asynchronous, Isochronous, and General-Receive FIFOs Totaling 2K Bytes

1.2.2 Physical-Link Interface

• Interfaces Directly to the TSB11LV01, TSB14C01, TSB21LV03A, and TSB41LV0x PHY Chips

• Supports Speeds of 100 Mbits/s, 200 Mbits/s, and 400 Mbits/s

• Implements the Physical-Link Interface Described in Annex J of the IEEE 1394-1995 Standard

• Supports TI Bus Holder Isolation External Implementation

1.2.3 Host Bus Interface

• Provides Chip Control With Directly Addressable Registers

• Is Interrupt Driven to Minimize Host Polling

• Has a Generic 32-Bit Host Bus Interface

1.2.4 General

• Operates from a 3.3-V Power Supply While Maintaining 5-V Tolerant Inputs

• Manufactured with Low-Power CMOS Technology

• Packaged in a 100-Pin Thin Quad Flat Package (TQFP) (PZ Package) for 0°C to 70°C and –40°C

to 85°C Operation

1–3

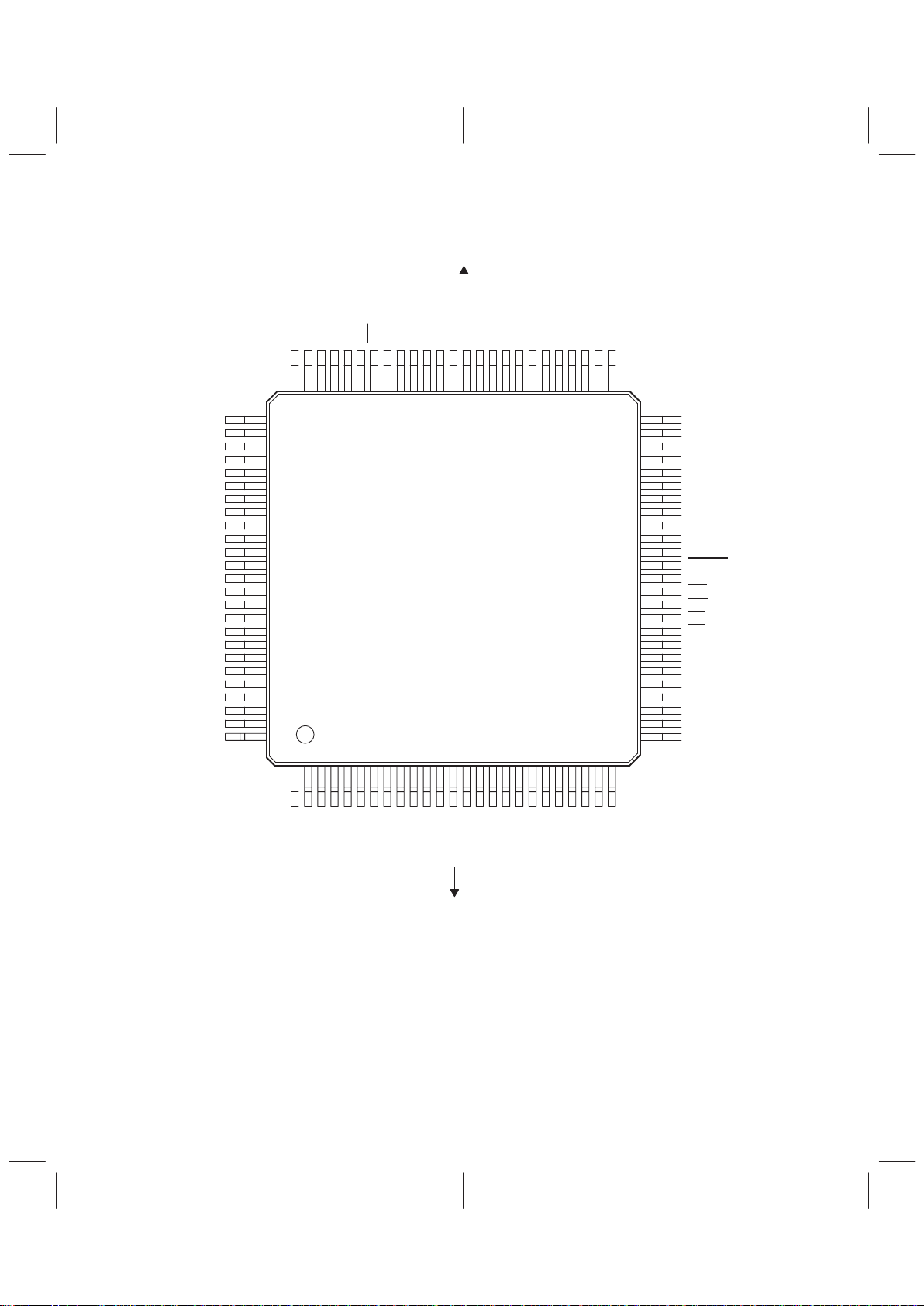

1.3 Terminal Assignments

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

12345678910111213141516171819202122232425

75747372717069686766656463626160595857565554535251

GND

DATA16

DATA17

DATA18

DATA19

DATA20

DATA21

DATA22

DATA23

GND

DATA24

DATA25

DATA26

DATA27

DATA28

DATA29

DATA30

DATA31

GND

ADDR0

ADDR1

ADDR2

ADDR3

Reserved

NTCLK

NTOUT

NTBIHIZ

GND

ISO

GND

LREQ

GND

SCLK

CTL0

CTL1

GNDD0D1D2D3D4D5D6D7

GND

CYST

CYDNE

GRFEMP

GND

GND

GND

CYCLEOUT

V

CC

CYCLEIN

GND

GND

RESET

GND

INT

WR

CA

CS

VCC+5V

BCLK

GND

ADDR7

ADDR6

ADDR5

ADDR4

V

CC

POWERON

RAMEZ

GND

GND

GND

GND

DATA0

DATA1

DATA2

DATA3

VCC+5V

DATA4

DATA5

DATA6

DATA7

GND

DATA8

DATA9

DATA10

DATA11

V

CC

DATA12

DATA13

DATA14

DATA15

V

CC

V

V

CC

CC

To Host

To PHY Layer

NOTES: A. Tie reserved terminals to GND.

TSB12LV01A

PZ PACKAGE

(TOP VIEW)

B. Bit 0 is the most significant bit (MSB).

V

CC

+5V

V

CC

+5V

1–4

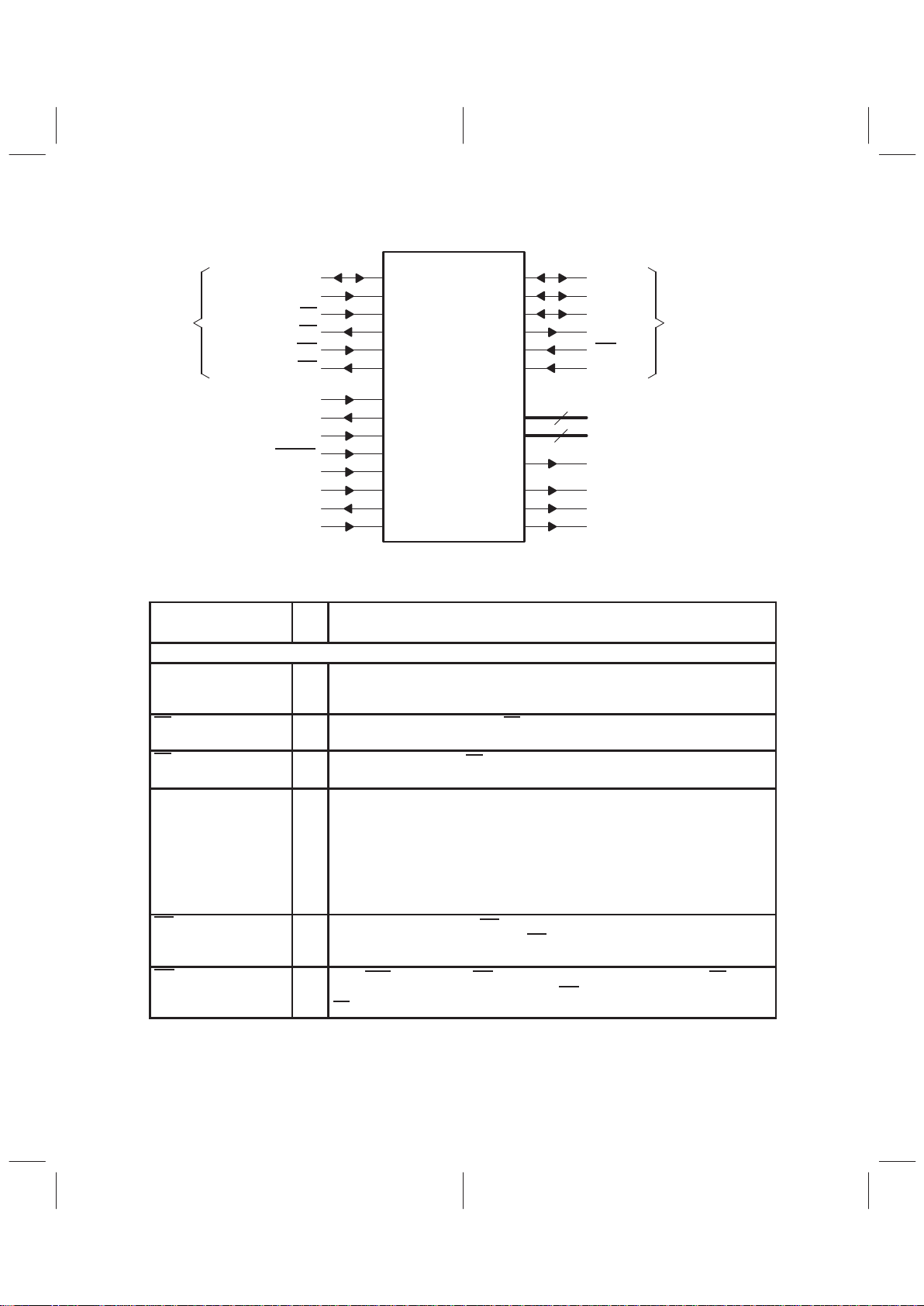

1.4 Terminal Functions

PHY Interface

D0 – D7

CTL0

CTL1

LREQ

ISO

SCLK

DATA0 – DATA31

ADDR0 – ADDR7

CS

CA

WR

INT

CYCLEIN

CYCLEOUT

BCLK

RESET

RAMEZ

V

CC

GND

Host

Bus

10

20

TSB12LV01A

NTCLK

NTOUT

NTBIHIZ

CYST

CYDNE

GRFEMP

POWERON

Figure 1–1. TSB12LV01A Terminal Functions

Table 1–1. Terminal Functions

TERMINAL

NAME NO.

I/O

DESCRIPTION

Host Bus Interface

ADDR0 –

ADDR7

22–25

27–30

I Address 0 through address 7. Host bus address bus bits 0 through 7 that address

the quadlet-aligned FIFOs and configuration registers. The two least significant

address lines, 6 and 7, must be grounded. Bit 0 is the most significant bit.

CA 35 O Cycle acknowledge (active low). CA is a TSB12L V01A control signal to the host bus.

When asserted (low), access to the configuration registers or FIFO is complete.

CS 34 I

Cycle start (active low). CS is a host bus control signal to initiate access to the

configuration registers or FIFO.

DATA0 –

DATA31

2–5

7–10

12–15

17–20

82–85

87–90

92–95

97–100

I/O Data 0 through 31. DATA is a host bus data bus bits 0 through 31. Bit 0 is the most

significant bit. Byte 0 is the most significant byte.

INT 37 O

Interrupt (active low). When INT is asserted (low), the TSB12L V01A notifies the host

bus that an interrupt has occurred. INT

is cleared when all the bits INT bits are

cleared in the INT register (or the mask is set false).

WR 36 I

Read/write enable. When WR is deasserted (high) in conjunction with CS, a read

from the TSB12LV01A is requested. When WR

is asserted (low) in conjunction with

CS

, a write to the TSB12LV01A is requested.

1–5

Table 1–1. Terminal Functions (Continued)

TERMINAL

NAME NO.

I/O

DESCRIPTION

PHY Interface

CTL1, CTL0 62, 63 I/O Control 1 and control 0 of the PHY -link control bus. CTL1 and CTL0 indicate the four

operations that can occur in this interface (see Section 7 of this document or Annex

J of the IEEE 1394-1995 standard for more information about the four operations).

These terminals have bus holder functionality built in. When RESET

is asserted,

CTL0 and CTL1 are initialized to 0 (low) for one SCLK cycle and then released. The

bus holders then hold CTL0 and CTL1 at 0 (low) until a transition is driven.

D0 – D7 52–55

57–60

I/O Data 0 through data 7 of the PHY-link data bus. Data is expected on D0 – D1 for

100 Mbits/s packets, D0 – D3 for 200 Mbits/s, and D0 – D7 for 400 Mbits/s transfers.

These terminals have bus holder functionality built in. When RESET

is asserted,

D0 – D7 are initialized to 0 (low) for one SCLK cycle and then released. The bus

holders then hold D0 – D7 at 0 (low) until a transition is driven.

ISO 69 I

Isolation barrier (active low). ISO is asserted (low) when an isolation barrier is

present. This terminal only supports bus holder type isolation.

LREQ 67 O Link request. LREQ is a TSB12LV01A output that makes bus requests and access

requests to the PHY layer. On the first rising edge of SCLK when RESET

is asserted,

LREQ is driven to 0 (low).

POWERON 76 O Power on indicator to PHY interface. When active, POWERON has a clock output

with 1/16 of the BCLK frequency and indicates to the PHY interface that the

TSB12LV01A is powered. This terminal can be connected to the link power status

(LPS) terminal on the TI PHY devices to provide an indication of the LLC power

condition. When RESET

is asserted, POWERON is driven to 0 (low).

SCLK 65 I System clock. SCLK is a 49.152-MHz clock from the PHY, that generates the internal

24.576-MHz clock used internally in the TSB12L V01A.

Miscellaneous Signals

BCLK 32 I Bus clock. BCLK is the host bus clock used for the host-interface module of the

TSB12LV01A. It is asynchronous to SCLK.

CYCLEIN 42 I Cycle in. CYCLEIN is an optional external 8,000-Hz clock used to time the

isochronous cycle clock, and it should only be used when attached to the

cycle-master node. It is enabled by the cycle source bit and should be tied high when

not used.

CYCLEOUT 44 O Cycle out. CYCLEOUT is the version of the isochronous cycle clock used by the

TSB12LV01A. It is based on the internal timer controls and received cycle-start

messages.

CYDNE 49 O Status of CyDne bit. CYDNE indicates the value of the CyDne bit of the interrupt

register. This terminal is asserted for as long as the interrupt bit is assigned.

CYST 50 O Status of CySt bit. CYST indicates the value of the CySt bit of the interrupt register.

This terminal is asserted for as long as the interrupt bit is set.

1–6

Table 1–1. Terminal Functions (Continued)

TERMINAL

NAME NO.

I/O

DESCRIPTION

GND 1, 11, 21,

31, 38, 40,

41, 45–47,

51, 61, 66,

68, 70,

78–81, 91

Ground reference

GRFEMP 48 O Status of Empty bit. This terminal is asserted for as long as the GRFEMP bit is set.

RAMEZ 77 I RAM 3-state enable. When RAMEZ is deasserted (low), FIFOs are enabled. When

RAMEZ is asserted, the FIFOs are 3-state outputs. (This is a manufacturing

test-mode condition and should be grounded under normal operating conditions.)

NTBIHIZ 71 I NAND-tree bidirectional 3-state output. When NTBIHIZ is deasserted (low), the

bidirectional I/Os operate in a normal state. When NTBIHZ is asserted (high), the

bidirectional I/Os are in the 3-state output mode. (This is a manufacturing

test-mode condition and should be grounded under normal operating conditions.)

NTCLK 73 I NAND clock input. The NAND-tree clock is used for VIH and VIL manufacturing

tests. (This input should be grounded under normal operating conditions.)

NTOUT 72 O NAND-tree output. This output should remain open under normal operating

conditions.

RESET 39 I Reset (active low). RESET is the asynchronous reset to the TSB12LV01A.

V

CC

6, 26, 43,

56, 74, 96

3.3-V ±5% power supplies

VCC+5V 16, 33

64, 86

5-V ±5% power supplies

2–1

2 Architecture

2.1 Functional Block Diagram

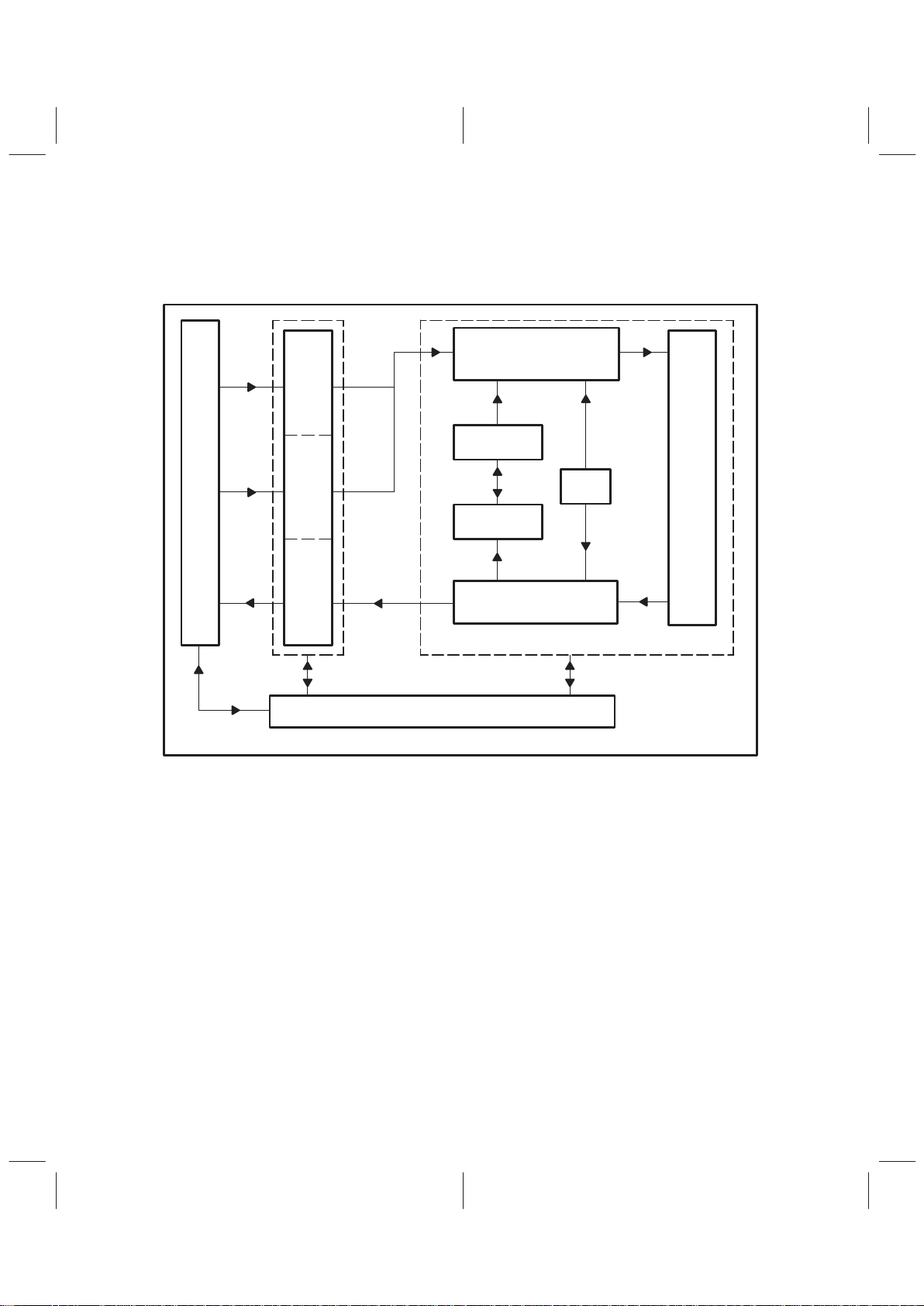

The functional block architecture of the TSB12LV01A is shown in Figure 2–1.

Transmitter

Cycle Timer

Cycle Monitor

CRC

Receiver

Configuration Registers

GRF

ITF

ATF

P

h

y

s

i

c

a

l

I

n

t

e

r

f

a

c

e

H

o

s

t

I

n

t

e

r

f

a

c

e

Figure 2–1. TSB12LV01A Block Diagram

2.1.1 Physical Interface

The physical (PHY) interface provides PHY-level services to the transmitter and receiver . This includes gaining access to the serial bus, sending packets, receiving packets, sending and receiving acknowledge packets, and reading and writing PHY registers.

The PHY interface module also interfaces to the PHY chip and conforms to the PHY -link interface specification described in Annex J of the IEEE 1394-1995 standard (refer to Section 7 of this document for more information).

2.1.2 Transmitter

The transmitter retrieves data from either the ATF or the ITF and creates correctly formatted serial-bus

packets to be transmitted through the PHY interface. When data is present at the ATF interface to the

transmitter, the TSB12LV01A PHY interface requests the serial bus and upon receiving a grant, sends a

packet. When data is present at the ITF interface to the transmitter, the TSB12L V01A arbitrates for the serial

bus during the next isochronous cycle. The transmitter autonomously sends the cycle-start packets when

the chip is the cycle master. The PHY interface provides PHY-level services to the transmitter and receiver.

This includes gaining access to the serial bus, sending packets, receiving packets, and receiving status from

the physical layer.

2–2

2.1.3 Receiver

The receiver takes incoming data from the PHY interface and determines if the incoming data is addressed

to this node. If the incoming packet is addressed to this node, the CRC of the packet header is checked.

If the header CRC is good, the header is stored in the GRF. For block and isochronous packets, the

remainder of the packet is stored one quadlet at a time. The receiver places a status quadlet in the GRF

after the last quadlet of the packet is checked in the GRF . The status quadlet contains the error code for the

packet. The error code is the acknowledge code that was or could have been sent for that packet. For

broadcast packets that do not need an acknowledge packet, the error code is the acknowledge code that

would have been sent. This acknowledge code tells the transaction layer whether or not the data CRC is

good or bad. When the header CRC is bad, the header is flushed and the rest of the packet is ignored. Bad

packets are automatically flushed by the receiver.

When a cycle-start message is received, it is detected and the cycle-start message data is sent to the cycle

timer. The cycle-start messages can be placed in the GRF like other quadlet packets.

2.1.4 Transmit and Receive FIFOs

The TSB12LV01A contains two transmit FIFOs (ATF and ITF) and one receive FIFO (GRF). Each of these

FIFOs is one quadlet wide and their length is software selectable. These software-selectable FIFOs allow

customization of the size of each FIFO for individual applications. The sum of all FIFOs cannot be larger

than 512 quadlets. The transmit FIFOs are write only from the host bus interface, and the receive FIFO is

read only from the host bus interface. FIFO sizes must not be changed on the fly. All transactions must be

ignored and FIFOs cleared before changing the FIFO sizes.

An example of how to use software-adjustable FIFOs follows:

In applications where isochronous packets are large and asynchronous packets are small, the

implementers can set the ITF to a large size, 200 quadlets, and set the ATF to a smaller size, 100

quadlets.This means 212 quadlets are allocated to the GRF . Notice that the sum of all FIFOs is equal to 512

quadlets. Only the A TF size and the ITF size can be programmed, the remaining space is assigned to the

GRF.

2.1.5 Cycle Timer

The cycle timer is used by nodes that support isochronous data transfer. The cycle timer is a 32-bit

cycle-timer register. Each node with isochronous data-transfer capability has a cycle-timer register as

defined in the IEEE 1394-1995 standard. In the TSB12L V01A, the cycle-timer register is implemented in the

cycle timer and is located in IEEE-1212 initial register space at location 200h. It can also be accessed

through the host bus at address 14h. The cycle timer contains the cycle-timer register. The cycle-timer

register consists of three fields; cycle offset, cycle-count, and seconds count. The low-order 12 bits of the

timer are a modulo 3072 counter, which increments once every 24.576-MHz clock periods (or 40.69 ns).

The next 13 higher-order bits are a count of 8,000-Hz (or 125 µs) cycles, and the highest 7 bits count

seconds. The timer can be disabled using the cycle-timer-enable bit in the control register.

The cycle timer has two possible sources. The first cycle-source option is when the cycle source (CySrc)

bit in the configuration register is set, then the CYCLEIN input causes the cycle-count field to increment for

each positive transition of the CYCLEIN input (8 kHz) and the cycle offset resets to all zeros. CYCLEIN

should only be the source when the node is cycle master. When the cycle-count field increments,

CYCLEOUT is generated.

The second cycle-source option is when the CySrc bit is cleared. In this state, the cycle-offset field of the

cycle-timer register is incremented by the internal 24.576-MHz clock. The cycle timer is updated by the

reception of the cycle-start packet for the noncycle master nodes. Each time the cycle-offset field rolls over ,

the cycle-count field is incremented and the CYCLEOUT signal is generated. The cycle-offset field in the

cycle-start packet is used by the cycle-master node to keep all nodes in phase and running with a nominal

isochronous cycle of 125 µs.

2–3

The CTCLEOUT signal indicates whenever the cycle-count field of the cycle timer register increments.

Therefore, for a cyclemaster node CYCLEOUT indicates that it is time to send a cycle-start packet. And,

on noncyclemaster nodes, CYCLEOUT indicates that it is time to expect a cycle-start packet. The cycle-start

interrupt bit is set when the cycle-start packet is sent from the cyclemaster node or received by a

noncyclemaster node.

2.1.6 Cycle Monitor

The cycle monitor is only used by nodes that support isochronous data transfer. The cycle monitor observes

chip activity and handles scheduling of isochronous activity. When a cycle-start message is received or sent,

the cycle monitor sets the cycle-started interrupt bit. It also detects missing cycle-start packets and sets the

cycle-lost interrupt bit when this occurs. When the isochronous cycle is complete, the cycle monitor sets the

cycle-done-interrupt bit. The cycle monitor instructs the transmitter to send a cycle-start message when the

cycle-master bit is set in the control register.

2.1.7 Cyclic Redundancy Check (CRC)

The CRC module generates a 32-bit CRC for error detection. This is done for both the header and data. The

CRC module generates the header and data CRC for transmitting packets and checks the header and data

CRC for received packets. See the IEEE 1394-1995 standard for details on the generation of the CRC.

NOTE:This is the same CRC used by the IEEE802 LANs and the X3T9.5 FDDI.

2.1.8 Internal Registers

The internal registers control the operation of the TSB12LV01A.

2.1.9 Host Bus Interface

The host bus interface allows the TSB12LV01A to be easily connected to most host processors. This host

bus interface consists of a 32-bit data bus and an 8-bit address bus. The TSB12LV01A utilizes cycle-start

and cycle-acknowledge handshake signals to allow the local bus clock and the 1394 clock to be

asynchronous to one another. The TSB12LV01A is interrupt driven to reduce polling.

2–4

3–1

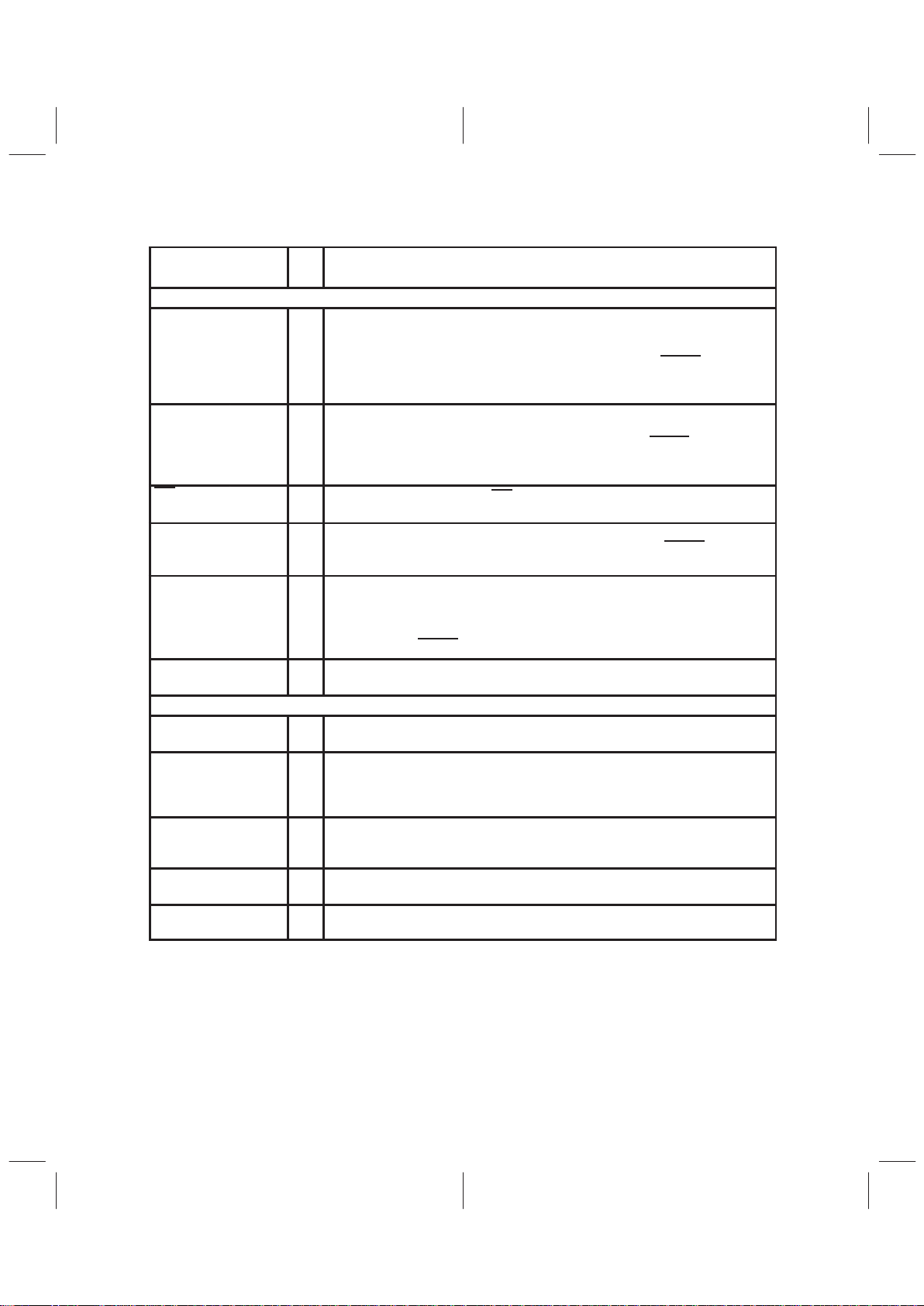

3 Internal Registers

3.1 General

The host-bus processor directs the operation of the TSB12LV01A through a set of registers internal to the

TSB12L V01A itself. These registers are read or written by asserting CS

with the proper address on ADDR0

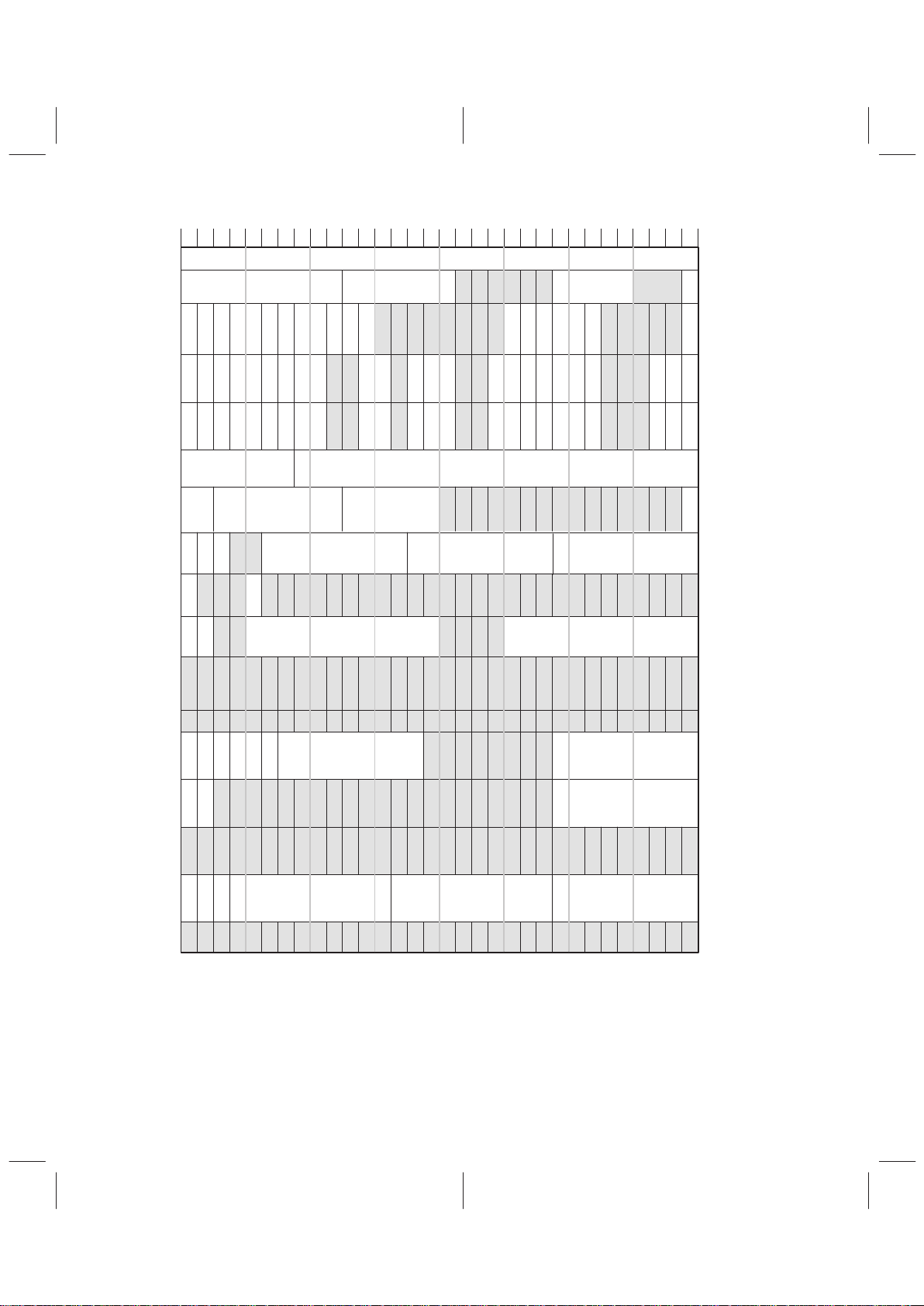

– ADDR7 and asserting or deasserting WR depending on whether a read or write is needed. Figure 3–1 lists

the register addresses; subsequent sections describe the function of the various registers.

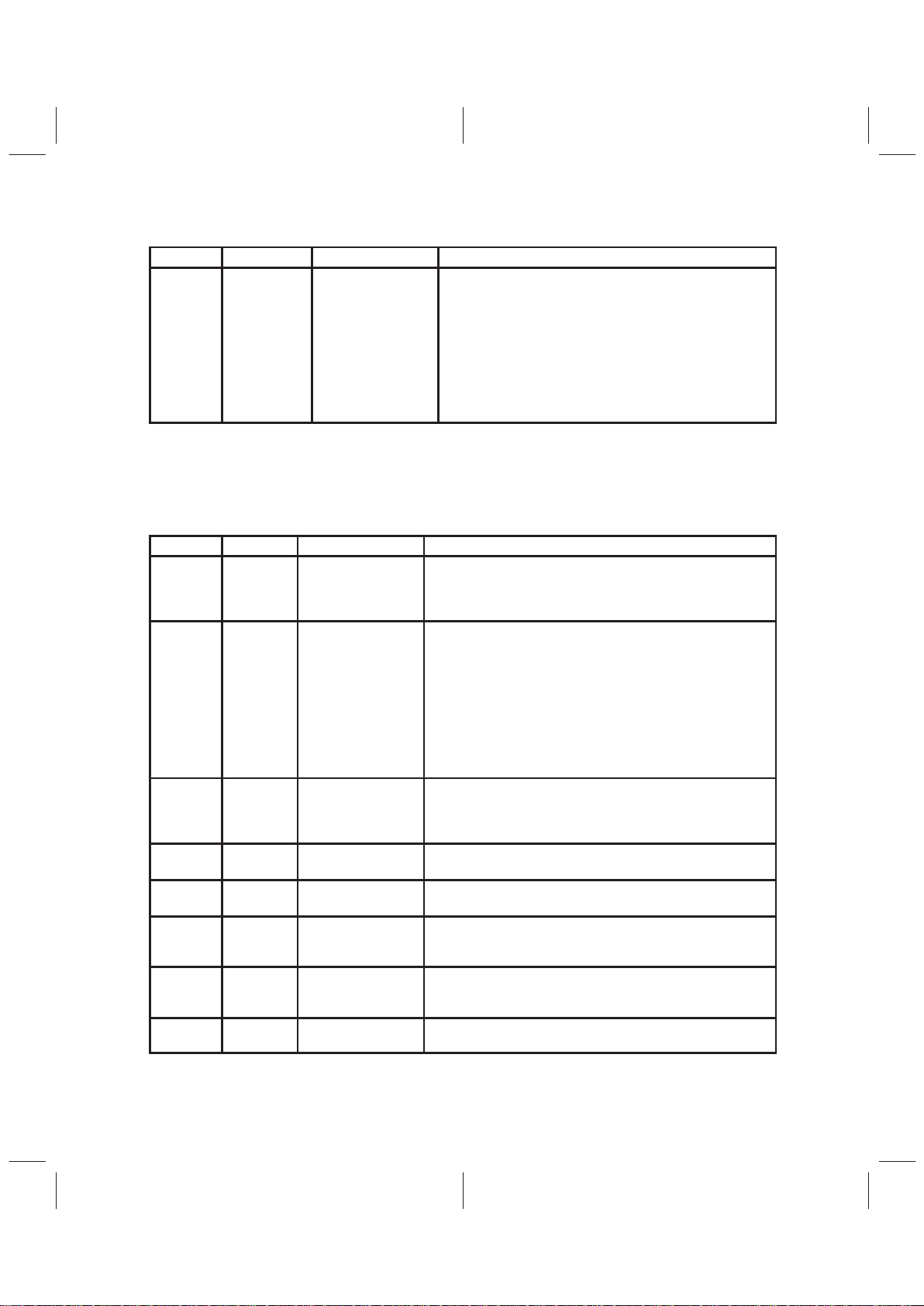

3.2 Internal Register Definitions

The TSB12LV01A internal registers control the operation of the TSB12LV01A. The bit definitions of the

internal registers are shown in Figure 3–1 and are described in subsections 3.2.1 through 3.2.12.

There are three modes to access the internal TSB12LV01A registers; normal mode, quick mode, and burst

mode. The registers from address 00h to 2Ch are accessed using normal mode as shown in Figures 6–2

and 6–3.

The registers 30h, 34h, 3Ch, and C0h may be accessed using quick mode reads as shown in Figure 6–5.

The registers 30h and 80h through 9Ch may be accessed using quick mode writes as shown in Figure 6–4.

NOTE:

The protocols for normal mode and quick mode are exactly the same. The only

difference being that quick mode simply returns CA

quicker.

The registers 84h, 8Ch, 94h, 9Ch, A0h, and B0h may be accessed using burst mode writes as shown in

Figure 6–6.

The register C0h may be accessed using burst mode reads as shown in Figure 6–7.

3–2

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 29 30 31

00h

Interrupt

CmdRst

ENSpRdPhy

TxlEn

ATAck

Int IdVal

PhInt RxSId

PhRRx

TxRdy

RxDta

PhRst

WrPhy

regRW

TxAEn

RxAEn

RstRx

RxlEn

AckCen

RstTx

ITBadF

ATBadF

SntRj

HdrEr

TCErr

CyDne

CySec

CySt

CyPnd

CyLst

CArbFl

IArbFl

Full

Empty

Full

Empty

Empty

cd

Control

PhyRgAd PhyRxAd

Version

Node

Address

Control

FIFO

Control

Cycle

Timer

Interrupt

Mask

Isoch Port

Number

Diagnostics

Phy Chip

Access

Reserved

Reserved

ATF Status

(R/W)

ITF Status

(Read Only)

Reserved

GRF Status

(Read Only)

Reserved

CyTEn

CyMas

CySrc

IRP1En

IRP2En

04h

08h

0Ch

10h

14h

18h

1Ch

20h

24h

28h

2Ch

30h

34h

38h

3Ch

40h

28

TrgEn

FhBad

7 Bits

IR Port1

Seconds Count

BsyCtrl

Bus Number

TAG2

TAG1

Rollover @ 8000

Cycle Count

13 Bits Rollover @ 3072 12 Bits

IR Port2

Node Number

Version

PhyRgData

Revision

Cycle Offset

PhyRxData

ATFSpaceCount

ITFSpaceCount

WriteCount

Root

AckV

3031-3042

RAl

RcvCyst

SIDCom

FrGp

ArbGp

CyTm0

MonTag

ClrGRF

Trigger Size ATFSize ITFSize

ClrITF

CLrATF

ConErr

AdrClr

RAMTest

AdrCounter

PacCom

GRFTotalCnt GRFSize

CmdRst

Int

PhInt

PhRRx

TxRdy

RxDta

PhRst

ITBadF

ATBadF

SntRj

HdrEr

TCErr

CyDne

CySec

CySt

CyPnd

CyLst

CArbFl

IArbFl

SIDCom

FrGp

ArbGp

CyTm0

ACKRCVACKRCV

NOTE A: All gray areas (bits) are reserved bits.

Figure 3–1. Internal Register Map

3–3

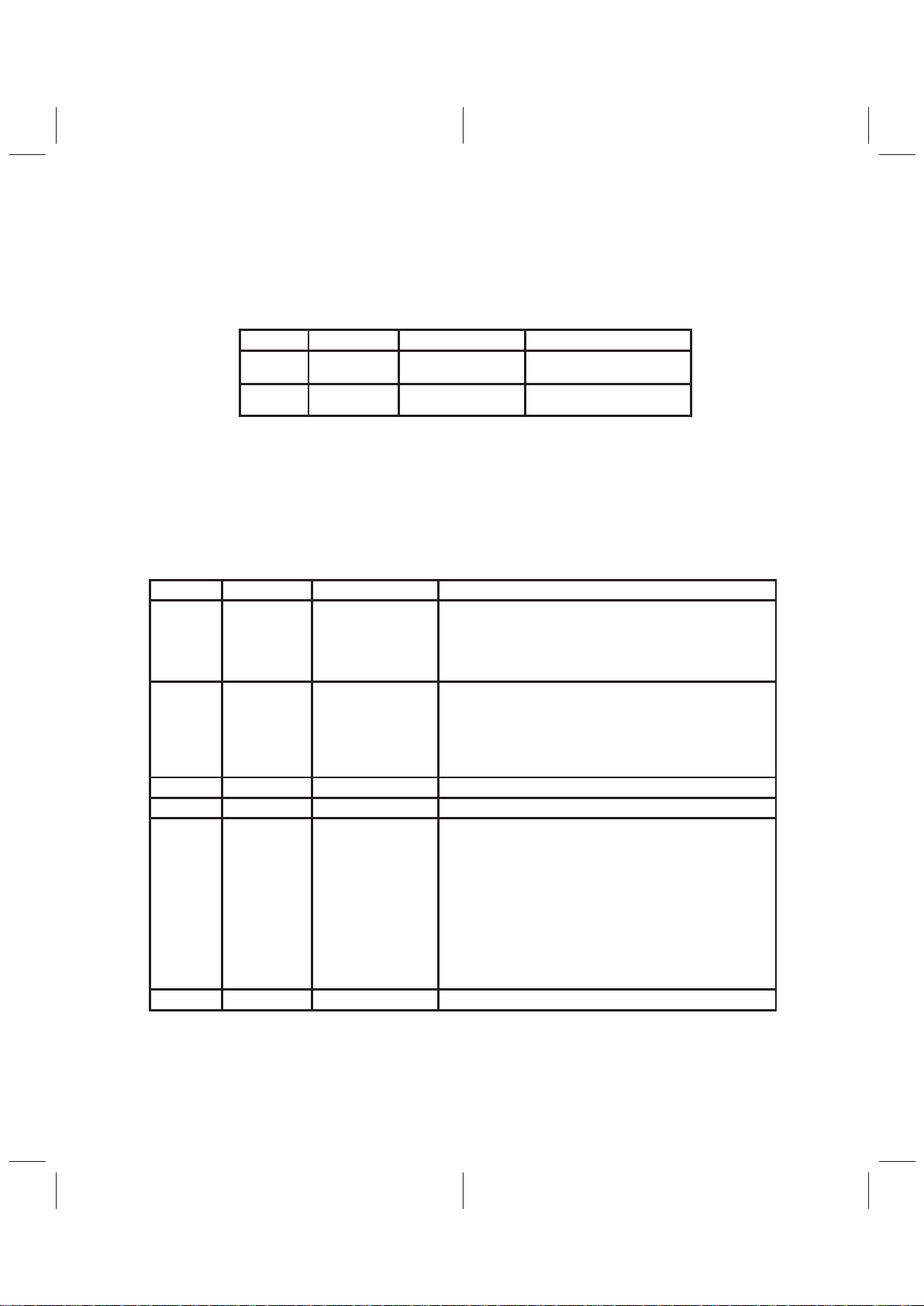

3.2.1 Version/Revision Register (@00h)

The version/revision register allows software to be written that supports multiple versions of the high-speed

serial-bus link-layer controllers. This register is at address 00h and is read only. The initial value is

3031_3042h.

Table 3–1. Version/Revision Register Field Descriptions

BITS ACRONYM FUNCTION NAME DESCRIPTION

0–15 Version Version Version of the

TSB12LV01A

16–31 Revision Revision Revision of the

TSB12LV01A

3.2.2 Node-Address/Transmitter Acknowledge Register (@04h)

The node-address/transmitter acknowledge register controls which packets are accepted/rejected, and it

presents the last acknowledge received for packets sent from the ATF. This register is at offset 04h. The

bus number and node number fields are read/write. The AT acknowledge (A T Ack) received is normally read

only. Setting the regRW bit in the diagnostic register makes these fields read/write. The initial value is

FFFF_0000h. The node number field and the root field are automatically updated by every PHY register 0

status transfer to the TSB12LV01A.

Table 3–2. Node-Address/Transmitter Acknowledge Register Field Descriptions

BITS ACRONYM FUNCTION NAME DESCRIPTION

0–9 BusNumber Bus number BusNumber is the 10-bit IEEE 1212 bus number that the

TSB12LV01A uses with the node number in the SOURCE

address for outgoing packets and to accept or reject incoming

packets. The TSB12LV01A always accepts packets with a bus

number equal to 3FFh.

10–15 NodeNumber Node number NodeNumber is the 6-bit node number that the TSB12LV01A

uses with the bus number in the source address for outgoing

packets and to accept or reject incoming packets. The

TSB12LV01A always accepts packets with the node address

equal to 3Fh. After bus reset, the node number is automatically

set to the node’s Physical_ID by a PHY register 0 transfer.

16

†

Root Root If Root =1 this node is root, read only

17–22

‡

Reserved Reserved Reserved

23–27

‡

ATAck Address transmitter

acknowledge

received

ATAck is the last acknowledge received by the transmitting

node in response to a packet sent from the asynchronous

transmit-FIFO.

ATAck=0_XXXX the low order 4 bits present normal ack code

receive from the receiving node.

ATAck=1_0000 an acknowledge timeout occured

ATAck=1_0011 ack packet error (ack parity error, or ack

pPending too long or ack pending too short)

28–30 Reserved Reserved Reserved

†

This bit is new to the TSB12LV01A and does not exist in the TSB12C01A.

‡

The bit number of these bits is different than the bit number listed for the TSB12C01A.

3–4

Table 3–2. Node-Address/Transmitter Acknowledge Register Field Descriptions (Continued)

BITS ACRONYM FUNCTION NAME DESCRIPTION

31

†

AckV Acknowledge valid Whenever an ack packet is received, AckV alid is set to 1. After

the node-address/transmitter acknowledge register is read,

AckValid is automatically reset to 0. This bit is also used to

indicate abitration failure. If a non-broadcast asynchronous

packet is in the ATF ready to transmit and a TxRdy interrupt

occurs, and AckValid is 0, this indicates no ack packet was

received and no ack time-out occured. The packet is still in the

ATF and the TSB12LV01A automatically arbitrates for the bus

again. Under normal conditions AckValid=0 means ATAck

contains last received ack code information.

†

This bit is new to the TSB12LV01A and does not exist in the TSB12C01A.

3.2.3 Control Register (@08h)

The control register dictates the basic operation of the TSB12LV01A. This register is at address 08h and

is read/write. The initial value is 0000_0000h.

Table 3–3. Control-Register Field Descriptions

BITS ACRONYM FUNCTION NAME DESCRIPTION

0 IdVal ID valid When IdVal is set, the TSB12LV01A accepts packets addressed

to the IEEE 1212 address set (Node Number) in the node-address

register. When IdVal is cleared, the TSB12LV01A accepts only

broadcast packets.

1 RxSId Received self-ID

packets

When RxSId is set, the self-identification packets generated by

phy chips during bus initialization are received and placed into the

GRF as a single packet. Each self-identification packet is

composed of two quadlets, where the second quadlet is the logical

inverse of the first. If ACK (4 bits) equals 1h, then the data is good.

If ACK equals Dh, then the data is wrong. When the RxSld is set

to 1, it also receives and places Link-on-packet and PHY

Configuration packet into the GRF. For Link-on-packet and PHY

Configuration packet only the first quadlet of each packet is stored

in the GRF.

2 BsyCtrl Busy control When this bit is set, this node sends an ack_busy_x acknowledge

in response to all received non-broadcast asynchronous packets.

When this bit is clear, this node sends ack_busy_x acknowledge

only if the GRF is full.

3

†

RAI Received all isochro-

nous packets

If RAI = 1 , RxIEn = 1, TSB12LV01A receives all Isochronous

packets and stores in the GRF.

4

†

RcvCySt Receive cycle start If RcvCySt = 1, it stores the received cycle start packet in the

GRF.

5 TxAEn Transmitter enable When TxAEn is cleared, the transmitter does not arbitrate or send

asynchronous packets. After bus reset, TxAEn is cleared since

the node number may have changed.

6 RxAEn Receiver enable When RxAEn is cleared, the receiver does not receive any

asynchronous packets. After bus reset, RxAEn is cleared since

the node number may have changed.

7

†

TxIEn Transmit

isochronous enable

When TxIEn is cleared, the transmitter does not arbitrate to send

isochronous packets

†

This bit is new to the TSB12LV01A and does not exist in the TSB12C01A.

Loading...

Loading...