D

Supports Provisions of IEEE 1394-1995

Standard for High Performance Serial Bus

D

Fully Interoperable With FireWire

Implementation of IEEE 1394-1995

D

Provides A Single Fully-Compliant Cable

Port at 100 Megabits per Second (Mbits/s)

D

Cable Port Monitors Line Conditions for

Active Connection to a Remote Node

D

Inactive Port Disabled to Save Power

D

Cable Inactivity Monitor Output and

Power-down Input Provided for Additional

Sleep-Mode Power Savings

D

Internal Bandgap Reference Provided for

Setting Stable Operating Bias Conditions

D

Logic Performs System Initialization and

Arbitration Functions

D

Encode and Decode Functions Included for

Data-Strobe Bit-Level Encoding

D

Incoming Data Resynchronized to Local

Clock

description

TSB11LV01

3-V 1-PORT IEEE 1394-1995 CABLE TRANSCEIVER/ARBITER

SLLS232B – MARCH 1996 – REVISED MA Y 1997

D

†

Data Interface to Link Layer Controller

(Link) Provided Through Two Parallel

Signal Lines at 50 Mbits/s

D

25-MHz Crystal Oscillator and PLL Provide

Transmit, Receive Data, and Link Layer

Controller Clocks at 50 MHz

D

Digital I/Os are 5 V tolerant

D

Node Power Class Information Signaling

for System Power Management

D

Cable Power Presence Monitoring

D

Cable Bias and Driver Termination Voltage

Supply

D

Single 3-V Supply Operation

D

Separate Multiple Package Terminals

Provided for Analog and Digital Supplies

and Grounds

D

High Performance 48-Pin TQFP (PT)

Package

The TSB1 1LV01 provides the analog transceiver functions needed to implement a single port node in a cable

based IEEE 1394-1995 network. The cable port incorporates two differential line transceivers. The transceivers

include circuitry to monitor the line conditions as needed for determining connection status, for initialization and

arbitration, and for packet reception and transmission. The TSB1 1L V01 is designed to interface with a link layer

controller, such as the TSB12C01A.

The TSB11LV01 requires an external 24.576-MHz crystal, which drives an internal phase-locked loop (PLL)

generating the required 98.304-MHz reference signal. The 98.304-MHz reference signal is internally divided

to provide the 49.152-MHz ±100 ppm system clock signals that control transmission of the outbound encoded

strobe and data information. The 49.152-MHz clock signal is also supplied to the associated link for

synchronization of the two chips and is used for resynchronization of the received data. The power-down

function, when enabled by asserting the PWRDN terminal high, stops operation of the PLL.

Data bits to be transmitted are received from the link on two parallel paths and are latched internally in the

TSB1 1L V01 in synchronization with the 49.152-MHz system clock. These bits are combined serially, encoded,

and transmitted at 98.304-Mbits/s as the outbound data-strobe information stream. During transmit, the

encoded data information is transmitted differentially on the TPB cable pair , and the encoded strobe information

is transmitted differentially on the TPA cable pair.

NOTE

In this document, phy is the physical layer and link is the link layer controller.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

†

Implements technology covered by one or more patents of Apple Computer, Incorporated and SGS Thomson, Limited.

FireWire is a trademark of Apple Computer, Incorporated.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Copyright 1997, Texas Instruments Incorporated

1

TSB11LV01

3-V 1-PORT IEEE 1394-1995 CABLE TRANSCEIVER/ARBITER

SLLS232B – MARCH 1996 – REVISED MA Y 1997

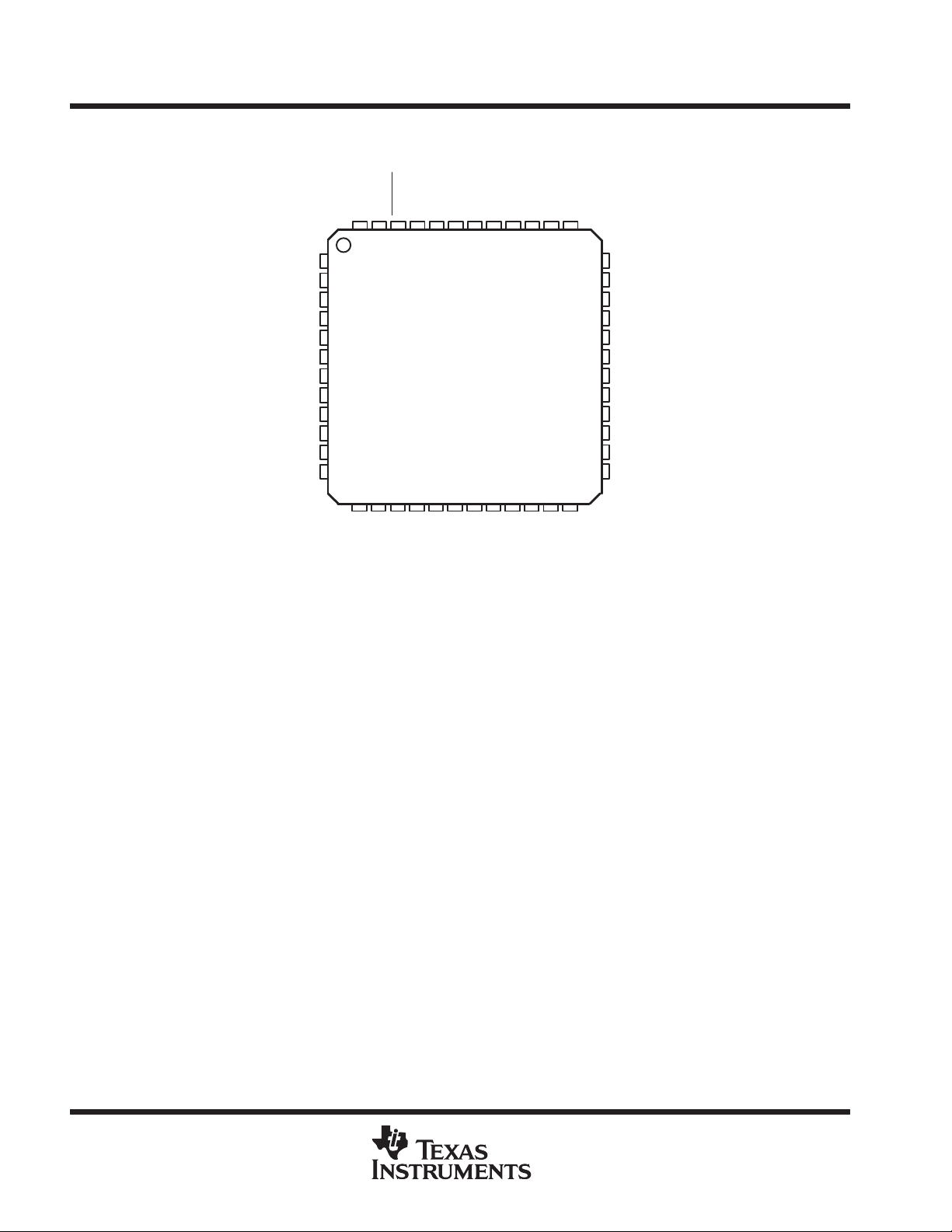

PT PACKAGE

(TOP VIEW)

CNA

LPS

C/LKON

PC0

PC1

PC2

LREQ

CTL0

CTL1

D0

D1

SYSCLK

TESTM1

TESTM2

47 46 45 44 4348 42

1

2

3

4

5

6

7

8

9

10

11

12

14 15

13

CC

DV

DGND

CC

RESET

DV

17 18 19 20

16

DGND

BIAS– 5 V

CC

AV

PWRDN

CC

DV

DGND

CC

PLL V

PLLFLT

40 39 3841

21

DGND

DGND

PLLGND

PLLGND

XI

22 23 24

CC

AV

AGND

AGND

XO

37

36

35

34

33

32

31

30

29

28

27

26

25

AGND

TPA+

TPA–

TPB+

TPB–

R0

R1

CPS

AV

CC

AV

CC

AGND

AGND

TPBIAS

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TSB11LV01

3-V 1-PORT IEEE 1394-1995 CABLE TRANSCEIVER/ARBITER

SLLS232B – MARCH 1996 – REVISED MA Y 1997

description (continued)

During packet reception the TP A and TPB transmitters of the cable port are disabled, and the receivers of the

port are enabled. The encoded data information is received on the TPA cable pair, and the encoded strobe

information is received on the TPB cable pair. The received data-strobe information is decoded to recover the

receive clock signal and the serial data bits. The serial data bits are split into two parallel streams,

resynchronized to the local system clock and sent to the associated link.

Both the TPA and TPB cable interfaces incorporate differential comparators to monitor the line states during

initialization and arbitration. The outputs of these comparators are used by the internal logic to determine the

arbitration status. In addition, the TPB channel monitors the incoming cable common-mode voltage for the

presence of the remotely supplied twisted-pair bias voltage. The presence or absence of this bias voltage is an

indication of cable connection status. The cable connection status signal is internally debounced in the

TSB11LV01. The debounced cable connection status signal initiates a bus reset. On a cable

disconnect-to-connect, the debounce delay is 335 ms. On a connect-to-disconnect there is minimal debounce.

The TSB11LV01 provides a 1.86-V nominal bias voltage for driver load termination. This bias voltage, when

seen through a cable by a remote receiver, indicates the presence of an active connection. The value of this

bias voltage has been chosen to allow interoperation between transceiver chips operating from either 5-V

nominal supplies or 3-V nominal supplies. This bias voltage source should be stabilized by using an external

filter capacitor of at least 1 µF.

The transmitter circuitry is disabled under the following conditions: powerdown, cable not active, reset, or

transmitter disable. The receiver circuitry is disabled during powerdown, cable not active, or receiver disable.

The twisted-pair bias voltage circuitry is disabled during the powerdown or reset conditions. The power-down

condition occurs when the PWRDN input is asserted high. The cable-not-active condition occurs

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

3

TSB11LV01

3-V 1-PORT IEEE 1394-1995 CABLE TRANSCEIVER/ARBITER

SLLS232B – MARCH 1996 – REVISED MA Y 1997

description (continued)

when the cable connection status indicates no cable is connected and is not debounced. The device reset

condition occurs when the RESET

conditions are determined from the internal logic.

The line drivers in the TSB1 1L V01 operate in the high-impedance current mode and are designed to work with

external 1 12-Ω line matching resistor networks. One network is provided at each end of each twisted-pair cable.

Each network is composed of a pair of series-connected 56-Ω resistors. The midpoint of the pair of resistors

that are directly connected to the twisted-pair A-package terminals is connected to the TPBIAS voltage terminal.

The midpoint of the pair of resistors that is directly connected to the twisted-pair B-package terminals is coupled

to ground through a parallel resistance-capacitance (R-C) network with the recommended value of 5 kΩ and

250 pF. The values of the external resistors are designed to meet the IEEE 1394-1995 standard specifications

when connected in parallel with the internal receiver circuits (see Figure 3).

An internal reference circuit (bandgap) provides stable bias voltages for the TSB11LV01 transceiver circuits.

The driver output current, along with other internal operating currents, is set by an external resistor. This resistor

is connected between terminals R1 and R0, and has a value of 6 kΩ ±0.5%.

Two of the package terminals set up various test conditions used in manufacturing. These terminals, TESTM1

and TESTM2, should be connected to V

Four package terminals are inputs to set four configuration status bits in the self-identification (Self-ID) packet.

These terminals are hardwired high or low as a function of the equipment design. PC0, PC1, and PC2

(corresponds to bits 21, 22, and 23 of the Self-ID packet) are three terminals that indicate either the need for

power from the cable or the ability to supply power to the cable. The fourth terminal, C/LKON (corresponds to

bit 20 of the Self-ID packet), indicates if a node is a contender for bus manager. C/LKON may also output a

6.114-MHz ±100 ppm signal, indicating reception of a link-on packet. See Table 4-29 of the IEEE 1394-1995

standard for additional details.

input terminal is asserted low. The transmitter disable and receiver disable

for normal operation.

CC

In order to operate with power supplies as low as 2.7 V , this device is restricted to applications that do not provide

cable power. See Note A in clause 4.2.2.2 of the IEEE 1394-1995 standard.

When the TSB11LV01 is used in applications with a 5-V link layer controller, such as the TSB12C01A, the

BIAS–5V terminal should be connected to the link layer controller 5-V supply . Otherwise, connect this terminal

to DV

A power-down terminal (PWRDN) is provided to allow most of the TSB1 1LV01 circuits to be powered down to

conserve energy in battery-driven applications. A cable status terminal (CNA) provides a high output when the

twisted-pair cable port is disconnected. This output is not debounced. The CNA output can determine when to

power the device down. In the power-down mode all circuitry is disabled except the CNA detection circuitry.

If the power supply of the TSB1 1L V01 is removed while the twisted-pair cables are connected, the TSB1 1L V01

transmitter and receiver circuitry has been designed to present a high-impedance signal to the cable and not

load the TPBIAS voltage on the other end of the cable.

CC

.

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

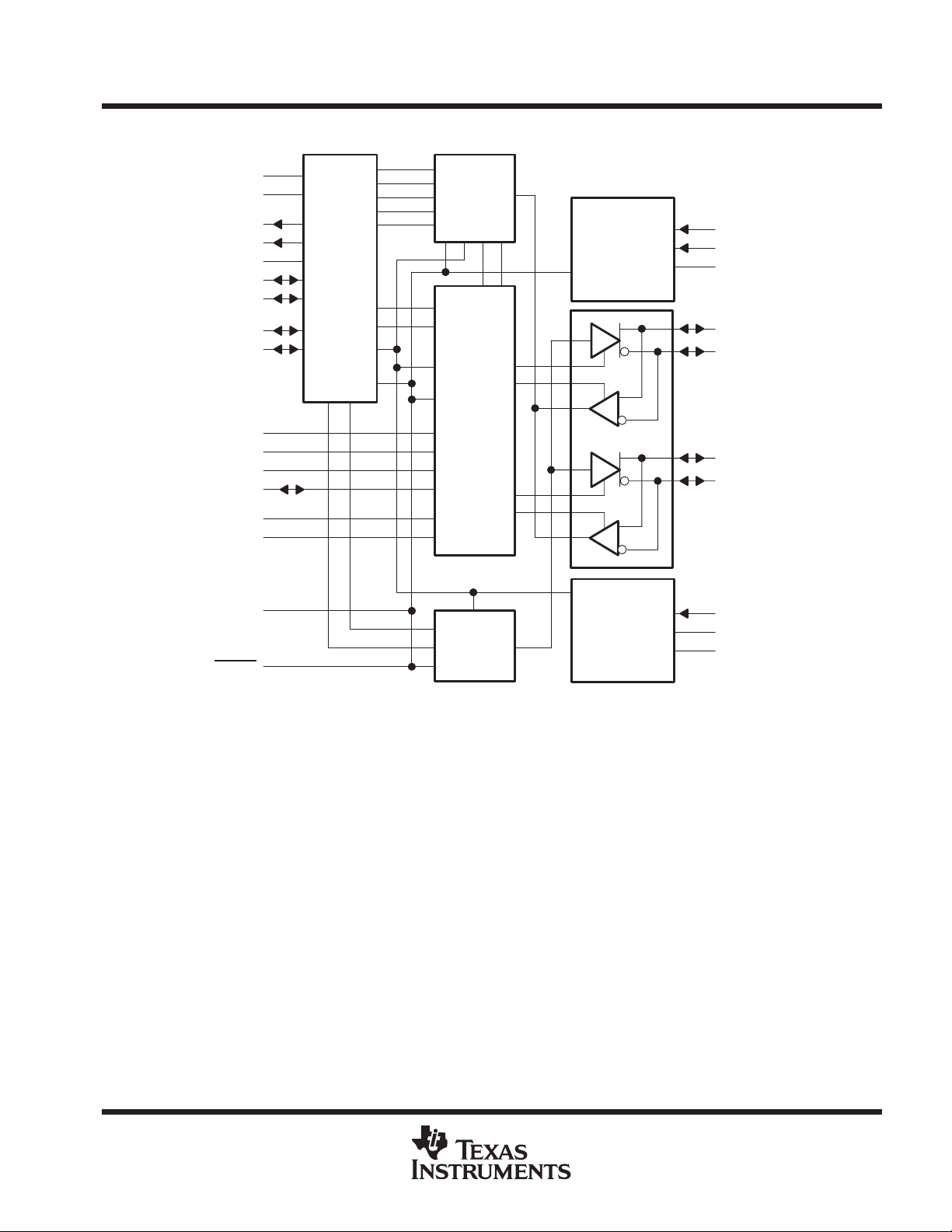

functional block diagram

TSB11LV01

3-V 1-PORT IEEE 1394-1995 CABLE TRANSCEIVER/ARBITER

SLLS232B – MARCH 1996 – REVISED MA Y 1997

CPS

LPS

CNA

SYSCLK

LREQ

CTL0

CTL1

D0

D1

PC0

PC1

PC2

C/LKON

TESTM1

TESTM2

PWRDN

RESET

Link

Interface

I/O

Received

Data

Decoder/

Retimer

Arbitration

and

Control

State

Machine

Logic

Transmit

Data

Encoder

Bias

Voltage

and

Current

Generator

Cable Port 1

Crystal

Oscillator,

PLL

System, and

Clock

Generator

R0

R1

TPBIAS

TPA+

TPA–

TPB+

TPB–

XI

XO

PLLFLT

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

5

TSB11LV01

I/O

TYPE

DESCRIPTION

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

3-V 1-PORT IEEE 1394-1995 CABLE TRANSCEIVER/ARBITER

SLLS232B – MARCH 1996 – REVISED MA Y 1997

Terminal Functions

TERMINAL

NAME NO.

AGND

ÁÁÁ

ÁÁÁ

AV

CC

ÁÁÁ

ÁÁÁ

ÁÁÁ

C/LKON

ÁÁÁ

ÁÁÁ

ÁÁÁ

ÁÁÁ

CNA

ÁÁÁ

CPS

ÁÁÁ

ÁÁÁ

ÁÁÁ

CTL0, CTL1

ÁÁÁ

D0, D1

DGND

ÁÁÁ

ÁÁÁ

DV

CC

ÁÁÁ

ÁÁÁ

ÁÁÁ

BIAS–5V

ÁÁÁ

ÁÁÁ

LPS

ÁÁÁ

ÁÁÁ

ÁÁÁ

ÁÁÁ

LREQ

ÁÁÁ

21, 23,

Á

24, 26,

27

Á

22, 28,

29, 44

Á

Á

Á

3

Á

Á

Á

Á

1

Á

30

Á

Á

Á

8, 9

Á

10, 11

13, 15,

Á

17, 19,

20,

Á

14, 18,

45

Á

Á

Á

16

Á

Á

2

Á

Á

Á

Á

7

Á

Á

Á

Á

Á

Á

I/O

Á

Á

Á

Á

O

Á

Á

Á

Á

I/O

Á

I/O

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

–

Supply

Á

Á

–

Supply

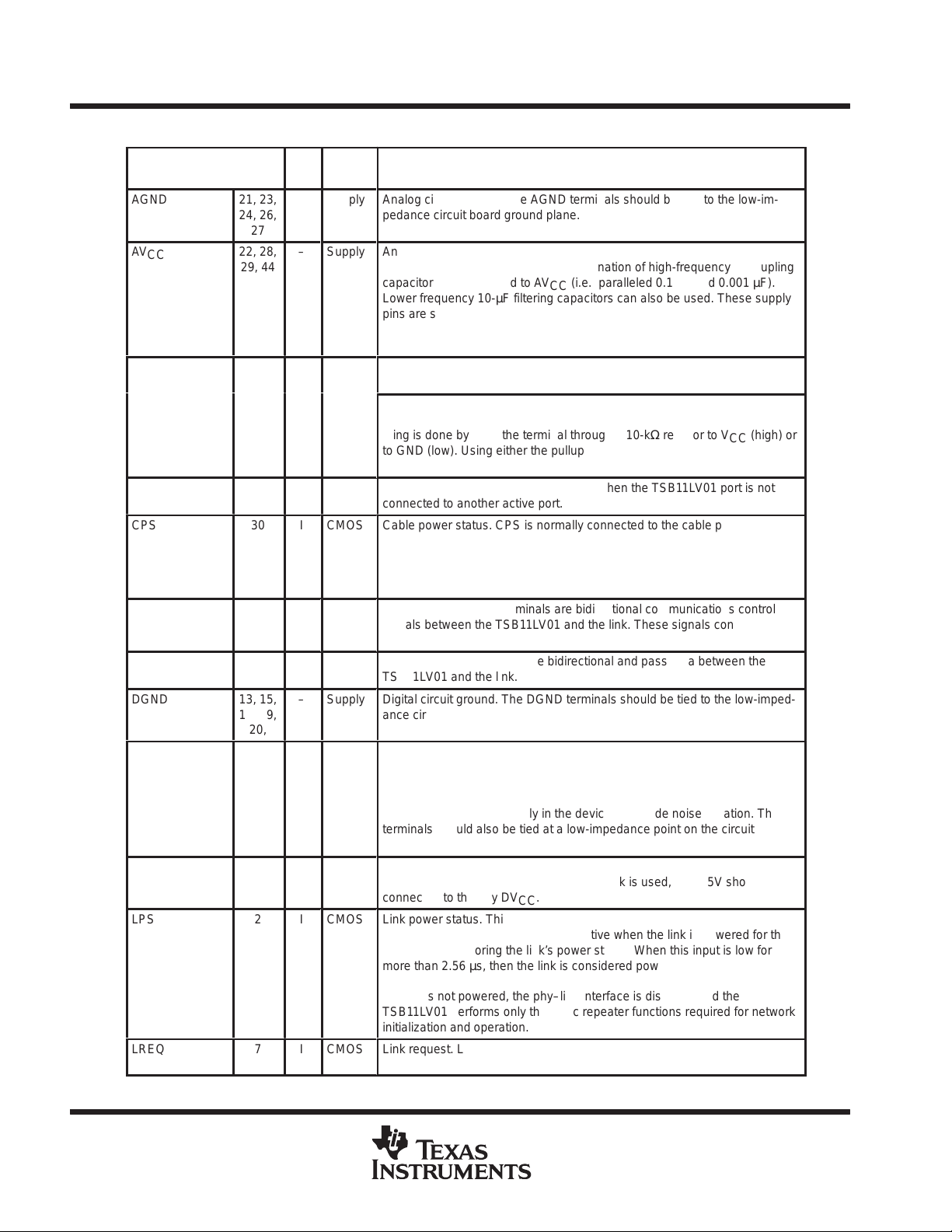

Analog circuit ground. The AGND terminals should be tied to the low-im-

БББББББББББББББББ

pedance circuit board ground plane.

БББББББББББББББББ

Analog circuit power. AVCC supplies power to the analog portion of the

device. It is recommended that a combination of high-frequency decoupling

Á

Á

Á

БББББББББББББББББ

capacitors be connected to AVCC (i.e., paralleled 0.1 µF and 0.001 µF).

Lower frequency 10-µF filtering capacitors can also be used. These supply

БББББББББББББББББ

pins are separated internally in the device to provide noise isolation. These

БББББББББББББББББ

terminals should also be tied at a low-impedance point on the circuit board.

Individual filtering networks for each is desired.

CMOS

Á

Bus manager capable (input). When set as an input, C/LKON is used to

БББББББББББББББББ

specify in the Self-ID packet that the node is bus manager capable.

Link-on (output). When set as an output, C/LKON indicates the reception of

Á

Á

Á

CMOS

Á

I

CMOS

Á

Á

Á

CMOS

a link-on message by asserting a 6.114-MHz signal. The bit value program-

БББББББББББББББББ

ming is done by tying the terminal through a 10-kΩ resistor to VCC (high) or

БББББББББББББББББ

to GND (low). Using either the pullup or pulldown resistor allows the LKON

output to override the input value when necessary.

БББББББББББББББББ

Cable not active. CNA is asserted high when the TSB11LV01 port is not

БББББББББББББББББ

connected to another active port.

Cable power status. CPS is normally connected to the cable power through

a 400-kΩ resistor. This circuit drives an internal comparator that detects the

БББББББББББББББББ

presence of cable power. This information is maintained in two internal

БББББББББББББББББ

registers and is available to the link by way of a register read. See the PhyLink Interface Application Note in the IEEE 1394-1995 standard.

БББББББББББББББББ

Control I/O. The CTL terminals are bidirectional communications control

signals between the TSB11LV01 and the link. These signals control the

Á

CMOS

БББББББББББББББББ

passage of information between the two devices.

Data I/O. The D terminals are bidirectional and pass data between the

TSB11LV01 and the link.

–

Supply

Á

Á

–

Supply

Digital circuit ground. The DGND terminals should be tied to the low-imped-

БББББББББББББББББ

ance circuit board ground plane.

БББББББББББББББББ

Digital circuit power. DVCC supplies power to the digital portion of the device. It is recommended that a combination of high-frequency decoupling

Á

Á

Á

capacitors be connected to DVCC (i.e., paralleled 0.1 µF and 0.001 µF).

БББББББББББББББББ

Lower frequency 10-µF filtering capacitors can also be used. These supply

БББББББББББББББББ

pins are separated internally in the device to provide noise isolation. These

terminals should also be tied at a low-impedance point on the circuit board.

БББББББББББББББББ

Individual filtering networks for each is desired.

–

Supply

Á

Á

I

CMOS

5 V bias. BIAS-5V should be connected to the link VCC supply when a 5-V

БББББББББББББББББ

link is connected to the phy. When a 3-V link is used, BIAS-5V should be

connected to the phy DVCC.

БББББББББББББББББ

Link power status. This terminal is connected to either the VCC supplying

the link or to a pulsed output that is active when the link is powered for the

Á

Á

Á

Á

I

CMOS

Á

purpose of monitoring the link’s power status. When this input is low for

БББББББББББББББББ

more than 2.56 µs, then the link is considered powered down. When this

БББББББББББББББББ

input is high for more than 80 ns, then the link is considered powered up. If

the link is not powered, the phy–link interface is disabled, and the

БББББББББББББББББ

TSB11LV01 performs only the basic repeater functions required for network

БББББББББББББББББ

initialization and operation.

Link request. LREQ is an input from the link that signals the TSB11LV01 of

a request to perform some service.

БББББББББББББББББ

6

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

I/O

TYPE

DESCRIPTION

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Board traces from these terminal should be ke t matched and as short as

Á

Á

Á

Á

Board traces from these terminal should be ke t matched and as short as

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

TSB11LV01

3-V 1-PORT IEEE 1394-1995 CABLE TRANSCEIVER/ARBITER

SLLS232B – MARCH 1996 – REVISED MA Y 1997

Terminal Functions (continued)

TERMINAL

NAME NO.

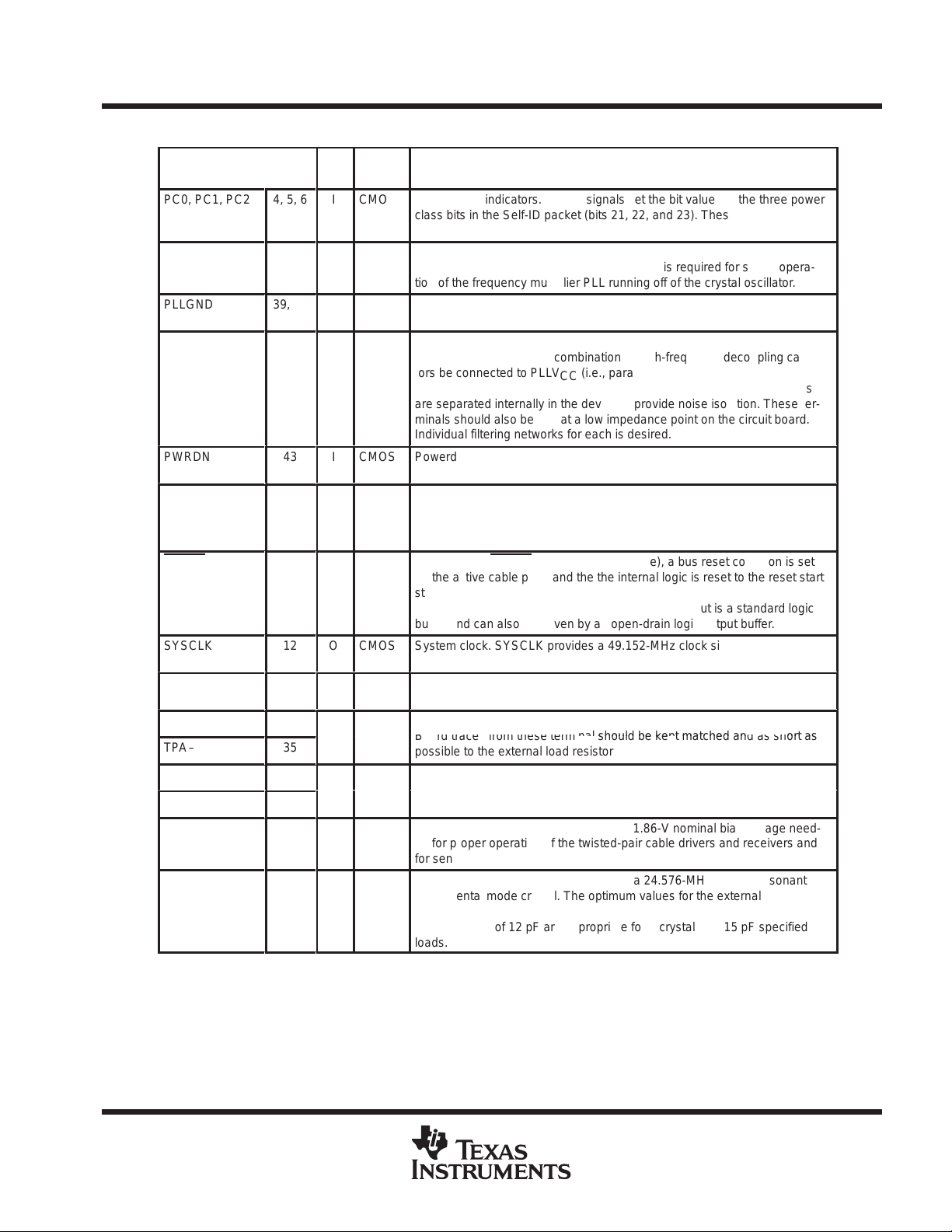

PC0, PC1, PC2

ÁÁÁÁ

ÁÁÁÁ

PLLFLT

ÁÁÁÁ

PLLGND

PLLV

CC

ÁÁÁÁ

ÁÁÁÁ

ÁÁÁÁ

ÁÁÁÁ

PWRDN

ÁÁÁÁ

R1, R0

ÁÁÁÁ

ÁÁÁÁ

RESET

ÁÁÁÁ

ÁÁÁÁ

SYSCLK

ÁÁÁÁ

TESTM1,

TESTM2

TPA+

TPA–

TPB+

ÁÁÁÁ

TPB–

TPBIAS

ÁÁÁÁ

XO, XI

ÁÁÁÁ

ÁÁÁÁ

4, 5, 6

Á

Á

42

Á

39, 40

41

Á

Á

Á

Á

43

Á

31, 32

Á

Á

46

Á

Á

12

Á

48, 47

36

35

34

Á

33

25

Á

37, 38

Á

Á

O

I/O

I/O

O

I

I

–

–

I

–

I

I

–

CMOS

ÁÁ

ÁÁ

CMOS

ÁÁ

Supply

Supply

ÁÁ

ÁÁ

ÁÁ

ÁÁ

CMOS

ÁÁ

Bias

ÁÁ

ÁÁ

CMOS

ÁÁ

ÁÁ

CMOS

ÁÁ

CMOS

Cable

Cable

ÁÁ

Cable

ÁÁ

Crystal

ÁÁ

ÁÁ

Power class indicators. the PC signals set the bit values of the three power

БББББББББББББББББ

class bits in the Self-ID packet (bits 21, 22, and 23). These bits can be programmed by tying the terminals to VCC (high) or to GND (low).

БББББББББББББББББ

PLL filter. PLLFLT is connected to a 0.1-µF capacitor and then to AGND to

complete the internal lag-lead filter. This filter is required for stable opera-

БББББББББББББББББ

tion of the frequency multiplier PLL running off of the crystal oscillator.

PLL circuit ground. The PLLGND terminals should be tied to the low-imped-

ance circuit board ground plane.

PLL circuit power. PLLVCC supplies power to the PLL portion of the device.

БББББББББББББББББ

It is recommended that a combination of high-frequency decoupling capacitors be connected to PLLVCC (i.e., paralleled 0.1 µF and 0.001 µF). Lower

БББББББББББББББББ

frequency 10-µF filtering capacitors can also be used. These supply pins

БББББББББББББББББ

are separated internally in the device to provide noise isolation. These terminals should also be tied at a low impedance point on the circuit board.

БББББББББББББББББ

Individual filtering networks for each is desired.

Powerdown. When asserted high, PWRDN turns off all internal circuitry

except the CNA monitor circuits that drive the CNA terminal.

БББББББББББББББББ

Current setting resistor. An internal reference voltage is applied to a resistor

connected between these two terminals to set the operating current and the

БББББББББББББББББ

cable driver output current. A low TCR 6 kΩ ±5% resistor should be used to

meet the IEEE 1394-1995 standard requirements for output voltage limits.

БББББББББББББББББ

Reset. When RESET is asserted low (active), a bus reset condition is set

on the active cable ports and the the internal logic is reset to the reset start

БББББББББББББББББ

state. An internal pullup resistor , which is connected to VCC, is provided so

only an external delay capacitor is required. This input is a standard logic

БББББББББББББББББ

buffer and can also be driven by an open-drain logic output buffer.

System clock. SYSCLK provides a 49.152-MHz clock signal, which is syn-

chronized with the data transfers, to the link.

БББББББББББББББББ

Test mode control. TESTM1 and TESTM2 are used during manufacturing

test and should be tied to VCC.

Port cable pair A. TPA is the port A connection to the twisted pair cable.

p

possible to the external load resistors and to the cable connector.

Port cable pair B. TPB is the port B connection to the twisted pair cable.

БББББББББББББББББ

p

possible to the external load resistors and to the cable connector.

Twisted-pair bias. TPBIAS provides the 1.86-V nominal bias voltage need-

ed for proper operation of the twisted-pair cable drivers and receivers and

БББББББББББББББББ

for sending a valid cable connection signal to the remote nodes.

Crystal oscillator. X0 and X1 connect to a 24.576-MHz parallel resonant

fundamental mode crystal. The optimum values for the external shunt ca-

БББББББББББББББББ

pacitors are dependent on the specifications of the crystal used. The sug-

БББББББББББББББББ

gested values of 12 pF are appropriate for a crystal with 15 pF specified

loads.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

7

Loading...

Loading...