Texas Instruments TLV5614IPWR, TLV5614IPW, TLV5614IDR, TLV5614CPWR, TLV5614ID Datasheet

...

2.7-V TO 5.5-V 12-BIT 3-µS QUADRUPLE DIGITAL-TO-ANALOG CONVERTERS

WITH POWER DOWN

SLAS188 – SEPTEMBER 1998

D

Four 12-Bit D/A Converters

D

Programmable Settling Time of Either 3 µs

or 9 µs Typ

D

TMS320, (Q)SPI, and Microwire Compatible

Serial Interface

D

Internal Power-On Reset

D

Low Power Consumption:

8 mW, Slow Mode – 5-V Supply

3.6 mW, Slow Mode – 3-V Supply

D

Reference Input Buffer

D

Voltage Output Range ...2× the Reference

Input Voltage

D

Monotonic Over Temperature

description

The TL V5614 is a quadruple 12-bit voltage output

digital-to-analog converter (DAC) with a flexible

4-wire serial interface. The 4-wire serial interface

allows glueless interface to TMS320, SPI, QSPI,

and Microwire serial ports. The TLV5614 is

programmed with a 16-bit serial word comprised

of a DAC address, individual DAC control bits, and

a 12-bit DAC value. The device has provision for

two supplies: one digital supply for the serial

interface (via pins DV

the DACs, reference buffers, and output buffers (via pins A VDD and AGND). Each supply is independent of the

other, and can be any value between 2.7 V and 5.5 V. The dual supplies allow a typical application where the

DAC will be controlled via a microprocessor operating on a 3 V supply (also used on pins DVDD and DGND),

with the DACs operating on a 5 V supply. Of course, the digital and anlog supplies can be tied together.

and DGND), and one for

DD

D

Dual 2.7-V to 5.5-V Supply (Separate Digital

and Analog Supplies)

D

Hardware Power Down (10 nA)

D

Software Power Down (10 nA)

D

Simultaneous Update

applications

D

Battery Powered Test Instruments

D

Digital Offset and Gain Adjustment

D

Industrial Process Controls

D

Machine and Motion Control Devices

D

Communications

D

Arbitrary Waveform Generation

D OR PW PACKAGE

(TOP VIEW)

DV

DD

PD

LDAC

DIN

SCLK

CS

FS

DGND

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

AV

DD

REFINAB

OUTA

OUTB

OUTC

OUTD

REFINCD

AGND

TLV5614

The resistor string output voltage is buffered by a x2 gain rail-to-rail output buffer . The buffer features a Class AB

output stage to improve stability and reduce settling time. A rail-to-rail output stage and a power-down mode

makes it ideal for single voltage, battery based applications. The settling time of the DAC is programmable to

allow the designer to optimize speed versus power dissipation. The settling time is chosen by the control bits

within the 16-bit serial input string. A high-impedance buffer is integrated on the REFINAB and REFINCD

terminals to reduce the need for a low source impedance drive to the terminal. REFINAB and REFINCD allow

DACs A and B to have a different reference voltage then DACs C and D.

The TLC5614 is implemented with a CMOS process and is available in a 16-terminal SOIC package. The

TL V5614C is characterized for operation from 0°C to 70°C. The TLV5614I is characterized for operation from

–40°C to 85°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Copyright 1998, Texas Instruments Incorporated

1

TLV5614

2.7-V TO 5.5-V 12-BIT 3-µS QUADRUPLE DIGITAL-TO-ANALOG CONVERTERS

WITH POWER DOWN

SLAS188 – SEPTEMBER 1998

AVAILABLE OPTIONS

PACKAGE

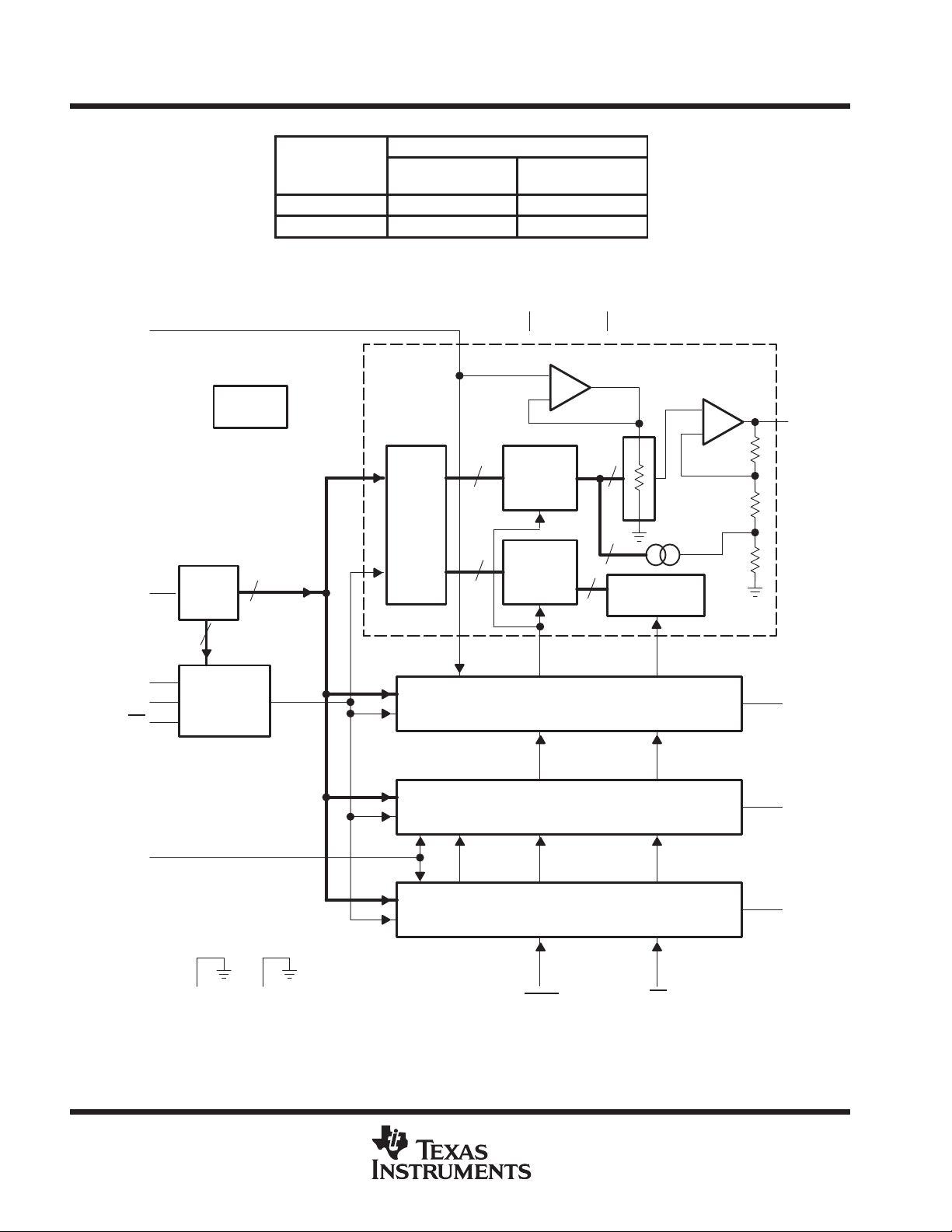

functional block diagram

T

A

0°C to 70°C TLV5614CD TLV5614CPW

–40°C to 85°C TLV5614ID TLV5614IPW

SOIC

(D)

TSSOP

(PW)

REFINAB

DIN

FS

SCLK

CS

AV

DD

15 16 1

+

_

12-Bit

DAC

Latch

2-Bit

Control

Data

Latch

DAC B

Serial

4

Input

Register

7

DAC Select/

5

6

Power-On

Reset

2

Control

Logic

14

14-Bit

Data

and

Control

Register

12

2

DV

DD

10

2

2

Power-Down/

Speed Control

DAC A

+

_

13

14

OUTA

OUTB

REFINCD

2

10

9

AGND

8

DGND

DAC C

DAC D

32

LDAC

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

PD

12

11

OUTC

OUTD

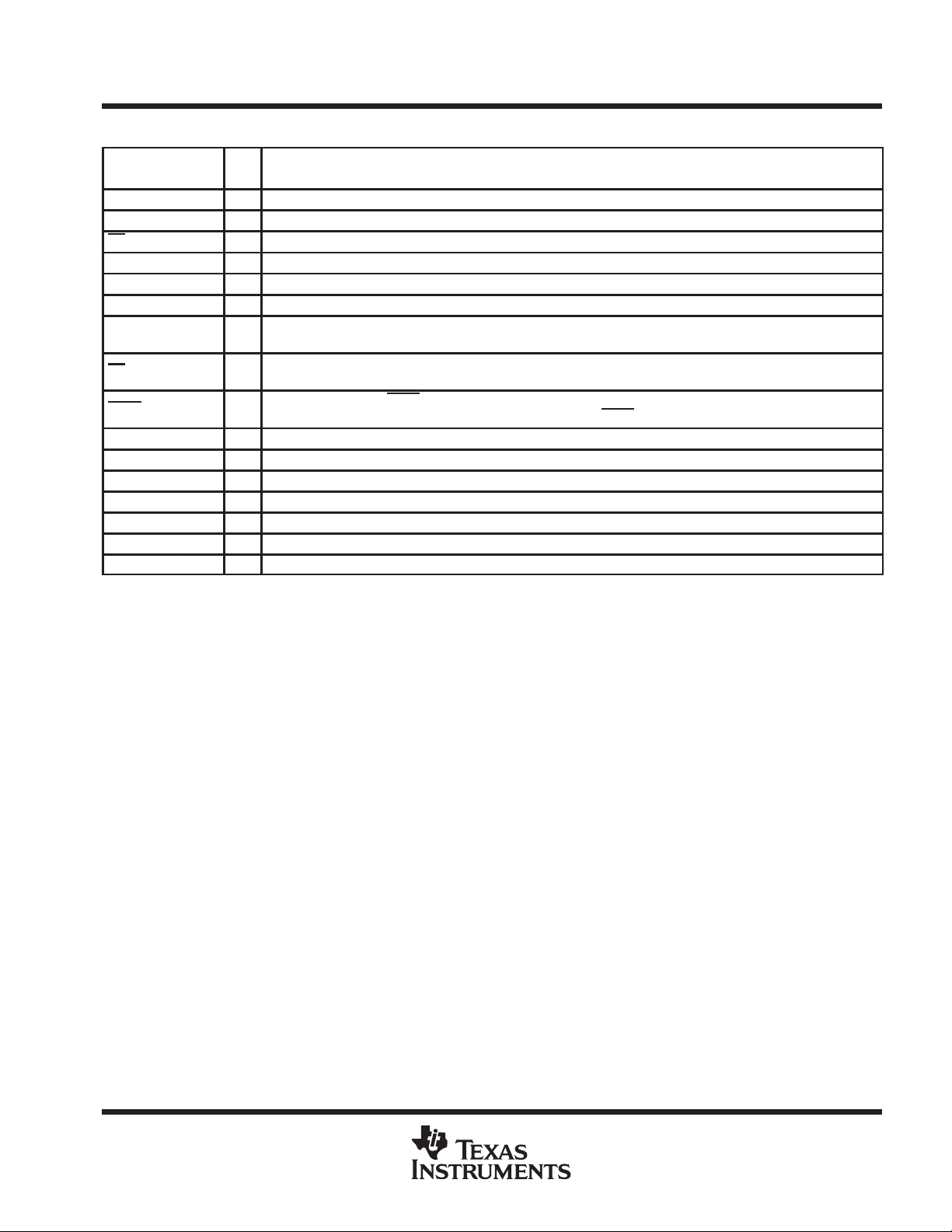

I/O

DESCRIPTION

2.7-V TO 5.5-V 12-BIT 3-µS QUADRUPLE DIGITAL-TO-ANALOG CONVERTERS

Terminal Functions

TERMINAL

NAME NO.

AGND 9 Analog ground

AV

DD

CS 6 I Chip select. This terminal is active low.

DGND 8 Digital ground

DIN 4 I Serial data input

DV

DD

FS

PD

LDAC

REFINAB 15 I Voltage reference input for DACs A and B.

REFINCD 10 I Voltage reference input for DACs C and D.

SCLK 5 I Serial Clock input

OUTA 14 O DACA output

OUTB 13 O DACB output

OUTC 12 O DACC output

OUTD 11 O DACD output

16 Analog supply

1 Digital supply

7 I Frame sync input. The falling edge of the frame sync pulse indicates the start of a serial data frame shifted out to

the TLV5614.

2 I Power down pin. Powers down all DACs (overriding their individual power down settings), and all output stages.

This terminal is active low.

3 I Load DAC. When the LDAC signal is high, no DAC output updates occur when the input digital data is read into

the serial interface. The DAC outputs are only updated when LDAC

TLV5614

WITH POWER DOWN

SLAS188 – SEPTEMBER 1998

is low.

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

Supply voltage, (DV

Supply voltage difference, (AVDD to DVDD) –2.8 V to 2.8 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Digital input voltage range –0.3 V to DVDD + 0.3 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Reference input voltage range –0.3 V to AVDD + 0.3 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating free-air temperature range, T

Storage temperature range, T

Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds 260°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

†

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

, AVDD to GND) 7 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DD

: TLV5614C 0°C to 70°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A

TLV5614I –40°C to 85°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

–65°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

stg

†

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

3

TLV5614

Suppl

oltage, AV

DV

V

Reference voltage, V

REFINAB, REFINCD terminal

V

Operating free-air temperature

°C

PSRR

Power supply rejection ratio

See Notes 8 and 9

2.7-V TO 5.5-V 12-BIT 3-µS QUADRUPLE DIGITAL-TO-ANALOG CONVERTERS

WITH POWER DOWN

SLAS188 – SEPTEMBER 1998

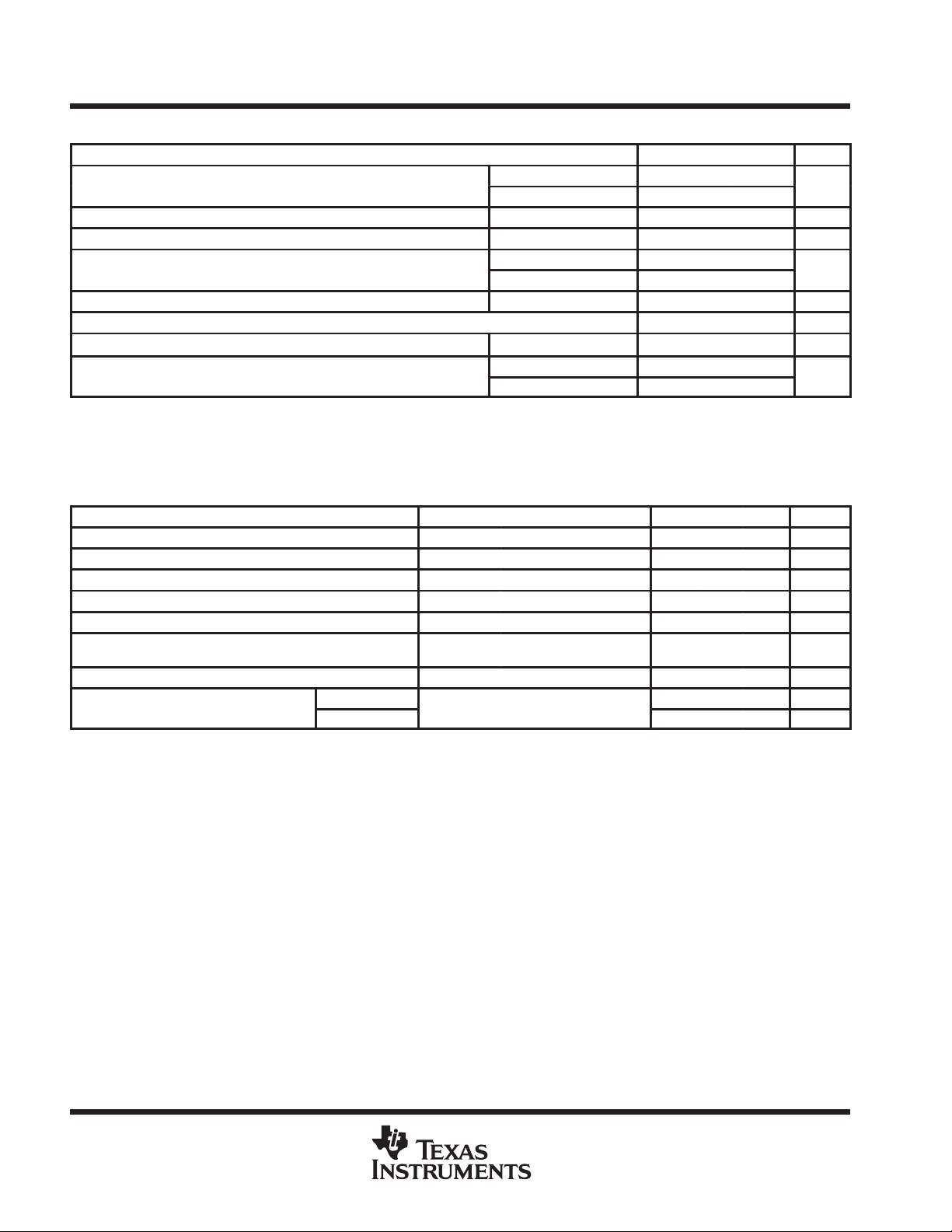

recommended operating conditions

MIN NOM MAX UNIT

pp

y v

High-level digital input, V

Low-level digital input, V

Load resistance, R

Load capacitance, C

Serial clock rate, SCLK 20 MHz

p

NOTE 1: Voltages greater than AVDD/2 will cause output saturation for large DAC codes.

DD

L

L

ref

,

DD

IH

IL

to

p

electrical characteristics over recommended operating free-air temperature range, supply

voltages, and reference voltages (unless otherwise noted)

5-V supply 4.5 5 5.5

3-V supply 2.7 3 3.3

DVDD = 2.7 V to 5.5 V 2 V

DVDD = 2.7 V to 5.5 V 0.8 V

5-V supply, See Note 1 0 2.048 VDD–1.5

3-V supply, See Note 1 0 1.024 VDD–1.5

2 10 kΩ

100 pF

TLV5614C 0 70

TLV5614I –40 85

°

static DAC specifications

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

Resolution 12 bits

Integral nonlinearity (INL), end point adjusted See Note 2 ±1.5 ±4 LSB

Differential nonlinearity (DNL) See Note 3 ±0.5 ±1 LSB

E

ZS

E

G

NOTES: 2. The relative accuracy or integral nonlinearity (INL) sometimes referred to as linearity error , is the maximum deviation of the output

Zero scale error (offset error at zero scale) See Note 4 ±12 mV

Zero scale error temperature coefficient See Note 5 10 ppm/ °C

min

% of FS

voltage

).

Gain error See Note 6 ±0.6

Gain error temperature coefficient See Note 7 10 ppm/ °C

pp

from the line between zero and full scale excluding the effects of zero code and full-scale errors.

3. The differential nonlinearity (DNL) sometimes referred to as differential error, is the difference between the measured and ideal

1 LSB amplitude change of any two adjacent codes. Monotonic means the output voltage changes in the same direction (or remains

constant) as a change in the digital input code.

4. Zero-scale error is the deviation from zero voltage output when the digital input code is zero.

5. Zero-scale-error temperature coefficient is given by: EZS TC = [EZS (T

6. Gain error is the deviation from the ideal output (2 V

7. Gain temperature coefficient is given by: EG TC = [EG(T

8. Zero-scale-error rejection ratio (EZS–RR) is measured by varying the AVDD from 5 ± 0.5 V and 3 ± 0.5 V dc, and measuring the

proportion of this signal imposed on the zero-code output voltage.

9. Full-scale rejection ratio (EG-RR) is measured by varying the AVDD from 5 ± 0.5 V and 3 ±0.5 V dc and measuring the proportion

of this signal imposed on the full-scale output voltage after subtracting the zero scale change.

Zero scale

Full scale

) – EZS (T

– 1 LSB) with an output load of 10 kΩ excluding the effects of the zero-error.

ref

max

) – EG (T

max

min

)]/V

× 106/(T

ref

min

)]/V

max

ref

– T

–80 dB

–80 dB

× 106/(T

min

max

).

– T

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Reference input bandwidth

REFIN

V

1.024 V dc large signal

MH

No load, Clock

mA

IDDPower supply current

No load, Clock

mA

TLV5614

2.7-V TO 5.5-V 12-BIT 3-µS QUADRUPLE DIGITAL-TO-ANALOG CONVERTERS

WITH POWER DOWN

SLAS188 – SEPTEMBER 1998

electrical characteristics over recommended operating free-air temperature range, supply

voltages, and reference voltages (unless otherwise noted) (continued)

individual DAC output specifications

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

V

O

reference inputs (REFINAB, REFINCD)

V

I

R

I

C

I

NOTES: 10. Reference input voltages greater than VDD/2 will cause output saturation for large DAC codes.

Voltage output range RL = 10 kΩ 0 AVDD–0.4 V

Output load regulation accuracy RL = 2 kΩ vs 10 kΩ 0.1 0.25

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

Input voltage range See Note 10 0 AVDD–1.5 V

Input resistance 10 MΩ

Input capacitance 5 pF

Reference feed through

p

11. Reference feedthrough is measured at the DAC output with an input code = 000 hex and a V

input = 1.024 Vdc + 1 Vpp at 1 kHz.

REFIN = 1 Vpp at 1 kHz + 1.024 V dc

(see Note 11)

= 0.2

pp

+

–75 dB

Slow 0.5

Fast 1

ref (REFINAB or REFINCD)

% of FS

voltage

z

digital inputs (DIN, CS, LDAC, PD)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

I

IH

I

IL

C

I

High-level digital input current VI = V

Low-level digital input current VI = 0 V ±1 µA

Input capacitance 3 pF

power supply

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

pp

Power down supply current (see Figure 12) 10 nA

DD

5-V supply,

running,

All inputs 0 V or V

3-V supply,

running,

All inputs 0 V or DV

DD

DD

±1 µA

Slow 1.6 2.4

Fast 3.8 5.6

Slow 1.2 1.8

Fast 3.2 4.8

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

5

TLV5614

SR

Output slew rate

V

10% to 90%

tsOutput settling time

,

L

,

s

t

Output settling time, code to code

,

L

,

s

S,

f

s

400 KSPS

C

L

100 pF

R

L

2.7-V TO 5.5-V 12-BIT 3-µS QUADRUPLE DIGITAL-TO-ANALOG CONVERTERS

WITH POWER DOWN

SLAS188 – SEPTEMBER 1998

electrical characteristics over recommended operating free-air temperature range, supply

voltages, and reference voltages (unless otherwise noted) (continued)

analog output dynamic performance

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

p

p

s(c)

SNR Signal-to-noise ratio

S/(N+D) Signal to noise + distortion

THD Total harmonic Distortion

SFDR Spurious free dynamic range

NOTES: 12. Settling time is the time for the output signal to remain within ±0.5 LSB of the final measured value for a digital input code change

p

Glitch energy Code transition from 7FF to 800 10 nV-sec

ofFFF hex to 080 hex for 080 hex to FFF hex.

13. Settling time is the time for the output signal to remain within ±0.5 LSB of the final measured value for a digital input code change

of one count.

14. Limits are ensured by design and characterization, but are not production tested.

CL = 100 pF, RL = 10 kΩ,

=

O

V

= 2.048 V, 1024 V

ref

To ± 0.5 LSB, C

RL = 10 kΩ, See Notes 12 and 14

To ± 0.5 LSB, C

RL = 10 kΩ, See Note 15

Sinewave generated by DAC,

Reference voltage = 1.024 at 3 V and 2.048 at 5 V ,

= 400 KSP

=

f

f

= 1.1 kHz sinewave,

OUT

=

BW = 20 kHz

p

,

,

,

= 100 pF,

= 100 pF,

= 10 kΩ,

Fast 5 V/µs

Slow 1 V/µs

Fast 3 5.5

Slow 9 20

Fast 1

Slow 2

74

66

–68

70

µ

µ

dB

6

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TLV5614

2.7-V TO 5.5-V 12-BIT 3-µS QUADRUPLE DIGITAL-TO-ANALOG CONVERTERS

WITH POWER DOWN

SLAS188 – SEPTEMBER 1998

electrical characteristics over recommended operating free-air temperature range, supply

voltages, and reference voltages (unless otherwise noted) (continued)

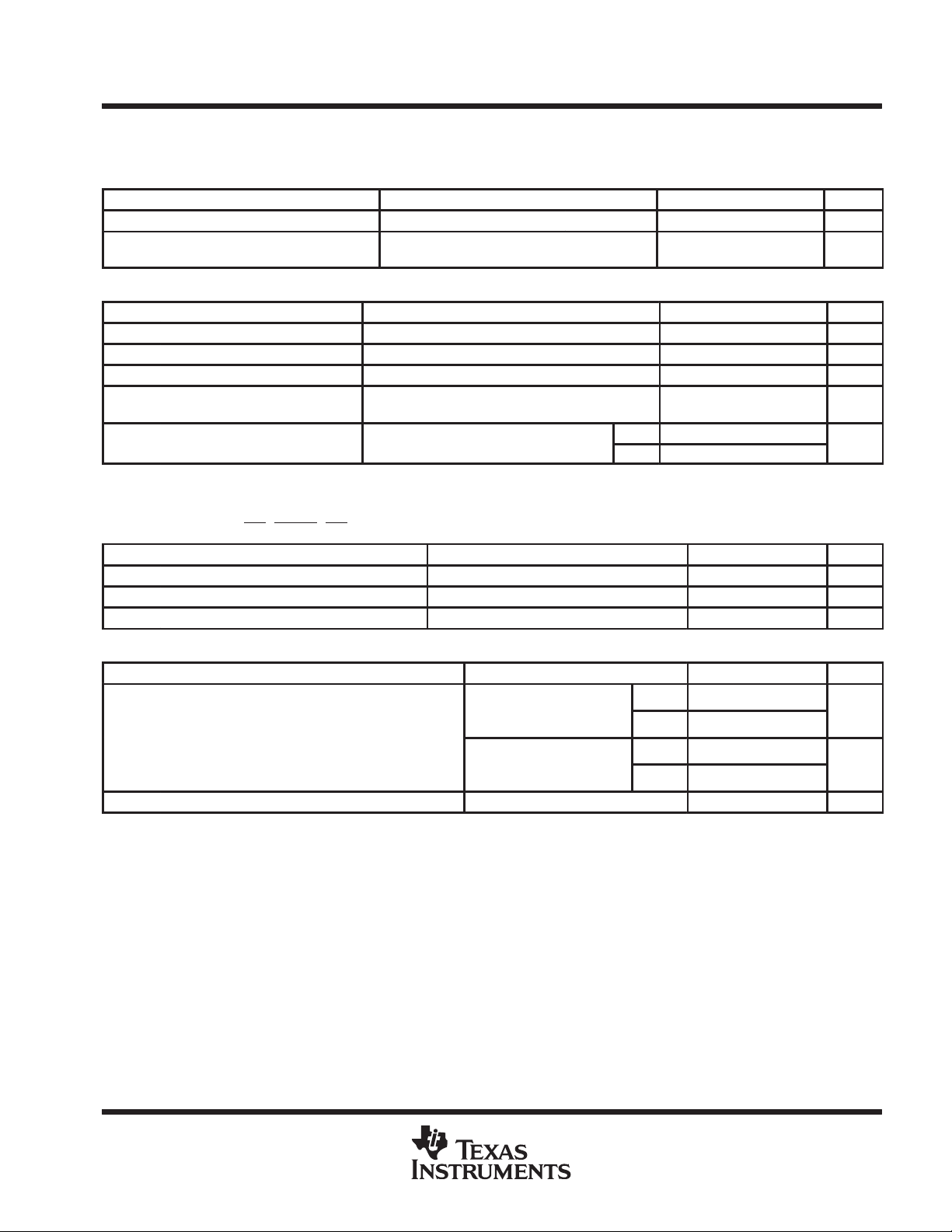

digital input timing requirements

MIN NOM MAX UNIT

t

su(CS–FS)

t

su(FS–CK)

t

su(C16–FS)

t

su(C16–CS)

t

wH

t

wL

t

su(D)

t

h(D)

t

wH(FS)

Setup time, CS low before FS↓ 10 ns

Setup time, FS low before first negative SCLK edge 8 ns

Setup time, sixteenth negative edge after FS low on which bit D0 is sampled before rising

edge of FS

Setup time, sixteenth positive SCLK edge (first positive after D0 is sampled) before CS rising

edge. If FS is used instead of the sixteenth positive edge to update the DAC, then the setup

time is between the FS rising edge and CS

Pulse duration, SCLK high 25 ns

Pulse duration, SCLK low 25 ns

Setup time, data ready before SCLK falling edge 8 ns

Hold time, data held valid after SCLK falling edge 5 ns

Pulse duration, FS high 20 ns

rising edge.

10 ns

10 ns

SCLK

DIN

CS

FS

t

su(D)

PARAMETER MEASUREMENT INFORMATION

t

wL

123451516

t

h(D)

D15 D14 D13 D12 D1 D0

t

su(FS-CK)

t

su(CS-FS)

t

wH(FS)

Figure 1. Timing Diagram

t

wH

t

t

su(C16-FS)

su(C16-CS)

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

7

TLV5614

2.7-V TO 5.5-V 12-BIT 3-µS QUADRUPLE DIGITAL-TO-ANALOG CONVERTERS

WITH POWER DOWN

SLAS188 – SEPTEMBER 1998

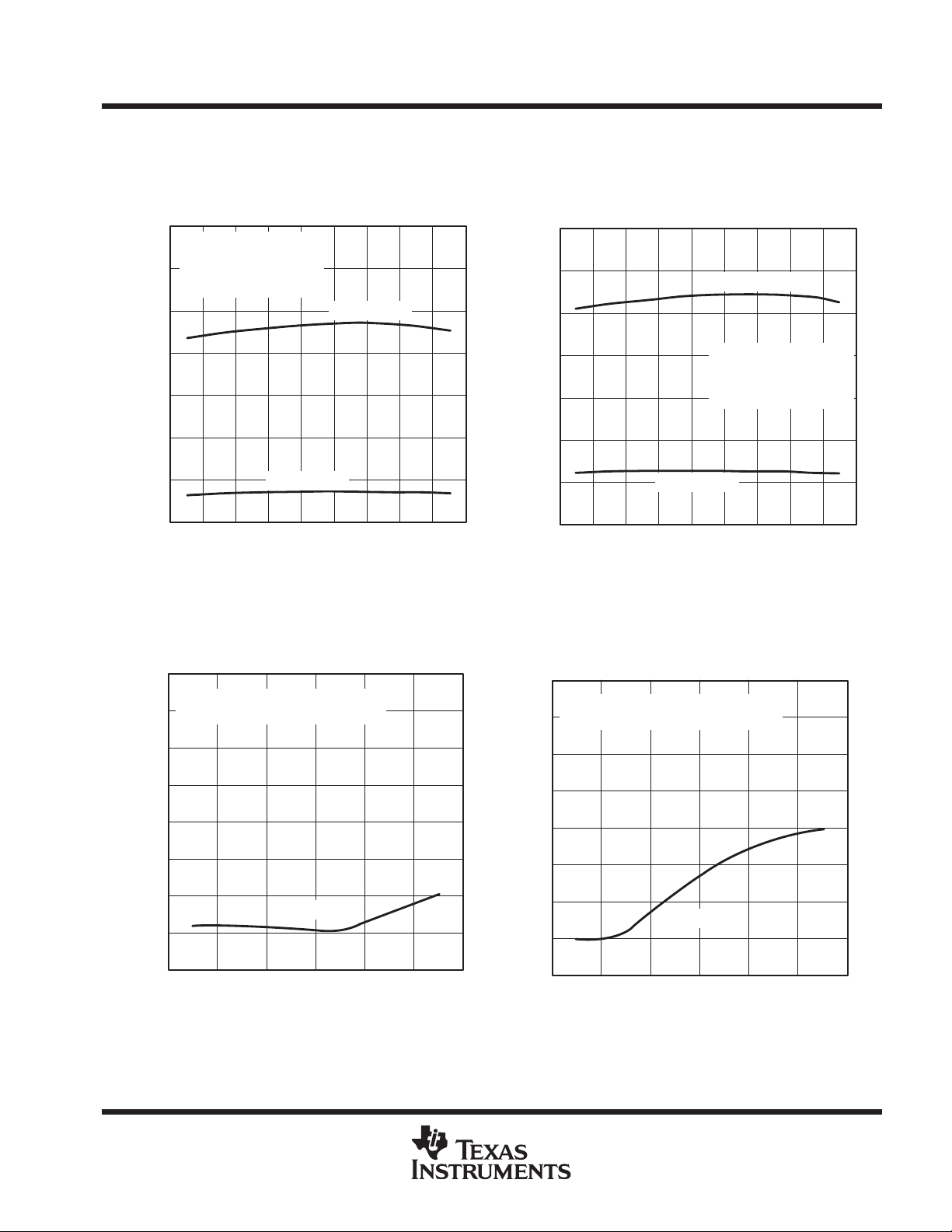

TYPICAL CHARACTERISTICS

0.2

0.18

0.16

0.14

0.12

0.10

– Output – V

0.08

O

V

0.06

0.04

0.02

0

4.01

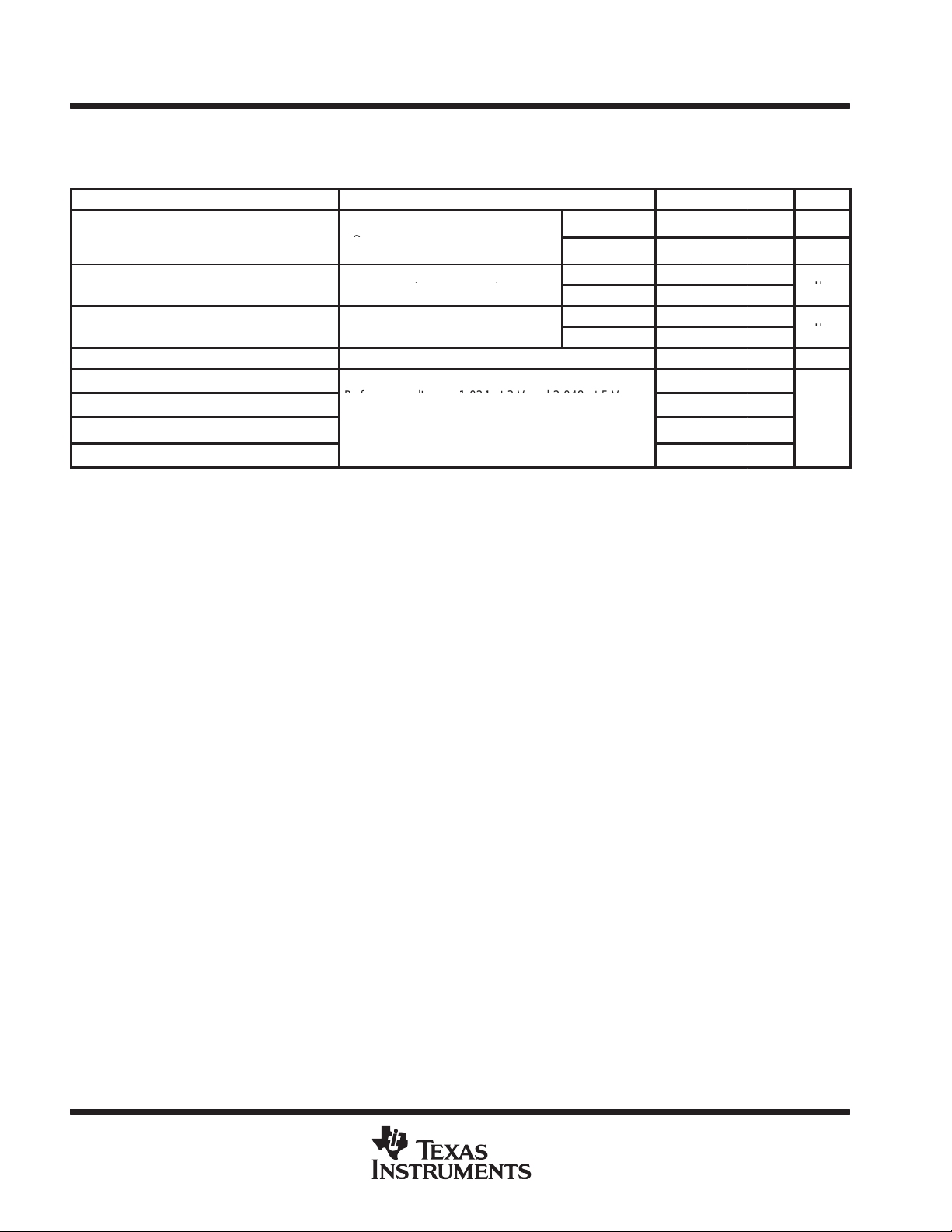

LOAD REGULATION

VDD = 3 V,

V

= 1 V,

ref

VO = Full Scale

3 V Slow Mode, Sink

3 V Fast Mode, Sink

0 0.01 0.02 0.05 0.1 0.2 0.5

Load Current – mA

Figure 2

LOAD REGULATION

5 V Slow Mode, Source

12

0.35

VDD = 5 V,

V

0.30

VO = Full Scale

0.25

0.20

– Output – V

0.15

O

V

0.10

0.05

0

0 0.02 0.04 0.1 0.2 0.4 1

2.001

2.001

ref

LOAD REGULATION

= 2 V,

5 V Slow Mode, Sink

5 V Fast Mode, Sink

24

Load Current – mA

Figure 3

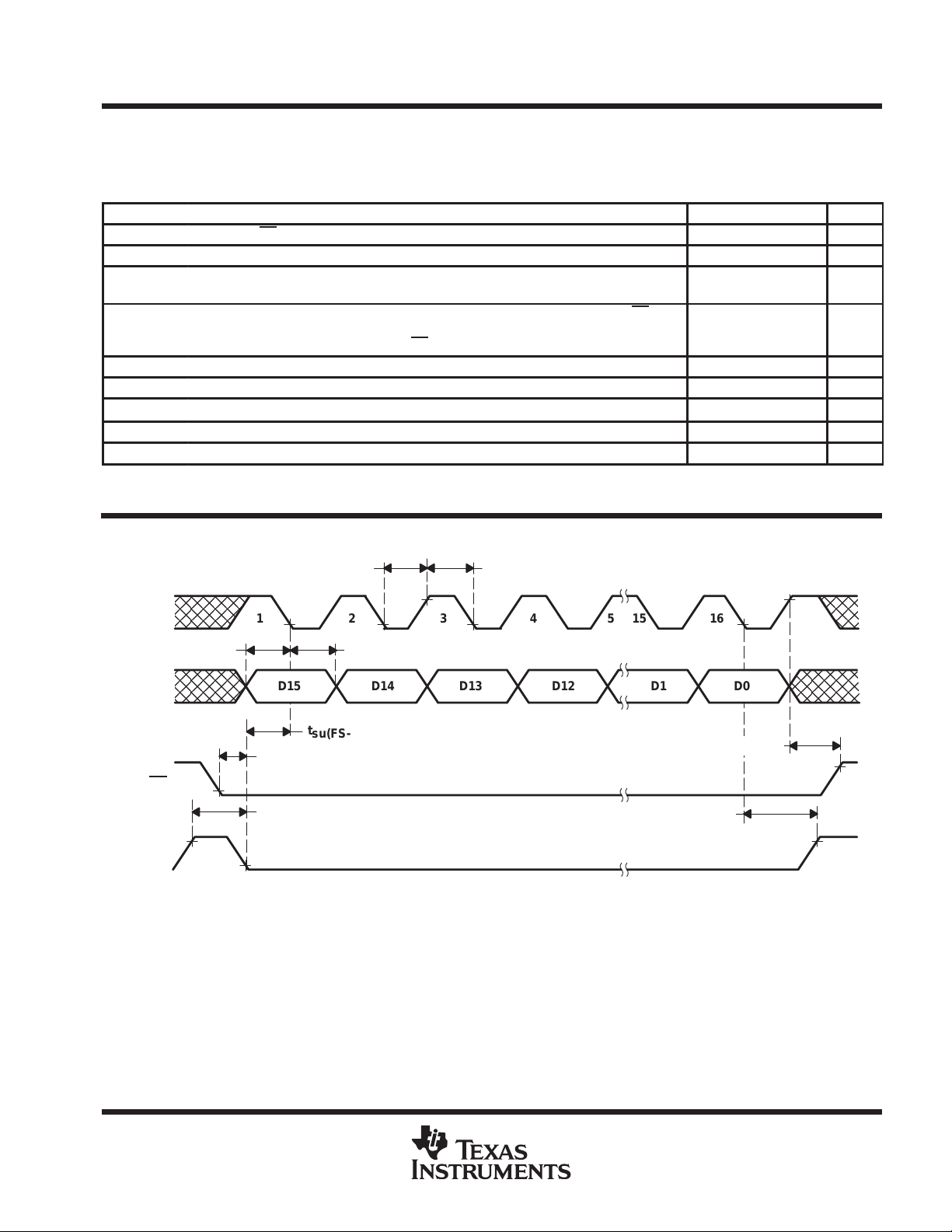

LOAD REGULATION

3 V Slow Mode, Source

4.005

4

– Output – V

3.995

O

V

3.99

3.985

5 V Fast Mode, Source

VDD = 5 V,

V

ref

VO = Full Scale

0 0.02 0.04 0.1 0.2 0.4 1

Load Current – mA

Figure 4

= 2 V,

24

2.000

2.000

1.999

1.999

– Output – V

1.998

O

V

1.998

1.997

1.997

1.996

0 0.01 0.02 0.05 0.1 0.2 0.5

3 V Fast Mode, Source

Load Current – mA

Figure 5

VDD = 3 V,

V

= 1 V,

ref

VO = Full Scale

12

8

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TLV5614

2.7-V TO 5.5-V 12-BIT 3-µS QUADRUPLE DIGITAL-TO-ANALOG CONVERTERS

WITH POWER DOWN

SLAS188 – SEPTEMBER 1998

TYPICAL CHARACTERISTICS

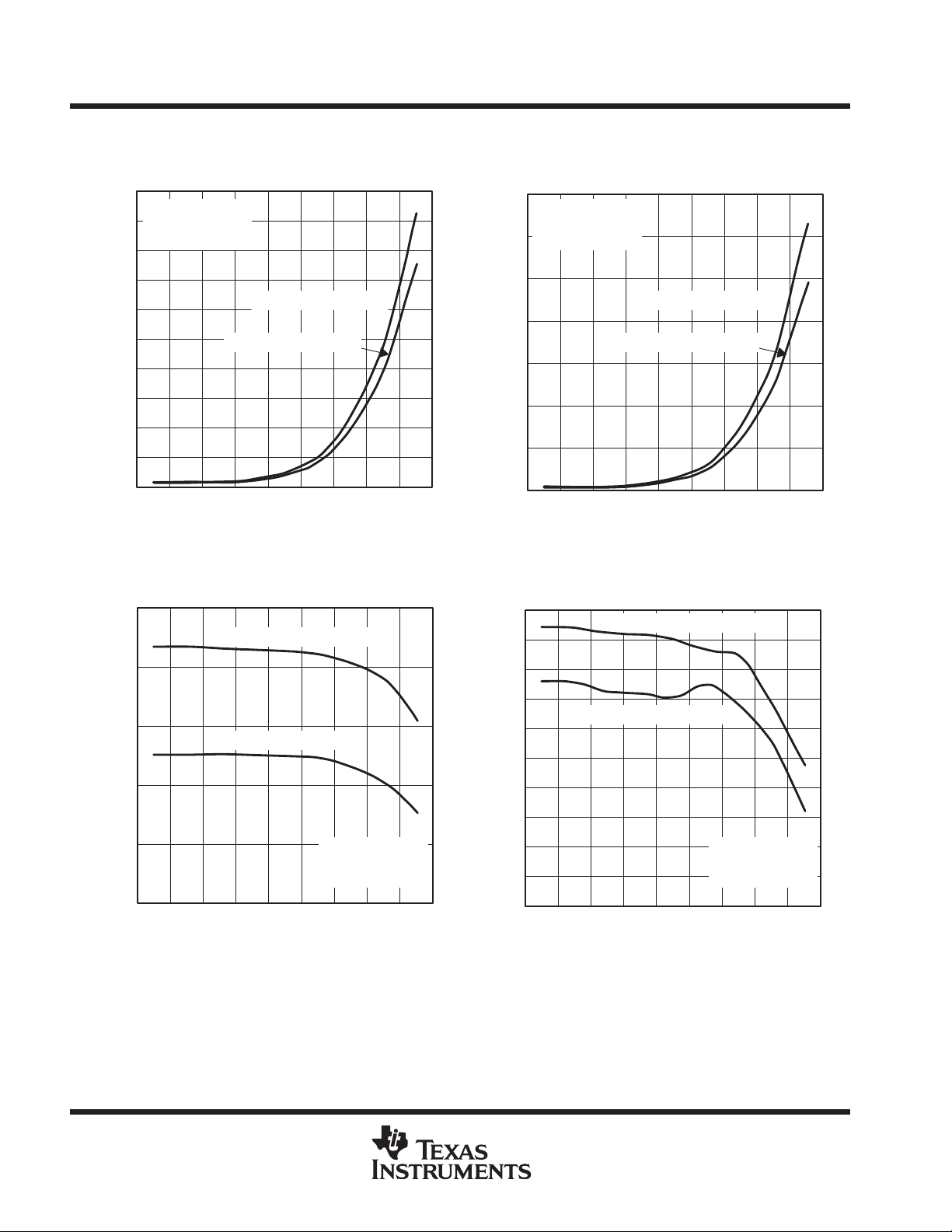

4

VDD = 3 V,

V

= 1.024 V,

3.5

2.5

– Supply Current – mA

1.5

DD

I

0.5

ref

VO Full Scale

(Worst Case For IDD)

3

2

1

–55 –40 –25 0 25 40 70

TOTAL HARMONIC DISTORTION

0

V

= 1 V dc + 1 V p/p Sinewave,

–10

ref

Output Full Scale

SUPPLY CURRENT

vs

TEMPERATURE

Fast Mode

Slow Mode

T – Temperature – °C

Figure 6

vs

FREQUENCY

85 125

4

3.5

3

2.5

2

– Supply Current – mA

DD

1.5

I

1

0.5

–55 –40 –25 0 25 40 70

TOTAL HARMONIC DISTORTION

0

V

= 1 V dc + 1 V p/p Sinewave,

–10

ref

Output Full Scale

SUPPLY CURRENT

vs

TEMPERATURE

Fast Mode

VDD = 5 V,

V

= 1.024 V,

ref

VO Full Scale

(Worst Case For IDD)

Slow Mode

T – Temperature – °C

Figure 7

vs

FREQUENCY

85 125

–20

–30

––40

–50

–60

THD – Total Harmonic Distortion – dB

–70

–80

0 5 10 20

f – Frequency – kHz

Figure 8

Fast Mode

–20

–30

––40

–50

–60

THD – Total Harmonic Distortion – dB

–70

30 50 100

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

–80

0 5 10 20

Slow Mode

30 50 100

f – Frequency – kHz

Figure 9

9

Loading...

Loading...