TL05x, TL05xA, TL05xY

ENHANCED-JFET LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS178 – FEBRUARY 1997

1

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

D

Direct Upgrades to TL07x and TL08x BiFET

Operational Amplifiers

D

Faster Slew Rate (20 V/µs Typ) Without

Increased Power Consumption

D

On-Chip Offset Voltage Trimming for

Improved DC Performance and Precision

Grades Are Available (1.5 mV, TL051A)

D

Available in TSSOP for Small Form-Factor

Designs

description

The TL05x series of JFET-input operational amplifiers of fers improved dc and ac characteristics over the TL07x

and TL08x families of BiFET operational amplifiers. On-chip zener trimming of offset voltage yields precision

grades as low as 1.5 mV (TL051A) for greater accuracy in dc-coupled applications. T exas Instruments improved

BiFET process and optimized designs also yield improved bandwidth and slew rate without increased power

consumption. The TL05x devices are pin-compatible with the TL07x and TL08x and can be used to upgrade

existing circuits or for optimal performance in new designs.

BiFET operational amplifiers offer the inherently higher input impedance of the JFET -input transistors, without

sacrificing the output drive associated with bipolar amplifiers. This makes them better suited for interfacing with

high-impedance sensors or very low-level ac signals. They also feature inherently better ac response than

bipolar or CMOS devices having comparable power consumption.

The TL05x family was designed to offer higher precision and better ac response than the TL08x with the low

noise floor of the TL07x. Designers requiring significantly faster ac response or ensured lower noise should

consider the Excalibur TLE208x and TLE207x families of BiFET operational amplifiers.

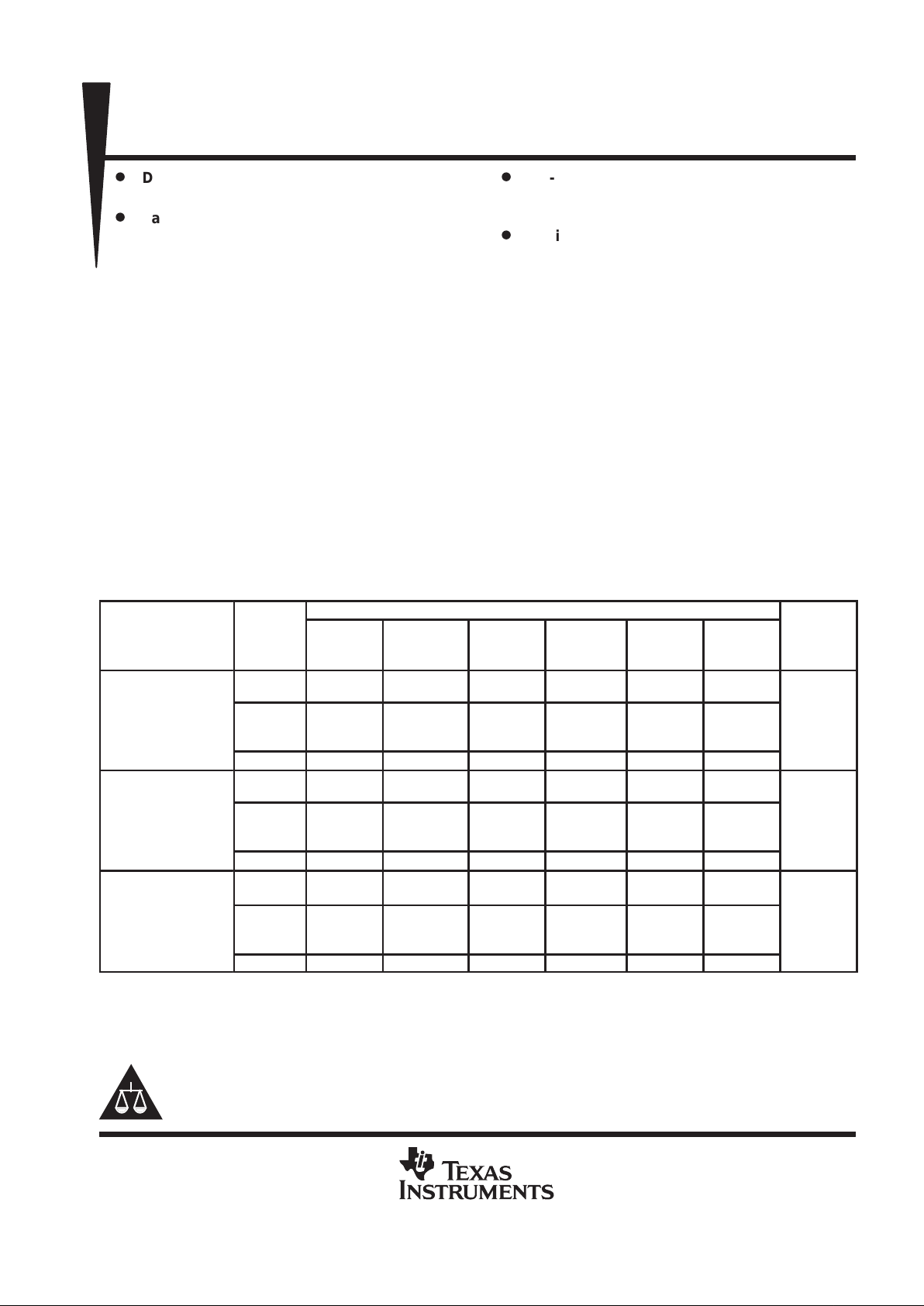

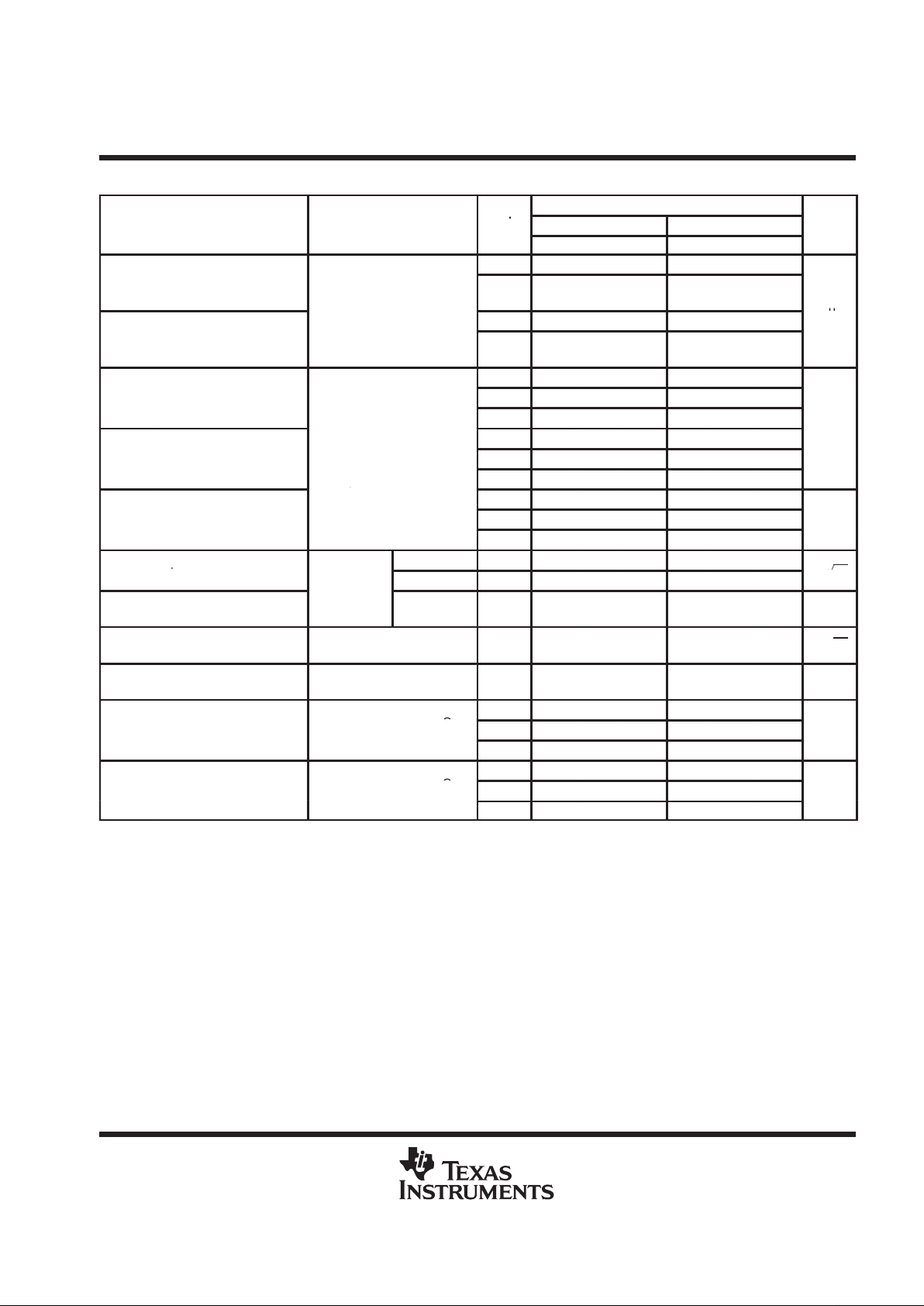

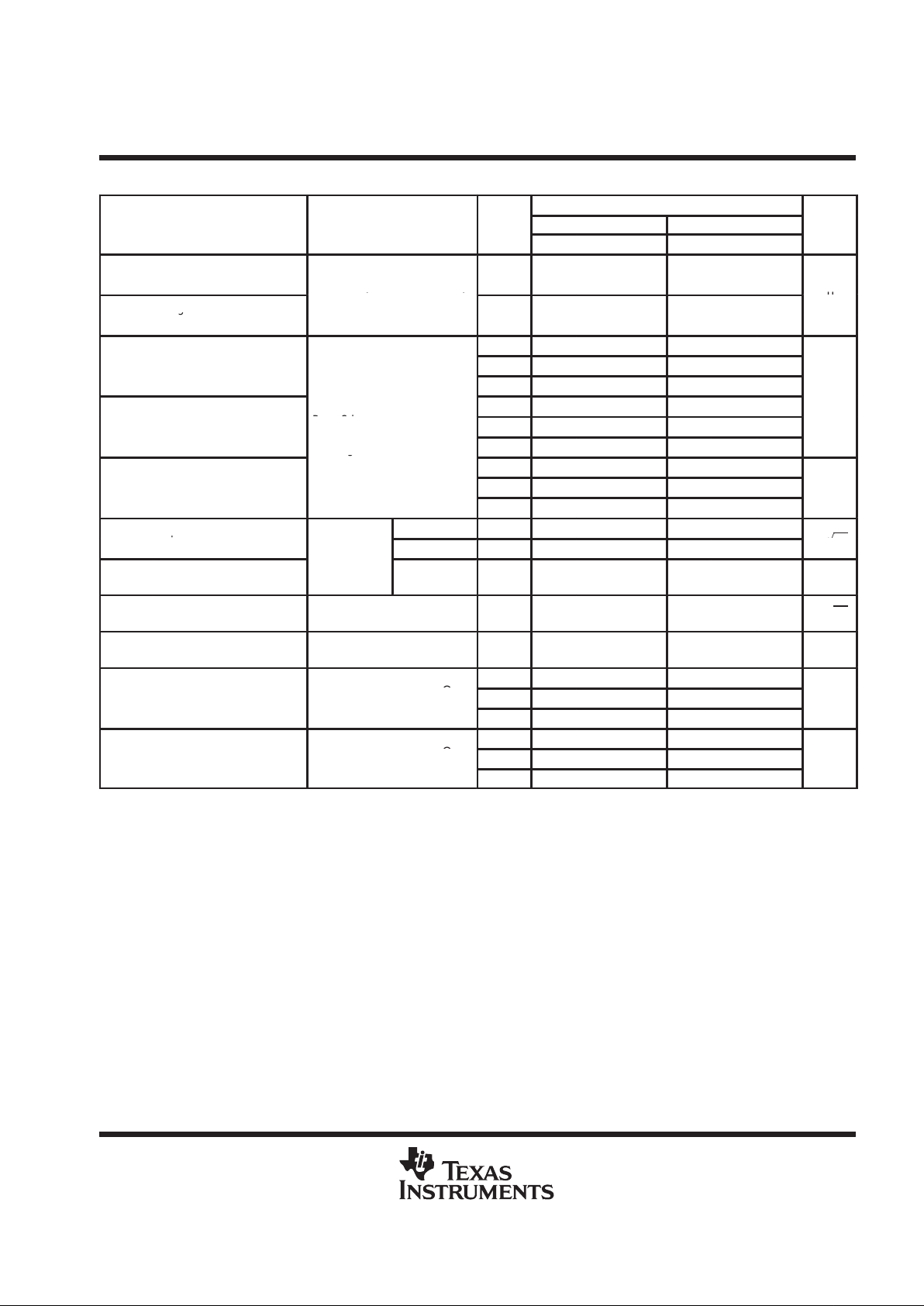

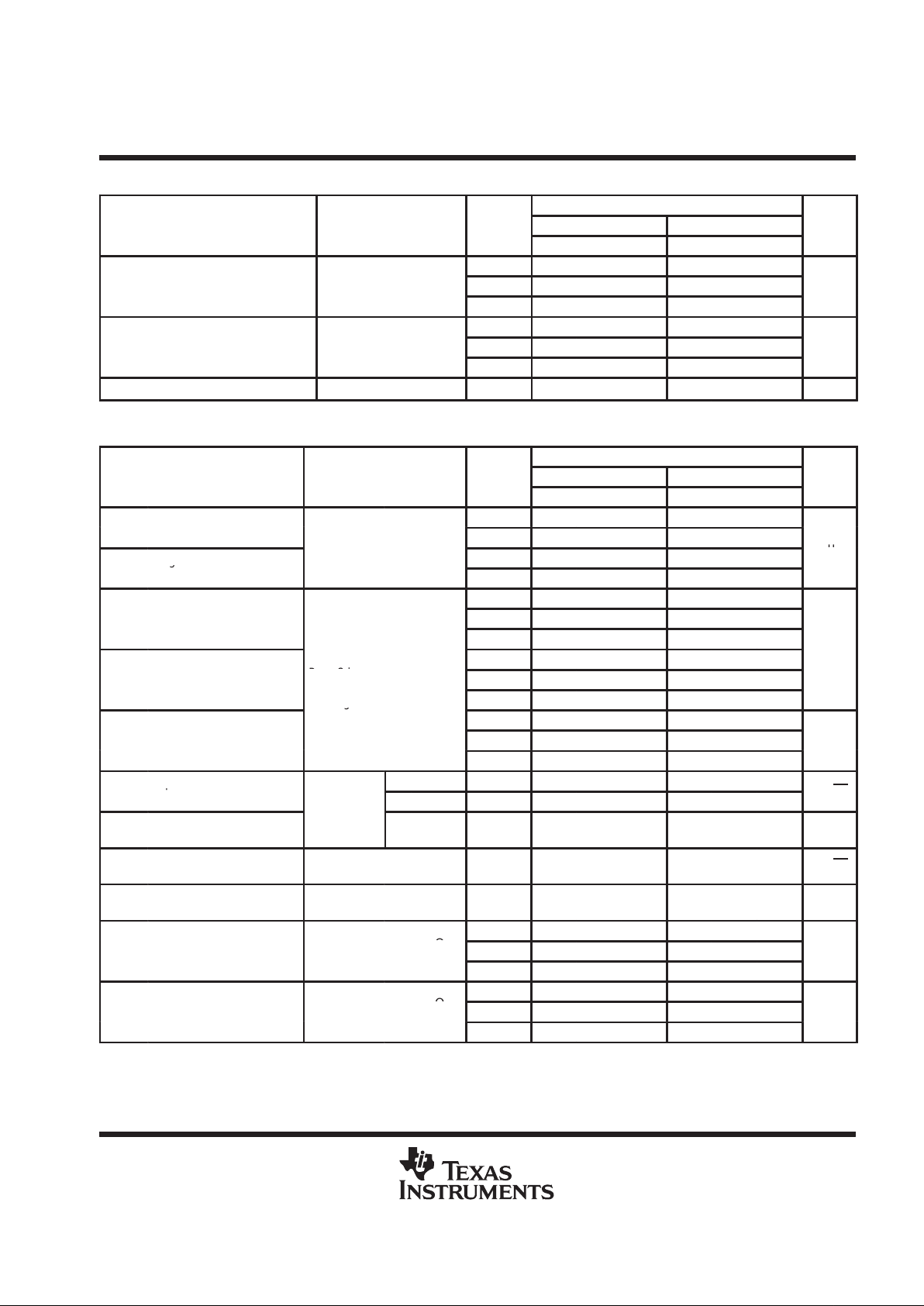

AVAILABLE OPTIONS

PACKAGED DEVICES

T

A

VIOmax

AT 25°C

SMALL

OUTLINE

†

(D)

CHIP

CARRIER

(FK)

CERAMIC

DIP

(J)

CERAMIC

DIP

(JG)

PLASTIC

DIP

(N)

PLASTIC

DIP

(P)

CHIP

FORM

‡

(Y)

800 µV

TL051ACD

TL052ACD

— — — —

TL051ACP

TL052ACP

0°C to 70°C

1.5 mV

TL051CD

TL052CD

TL054ACD

— — — TL054ACN

TL051CP

TL052CP

TL051Y

TL052Y

TL054Y

4 mV TL054CD — — — TL054CN —

800 µV

TL051AID

TL052AID

— — — —

TL051AIP

TL052AIP

–40°C to 85°C

1.5 mV

TL051ID

TL052ID

TL054AID

— — — TL054AIN

TL051IP

TL052IP

—

4 mV TL054ID — — TL054IN —

800 µV

TL051AMD

TL052AMD

TL051AMFK

TL052AMFK

—

TL051AMJG

TL052AMJG

—

TL051AMP

TL052AMP

–55°C to 125°C

1.5 mV

TL051MD

TL052MD

TL054AMD

TL051MFK

TL052MFK

TL054AMFK

TL054AMJ

TL051MJG

TL052MJG

TL054AMN

TL051MP

TL052MP

—

4 mV TL054MD TL054MFK TL054MJ — TL054MN —

†

The D packages are available taped and reeled. Add R suffix to device type (e.g., TL054CDR).

‡

Chip forms are tested at 25°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Copyright 1997, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

TL05x, TL05xA, TL05xY

ENHANCED-JFET LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS178 – FEBRUARY 1997

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

description (continued)

Because BiFET operational amplifiers are designed for use with dual power supplies, care must be taken to

observe common-mode input voltage limits and output swing when operating from a single supply . DC biasing

of the input signal is required and loads should be terminated to a virtual-ground node at midsupply. Texas

Instruments TLE2426 integrated virtual ground generator is useful when operating BiFET amplifiers from single

supplies.

The TL05x are fully specified at ±15 V and ±5 V. For operation in low-voltage and/or single-supply systems,

Texas Instruments LinCMOS families of operational amplifiers (TLC-prefix) are recommended. When moving

from BiFET to CMOS amplifiers, particular attention should be paid to the slew rate and bandwidth

requirements, and also the output loading.

3212019

910111213

4

5

6

7

8

18

17

16

15

14

4IN+

NC

V

CC–

NC

3IN+

1IN+

NC

V

CC+

NC

2IN+

1IN –

1OUT

NC

3OUT

3IN –

4IN –

2IN –

NC

4OUT

2OUT

1

2

3

4

5

6

7

14

13

12

11

10

9

8

1OUT

1IN–

1IN+

V

CC+

2IN+

2IN–

2OUT

4OUT

4IN–

4IN+

V

CC–

3IN+

3IN–

3OUT

1

2

3

4

8

7

6

5

OFFSET N1

IN–

IN+

V

CC–

NC

V

CC+

OUT

OFFSET N2

3 2 1 20 19

910111213

4

5

6

7

8

18

17

16

15

14

NC

V

CC+

NC

OUT

NC

NC

IN–

NC

IN+

NC

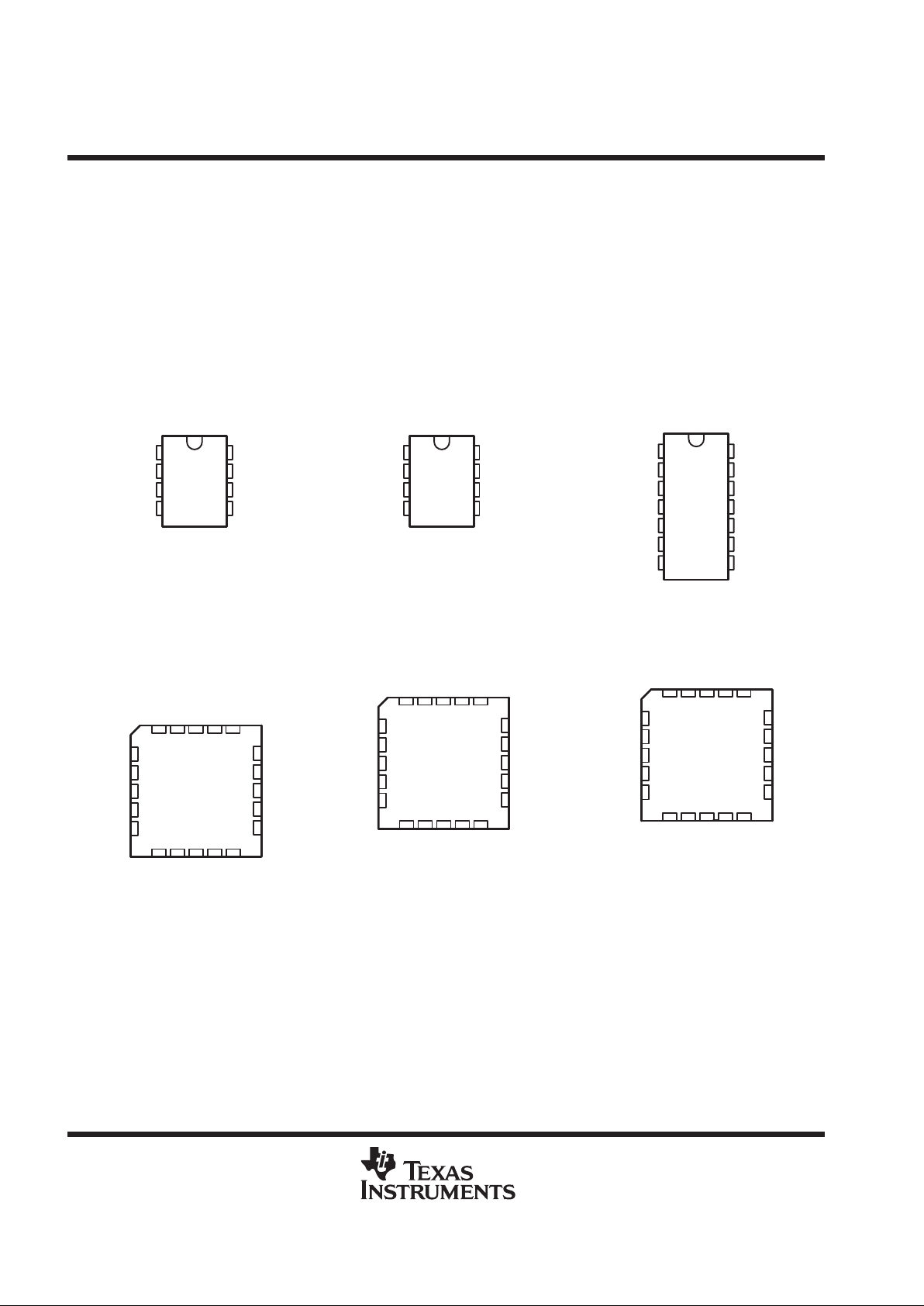

TL051

FK PACKAGE

(TOP VIEW)

NC

OFFSET N1

NC

OFFSET N2

NC

NC

NC

NC

NC – No internal connection

CC –

V

NC

1

2

3

4

8

7

6

5

1OUT

1IN–

1IN+

V

CC –

V

CC+

2OUT

2IN–

2IN+

3212019

910111213

4

5

6

7

8

18

17

16

15

14

NC

2OUT

NC

2IN –

NC

NC

1IN –

NC

1IN+

NC

TL052

FK PACKAGE

(TOP VIEW)

NC

1OUT

NC

2IN +

NC

NC

NC

NC

CC +

V

CC –

V

TL054

D, J, OR N PACKAGE

(TOP VIEW)

TL054

FK PACKAGE

(TOP VIEW)

TL051

D, JG, OR P PACKAGE

(TOP VIEW)

TL052

D, JG, OR P PACKAGE

(TOP VIEW)

TL05x, TL05xA, TL05xY

ENHANCED-JFET LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS178 – FEBRUARY 1997

3

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

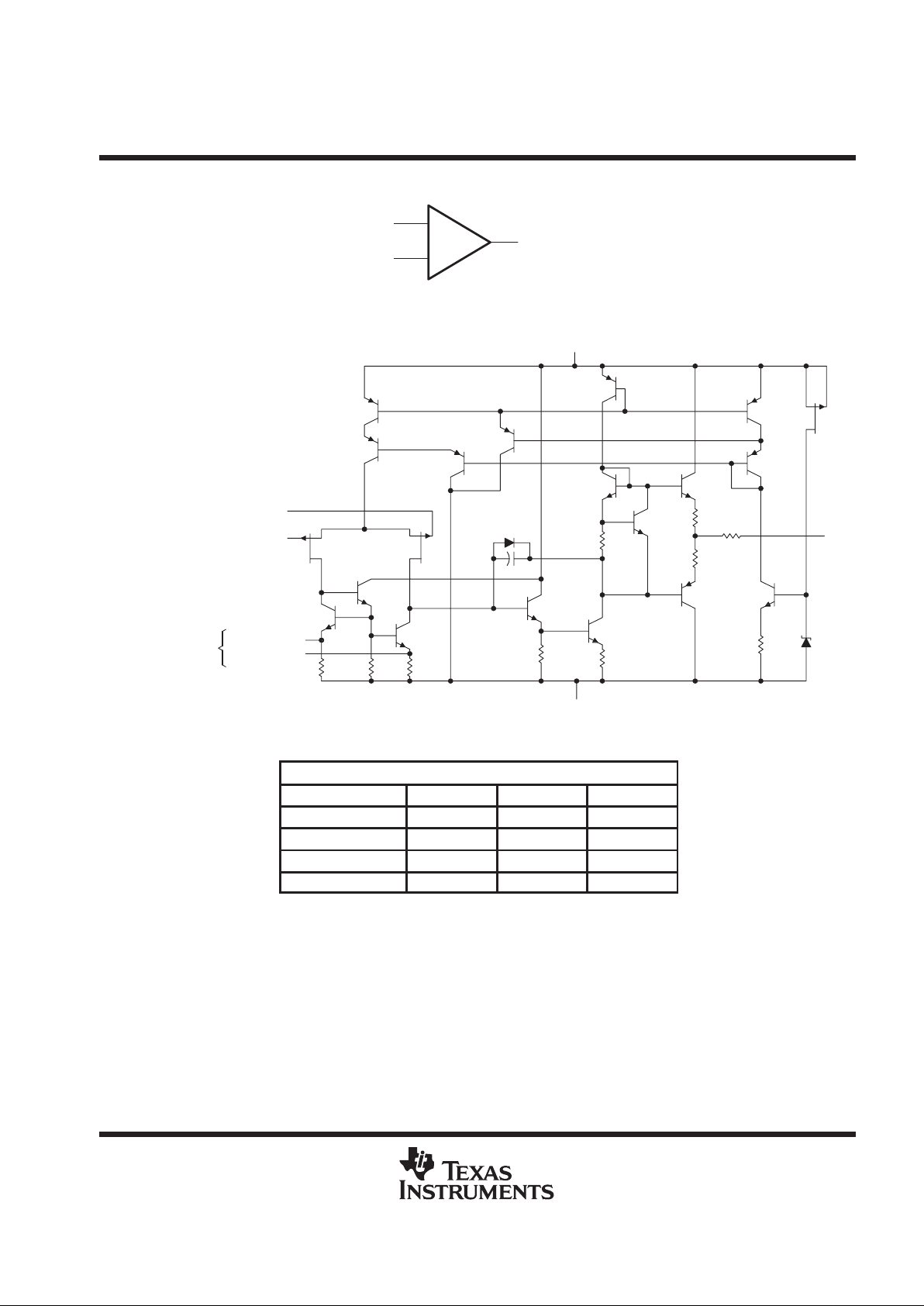

symbol (each amplifier)

+

–

IN–

IN+

OUT

equivalent schematic (each amplifier)

R9

OFFSET N2

OFFSET N1

IN–

IN+

Q2

Q3

Q7

V

CC+

Q14

Q6

R4

Q8

Q10

R7

Q11

R6

C1

Q9

Q5

Q4

R5

R1

Q1

JF1 JF2

Q13

Q16

R8

JF3

Q15

Q17

OUT

V

CC–

R2 R3

Q12

R10 D2

D1

See Note A

NOTE A: OFFSET N1 and OFFSET N2 are only available on the TL051x.

ACTUAL DEVICE COMPONENT COUNT

†

COMPONENT TL051 TL052 TL054

Transistors 20 34 62

Resistors 10 19 37

Diodes 2 3 5

Capacitors 1 2 4

†

These figures include all four amplifiers and all ESD, bias, and trim circuitry.

TL05x, TL05xA, TL05xY

ENHANCED-JFET LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS178 – FEBRUARY 1997

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

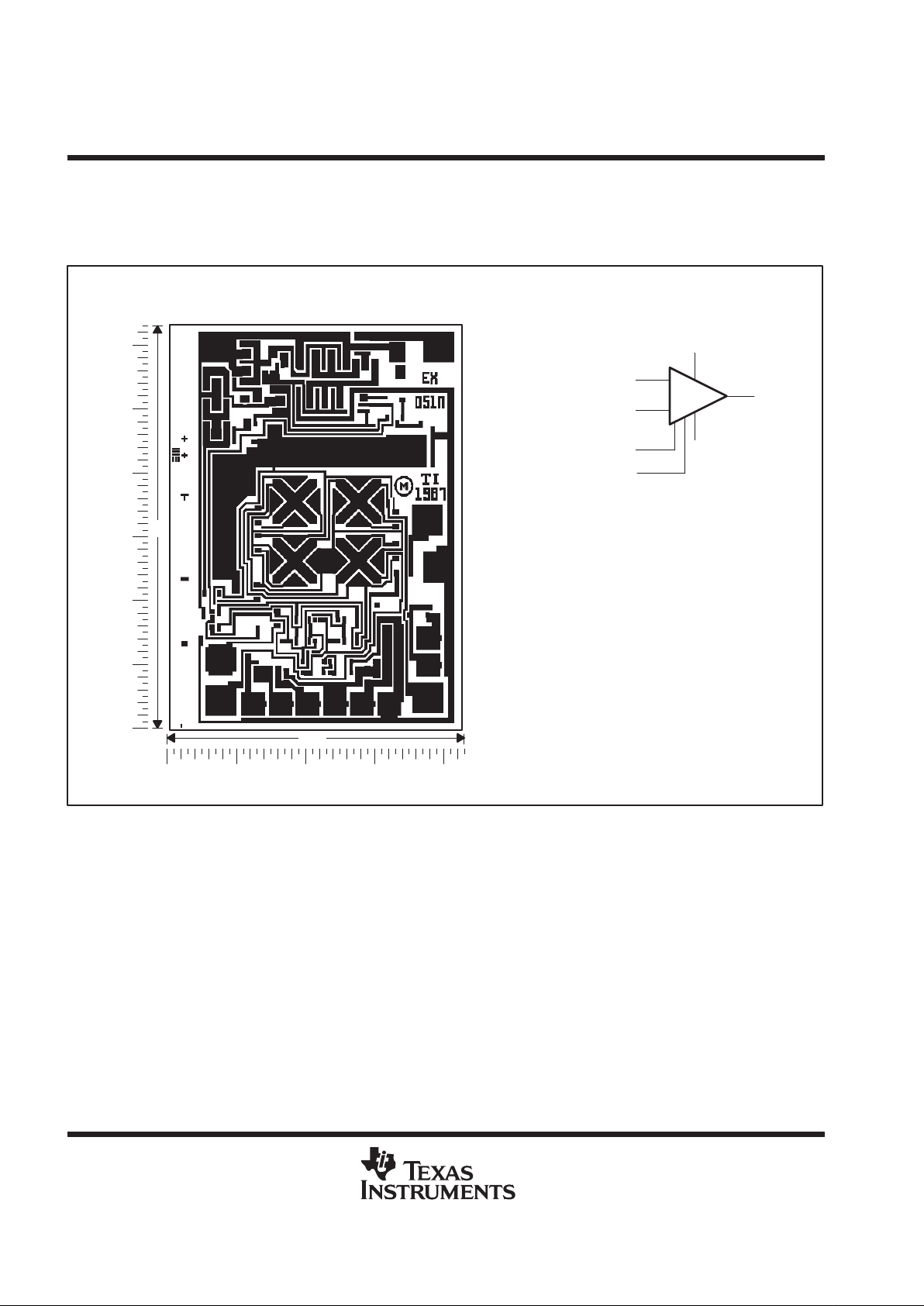

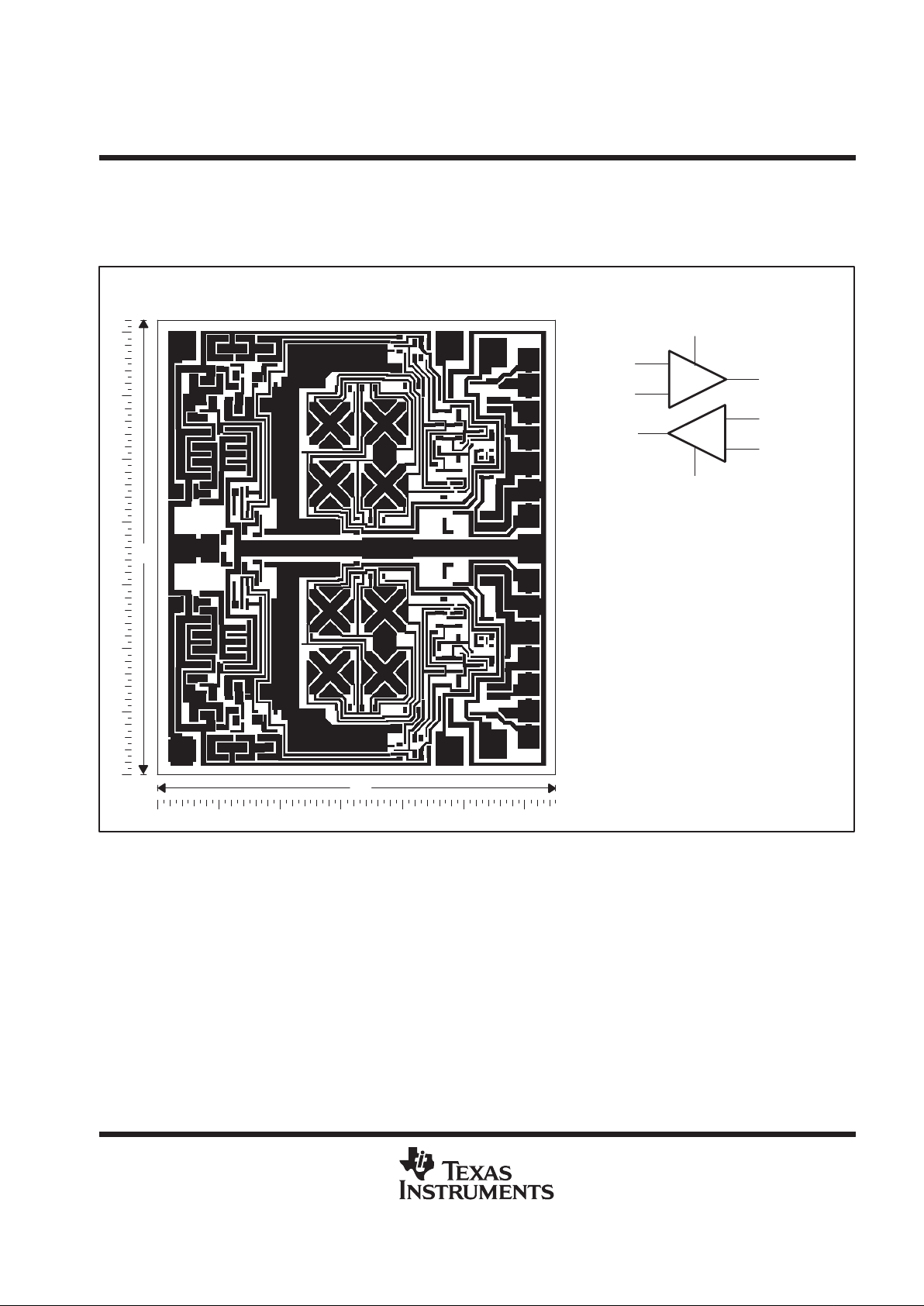

TL051Y chip information

This chip, when properly assembled, displays characteristics similar to the TL051. Thermal compression or

ultrasonic bonding may be used on the doped-aluminum bonding pads. Chips may be mounted with conductive

epoxy or a gold-silicon preform.

BONDING PAD ASSIGNMENTS

CHIP THICKNESS: 15 MILS TYPICAL

BONDING PADS: 4 × 4 MILS MINIMUM

TJmax = 150°C

TOLERANCES ARE ±10%.

ALL DIMENSIONS ARE IN MILS.

PIN (4) IS INTERNALLY CONNECTED

TO BACKSIDE OF CHIP.

+

–

OUT

IN+

IN–

V

CC+

(7)

(3)

(2)

(6)

(1)

(4)

(5)

V

CC–

OFFSET N1

OFFSET N2

63

43

(1)

(2)

(3)

(4)

(5)

(6)(7)

TL05x, TL05xA, TL05xY

ENHANCED-JFET LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS178 – FEBRUARY 1997

5

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

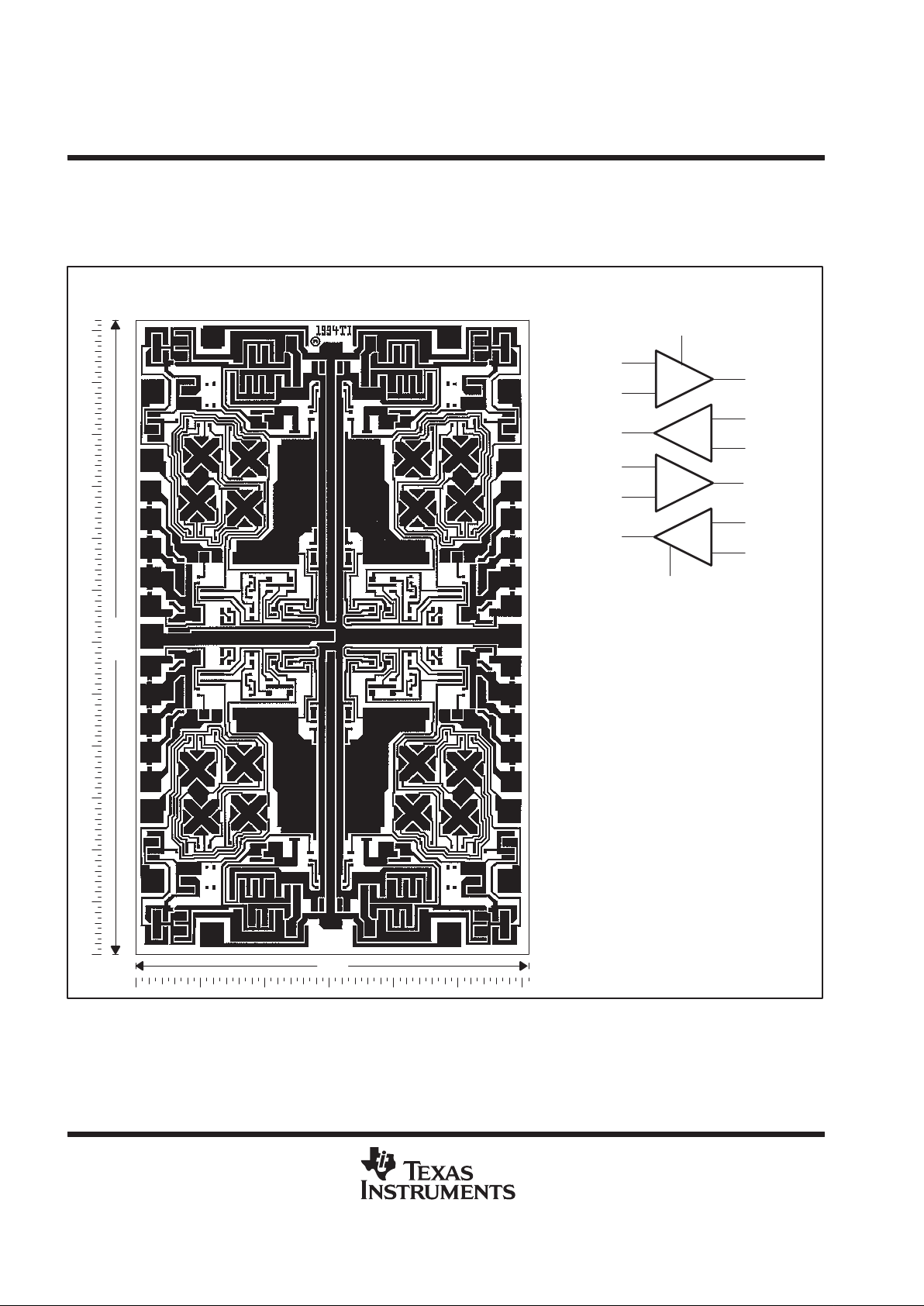

TL052Y chip information

This chip, when properly assembled, displays characteristics similar to the TL052. Thermal compression or

ultrasonic bonding may be used on the doped-aluminum bonding pads. Chips may be mounted with conductive

epoxy or a gold-silicon preform.

BONDING PAD ASSIGNMENTS

CHIP THICKNESS: 15 MILS TYPICAL

BONDING PADS: 4 × 4 MILS MINIMUM

TJmax = 150°C

TOLERANCES ARE ±10%.

ALL DIMENSIONS ARE IN MILS.

PIN (4) IS INTERNALLY CONNECTED

TO BACKSIDE OF CHIP.

+

–

1OUT

1IN+

1IN–

V

CC+

(8)

(6)

(3)

(2)

(5)

(1)

–

+

(7)

2IN+

2IN–

2OUT

(4)

V

CC–

(1)

(2)

(3)

(4)

(5)

(6)

(7)

(8)

66

72

TL05x, TL05xA, TL05xY

ENHANCED-JFET LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS178 – FEBRUARY 1997

6

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

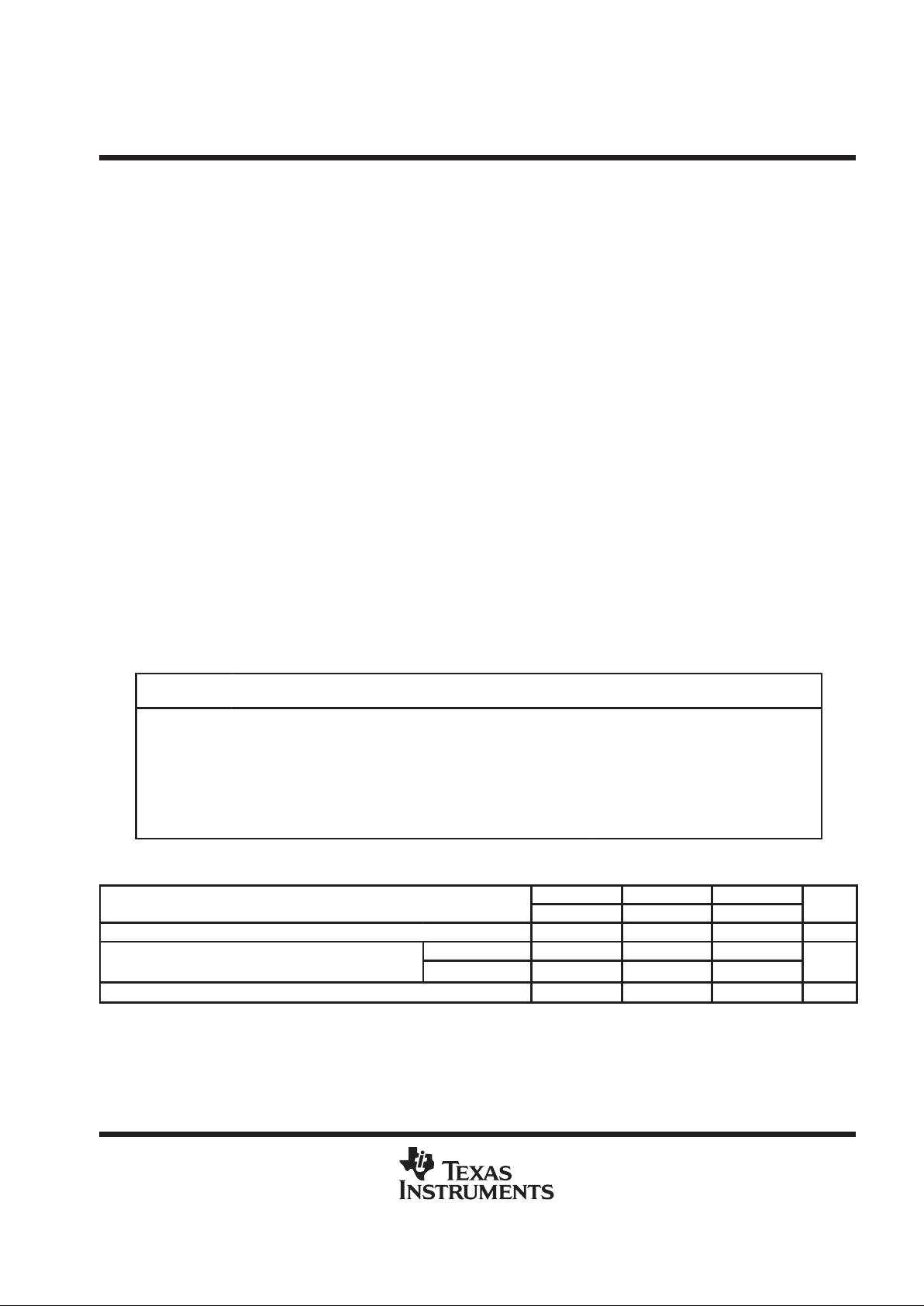

TL054 chip information

This chip, when properly assembled, displays characteristics similar to the TL054C. Thermal compression or

ultrasonic bonding may be used on the doped-aluminum bonding pads. These chips may be mounted with

conductive epoxy or a gold-silicon preform.

BONDING PAD ASSIGNMENTS

+

–

1OUT

1IN+

1IN–

V

CC+

(4)

(6)

(3)

(2)

(5)

(1)

–

+

(7)

2IN+

2IN–

2OUT

(11)

V

CC–

+

–

3OUT

3IN+

3IN–

(13)

(10)

(9)

(12)

(8)

–

+

(14)

4OUT

4IN+

4IN–

(6)

(7)

(8)

(9)

71

122

CHIP THICKNESS: 15 MILS TYPICAL

BONDING PADS: 4 × 4 MILS MINIMUM

TJmax = 150°C

TOLERANCES ARE ±10%.

ALL DIMENSIONS ARE IN MILS.

PIN (11) IS INTERNALLY CONNECTED

TO BACKSIDE OF THE CHIP.

(1)

(2)

(3)

(4)

(5)

(6)

(7) (8)

(9)

(10)

(11)

(12)

(13)

(14)

TL05x, TL05xA, TL05xY

ENHANCED-JFET LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS178 – FEBRUARY 1997

7

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

†

Supply voltage, V

CC+

(see Note 1) 18 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Supply voltage, V

CC–

(see Note 1) –18 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Differential input voltage (see Note 2) ±30 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input voltage range, V

I

(any input, see Notes 1 and 3) ±15 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input current, II (each input) ±1 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Output current, I

O

(each output) ±80 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Total current into V

CC+

160 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Total current out of V

CC–

160 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Duration of short-circuit current at (or below) 25°C (see Note 4) unlimited. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Continuous total power dissipation See Dissipation Rating Table. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating free-air temperature range, T

A

: C suffix 0°C to 70°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

I suffix –40°C to 85°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

M suffix –55°C to 125°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range –65°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Case temperature for 60 seconds: FK package 260°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Lead temperature 1,6 mm (1/16inch) from case for 10 seconds: D, N, or P package 260°C. . . . . . . . . . . . . .

Lead temperature 1,6 mm (1/16inch) from case for 60 seconds: J or JG package 300°C. . . . . . . . . . . . . . . .

†

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. All voltage values, except differential voltages, are with respect to the midpoint between V

CC+

and V

CC–.

2. Differential voltages are at IN+ with respect to IN–.

3. The magnitude of the input voltage must never exceed the magnitude of the supply voltage or 15 V, whichever is less.

4. The output may be shorted to either supply. Temperature and/or supply voltages must be limited to ensure that the maximum

dissipation rating is not exceeded.

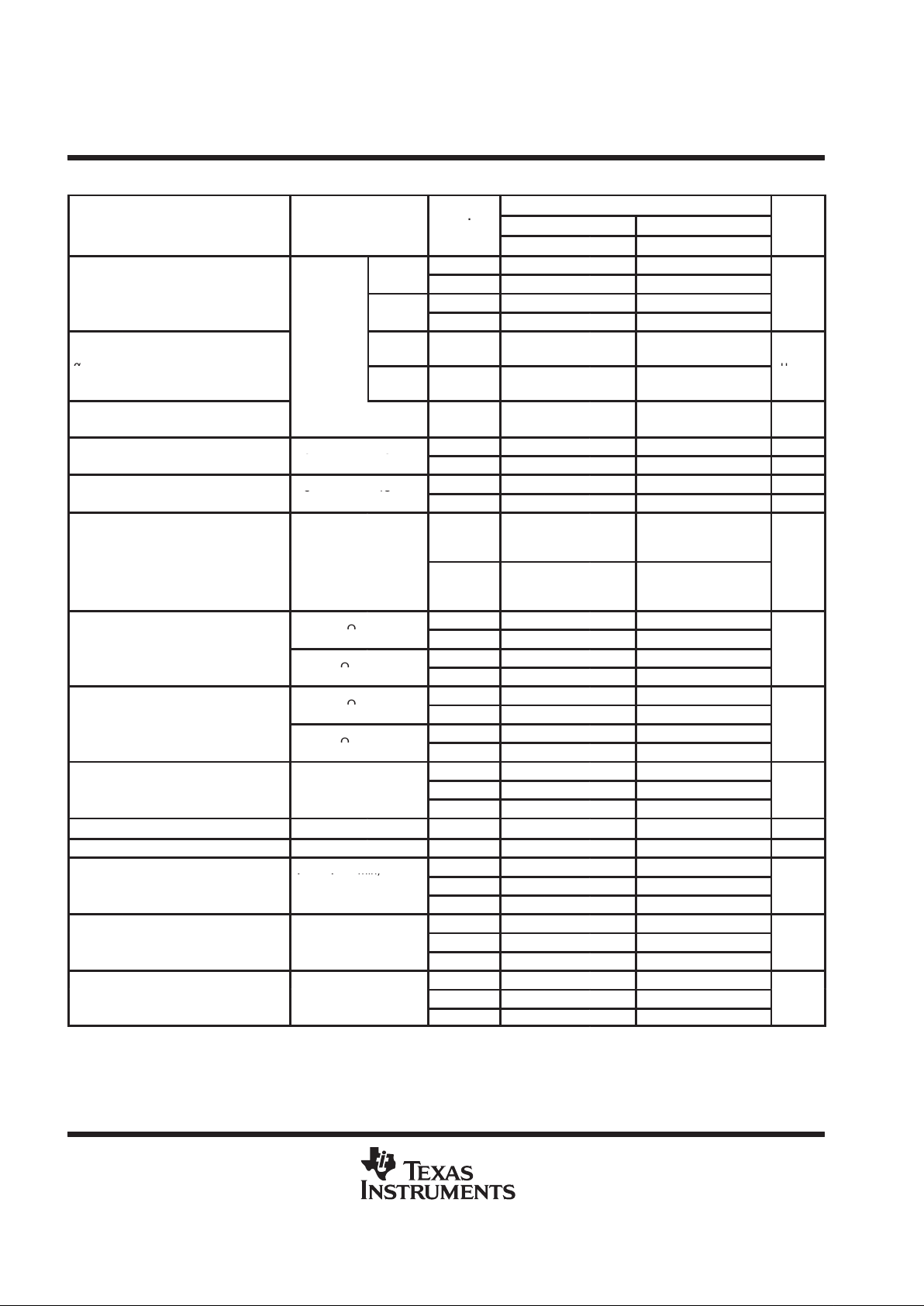

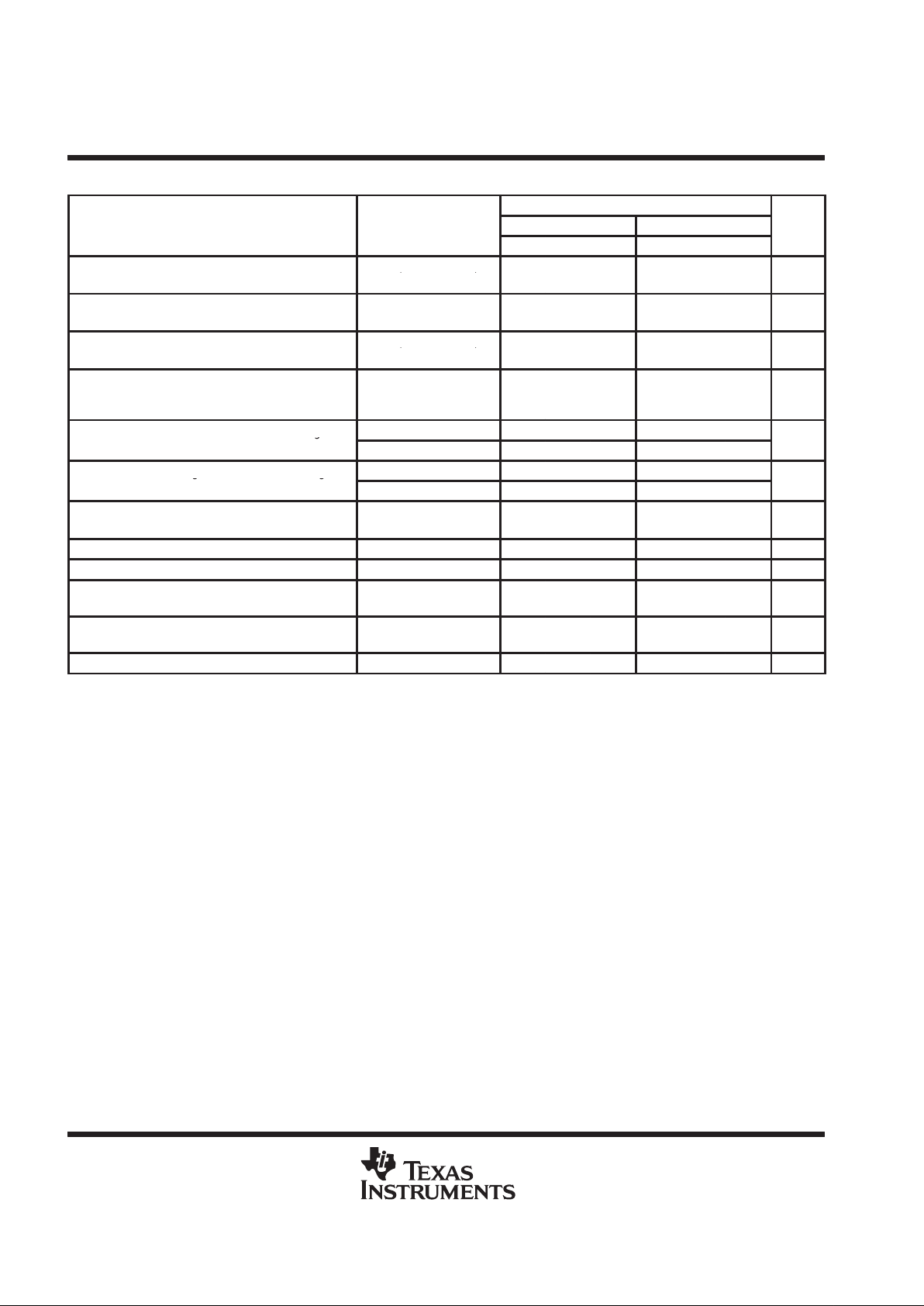

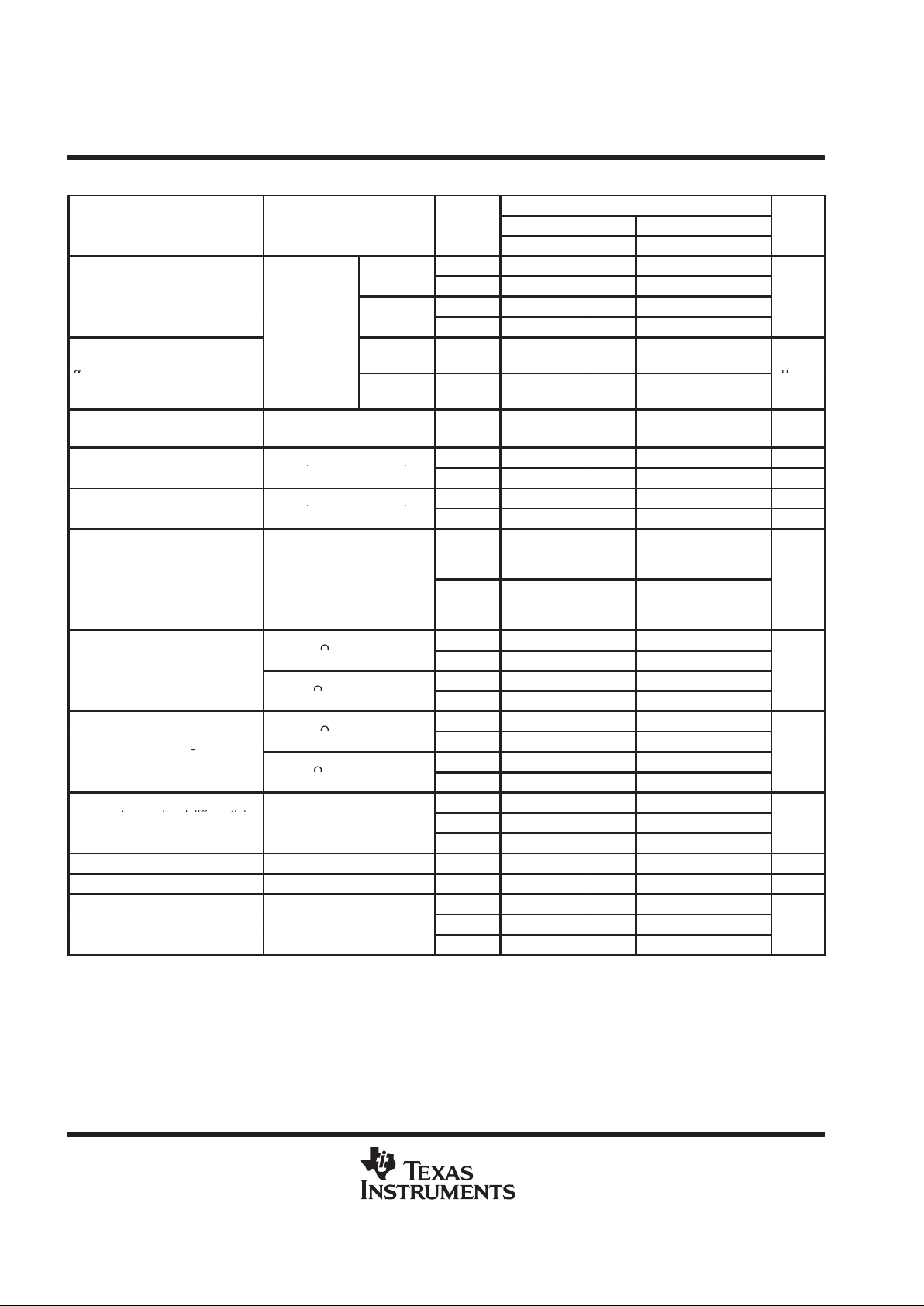

DISSIPATION RATING TABLE

PACKAGE

TA ≤ 25°C

POWER RATING

DERATING FACTOR

ABOVE TA = 25°C

TA = 70°C

POWER RATING

TA = 85°C

POWER RATING

TA = 125°C

POWER RATING

D–8 725 mW 5.8 mW/°C 464 mW 377 mW 145 mW

D–14 950 mW 7.6 mW/°C 608 mW 494 mW 190 mW

FK 1375 mW 11.0 mW/°C 880 mW 715 mW 275 mW

J 1375 mW 11.0 mW/°C 880 mW 715 mW 275 mW

JG 1050 mW 8.4 mW/°C 672 mW 546 mW 210 mW

N 1575 mW 12.6 mW/°C 1008 mW 819 mW 315 mW

P 1000 mW 8.0 mW/°C 640 mW 520 mW 200 mW

recommended operating conditions

C SUFFIX I SUFFIX M SUFFIX

MIN MAX MIN MAX MIN MAX

UNIT

Supply voltage, V

CC±

±5 ±15 ±5 ±15 ±5 ±15 V

V

CC±

= ±5 V –1 4 –1 4 –1 4

C

ommon-mode input voltage,

V

IC

V

CC±

= ±15 V

–11

11

–11

11

–11

11

V

Operating free-air temperature, T

A

0 70

–40

85 –55 125 °C

TL05x, TL05xA, TL05xY

ENHANCED-JFET LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS178 – FEBRUARY 1997

8

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

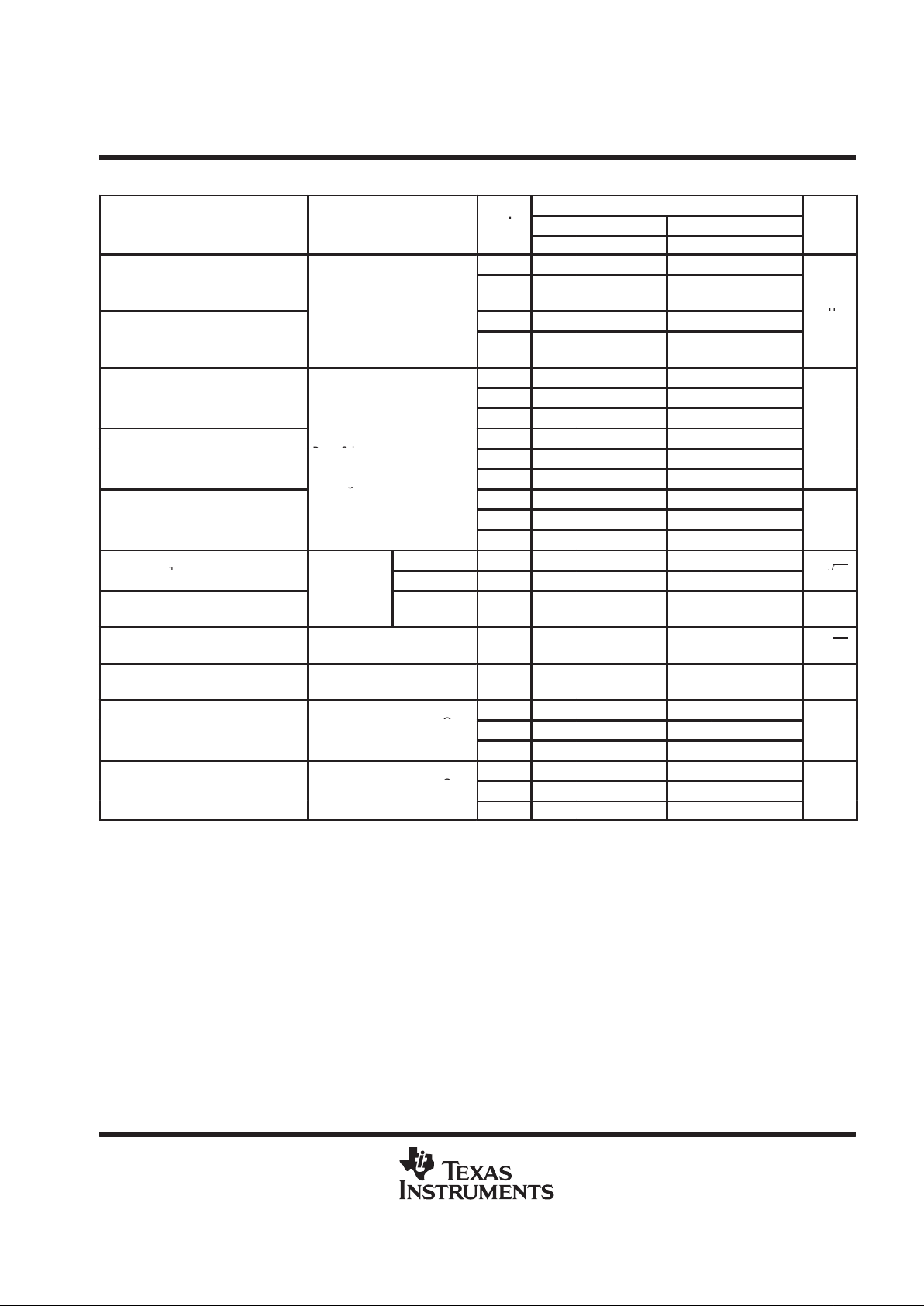

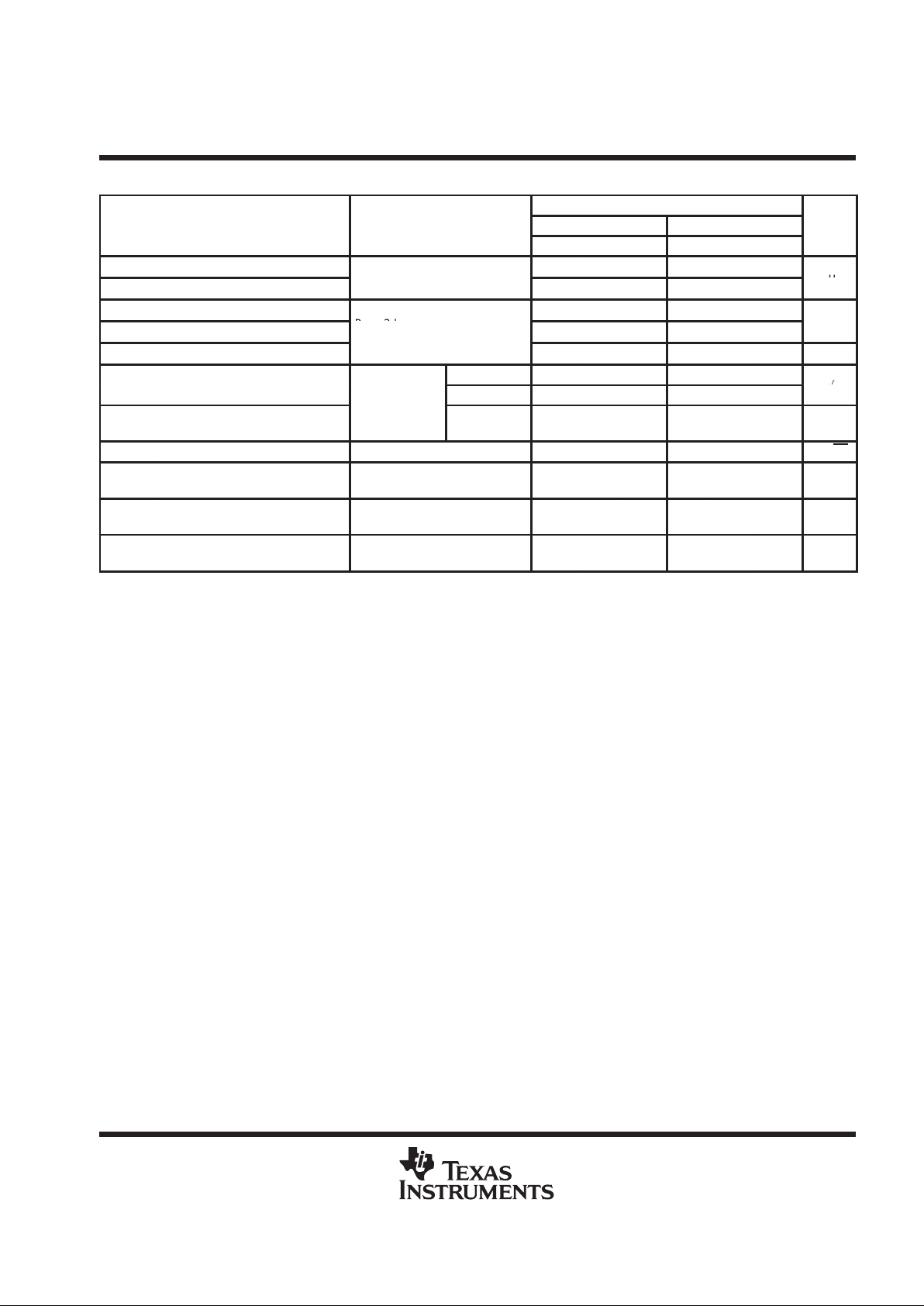

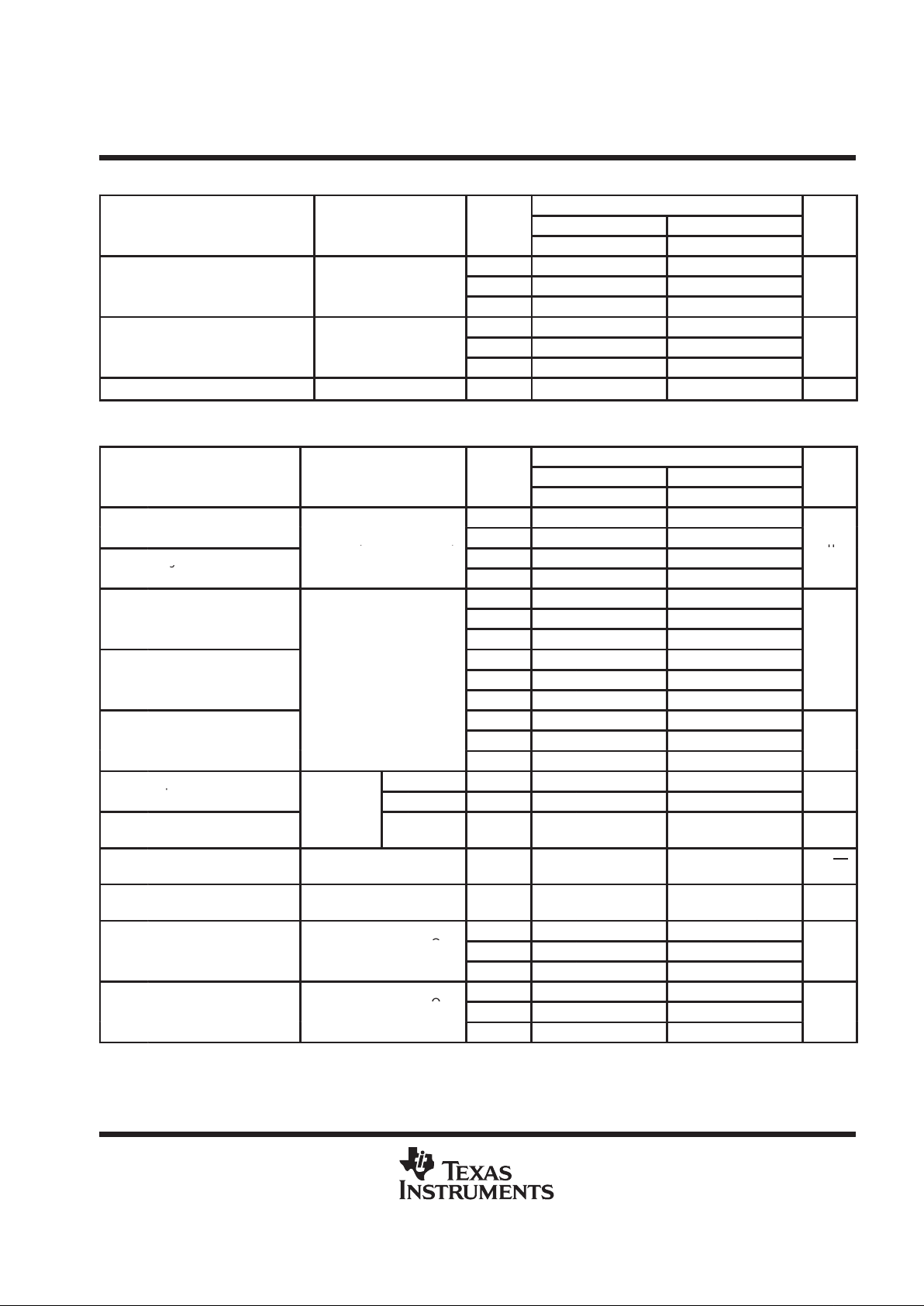

TL051C and TL051AC electrical characteristics at specified free-air temperature

TL051C, TL051AC

PARAMETER TEST CONDITIONS

T

A

†

VCC ± = ± 5 V VCC ± = ± 15 V

UNIT

MIN TYP MAX MIN TYP MAX

25°C 0.75 3.5 0.59 1.5

p

TL051C

Full range 4.5 2.5

VIOInput offset voltage

25°C 0.55 2.8 0.35 0.8

mV

TL051AC

Full range 3.8 1.8

T emperature coef ficient

V

O

= 0,

VIC = 0,

R

= 50 Ω

TL051C

25°C to

70°C

8 8

°

α

VIO

of input offset voltage

‡

R

S

= 50

Ω

TL051AC

25°C to

70°C

8 8 25

µ

V/°C

Input offset voltage

long-term drift

§

25°C 0.04 0.04 µV/mo

p

VO = 0, VIC = 0,

25°C 4 100 5 100 pA

IIOInput offset current

OIC

See Figure 5

70°C 0.02 1 0.025 1 nA

p

VO = 0, VIC = 0,

25°C 20 200 30 200 pA

IIBInput bias current

OIC

See Figure 5

70°C 0.15 4 0.2 4 nA

Common-mode input

25°C

–1

to

4

–2.3

to

5.6

–11

to

11

–12.3

to

15.6

V

ICR

voltage range

Full range

–1

to

4

–11

to

11

V

25°C 3 4.2 13 13.9

Maximum positive peak

R

L

= 10

kΩ

Full range 3 13

V

OM +

output voltage swing

25°C 2.5 3.8 11.5 12.7

V

R

L

=

2 kΩ

Full range 2.5 11.5

25°C –2.5 –3.5 –12 –13.2

Maximum negative peak

R

L

= 10

kΩ

Full range –2.5 –12

V

OM –

g

output voltage swing

25°C –2.3 –3.2 –11 –12

V

R

L

= 2

kΩ

Full range –2.3 –11

25°C 25 59 50 105

A

VD

L

arge-signal

diff

erentia

l

p

¶

RL = 2 kΩ

0°C 30 65 60 129

V/mV

voltage am lification

¶

70°C 20 46 30 85

r

i

Input resistance 25°C 10

12

10

12

Ω

c

i

Input capacitance 25°C 10 12 pF

25°C 65 85 75 93

CMRR

C

ommon-mode

V

IC

=

V

ICR

min,

0°C 65 84 75 92

dB

rejection ratio

V

O

= 0,

R

S

= 50

Ω

70°C 65 84 75 91

25°C 75 99 75 99

k

SVR

S

upply-voltage rejection

VO = 0, RS = 50 Ω

0°C 75 98 75 98

dB

ratio (∆V

CC±

/∆VIO)

70°C 75 97 75 97

25°C 2.6 3.2 2.7 3.2

I

CC

Supply current VO = 0, No load

0°C 2.7 3.2 2.8 3.2

mA

CCyO

70°C 2.6 3.2 2.7 3.2

†

Full range is 0°C to 70°C.

‡

This parameter is tested on a sample basis for the TL051A. For other test requirements, please contact the factory. This statement has no bearing

on testing or nontesting of other parameters.

§

Typical values are based on the input offset voltage shift observed through 168 hours of operating life test at TA = 150°C extrapolated to

TA = 25°C using the Arrhenius equation and assuming an activation energy of 0.96 eV .

¶

For V

CC±

= ±5 V, VO = ±2.3 V, or for V

CC±

= ±15 V, VO = ±10 V.

TL05x, TL05xA, TL05xY

ENHANCED-JFET LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS178 – FEBRUARY 1997

9

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

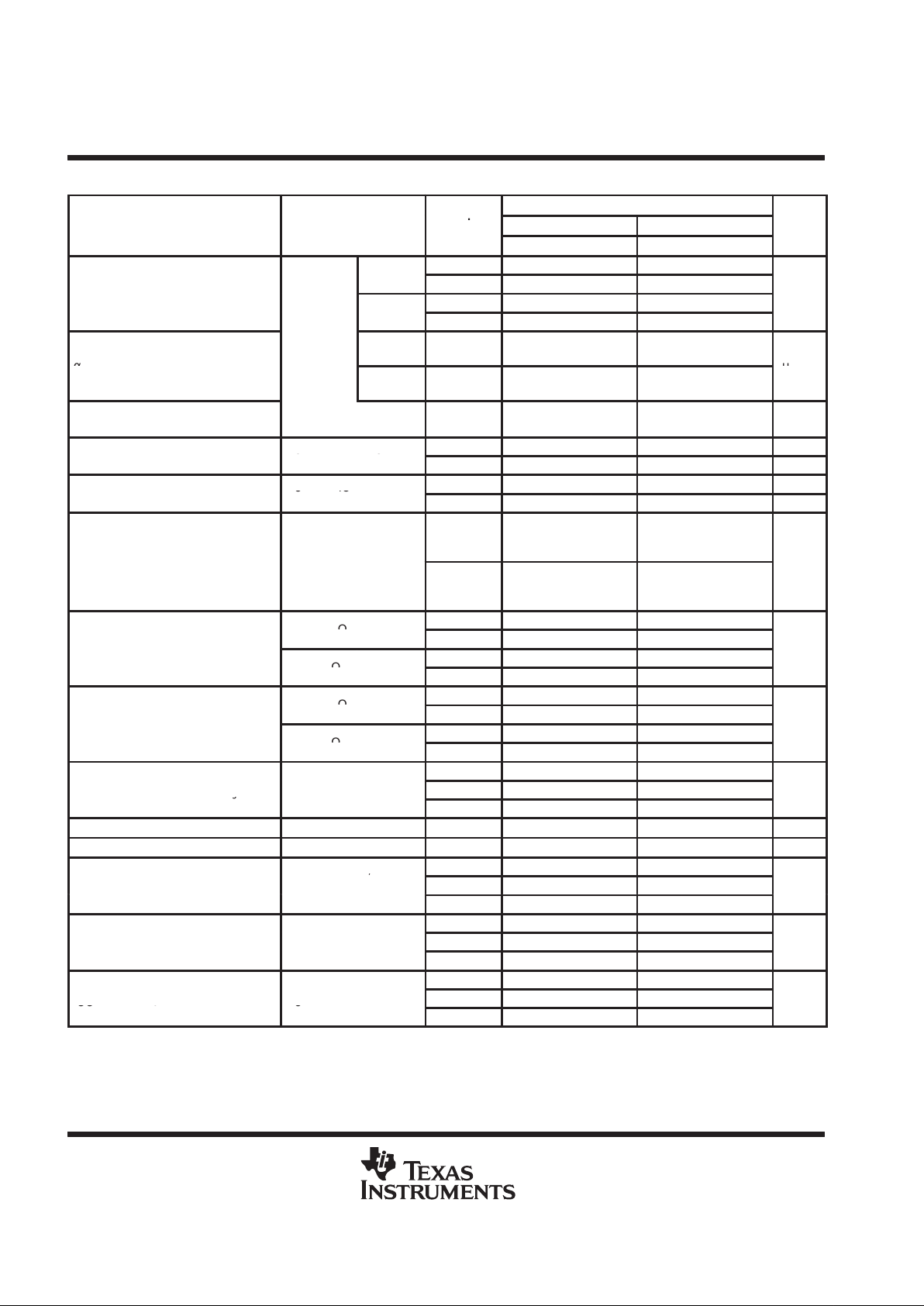

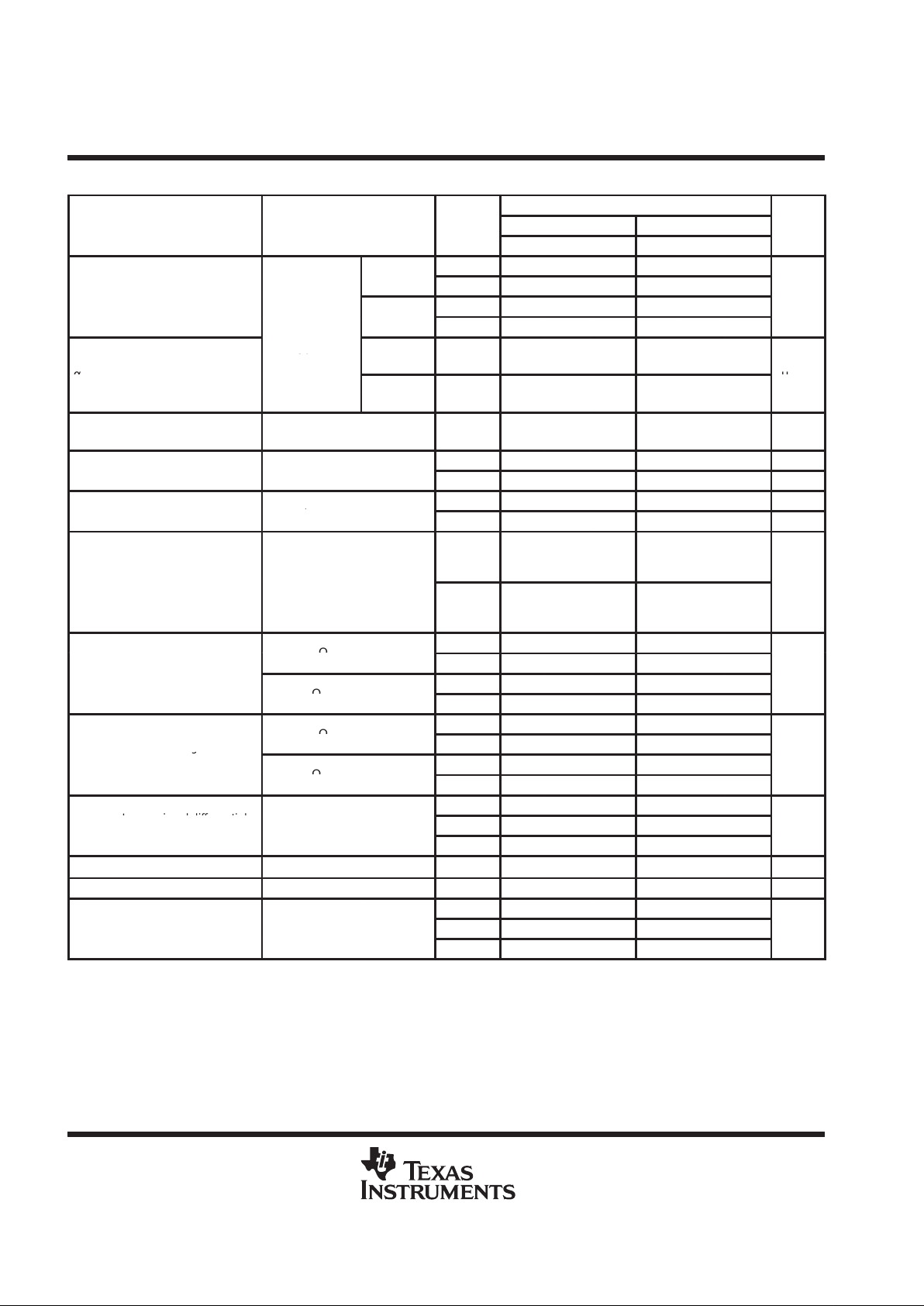

TL051C and TL051AC operating characteristics at specified free-air temperature

TL051C, TL051AC

PARAMETER TEST CONDITIONS

T

A

†

V

CC±

= ±5 V V

CC±

= ±15 V

UNIT

MIN TYP MAX MIN TYP MAX

25°C 16 13 20

SR+

Positi

ve slew rate

at unity gain

‡

R

= 2 kΩ,C

= 100 pF,

Full

range

16.4 11 22.6

L

,

L

,

See Figure 1

25°C 15 13 18

V/µs

SR–

N

egative slew rate

at unity gain

‡

Full

range

16 11 19.3

25°C 55 56

t

r

Rise time

0°C 54 55

70°C 63 63

V

I(PP)

= ±10 mV ,

25°C 55 57

ns

t

f

Fall time

RL = 2 kΩ,

p

0°C 54 56

C

L

=

100 F

,

See Figures 1 and 2

70°C 62 64

g

25°C 24% 19%

Overshoot factor

0°C 24% 19%

70°C 24% 19%

Equivalent input noise

f = 10 Hz 25°C 75 75

V

n

q

voltage

§

RS = 20 Ω,

f = 1 kHz 25°C 18 18 30

n

V/√H

z

V

N(PP)

Peak-to-peak equivalent

input noise voltage

See Figure 3

f = 10 Hz to

10 kHz

25°C 4 4 µV

I

n

Equivalent input

noise current

f = 1 kHz 25°C 0.01 0.01

pA/√Hz

THD

Total harmonic distortion

¶

RS = 1 kΩ,

f = 1 kHz

RL = 2 kΩ,

25°C 0.003% 0.003%

25°C 3 3.1

B

1

Unity-gain bandwidth

VI = 10 mV, RL = 2 kΩ,

p

0°C 3.2 3.3

MHz

C

L

= 25 F,

See Figure 4

70°C 2.7 2.8

25°C 59° 62°

φ

m

Phase margin at unity

VI = 10 mV, RL = 2 kΩ,

p

0°C 58° 62°

gain

C

L

= 25 F,

See Figure 4

70°C 59° 62°

†

Full range is 0°C to 70°C.

‡

For V

CC±

= ±5 V, V

I(PP)

= ±1 V; for V

CC±

= ±15 V, V

I(PP)

= ±5 V.

§

This parameter is tested on a sample basis for the TL051A. For other test requirements, please contact the factory. This statement has no bearing

on testing or nontesting of other parameters.

¶

For V

CC±

= ±5 V, VOrms = 1 V; for V

CC±

= ±15 V, VOrms = 6 V.

TL05x, TL05xA, TL05xY

ENHANCED-JFET LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS178 – FEBRUARY 1997

10

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

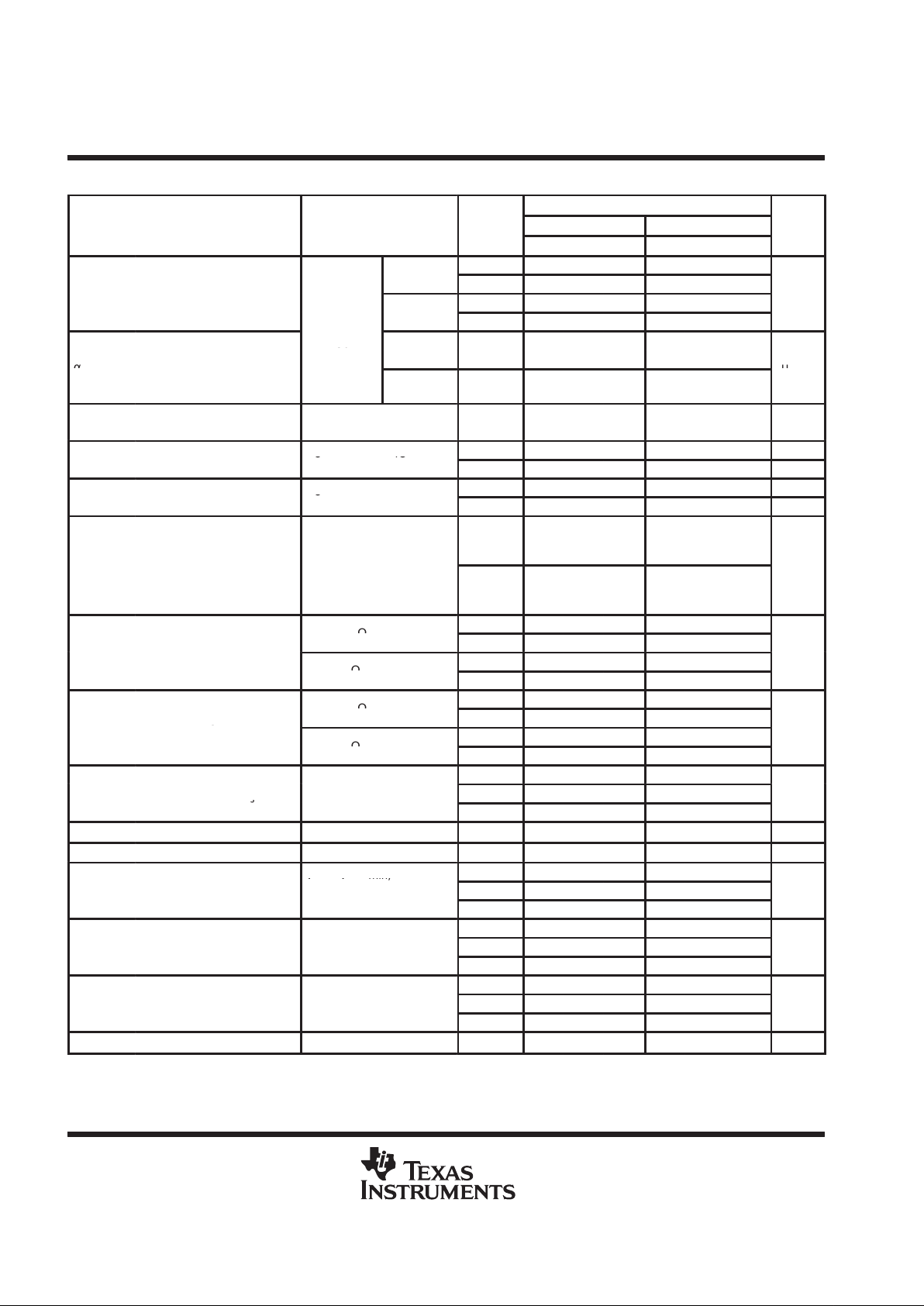

TL051I and TL051AI electrical characteristics at specified free-air temperature

TL051I, TL051AI

PARAMETER TEST CONDITIONS

T

A

†

V

CC±

= ±5 V V

CC±

= ±15 V

UNIT

A

MIN TYP MAX MIN TYP MAX

25°C 0.75 3.5 0.59 1.5

p

TL051I

Full range 5.3 3.3

VIOInput offset voltage

25°C 0.55 2.8 0.35 0.8

mV

TL051AI

Full range 4.6 2.6

T emperature coef ficient of

V

O

=

0

,

VIC = 0,

R

= 50 Ω

TL051I

25°C to

85°C

7 8

°

α

VIO

input offset voltage

‡

R

S

= 50

Ω

TL051AI

25°C to

85°C

8 8 25

µ

V/°C

Input offset voltage

long-term drift

§

25°C 0.04 0.04 µV/mo

p

VO = 0, VIC = 0,

25°C 4 100 5 100 pA

IIOInput offset current

OIC

See Figure 5

85°C 0.06 10 0.07 10 nA

p

VO = 0, VIC = 0,

25°C 20 200 30 200 pA

IIBInput bias current

OIC

See Figure 5

85°C 0.6 20 0.7 20 nA

Common-mode input

25°C

–1

to

4

–2.3

to

5.6

–11

to

11

–12.3

to

15.6

V

ICR

voltage range

Full range

–1

to

4

–11

to

11

V

25°C 3 4.2 13 13.9

Maximum positive peak

R

L

= 10

kΩ

Full range 3 13

V

OM +

output voltage swing

25°C 2.5 3.8 11.5 12.7

V

R

L

= 2

kΩ

Full range 2.5 11.5

25°C –2.5 –3.5 –12 –13.2

Maximum negative peak

R

L

= 10

kΩ

Full range –2.5 –12

V

OM –

g

output voltage swing

25°C –2.3 –3.2 –11 –12

V

R

L

= 2

kΩ

Full range –2.3 –11

25°C 25 59 50 105

A

VD

L

arge-signal

diff

erentia

l

p

¶

RL = 2 kΩ –40°C 30 74 60 145 V/mV

voltage am lification

¶

85°C 20 43 30 76

r

i

Input resistance 25°C

10

12

10

12

Ω

c

i

Input capacitance 25°C 10 12 pF

V

= V

min

,

25°C 65 85 75 93

CMRR

C

ommon-mode

V

IC

V

ICR

min,

VO = 0,

–40°C 65 83 75 90 dB

rejection ratio

RS = 50 Ω

85°C 65 84 75 93

25°C 75 99 75 99

k

SVR

S

upply-voltage rejection

V

O

= 0,

–40°C 75 98 75 98 dB

ratio (∆V

CC±

/∆VIO)

R

S

= 50

Ω

85°C 75 99 75 99

25°C 2.6 3.2 2.7 3.2

I

CC

Supply current VO = 0, No load –40°C 2.4 3.2 2.6 3.2 mA

85°C 2.5 3.2 2.6 3.2

†

Full range is –40°C to 85°C

‡

This parameter is tested on a sample basis for the TL051A. For other test requirements, please contact the factory. This statement has no bearing

on testing or nontesting of other parameters.

§

Typical values are based on the input offset voltage shift observed through 168 hours of operating life test at TA = 150°C extrapolated to

TA = 25°C using the Arrhenius equation and assuming an activation energy of 0.96 eV .

¶

For V

CC±

= ±5 V, VO = ±2.3 V, or for V

CC±

= ±15 V, VO = ±10 V.

TL05x, TL05xA, TL05xY

ENHANCED-JFET LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS178 – FEBRUARY 1997

11

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TL051I and TL051AI operating characteristics at specified free-air temperature

TL051I, TL051AI

PARAMETER TEST CONDITIONS

T

A

†

V

CC±

= ±5 V V

CC±

= ±15 V

UNIT

MIN TYP MAX MIN TYP MAX

25°C 16 13 20

SR+

Positi

ve slew rate

at unity gain

‡

R

= 2 kΩ,C

= 100 pF,

Full

range

11

L

,

L

,

See Figure 1

25°C 15 13 18

V/µs

SR–

N

egative slew rate

at unity gain

‡

Full

range

11

25°C 55 56

t

r

Rise time

–40°C 52 53

85°C 64 65

V

I(PP)

= ±10 mV ,

25°C 55 57

ns

t

f

Fall time

()

RL = 2 kΩ,

p

–40°C 51 53

C

L

=

100 F

,

See Fi

g

ures 1 and 2

85°C 64 65

g

25°C 24% 19%

Overshoot factor

–40°C 24% 19%

85°C 24% 19%

Equivalent input noise

f = 10 Hz 25°C 75 75

V

n

q

voltage

§

RS = 20 Ω,

f = 1 kHz 25°C 18 18 30

n

V/√H

z

V

N(PP)

Peak-to-peak equivalent

input noise voltage

See Figure 3

f = 10 Hz to

10 kHz

25°C 4 4 µV

I

n

Equivalent input

noise current

f = 1 kHz 25°C 0.01 0.01 pA/√Hz

THD Total harmonic distortion

¶

RS = 1 kΩ,

f = 1 kHz

RL = 2 kΩ,

25°C 0.003% 0.003%

25°C 3 3.1

B

1

Unity-gain bandwidth

VI = 10 mV, RL = 2 kΩ,

p

–40°C 3.5 3.6

MHz

C

L

= 25 F,

See Figure 4

85°C 2.6 2.7

25°C 59° 62°

φ

m

Phase margin at unity

VI = 10 mV, RL = 2 kΩ,

p

–40°C 58° 61°

gain

C

L

= 25 F,

See Figure 4

85°C 59° 62°

†

Full range is –40°C to 85°C.

‡

For V

CC±

= ±5 V, V

I(PP)

= ±1 V; for V

CC±

= ±15 V, V

I(PP)

= ±5 V.

§

This parameter is tested on a sample basis for the TL051A. For other test requirements, please contact the factory. This statement has no bearing

on testing or nontesting of other parameters.

¶

For V

CC±

= ±5 V, VOrms = 1 V; for V

CC±

= ±15 V, VOrms = 6 V.

TL05x, TL05xA, TL05xY

ENHANCED-JFET LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS178 – FEBRUARY 1997

12

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TL051M and TL051AM electrical characteristics at specified free-air temperature

TL051M, TL051AM

PARAMETER TEST CONDITIONS

T

A

†

VCC ± = ± 5 V VCC ± = ± 15 V

UNIT

A

MIN TYP MAX MIN TYP MAX

25C 0.75 3.5 0.59 1.5

p

TL051M

Full range 6.5 4.5

VIOInput offset voltage

25°C 0.55 2.8 0.35 0.8

mV

TL051AM

Full range 5.8 3.8

T emperature coef ficient of

V

O

=

0

,

VIC = 0,

R

= 50 Ω

TL051M

25°C to

125°C

8 8

°

α

VIO

input offset voltage

R

S

= 50

Ω

TL051AM

25°C to

125°C

8 8

µ

V/°C

Input offset voltage

long-term drift

‡

25°C 0.04 0.04 µV/mo

p

VO = 0, VIC = 0,

25°C 4 100 5 100 pA

IIOInput offset current

OIC

See Figure 5

125°C 1 20 2 20 nA

p

VO = 0, VIC = 0,

25°C 20 200 30 200 pA

IIBInput bias current

OIC

See Figure 5

125°C 10 50 20 50 nA

Common-mode input

25°C

–1

to

4

–2.3

to

5.6

–11

to

11

–12.3

to

15.6

V

ICR

voltage range

Full range

–1

to

4

–11

to

11

V

25°C 3 4.2 13 13.9

Maximum positive peak

R

L

= 10

kΩ

Full range 3 13

V

OM+

output voltage swing

25°C 2.5 3.8 11.5 12.7

V

R

L

= 2

kΩ

Full range 2.5 11.5

25°C –2.5 –3.5 –12 –13.2

Maximum negative peak

R

L

= 10

kΩ

Full range –2.5 –12

V

OM–

g

output voltage swing

25°C –2.3 –3.2 –11 –12

V

R

L

= 2

kΩ

Full range –2.3 –11

25°C 25 59 50 105

A

VD

L

arge-signal

diff

erentia

l

p

§

RL = 2 kΩ

–55°C 30 76 60 149

V/mV

voltage am lification

§

125°C 10 32 15 49

r

i

Input resistance 25°C 10

12

10

12

Ω

c

i

Input capacitance 25°C 10 12 pF

V

= V

min

,

25°C 65 85 75 93

CMRR

C

ommon-mode

V

IC

V

ICR

min,

VO = 0,

–55°C 65 83 75 92

dB

rejection ratio

RS = 50 Ω

125°C 65 84 75 94

25°C 75 99 75 99

k

SVR

S

upply-voltage rejection

VO = 0, RS = 50 Ω

–55°C 75 98 75 98

dB

ratio (∆V

CC±

/∆VIO)

125°C 75 100 75 100

25°C 2.6 3.2 2.7 3.2

I

CC

Supply current VO = 0, No load

–55°C 2.3 3.2 2.4 3.2

mA

CCyO

125°C 2.4 3.2 2.5 3.2

†

Full range is –55°C to 125°C.

‡

Typical values are based on the input offset voltage shift observed through 168 hours of operating life test at TA = 150°C extrapolated to

TA = 25°C using the Arrhenius equation and assuming an activation energy of 0.96 eV .

§

For V

CC±

= ± 5 V, VO = ± 2.3 V, or for V

CC±

=

±15 V, V

O

= ±10 V.

TL05x, TL05xA, TL05xY

ENHANCED-JFET LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS178 – FEBRUARY 1997

13

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TL051M and TL051AM operating characteristics at specified free-air temperature

TL051M, TL051AM

PARAMETER TEST CONDITIONS

T

A

V

CC±

= ±5 V V

CC±

= ±15 V

UNIT

A

MIN TYP MAX MIN TYP MAX

Positive slew rate

°

SR

+

at unity gain

†

R

= 2 kΩ,C

= 100 pF,

25°C1613

20

Negative slew rate

L

,

L

,

See Figure 1

°

V/µs

SR

–

g

at unity gain

†

25°C1513

25°C 55 56

t

r

Rise time

–55°C 51 52

125°C 68 68

V

I(PP)

= ±10 mV,

25°C 55 57

ns

t

f

Fall time

()

RL = 2 kΩ,

p

–55°C 51 52

C

L

=

100 F

,

See Fi

g

ures 1 and 2

125°C 68 69

g

25°C 24% 19%

Overshoot factor

–55°C 25% 19%

125°C 25% 19%

Equivalent input noise

f = 10 Hz 25°C 75 75

V

n

q

voltage

‡

RS = 20 Ω,

f = 1 kHz 25°C 18 19

n

V/√H

z

V

N(PP)

Peak-to-peak equivalent

input noise voltage

See Figure 3

f = 10 Hz to

10 kHz

25°C 4 4 µV

I

n

Equivalent input noise

current

f = 1 kHz 25°C 0.01 0.01 pA/√Hz

THD

Total harmonic distortion

§

RS = 1 kΩ,

f = 1 kHz

RL = 2kΩ,

25°C 0.003% 0.003%

25°C 3 3.1

B

1

Unity-gain bandwidth

VI = 10 mV,

p

RL = 2 kΩ,

–55°C 3.6 3.7

MHz

C

L

= 25 F,

See Figure 4

125°C 2.3 2.4

25°C 59° 62°

φ

m

Phase margin at unity

VI = 10 mV,pRL = 2 kΩ,

–55°C 57° 61°

gain

C

L

= 25 F,

See Figure 4

125°C 59° 62°

†

For V

CC±

= ±5 V, V

I(PP)

= ±1 V; for V

CC±

= ±15 V, V

I(PP)

= ±5 V.

‡

This parameter is tested on a sample basis for the TL051A. For other test requirements, please contact the factory. This statement has no bearing

on testing or nontesting of other parameters.

§

For V

CC±

= ±5 V, VOrms = 1 V; for V

CC±

= ±15 V, VOrms = 6 V.

TL05x, TL05xA, TL05xY

ENHANCED-JFET LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS178 – FEBRUARY 1997

14

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TL051Y electrical characteristics, TA = 25°C

TL051Y

PARAMETER TEST CONDITIONS

VCC ± = ± 5 V VCC ± = ± 15 V

UNIT

MIN TYP MAX MIN TYP MAX

p

V

= 0, V

= 0,

VIOInput offset voltage

O

,

RS = 50 Ω

IC

,

0.75

0.59

mV

p

V

= 0, V

= 0,

p

IIOInput offset current

O

,

IC

,

See Figure 5

45pA

p

V

= 0, V

= 0,

p

IIBInput bias current

O

,

IC

,

See Figure 5

2030pA

V

ICR

Common-mode input voltage range

–2.3

to

5.6

–12.3

to

15.6

V

Maximum positive peak output voltage

RL = 10 kΩ 4.2 13.9

V

OM+

g

swing

RL = 2 kΩ

3.8 12.7

V

Maximum negative peak output voltage

RL = 10 kΩ –3.5 –13.2

V

OM –

gg

swing

RL = 2 kΩ

–3.2 –12

V

A

VD

Large-signal differential voltage

amplification

†

RL = 2 kΩ 59 105 V/mV

r

i

Input resistance 10

12

10

12

Ω

c

i

Input capacitance 10 12 pF

CMRR Common-mode rejection ratio

VIC = V

ICR

min,

VO = 0, RS = 50 Ω

85 93 dB

k

SVR

Supply-voltage rejection ratio

(∆V

CC±

/∆VIO)

VO = 0, RS = 50 Ω 99 99 dB

I

CC

Supply current VO = 0, No load 2.6 2.7 mA

†

For V

CC±

= ±5 V, VO = ±2.3 V, or for V

CC±

= ± 15 V, V

O

= ±10 V.

TL05x, TL05xA, TL05xY

ENHANCED-JFET LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS178 – FEBRUARY 1997

15

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TL051Y operating characteristics, T

A

= 25°C

TL051Y

PARAMETER TEST CONDITIONS

V

CC±

= ±5 V V

CC±

= ±15 V

UNIT

MIN TYP MAX MIN TYP MAX

SR+

Positive slew rate at unity gain

†

R

= 2 kΩ,C

= 100 pF,

16 20

SR–

Negative slew rate at unity gain

†

L

,

L

,

See Figure 1

15 18

V/µs

t

r

Rise time

V

I(PP)

= ±10 mV ,

55 56

t

f

Fall time

()

RL = 2 kΩ,

=

p

55 57

ns

Overshoot factor

C

L

=

100 F

,

See Figures 1 and 2

24% 19%

f = 10 Hz 75 75

V

n

Equival

ent input noise voltage

‡

RS = 20 Ω,

f = 1 kHz 18 18

n

V/√H

z

V

N(PP)

Peak-to-peak equivalent input

noise voltage

See Figure 3

f = 10 Hz to

10 kHz

4 4 µV

I

n

Equivalent input noise current f = 1 kHz 0.01 0.01 pA/√Hz

THD Total harmonic distortion

§

RS = 1 kΩ,RL = 2 kΩ,

f = 1 kHz

0.003% 0.003%

B

1

Unity-gain bandwidth

VI = 10 mV, RL = 2 kΩ,

CL = 25 pF, See Figure 4

3 3.1 MHz

φ

m

Phase margin at unity gain

VI = 10 mV, RL = 2 kΩ,

CL = 25 pF, See Figure 4

59° 62°

†

For V

CC±

= ±5 V, V

I(PP)

= ±1 V; for V

CC±

= ±15 V, V

I(PP)

= ±5 V.

‡

This parameter is tested on a sample basis for the TL051A. For other test requirements, please contact the factory. This statement has no bearing

on testing or nontesting of other parameters.

§

For V

CC±

= ±5 V, VOrms = 1 V; for V

CC±

= ±15 V, VOrms = 6 V.

TL05x, TL05xA, TL05xY

ENHANCED-JFET LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS178 – FEBRUARY 1997

16

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TL052C and TL052AC electrical characteristics at specified free-air temperature

TL052C, TL052AC

PARAMETER TEST CONDITIONS

T

A

†

V

CC±

= ±5 V V

CC±

= ±15 V

UNIT

A

MIN TYP MAX MIN TYP MAX

25°C 0.73 3.5 0.65 1.5

p

TL052C

Full range 4.5 2.5

VIOInput offset voltage

25°C 0.51 2.8 0.4 0.8

mV

VO = 0,

TL052AC

Full range 3.8 1.8

V

IC

= 0,

R

= 50 Ω

25°C to

T emperature coef ficient

R

S

50

Ω

TL052C

70°C

8

8

°

α

VIO

of input offset voltage

‡

25°C to

µ

V/°C

TL052AC

70°C

8625

Input offset voltage longterm drift

§

VO = 0,

RS = 50 Ω

VIC = 0, 25°C 0.04 0.04 µV/mo

p

V

= 0,

25°C 4 100 5 100 pA

IIOInput offset current

O

,

See Figure 5

V

IC

=

0

,

70°C

0.02 1 0.025 1 nA

p

V

= 0,

25°C 20 200 30 200 pA

IIBInput bias current

O

,

See Figure 5

V

IC

=

0

,

70°C

0.15 4 0.2 4 nA

Common-mode input

25°C

–1

to

4

–2.3

to

5.6

–11

to

11

–12.3

to

15.6

V

ICR

voltage range

Full range

–1

to

4

–11

to

11

V

25°C 3 4.2 13 13.9

Maximum positive peak

R

L

= 10

kΩ

Full range 3 13

V

OM+

output voltage swing

25°C 2.5 3.8 11.5 12.7

V

R

L

= 2

kΩ

Full range 2.5 11.5

25°C –2.5 –3.5 –12 –13.2

Maximum negative peak

R

L

=

10 kΩ

Full range –2.5 –12

V

OM–

g

output voltage swing

25°C –2.3 –3.2 –11 –12

V

R

L

= 2

kΩ

Full range –2.3 –11

25°C 25 59 50 105

A

VD

Large-signal differential

p

¶

RL = 2 kΩ

0°C 30 65 60 129

V/mV

voltage am lification

¶

70°C 20 46 30 85

r

i

Input resistance 25°C

10

12

10

12

Ω

c

i

Input capacitance 25°C 10 12 pF

25°C 65 85 75 93

CMRR

C

ommon-mode

V

IC

=

V

ICR

min,

=

RS = 50 Ω

0°C

65 84 75 92

dB

rejection ratio

V

O

= 0,

70°C 65 84 75 91

†

Full range is 0°C to 70°C.

‡

This parameter is tested on a sample basis. For other test requirements, please contact the factory. This statement has no bearing on testing

or nontesting of other parameters.

§

Typical values are based on the input offset voltage shift observed through 168 hours of operating life test at TA = 150°C extrapolated to

TA = 25°C using the Arrhenius equation and assuming an activation energy of 0.96 eV .

¶

For V

CC±

= ±5 V, VO = ±2.3 V; at V

CC±

= ±15 V, VO = ±10 V.

TL05x, TL05xA, TL05xY

ENHANCED-JFET LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS178 – FEBRUARY 1997

17

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TL052C and TL052AC electrical characteristics at specified free-air temperature (continued)

TL052C, TL052AC

PARAMETER TEST CONDITIONS

T

A

V

CC±

= ±5 V V

CC±

= ±15 V

UNIT

A

MIN TYP MAX MIN TYP MAX

25°C 75 99 75 99

k

SVR

Supply-voltage rejection

VO = 0, RS = 50 Ω

0°C

75 98 75 98

dB

ratio (∆V

CC ±

/∆VIO)

70°C 75 97 75 97

25°C 4.6 5.6 4.8 5.6

I

CC

Supply current

p

VO = 0, No load

0°C

4.7 6.4 4.8 6.4

mA

(two am lifiers)

70°C 4.4 6.4 4.6 6.4

VO1/V

O2

Crosstalk attenuation AVD = 100 25°C 120 120 dB

TL052C and TL052AC operating characteristics at specified free-air temperature

TL052C, TL052AC

PARAMETER TEST CONDITIONS

T

A

†

V

CC±

= ± 5 V V

CC±

= ± 15 V

UNIT

A

MIN TYP MAX MIN TYP MAX

25°C 17.8 9 20.7

SR +Slew rate at unity gain

RL = 2 kΩ, CL = 100 pF,

Full range

8

Negative slew rate

See Figure 1

25°C 15.4 9 17.8

V/µs

SR

–

g

at unity gain

‡

Full range 8

25°C 55 56

t

r

Rise time

0°C 54 55

70°C 63 63

V

I(PP)

= ±10 mV,

25°C 55 57

ns

t

f

Fall time

()

RL = 2 kΩ,

p

0°C 54 56

C

L

=

100 F

,

See Fi

g

ures 1 and 2

70°C 62 64

g

25°C 24% 19%

Overshoot factor

0°C 24% 19%

70°C 24% 19%

Equivalent input noise

f = 10 Hz 25°C 71 71

V

n

q

voltage

§

RS = 20 Ω,

f = 1 kHz 25°C 19 19 30

n

V/√H

z

V

N(PP)

Peak-to-peak equivalent

input noise current

See Figure 3

f =

10 Hz t

10 kHz

25°C 4 4 µV

I

n

Equivalent input

noise current

f = 1 kHz 25°C 0.01 0.01 pA/√Hz

THD T otal harmonic distortion

¶

RS = 1 kΩ,

f = 1 kHz

RL = 2 kΩ,

25°C 0.003% 0.003%

25°C 3 3

B

1

Unity-gain bandwidth

VI = 10 mV,

p

RL = 2 kΩ,

0°C 3.2 3.2

MHz

C

L

= 25 F,

See Figure 4

70°C 2.6 2.7

25°C 60° 63°

φ

m

Ph

ase margin at unity

V

I

= 10 mV,

=

p

R

L

= 2 kΩ,

0°C 59° 63°

gain

C

L

= 25 F,

See Figure 4

70°C 60° 63°

†

Full range is 0°C to 70°C.

‡

For V

CC±

= ±5 V, V

I(PP)

= ±1 V; for V

CC±

= ±15 V, V

I(PP)

= ±5 V.

§

This parameter is tested on a sample basis. For other test requirements, please contact the factory. This statement has no bearing on testing

or nontesting of other parameters.

¶

For V

CC±

= ±5 V, V

O(RMS)

= 1 V; for V

CC±

= ±15 V, V

O(RMS)

= 6 V.

TL05x, TL05xA, TL05xY

ENHANCED-JFET LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS178 – FEBRUARY 1997

18

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TL052I and TL052AI electrical characteristics at specified free-air temperature

TL052I, TL052AI

PARAMETER TEST CONDITIONS

T

A

†

V

CC±

= ±5 V V

CC±

= ±15 V

UNIT

A

MIN TYP MAX MIN TYP MAX

25°C 0.73 3.5 0.65 1.5

p

TL052I

Full range 5.3 3.3

VIOInput offset voltage

25°C 0.51 2.8 0.4 0.8

mV

V

O

= 0,

=

TL052AI

Full range 4.6 2.6

V

IC

= 0,

RS = 50 Ω

TL052I

25°C to

85°C

7 6

°

α

VIO

T

emperature coe

ffici

ent

‡

TL052AI

25°C to

85°C

6 6 25

µ

V/°C

Input offset voltage longterm drift

§

VO = 0,

RS = 50 Ω

VIC = 0, 25°C 0.04 0.04 µV/mo

p

V

= 0, V

= 0,

25°C 4 100 5 100 pA

IIOInput offset current

O

,

See Figure 5

IC

,

85°C 0.06 10 0.07 10 nA

p

V

= 0, V

= 0,

25°C 20 200 30 200 pA

IIBInput bias current

O

,

See Figure 5

IC

,

85°C 0.6 20 0.7 20 nA

Common-mode input

25°C

–1

to

4

–2.3

to

5.6

–11

to

11

–12.3

to

15.6

V

ICR

voltage range

Full range

–1

to

4

–11

to

11

V

25°C 3 4.2 13 13.9

Maximum positive peak

R

L

= 10

kΩ

Full range 3 13

V

OM+

output voltage swing

25°C 2.5 3.8 11.5 12.7

V

R

L

=

2 kΩ

Full range 2.5 11.5

25°C –2.5 –3.5 –12 –13.2

Maximum negative peak

R

L

= 10

kΩ

Full range –2.5 –12

V

OM–

g

output voltage swing

25°C –2.3 –3.2 –11 –12

V

R

L

= 2

kΩ

Full range –2.3 –11

25°C 25 59 50 105

A

VD

Large-signal differential

p

¶

RL = 2 kΩ

–40°C 30 74 60 145

V/mV

voltage am lification

¶

85°C 20 43 30 76

r

i

Input resistance 25°C 10

12

10

12

Ω

c

i

Input capacitance 25°C 10 12 pF

25°C 65 85 75 93

CMRR

C

ommon-mode

V

IC

=

V

ICR

min,

=

RS = 50 Ω

–40°C

65 83 75 90

dB

rejection ratio

V

O

= 0,

85°C 65 84 75 93

†

Full range is –40°C to 85°C.

‡

This parameter is tested on a sample basis. For other test requirements, please contact the factory. This statement has no bearing on testing

or nontesting of other parameters

§

Typical values are based on the input offset voltage shift observed through 168 hours of operating life test at TA = 150°C extrapolated to

TA = 25°C using the Arrhenius equation and assuming an activation energy of 0.96 eV.

¶

At V

CC±

= ± 5 V, VO = ± 2.3 V; at V

CC±

= ±15 V, VO = ±10 V.

TL05x, TL05xA, TL05xY

ENHANCED-JFET LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS178 – FEBRUARY 1997

19

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TL052I and TL052AI electrical characteristics at specified free-air temperature (continued)

TL052I, TL052AI

PARAMETER TEST CONDITIONS

T

A

V

CC±

= ±5 V V

CC±

= ±15 V

UNIT

A

MIN TYP MAX MIN TYP MAX

25°C 75 99 75 99

k

SVR

Supply-voltage rejection

VO = 0, RS = 50 Ω

–40°C

75 98 75 98

dB

ratio (∆V

CC±

/∆VIO)

85°C 75 99 75 99

25°C 4.6 5.6 4.8 5.6

I

CC

Supply current

p

VO = 0, No load

–40°C

4.5 6.4 4.7 6.4

mA

(two am lifiers)

85°C 4.4 6.4 4.6 6.4

VO1/V

O2

Crosstalk attenuation AVD = 100 25°C 120 120 dB

TL052I and TL052AI operating characteristics at specified free-air temperature

TL052I, TL052AI

PARAMETER TEST CONDITIONS

T

A

†

V

CC±

= ± 5 V V

CC±

= ± 15 V

UNIT

A

MIN TYP MAX MIN TYP MAX

25°C 17.8 9 20.7

SR

+

Sl

ew rate at unity gain

‡

R

= 2 kΩ, C

= 100 pF,

Full range 8

Negative slew rate at

L

,

L

,

See Figure 1

25°C 15.4 9 17.8

V/µs

SR

–

g

unity gain

‡

Full range 8

25°C 55 56

t

r

Rise time

–40°C 52 53

85°C 64 65

=

25°C 55 57

ns

t

f

Fall time

V

I(PP)

=

±10 mV

,

RL = 2 kΩ, CL = 100 pF,

–40°C 51 53

See Figures 1 and 2

85°C 64 65

25°C 24% 19%

Overshoot factor

–40°C 24% 19%

85°C 24% 19%

Equivalent input noise

f = 10 Hz 25°C 71 71

V

n

q

voltage

§

RS = 20 Ω,

f = 1 kHz 25°C 19 19 30

V

N(PP)

Peak-to-peak equivalent

input noise current

See Figure 3

f =

10 Hz to

10 kHz

25°C 4 4 µV

I

n

Equivalent input noise

current

f = 1 kHz 25°C 0.01 0.01 pA/√Hz

THD T otal harmonic distortion

¶

RS = 1 kΩ,

f = 1 kHz

RL = 2 kΩ,

25°C 0.003% 0.003%

25°C 3 3

B

1

Unity-gain bandwidth

VI = 10 mV,

p

RL = 2 kΩ,

–40°C 3.5 3.6

MHz

C

L

= 25 F,

See Figure 4

85°C 2.5 2.6

25°C 60° 63°

φ

m

Ph

ase margin at unity

V

I

= 10 mV,

=

p

R

L

= 2 kΩ,

–40°C 58° 61°

gain

C

L

= 25 F,

See Figure 4

85°C 60° 63°

†

Full range is –40°C to 85°C.

‡

For V

CC±

= ±5 V, V

I(PP)

= ±1 V; for V

CC±

= ±15 V, V

I(PP)

= ±5 V.

§

This parameter is tested on a sample basis. For other test requirements, please contact the factory. This statement has no bearing on testing

or nontesting of other parameters.

¶

For V

CC±

= ±5 V, V

O(RMS)

= 1 V; for V

CC±

= ±15 V, V

O(RMS)

= 6 V.

TL05x, TL05xA, TL05xY

ENHANCED-JFET LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS178 – FEBRUARY 1997

20

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TL052M and TL052AM electrical characteristics at specified free-air temperature

TL052M, TL052AM

PARAMETER TEST CONDITIONS

T

A

†

V

CC±

= ± 5 V V

CC±

= ± 15 V

UNIT

A

MIN TYP MAX MIN TYP MAX

25°C 0.73 3.5 0.65 1.5

p

TL052M

Full range 6.5 4.5

VIOInput offset voltage

25°C 0.51 2.8 0.4 0.8

mV

V

O

= 0,

TL052AM

Full range 5.8 3.8

V

IC

= 0,

R

= 50 Ω

25°C to

T emperature coef ficient

R

S

50

Ω

TL052M

125°C

10

9

°

α

VIO

of input offset voltage

TL052AM

25°C to

125°C

9 8

µV/°C

Input offset voltage longterm drift

‡

VO = 0,

RS = 50 Ω

VIC = 0,

25°C 0.04 0.04 µV/mo

p

VO = 0, VIC = 0,

25°C 4 100 5 100 pA

IIOInput offset current

O

See Figure 5

IC

125°C 1 20 2 20 nA

p

VO = 0,

VIC = 0,

25°C 20 200 30 200 pA

IIBInput bias current

O

See Figure 5

125°C 10 50 20 50 nA

Common-mode input

25°C

–1

to

4

–2.3

to

5.6

–11

to

11

–12.3

to

15.6

V

ICR

voltage range

Full range

–1

to

4

–11

to

11

V

25°C 3 4.2 13 13.9

Maximum positive peak

R

L

= 10

kΩ

Full range 3 13

V

OM+

output voltage swing

25°C 2.5 3.8 11.5 12.7

V

R

L

= 2

kΩ

Full range 2.5 11.5

25°C –2.5 –3.5 –12 –13.2

Maximum negative peak

R

L

= 10

kΩ

Full range –2.5 –12

V

OM–

g

output voltage swing

25°C –2.3 –3.2 –11 –12

V

R

L

= 2

kΩ

Full range –2.3 –11

25°C 25 59 50 105

A

VD

L

arge-signal

diff

erentia

l

p

§

RL = 2 kΩ

–55°C 30 76 60 149

V/mV

voltage am lification

§

125°C 10 32 15 49

r

i

Input resistance 25°C

10

12

10

12

Ω

c

i

Input capacitance 25°C 10 12 pF

V

= V

min

,

25°C 65 85 75 93

CMRR

C

ommon-mode

V

IC

V

ICR

min,

VO = 0,

–55°C 65 83 75 92

dB

rejection ratio

RS = 50 Ω

125°C 65 84 75 94

25°C 75 99 75 99

k

SVR

S

upply-voltage rejection

VO = 0, RS = 50 Ω

–55°C

75 98 75 98

dB

ratio (∆V

CC±

/∆VIO)

125°C 75 100 75 100

25°C 4.6 5.6 4.8 5.6

I

CC

S

upply curren

t

p

VO = 0, No load

–55°C

4.4 6.4 4.5 6.4

mA

(two am lifiers)

125°C 4.2 6.4 4.4 6.4

VO1/V

O2

Crosstalk attenuation AVD = 100 25°C 120 120 dB

†

Full range is – 55°C to 125°C.

‡

Typical values are based on the input offset voltage shift observed through 168 hours of operating life test at TA = 150°C extrapolated to

TA = 25°C using the Arrhenius equation and assuming an activation energy of 0.96 eV .

§

For V

CC±

= ± 5 V, VO = ± 2.3 V; at V

CC±

= ±15 V, VO = ±10 V.

TL05x, TL05xA, TL05xY

ENHANCED-JFET LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS178 – FEBRUARY 1997

21

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TL052M and TL052AM operating characteristics at specified free-air temperature

TL052M, TL052AM

PARAMETER TEST CONDITIONS

T

A

†

V

CC±

= ± 5 V V

CC±

= ± 15 V

UNIT

A

MIN TYP MAX MIN TYP MAX

Positive slew rate

25°C 17.8 9 20.7

SR

+

at unity gain

‡

RL = 2 kΩ,

p

Full range 8

Negative slew rate

C

L

=

100 pF

,

See

Figure 1

25°C 15.4 9 17.8

V/µs

SR

–

g

at unity gain

‡

See Figure 1

Full range 8

25°C 55 56

t

r

Rise time

–55°C 51 52

125°C 68 68

V

I(PP)

= ± 10 mV,

25°C 55 57

ns

t

f

Fall time

()

RL = 2 kΩ,

p

–55°C 51 52

C

L

=

100 F

,

See Fi

g

ures 1 and 2

125°C 68 69

g

25°C 24% 19%

Overshoot factor

–55°C 25% 19%

125°C 25% 19%

Equivalent input noise

f = 10 Hz 25°C 71 71

V

n

q

voltage

§

f = 1 kHz 25°C 19 19

n

V/√H

z

V

N(PP)

Peak-to-peak

equivalent input noise

current

R

S

= 20 Ω,

See Figure 3

f =

10 Hz

to

10 kHz

25°C 4 4 µV

I

n

Equivalent input

noise current

f = 1 kHz 25°C 0.01 0.01 pA/√Hz

THD

Total harmonic

distortion

¶

RS = 1 kΩ,

f = 1 kHz

RL = 2 kΩ,

25°C 0.003% 0.003%

25°C 3 3

B

1

Unity-gain bandwidth

VI = 10 mV,

p

RL = 2 kΩ,

–55°C 3.6 3.7

MHz

C

L

= 25 F,

See Figure 4

125°C 2.3 2.4

25°C 60° 63°

φ

m

Phase margin at unity

VI = 10 mV,pRL = 2 kΩ,

–55°C 57° 61°

gain

C

L

= 25 F,

See Figure 4

125°C 60° 63°

†

Full range is – 55°C to 125°C.

‡

For V

CC±

= ±5 V, V

I(PP)

= ±1 V; for V

CC±

= ±15 V, V

I(PP)

= ±5 V.

§

This parameter is tested on a sample basis. For other test requirements, please contact the factory. This statement has no bearing on testing

or nontesting of other parameters.

¶

For V

CC±

= ±5 V, V

O(RMS)

= 1 V; for V

CC±

= ±15 V, V

O(RMS)

= 6 V.

TL05x, TL05xA, TL05xY

ENHANCED-JFET LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS178 – FEBRUARY 1997

22

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TL052Y electrical characteristics, TA = 25°C

TL052Y

PARAMETER TEST CONDITIONS

V

CC±

= ± 5 V V

CC±

= ± 15 V

UNIT

MIN TYP MAX MIN TYP MAX

V

IO

Input offset voltage

0.73 0.65 mV

Input offset voltage long-term

drift

V

O

= 0,

RS = 50 Ω

VIC = 0,

0.04 0.04 µV/mo

I

IO

Input offset current

VO = 0,

See Figure 5

VIC = 0,

4 5 pA

I

IB

Input bias current

VO = 0,

See Figure 5

VIC = 0,

20 30 pA

V

ICR

Common-mode input voltage

range

–2.3

to

5.6

–12.3

to

15.6

V

Maximum positive peak

RL = 10 kΩ 4.2 13.9

V

OM+

output voltage swing

RL = 2 kΩ

3.8 12.7

Maximum negative peak output

RL = 10 kΩ –3.5 –13.2

V

V

OM–

g

voltage swing

RL = 2 kΩ

–3.2 –12

A

VD

Large-signal differential

voltage amplification

†

RL = 2 kΩ 59 105 V/mV

r

i

Input resistance

10

12

10

12

Ω

c

i

Input capacitance 10 12 pF

CMRR Common-mode rejection ratio

VIC = V

ICR

min,

VO = 0,

RS = 50 Ω

85 93 dB

k

SVR

Supply-voltage rejection ratio

(∆V

CC±

/∆VIO)

VO = 0, RS = 50 Ω 99 99 dB

I

CC

Supply current (two amplifiers) VO = 0, No load 4.6 4.8 mA

VO1/V

O2

Crosstalk attenuation AVD = 100 120 120 dB

†

For V

CC±

= ±5 V, VO = ±2.3 V; at V

CC±

= ±15 V, VO = ±10 V.

TL05x, TL05xA, TL05xY

ENHANCED-JFET LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS178 – FEBRUARY 1997

23

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TL052Y operating characteristics, TA = 25°C

TL052Y

PARAMETER TEST CONDITIONS

V

CC±

= ±5 V V

CC±

= ±15 V

UNIT

MIN TYP MAX MIN TYP MAX

SR +

Positive slew rate at

unity gain

†

R

= 2 kΩ, C

= 100 pF,

17.8 20.7

SR –

Negative slew rate at

unity gain

†

L

,

L

,

See Figure 1

15.4 17.8

V/µs

t

r

Rise time

=

55 56

t

f

Fall time

V

I(PP)

=

±10 mV

,

RL = 2 kΩ, CL = 100 pF,

55 57

ns

Overshoot factor

See Figures 1 and 2

24% 19%

Equivalent input noise

f = 10 Hz 71 71

V

n

q

voltage

‡

RS = 20 Ω,

f = 1 kHz 19 19

n

V/√H

z

V

N(PP)

Peak-to-peak equivalent input

noise current

See Figure 3

f = 10 Hz to 10 kHz 4 4 µV

I

n

Equivalent input noise

current

f = 1 kHz 0.01 0.01 pA/√Hz

THD

Total harmonic distortion

§

RS = 1 kΩ,

f = 1 kHz

RL = 2 kΩ,

0.003% 0.003%

B

1

Unity-gain bandwidth

VI = 10 mV,

CL = 25 pF,

RL = 2 kΩ,

See Figure 4

3 3

MHz

φ

m

Phase margin at unity gain

VI = 10 mV,

CL = 25 pF,

RL = 2 kΩ,

See Figure 4

60° 63°

†

This parameter is tested on a sample basis. For other test requirements, please contact the factory. This statement has no bearing on testing

or nontesting of other parameters.

‡

For V

CC±

= ±5 V, V

I(PP)

= ±1 V; for V

CC±

= ±15 V, V

I(PP)

= ±5 V.

§

For V

CC±

= ±5 V, V

O(RMS)

= 1 V; for V

CC±

= ±15 V, V

O(RMS)

= 6 V.

TL05x, TL05xA, TL05xY

ENHANCED-JFET LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS178 – FEBRUARY 1997

24

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TL054C and TL054AC electrical characteristics at specified free-air temperature

TL054C, TL054AC

PARAMETER TEST CONDITIONS

T

A

†

VCC ± = ± 5 V VCC ± = ± 15 V

UNIT

MIN TYP MAX MIN TYP MAX

25°C 0.64 5.5 0.56 4

p

TL054C

Full range 7.7 6.2

VIOInput offset voltage

25°C 0.57 3.5 0.5 1.5

mV

TL054AC

Full range 5.7 3.7

T emperature coef ficient

V

O

= 0,

VIC = 0,

R

= 50 Ω

TL054C

25°C to

70°C

25 23

°

α

VIO

of input offset voltage

R

S

50

Ω

TL054AC

25°C to

70°C

24 23

µ

V/°C

Input offset voltage

long-term drift

‡

25°C 0.04 0.04 µV/mo

p

VO = 0, VIC = 0,

25°C 4 100 5 100 pA

IIOInput offset current

OIC

See Figure 5

70°C 0.02 1 0.025 1 nA

p

VO = 0, VIC = 0,

25°C 20 200 30 200 pA

IIBInput bias current

OIC

See Figure 5

70°C 0.15 4 0.2 4 nA

Common-mode input

25°C

–1

to

4

–2.3

to

5.6

–11

to

11

–12.3

to

15.6

V

ICR

voltage range

Full range

–1

to

4

–11

to

11

V

25°C 3 4.2 13 13.9

Maximum positive peak

R

L

=

10 kΩ

Full range 3 13

V

OM +

output voltage swing

25°C 2.5 3.8 11.5 12.7

V

R

L

= 2

kΩ

Full range 2.5 11.5

25°C –2.5 –3.5 –12 –13.2

Maximum negative peak

R

L

= 10

kΩ

Full range –2.5 –12

V

OM –

g

output voltage swing

25°C –2.3 –3.2 –11 –12

V

R

L

=

2 kΩ

Full range –2.3 –11

25°C 25 72 50 133

A

VD

L

arge-signal

diff

erentia

l

p

RL = 2 kΩ 0°C 30 88 60 173 V/mV

voltage am lification

§

70°C 20 57 30 85

r

i

Input resistance 25°C

10

12

10

12

Ω

c

i

Input capacitance 25°C 10 12 pF

25°C 65 84 75 92

CMRR

C

ommon-mode

V

IC

=

V

ICR

min,

0°C 65 84 75 92 dB

rejection ratio

V

O

= 0,

R

S

= 50

Ω

70°C 65 84 75 93

25°C 75 99 75 99

k

SVR

S

upply-voltage rejection

V

CC±

= ±5 V to ±15 V,

0°C 75 99 75 99 dB

ratio (∆V

CC±

/∆VIO)

V

O

= 0,

R

S

= 50

Ω

70°C 75 99 75 99

25°C 8.1 11.2 8.4 11.2

I

CC

S

upply curren

t

p

VO = 0, No load 0°C 8.2 12.8 8.5 12.8 mA

(four am lifiers)

70°C 7.9 11.2 8.2 11.2

VO1/VO2Crosstalk attenuation AVD = 100 25°C 120 120 dB

†

Full range is 0°C to 70°C.

‡

Typical values are based on the input offset voltage shift observed through 168 hours of operating life test at TA = 150°C extrapolated to

TA = 25°C using the Arrhenius equation and assuming an activation energy of 0.96 eV .

§

For V

CC±

= ±5 V, VO = ±2.3 V, at V

CC±

= ±15 V, VO = ±10 V.B

TL05x, TL05xA, TL05xY

ENHANCED-JFET LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS178 – FEBRUARY 1997

25

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TL054C and TL054AC operating characteristics at specified free-air temperature

TL054C, TL054C

PARAMETER TEST CONDITIONS

T

A

†

V

CC±

= ±5 V V

CC±

= ±15 V

UNIT

MIN TYP MAX MIN TYP MAX

Positive slew rate

25°C 15.4 10 17.8

SR

+

at unity gain

0°C 15.7 8 17.9

RL = 2 kΩ,CL = 100 pF,

70°C 14.4 8 17.5

Negative slew rate at

L L

See Figure 1 and Note 7

25°C 13.9 10 15.9

V/µs

SR

–

g

unity gain

‡

0°C 14.3 8 16.1

70°C 13.3 8 15.5

25°C 55 56

t

r

Rise time 0°C 54 55

70°C 63 63

V

I(PP)

= ±10 mV ,

25°C 55 57

ns

t

f

Fall time

R

L

= 2 kΩ,

p

0°C 54 56

C

L

=

100 F

,

See Fi

g

ures 1 and 2

70°C 62 64

See Figures 1 and 2

25°C 24% 19%

Overshoot factor 0°C 24% 19%

70°C 24% 19%

Equivalent input noise

f = 10 Hz 25°C 75 75

V

n

q

voltage

§

RS = 20 Ω,

f = 1 kHz 25°C 21 21 45

nV/√Hz

V

N(PP)

Peak-to-peak equivalent

input noise voltage

See Figure 3

f = 10 Hz to

10 kHz

25°C 4 4 µV

I

n

Equivalent input

noise current

f = 1 kHz 25°C 0.01 0.01

pA/√Hz

THD

Total harmonic

distortion

¶

RS = 1 kΩ,

f = 1 kHz

RL = 2 kΩ,

25°C 0.003% 0.003%

25°C 2.7 2.7

B

1

Unity-gain bandwidth

V

I

= 10 mV,

R

L

= 2 kΩ,

p

0°C 3 3 MHz

C

L

= 25 F,

See Figure 4

70°C 2.4 2.4

25°C 61° 64°

φ

m

Phase margin at

V

I

= 10 mV,

R

L

= 2 kΩ,

=

p

0°C 60° 64°

unity gain

C

L

= 25 F,

See Figure 4

70°C 61° 63°

†

Full range is 0°C to 70°C.

‡

For V

CC±

= ±5 V, V

I(PP)

= ±1 V; for V

CC±

= ±15 V, V

I(PP)

= ±5 V.

§

This parameter is tested on a sample basis. For other test requirements, please contact the factory. This statement has no bearing on testing

or nontesting of other parameters.

¶

For V

CC±

= ±5 V, V

o(rms

) = 1 V; for V

CC±

= ±15 V, V

o(rms)

= 6 V.

TL05x, TL05xA, TL05xY

ENHANCED-JFET LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS178 – FEBRUARY 1997

26

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TL054I and TL054AI electrical characteristics at specified free-air temperature

TL054I, TL054AI

PARAMETER TEST CONDITIONS

T

A

†

V

CC±

= ±5 V V

CC±

= ±15 V UNIT

A

MIN TYP MAX MIN TYP MAX

25°C

0.64 5.5 0.56 4

p

TL054I

Full range 8.8 7.3

VIOIn ut offset voltage

25°C 0.57 3.5 0.5 1.5

mV

TL054AI

Full range 6.8 4.8

T emperature coef ficient of

V

O

= 0,

VIC = 0,

R

= 50 Ω

TL054I

25°C to

85°C

25 24

°

α

VIO

input offset voltage

R

S

50

Ω

TL054AI

25°C to

85°C

25 23

µ

V/°C

Input offset voltage

long-term drift

‡

25°C 0.04 0.04 µV/mo

p

VO = 0, VIC = 0,

25°C 4 100 5 100 pA

IIOInput offset current

OIC

See Figure 5

85°C 0.06 10 0.07 10 nA

p

VO = 0, VIC = 0,

25°C 20 200 30 200 pA

IIBInput bias current

OIC

See Figure 5

85°C 0.6 20 0.7 20 nA

Common-mode input

25°C

–1

to

4

–2.3

to

5.6

–11

to

11

–12.3

to

15.6

V

ICR

voltage range

Full range

–1

to

4

–11

to

11

V

25°C 3 4.2 13 13.9

Maximum positive peak

R

L

=

10 kΩ

Full range 3 13

V

OM +

output voltage swing

25°C 2.5 3.8 11.5 12.7

V

R

L

= 2

kΩ

Full range 2.5 11.5

25°C –2.5 –3.5 –12 –13.2

Maximum negative peak

R

L

= 10

kΩ

Full range –2.5 –12

V

OM –

g

output voltage swing

25°C –2.3 –3.2 –11 –12

V

R

L

=

2 kΩ

Full range –2.3 –11

25°C 25 72 50 133

A

VD

L

arge-signal

diff

erentia

l

p

RL = 2 kΩ –40°C 30 101 60 212 V/mV

voltage am lification

§

85°C 20 50 30 70

r

i

Input resistance 25°C

10

12

10

12

Ω

c

i

Input capacitance 25°C 10 12 pF

25°C 65 84 75 92

CMRR

C

ommon-mode

V

IC

=

V

ICR

min,

–40°C 65 83 75 92 dB

rejection ratio

V

O

= 0,

R

S

= 50

Ω

85°C 65 84 75 93

25°C 75 99 75 99

k

SVR

S

upply-voltage rejection

V

CC±

= ±

5 V t

o ±15 V,

–40°C 75 98 75 99 dB

ratio (∆V

CC±

/∆VIO)

V

O

= 0,

R

S

= 50

Ω

85°C 75 99 75 99

25°C 8.1 11.2 8.4 11.2

I

CC

S

upply curren

t

p

VO = 0, No load –40°C 7.9 12.8 8.2 12.8 mA

(four am lifiers)

85°C 7.6 11.2 7.9 11.2

VO1/VO2Crosstalk attenuation AVD = 100 25°C 120 120 dB

†

Full range is –40°C to 85°C.

‡

Typical values are based on the input offset voltage shift observed through 168 hours of operating life test at TA = 150°C extrapolated to

TA = 25°C using the Arrhenius equation and assuming an activation energy of 0.96 eV .

§

For V

CC±

= ±5 V, VO = ±2.3 V, at V

CC±

= ±15 V, VO = ±10 V.

TL05x, TL05xA, TL05xY

ENHANCED-JFET LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS178 – FEBRUARY 1997

27

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TL054I and TL054AI operating characteristics at specified free-air temperature

TL054I, TL054AI

PARAMETER TEST CONDITIONS

T

A

†

V

CC±

= ±5 V V

CC±

= ±15 V UNIT

A

MIN TYP MAX MIN TYP MAX

Positive slew rate

25°C 15.4 10 17.8

SR

+

at unity gain

–40°C 16.4 8 18

RL = 2 kΩ,CL = 100 pF,

85°C 14 8 17.3

Negative slew rate at

L L

See Figure 1

25°C 13.9 10 15.9

V/µs

SR

–

g

unity gain

‡

–40°C 14.7 8 16.1

85°C 13 8 15.3

25°C 55 56

t

r

Rise time –40°C 52 53

85°C 64 65

V

= ±10 mV, R

= 2 kΩ

,

25°C 55 57

ns

t

f

Fall time

V

I(PP)

±10 mV, R

L

2

kΩ,

CL = 100 pF,

–40°C 51 53

See Figures 1 and 2

85°C 64 65

25°C 24% 19%

Overshoot factor –40°C 24% 19%

85°C 24% 19%

Equivalent input noise

f = 10 Hz 25°C 75 75

V

n

q

voltage

§

RS = 20 Ω,

f = 1 kHz 25°C 21 21 45

nV/√Hz

V

N(PP)

Peak-to-peak equivalent

input noise voltage

See Figure 3

f = 10 Hz to

10 kHz

25°C 4 4 µV

I

n

Equivalent input

noise current

f = 1 kHz 25°C 0.01 0.01 pA/√Hz

THD

Total harmonic distortion

¶

RS = 1 kΩ,

f = 1 kHz

RL = 2 kΩ,

25°C 0.003% 0.003%

25°C 2.7 2.7

B

1

Unity-gain bandwidth

V

I

= 10 mV,

R

L

= 2 kΩ,

p

–40°C 3.3 3.3 MHz

C

L

= 25 F,

See Figure 4

85°C 2.3 2.4

25°C 61° 64°

φ

m

Phase margin at

V

I

=

10 mV,R

L

=

2 kΩ

,

=

p

–40°C 59° 62°

unity gain

C

L

= 25 F,

See Figure 4

85°C 61° 64°

†

Full range is –40°C to 85°C.

‡

For V

CC±

= ±5 V, V

I(PP)

= ±1 V; for V

CC±

= ±15 V, V

I(PP)

= ±5 V.

§

This parameter is tested on a sample basis. For other test requirements, please contact the factory. This statement has no bearing on testing

or nontesting of other parameters.

¶

For V

CC±

= ±5 V, V

o(rms

) = 1 V; for V

CC±

= ±15 V, V

o(rms)

= 6 V.

TL05x, TL05xA, TL05xY

ENHANCED-JFET LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS178 – FEBRUARY 1997

28

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TL054M and TL054AM electrical characteristics at specified free-air temperature

TL054M, TL054AM

PARAMETER TEST CONDITIONS

T

A

†

V

CC±

= ±5 V V

CC±

= ±15 V UNIT

A

MIN TYP MAX MIN TYP MAX

25°C 0.64 5.5 0.56 4

p

TL054M

Full range 10.5 9

VIOInput offset voltage

25°C 0.57 3.5 0.5 1.5

mV

TL054AM

Full range 8.5 6.5

T emperature coef ficient of

V

O

= 0,

VIC = 0,

R

= 50 Ω

TL054M

25°C to

85°C

21 20

°

α

VIO

input offset voltage

R

S

50

Ω

TL054AM

25°C to

85°C

21 20

µ

V/°C

Input offset voltage

long-term drift

‡

25°C 0.04 0.04 µV/mo

p

VO = 0, VIC = 0,

25°C 4 100 5 100 pA

IIOInput offset current

OIC

See Figure 5

125°C 1 20 2 20 nA

p

VO = 0, VIC = 0,

25°C 20 200 30 200 pA

IIBInput bias current

OIC

See Figure 5

125°C 10 50 20 50 nA

Common-mode input

25°C

–1

to

4

–2.3

to

5.6

–11

to

11

–12.3

to

15.6

V

ICR

voltage range

Full range

–1

to

4

–11

to

11

V

25°C 3 4.2 13 13.9

Maximum positive peak

R

L

= 10

kΩ

Full range 3 13

V

OM +

output voltage swing

25°C 2.5 3.8 11.5 12.7

V