Texas Instruments TIBPAL20R8-25CNT, TIBPAL20R8-25CFN, TIBPAL20L8-25CFN, TIBPAL20R4-25CFN, TIBPAL20R4-25CNT Datasheet

...

TIBPAL20L8-25C, TIBPAL20R4-25C, TIBPAL20R6-25C, TIBPAL20R8-25C

LOW-POWER HIGH-PERFORMANCE IMPACT PAL

SRPS022 – D2920, MA Y 1987 – REVISED MARCH 1992

CIRCUITS

• Low-Power, High-Performance

Reduced I

f

:

max

Without Feedback . . . 33 MHz Min

With Feedback . . . 25 MHz Min

. . . 25 ns Max

t

pd

of 105 mA Max

CC

• Direct Replacement for PAL20L8A,

PAL20R4A, PAL20R6A, PAL20L8A, with at

Least 50% Reduction in Power

• Preload Capability on Output Registers

Simplifies Testing

• Power-Up Clear on Registered Devices (All

Register Outputs are Set Low, but Voltage

Levels at the Output Pins Go High)

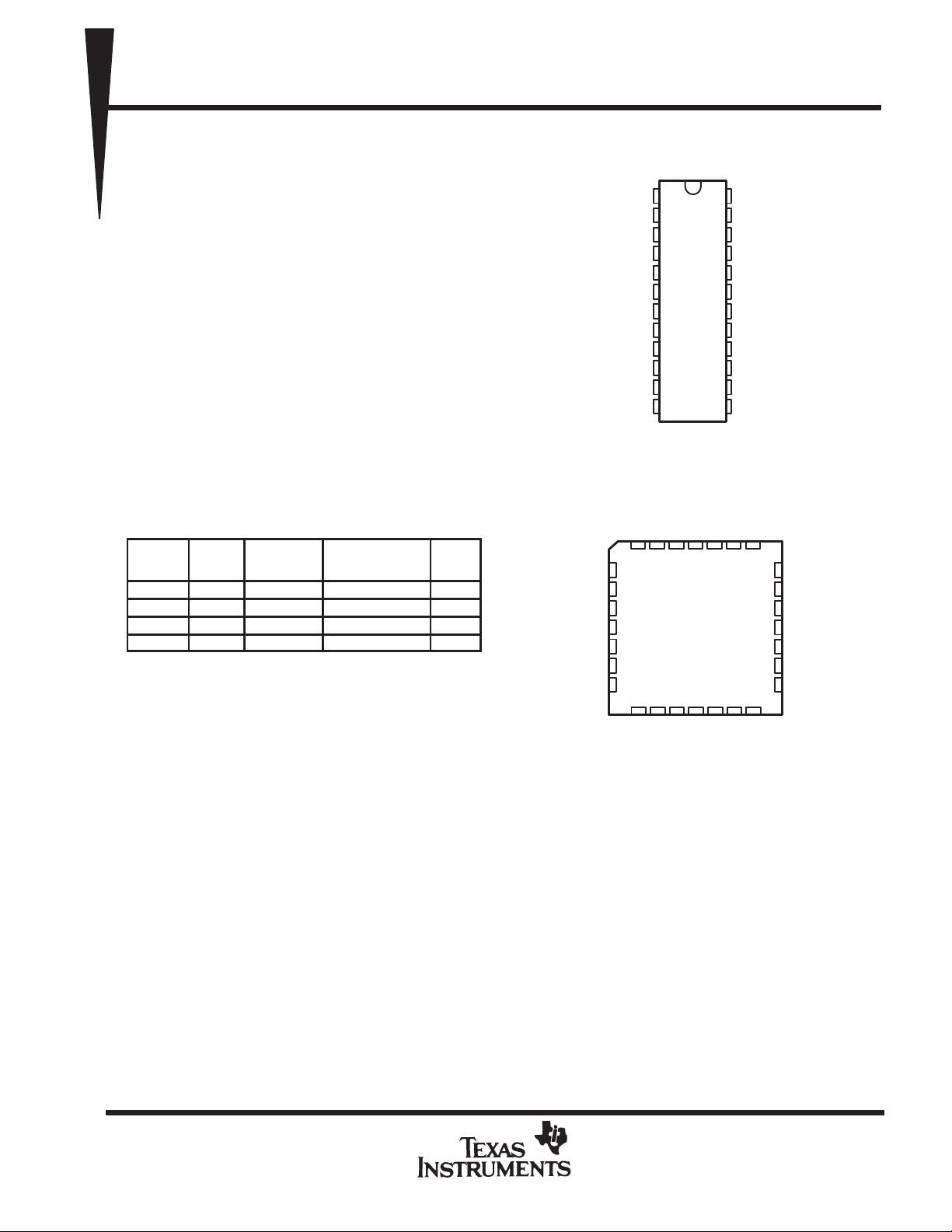

TIBPAL20L8’

JT OR NT PACKAGE

(TOP VIEW)

I

I

I

I

I

I

I

I

I

I

I

GND

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

V

I

O

I/O

I/O

I/O

I/O

I/O

I/O

O

I

I

CC

• Package Options Include Plastic Chip

Carriers in Addition to Plastic and Ceramic

DIPs

• Dependable Texas Instruments Quality and

Reliability

I

DEVICE

PAL20L8 14 2 0 6

PAL20R4 12 0 4 (3-state buffers) 4

PAL20R6 12 0 6 (3-state buffers) 2

PAL20R8 12 0 8 (3-state buffers) 0

INPUTS

3-STATE

O OUTPUTS

REGISTERED

Q OUTPUTS

description

These programmable array logic devices feature

high speed and functional equivalency when

compared with currently available devices. These

IMP ACT circuits combine the latest

AdvancedLow-Power Schottky technology with

proven titanium-tungsten fuses to provide reliable,

high-performance substitutes for conventional

TTL logic. Their easy programmability allows forquick design of custom functions and typically results in a more

compact circuit board. In addition, chip carriers are available for futher reduction in board space.

I/O

PORT

S

I

I

I

NC

I

I

I

NC

– No internal connection

Pin assignments in operating mode

TIBPAL20L8’

FN PACKAGE

(TOP VIEW)

CC

I

GND

NC

NC

V

I

O

I/O

25

I/O

24

I/O

23

NC

22

I/O

21

I/O

20

19

I/O

I

I

O

I

I

3212827

426

5

6

7

8

9

10

11

12 13

14 15 16 1718

I

I

All of the register outputs are set to a low level during power-up. Extra circuitry has been provided to allow loading

of each register asynchronously to either a high or low state. This feature simplifies testing because the registers

can be set to an initial state prior to executing the test sequence.

The TIBPAL20’ C series is characterized from 0°C to 75°C.

These devices are covered by U.S. Patent 4,410,987

IMPACT is a trademark of Texas Instruments Incorporated.

PAL is a registered trademark of Advanced Micro Devices Inc.

PRODUCTION DATA information is current as of publication date. Products

conform to specifications per the terms of Texas Instruments standard

warranty. Production processing does not necessarily include testing of all

parameters.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Copyright 1992, Texas Instruments Incorporated

1

TIBPAL20R4-25C, TIBPAL20R6-25C, TIBPAL20R8-25C

LOW-POWER HIGH-PERFORMANCE IMPACT PAL

SRPS022 – D2920, MA Y 1987 – REVISED MARCH 1992

CIRCUITS

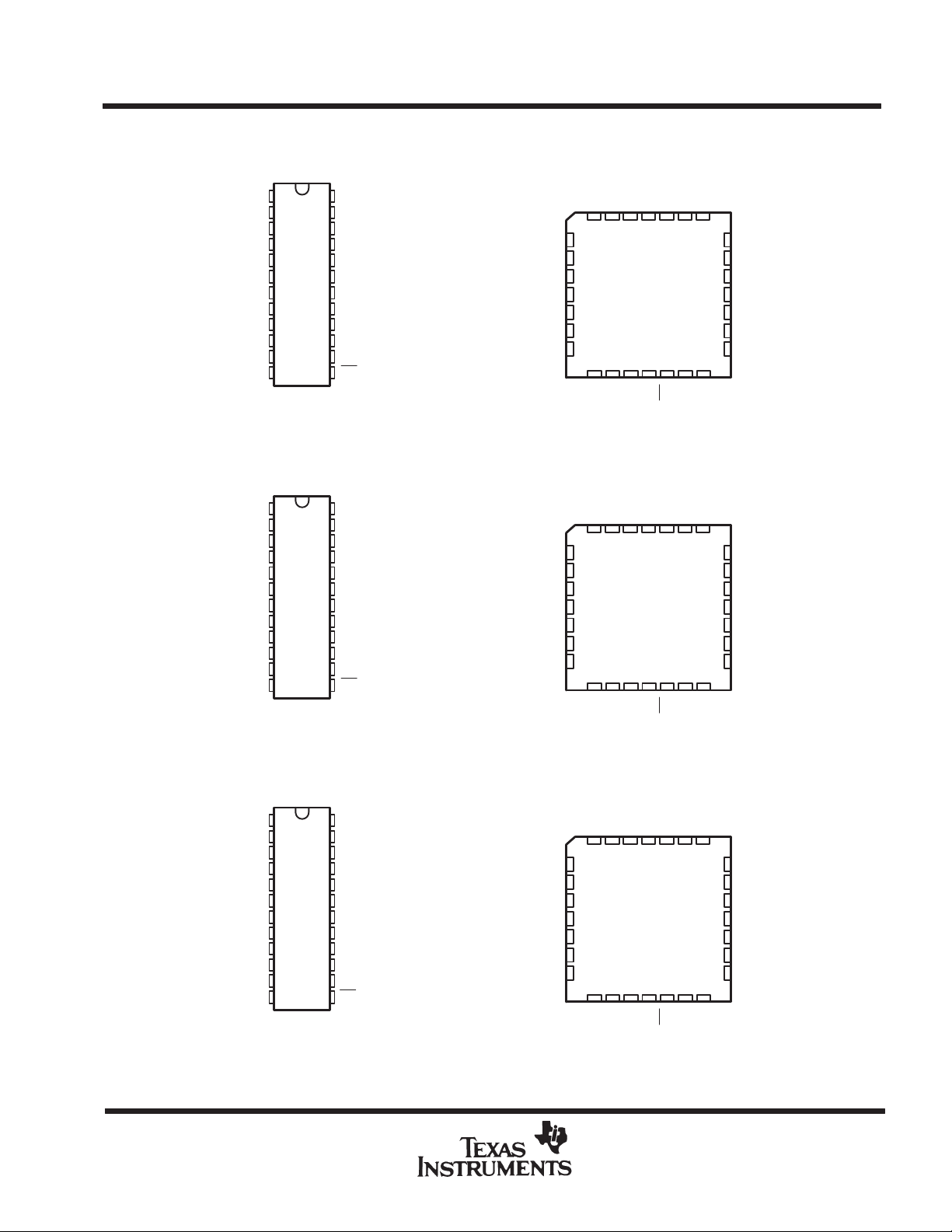

TIBPAL20R4’

JT OR NT PACKAGE

(TOP VIEW)

1

CLK

I

I

I

I

I

I

I

I

I

I

GND

TIBPAL20R6’

JT OR NT PACKAGE

CLK

I

I

I

I

I

I

I

I

I

I

GND

24

2

23

3

22

4

21

5

20

6

19

7

18

8

17

9

16

10

15

11

14

12

13

(TOP VIEW)

1

24

2

23

3

22

4

21

5

20

6

19

7

18

8

17

9

16

10

15

11

14

12

13

V

I

I/O

I/O

Q

Q

Q

Q

I/O

I/O

I

OE

V

I

I/O

Q

Q

Q

Q

Q

Q

I/O

I

OE

CC

CC

TIBPAL20R4’

FN PACKAGE

(TOP VIEW)

CC

I

I

4

3 2 1 282726

5 I/O

I

6

I

7

I

8

NC

9

I

10

I

11 19

I

12 13 14 15 16 17 18

I

I

TIBPAL20R6’

FN PACKAGE

(TOP VIEW)

I

I

4

3 2 1 282726

5Q

I

6

I

7

I

8

NC

9

I

10

I

11 19

I

12 13 14 15 16 17 18

I

I

V

CLKNCI

OE

NC

GND

CC

V

CLKNCI

OE

NC

GND

I/O

25

Q

24

Q

23

NC

22

Q

21

Q

20

I/O

I

I/O

I/O

25

Q

24

Q

23

NC

22

Q

21

Q

20

Q

I

I/O

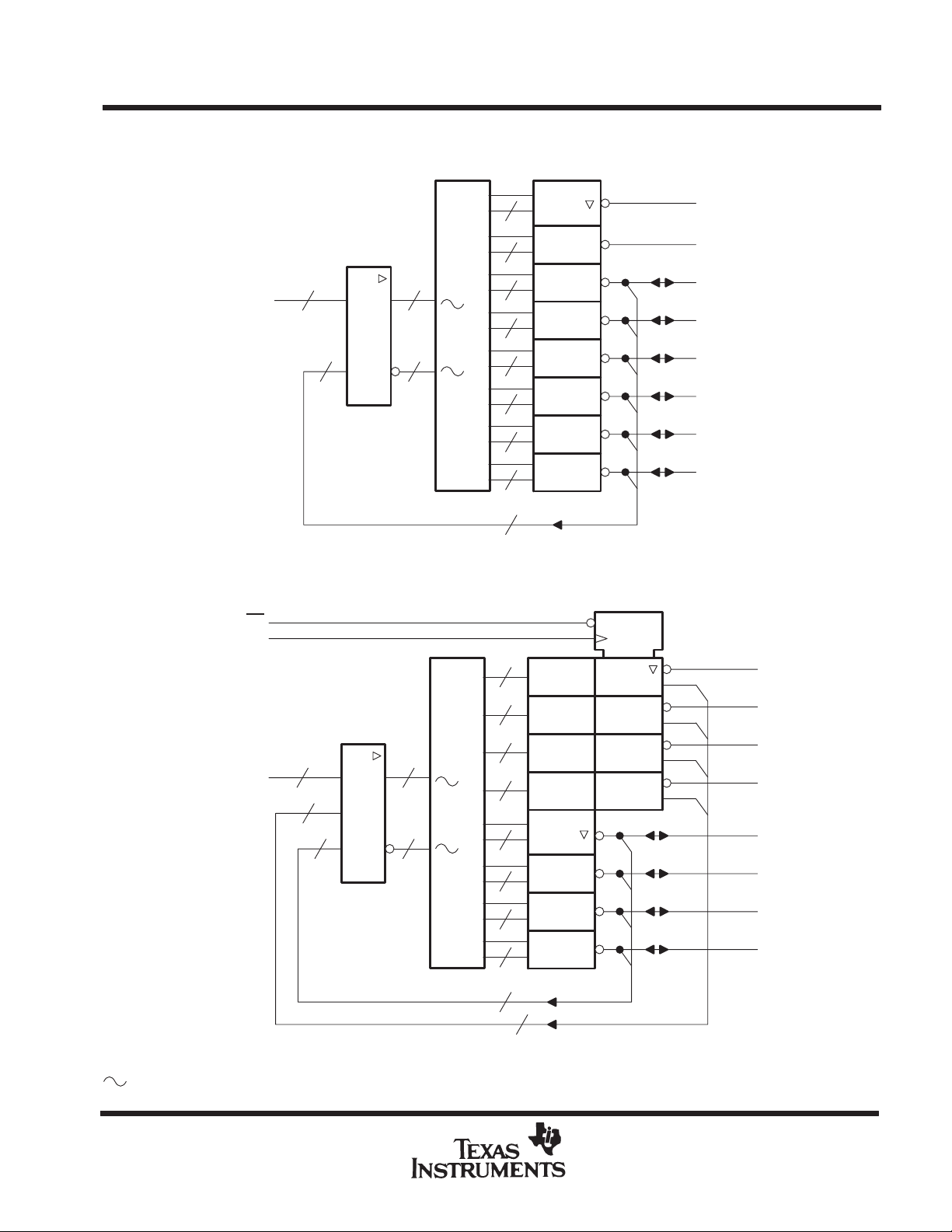

TIBPAL20R8’

JT OR NT PACKAGE

(TOP VIEW)

1

CLK

2

I

3

I

4

I

5

I

6

I

7

I

8

I

9

I

10

I

11

I

12

GND

Pin assignments in operating mode

2

24

23

22

21

20

19

18

17

16

15

14

13

V

CC

I

Q

Q

Q

Q

Q

Q

Q

Q

I

OE

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TIBPAL20R8’

FN PACKAGE

(TOP VIEW)

I

I

4

3 2 1 282726

5Q

I

6

I

7

I

8

NC

9

I

10

I

11

I

12 13 14 15 16 17 18

I

I

– No internal connection

NC

CC

CLKNCI

V

NC

OE

GND

Q

25

Q

24

Q

23

NC

22

Q

21

Q

20

19

Q

I

Q

LOW-POWER HIGH-PERFORMANCE IMPACT PAL

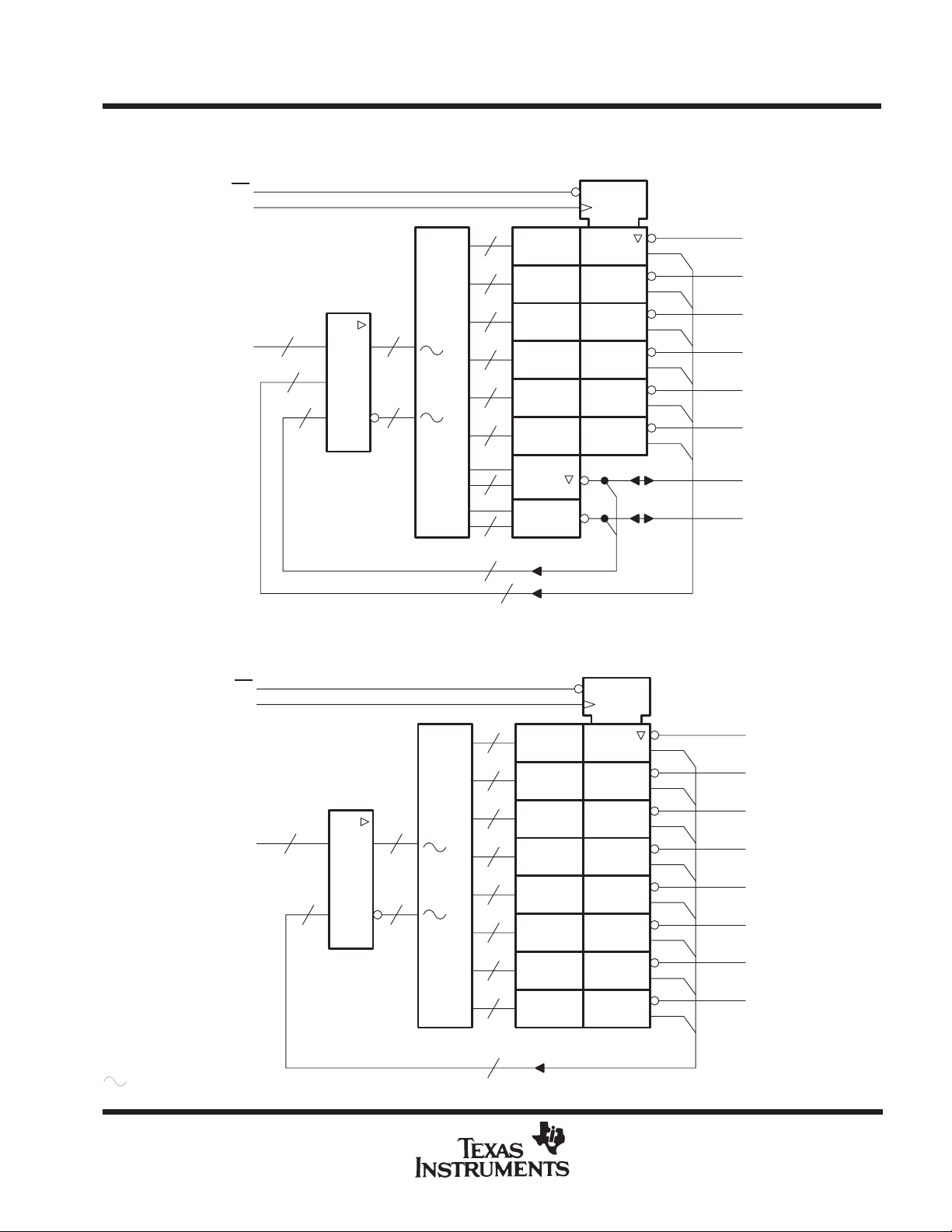

functional block diagrams (positive logic)

TIBPAL20L8’

TIBPAL20L8-25C, TIBPAL20R4-25C

CIRCUITS

SRPS022 – D2920, MA Y 1987 – REVISED MARCH 1992

OE

CLK

14 20

I

20 x

&

40 X 64

206

TIBPAL20R4’

7

7

7

7

7

7

7

7

6

EN

≥1

O

O

I/O

I/O

I/O

I/O

I/O

I/O

EN 2

C1

denotes fused inputs

12 20

I

4

20 x

1D

I = 0

2

Q

Q

Q

Q

I/O

I/O

I/O

I/O

&

40 X 64

204

8

8

8

8

7

7

7

7

4

≥1

≥1

EN

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

3

TIBPAL20R6-25C, TIBPAL20R8-25C

LOW-POWER HIGH-PERFORMANCE IMPACT PAL

SRPS022 – D2920, MA Y 1987 – REVISED MARCH 1992

functional block diagrams (positive logic)

TIBPAL20R6’

CIRCUITS

OE

CLK

12 20

I

6

20 x

EN 2

C1

1D

I = 0

2

Q

Q

Q

Q

Q

Q

I/O

I/O

&

40 X 64

202

8

8

8

8

8

8

7

7

2

≥1

≥1

EN

6

CLK

denotes fused inputs

OE

12 20

I

20 x

TIBPAL20R8’

EN 2

C1

1D

I = 0

2

Q

Q

Q

Q

Q

Q

Q

Q

&

40 X 64

208

8

8

8

8

8

8

8

8

8

≥1

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

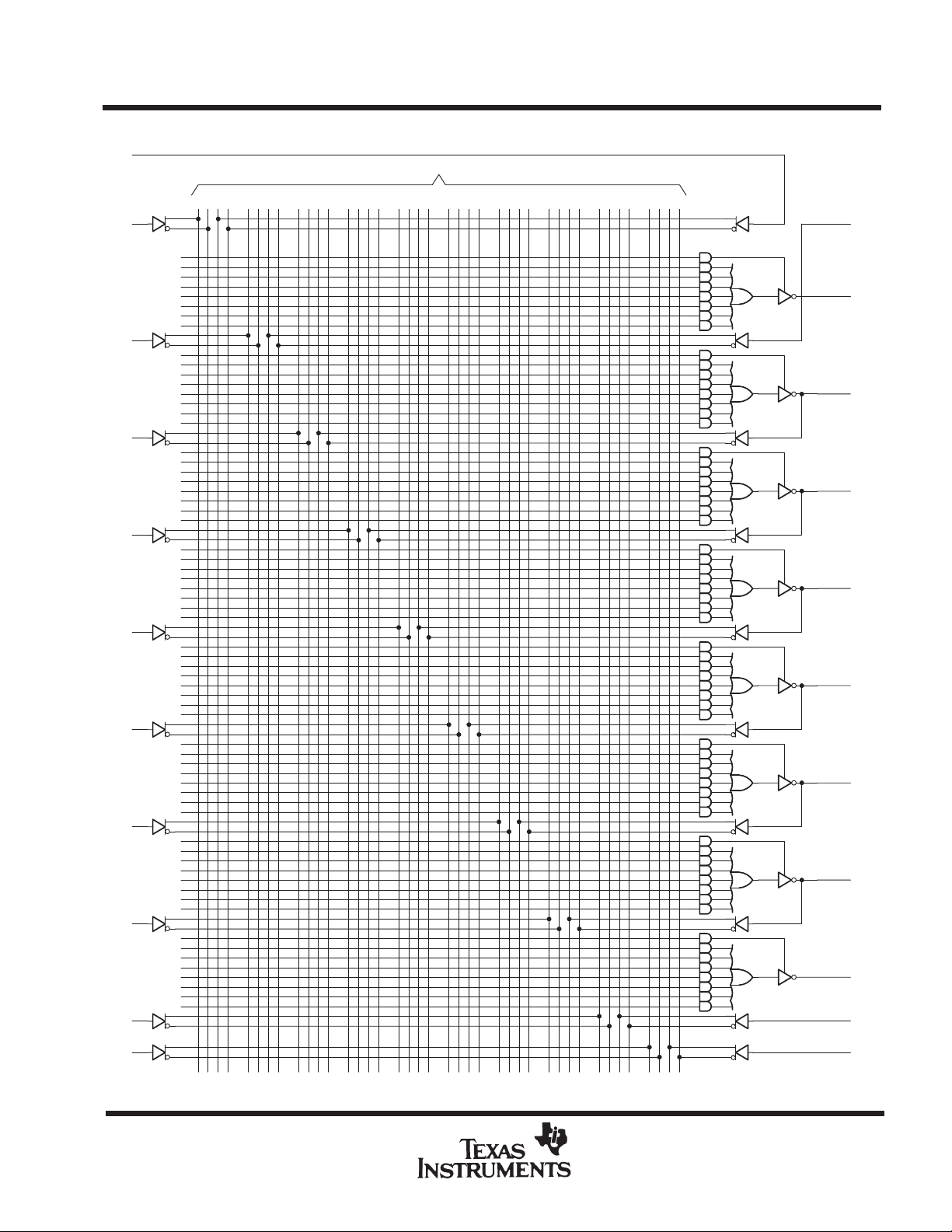

logic diagram (positive logic)

1

I

TIBPAL20L8-25C

LOW-POWER HIGH-PERFORMANCE IMPACT PAL

SRPS022 – D2920, MA Y 1987 – REVISED MARCH 1992

Increment

CIRCUITS

2

I

First Fuse

Numbers

120

160

200

240

280

3

I

320

360

400

440

480

520

560

600

4

I

640

680

720

760

800

840

880

920

5

I

960

1000

1040

1080

1120

1160

1200

1240

6

I

1280

1320

1360

1400

1440

1480

1520

1560

7

I

1600

1640

1680

1720

1760

1800

1840

1880

8

I

1920

1960

2000

2040

2080

2120

2160

2200

9

I

2240

2280

2320

2360

2400

2440

2480

2520

10

I

11

I

4 8 12 16 20 24 28 32

0

40

80

36 390

23

I

22

O

21

I/O

20

I/O

19

I/O

18

I/O

17

I/O

16

I/O

15

O

14

I

13

I

Fuse number = First fuse number + Increment

Pin numbers shown are for JT and NT packages.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

5

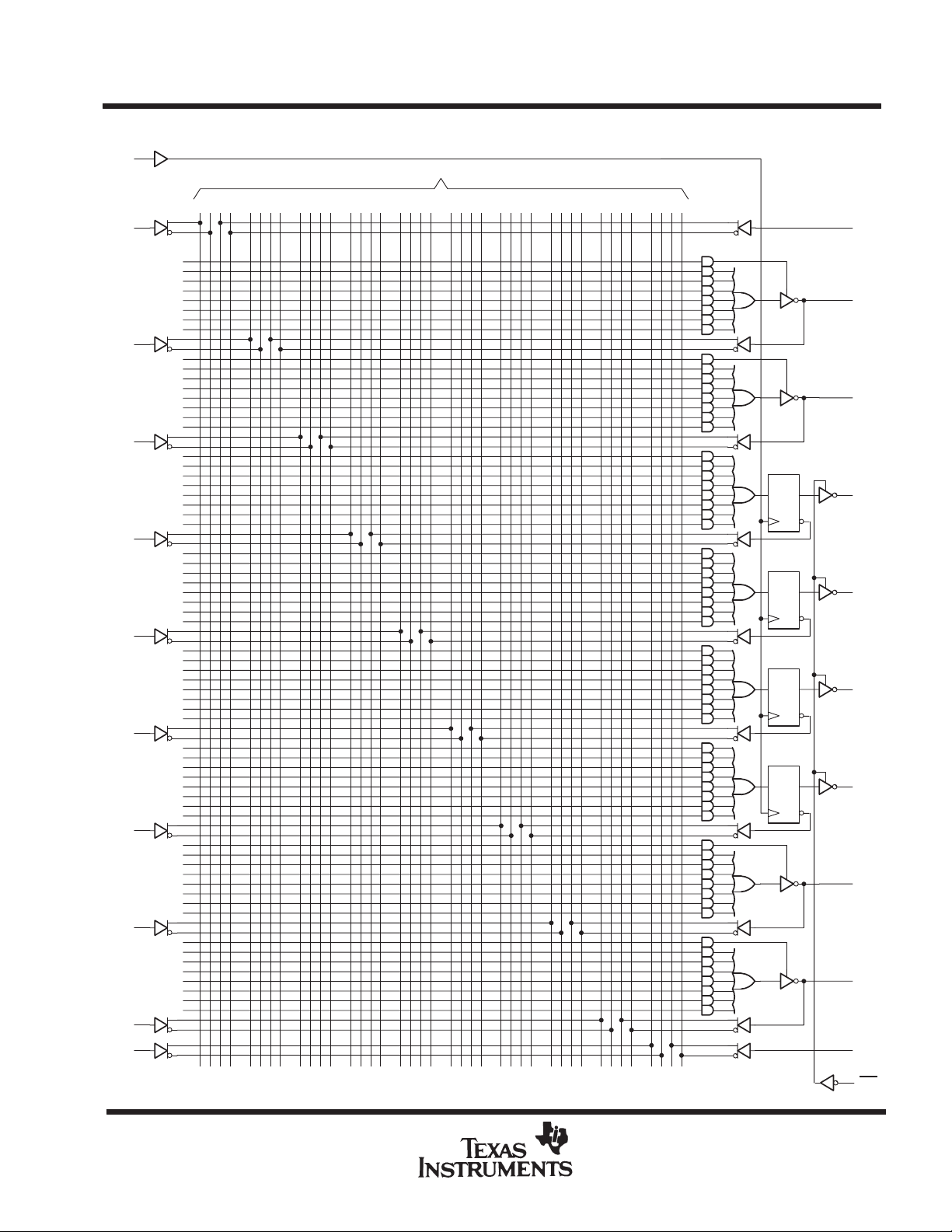

TIBPAL20R4-25C

LOW-POWER HIGH-PERFORMANCE IMPACT PAL

SRPS022 – D2920, MA Y 1987 – REVISED MARCH 1992

logic diagram (positive logic)

1

CLK

Increment

CIRCUITS

2

I

First Fuse

Numbers

0

40

80

120

160

200

240

280

3

I

320

360

400

440

480

520

560

600

4

I

640

680

720

760

800

840

880

920

5

I

960

1000

1040

1080

1120

1160

1200

1240

6

I

1280

1320

1360

1400

1440

1480

1520

1560

7

I

1600

1640

1680

1720

1760

1800

1840

1880

8

I

1920

1960

2000

2040

2080

2120

2160

2200

9

I

2240

2280

2320

2360

2400

2440

2480

2520

10

I

11

I

Fuse number = First fuse number + Increment

Pin numbers shown are for JT and NT packages.

4 8 12 16 20 24 28 32

36 390

23

I

22

I/O

21

I/O

I = 0

1D

C1

I = 0

1D

C1

I = 0

1D

C1

I = 0

1D

C1

20

19

18

17

16

15

14

13

Q

Q

Q

Q

I/O

I/O

I

OE

6

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Loading...

Loading...