Texas Instruments SN74ALS667NT, SN74ALS667NT3, SN74ALS666DW, SN74ALS666DWR, SN74ALS666NT Datasheet

...

SN74ALS666, SN74ALS667

8-BIT D-TYPE TRANSPARENT READ-BACK LATCHES

WITH 3-STATE OUTPUTS

SDAS227A – JUNE 1984 – REVISED JANUARY 1995

Copyright 1995, Texas Instruments Incorporated

1

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

• 3-State I/O-Type Read-Back Inputs

• Bus-Structured Pinout

• Choice of True or Inverting Logic

– SN74ALS666...True Outputs

– SN74ALS667...Inverted Outputs

• Preset and Clear Inputs

• Package Options Include Plastic

Small-Outline (DW) Packages and Standard

Plastic (NT) 300-mil DIPs

description

These 8-bit D-type transparent latches are

designed specifically for storing the contents of

the input data bus, plus reading back the stored

data onto the input data bus. In addition, they

provide a 3-state buffer-type output and are easily

utilized in bus-structured applications.

While the latch enable (LE) is high, the Q outputs

of the SN74ALS666 follow the data (D) inputs. The

Q

outputs of the SN74ALS667 provide the inverse

of the data applied to its D inputs. The Q or

Q

output of both devices is in the high-impedance

state if either output-enable (OE1

or OE2) input is

at a high logic level.

Read back is provided through the read-back

control (OERB

) input. When OERB is taken low,

the data present at the output of the data latches

passes back onto the input data bus. When OERB

is taken high, the output of the data latches is

isolated from the D inputs. OERB

does not affect

the internal operation of the latches; however,

caution should be exercised to avoid a bus

conflict.

The SN74ALS666 and SN74ALS667 are

characterized for operation from 0°C to 70°C.

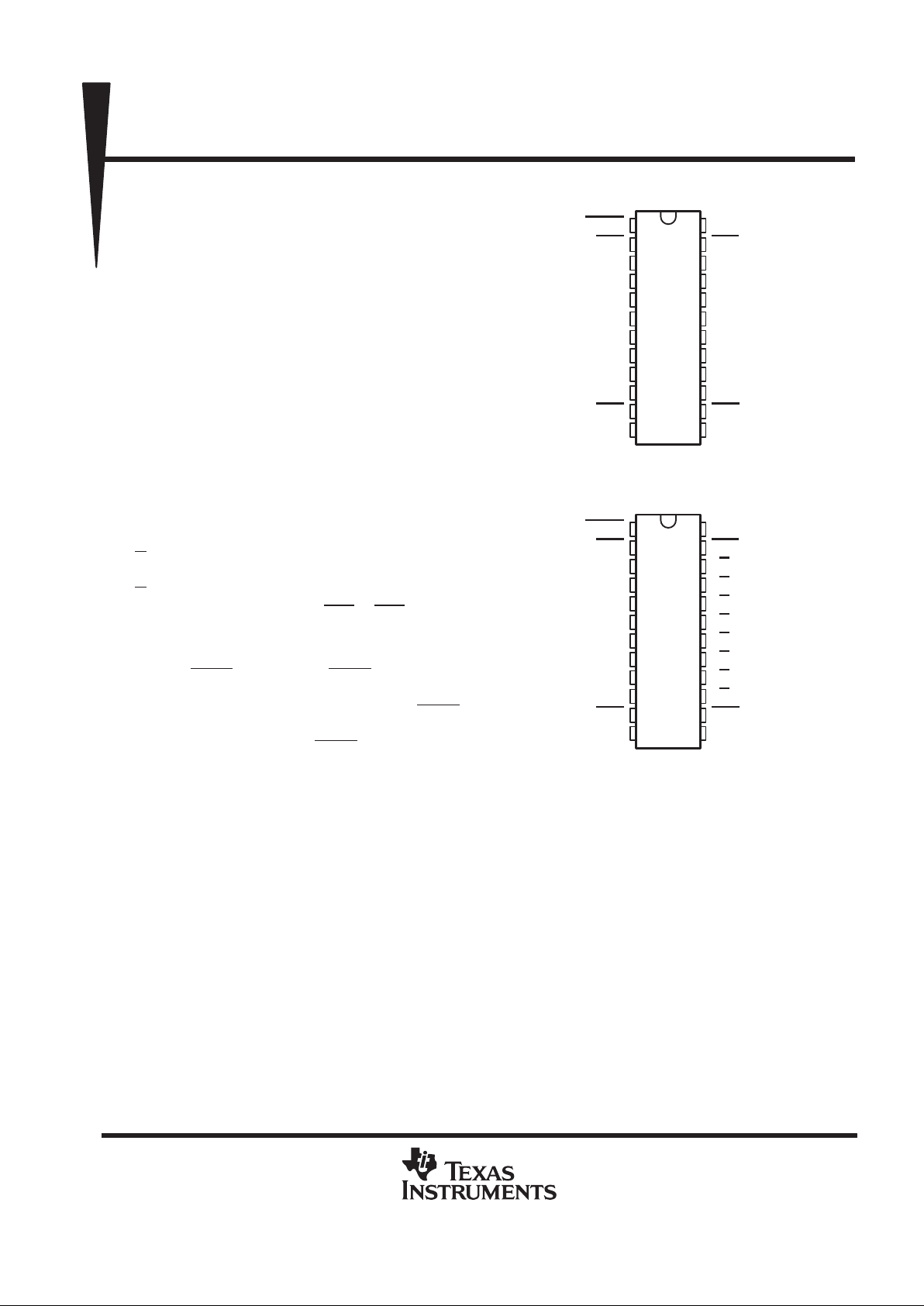

SN74ALS666 ...DW OR NT PACKAGE

(TOP VIEW)

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

OERB

OE1

1D

2D

3D

4D

5D

6D

7D

8D

CLR

GND

V

CC

OE2

1Q

2Q

3Q

4Q

5Q

6Q

7Q

8Q

PRE

LE

SN74ALS667 . . . DW OR NT PACKAGE

(TOP VIEW)

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

OERB

OE1

1D

2D

3D

4D

5D

6D

7D

8D

CLR

GND

V

CC

OE2

1Q

2Q

3Q

4Q

5Q

6Q

7Q

8Q

PRE

LE

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

SN74ALS666, SN74ALS667

8-BIT D-TYPE TRANSPARENT READ-BACK LATCHES

WITH 3-STATE OUTPUTS

SDAS227A – JUNE 1984 – REVISED JANUAR Y 1995

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

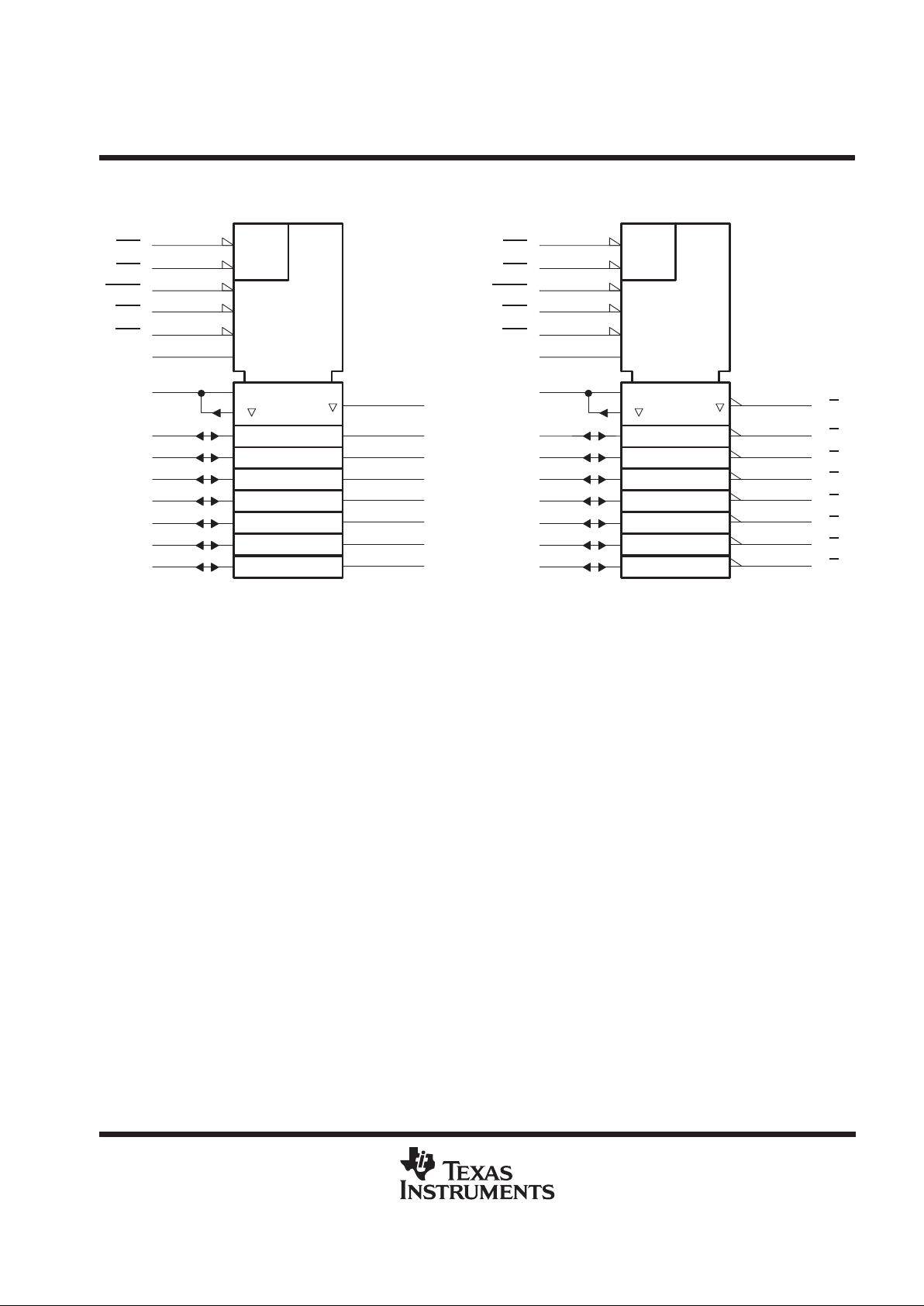

logic symbols

†

1Q

2Q

3Q

4Q

5Q

6Q

7Q

8Q

R

11

C1

13

LE

2D

4

3D

5

4D

6

5D

7

6D

8

7D

9

8D

10

3

18

17

16

15

21

20

19

22

1D

3

1D

S

14

EN3

1

23

2

2

&

EN2

OE1

OE2

OERB

PRE

CLR

SN74ALS667

R

11

C1

13

LE

2D

4

3D

5

4D

6

5D

7

6D

8

7D

9

8D

10

3

5Q

18

6Q

17

7Q

16

8Q

15

2Q

21

3Q

20

4Q

19

1Q

22

1D

3

1D

S

14

EN3

1

23

2

2

&

EN2

OE1

OE2

OERB

PRE

CLR

SN74ALS666

†

These symbols are in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

SN74ALS666, SN74ALS667

8-BIT D-TYPE TRANSPARENT READ-BACK LATCHES

WITH 3-STATE OUTPUTS

SDAS227A – JUNE 1984 – REVISED JANUARY 1995

3

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

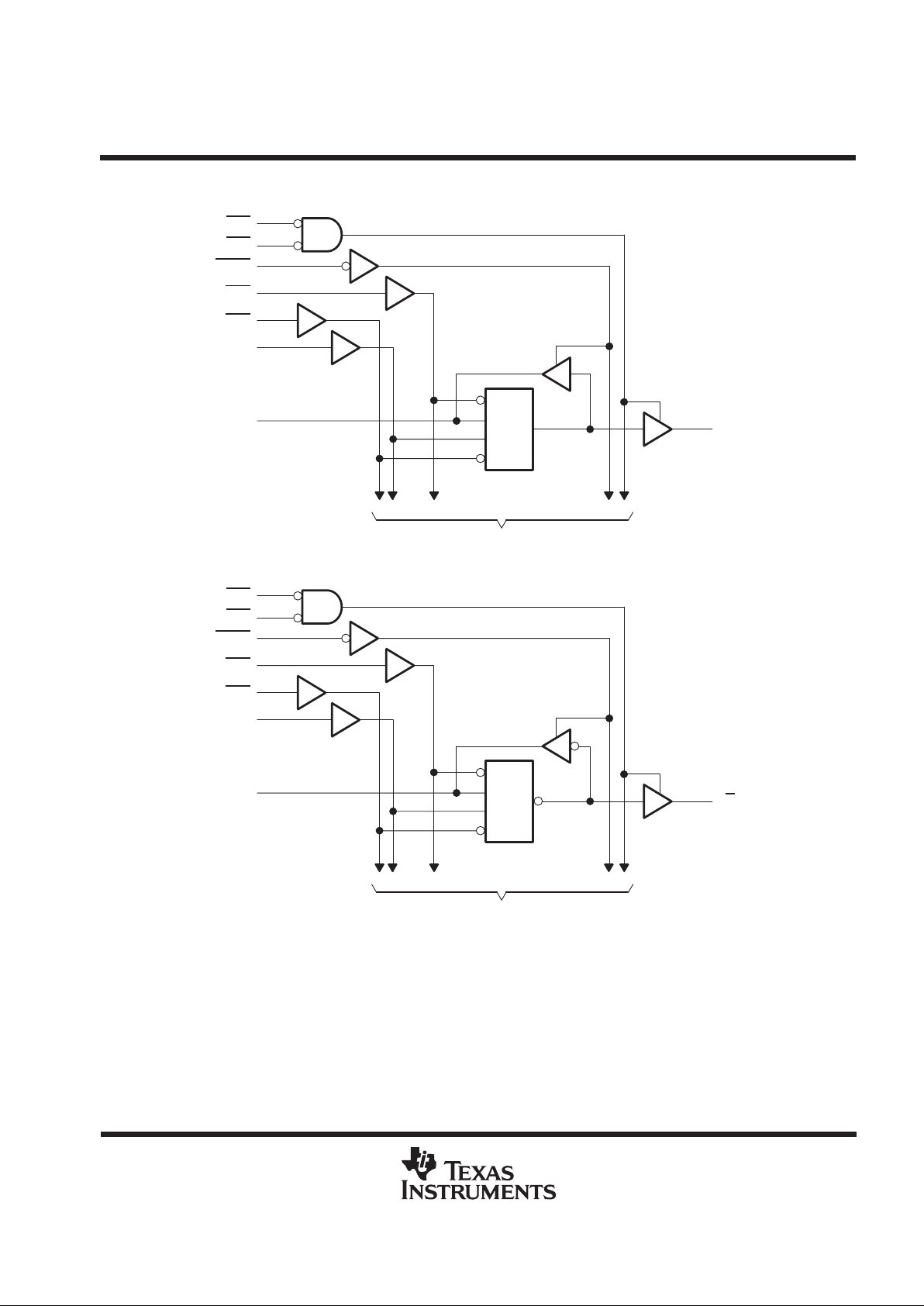

logic diagrams (positive logic)

S

1D

C1

R

To Seven Other Channels

2

23

1

14

11

13

3

22

OE1

OE2

OERB

PRE

CLR

LE

1D

1Q

SN74ALS666

S

1D

C1

R

To Seven Other Channels

2

23

1

14

11

13

3

22

OE1

OE2

OERB

PRE

CLR

LE

1D

1Q

SN74ALS667

Loading...

Loading...