Texas Instruments SN54AS169AJ, SN74ALS169BD, SN74ALS169BDR, SN74ALS169BN, SN74AS169AD Datasheet

...

SN54ALS169B, SN54AS169A, SN74ALS169B, SN74AS169A

SYNCHRONOUS 4-BIT UP/DOWN BINARY COUNTERS

SDAS125B – MARCH 1984 – REVISED DECEMBER 1994

Copyright 1994, Texas Instruments Incorporated

2–1

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

• Fully Synchronous Operation for Counting

and Programming

• Internal Carry Look-Ahead Circuitry for

Fast Counting

• Carry Output for n-Bit Cascading

• Fully Independent Clock Circuit

• Package Options Include Plastic

Small-Outline (D) Packages, Ceramic Chip

Carriers (FK), and Standard Plastic (N) and

Ceramic (J) 300-mil DIPs

description

These synchronous 4-bit up/down binary

presettable counters feature an internal carry

look-ahead circuitry for cascading in high-speed

counting applications. Synchronous operation is

provided by having all flip-flops clocked

simultaneously so that the outputs change

coincident with each other when so instructed by

the count-enable (ENP

, ENT) inputs and internal

gating. This mode of operation eliminates the

output counting spikes normally associated with

asynchronous (ripple-clock) counters. A buffered

clock (CLK) input triggers the four flip-flops on the

rising (positive-going) edge of the clock waveform.

These counters are fully programmable; that is,

they may be preset to either level. The load-input

circuitry allows loading with the carry-enable

output of cascaded counters. Because loading is

synchronous, setting up a low level at the load

(LOAD

) input disables the counter and causes the

outputs to agree with the data inputs after the next

clock pulse.

The internal carry look-ahead circuitry provides for cascading counters for n-bit synchronous application without

additional gating. ENP

and ENT inputs and a ripple-carry output (RCO) are instrumental in accomplishing this

function. Both ENP

and ENT must be low to count. The direction of the count is determined by the level of the

up/down (U/D

) input. When U/D is high, the counter counts up; when low, it counts down. ENT is fed forward

to enable RCO

. RCO, thus enabled, produces a low-level pulse while the count is zero (all inputs low) counting

down or maximum (15) counting up. This low-level overflow ripple-carry pulse can be used to enable successive

cascaded stages. Transitions at ENP

or ENT are allowed regardless of the level of the clock input. All inputs

are diode clamped to minimize transmission-line effects, thereby simplifying system design.

These counters feature a fully independent clock circuit. Changes at control inputs (ENP

, ENT, LOAD, or U/D)

that modify the operating mode have no effect on the contents of the counter until clocking occurs. The function

of the counter (whether enabled, disabled, loading, or counting) is dictated solely by the conditions meeting the

stable setup and hold times.

The SN54ALS169B and SN54AS169A are characterized for operation over the full military temperature range

of –55°C to 125°C. The SN74ALS169B and SN74AS169A are characterized for operation from 0°C to 70°C.

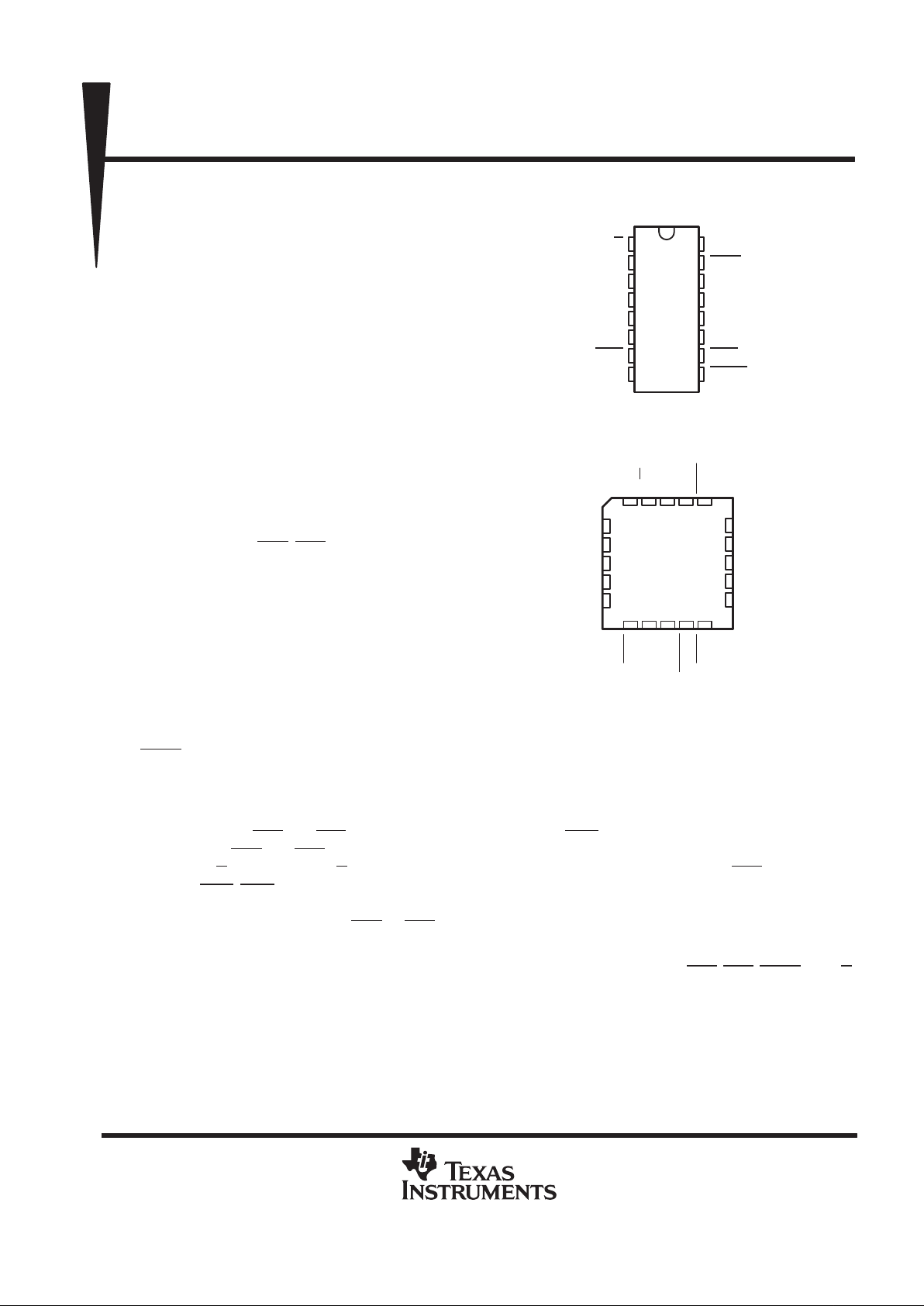

SN54ALS169B, SN54AS169A ...J PACKAGE

SN74ALS169B, SN74AS169A ...D OR N PACKAGE

(TOP VIEW)

3212019

910111213

4

5

6

7

8

18

17

16

15

14

Q

A

Q

B

NC

Q

C

Q

D

A

B

NC

C

D

SN54ALS169B, SN54AS169A . . . FK PACKAGE

(TOP VIEW)

CLK

U/D

NC

LOAD

ENT

RCO

ENP

GND

NC

NC – No internal connection

V

CC

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

U/D

CLK

A

B

C

D

ENP

GND

V

CC

RCO

Q

A

Q

B

Q

C

Q

D

ENT

LOAD

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

SN54ALS169B, SN54AS169A, SN74ALS169B, SN74AS169A

SYNCHRONOUS 4-BIT UP/DOWN BINARY COUNTERS

SDAS125B – MARCH 1984 – REVISED DECEMBER 1994

2–2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

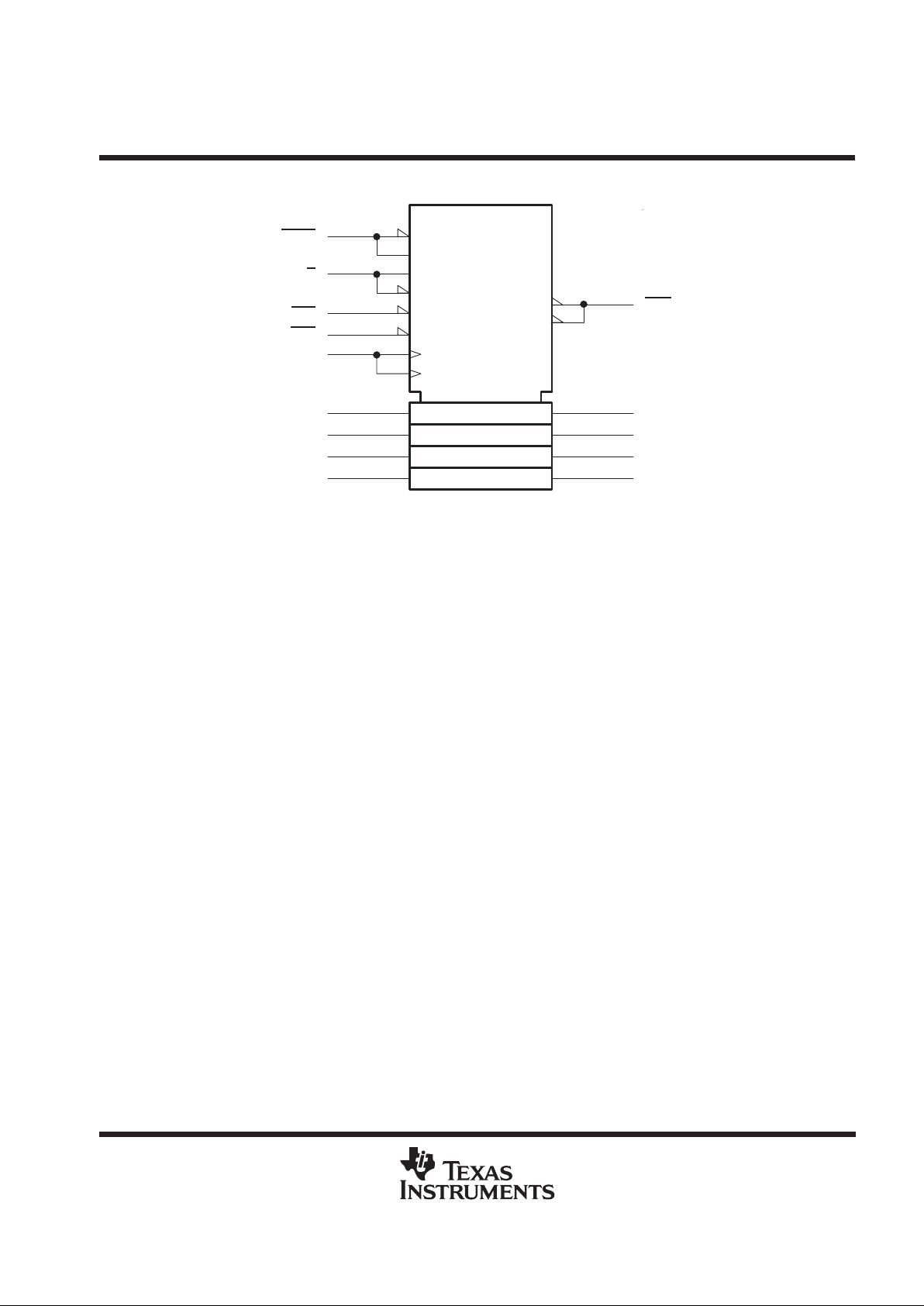

logic symbol

†

CTRDIV16

LOAD

1, 7D

3

A

4

B

5

C

6

D

M2 [COUNT]

M1 [LOAD]

9

2,3,5,6+/C7

G5

10

15

3,5CT=15

14

13

12

11

Q

A

Q

B

Q

C

Q

D

G6

7

2

CLK

1

2

4

8

U/D

M4 [DOWN]

M3 [UP]

1

2,4,5,6 –

ENT

ENP

RCO

4,5CT=0

†

This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

Pin numbers shown are for the D, J, and N packages.

SN54ALS169B, SN54AS169A, SN74ALS169B, SN74AS169A

SYNCHRONOUS 4-BIT UP/DOWN BINARY COUNTERS

SDAS125B – MARCH 1984 – REVISED DECEMBER 1994

2–3

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

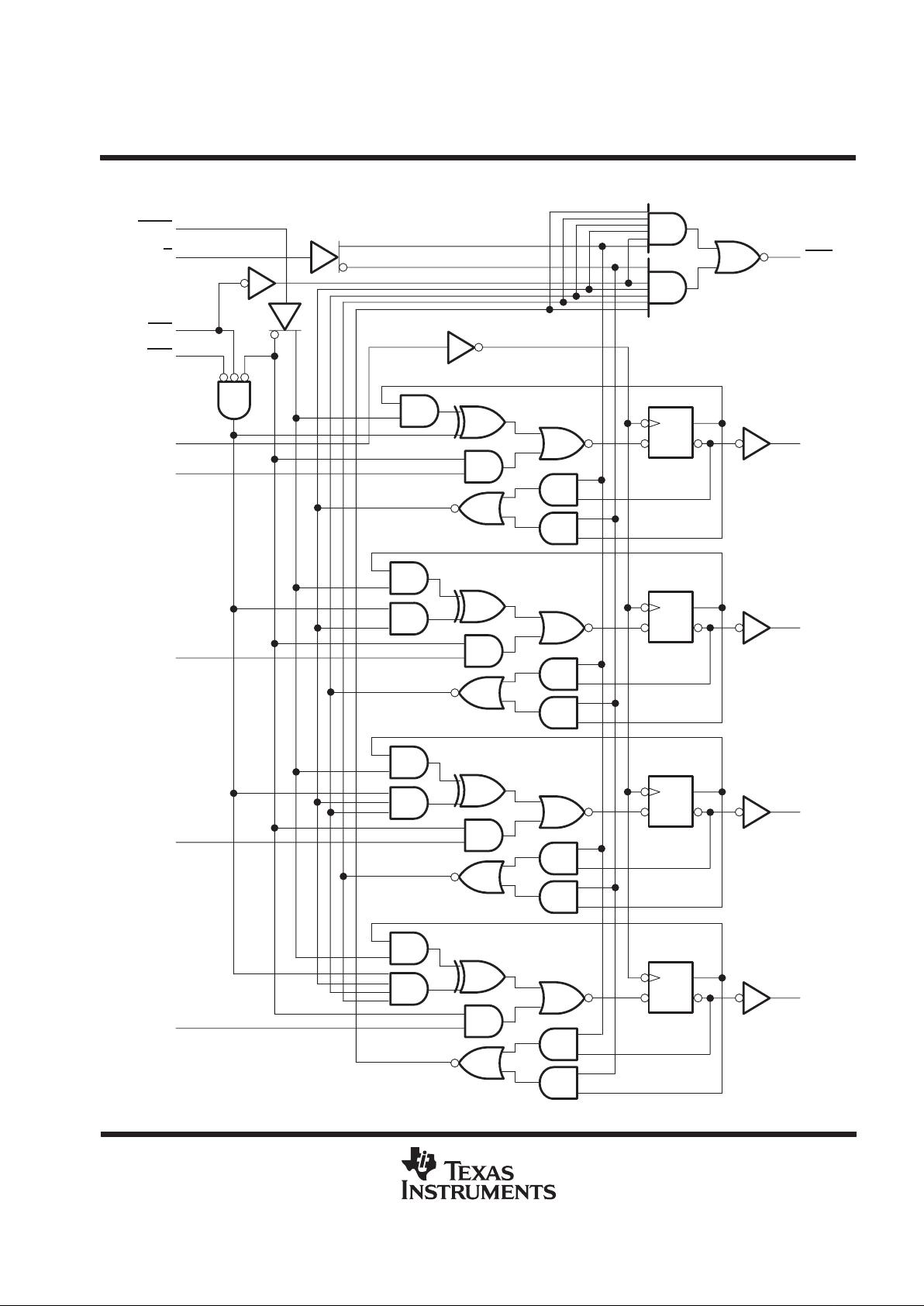

logic diagram (positive logic)

C1

1D

142

3

7

10

1

9

15

C1

1D

13

4

C1

1D

12

5

C1

1D

11

6

LOAD

U/D

ENT

ENP

CLK

A

B

C

D

Q

A

Q

B

Q

C

Q

D

RCO

Pin numbers shown are for the D, J, and N packages.

SN54ALS169B, SN54AS169A, SN74ALS169B, SN74AS169A

SYNCHRONOUS 4-BIT UP/DOWN BINARY COUNTERS

SDAS125B – MARCH 1984 – REVISED DECEMBER 1994

2–4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

typical load, count, and inhibit sequences

The following sequence is illustrated below:

1. Load (preset) to binary 13

2. Count up to 14, 15 (maximum), 0, 1, and 2

3. Inhibit

4. Count down to 1, 0 (minimum), 15, 14, and 13

Data

Inputs

Data

Outputs

LOAD

A

B

C

D

CLK

U/D

ENP and ENT

RCO

Q

A

Q

B

Q

C

Q

D

Load

Count Up Inhibit

13 14

15 0 012

Count Down

221 1315 14

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

†

Supply voltage, V

CC

7 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input voltage, V

I

7 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating free-air temperature range, T

A

: SN54ALS169B –55°C to 125°C. . . . . . . . . . . . . . . . . . . . . . . . . . .

SN74ALS169B 0°C to 70°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range –65°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

†

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

SN54ALS169B, SN54AS169A, SN74ALS169B, SN74AS169A

SYNCHRONOUS 4-BIT UP/DOWN BINARY COUNTERS

SDAS125B – MARCH 1984 – REVISED DECEMBER 1994

2–5

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

recommended operating conditions

SN54ALS169B SN74ALS169B

MIN NOM MAX MIN NOM MAX

UNIT

V

CC

Supply voltage 4.5 5 5.5 4.5 5 5.5 V

V

IH

High-level input voltage 2 2 V

V

IL

Low-level input voltage 0.7 0.8 V

I

OH

High-level output current –0.4 –0.4 mA

I

OL

Low-level output current 4 8 mA

f

clock

Clock frequency 0 22 0 40 MHz

t

w

Pulse duration, CLK high or low 14 12.5 ns

A, B, C, or D 20 15

p

ENP or ENT 25 15

tsuSetup time before CLK↑

LOAD 20 15

ns

U/D 28 15

t

h

Hold time, data after CLK↑ 0 0 ns

T

A

Operating free-air temperature –55 125 0 70 °C

electrical characteristics over recommended operating free-air temperature range (unless

otherwise noted)

SN54ALS169B SN74ALS169B

PARAMETER

TEST CONDITIONS

MIN TYP†MAX MIN TYP†MAX

UNIT

V

IK

VCC = 4.5 V, II = –18 mA –1.5 –1.5 V

V

OH

VCC = 4.5 V to 5.5 V, IOH = –0.4 mA VCC –2 VCC –2 V

IOL = 4 mA 0.25 0.4 0.25 0.4

V

OL

V

CC

= 4.5

V

IOL = 8 mA 0.35 0.5

V

I

I

VCC = 5.5 V, VI = 7 V 0.1 0.1 mA

I

IH

VCC = 5.5 V, VI = 2.7 V 20 20 µA

I

IL

VCC = 5.5 V, VI = 0.4 V –0.2 –0.2 mA

I

O

‡

VCC = 5.5 V, VO = 2.25 V –20 –112 –30 –112 mA

I

CC

VCC = 5.5 V 15 25 15 25 mA

†

All typical values are at VCC = 5 V, TA = 25°C.

‡

The output conditions have been chosen to produce a current that closely approximates one half of the true short-circuit output current, IOS.

SN54ALS169B, SN54AS169A, SN74ALS169B, SN74AS169A

SYNCHRONOUS 4-BIT UP/DOWN BINARY COUNTERS

SDAS125B – MARCH 1984 – REVISED DECEMBER 1994

2–6

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

switching characteristics (see Figure 1)

PARAMETER

FROM

(

INPUT

)

TO

(

OUTPUT

)

VCC = 4.5 V to 5.5 V,

CL = 50 pF,

RL = 500 Ω

,

TA = MIN to MAX

†

UNIT

(INPUT)

(OUTPUT)

SN54ALS169B SN74ALS169B

MIN MAX MIN MAX

f

max

22 40 MHz

t

PLH

3 20 3 20

t

PHL

CLK

RCO

6 25 6 20

ns

t

PLH

2 20 2 15

t

PHL

CLK

Any Q

5 23 5 20

ns

t

PLH

2 16 2 13

t

PHL

ENT

RCO

3 24 3 16

ns

t

PLH

4 22 5 19

t

PHL

U/D

RCO

5 26 5 19

ns

†

For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

‡

Supply voltage, V

CC

7 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input voltage, V

I

7 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating free-air temperature range, T

A

: SN54AS169A –55°C to 125°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SN74AS169A 0°C to 70°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range –65°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

‡

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

recommended operating conditions

SN54AS169A SN74AS169A

MIN NOM MAX MIN NOM MAX

UNIT

V

CC

Supply voltage 4.5 5 5.5 4.5 5 5.5 V

V

IH

High-level input voltage 2 2 V

V

IL

Low-level input voltage 0.8 0.8 V

I

OH

High-level output current –2 –2 mA

I

OL

Low-level output current 20 20 mA

f

clock

* Clock frequency 0 60 0 75 MHz

tw* Pulse duration, CLK high or low 7.7 6.7 ns

A, B, C, or D 10 8

*

p

ENP or ENT 10 8

tsu*

Setup time before CLK↑

LOAD 10 8

ns

U/D 14 11

th* Hold time, data after CLK↑ 2 0 ns

T

A

Operating free-air temperature –55 125 0 70 °C

* On products compliant to MIL-STD-883, Class B, this parameter is based on characterization data but is not production tested.

SN54ALS169B, SN54AS169A, SN74ALS169B, SN74AS169A

SYNCHRONOUS 4-BIT UP/DOWN BINARY COUNTERS

SDAS125B – MARCH 1984 – REVISED DECEMBER 1994

2–7

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

electrical characteristics over recommended operating free-air temperature range (unless

otherwise noted)

SN54AS169A SN74AS169A

PARAMETER

TEST CONDITIONS

MIN TYP†MAX MIN TYP†MAX

UNIT

V

IK

VCC = 4.5 V, II = –18 mA –1.2 –1.2 V

V

OH

VCC = 4.5 V to 5.5 V, IOH = –2 mA VCC –2 VCC –2 V

V

OL

VCC = 4.5 V, IOL = 20 mA 0.25 0.5 0.25 0.5 V

LOAD, ENT, U/D

0.2 0.2

I

I

All others

V

CC

= 5.5 V,

V

I

= 7

V

0.1 0.1

mA

LOAD, ENT, U/D

40 40

I

IH

All others

V

CC

=

5.5 V

,

V

I

=

2.7 V

20 20

µ

A

LOAD, ENT, U/D

–1 –1

I

IL

All others

V

CC

= 5.5 V,

V

I

= 0.4

V

–0.5 –0.5

mA

I

O

‡

VCC = 5.5 V, VO = 2.25 V –30 –112 –30 –112 mA

I

CC

VCC = 5.5 V 41 63 41 63 mA

†

All typical values are at VCC = 5 V, TA = 25°C.

‡

The output conditions have been chosen to produce a current that closely approximates one half of the true short-circuit output current, IOS.

switching characteristics (see Figure 1)

PARAMETER

FROM

(

INPUT

)

TO

(

OUTPUT

)

VCC = 4.5 V to 5.5 V,

CL = 50 pF,

RL = 500 Ω

,

TA = MIN to MAX

§

UNIT

(INPUT)

(OUTPUT)

SN54AS169A SN74AS169A

MIN MAX MIN MAX

f

max

* 60 75 MHz

t

PLH

RCO

3 17.5 3 16.5

t

PHL

CLK

(LOAD high or low)

2 14 2 13

ns

t

PLH

1 7.5 1 7

t

PHL

CLK

Any Q

2 14 2 13

ns

t

PLH

1.5 10 1.5 9

t

PHL

ENT

RCO

1.5 10 1.5 9

ns

t

PLH

2 14 2 12

t

PHL

U/D

RCO

2 14.5 2 13

ns

* On products compliant to MIL-STD-883, Class B, this parameter is based on characterization data but is not production tested.

§

For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

SN54ALS169B, SN54AS169A, SN74ALS169B, SN74AS169A

SYNCHRONOUS 4-BIT UP/DOWN BINARY COUNTERS

SDAS125B – MARCH 1984 – REVISED DECEMBER 1994

2–8

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

PARAMETER MEASUREMENT INFORMATION

SERIES 54ALS/74ALS AND 54AS/74AS DEVICES

t

PHZ

t

PLZ

t

PHL

t

PLH

0.3 V

t

PZL

t

PZH

t

PLH

t

PHL

LOAD CIRCUIT

FOR 3-STATE OUTPUTS

From Output

Under Test

Test

Point

R1

S1

C

L

(see Note A)

7 V

1.3 V

1.3 V1.3 V

3.5 V

3.5 V

0.3 V

0.3 V

t

h

t

su

VOLTAGE WAVEFORMS

SETUP AND HOLD TIMES

Timing

Input

Data

Input

1.3 V 1.3 V

3.5 V

3.5 V

0.3 V

0.3 V

High-Level

Pulse

Low-Level

Pulse

t

w

VOLTAGE WAVEFORMS

PULSE DURATIONS

Input

Out-of-Phase

Output

(see Note C)

1.3 V 1.3 V

1.3 V1.3 V

1.3 V 1.3 V

1.3 V1.3 V

1.3 V

1.3 V

3.5 V

3.5 V

0.3 V

0.3 V

V

OL

V

OH

V

OH

V

OL

Output

Control

(low-level

enabling)

Waveform 1

S1 Closed

(see Note B)

Waveform 2

S1 Open

(see Note B)

[

0 V

V

OH

V

OL

[

3.5 V

In-Phase

Output

0.3 V

1.3 V 1.3 V

VOLTAGE WAVEFORMS

PROPAGATION DELAY TIMES

VOLTAGE WAVEFORMS

ENABLE AND DISABLE TIMES, 3-STATE OUTPUTS

R2

V

CC

R

L

Test

Point

From Output

Under Test

C

L

(see Note A)

LOAD CIRCUIT

FOR OPEN-COLLECTOR OUTPUTS

LOAD CIRCUIT FOR

BI-STATE

TOTEM-POLE OUTPUTS

From Output

Under Test

Test

Point

C

L

(see Note A)

R

L

RL = R1 = R2

NOTES: A. CL includes probe and jig capacitance.

B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control.

Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

C. When measuring propagation delay items of 3-state outputs, switch S1 is open.

D. All input pulses have the following characteristics: PRR ≤ 1 MHz, tr = tf = 2 ns, duty cycle = 50%.

E. The outputs are measured one at a time with one transition per measurement.

Figure 1. Load Circuits and Voltage Waveforms

IMPORTANT NOTICE

T exas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue

any product or service without notice, and advise customers to obtain the latest version of relevant information

to verify, before placing orders, that information being relied on is current and complete. All products are sold

subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those

pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent

TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily

performed, except those mandated by government requirements.

CERT AIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF

DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL

APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR

WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER

CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICA TIONS IS UNDERST OOD TO

BE FULLY AT THE CUSTOMER’S RISK.

In order to minimize risks associated with the customer’s applications, adequate design and operating

safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent

that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other

intellectual property right of TI covering or relating to any combination, machine, or process in which such

semiconductor products or services might be or are used. TI’s publication of information regarding any third

party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.

Copyright 1998, Texas Instruments Incorporated

Loading...

Loading...