Page 1

MSP50C614

Mixed-Signal Processor

User’s Guide

SPSU014

January 2000

Printed on Recycled Paper

Page 2

IMPORTANT NOTICE

T exas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue

any product or service without notice, and advise customers to obtain the latest version of relevant information

to verify, before placing orders, that information being relied on is current and complete. All products are sold

subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those

pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent

TI deems necessary to support this warranty . Specific testing of all parameters of each device is not necessarily

performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF

DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL

APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR

WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER

CRITICAL APPLICA TIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERST OOD TO

BE FULLY AT THE CUSTOMER’S RISK.

In order to minimize risks associated with the customer’s applications, adequate design and operating

safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent

that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other

intellectual property right of TI covering or relating to any combination, machine, or process in which such

semiconductor products or services might be or are used. TI’s publication of information regarding any third

party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.

Copyright 2000, Texas Instruments Incorporated

Page 3

About This Manual

This user’s guide gives information for the MSP50C61 mixed-signal processor. This information includes a functional overview, a detailed architectural

description, device peripheral functional description, assembly language

instruction listing, code development tools, applications, customer information, and electrical characteristics (in data sheet). This document also contains

information for the MSP50C604 and MSP50C605, which are in the Product

Preview stage of development.

How to Use This Manual

This document contains the following chapters:

-

Preface

Read This First

Chapter 1 –Introduction to the MSP50C614

-

-

-

-

-

-

-

-

-

Notational Conventions

This document uses the following conventions.

-

Chapter 2 –MSP50C614 Architecture

Chapter 3 –Peripheral Functions

Chapter 4 –Assembly Language Instructions

Chapter 5 –Code Development Tools

Chapter 6 –Applications

Chapter 7 –Customer Information

Appendix A –MSP50C605 Preliminary Data

Appendix B –MSP50C604 Preliminary Data

Appendix C –MSP50C605 Data Sheet

Program listings, program examples, and interactive displays are shown

in a special typeface similar to a typewriter’s. Examples use a bold

Read This First

iii

Page 4

Notational Conventions

version of the special typeface for emphasis; interactive displays use a

bold version of the special typeface to distinguish commands that you

enter from items that the system displays (such as prompts, command

output, error messages, etc.).

Here is a sample program listing:

0011 0005 0001 .field 1, 2

0012 0005 0003 .field 3, 4

0013 0005 0006 .field 6, 3

0014 0006 .even

Here is an example of a system prompt and a command that you might

enter:

C: csr –a /user/ti/simuboard/utilities

-

In syntax descriptions, the instruction, command, or directive is in a bold

typeface font and parameters are in an

italic typeface

. Portions of a syntax

that are in bold should be entered as shown; portions of a syntax that are

italics

in

describe the type of information that should be entered. Here is

an example of a directive syntax:

.asect ”

section name

”,

address

.asect is the directive. This directive has two parameters, indicated by

tion name

and

address

. When you use .asect, the first parameter must be

an actual section name, enclosed in double quotes; the second parameter

must be an address.

-

Square brackets ( [ and ] ) identify an optional parameter. If you use an

optional parameter, you specify the information within the brackets; you

don’t enter the brackets themselves. Here’s an example of an instruction

that has an optional parameter:

LALK

The LALK instruction has two parameters. The first parameter,

stant

16–bit constant [, shift]

, is required. The second parameter,

16-bit con-

shift

, is optional. As this syntax

shows, if you use the optional second parameter, you must precede it with

a comma.

Square brackets are also used as part of the pathname specification for

VMS pathnames; in this case, the brackets are actually part of the pathname (they are not optional).

-

Braces ( { and } ) indicate a list. The symbol | (read as or) separates items

within the list. Here’s an example of a list:

{ * | *+ | *– }

sec-

This provides three choices: *, *+, or *–.

iv

Page 5

Information About Cautions and Warnings

Unless the list is enclosed in square brackets, you must choose one item

from the list.

-

Some directives can have a varying number of parameters. For example,

the .byte directive can have up to 100 parameters. The syntax for this directive is:

.byte

value1 [, ... , valuen]

This syntax shows that .byte must have at least one value parameter, but

you have the option of supplying additional value parameters, separated

by commas.

Information About Cautions and Warnings

This book may contain cautions and warnings.

This is an example of a caution statement.

A caution statement describes a situation that could potentially

damage your software or equipment.

This is an example of a warning statement.

A warning statement describes a situation that could potentially

cause harm to you.

The information in a caution or a warning is provided for your protection.

Please read each caution and warning carefully.

Trademarks

Intel, i486, and Pentium are trademarks of Intel Corporation.

Microsoft, Windows, Windows 95, and Windows 98 are registered trademarks of Microsoft Corporation.

Read This First

v

Page 6

vi

Page 7

Contents

Contents

1 Introduction to the MSP50C614 1-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1 Features of the C614 1-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2 Applications 1-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3 Development Device: MSP50P614 1-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4 Functional Description 1-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.5 C605 and C604 (Preliminary Information) 1-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.6 Terminal Assignments and Signal Descriptions 1-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2 MSP50C614 Architecture 2-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1 Architecture Overview 2-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2 Computation Unit 2-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.1 Multiplier 2-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.2 Arithmetic Logic Unit 2-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3 Data Memory Address Unit 2-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3.1 RAM Configuration 2-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3.2 Data Memory Addressing Modes 2-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4 Program Counter Unit 2-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5 Bit Logic Unit 2-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6 Memory Organization: RAM and ROM 2-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.1 Memory Map 2-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.2 Peripheral Communications (Ports) 2-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.3 Interrupt Vectors 2-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.4 ROM Code Security 2-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.5 Macro Call Vectors 2-22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.7 Interrupt Logic 2-22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.8 Timer Registers 2-26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.9 Clock Control 2-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.9.1 Oscillator Options 2-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.9.2 PLL Performance 2-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.9.3 Clock Speed Control Register 2-30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.9.4 RTO Oscillator Trim Adjustment 2-32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.10 Execution Timing 2-33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.11 Reduced Power Modes 2-34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3 Peripheral Functions 3-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1 I/O 3-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

vii

Page 8

Contents

3.1.1 General-Purpose I/O Ports 3-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.2 Dedicated Input Port F 3-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.3 Dedicated Output Port G 3-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.4 Branch on D Port 3-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.5 Internal and External Interrupts 3-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2 Digital-to-Analog Converter (DAC) 3-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.1 Pulse-Density Modulation Rate 3-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.2 DAC Control and Data Registers 3-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.3 PDM Clock Divider 3-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3 Comparator 3-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4 Interrupt/General Control Register 3-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5 Hardware Initialization States 3-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4 Assembly Language Instructions 4-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1 Introduction 4-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2 System Registers 4-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.1 Multiplier Register (MR) 4-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.2 Shift Value Register (SV) 4-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.3 Data Pointer Register (DP) 4-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.4 Program Counter (PC) 4-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.5 Top of Stack, (TOS) 4-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.6 Product High Register (PH) 4-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.7 Product Low Register (PL) 4-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.8 Accumulators (AC0–AC31) 4-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.9 Accumulator Pointers (AP0–AP3) 4-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.10 Indirect Register (R0–R7) 4-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.11 String Register (STR) 4-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.12 Status Register (STAT) 4-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3 Instruction Syntax and Addressing Modes 4-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.1 MSP50P614/MSP50C614 Instruction Syntax 4-8. . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.2 Addressing Modes 4-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.3 Immediate Addressing 4-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.4 Direct Addressing 4-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.5 Indirect Addressing 4-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.6 Relative Addressing 4-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.7 Flag Addressing 4-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.8 Tag/Flag Bits 4-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4 Instruction Classification 4-22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.2 Class 2 Instructions: Accumulator and Constant Reference 4-28. . . . . . . . . . . . . .

4.4.3 Class 3 Instruction: Accumulator Reference 4-30. . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.4 Class 4 Instructions: Address Register and Memory Reference 4-34. . . . . . . . . . .

4.4.5 Class 5 Instructions: Memory Reference 4-36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.6 Class 6 Instructions: Port and Memory Reference 4-38. . . . . . . . . . . . . . . . . . . . . .

4.4.7 Class 7 Instructions: Program Control 4-39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

viii

Page 9

Contents

4.4.8 Class 8 Instructions: Logic and Bit 4-41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.9 Class 9 Instructions: Miscellaneous 4-42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5 Bit, Byte, Word and String Addressing 4-44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.6 MSP50P614/MSP50C614 Computational Modes 4-49. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.7 Hardware Loop Instructions 4-53. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.8 String Instructions 4-55. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.9 Lookup Instructions 4-57. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.10 Input/Output Instructions 4-59. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.11 Special Filter Instructions 4-59. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.12 Conditionals 4-69. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.13 Legend 4-70. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.14 Individual Instruction Descriptions 4-74. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.15 Instruction Set Encoding 4-187. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.16 Instruction Set Summary 4-196. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5 Code Development Tools 5-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1 Introduction 5-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2 MSP50C6xx Software Development Tool 5-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3 Requirements 5-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.4 Hardware Installation 5-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.5 Software Installation 5-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6 Software Emulator 5-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6.1 The Open Screen 5-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6.2 Projects 5-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6.3 Description of Windows 5-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6.4 Debugging a Program 5-22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6.5 Initializing Chip 5-27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6.6 Emulator Options 5-28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6.7 Emulator Online Help System 5-30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6.8 Known Differences, Incompatibilities, Restrictions 5-32. . . . . . . . . . . . . . . . . . . . . . .

5.7 Assembler 5-33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.7.1 Assembler DLL 5-33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.7.2 Assembler Directives 5-34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.8 Linker 5-38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.9 C–– Compiler 5-39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.9.1 Foreword 5-40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.9.2 Variable Types 5-41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.9.3 External References 5-41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.9.4 C– – Directives 5-42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.9.5 Include Files 5-44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.9.6 Function Prototypes and Declarations 5-45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.9.7 Initializations 5-45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.9.8 RAM Usage 5-45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.9.9 Variable Types 5-45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Contents

ix

Page 10

Contents

5.9.10 String Functions 5-45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.9.11 Constant Functions 5-47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.10 Implementation Details 5-48. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.10.1 Comparisons 5-48. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.10.2 Division 5-50. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.10.3 Function Calls 5-50. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.10.4 Programming Example 5-51. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.10.5 Programming Example, C – With Assembly Routines 5-53. . . . . . . . . . . . . . . . . . .

5.11 Beware of Stack Corruption 5-67. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.12 Reported Bugs With Code Development Tool 5-67. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6 Applications 6-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.1 Application Circuits 6-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2 MSP50C614/MSP50P614 Initialization Codes 6-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2.1 File init.asm 6-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3 Texas Instruments C614 Synthesis Code 6-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.1 Memory Overlay 6-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.4 ROM Usage With Respect to Various Synthesis Algorithms 6-14. . . . . . . . . . . . . . . . . . . . .

7 Customer Information 7-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.1 Mechanical Information 7-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.1.1 Die Bond-Out Coordinates 7-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.1.2 Package Information 7-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2 Customer Information Fields in the ROM 7-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.3 Speech Development Cycle 7-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.4 Device Production Sequence 7-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.5 Ordering Information 7-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.6 New Product Release Forms 7-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A MSP50C605 Preliminary Data A-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.1 Introduction A-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.2 Features A-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.3 Architecture A-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.3.1 RAM A-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.3.2 ROM A-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.3.3 I/O Pins A-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B MSP50C604 Preliminary Data B-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.1 Introduction B-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.2 Features B-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.3 Architecture B-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.3.1 RAM B-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.3.2 ROM B-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.3.3 I/O Pins B-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.3.4 Slave Mode Operation B-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

x

Page 11

Contents

B.3.5 Host Write Sequence B-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.3.6 Host Read Sequence B-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.3.7 Interrupts B-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.4 Packaging B-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C MSP50C605 Data Sheet C-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C.1 MSP50C605 Data Sheet C-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Contents

xi

Page 12

Figures

Figures

1–1 Functional Block Diagram for the C614 1-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1–2 Oscillator and PLL Connection 1-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1–3 RESET Circuit 1-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

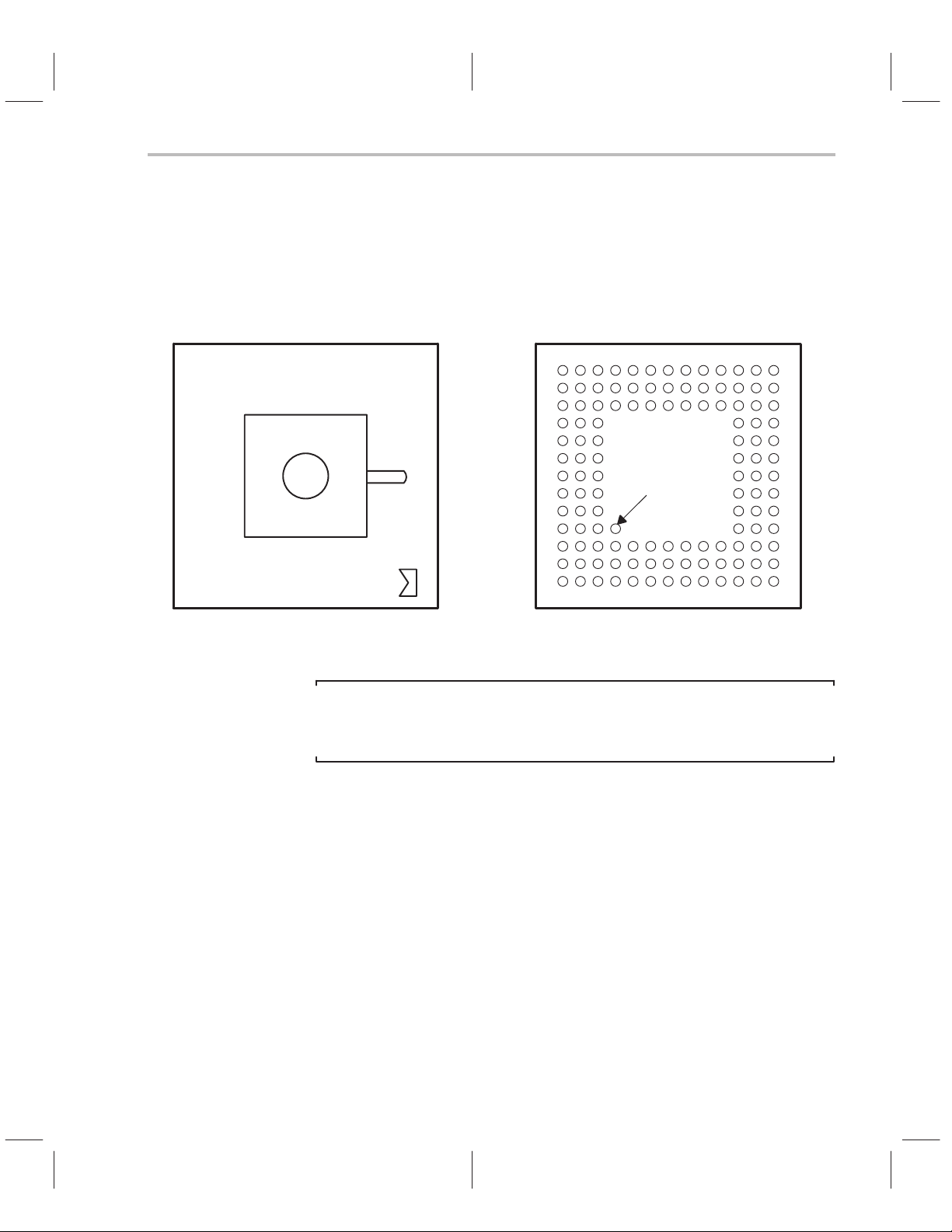

1–4 MSP50C614 100 Pin PJM PLastic Package Pinout 1-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1–5 120 Pin Grid Array Package for the Development Device, P614 1-13. . . . . . . . . . . . . . . . . . . .

2–1 MSP50C614 Core Processor Block Diagram 2-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–2 Computational Unit Block Diagram 2-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–3 Overview of the Multiplier Unit Operation 2-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–4 Overview of the Arithmetic Logic Unit 2-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–5 Overview of the Arithmetic Logic Unit 2-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–6 Data Memory Address Unit 2-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–7 C614 Memory Map (not drawn to scale) 2-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–8 Interrupt Initialization Sequence 2-25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–9 PLL Performance 2-30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–10 Instruction Execution and Timing 2-34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–1 PDM Clock Divider 3-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–2 Relationship Between Comparator/Interrupt Activity and the TIMER1 Control 3-15. . . . . . . .

4–1 Top of Stack (TOS) Register Operation 4-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–2 Relative Flag Addressing 4-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–3 Data Memory Organization and Addressing 4-45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–4 Data Memory Example 4-47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–5 FIR Filter Structure 4-59. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–6 Setup and Execution of MSP50P614/MSP50C614 Filter Instructions, N+1 Taps 4-67. . . . . .

4–7 Filter Instruction and Circular Buffering for N+1 Tap Filter 4-68. . . . . . . . . . . . . . . . . . . . . . . . . .

4–8 Valid Moves/Transfer in MSP50P614/MSP50C614 Instruction Set 4-131. . . . . . . . . . . . . . . . .

5–1 Level Translator Circuit 5-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–2 Hardware Installation 5-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–3 10-Pin IDC Connector 5-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–4 InstallShield Window 5-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–5 Setup Window 5-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–6 Exit Setup Dialog 5-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–7 User Information Dialog 5-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–8 Choose Destination Location Dialog 5-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xii

Page 13

Figures

5–9 Select Program Folder Dialog 5-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–10 Copying Files 5-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–11 Setup Complete Dialog 5-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–12 Open Screen 5-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–13 Project Menu 5-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–14 Project Open Dialog 5-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–15 File Menu Options 5-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–16 MSP50P614/MSP50C614 Code Development Windows 5-16. . . . . . . . . . . . . . . . . . . . . . . . . .

5–17 RAM Window 5-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–18 CPU Window 5-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–19 Program Window 5-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–20 Hardware Breakpoint Dialog 5-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–21 Inspect Dialog 5-21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–22 Inspect Window 5-21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–23 I/O Ports Window 5-22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–24 Debug Menu 5-23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–25 EPROM Programming Dialog 5-25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–26 Trace Mode 5-26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–27 Init Menu Option 5-27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–28 Options Menu 5-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–29 Miscellaneous Dialog 5-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–30 Windows Menu Options 5-30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–31 Context Sensitive Help System 5-31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–1 100-Pin PJM Mechanical Information 7-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–2 120-Pin Grid Array Package for the Development Device, P614 7-5. . . . . . . . . . . . . . . . . . . . .

7–3 120 Pin Grid Array (PGA) Package Leads, P614 7-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–4 Speech Development Cycle 7-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–1 MSP50C605 Architecture A-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–2 MSP50C605 Memory Organization A-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–3 MSP50C605 100-Pin PJM Package A-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B–1 MSP50C604 Block Diagram B-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B–2 MSP50C604 Memory Organization and I/O ports B-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B–3 MSP50C604 Slave Mode Signals B-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B–4 MSP50C604 64-Pin PJM Package B-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Contents

xiii

Page 14

Tables

Tables

1–1 Signal and Pad Descriptions for the C614 1-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1–2 MSP50C614 100-Pin PJM Plastic Package Pinout Description 1-11. . . . . . . . . . . . . . . . . . . . .

2–1 Signed and Unsigned Integer Representation 2-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–2 Summary of C614’s Peripheral Communications Ports 2-17. . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–3 Programmable Bits Needed to Control Reduced Power Modes 2-37. . . . . . . . . . . . . . . . . . . . .

2–4 Status of Circuitry When in Reduced Power Modes 2-38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–5 How to Wake-Up from Reduced Power Modes 2-39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–6 Destination of Program Counter on Wake-Up Under Various Conditions 2-40. . . . . . . . . . . . .

3–1 Interrupts 3-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–2 State of the Status Register (17 bit) after RESET Low-to-High 3-21. . . . . . . . . . . . . . . . . . . . .

4–1 Status Register (STAT) 4-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–2 Addressing Mode Encoding 4-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–3 Rx Bit Description 4-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–4 Addressing Mode Bits and {adrs} Field Description 4-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–5 MSP50P614/MSP50C614 Addressing Modes Summary 4-11. . . . . . . . . . . . . . . . . . . . . . . . . .

4–6 Auto Increment and Auto Decrement Modes 4-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–7 Flag Addressing Field {flagadrs} for Certain Flag Instructions (Class 8a) 4-12. . . . . . . . . . . . .

4–8 Initial Processor State for the Examples Before Execution of Instruction 4-13. . . . . . . . . . . . .

4–9 Indirect Addressing Syntax 4-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–10 Symbols and Explanation 4-22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–1 1 Instruction Classification 4-23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–12 Classes and Opcode Definition 4-25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–13 Class 1 Instruction Encoding 4-26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–14 Class 1a Instruction Description 4-26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–15 Class 1b Instruction Description 4-27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–16 Class 2 Instruction Encoding 4-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–17 Class 2a Instruction Descritpion 4-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–18 Class 2b Insstruction Description 4-30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–19 Class 3 Instruction Encoding 4-31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–20 Class 3 Instsruction Description 4-31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–21 Class 4a Instruction Encoding 4-34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–22 Class 4a Instruction Description 4-35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–23 Class 4b Instruction Description 4-35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–24 Class 4c Instruction Description 4-35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xiv

Page 15

4–25 Class 4d Instruction Description 4-35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–26 Class 5 Instruction Encoding 4-36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–27 Class 5 Instruction Description 4-36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–28 Class 6a Instruction Encoding 4-38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–29 Class 6a Instruction Description 4-38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–30 Class 6b Instruction Description 4-39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–31 Class 7 Instruction Encoding and Description 4-40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–32 Class 8a Instruction Encoding 4-41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–33 Class 8a Instruction Description 4-42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–34 Class 8b Instruction Description 4-42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–35 Class 9a Instruction Encoding 4-43. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–36 Class 9a Instruction Description 4-43. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–37 Class 9b Instruction Description 4-43. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–38 Class 9c Instruction Description 4-44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–39 Class 9d Instruction Description 4-44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–40 Data Memory Address and Data Relationship 4-46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–41 MSP50P614/MSP50C614 Computational Modes 4-50. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–42 Hardware Loops in MSP50P614/MSP50C614 4-54. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–43 Initial Processor State for String Instructions 4-55. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–44 Lookup Instructions 4-57. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–45 Auto Increment and Decrement 4-73. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–46 Addressing Mode Bits and adrs Field Description 4-73. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–47 Flag Addressing Syntax and BIts 4-73. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–48 Names for cc 4-87. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tables

5–1 String Functions 5-46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–1 MSP50C614 100-Pin PJM Plastic Package Pinout Description 7-3. . . . . . . . . . . . . . . . . . . . . .

A–1 MSP50C605 100-Pin PJM Plastic Package Pinout Description A-7. . . . . . . . . . . . . . . . . . . . . .

B–1 MSP50C604 64-Pin PJM Plastic Package Pinout Description B-8. . . . . . . . . . . . . . . . . . . . . . .

Contents

xv

Page 16

Notes, Cautions, and Warnings

Notes, Cautions, and W arnings

MSP50C605 and MSP50C604 1-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PGA Package 1-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

ROM Locations that Hold Interrupt Vectors 2-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Instructions with References 2-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Block Protection Mode 2-21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Block Protections Word 2-21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Setting a Bit in the IFR Using the OUT Instruction 2-24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Interrupt Service Branch 2-24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Writing to the TIM Register 2-27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

ClkSpdCtrl Bits 8 and 9 2-31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Reference Oscillator Stopped by Programmed Disable 2-32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Register Trim Value 2-33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Idle State Clock Control Bit 2-36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Reading the Data Register 3-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PDM Enable Bit 3-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

IntGenCtrl Register Bit 15 3-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Internal RAM State after Reset 3-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Stack Pointer Initialization 3-21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Data Memory Access 4-45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Scan Port Bond Out 7-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

MSP50C605 A-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

MSP50C604 B-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xvi

Page 17

Chapter 1

Introduction to the MSP50C614

The MSP50C614 (C614) is a low cost, mixed signal controller, that combines

a speech synthesizer, general-purpose I/O, onboard ROM, and direct

speaker-drive in a single package. The computational unit utilizes a powerful

new DSP which gives the C614 unprecedented speed and computational

flexibility compared with previous devices of its type. The C614 supports a

variety of speech and audio coding algorithms, providing a range of options

with respect to speech duration and sound quality.

Topic Page

1.1 Features of the C614 1–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2 Applications 1–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3 Development Version: P614 1–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4 Functional Description 1–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.5 C605 and C604 1–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.6 T erminal Assignments and Signal Descriptions 1–10. . . . . . . . . . . . . . .

1-1

Page 18

Features of the C614

1.1 Features of the C614

-

Advanced, integrated speech synthesizer for high quality sound

-

Operates up to 8 MHz (performs up to 8 MIPS)

-

Very low-power operation, ideal for hand-held devices

-

Low voltage operation, sustainable by three batteries

-

Reduced power stand-by modes, less than 10 µA in deep-sleep mode

-

Supports high-quality synthesis algorithms such as MELP, CELP, LPC,

and ADPCM

-

Contains 32K words onboard ROM (2K words reserved)

-

640 words RAM

-

40 general purpose, bit configurable I/O

-

8 inputs with programmable pullup resistors and a dedicated interrupt

(key-scan)

-

16 dedicated output pins

-

Direct speaker driver, 32 Ω (PDM)

-

One-bit comparator with edge-detection interrupt service (IMPORTANT:

Not currently supported)

-

Resistor-trimmed oscillator or 32-kHz crystal reference oscillator

-

Serial scan port for in-circuit emulation and diagnostics

-

The MSP50C614 is sold in die form; an emulator device for the

MSP50C614 is sold in a ceramic package for development.

1-2

Page 19

1.2 Applications

Applications

Due to its low cost, low-power needs, and high programmability, the C614 is

suitable for a wide variety of applications incorporating I/O control and highquality speech:

-

Talking Toys

-

Electronic Learning Aids

-

Games

-

Talking Clocks

-

Talking Books

-

Talking Dictionaries

-

Warning Systems

-

Equipment for the Handicapped

Introduction to the MSP50C614

1-3

Page 20

Development Device: MSP50P614

1.3 Development Device: MSP50P614

The MSP50P614 is an EPROM based version of the MSP50C614, and is

available in 120 pin windowed ceramic pin grid array. This EPROM based

version of the device is only available in limited quantities to support software

development. Since the MSP50P614 program memory is EPROM, each

person doing software development should have several of these PGA

packaged devices.

The MSP software development tool supports non-real-time debugging by

scanning the code sequence through the MSP50C614/MSP50P614 scanport

without programming the EPROM. However, the rate of code execution is limited by the speed of the PC parallel port. Any MSP50C614/MSP50P614 can

be used in this debugging mode.

The MSP50P614 EPROM must be programmed to debug the code in real

time. The MSP software development tool is used to program the EPROM, set

a breakpoint, and evaluate the internal registers after the breakpoint is

reached. If a change is made to the code, the code will need to be updated and

programmed into another device while erasing previous devices. This cycle

of programming, debugging, and erasing typically requires 10–15 devices to

be in the eraser at any one time, so 15–20 devices may be required to operate

efficiently . The windowed PGA version of the MSP50P614 is required for this

debugging mode.

1-4

Page 21

1.4 Functional Description

The device consists of a micro-DSP core, embedded program and data

memory , and a self-contained clock generation system. General-purpose periphery is comprised of 64 bits of partially configurable I/O.

The core processor is a general-purpose 16 bit micro-controller with DSP

capability. The basic core block includes a computational unit (CU), data

address unit, program address unit, two timers, eight level interrupt processor,

and several system and control registers. The core processor gives the P614

and C614 break-point capability in emulation.

The processor is a Harvard type for efficient DSP algorithm execution. It requires separate program and data memory blocks to permit simultaneous access. The ROM has a protection scheme to prevent third-party pirating. It is

configured in 32K 17-bit words.

The total ROM space is divided into two areas: 1) The lower 2K words are reserved by T exas Instruments for a built-in self-test, 2) the upper 30K is for user

program/data.

The data memory is internal static RAM. The RAM is configured in 640 17-bit

words. Both memories are designed to consume minimum power at a given

system clock and algorithm acquisition frequency.

Functional Description

A flexible clock generation system is included that enables the software to

control the clock over a wide frequency range. The implementation uses a

phase-locked loop (PLL) circuit that drives the processor clock at a selectable

frequency between the minimum and maximum achievable. Selectable

frequencies for the processor clock are spaced apart in 65.536-kHz steps. The

PLL clock-reference is also selectable; either a resistor-trimmed oscillator or

a crystal-referenced oscillator may be used. Internal and peripheral clock

sources are controlled separately to provide different levels of power

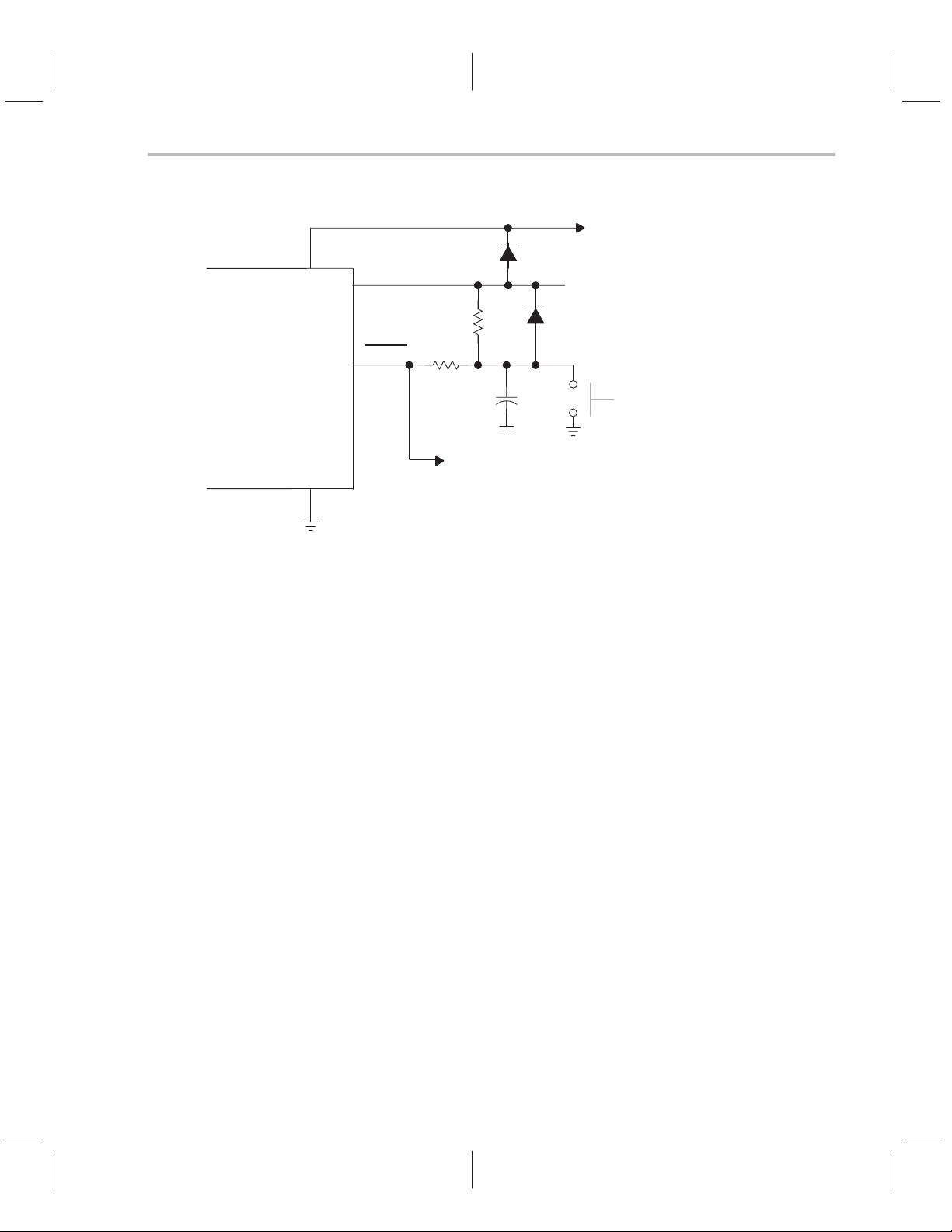

management (see Figure 1–2).

The peripheral consists of five 8-bit wide general-purpose I/O ports, one 8-bit

wide dedicated input port, and one 16-bit wide dedicated output port. The

bidirectional I/O can be configured under software control as either

high-impedance inputs or as totem-pole outputs. They are controlled via

addressable I/O registers. The input-only port has a programmable pullup

option (100-kΩ minimum resistance) and a dedicated service interrupt. These

features make the input port especially useful as a key-scan interface.

A simple one-bit comparator is also included in the periphery . The comparator

is enabled by a control register, and its pin access is shared with two pins in

one of the general-purpose I/O ports. Rounding out the C614 periphery is a

Introduction to the MSP50C614

1-5

Page 22

C605 and C604 (Preliminary Information)

built in pulse-density-modulated DAC (digital-to-analog converter) with direct

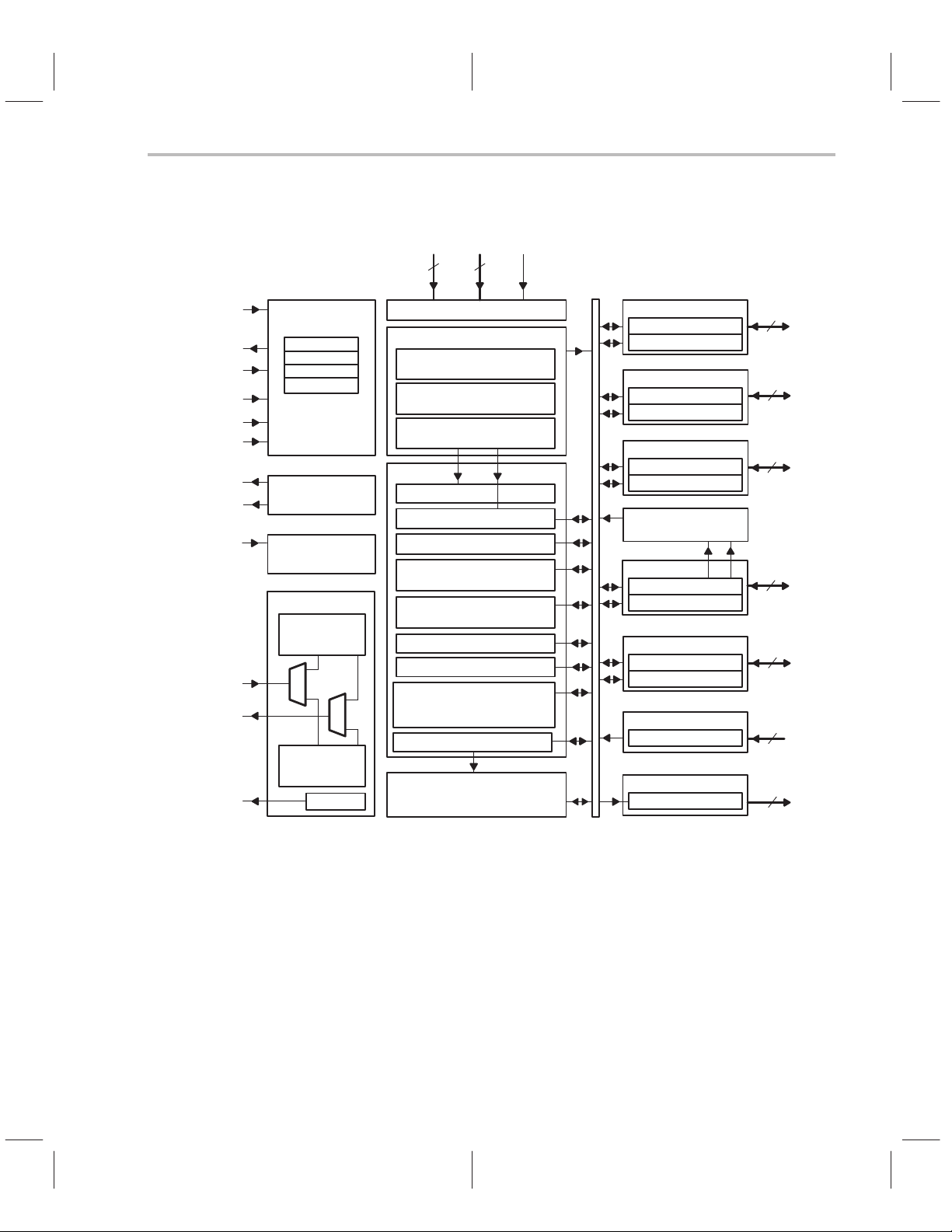

speaker-drive capability . The block diagram appearing in Figure 1–1 gives an

overview of the C614 functionality. IMPORTANT: a one bit comparator is not

currently supported.

Typical connections to implement reset functionality are shown in Figure 1–3.

1.5 C605 and C604 (Preliminary Information)

Two related products, the MSP50C605 (C605) and MSP50C604(C604) use

the C614 core. The C605 has a 224K byte data ROM built into the chip and

32 I/O port pins. The C605 can provide up to 30 minutes of uninterrupted

speech. The C604 is designed to support slave operation with an external host

microcontroller. In this mode the C604 can be programmed with a code that

communicates with the host via a command set. This command set can be designed to support LPC, CELP , MELP, and ADPCM coders by selecting the appropriate command. The C604 can also be used stand-alone in master mode.

The C604 and the C605 use the P614 as the development version device. Details on C605 and C604 processors are found in Appendix A and B.

Note: MSP50C605 and MSP50C604

MSP50C605 and MSP50C604 are in the Product Preview stage of development. For more information contact your local TI sales office. See Appendices A and B for more information.

1-6

Page 23

Figure 1–1. Functional Block Diagram for the C614

C605 and C604 (Preliminary Information)

V

SCAN

SCAN

PGM

SCAN

PULSE

RESET

OSC

OSC

OUT

CLK

SYNC

TEST

DAC

DAC

OUT

PLL

V

Power (P614 only)

(EP)ROM 32k x (16 + 1) bit

Test-Area

(reserved)

User ROM 0x0800 to

INT vectors 0x7FF0 to

Core

Instr. Decoder

PCU Prog. Counter Unit

CU Computational Unit

TIMER1 PRD1

TIMER2

Clock Control

Gen. Control

Interrupt Processor

or

DMAU

RAM 640 x 17 bit

(data)

P

M

Scan Interface

Break Point

Emulation

OTP Program

Serial Comm.

(C614 only)

(P614 only)

DAC 0x30

32 Ohm PDM

Initialization

Logic

OSC Reference

Resistor

Trimmed

32 kHz nominal

or

Crystal

Referenced

32.768 kHz

PLL Filter

IN

IN

DDVPP

SS

55

0x0000 to

0x3A

PRD2

0x3E

FLAG

0x39

Data Mem. Addr.

0x07FF

0x7FEF

0x7FFF

TIM1

0x3B

TIM2

0x3F

0x3D

0x38

MASK

0x38

0x000 to

0x027F

A port I/O

Data 0x00

Control 0x04

B port I/O

Data 0x08

Control 0x0C

C port I/O

Data 0x10

Control 0x14

Comparator

1 bit: PD5 vs PD

D port I/O

Data 0x18

Control 0x1C

E port I/O

Data 0x20

Control 0x24

F port INPUT

Data 0x28

G port OUTPUT

Data 0x2C

4

+–

PA

PB

PC

PD

PE

PF

PG

0–7

8

0–7

8

0–7

8

0–7

8

0–7

8

0–7

8

0–15

16

Introduction to the MSP50C614

1-7

Page 24

C605 and C604 (Preliminary Information)

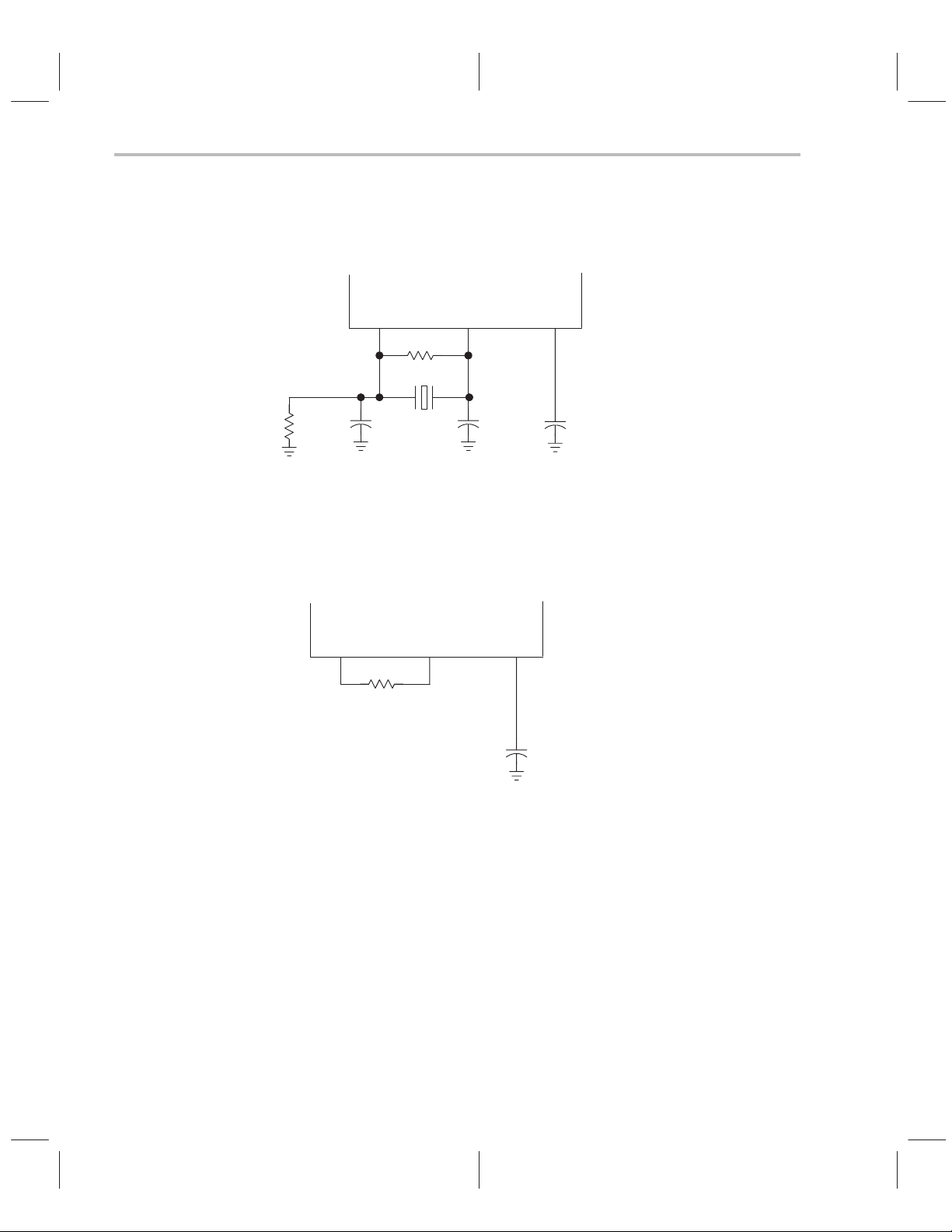

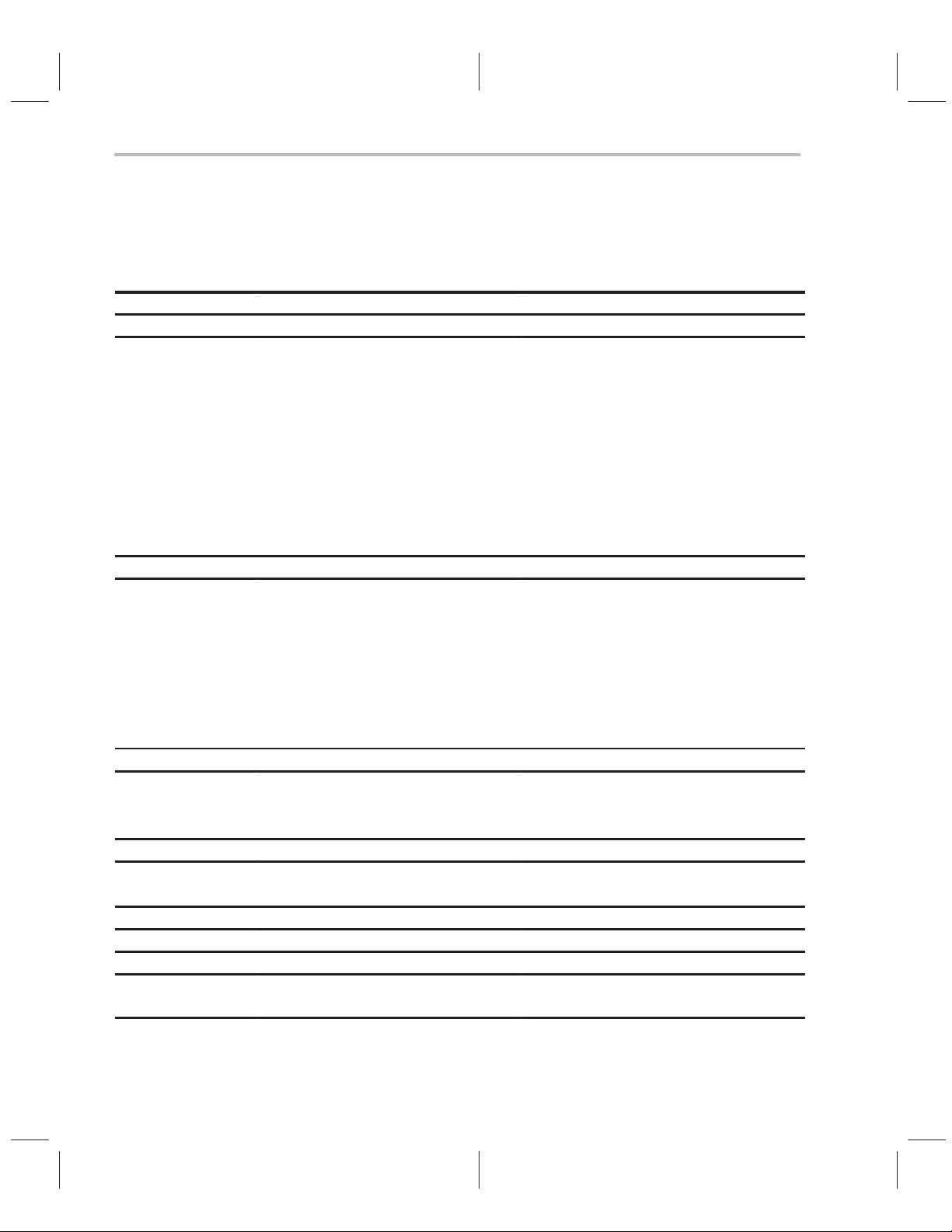

Figure 1–2. Oscillator and PLL Connection

a) Crystal Oscillator Operation Connections

MSP50P614

MSP50C614

OSC

IN

32.768 kHz†

10 Mن

†

Keep these components as close as possible to the OSCIN, OSC

22 pF†

OSCOUT PLL

10 Mن

b) Resistor Trim Operation Connections

MSP50C614

MSP50P614

OSC

R

(RTO)

IN

OSCOUT PLL

470 kΩ 1%†

=

22 pF†

, and PLL pins.

OUT

C

(PLL)

C

= 3300 pF†

(PLL)

= 3300 pF†

†

Keep these components as close as possible to the OSCIN, OSC

1-8

, and PLL pins.

OUT

Page 25

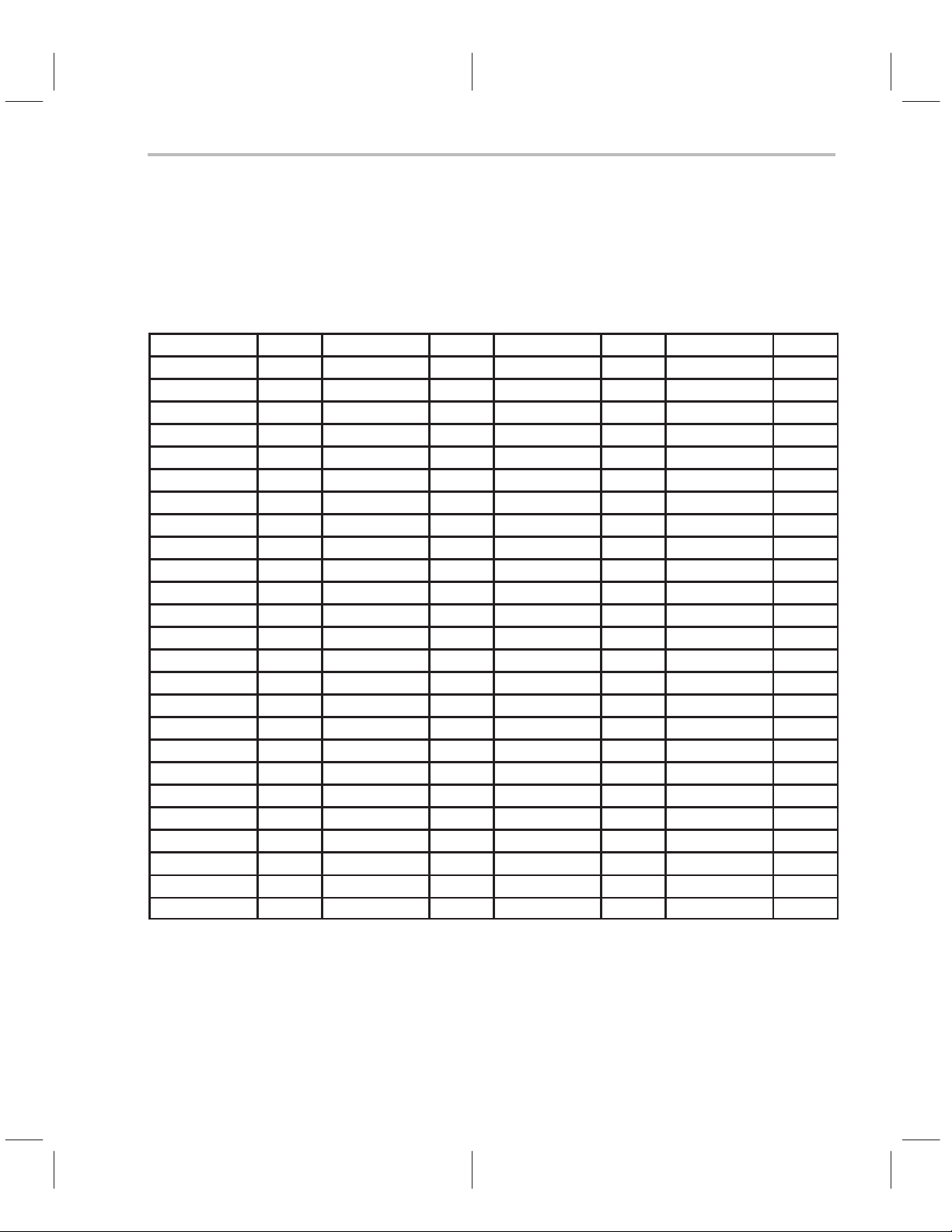

Figure 1–3. RESET Circuit

V

PP

(MSP50P614 only)

IN914

C605 and C604 (Preliminary Information)

To Pin 1 of Optional (Scanport)

Connector

‡

V

DD

100 kΩ

†

Inside the

MSP50P614

MSP50C614

†

If it is necessary to use the software development tools to control the MSP50P614 in application board, the 1 kΩ resistor is needed to allow the development tool to over drive the RESET circuit on the application board.

‡

This Diode can be omitted (shorted) if the application does not require use of the scanport interface. See Section 7.1.1 regarding

scan port bond out.

RESET

V

SS

1 kΩ

1 µF

(20%)

To Pin 2 of optional (scan port) connector

5 V

IN914

Reset

Switch

†

Introduction to the MSP50C614

1-9

Page 26

Terminal Assignments and Signal Descriptions

1.6 Terminal Assignments and Signal Descriptions

Table 1–1. Signal and Pad Descriptions for the C614

SIGNAL PAD NUMBER I/O DESCRIPTION

Input/Output Ports

PA0 – PA

PB0 – PB

PC0 – PC

PD0 – PD

PE0 – PE

PF0 – PF

PG0 – PG

PG8 – PG

Pins PD4 and PD5 may be dedicated to the comparator function, if the comparator enable bit is set.

Refer to Section 3.3,

SCANIN 54 I Scan port data input

SCANOUT 50 O Scan port data output

SCANCLK 53 I Scan port clock

SYNC 52 I Scan port synchronization

TEST

PGMPULSE

The scan port pins must be bonded out on any C614 production board.

Consult the “Important Note regarding Scan Port Bond Out”, Section 7.1.1,

OSC

OSC

PLL 67 O Phase-lock-loop filter

DAC

DAC

RESET 55 I Initialization

V

V

†

Pads VSS (19) and VDD (21) service the DAC circuitry. Their pins tend to sustain a higher current draw . A dedicated decoupling

capacitor across these pins is therefore required. Refer to Section 6.1,

7

7

7

7

7

7

7

15

Comparator

IN

OUT

P

M

SS

DD

75 → 68 I/O Port A general-purpose I/O (1 Byte)

85 → 78 I/O Port B general-purpose I/O (1 Byte)

8 → 1 I/O Port C general-purpose I/O (1 Byte)

18 → 11 I/O Port D general-purpose I/O (1 Byte)

63 → 56 I/O Port E general-purpose I/O (1 Byte)

31 → 24 I Port F key-scan input (1 Byte)

49 → 42

39 → 32

, for details. (Currently not supported)

Scan Port Control Signals

51 I C614 : test modes

Oscillator Reference Signals

65 I Resistor/crystal reference in

66 O Resistor/crystal reference out

DAC Sound Output

22 O Digital-to-analog output 1 (+)

20 O Digital-to-analog output 2 (–)

Power Signals

9, 19†, 40, 64, 76 Ground

10, 21†, 23, 41, 77 Processor power (+)

O Port G dedicated output (2 Bytes)

P614 : programming pulse

Scan Port Bond Out

Initialization

Application Circuits

.

, for details.

1-10

Page 27

Terminal Assignments and Signal Descriptions

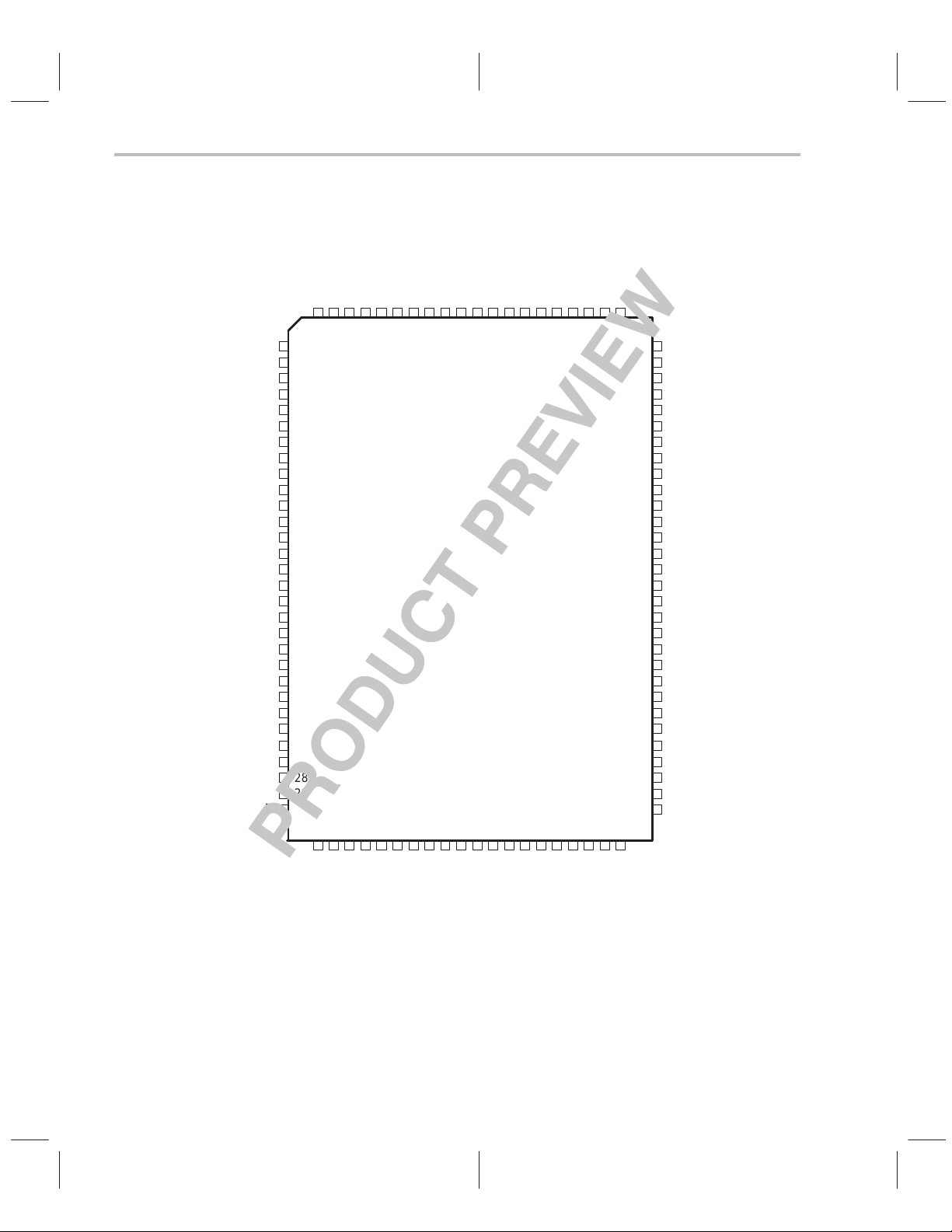

The C614 is sold in die form for its volume production. Contact you local TI

sales office for mount and bond information.

MSP50C614 is also available in 100 pin plastic QFP package. The pinout is

shown in Figure 1–4 and Table 1–2.

Table 1–2. MSP50C614 100-Pin PJM Plastic Package Pinout Description

Description Pin # Description Pin # Description Pin # Description Pin #

GND3/DA 1 GND4 26 PE

0

NC 2 VCC4 27 GND 52 NC 77

NC 3 NC 28 NC 53 NC 78

NC 4 NC 29 NC 54 NC 79

DAC

M

VCC3/DA 6 PF

DAC

P

V

CC

PF

7

PF

6

PF

5

PF

4

PF

3

PF

2

PF

1

PF

0

5 PG

7 PF

8 PF

9 PF

10 PF

11 PF

12 PF

7

6

5

4

3

2

1

0

30 NC 55 NC 80

31 X2 56 NC 81

32 X1 57 NC 82

33 PLL 58 PC

34 PA

35 PA

36 PA

37 PA

13 SCANOUT 38 PA

14 TEST 39 PA

15 SYNC 40 PA

16 SCANCLK 41 PA

7

6

5

4

3

2

1

0

NC 17 SCANIN 42 GND1 67 VCC2 92

PG

PG

PG

PG

PG

PG

PG

PG

15

14

13

12

11

10

9

8

18 RESET 43 VCC1 68 PD

19 PE

20 PE

21 PE

22 PE

23 PE

24 PE

25 PE

7

6

5

4

3

2

1

44 PB

45 PB

46 PB

47 PB

48 PB

49 PB

50 PB

7

6

5

4

3

2

1

51 PB

59 PC

60 PC

61 PC

62 PC

63 PC

64 PC

65 PC

0

7

6

5

4

3

2

1

0

66 GND2 91

7

69 PD

70 PD

71 PD

72 PD

73 PD

74 PD

75 PD

6

5

7

73

2

1

0

76

83

84

85

86

87

88

89

90

93

94

95

96

97

98

99

100

Introduction to the MSP50C614

1-11

Page 28

Terminal Assignments and Signal Descriptions

Figure 1–4. MSP50C614 100 Pin PJM PLastic Package Pinout (Preliminary Information)

PJM PACKAGE

(TOP VIEW)

2

PD6

94

37

PD7

93

38

CC

V

92

39

GND2

PC0

90

91

41

40

PC1

89

42

PC2

88

43

PC3

87

44

PC4

86

45

PC5

85

46

PC6

PC7NCNC

83

84

48

47

82

49

81

50

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

NC

NC

NC

NC

PB0

PB1

PB2

PB3

PB4

PB5

PB6

PB7

V

CC

GND1

PA0

PA1

PA2

PA3

PA4

PA5

PA6

PA7

PLL

X1

X2

NC

NC

NC

GND

PE0

1

GND3/DA

NC

NC

NC

DACM

3/DAV

CC

DACP

V

CC

PF7

PF6

PF5

PF4

PF3

PF2

PF1

PF0

NC

PG15

PG14

PG13

PG12

PG11

PG10

PG9

PG8

GND4

CC

NC

NC

PG7

PD1

PD2

PD4

PD5

99

32

98

33

PD3

97

34

96

35

95

36

PD0

100

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

4V

28

29

30

31

1-12

PG6

PG5

PG4

PG3

PG2

PG1

PG0

TEST

SCANOUT

SYNC

SCANIN

SCANCLK

PE7

PE6

RESET

PE5

PE4

PE3

PE2

PE1

Page 29

Terminal Assignments and Signal Descriptions

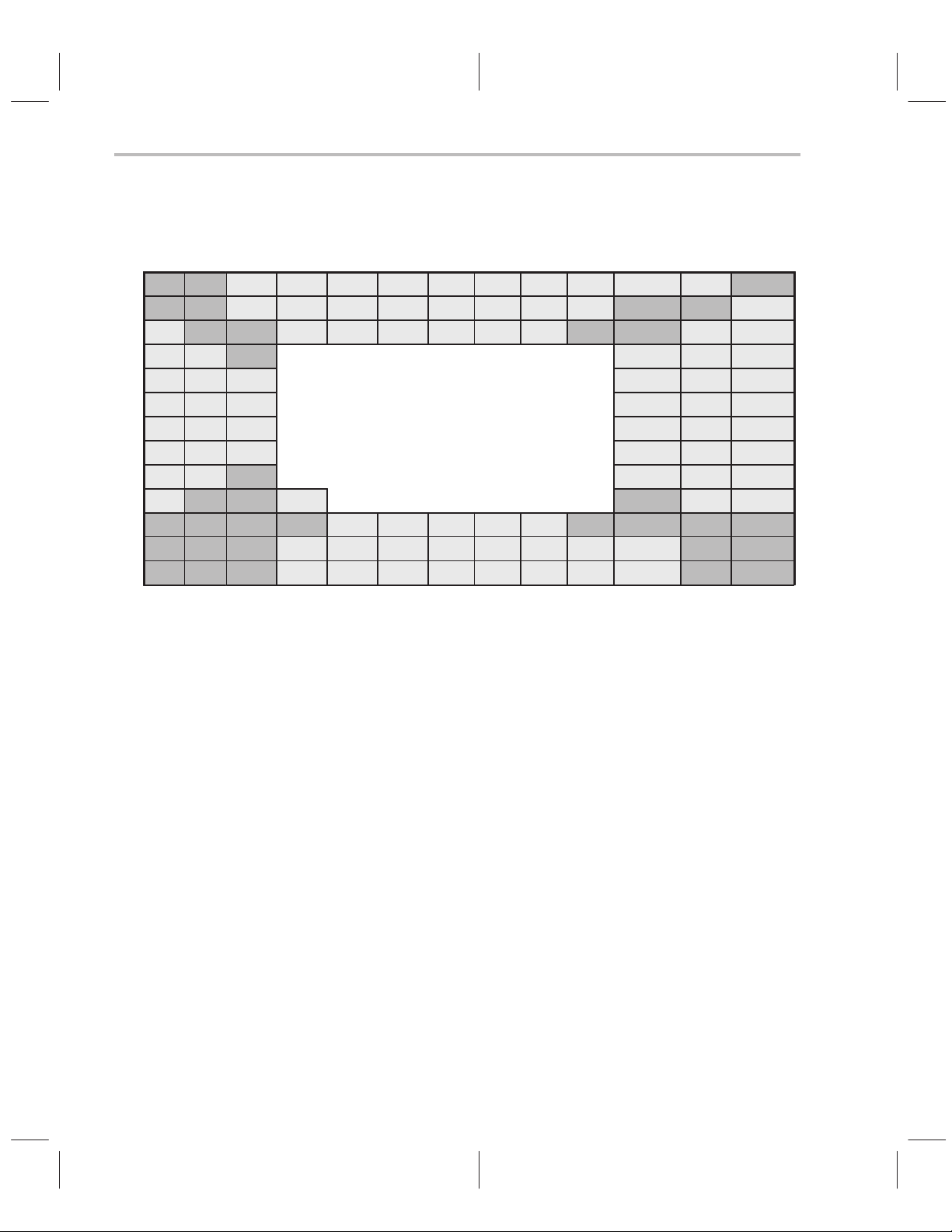

For software development and prototyping, a windowed ceramic 120-pin grid

array packaged P614 is available. The P614’s PGA package is shown in

Figure 1–5 and Table 1–3:

Figure 1–5. 120 Pin Grid Array Package for the Development Device, P614

MSP50P614

N

M

L

K

J

H

G

F

E

D

C

B

A

214365871012 1113 9

N

M

L

K

J

H

G

F

E

D

C

B

A

1

42 3

extra pin

5

(bottom view)(top view)

12 1310 118967

Note: PGA Package

The PGA package is only available in limited quantities for development purposes.

Introduction to the MSP50C614

1-13

Page 30

Terminal Assignments and Signal Descriptions

The pin assignments for the 120-pin PGA package (P614 device only) are outlined in the following table. Refer to Section 1.6 for more information on the

signal functions.

nc nc V

N

nc nc DACMDACPPF

M

PD0nc nc V

L

PD3PD

K

PD5PD4PD

J

V

H

DD

V

G

SS

PC2PC3PC

F

PC5PC

E

PC7nc nc extra nc V

D

nc nc nc nc PB

C

nc nc nc PB

B

nc nc nc PB

A

1

PD7PD

PC1PC

6

†

DD

PF

nc PG

2

6

0

4

nc PE

SS

PF

7

†

V

PB

0

PB

2

DD

5

6

1

3

4

PF2V

PF

3

PF

4

(bottom view) RESET scanin PE

PB5V

PB

6

PB7V

PG15PG12PG

PP

PF1PG14PG11PG

PF0PG

PA

SS

PA0PA

PA

DD

13

PG

9

PA

3

7

PA

2

PA

1

5

4

PLL OSC

PA

V

10

8

nc nc PG

PG

pgmpuls SYNC scanclk

PE

nc nc nc nc

OSC

6

6

2

4

0

OUT

IN

V

DD

PG

5

PG

PG0scanout

PE

PE

SS

nc nc

nc nc

PG

3

PE

5

PE

2

PE

SS

nc nc PG

nc

7

4

1

7

6

3

1

1 2 3 4 5 6 7 8 9 10 11 12 13

†

It is important to provide a separate decoupling capacitor for the VDD, VSS pair which services the DAC. These pins are PGA

numbers N3 and L4, respectively. The relatively high current demands of the digital-to-analog circuitry make this a requirement.

Refer to Section 6.1,

TBD

, for details.

1-14

Page 31

Chapter 2

MSP50C614 Architecture

A detailed description of MSP50C614 architecture is included in this chapter.

After reading this chapter, the reader will have in-depth knowledge of internal

blocks, memory organization, interrupt system, timers, clock control mechanism, and various low power modes.

Topic Page

2.1 Architecture Overview 2–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2 Computation Unit 2–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3 Data Memory Address Unit 2–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4 Program Counter Unit 2–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5 Bit Logic Unit 2–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6 Memory Organization: RAM and ROM 2–15. . . . . . . . . . . . . . . . . . . . . . . .

2.7 Interrupt Logic 2–22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.8 Timer Registers 2–26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.9 Clock Control 2–29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.10 Execution Timing 2–33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.11 Reduced Power Modes 2–34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-1

Page 32

2.1 Architecture Overview

The core processor in the C614 is a medium performance mixed signal processor with enhanced microcontroller features and a limited DSP instruction

set. In addition to its basic multiply/accumulate structure for DSP routines, the

core provides for a very efficient handling of string and bit manipulation. A

unique accumulator-register file provides additional scratch pad memory and

minimizes memory thrashing for many operations. Five different addressing

modes and many short direct references provide enhanced execution and

code efficiency.

The basic elements of the C614 core are shown in Figure 2–1. In addition to

the main computational units, the core’s auxiliary functions include two timers,

an eight-level interrupt processor, a clock generation circuit, a serial scan-port

interface, and a general control register.

2-2

Page 33

Figure 2–1. MSP50C614 Core Processor Block Diagram

Interrupt Inputs

Interrupt Flag Register (IFR)†

Multiplier (MR)† Shift Value (SV)†

17 x 17 Multiplier

Product High (PH)†

MUX

16 bit ALU

32 Accumulators (AC0–AC31)†

Control Register (CTRL)†

Interrupt Processor

Serial Interface Register†

Oscillator Register†

Timer Period (PRD1 and PRD2)†

Timer Register (TIM1 and TIM2)†

AP0–AP3†

Accumulator Pointer

Peripheral

Interface

Serial

Interface

VCO

Frequency

Divider

Instruction

Decoder

+1

Column Exchange

Stack (R7)

Page (R6)

Index (R5)

Loop (R4)

R3

R2

R1

R0

MUX

Arithmetic Unit

MUX

Data Memory

640 x 17 bit

†

Indicates internal programmable registers.

Incrementor

Top Of Stack (TOS)†

Program Counter (PC)†

Protection Register (PR)†

Data Pointer (DP)†

MUX

String Register†

MUX

Repeat Counter†

Status Register (STAT)†

Flag Register†

Test Code

2k x 17 bit

Program Memory

30k x 17 bit

Macro Calls

Vectors

MSP50C614 Architecture

2-3

Page 34

Figure 2–2. Computational Unit Block Diagram (The shaded boxes represent internal

programmable registers.)

16

16

16

16

16

16

5

Internal Databus – 16 bit

Shift Value (SV)

Multiplier Register (MR)

17 bit x 17 bit

Multiplexer

Product High (PH)

Accumulators

AP0

AP1

AP2

AP3

16

16

(Product Low, PL)

16 LSB

16 MSB

16

0

0

16

AB

ALU

16

Read/Write

AC0

AC1

AC2

AC3

AC4

5

AC5

AC6

AC7

AC8

AC9

AC10

AC11

AC12

AC13

AC14

AC15

AC16

AC17

AC18

AC19

AC20

AC21

AC22

AC23

AC24

AC25

AC26

AC27

AC28

AC29

AC30

AC31

16

16

2-4

Page 35

2.2 Computation Unit

The computational unit (CU) is comprised of a (17-bit by 17-bit) Booth’s

algorithm multiplier and a 16-bit arithmetic logic unit (ALU). The block diagram