Page 1

MSP430x1xx Family

User’s Guide

2000 Mixed Signal Products

SLAU049

Page 2

IMPORTANT NOTICE

T exas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue

any product or service without notice, and advise customers to obtain the latest version of relevant information

to verify, before placing orders, that information being relied on is current and complete. All products are sold

subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those

pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent

TI deems necessary to support this warranty . Specific testing of all parameters of each device is not necessarily

performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer’s applications, adequate design and operating

safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent

that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other

intellectual property right of TI covering or relating to any combination, machine, or process in which such

semiconductor products or services might be or are used. TI’s publication of information regarding any third

party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.

Copyright 2000, Texas Instruments Incorporated

Page 3

About This Manual

How to Use This Manual

Preface

Read This First

The MSP430x1xx User’s Guide is intended to assist the development of

MSP430x1xx family products by assembling together and presenting

hardware and software information in a manner that is easy for engineers and

programmers to use.

This manual discusses modules and peripherals of the MSP430x1xx family of

devices. Each discussion presents the module or peripheral in a general

sense. Not all features and functions of all modules or peripherals are present

on all devices. In addition, modules or peripherals may differ in their exact

implementation between device families, or may not be fully implemented on

an individual device or device family. Therefore, a user must always consult

the data sheet of any device of interest to determine what peripherals and

modules are implemented, and exactly how they are implemented on that

particular device.

How to Use This Manual

This document contains the following chapters:

Chapter 1 – Introduction

Chapter 2 – Architectural Overview

Chapter 3 – System Resets, Interrupts, and Operating Modes

Chapter 4 – Memory

Chapter 5 – 16-Bit CPU

Chapter 6 – Hardware Multiplier

Chapter 7 – Basic Clock Module

Chapter 8 – Digital I/O Configuration

Chapter 9 – Watchdog Timer

Chapter 10 – Timer_A

Chapter 11 – Timer_B

Chapter 12 – USART Peripheral Interface, UART Mode

Chapter 13 – USART Peripheral Interface, SPI Mode

Read This First

iii

Page 4

Related Documentation From Texas Instruments

Chapter 14 – Comparator_A

Chapter 15 – ADC12

Appendix A – Peripheral File Map

Appendix B – Instruction Set Description

Appendix C – Flash Memory

Notational Conventions

This document uses the following conventions.

-

Program listings, program examples, and interactive displays are shown

in a special typeface similar to a typewriter’s.

Here is a sample program listing:

0011 0005 0001 .field 1, 2

0012 0005 0003 .field 3, 4

0013 0005 0006 .field 6, 3

0014 0006 .even

Related Documentation From Texas Instruments

FCC Warning

For related documentation see the web site http://www.ti.com/sc/msp430.

This equipment is intended for use in a laboratory test environment only . It generates, uses, and can radiate radio frequency energy and has not been tested

for compliance with the limits of computing devices pursuant to subpart J of

part 15 of FCC rules, which are designed to provide reasonable protection

against radio frequency interference. Operation of this equipment in other environments may cause interference with radio communications, in which case

the user at his own expense will be required to take whatever measures may

be required to correct this interference.

iv

Page 5

Running Title—Attribute Reference

Contents

1 Introduction 1-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1 Features and Capabilities 1-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2 1 1x Devices 1-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3 11x1 Devices 1-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4 13x Devices 1-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.5 14x Devices 1-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2 Architectural Overview 2-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1 Introduction 2-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2 Central Processing Unit 2-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3 Program Memory 2-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4 Data Memory 2-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5 Operation Control 2-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6 Peripherals 2-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.7 Oscillator and Clock Generator 2-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3 System Resets, Interrupts, and Operating Modes 3-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1 System Reset and Initialization 3-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.1 Introduction 3-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.2 Device Initialization After System Reset 3-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2 Global Interrupt Structure 3-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3 MSP430 Interrupt-Priority Scheme 3-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.1 Operation of Global Interrupt—Reset/NMI 3-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.2 Operation of Global Interrupt—Oscillator Fault Control 3-9. . . . . . . . . . . . . . . . . . .

3.4 Interrupt Processing 3-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4.1 Interrupt Control Bits in Special-Function Registers (SFRs) 3-11. . . . . . . . . . . . . .

3.4.2 Interrupt Vector Addresses 3-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5 Operating Modes 3-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.1 Low-Power Mode 0 and 1 (LPM0 and LPM1) 3-20. . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.2 Low-Power Modes 2 and 3 (LPM2 and LPM3) 3-21. . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.3 Low-Power Mode 4 (LPM4) 3-21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6 Basic Hints for Low-Power Applications 3-22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4 Memory 4-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1 Introduction 4-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2 Data in the Memory 4-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3 Internal ROM Organization 4-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.1 Processing of ROM Tables 4-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.2 Computed Branches and Calls 4-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Chapter Title—Attribute Reference

v

Page 6

Contents

4.4 RAM and Peripheral Organization 4-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.1 Random Access Memory 4-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.2 Peripheral Modules—Address Allocation 4-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.3 Peripheral Modules—Special Function Registers (SFRs) 4-10. . . . . . . . . . . . . . . .

5 16-Bit CPU 5-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1 CPU Registers 5-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.1 The Program Counter (PC) 5-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.2 The System Stack Pointer (SP) 5-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.3 The Status Register (SR) 5-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.4 The Constant Generator Registers CG1 and CG2 5-5. . . . . . . . . . . . . . . . . . . . . . .

5.2 Addressing Modes 5-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.1 Register Mode 5-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.2 Indexed Mode 5-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.3 Symbolic Mode 5-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.4 Absolute Mode 5-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.5 Indirect Mode 5-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.6 Indirect Autoincrement Mode 5-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.7 Immediate Mode 5-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.8 Clock Cycles, Length of Instruction 5-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3 Instruction Set Overview 5-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3.1 Double-Operand Instructions 5-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3.2 Single-Operand Instructions 5-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3.3 Conditional Jumps 5-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3.4 Short Form of Emulated Instructions 5-21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3.5 Miscellaneous 5-22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.4 Instruction Map 5-23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6 Hardware Multiplier 6-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.1 Hardware Multiplier Module Support 6-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2 Hardware Multiplier Operation 6-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2.1 Multiply Unsigned, 16×16 bit, 16×8 bit, 8× 16 bit, 8×8 bit 6-5. . . . . . . . . . . . . . . .

6.2.2 Multiply Signed, 16×16 bit, 16×8 bit, 8×16 bit, 8×8 bit 6-6. . . . . . . . . . . . . . . . . . . .

6.2.3 Multiply Unsigned and Accumulate, 16x16bit, 16x8bit, 8x16bit, 8x8bit 6-7. . . . . .

6.2.4 Multiply Signed and Accumulate, 16x16bit, 16x8bit, 8x16bit, 8x8bit 6-8. . . . . . . .

6.3 Hardware Multiplier Registers 6-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.4 Hardware Multiplier Special Function Bits 6-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.5 Hardware Multiplier Software Restrictions 6-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.5.1 Hardware Multiplier Software Restrictions—Address Mode 6-10. . . . . . . . . . . . . . .

6.5.2 Hardware Multiplier Software Restrictions—Interrupt Routines 6-11. . . . . . . . . . . .

6.5.3 Hardware Multiplier Software Restrictions—MACS 6-12. . . . . . . . . . . . . . . . . . . . . .

7 Basic Clock Module 7-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.1 Basic Clock Module 7-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2 LFXT1 and XT2 Oscillators 7-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2.1 LFXT1 Oscillator 7-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2.2 XT2 Oscillator 7-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2.3 Oscillator Fault Detection 7-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2.4 Select DCO Oscillator for MCLK on XT Oscillator Fault 7-8. . . . . . . . . . . . . . . . . . .

7.3 Digitally-Controlled Oscillator (DCO) 7-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.3.1 Operation of the DCO Modulator 7-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

vi

Page 7

Contents

7.4 Basic Clock Module Operating Modes 7-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.4.1 Starting From Power Up Clear (PUC) 7-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.4.2 Adjusting the Basic Clock 7-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.4.3 Basic Clock Features for Low-Power Applications 7-15. . . . . . . . . . . . . . . . . . . . . .

7.4.4 Selecting a Crystal Clock for MCLK 7-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.4.5 Synchronization of Clock Signals 7-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.5 Basic Clock Module Control Registers 7-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.5.1 Digitally-Controlled Oscillator (DCO) Clock-Frequency Control 7-18. . . . . . . . . . .

7.5.2 Oscillator and Clock Control Register 7-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.5.3 Special-Function Register Bits 7-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8 Digital I/O Configuration 8-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.1 Introduction 8-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.2 Ports P1, P2 8-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.2.1 Port P1, Port P2 Control Registers 8-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.2.2 Port P1, Port P2 Schematic 8-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.2.3 Port P1, P2 Interrupt Control Functions 8-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.3 Ports P3, P4, P5, P6 8-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.3.1 Port P3–P6 Control Registers 8-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.3.2 Port P3–P6 Schematic 8-1 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9 Watchdog Timer 9-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.1 The Watchdog Timer 9-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.1.1 Watchdog Timer Register 9-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.1.2 Watchdog Timer Interrupt Control Functions 9-5. . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.1.3 Watchdog Timer Operation 9-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10 Timer_A 10-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.1 Introduction 10-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.2 Timer_A Operation 10-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.2.1 Timer Mode Control 10-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.2.2 Clock Source Select and Divider 10-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.2.3 Starting the Timer 10-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.3 Timer Modes 10-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.3.1 Timer—Stop Mode 10-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.3.2 Timer—Up Mode 10-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.3.3 Timer—Continuous Mode 10-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.3.4 Timer—Up/Down Mode 10-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.4 Capture/Compare Blocks 10-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.4.1 Capture/Compare Block—Capture Mode 10-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.4.2 Capture/Compare Block—Compare Mode 10-18. . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.5 The Output Unit 10-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.5.1 Output Unit—Output Modes 10-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.5.2 Output Control Block 10-21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.5.3 Output Examples 10-22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.6 Timer_A Registers 10-24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.6.1 Timer_A Control Register TACTL 10-25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.6.2 Timer_A Register TAR 10-26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.6.3 Capture/Compare Control Register CCTLx 10-27. . . . . . . . . . . . . . . . . . . . . . . . . . .

10.6.4 Timer_A Interrupt Vector Register 10-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.7 Timer_A UART 10-33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Contents

vii

Page 8

Contents

11 Timer_B 11-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1 1.1 Introduction 11-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.1.1 Similarities and Differences From Timer_A 11-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.2 Timer_B Operation 11-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.2.1 Timer Length 11-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.2.2 Timer Mode Control 11-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.2.3 Clock Source Select and Divider 11-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.2.4 Starting the Timer 11-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.3 Timer Modes 11-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.3.1 Timer—Stop Mode 11-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.3.2 Timer—Up Mode 11-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.3.3 Timer—Continuous Mode 11-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.3.4 Timer—Up/Down Mode 11-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1 1.4 Capture/Compare Blocks 11-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.4.1 Capture/Compare Block—Capture Mode 11-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.4.2 Capture/Compare Block—Compare Mode 11-19. . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.5 The Output Unit 11-23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.5.2 Output Control Block 11-25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1 1.5.3 Output Examples 11-26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.6 Timer_B Registers 11-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.6.1 Timer_B Control Register TBCTL 11-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.6.2 Timer_B Register TBR 11-32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.6.3 Capture/Compare Control Register CCTLx 11-32. . . . . . . . . . . . . . . . . . . . . . . . . . .

11.6.4 Timer_B Interrupt Vector Register 11-35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12 USART Peripheral Interface, UART Mode 12-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.1 USART Peripheral Interface 12-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.2 USART Peripheral Interface, UART Mode 12-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.2.1 UART Serial Asynchronous Communication Features 12-3. . . . . . . . . . . . . . . . . . .

12.3 Asynchronous Operation 12-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.3.1 Asynchronous Frame Format 12-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.3.2 Baud Rate Generation in Asynchronous Communication Format 12-5. . . . . . . . . .

12.3.3 Asynchronous Communication Formats 12-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.3.4 Idle-Line Multiprocessor Format 12-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.3.5 Address-Bit Multiprocessor Format 12-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.4 Interrupt and Enable Functions 12-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.4.1 USART Receive Enable Bit 12-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.4.2 USART Transmit Enable Bit 12-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.4.3 USART Receive Interrupt Operation 12-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.4.4 USART Transmit Interrupt Operation 12-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.5 Control and Status Registers 12-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.5.1 USART Control Register UCTL 12-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.5.2 Transmit Control Register UTCTL 12-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.5.3 Receiver Control Register URCTL 12-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.5.4 Baud Rate Select and Modulation Control Registers 12-20. . . . . . . . . . . . . . . . . . .

12.5.5 Receive-Data Buffer URXBUF 12-21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.5.6 Transmit Data Buffer UTXBUF 12-21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.6 Utilizing Features of Low-Power Modes 12-22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.6.1 Receive-Start Operation From UART Frame 12-22. . . . . . . . . . . . . . . . . . . . . . . . . .

12.6.2 Maximum Utilization of Clock Frequency vs Baud Rate UART Mode 12-24. . . . .

12.6.3 Support of Multiprocessor Modes for Reduced Use of

MSP430 Resources 12-25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

viii

Page 9

Contents

12.7 Baud Rate Considerations 12-25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.7.1 Bit Timing in Transmit Operation 12-25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.7.2 Typical Baud Rates and Errors 12-27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.7.3 Synchronization Error 12-28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13 USART Peripheral Interface, SPI Mode 13-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.1 USART Peripheral Interface 13-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.2 USART Peripheral Interface, SPI Mode 13-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.2.1 SPI Mode Features 13-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.3 Synchronous Operation 13-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.3.1 Master SPI Mode 13-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.3.2 Slave SPI Mode 13-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.4 Interrupt and Control Functions 13-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.4.1 USART Receive/T ransmit Enable Bit, Receive Operation 13-9. . . . . . . . . . . . . . . .

13.4.2 USART Receive/T ransmit Enable Bit, Transmit Operation 13-11. . . . . . . . . . . . . . .

13.4.3 USART Receive-Interrupt Operation 13-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.4.4 Transmit-Interrupt Operation 13-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.5 Control and Status Registers 13-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.5.1 USART Control Register 13-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.5.2 Transmit Control Register UTCTL 13-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.5.3 Receive Control Register URCTL 13-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.5.4 Baud-Rate Select and Modulation Control Registers 13-19. . . . . . . . . . . . . . . . . . .

13.5.5 Receive Data Buffer URXBUF 13-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.5.6 Transmit Data Buffer UTXBUF 13-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14 Comparator_A 14-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14.1 Comparator_A Overview 14-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14.2 Comparator_A Description 14-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14.2.1 Input Analog Switches 14-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14.2.2 Input Multiplexer 14-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14.2.3 The Comparator 14-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14.2.4 The Output Filter 14-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14.2.5 The Voltage Reference Generator 14-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14.2.6 Comparator_A Interrupt Circuitry 14-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14.3 Comparator_A Control Registers 14-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14.3.1 Comparator_A, Control Register CACTL1 14-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14.3.2 Comparator_A, Control Register CACTL2 14-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14.3.3 Comparator_A, Port Disable Register CAPD 14-7. . . . . . . . . . . . . . . . . . . . . . . . . . .

14.4 Comparator_A in Applications 14-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14.4.1 Analog Signals at Digital Inputs 14-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14.4.2 Comparator_A Used to Measure Resistive Elements 14-11. . . . . . . . . . . . . . . . . . .

14.4.3 Measuring Two Independent Resistive Element Systems 14-13. . . . . . . . . . . . . . .

14.4.4 Comparator_A Used to Detect a Current or Voltage Level 14-16. . . . . . . . . . . . . . .

14.4.5 Comparator_A Used to Measure a Current or Voltage Level 14-17. . . . . . . . . . . . .

14.4.6 Measuring the Offset Voltage of Comparator_A 14-20. . . . . . . . . . . . . . . . . . . . . . . .

14.4.7 Compensating for the Offset Voltage of Comparator_A 14-22. . . . . . . . . . . . . . . . .

14.4.8 Adding Hysteresis to Comparator_A 14-22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15 ADC12 15-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.1 Introduction 15-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.2 ADC12 Description and Operation 15-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Contents

ix

Page 10

Contents

15.2.1 ADC Core 15-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.2.2 Reference 15-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.3 Analog Inputs and Multiplexer 15-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.3.1 Analog Multiplexer 15-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.3.2 Input Signal Considerations 15-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.3.3 Using the Temperature Diode 15-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.4 Conversion Memory 15-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.5 Conversion Modes 15-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.5.1 Single-Channel, Single-Conversion Mode 15-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.5.2 Sequence-of-Channels Mode 15-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.5.3 Repeat-Single-Channel Mode 15-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.5.4 Repeat-Sequence-of-Channels Mode 15-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.5.5 Switching Between Conversion Modes 15-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.5.6 Power Down 15-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.6 Conversion Clock and Conversion Speed 15-21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.7 Sampling 15-22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.7.1 Sampling Operation 15-22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.7.2 Sample Signal Input Selection 15-23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.7.3 Sampling Modes 15-24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.7.4 Using the MSC Bit 15-27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.7.5 Sample Timing Considerations 15-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.8 ADC12 Control Registers 15-30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.8.1 Control Registers ADC12CTL0 and ADC12CTL1 15-31. . . . . . . . . . . . . . . . . . . . . .

15.8.2 Conversion-Memory Registers ADC12MEMx 15-35. . . . . . . . . . . . . . . . . . . . . . . . .

15.8.3 Control Registers ADC12MCTLx 15-35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.8.4 ADC12 Interrupt Flags ADC12IFG.x and Interrupt-Enable Registers

ADC12IEN.x 15-37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.8.5 ADC12 Interrupt Vector Register ADC12IV 15-37. . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.9 A/D Grounding and Noise Considerations 15-41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A Peripheral File Map A-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.1 Overview A-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.2 Special Function Register of MSP430x1xx Family, Byte Access A-3. . . . . . . . . . . . . . . . . . .

A.3 Digital I/O, Byte Access A-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.4 Basic Clock Registers, Byte Access A-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.5 EPROM Control Register Byte Access A-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.6 Comparator_A Registers, Byte Access A-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.7 USART0, USART1, UAR T Mode (Sync=0), Byte Access A-6. . . . . . . . . . . . . . . . . . . . . . . . .

A.8 USART0, USART1, SPI Mode (Sync=1), Byte Access A-7. . . . . . . . . . . . . . . . . . . . . . . . . . .

A.9 ADC12 Registers, Byte and Word Access A-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.10 Watchdog/Timer, Word Access A-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.11 Flash Control Registers, Word Access A-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.12 Hardware Multiplier, Word Access A-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.13 Timer_A Registers, Word Access A-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.14 Timer_B Registers, Word Access A-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B Instruction Set Description B-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.1 Instruction Set Overview B-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.1.1 Instruction Formats B-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.1.2 Conditional and Unconditional Jumps (Core Instructions) B-5. . . . . . . . . . . . . . . . .

B.1.3 Emulated Instructions B-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

x

Page 11

Contents

B.2 Instruction Set Description B-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C Flash Memory C-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

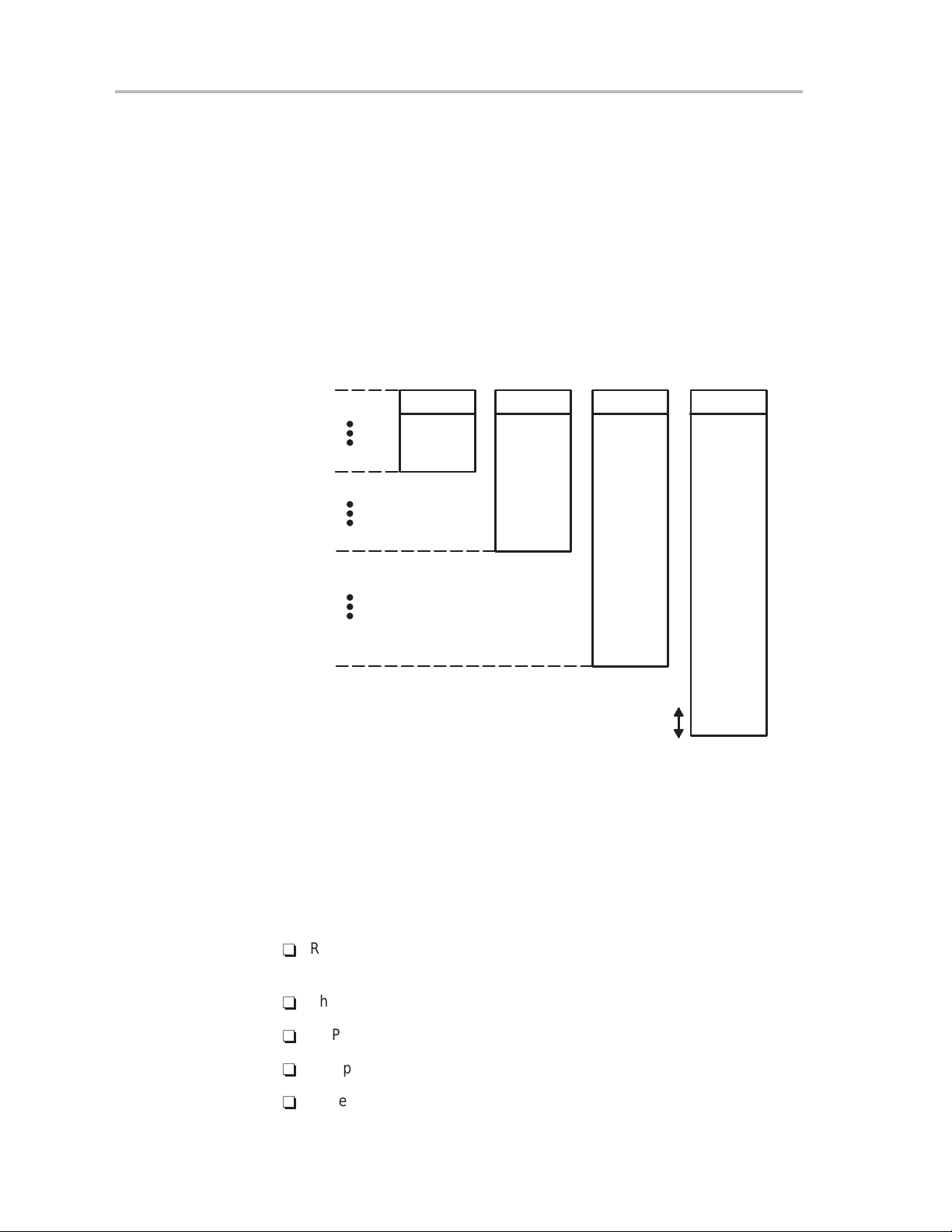

C.1 Flash Memory Organization C-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C.1.1 Why Is a Flash Memory Module Divided Into Several Segments? C-5. . . . . . . . . .

C.2 Flash Memory Data Structure and Operation C-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C.2.1 Flash Memory Basic Functions C-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C.2.2 Flash Memory Block Diagram C-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C.2.3 Flash Memory, Basic Operation C-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C.2.4 Flash Memory Status During Code Execution C-8. . . . . . . . . . . . . . . . . . . . . . . . . . .

C.2.5 Flash Memory Status During Erase C-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C.2.6 Flash Memory Status During Write (Programming) C-10. . . . . . . . . . . . . . . . . . . . . .

C.3 Flash Memory Control Registers C-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C.3.1 Flash Memory Control Register FCTL1 C-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C.3.2 Flash Memory Control Register FCTL2 C-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C.3.3 Flash Memory Control Register FCTL3 C-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C.4 Flash Memory, Interrupt and Security Key Violation C-18. . . . . . . . . . . . . . . . . . . . . . . . . . . .

C.4.1 Example of an NMI Interrupt Handler C-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C.4.2 Protecting One-Flash Memory-Module Systems From Corruption C-20. . . . . . . . .

C.5 Flash Memory Access via JTAG and Software C-22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C.5.1 Flash Memory Protection C-22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C.5.2 Program Flash Memory Module via Serial Data Link Using JTAG Feature C-22. .

C.5.3 Programming a Flash Memory Module via Controller Software C-22. . . . . . . . . . .

Contents

xi

Page 12

Running Title—Attribute Reference

Figures

2–1 MSP430 System Configuration 2-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–2 Bus Connection of Modules/Peripherals 2-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–1 Power-On Reset and Power-Up Clear Schematic 3-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–2 Power-On Reset Timing on Fast VCC Rise Time 3-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–3 Power-On Reset Timing on Slow VCC Rise Time 3-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–4 Interrupt Priority Scheme 3-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–5 Block Diagram of NMI Interrupt Sources 3-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–6 RST/NMI Mode Selection 3-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–7 Interrupt Processing 3-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–8 Return From Interrupt 3-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–9 Status Register (SR) 3-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–10 MSP430x1xx Operating Modes for Basic Clock System 3-19. . . . . . . . . . . . . . . . . . . . . . . . . . .

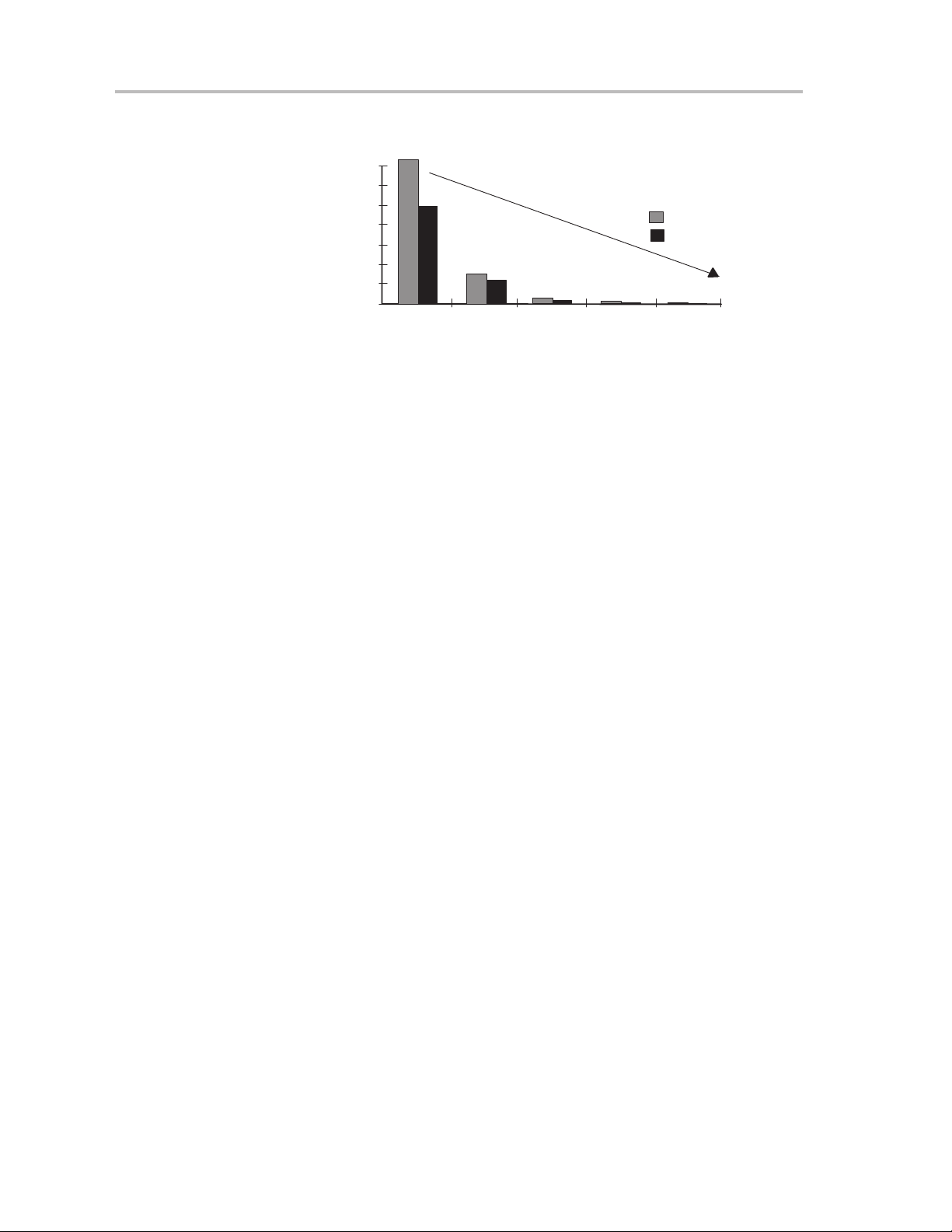

3–11 Typical Current Consumption of 13x and 14x Devices vs Operating Modes 3-20. . . . . . . . . .

4–1 Memory Map of Basic Address Space 4-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–2 Memory Data Bus 4-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–3 Bits, Bytes, and Words in a Byte-Organized Memory 4-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–4 ROM Organization 4-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–5 Byte and Word Operation 4-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–6 Register-Byte/Byte-Register Operations 4-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–7 Example of RAM/Peripheral Organization 4-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–1 Program Counter 5-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–2 System Stack Pointer 5-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–3 Stack Usage 5-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–4 PUSH SP and POP SP 5-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–5 Status Register Bits 5-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–6 Operand Fetch Operation 5-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–7 Double Operand Instruction Format 5-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–8 Single Operand Instruction Format 5-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–9 Conditional-Jump Instruction Format 5-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–10 Core Instruction Map 5-23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

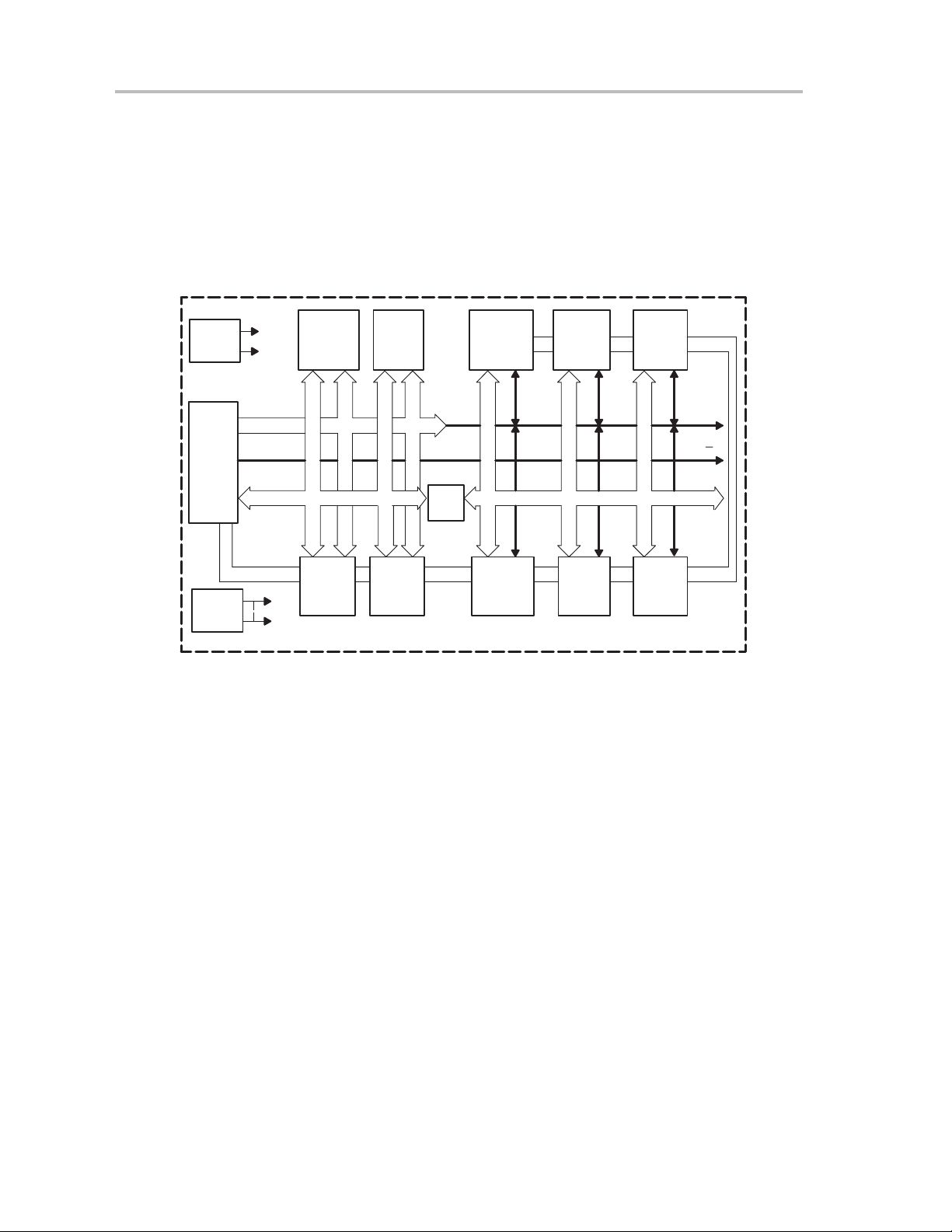

6–1 Connection of the Hardware Multiplier Module to the Bus System 6-2. . . . . . . . . . . . . . . . . . .

6–2 Block Diagram of the MSP430 16y16-Bit Hardware Multiplier 6-3. . . . . . . . . . . . . . . . . . . . . . .

6–3 Registers of the Hardware Multiplier 6-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–1 Basic Clock Schematic 7-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–2 Principle of LFXT1 Oscillator 7-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–3 Off Signals for the LFXT1 Oscillator 7-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–4 Off Signals for Oscillator XT2 7-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–5 Oscillator-Fault-Interrupt 7-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–6 Oscillator-Fault Signal 7-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xii

Page 13

Figures

7–7 Oscillator Fault in Oscillator Error Condition 7-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–8 Oscillator Fault in Oscillator Error Condition at Start-Up 7-8. . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–9 NMI/OSCFault Interrupt Handler 7-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–10 DCO Schematic 7-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–11 Principle Period Steps of the DCO 7-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–12 On/Off Control of DCO 7-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–13 Operation of the DCO Modulator 7-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–14 Select Crystal Oscillator for MCLK, Example Uses LFXT1 for MCLK 7-15. . . . . . . . . . . . . . . .

7–15 Timing to Select Crystal Oscillator for MCLK, Example Uses LFXT1 in HF

Mode for MCLK 7-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–16 Select Another Clock Source Signal, Example Switches From DCOCLK to

LFXT1CLK for Clock MCLK 7-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8–1 Port P1, Port P2 Configuration 8-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8–2 Schematic of One Bit in Port P1, P2 8-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

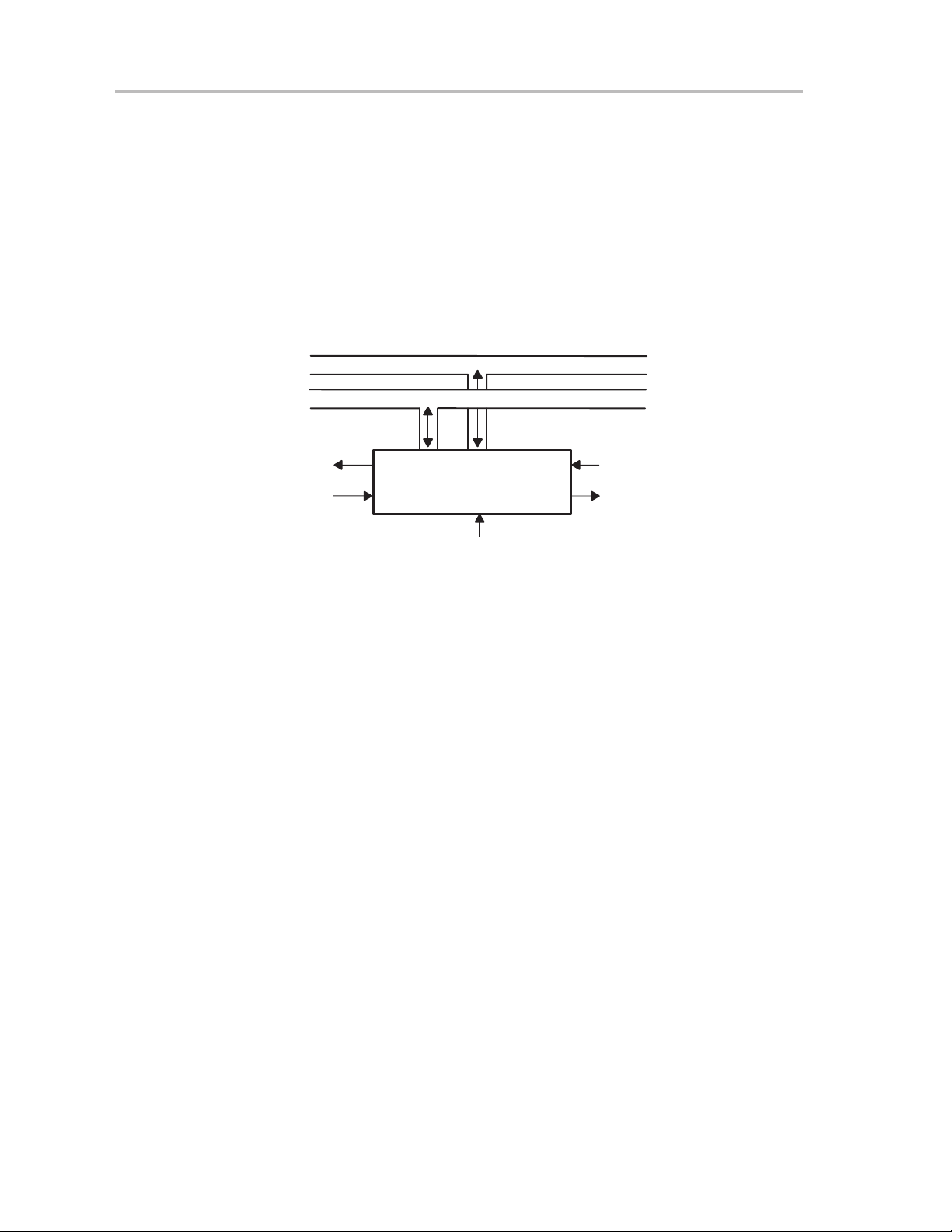

8–3 Ports P3–P6 Configuration 8-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8–4 Schematic of Bits PN-x 8-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–1 Schematic of Watchdog Timer 9-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–2 Watchdog Timer Control Register 9-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–3 Reading WDTCTL 9-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–4 Writing to WDTCTL 9-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–1 Timer_A Block Diagram 10-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–2 Mode Control 10-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–3 Schematic of 16-Bit Timer 10-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–4 Schematic of Clock Source Select and Input Divider 10-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–5 Timer Up Mode 10-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–6 Up Mode Flag Setting 10-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–7 New Period > Old Period 10-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–8 New Period < Old Period 10-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–9 Timer Continuous Mode 10-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–10 Continuous Mode Flag Setting 10-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–11 Output Unit in Continuous Mode for Time Intervals 10-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–12 Timer Up/Down Mode 10-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–13 Output Unit in Up/Down Mode (II) 10-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–14 Timer Up/Down Direction Control 10-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–15 Up/Down Mode Flag Setting 10-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–16 Altering CCR0—Timer in Up/Down Mode 10-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–17 Capture/Compare Blocks 10-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–18 Capture Logic Input Signal 10-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–19 Capture Signal 10-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–20 Capture Cycle 10-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–21 Software Capture Example 10-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–22 Output Unit 10-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–23 Output Control Block 10-21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–24 Output Examples—Timer in Up Mode 10-23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–25 Output Examples—Timer in Continuous Mode 10-23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–26 Output Examples—Timer in Up/Down Mode (I) 10-24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–27 Timer_A Control Register TACTL 10-25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–28 TAR Register 10-26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–29 Capture/Compare Control Register CCTLx 10-27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–30 Capture/Compare Interrupt Flag 10-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–31 Schematic of Capture/Compare Interrupt Vector Word 10-30. . . . . . . . . . . . . . . . . . . . . . . . . . .

Figures

xiii

Page 14

Figures

10–32 Vector Word Register 10-30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–33 UART Implementation 10-34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–34 Timer_A UART Timing 10-35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–1 Timer_B Block Diagram 11-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–2 Mode Control 11-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–3 Schematic of 16-Bit Timer 11-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–4 Schematic of Clock Source Select and Input Divider 11-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–5 Timer Up Mode 11-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–6 Up Mode Flag Setting 11-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–7 New Period > Old Period 11-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–8 New Period < Old Period 1 1-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–9 Timer Continuous Mode 11-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–10 Continuous Mode Flag Setting 11-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–11 Output Unit in Continuous Mode for Time Intervals 11-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–12 Timer Up/Down Mode 11-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–13 Output Unit in Up/Down Mode (II) 11-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–14 Timer Up/Down Direction Control 11-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–15 Up/Down Mode Flag Setting 11-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–16 Altering TBCL0—Timer in Up/Down Mode 11-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1 1–17 Capture/Compare Blocks 11-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–18 Capture Logic Input Signal 11-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–19 Capture Signal 11-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–20 Capture Cycle 11-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–21 Software Capture Example 11-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–22 Output Unit 11-23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–23 Output Control Block 11-25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–24 Output Examples—Timer in Up Mode 11-27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–25 Output Examples—Timer in Continuous Mode 11-27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–26 Output Examples—Timer in Up/Down Mode (I) 11-28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–27 Timer_B Control Register TBCTL 11-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–28 TBR Register 11-32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–29 Capture/Compare Control Register CCTLx 11-32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–30 Capture/Compare Interrupt Flag 11-35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–31 Schematic of Capture/Compare Interrupt Vector Word 11-36. . . . . . . . . . . . . . . . . . . . . . . . . . .

11–32 Vector Word Register 11-36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12–1 Block Diagram of USART 12-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12–2 Block Diagram of USART—UART Mode 12-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12–3 Asynchronous Frame Format 12-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12–4 Asynchronous Bit Format Example for n or n + 1 Clock Periods 12-4. . . . . . . . . . . . . . . . . . . .

12–5 Typical Baud-Rate Generation Other Than MSP430 12-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12–6 MSP430 Baud Rate Generation Example for n or n + 1 Clock Periods 12-6. . . . . . . . . . . . . .

12–7 Idle-Line Multiprocessor Format 12-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12–8 USART Receiver Idle Detect 12-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12–9 Double-Buffered WUT and TX Shift Register 12-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12–10 USART Transmitter Idle Generation 12-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12–11 Address-Bit Multiprocessor Format 12-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12–12 State Diagram of Receiver Enable 12-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12–13 State Diagram of Transmitter Enable 12-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12–14 Receive Interrupt Operation 12-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12–15 Transmit Interrupt Operation 12-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xiv

Page 15

Figures

12–16 USART Control Register UCTL 12-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12–17 Transmitter Control Register UTCTL 12-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12–18 Receiver-Control Register URCTL 12-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12–19 USART Baud Rate Select Register 12-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12–20 USART Modulation Control Register 12-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12–21 USART0 Receive Data Buffer URXBUF 12-21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12–22 Transmit Data Buffer UTXBUF 12-21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12–23 Receive-Start Conditions 12-22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12–24 Receive-Start Timing Using URXS Flag, Start Bit Accepted 12-23. . . . . . . . . . . . . . . . . . . . . . .

12–25 Receive-Start Timing Using URXS Flag, Start Bit Not Accepted 12-23. . . . . . . . . . . . . . . . . . .

12–26 Receive-Start Timing Using URXS Flag, Glitch Suppression 12-23. . . . . . . . . . . . . . . . . . . . . .

12–27 MSP430 Transmit Bit Timing 12-26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12–28 MSP430 Transmit Bit Timing Errors 12-26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12–29 Synchronization Error 12-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13–1 Block Diagram of USART 13-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13–2 Block Diagram of USART—SPI Mode 13-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13–3 MSP430 USART as Master, External Device With SPI as Slave 13-5. . . . . . . . . . . . . . . . . . . .

13–4 Serial Synchronous Data Transfer 13-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13–5 Data Transfer Cycle 13-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13–6 MSP430 USART as Slave in Three-Pin or Four-Pin Configuration 13-7. . . . . . . . . . . . . . . . . .

13–7 State Diagram of Receiver Enable Operation—MSP430 as Master 13-10. . . . . . . . . . . . . . . .

13–8 State Diagram of Receive/Transmit Enable—MSP430 as Slave, Three-Pin Mode 13-10. . . .

13–9 State Diagram of Receive Enable—MSP430 as Slave, Four-Pin Mode 13-11. . . . . . . . . . . . .

13–10 State Diagram of Transmit Enable—MSP430 as Master 13-11. . . . . . . . . . . . . . . . . . . . . . . . . .

13–11 State Diagram of Transmit Enable—MSP430 as Slave 13-12. . . . . . . . . . . . . . . . . . . . . . . . . . .

13–12 Receive Interrupt Operation 13-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13–13 Receive Interrupt State Diagram 13-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13–14 Transmit-Interrupt Operation 13-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13–15 USART Control Register 13-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13–16 Transmit Control Register UTCTL 13-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13–17 USART Clock Phase and Polarity 13-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13–18 Receive Control Register URCTL 13-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13–19 USART Baud-Rate Select Register 13-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13–20 USART Modulation Control Register 13-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13–21 Receive Data Buffer URXBUF 13-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13–22 Transmit Data Buffer UTXBUF 13-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14–1 Schematic of Comparator_A 14-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14–2 RC-Filter Response at the Output of the Comparator 14-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14–3 Comparator_A Interrupt System 14-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14–4 Transfer Characteristic and Power Dissipation in a CMOS Inverter/Buffer 14-9. . . . . . . . . . . .

14–5 Transfer Characteristic and Power Dissipation in a CMOS Gate 14-9. . . . . . . . . . . . . . . . . . . .

14–6 Application Example With One Active(Driving R3) and Three Passive Pins

With Applied Analog Signals 14-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14–7 Temperature Measurement Systems 14-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14–8 Timing for Temperature Measurement Systems 14-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14–9 Two Independent Temperature Measurement Systems 14-13. . . . . . . . . . . . . . . . . . . . . . . . . . .

14–10 Temperature Measurement Via Temperature Sensor R1(meas) 14-14. . . . . . . . . . . . . . . . . . .

14–11 Temperature Measurement Via Temperature Sensor R2(meas) 14-15. . . . . . . . . . . . . . . . . . .

14–12 Detect a Voltage Level Using an External Reference Level 14-16. . . . . . . . . . . . . . . . . . . . . . .

14–13 Detect a Current Level Using an Internal Reference Level 14-17. . . . . . . . . . . . . . . . . . . . . . . .

14–14 Measuring a Current Source 14-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figures

xv

Page 16

Figures

14–15 Timing for Measuring a Current Source 14-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14–16 A/D Converter for Voltage Sources 14-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14–17 A/D Converter for Voltage Sources, Conversion Timing 14-19. . . . . . . . . . . . . . . . . . . . . . . . . .

14–18 Measuring the Offset Voltage of the Comparator, CAEX = 0 14-20. . . . . . . . . . . . . . . . . . . . . .

14–19 Offset Voltage of the Comparator, CAEX = 0 14-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14–20 Measuring the Offset Voltage of the Comparator, CAEX = 1 14-21. . . . . . . . . . . . . . . . . . . . . .

14–21 Offset Voltage of the Comparator, CAEX = 1 14-21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14–22 Use CAOUT at an External Pin to Add Hysteresis to the Reference Level 14-23. . . . . . . . . .

15–1 ADC12 Schematic 15-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15–2 ADC Core, Input Multiplexer, and Sample-and-Hold 15-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15–3 Analog Multiplexer Channel 15-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15–4 Stopping Conversion With ENC Bit 15-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15–5 Single-Channel, Single-Conversion Mode 15-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15–6 Example Conversion-Memory Setup 15-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15–7 ENC Does Not Effect Active Sequence 15-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15–8 Sequence-of-Channels Mode 15-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15–9 Sequence-of-Channels Mode Flow 15-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15–10 Sequence-of-Channels Mode Example 15-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15–11 Repeat-Single-Channel Mode 15-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15–12 Repeat-Sequence-of-Channels Mode 15-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15–13 The Conversion Clock ADC12CLK 15-21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15–14 The Sample-and-Hold Function 15-22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15–15 Sample and Conversion, Basic Signal Timing 15-23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15–16 Synchronized Sample and Conversion Signal With Enable Conversion 15-24. . . . . . . . . . . . .

15–17 Conversion Timing, Pulse-Sample Mode 15-25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15–18 Pulse-Sample Mode Example Configuration 15-25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15–19 Pulse-Sample Mode Example Timing 15-26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15–20 Conversion Timing for Extended-Sample Mode 15-26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15–21 Extended-Sample Mode Example Configuration 15-27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15–22 Extended-Sample Mode Example Timing 15-27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15–23 Use of MSC Bit With Nonrepeated Modes 15-28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15–24 Use of MSC Bit With Repeated Modes 15-28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15–25 Equivalent Circuit 15-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15–26 A/D Grounding and Noise Considerations 15-41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B–1 Double-Operand Instructions B-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B–2 Single-Operand Instructions B-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B–3 Conditional and Unconditional Jump Instructions B-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B–4 Decrement Overlap B-26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B–5 Main Program Interrupt B-46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B–6 Destination Operand—Arithmetic Shift Left B-47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B–7 Destination Operand—Carry Left Shift B-48. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B–8 Destination Operand—Arithmetic Right Shift B-49. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B–9 Destination Operand—Carry Right Shift B-51. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B–10 Destination Operand Byte Swap B-58. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B–11 Destination Operand Sign Extension B-59. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C–1 Interconnection of Flash Memory Module(s) C-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C–2 Flash Memory Module1 Disabled, Module2 Can Execute Code

Simultaneously C-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C–3 Flash Memory Module Example C-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C–4 Segments in Flash Memory Module, 4K-Byte Example C-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C–5 Flash Memory Module Block Diagram C-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xvi

Page 17

Figures

C–6 Block Diagram of the Timing Generator in the Flash Memory Module C-7. . . . . . . . . . . . . . . .

C–7 Basic Flash EEPROM Module Timing During the Erase Cycle C-9. . . . . . . . . . . . . . . . . . . . . .

C–8 Basic Flash Memory Module Timing During Write (Single Byte or Word) Cycle C-11. . . . . . .

C–9 Basic Flash Memory Module Timing During a Segment-Write Cycle C-11. . . . . . . . . . . . . . . .

C–10 Basic Flash Memory Module Timing During Segment Write Cycle C-19. . . . . . . . . . . . . . . . . .

C–11 Signal Connections to MSP430 JTAG Pins C-22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figures

xvii

Page 18

Running Title—Attribute Reference

Tables

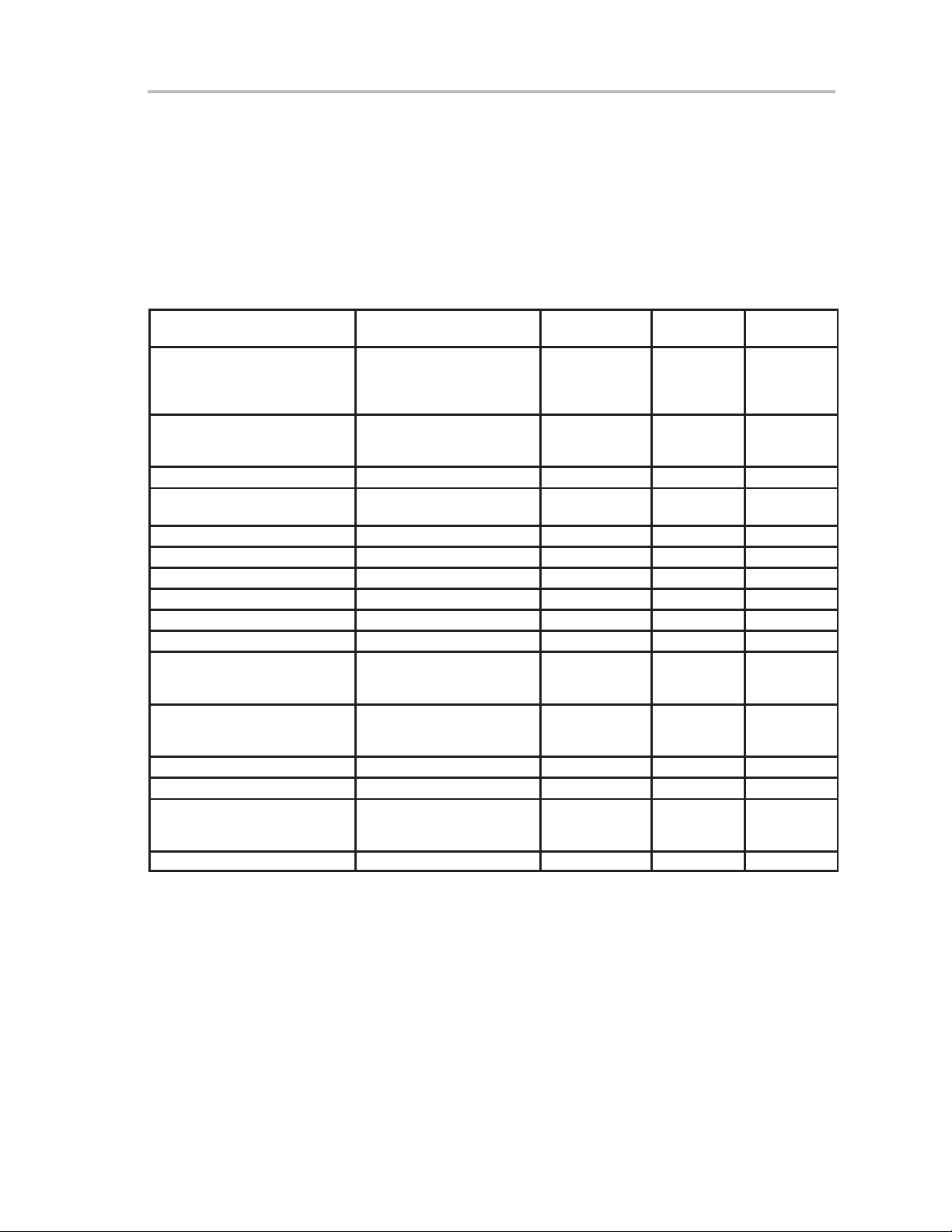

3–1 Interrupt Control Bits in SFRs 3-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–2 Interrupt Enable Registers 1 and 2 3-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–3 Interrupt Flag Register 1 and 2 3-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–4 Module Enable Registers 1 and 2 3-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–5 Interrupt Sources, Flags, and Vectors of 14x Configurations 3-15. . . . . . . . . . . . . . . . . . . . . . .

3–6 Low Power Mode Logic Chart for Basic Clock System 3-19. . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–1 Peripheral File Address Map—Word Modules 4-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–2 Peripheral File Address Map—Byte Modules 4-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–3 Special Function Register Address Map 4-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–1 Register by Functions 5-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–2 Description of Status Register Bits 5-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–3 Values of Constant Generators CG1, CG2 5-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–4 Source/Destination Operand Addressing Modes 5-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .