Texas Instruments CY74FCT2257CTSOCT, CY74FCT2257CTSOC, CY74FCT2257CTQCT, CY74FCT2257CTQC, CY74FCT2257ATQCT Datasheet

...

Quad 2-Input Multiplexe

r

CY74FCT2257T

SCCS038 - September 1994 - Revised March 2000

Data sheet acquired from Cypress Semiconductor Corporation.

Data sheet modified to remove devices not offered.

Copyright © 2000, Texas Instruments Incorporated

1CY74FCT2257T

Features

• Function and pinout compatible with FCT and F logic

• 25Ωoutputseriesresistorstoreducetransmissionline

reflection noise

• FCT-C speed at 4.3 ns max.,

FCT-A speed at 5.0 ns max.

• TTL output level versions of equivalent FCT functions

• Edge-rate control circuitry for significantly improved

noise characteristics

• Power-off disable feature

• Fully compatible with TTL input and output logic levels

• ESD > 2000V

• Sink current 12 mA

Source current15 mA

• Extended commercial temp. range of –40˚C to +85˚C

• Three-state outputs

Functional Description

The FCT2257T has four identical two-input multiplexers that

select four bits of data from two sources under the control of a

common data Select input (S). The I0 inputs are selected

when the Select input is LOW and the I1 inputs are selected

when the Select input is HIGH. Data appears at the output in

true non-inverted form for the FCT2257T.On-chip termination

resistors have been added to the outputs to reduce system

noise caused by reflections. The FCT2257T can be used to

replace the FCT257T to reduce noise in an existing design.

The FCT2257T is a logic implementation of a four-pole,

two-position switch where the position of the switch is

determined by the logic levelssupplied to the select input. Outputs are forced to a high-impedance “OFF” state when the

Output Enable input (

OE) is HIGH.

All but one device must be in the high-impedance state to

avoid currents exceeding the maximum ratings if outputs are

tied together. Design of the output enable signals must ensure

that there is no overlap when outputs of three-state devices

are tied together.

The outputs are designed with a power-off disable feature to

allow for live insertion of boards.

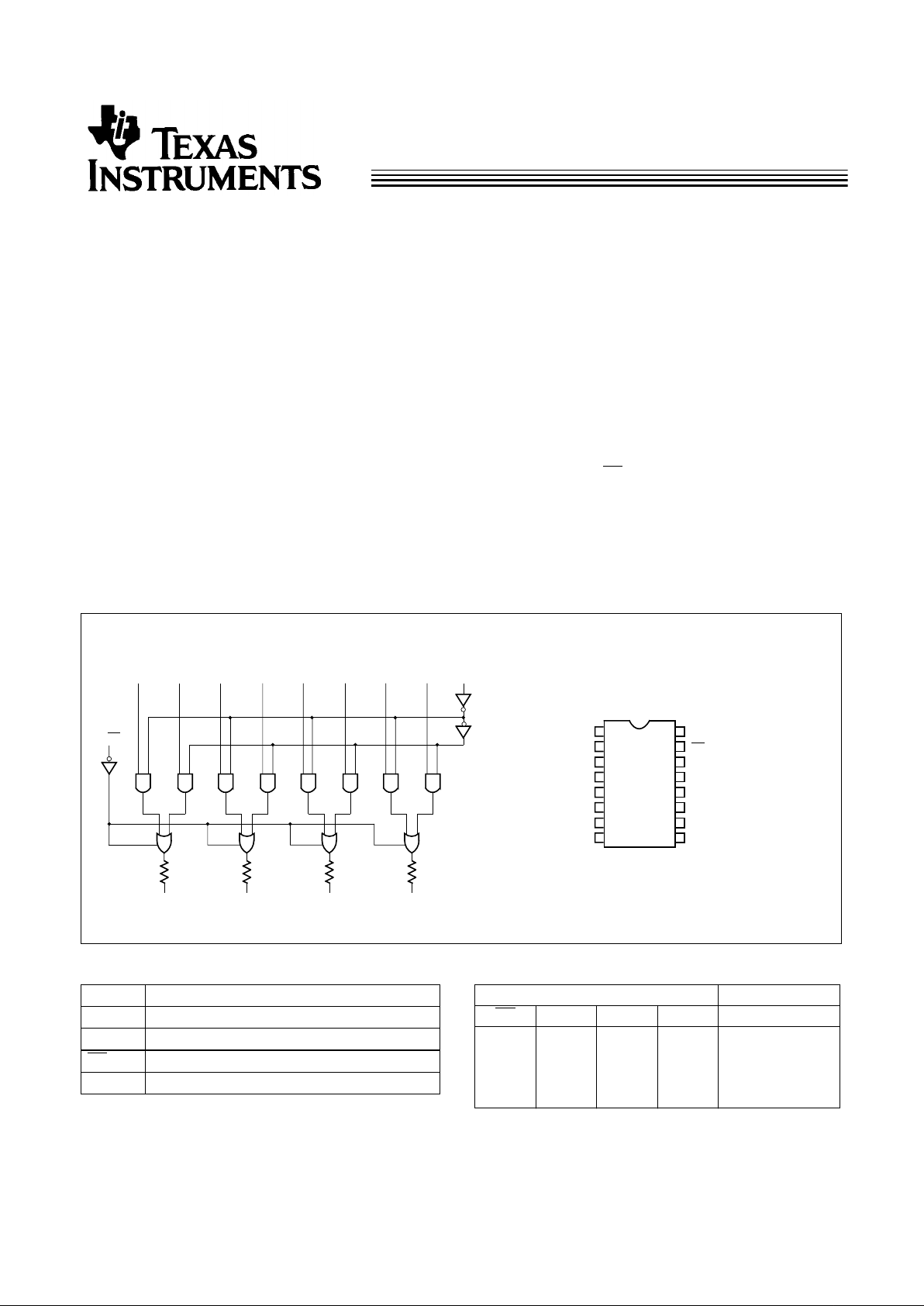

Logic Block Diagram

Pin Configurations

I

0a

S

FCT2257T–1

I

1a

I

0b

I

1b

I

0c

I

1c

I

0dI1d

Y

a

Y

b

Y

c

Y

d

OE

1

2

3

4

5

6

7

8

V

CC

GND

Top View

SOIC/QSOP

16

15

14

13

12

11

10

9

Y

a

S

I

1a

I

0a

I

1c

I

0c

OE

Y

b

I

1b

I

0b

I

1d

I

0d

Y

c

Y

d

FCT2257T–3

Pin Description

Name Description

I Data Inputs

S Common Select Input

OE Enable Inputs (Active LOW)

Y Data Outputs

Function Table

[1]

Inputs Output

OE S I

0

I

1

Y

H

L

L

L

L

X

H

H

L

L

X

X

X

L

H

X

L

H

X

X

Z

L

H

L

H

Note:

1. H = HIGH Voltage Level, L = LOW Voltage Level, X = Don’t Care,

Z = High impedance (OFF) state.

CY74FCT2257T

2

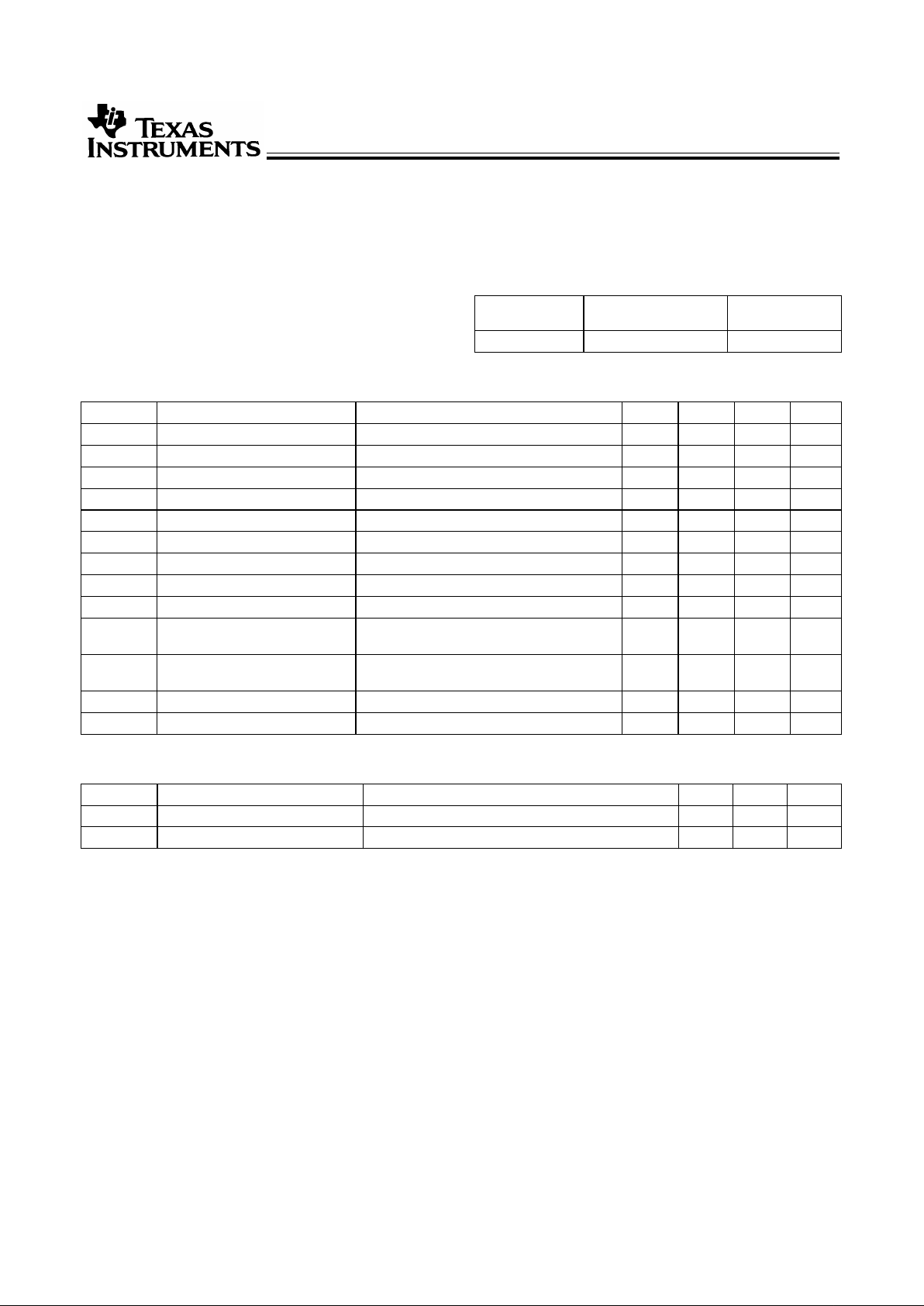

Maximum Ratings

[2, 3]

(Above which the useful life may be impaired. For user guidelines, not tested.)

Storage Temperature .................................–65°C to +150°C

Ambient Temperature with

Power Applied.............................................–65°C to +135°C

Supply Voltage to Ground Potential...............–0.5V to +7.0V

DC Input Voltage............................................–0.5V to +7.0V

DC Output Voltage.........................................–0.5V to +7.0V

DC Output Current (Maximum Sink Current/Pin) ......120 mA

Power Dissipation..........................................................0.5W

Static Discharge Voltage............................................>2001V

(per MIL-STD-883, Method 3015)

Operating Range

Range

Ambient

Temperature V

CC

Commercial –40°C to +85°C 5V ± 5%

Electrical Characteristics Over the Operating Range

Parameter Description Test Conditions Min. Typ.

[5]

Max. Unit

V

OH

Output HIGH Voltage VCC=Min., IOH=–15 mA 2.4 3.3 V

V

OL

Output LOW Voltage VCC=Min., IOL=12 mA 0.3 0.55 V

R

OUT

Output Resistance VCC=Min., IOL=12 mA 20 25 40 Ω

V

IH

Input HIGH Voltage 2.0 V

V

IL

Input LOW Voltage 0.8 V

V

H

Hysteresis

[6]

All inputs 0.2 V

V

IK

Input Clamp Diode Voltage VCC=Min., IIN=–18 mA –0.7 –1.2 V

I

IH

Input HIGH Current VCC=Max., VIN=2.7V ±1 µA

I

IL

Input LOW Current VCC=Max., VIN=0.5V ±1 µA

I

OZH

Off State HIGH-Level Output

Current

VCC=Max., V

OUT

=2.7V 10 µA

I

OZL

Off State LOW-Level

Output Current

VCC=Max., V

OUT

=0.5V –10 µA

I

OS

Output Short Circuit Current

[7]

VCC=Max., V

OUT

=0.0V –60 –120 –225 mA

I

OFF

Power-Off Disable VCC=0V, V

OUT

=4.5V ±1 µA

Capacitance

[6]

Parameter Description Test Conditions Typ.

[5]

Max. Unit

C

IN

Input Capacitance 5 10 pF

C

OUT

Output Capacitance 9 12 pF

Notes:

2. Unless otherwise noted, these limits are over the operating free-air temperature range.

3. Unused inputs must always be connected to an appropriate logic voltage level, preferably either V

CC

or ground.

4. T

A

is the “instant on” case temperature.

5. Typical values are at V

CC

=5.0V, TA=+25˚C ambient.

6. This parameter is specified but not tested.

7. Not more than one output should be shorted at a time. Duration of short should not exceed one second. The use of high-speed test apparatus and/or sample

and hold techniques are preferable in order to minimize internal chip heating and more accurately reflect operational values. Otherwise prolonged shorting of

a high output may raise the chip temperature well above normal and thereby cause invalid readings in other parametric tests. In any sequence of parameter

tests, I

OS

tests should be performed last.

Loading...

Loading...