Texas Instruments CD74HCT109M96, CD74HCT109M, CD74HCT109E, CD74HC109M96, CD74HC109M Datasheet

...

Data sheet acquired from Harris Semiconductor

/

SCHS140

March 1998

CD74HC109,

CD74HCT109

Dual J-K Flip-Flop with Set and Reset

Positive-Edge Trigger

[ /Title

(CD74H

C109,

CD74H

CT109)

Subject

(Dual JK FlipFlop

with Set

and

Reset

Features

• Asynchronous Set and Reset

• Schmitt Trigger Clock Inputs

• Typical Propagation Delay = 18ns at V

C

= 15pF, TA = 25oC

L

• Typical f

T

= 25oC

A

• Fanout (Over Temperature Range)

- Standard Outputs. . . . . . . . . . . . . . . 10 LSTTL Loads

- Bus Driver Outputs . . . . . . . . . . . . . 15 LSTTL Loads

• Wide Operating Temperature Range . . . -55

• Balanced Propagation Delay and Transition Times

• Significant Power Reduction Compared to LSTTL

Logic ICs

• HC Types

- 2V to 6V Operation

- High Noise Immunity: N

= 60MHz at VCC = 5V, CL = 15pF,

MAX

= 30%, NIH = 30% of V

IL

CC

= 5V,

o

C to 125oC

Pinout

at VCC = 5V

• HCT Types

- 4.5V to 5.5V Operation

- Direct LSTTL Input Logic Compatibility,

V

= 0.8V (Max), VIH = 2V (Min)

IL

- CMOS Input Compatibility, I

≤ 1µA at VOL, V

l

Description

The Harris CD74HC109 and CD74HCT109 are dual J-K flipflops with set and reset. The flip-flop changes state with the

positive transition of Clock (1CP and 2CP).

The flip-flop is set and reset by active-low

respectively. A low on both the set and reset inputs

simultaneously will force both Q and

However, both set and reset going high simultaneously

results in an unpredictable output condition.

Q outputs high.

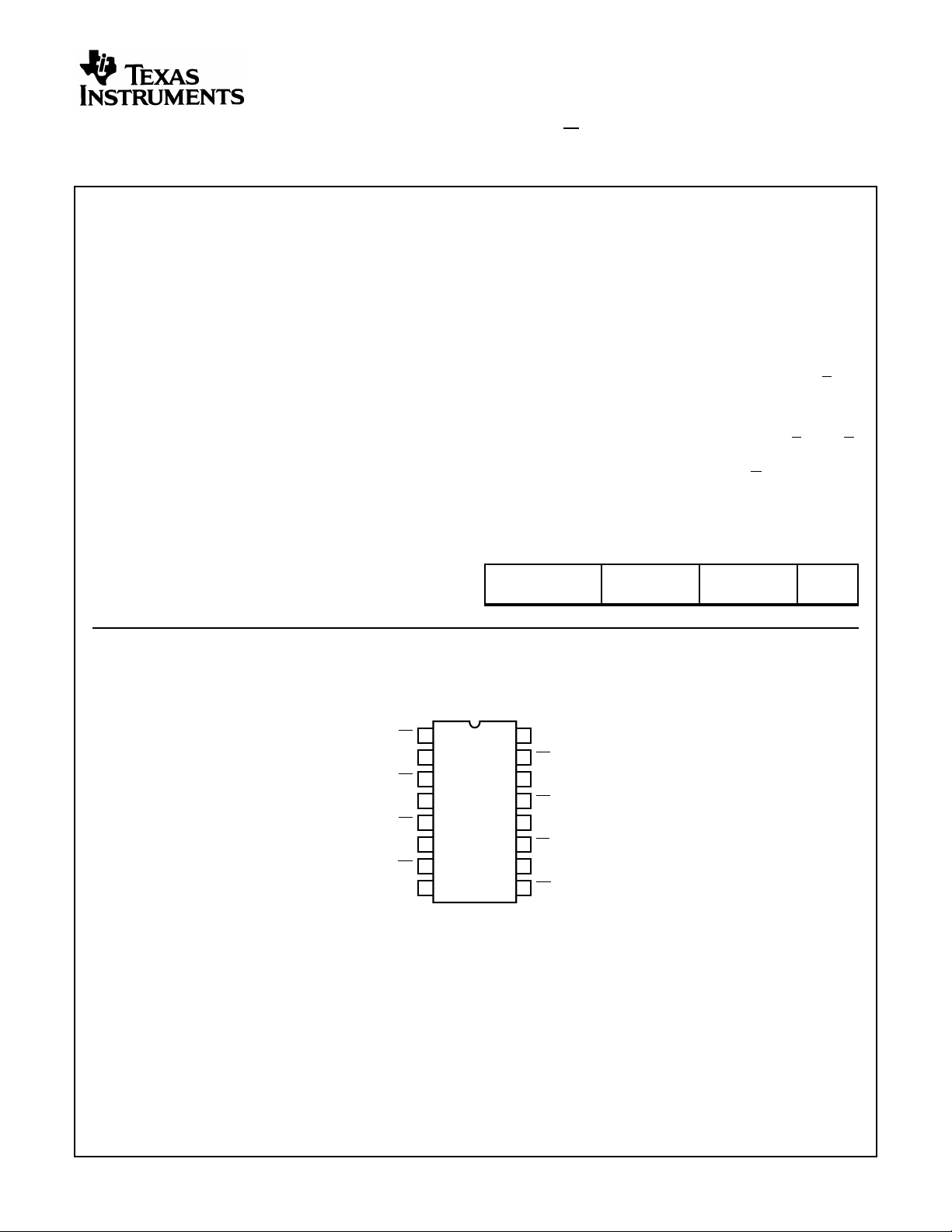

Ordering Information

CC

PART NUMBER

TEMP. RANGE

(oC) PACKAGE

OH

S and R,

PKG.

NO.

CD74HC109, CD74HCT109

(PDIP, SOIC)

TOP VIEW

1R

1K

1CP

1S

1Q

1Q

GND

1

2

1J

3

4

5

6

7

8

16

15

14

13

12

11

10

9

V

CC

2R

2J

2K

2CP

2S

2Q

2Q

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures.

Copyright

© Harris Corporation 1998

1

File Number 1667.1

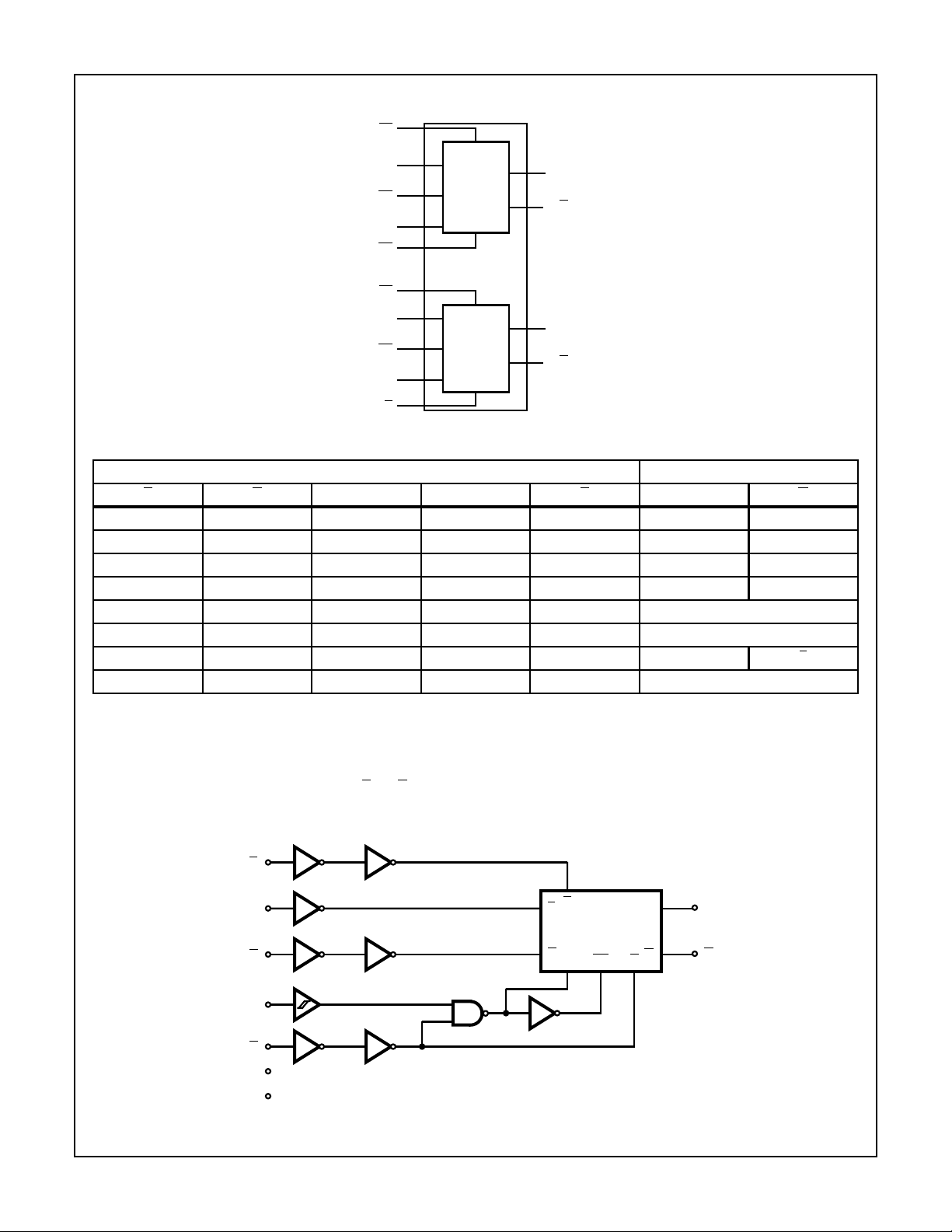

Functional Diagram

CD74HC109, CD74HCT109

5

1S

2

1J

1K

1CP

1R

2S

2K

2CP

2R

3

4

1

11

14

2J

13

12

15

F/F 1

F/F 2

TRUTH TABLE

INPUTS OUTPUTS

S RCPJ KQQ

LHXXXHL

H

L

H

H

L

L

H

H

XXXLH

X X X H (Note 3) H (Note 3)

↑ LLLH

↑ H L Toggle

HH↑ L H No Change

HH↑ HHHL

H H L X X No Change

NOTES:

H= High Level (Steady State)

L= Low Level (Steady State)

X= Don’t Care

↑= Low-to-High Transition

3. Unpredictable and unstable condition if both S and R go high simultaneously.

6

1Q

7

1

Q

10

2Q

9

Q

2

GND = 8

V

= 16

CC

Logic Diagram

CP

V

CC

GND

5(11)

S

2(14)

J

3(13)

K

4(12)

1(15)

R

16

S

J

FF

K

CL

CL R

8

Q

Q

6(10)

Q

7(9)

Q

2

CD74HC109, CD74HCT109

Absolute Maximum Ratings Thermal Information

DC Supply Voltage, VCC. . . . . . . . . . . . . . . . . . . . . . . . -0.5V to 7V

DC Input Diode Current, I

IK

For VI < -0.5V or VI > VCC + 0.5V. . . . . . . . . . . . . . . . . . . . . .±20mA

DC Drain Current, per Output, I

O

For -0.5V < VO < VCC + 0.5V. . . . . . . . . . . . . . . . . . . . . . . . . .±25mA

DC Output Diode Current, I

OK

For VO < -0.5V or VO > VCC + 0.5V . . . . . . . . . . . . . . . . . . . .±20mA

DC Output Source or Sink Current per Output Pin, I

O

For VO > -0.5V or VO < VCC + 0.5V . . . . . . . . . . . . . . . . . . . .±25mA

DC VCC or Ground Current, ICC . . . . . . . . . . . . . . . . . . . . . . . . .±50mA

Operating Conditions

Temperature Range, TA . . . . . . . . . . . . . . . . . . . . . . -55oC to 125oC

Supply Voltage Range, V

HC Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2V to 6V

HCT Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4.5V to 5.5V

DC Input or Output Voltage, VI, VO . . . . . . . . . . . . . . . . . 0V to V

CP Input Rise and Fall Time, tr, t

2V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1.0ms (Max)

4.5V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1.0ms (Max)

6V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1.0ms (Max)

Input Rise and Fall Time (All Inputs Except CP), tr, t

2V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1000ns (Max)

4.5V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 500ns (Max)

6V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 400ns (Max)

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation

of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

4. θJA is measured with the component mounted on an evaluation PC board in free air.

CC

f

f

Thermal Resistance (Typical, Note 4) θJA (oC/W)

PDIP Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

SOIC Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

Maximum Junction Temperature (Hermetic Package or Die) . . . 175oC

Maximum Junction Temperature (Plastic Package) . . . . . . . . 150oC

Maximum Storage Temperature Range . . . . . . . . . .-65oC to 150oC

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . . 300oC

(SOIC - Lead Tips Only)

CC

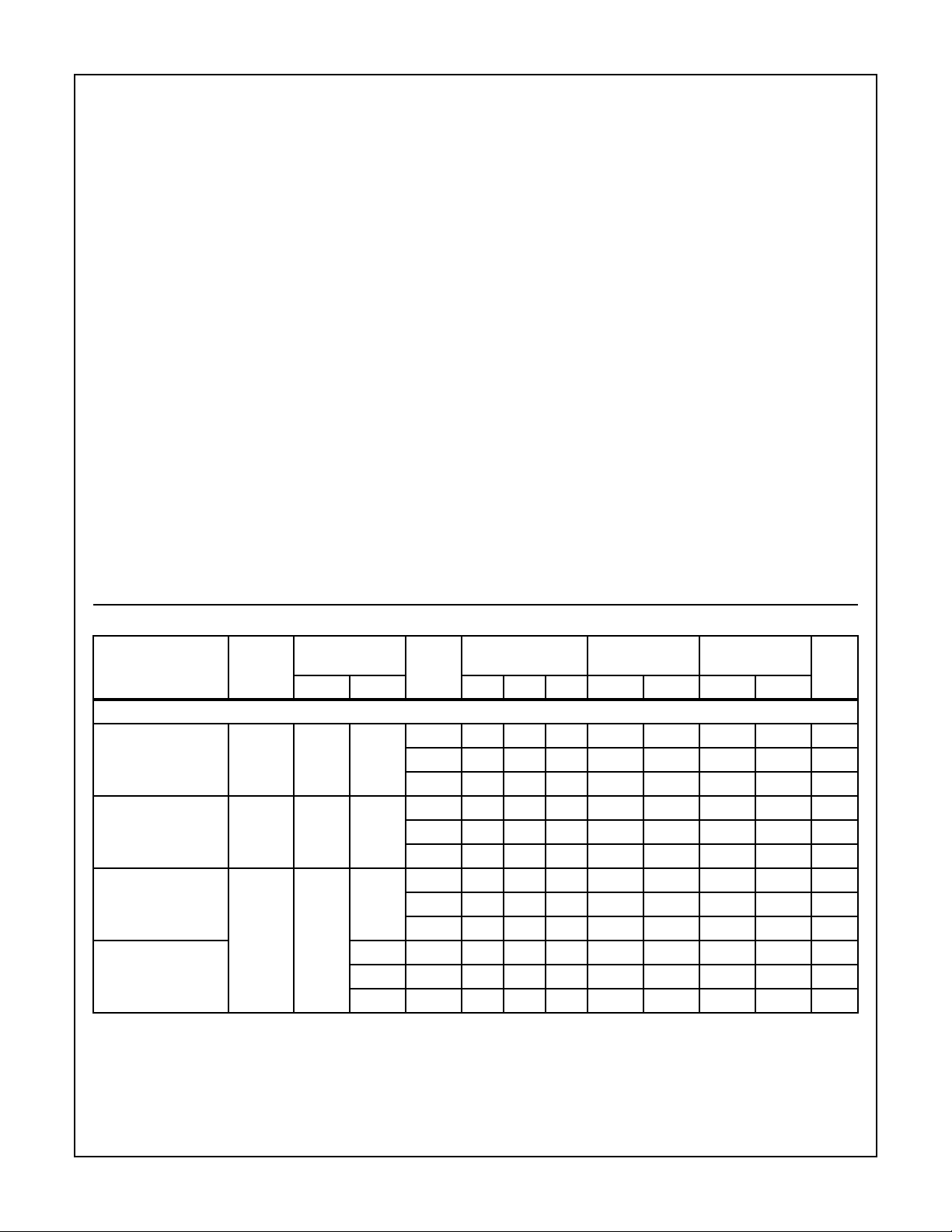

DC Electrical Specifications

PARAMETER SYMBOL

HC TYPES

High Level Input

Voltage

Low Level Input

Voltage

High Level Output

Voltage

CMOS Loads

High Level Output

Voltage

TTL Loads

V

IH

V

IL

V

OH

TEST

CONDITIONS

25oC -40oC TO 85oC -55oC TO 125oC

VCC (V)

- - 2 1.5 - - 1.5 - 1.5 - V

4.5 3.15 - - 3.15 - 3.15 - V

6 4.2 - - 4.2 - 4.2 - V

- - 2 - - 0.5 - 0.5 - 0.5 V

4.5 - - 1.35 - 1.35 - 1.35 V

6 - - 1.8 - 1.8 - 1.8 V

VIH or

V

-0.02 2 1.9 - - 1.9 - 1.9 - V

IL

4.5 4.4 - - 4.4 - 4.4 - V

6 5.9 - - 5.9 - 5.9 - V

---------V

-4 4.5 3.96 - - 3.84 - 3.7 - V

-5.2 6 5.48 - - 5.34 - 5.2 - V

UNITSVI(V) IO(mA) MIN TYP MAX MIN MAX MIN MAX

3

Loading...

Loading...