Texas Instruments BQ4010MA-70, BQ4010MA-200, BQ4010MA-150, BQ4010YMA-85N, BQ4010YMA-85 Datasheet

...

bq4010/bq4010Y

8Kx8 Nonvolatile SRAM

Features

➤ Data retention in the absence of

power

➤ Automatic write-pro tection

during power-up/power-down

cycles

➤ Industry-standard 28-pin 8K x 8

pinout

➤ Conventional SRAM operation;

unlimited write cycles

➤ 10-year minimum data retention

in absence of power

➤ Battery internally isolated until

power is applied

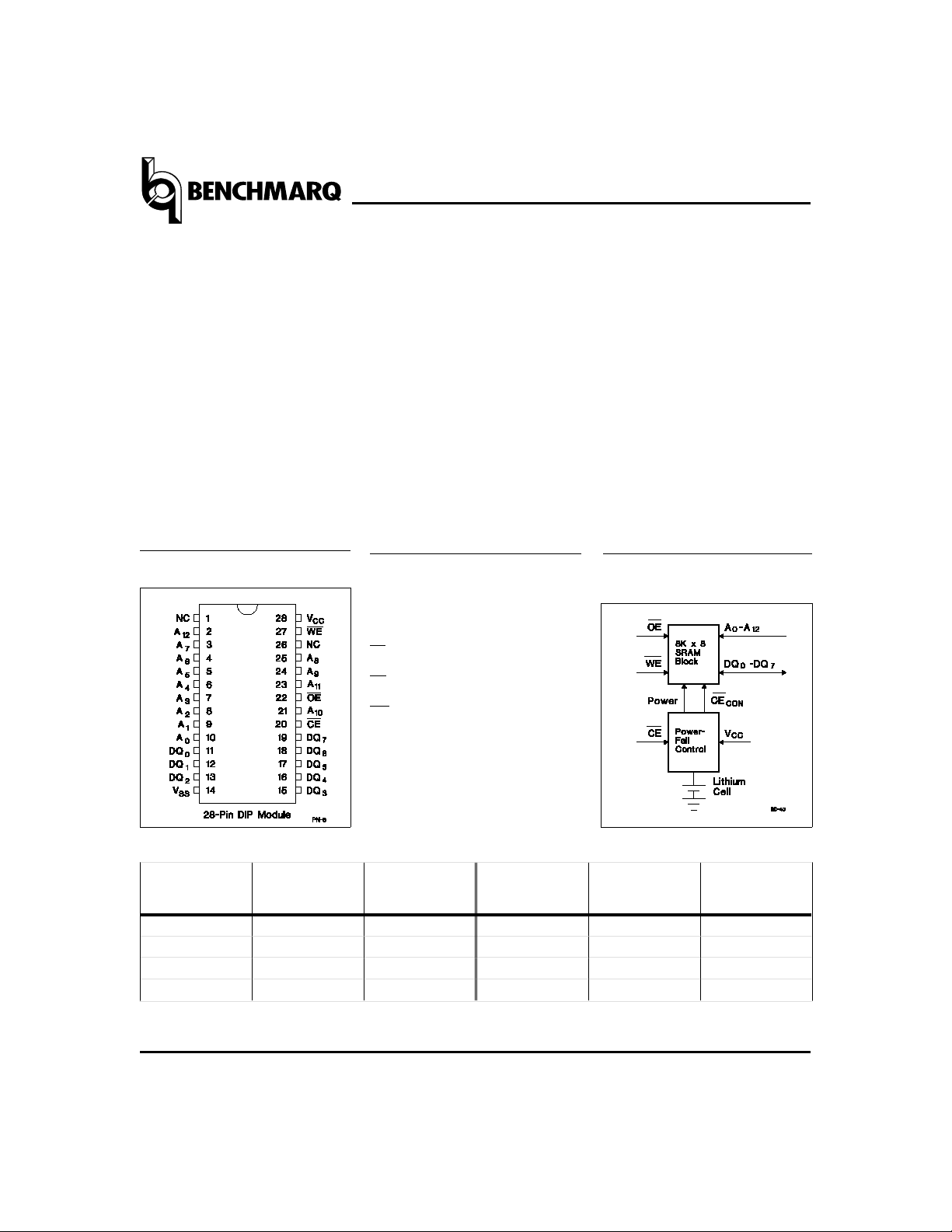

Pin Connections

General Description

The CMOS bq4010 is a nonvolatile

65,536-bit static RAM organized as

8,192 words by 8 bits. The integral

control circuitry and lithium energy

source provide reliable nonvolatility

coupled with the unlimited write

cycles of standard SRAM.

The control circuitry constantly

monitors the single 5V supply for an

out-of-tolerance condition. When V

falls out of tolerance, the SRAM is

unconditionally write-protected to

prevent inadvertent write operation.

CC

Pin Names

A0 –A

DQ

0

CE Chip enable input

OE Output enable input

WE Write enable input

Address inputs

12

–DQ7Data input/output

At this time the integral energy

source is switched on to sustain the

memory until af ter V

The bq4010 uses an extremely low

standby current CMOS SRAM,

coupled with a small lithium coin

cell to provide nonvolatility without

long write-cycle times and the writecycle limitations associated with

EEPROM.

The bq4010 re quires no exter nal circuitry and is sock et-com patible wit h

industry-standard SRAMs and most

EPROMs and EEPROMs.

returns valid.

CC

Block Diagram

Selection Guide

Part

Number

bq4010 -85

bq4010 -150

bq4010 -200

Sept. 1996 D

NC No connect

V

CC

V

SS

Maximum

Access

Time (ns)

85 -5%

150 -5%

200 -5%

+5 volt supply input

Ground

Negative

Supply

Tolerance

Part

Number

bq4010 Y -70

bq4010 Y -85

bq4010 Y -150

bq4010 Y -200

1

Maximum

Access

Time (ns)

70 -10%

85 -10%

150 -10%

200 -10%

Negative

Supply

Tolerance

bq4010/bq4010Y

Functional Descri ption

When p ower is val id, the bq4010 o perates as a standard

CMOS SRAM. During power-down and power-up cycles,

the bq4010 acts as a nonvo latile memor y, automatically

protecting and preserving the memory contents.

Power-down/power-up control circuitry constantly

monitor s the V

. The bq4010 monitors for V

V

PFD

use in syst ems with 5% suppl y tolerance. Th e bq4010Y

monitors f or V

10% supply tolerance.

When V

CC

automatically write-protects the data. All outputs

become high impedance, and all inputs are treated as

“don’t care.” If a valid access is in process at the time of

power-fail detection, the memory cycle continues to completion. If the memory cycle fails to terminate within

time t

WPT

supply for a power-fail-detect threshold

CC

= 4.37V typi cal for use in systems with

PFD

falls below the V

= 4.62V typic al for

PFD

threshold, the SRAM

PFD

, write-protection takes place.

falls past V

As V

CC

circuitry switches to the internal lithium backup supply,

which provides data retention until valid V

When V

returns to a level above the internal backup

CC

cell voltage, the supply is switched back to V

ramps above the V

V

CC

continues for a time t

processor stabilization. Normal memory operation may

resume after this time.

The internal coin cell used by the bq4010 has an

extrem ely long shel f life and prov ides data reten tion for

more than 10 years in the absence of system power.

As shipped from Benchmar q, the integral lithium cell is

electr ically isola ted from th e memory . (Self-dis charge in

this con di ti on is approx ima te ly 0.5 % p e r ye ar .) Foll ow in g

the first application of V

the lithium backup cell provides data retention on

subsequent power-downs.

and approaches 3V, the co ntrol

PFD

is applied.

CC

threshold, write-protection

PFD

(120ms m aximu m) to allo w f or

CER

, this iso lation is broken , and

CC

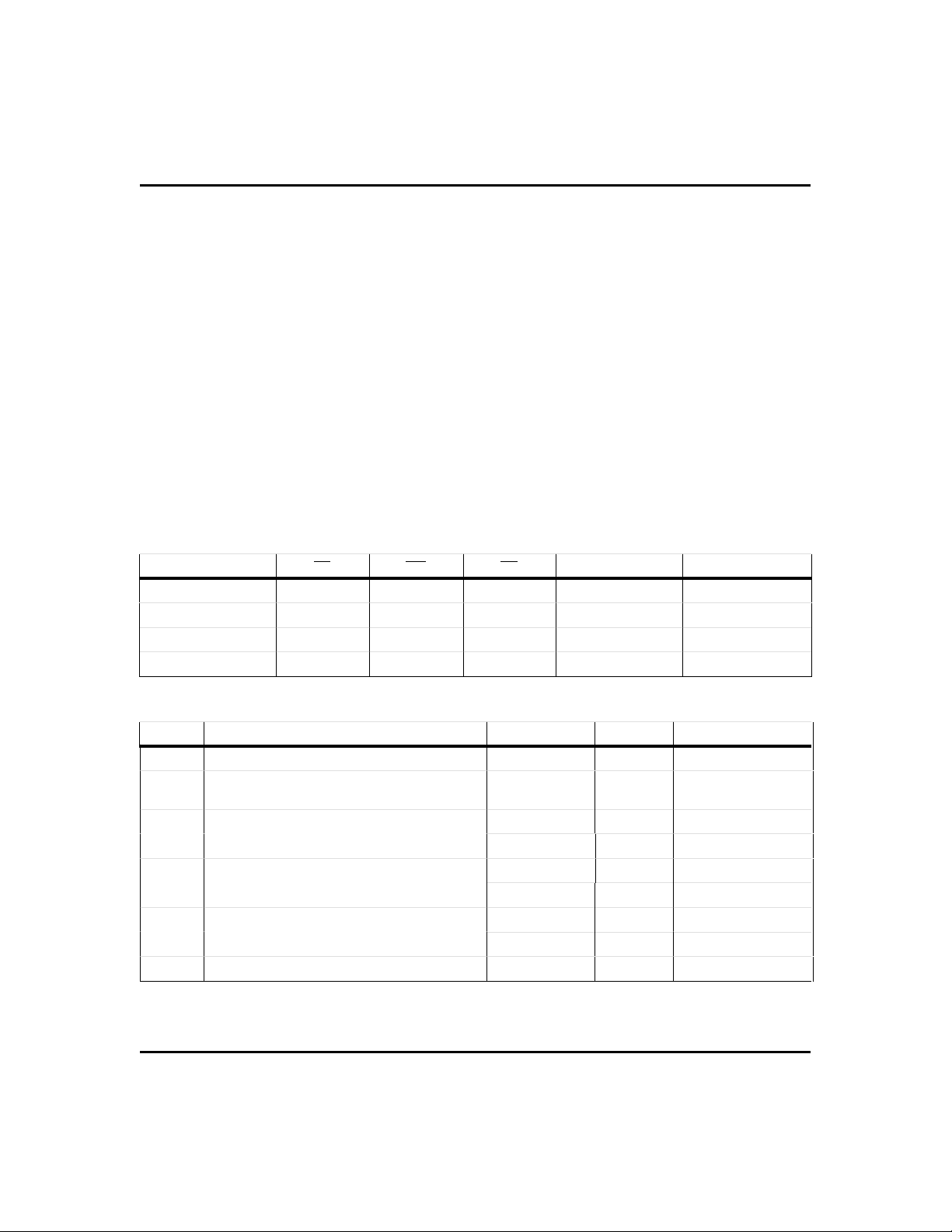

Truth Table

Mode CE WE OE I/O Operatio n Power

Not selected H X X High Z Standby

Output disable L H H High Z Active

Read L H L D

Write LLX D

OUT

IN

Active

Active

CC

. After

Absolute Maximum Ratings

Symbol Parameter Value Unit Conditions

V

CC

V

T

T

OPR

T

STG

T

BIAS

T

SOLDER

Note: Permanent device damage may occur if Absolute Maxi mum Ratings are exceeded. F unctional operation

DC voltage applied on VCC relative to V

SS

DC voltage applied on any pin excluding V

relative to V

SS

CC

-0.3 to 7.0 V

-0.3 to 7.0 V

V

≤ VCC + 0.3

T

0 to +70 °C Commercial

Operat ing temperature

-40 to +85 °C Industrial “N”

-40 to +70 °C Commercial

Storage temperature

-40 to +85 °C Industrial “N”

-10 to +70 °C Commercial

Temperature under bias

-40 to +85 °C Industrial “N”

Soldering temperature +260 °C For 10 seconds

should be limited to the Recommended DC Operating Conditions detailed in this data sheet. Exposure to conditions beyond the operational limits for extended periods of time may affect device reliability.

Sept. 1996 D

6-2

bq4010/bq4010Y

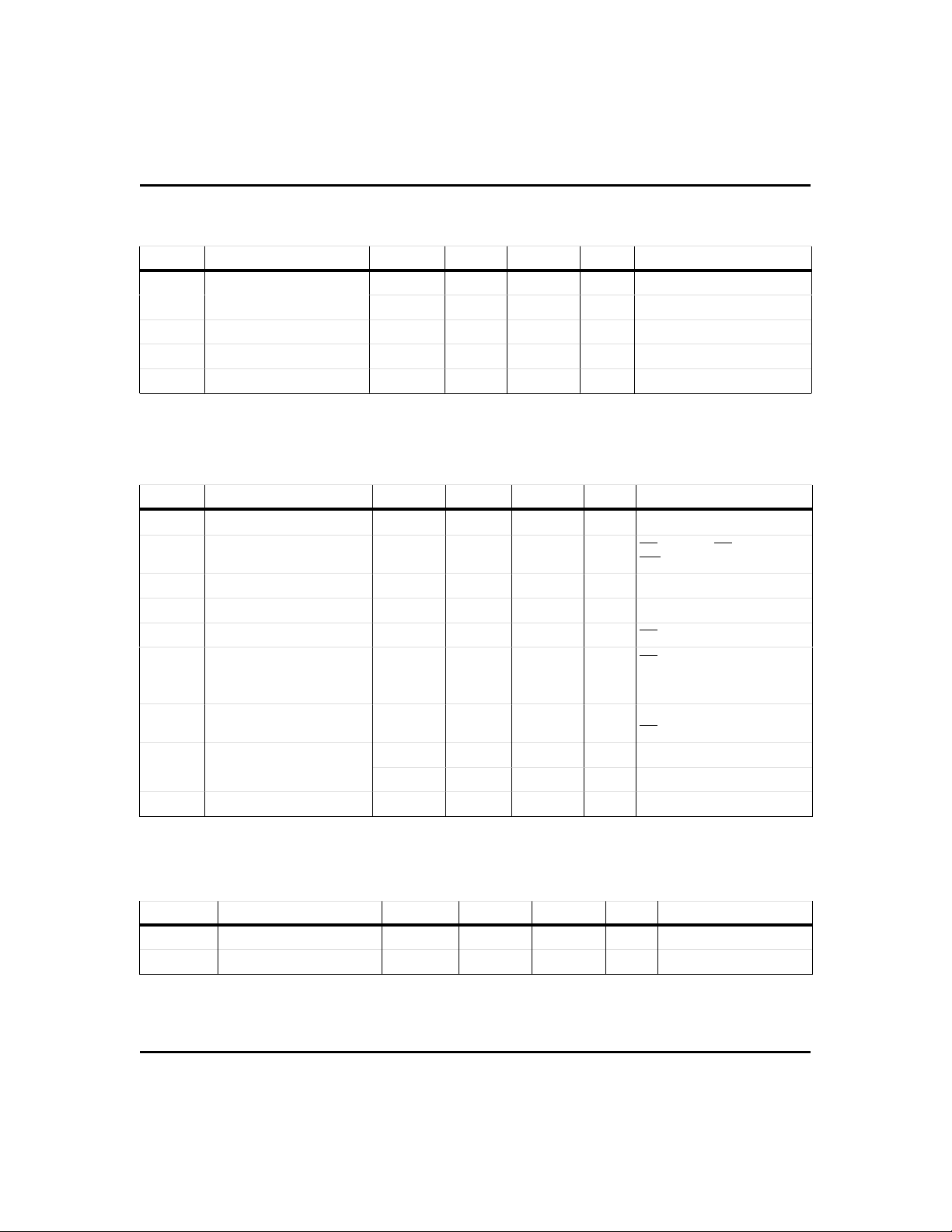

Recommended DC Operating Conditions (T

A

= T

OPR

)

Symbol Parameter Minimum Typical Maximum Unit Notes

4.5 5.0 5.5 V bq4010Y/bq4010Y-xxxN

V

V

V

Note: Typical values indicate operation at T

DC Electrical Characteristics (T

Supply voltage

CC

Supply voltage 0 0 0 V

SS

Input low voltage -0.3 - 0.8 V

V

IL

Input high voltage 2.2 - VCC + 0.3 V

IH

4.75 5.0 5.5 V bq4010

= 25°C.

A

A

= T

OPR

, V

CCmin

≤ VCC ≤ V

CCmax)

Symbol Parameter Minimum Typical Maximum Unit Conditions/Notes

I

I

V

V

I

LI

LO

OH

OL

SB1

Input leakage current - -

Output leakage current - -

± 1 µA

± 1 µA

VIN = VSS to V

CE = VIH or OE = VIH or

WE = V

IL

Output high voltage 2.4 - - V IOH = -1.0 mA

Output low voltage - - 0.4 V IOL = 2.1 mA

Standby supply current - 4 7 mA CE = V

IH

CC

CE ≥ VCC - 0.2V,

I

I

SB2

CC

Standby supply current - 2.5 4 mA

Operating supply current - 65 75 mA

0V ≤ V

or V

≤ 0.2V,

IN

≥ VCC - 0.2V

IN

Min. cycle, duty = 100%,

CE = VIL, I

= 0mA

I/O

4.55 4.62 4.75 V bq4010

V

PFD

V

SO

Power-fail-detect voltage

4.30 4.37 4.50 V bq4010Y

Supply switch-over vol t age - 3 - V

Note: Typical values indicate operation at T

Capacitance (T

= 25°C, F = 1MHz, VCC = 5.0V)

A

= 25°C, VCC = 5V.

A

Symbol Parameter Minimum Typical Maximum Unit Conditions

C

I/O

C

IN

Input/output capacitance - - 10 pF Output voltage = 0V

Input capacitance - - 10 pF Input voltage = 0V

Note: These parameters are sampled and not 100% tested.

Sept. 1996 D

6-3

bq4010/bq4010Y

AC Test Conditions

Parameter Test Conditions

Input pulse levels 0V to 3.0V

Input rise and fall times 5 ns

Input and output timing reference levels 1.5 V (unless otherwise specified)

Output load (including scope and jig) See Figures 1 and 2

Figure 1. Output Load A Figure 2. Output Load B

Read Cycle (T

Symbol Parameter

t

RC

t

AA

t

ACE

t

OE

t

CLZ

t

OLZ

t

CHZ

t

OHZ

t

OH

Read cycle time 70 - 85 - 150 - 200 - ns

Address access time - 70 - 85 - 150 - 200 ns Output load A

Chip enable access time - 70 - 85 - 150 - 200 ns Output load A

Output enable to output

valid

Chip enable to output

in low Z

Output enable to output

in low Z

Chip disable to output

in high Z

Output disable to

output in high Z

Output hold from

address change

A

= T

OPR

, V

CCmin

≤ V

CC

≤ V

CCmax

)

-70/-70N -85/-85N -150/-150N -200

Min. Max. Min. Max. Min. Max.

Min. Max.

Unit Conditions

- 35 - 45 - 70 - 90 ns Output load A

5-5-10-10-nsOutput load B

5-5-5-5-nsOutput load B

025040060070nsOutput load B

025030050070nsOutput load B

10 - 10 - 10 - 10 - ns Output load A

Sept. 1996 D

6-4

Loading...

Loading...