Page 1

bq34210-Q1

Technical Reference Manual

Literature Number: SLUUBE8

September 2018

Page 2

Contents

Preface ........................................................................................................................................ 6

1 General Description.............................................................................................................. 7

1.1 Gas Gauging ................................................................................................................. 7

1.1.1 CEDV Gas Gauging Operational Overview ..................................................................... 8

1.1.2 Main Fuel Gauge Registers ....................................................................................... 8

1.1.3 Capacity Learning (FCC Update)................................................................................. 9

1.1.4 End-of-Discharge (EDV) Thresholds and Capacity Correction ............................................... 9

1.1.5 EDV Discharge Rate and Temperature Compensation ...................................................... 10

1.1.6 EDV Age Factor ................................................................................................... 11

1.1.7 Self-Discharge..................................................................................................... 11

1.1.8 Battery Electronic Load Compensation......................................................................... 11

1.1.9 Initial Battery Capacity at Device Reset........................................................................ 12

1.1.10 Fuel Gauge Operating Modes.................................................................................. 12

1.1.11 CEDV Smoothing ................................................................................................ 13

1.2 Accumulated Charge Measurement ..................................................................................... 14

1.3 End-Of-Service Determination............................................................................................ 15

1.3.1 Alert Config Registers ............................................................................................ 16

1.3.2 Smoothing Config Register ...................................................................................... 21

1.3.3 End-Of-Service Determination—Detailed Description........................................................ 21

2 Functional Description........................................................................................................ 31

2.1 Device Configuration....................................................................................................... 31

2.1.1 Smoothing Config Register ...................................................................................... 31

2.1.2 Operation Configuration A (Operation Config A) Register................................................... 31

2.2 External Pin Functions..................................................................................................... 32

2.2.1 Wake-Up Comparator ............................................................................................ 32

2.2.2 Autocalibration..................................................................................................... 32

2.3 Temperature Measurement ............................................................................................... 33

2.3.1 Overtemperature Indication ...................................................................................... 33

2.3.2 Undertemperature Indication..................................................................................... 33

2.4 Battery Condition Warnings............................................................................................... 33

2.4.1 Battery Low Warning.............................................................................................. 33

2.4.2 Battery High Warning ............................................................................................. 34

2.4.3 Battery Low SOC Warning....................................................................................... 34

2.4.4 Battery Level Threshold .......................................................................................... 34

2.5 Charging and Charge Termination Indication .......................................................................... 35

2.5.1 Detecting Charge Termination................................................................................... 35

2.5.2 Charge Inhibit...................................................................................................... 35

2.6 Power Modes ............................................................................................................... 35

2.6.1 NORMAL Mode.................................................................................................... 37

2.6.2 SLEEP Mode....................................................................................................... 37

2.6.3 SHUTDOWN Mode ............................................................................................... 37

2.7 CONFIG UPDATE Mode .................................................................................................. 37

2.8 Application-Specific Information.......................................................................................... 37

2.8.1 Battery Profile Storage and Selection .......................................................................... 37

2.8.2 First OCV Measurement.......................................................................................... 38

2

Contents

Copyright © 2018, Texas Instruments Incorporated

SLUUBE8–September 2018

Submit Documentation Feedback

Page 3

www.ti.com

2.9 Additional Data Memory Parameter Descriptions...................................................................... 38

2.9.1 Calibration ......................................................................................................... 38

2.9.2 Coulomb Counter Offset (CC Offset) ........................................................................... 38

2.9.3 Board Offset ....................................................................................................... 38

2.9.4 Int Temp Offset ................................................................................................... 38

2.9.5 Ext Temp Offset .................................................................................................. 38

2.9.6 Pack VOffset ...................................................................................................... 38

2.9.7 Internal Temp Model ............................................................................................. 38

2.9.8 Ext a Coef and Ext b Coef ...................................................................................... 39

2.9.9 RC0 ................................................................................................................. 39

2.9.10 Filter................................................................................................................ 39

2.9.11 Deadband ........................................................................................................ 39

2.9.12 CC Deadband .................................................................................................... 39

2.9.13 SOC Flag Configuration A (SOC Flag Config A) Register ................................................. 39

2.9.14 SOC Flag Configuration B (SOC Flag Config B) Register ................................................. 40

2.9.15 CEDV Gauging Configuration (CEDV Config) Register .................................................... 41

2.9.16 EMF ............................................................................................................... 41

2.9.17 C0 ................................................................................................................. 41

2.9.18 R0 ................................................................................................................. 42

2.9.19 T0 .................................................................................................................. 42

2.9.20 R1 ................................................................................................................. 42

2.9.21 TC ................................................................................................................. 42

2.9.22 C1 ................................................................................................................. 42

2.9.23 Age Factor ........................................................................................................ 42

2.9.24 Fixed EDV0 ...................................................................................................... 42

2.9.25 Fixed EDV1 ...................................................................................................... 42

2.9.26 Fixed EDV2 ...................................................................................................... 42

2.9.27 Battery Low % ................................................................................................... 42

2.9.28 Learning Low Temp ............................................................................................. 42

2.9.29 Overload Current ................................................................................................ 42

2.9.30 Self Discharge Rate ............................................................................................. 42

2.9.31 Electronics Load ................................................................................................. 42

2.9.32 Near Full .......................................................................................................... 42

2.9.33 Reserve Capacity ................................................................................................ 43

2.9.34 Charge Efficiency (Chg Eff)..................................................................................... 43

2.9.35 Discharge Efficiency (Dsg Eff).................................................................................. 43

2.9.36 Depth of Discharge (DOD) at EDV2........................................................................... 43

2.9.37 Design Capacity ................................................................................................. 43

2.9.38 Design Voltage ................................................................................................... 43

2.9.39 Cycle Count % ................................................................................................... 43

2.9.40 Charge Inhibit Temp Low ....................................................................................... 43

2.9.41 Charge Inhibit Temp High ...................................................................................... 44

2.9.42 Temp Hys ......................................................................................................... 44

2.9.43 Charging and Charge Termination............................................................................. 44

2.9.44 Fast Charge Current ............................................................................................ 45

2.9.45 Charging Voltage ................................................................................................ 46

2.9.46 Taper Current..................................................................................................... 46

2.9.47 Taper Voltage..................................................................................................... 46

2.9.48 Sleep Current ..................................................................................................... 46

2.9.49 Bus Low Time .................................................................................................... 46

2.9.50 Offset Calibration Inhibit Temperature Low................................................................... 46

2.9.51 Offset Calibration Inhibit Temperature High .................................................................. 46

2.9.52 Sleep Voltage Time.............................................................................................. 47

SLUUBE8–September 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Contents

3

Page 4

www.ti.com

2.9.53 Sleep Current Time .............................................................................................. 47

2.9.54 Dsg Current Threshold (Discharge Detection Threshold) .................................................. 47

2.9.55 Chg Current Threshold (Charge Detection Threshold)...................................................... 47

2.9.56 Quit Current ...................................................................................................... 47

2.9.57 Discharge Relax Time .......................................................................................... 47

2.9.58 Charge Relax Time .............................................................................................. 47

2.9.59 Quit Relax Time ................................................................................................. 47

2.9.60 OT Charge ........................................................................................................ 47

2.9.61 OT Chg Recovery ............................................................................................... 48

2.9.62 OT Discharge ..................................................................................................... 48

2.9.63 OT Dsg Recovery ............................................................................................... 48

3 Communications ............................................................................................................... 49

3.1 I

3.2 I

3.3 I

3.4 I

2

C Interface................................................................................................................. 49

2

C Time Out ................................................................................................................ 49

2

C Command Waiting Time .............................................................................................. 50

2

C Clock Stretching........................................................................................................ 50

4 Data Commands................................................................................................................. 51

4.1 Control()/CONTROL_STATUS(): 0x00 and 0x01...................................................................... 52

4.1.1 CONTROL_STATUS: 0x0000 ................................................................................... 53

4.1.2 DEVICE_NUMBER: 0x0001 ..................................................................................... 54

4.1.3 FW_VERSION: 0x0002........................................................................................... 54

4.1.4 BOARD_OFFSET: 0x0009....................................................................................... 54

4.1.5 CC_OFFSET: 0x000A ............................................................................................ 54

4.1.6 CC_OFFSET_SAVE: 0x000B ................................................................................... 54

4.1.7 SET_PROFILE_1: 0x0015 ...................................................................................... 54

4.1.8 SET_PROFILE_2: 0x0016 ...................................................................................... 54

4.1.9 SHUTDOWN_ENABLE: 0x001B ................................................................................ 54

4.1.10 SHUTDOWN: 0x001C........................................................................................... 54

4.1.11 ACCUM_DSG_EN: 0x001E .................................................................................... 54

4.1.12 ACCUM_CHG_EN: 0x001F .................................................................................... 54

4.1.13 IGNORE_SELFDSG_EN: 0x0020 ............................................................................ 55

4.1.14 PIN_CONTROL_EN: 0x0022................................................................................... 55

4.1.15 CAL_TOGGLE: 0x002D......................................................................................... 55

4.1.16 SEAL: 0x0030 .................................................................................................... 55

4.1.17 EOS_START_LEARN: 0x0039................................................................................. 55

4.1.18 EOS_ABORT_LEARN: 0x003A ................................................................................ 55

4.1.19 EOS_RCELL_RRATE_LEARN: 0x003B...................................................................... 55

4.1.20 EOS_WARN_CLEAR: 0x003C................................................................................. 55

4.1.21 EOS_INITIAL_RCELL: 0x003E ................................................................................ 55

4.1.22 EOS_INITIAL_RRATE: 0x003F ................................................................................ 55

4.1.23 RESET: 0x0041 .................................................................................................. 55

4.1.24 ACCUM_RESET: 0x004B....................................................................................... 55

4.1.25 GAUGING_STATUS: 0x0056 .................................................................................. 56

4.1.26 ManufacturingStatus(): 0x57.................................................................................... 56

4.1.27 ALERT_SET: 0x0068............................................................................................ 57

4.1.28 ALERT_RESET: 0x0069 ........................................................................................ 57

4.1.29 EDV_Threshold: 0x0073 ........................................................................................ 57

4.1.30 EXIT_ CAL: 0x0080.............................................................................................. 57

4.1.31 ENTER_CAL: 0x0081 ........................................................................................... 57

4.1.32 ENTER_CFG_UPDATE: 0x0090............................................................................... 57

4.1.33 EXIT_CFG_UPDATE_REINIT: 0x0091 ....................................................................... 57

4.1.34 EXIT_CFG_UPDATE: 0x0092.................................................................................. 57

4.2 Temperature(): 0x06 and 0x07 ........................................................................................... 57

4

Contents

Copyright © 2018, Texas Instruments Incorporated

SLUUBE8–September 2018

Submit Documentation Feedback

Page 5

www.ti.com

4.3 Voltage(): 0x08 and 0x09 ................................................................................................. 58

4.4 BatteryStatus(): 0x0A and 0x0B.......................................................................................... 58

4.5 Current(): 0x0C and 0x0D................................................................................................. 58

4.6 RemainingCapacity(): 0x10 and 0x11 ................................................................................... 58

4.7 FullChargeCapacity(): 0x12 and 0x13................................................................................... 58

4.8 AverageCurrent(): 0x14 and 0x15........................................................................................ 59

4.9 AverageTimeToEmpty(): 0x16 and 0x17................................................................................ 59

4.10 AverageTimeToFull(): 0x18 and 0x19................................................................................... 59

4.11 AccumulatedCharge(): 0x1A and 0x1B.................................................................................. 59

4.12 AccumulatedChargeTime(): 0x1C and 0x1D ........................................................................... 59

4.13 LastAccumulatedCharge(): 0x1E and 0x1F............................................................................. 59

4.14 LastAccumulatedChargeTime(): 0x20 and 0x21....................................................................... 60

4.15 AveragePower(): 0x24 and 0x25......................................................................................... 60

4.16 InternalTemperature(): 0x28 and 0x29 .................................................................................. 60

4.17 CycleCount(): 0x2A and 0x2B............................................................................................ 60

4.18 RelativeStateOfCharge(): 0x2C and 0x2D.............................................................................. 60

4.19 StateOfHealth(): 0x2E and 0x2F ......................................................................................... 60

4.20 ChargingVoltage(): 0x30 and 0x31 ...................................................................................... 60

4.21 ChargingCurrent(): 0x32 and 0x33....................................................................................... 60

4.22 BLTDischargeSet(): 0x34 and 0x35 ..................................................................................... 60

4.23 BLTChargeSet(): 0x36 and 0x37......................................................................................... 60

4.24 OperationStatus(): 0x3A and 0x3B ...................................................................................... 61

4.25 DesignCapacity(): 0x3C and 0x3D....................................................................................... 61

4.26 ManufacturerAccessControl(): 0x3E and 0x3F......................................................................... 61

4.27 MACData(): 0x40 through 0x5F .......................................................................................... 61

4.28 MACDataSum(): 0x60 ..................................................................................................... 61

4.29 MACDataLen(): 0x61 ...................................................................................................... 62

4.30 EOSLearnStatus(): 0x64 and 0x65 ...................................................................................... 62

4.31 EOSSafetySatus(): 0x66 and 0x67 ...................................................................................... 64

4.32 EOSStatus(): 0x68 ......................................................................................................... 65

4.33 AnalogCount(): 0x79....................................................................................................... 66

4.34 RawCurrent(): 0x7A and 0x7B............................................................................................ 66

4.35 RawVoltage(): 0x7C and 0x7D ........................................................................................... 66

4.36 RawIntTemp(): 0x7E and 0x7F........................................................................................... 66

4.37 RawExtTemp(): 0x80 and 0x81 .......................................................................................... 66

5 Data Memory Interface ........................................................................................................ 67

5.1 Accessing the Data Memory.............................................................................................. 67

5.2 Device Access Modes ..................................................................................................... 67

5.3 Sealing and Unsealing Data Memory Access .......................................................................... 67

6 Data Memory Summary....................................................................................................... 68

7 Application Example........................................................................................................... 81

7.1 Data Memory Parameter Update Example ............................................................................. 81

7.2 GAUGEPARCAL ........................................................................................................... 82

Revision History.......................................................................................................................... 83

SLUUBE8–September 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Contents

5

Page 6

This manual discusses the modules and peripherals of the automotive-qualified AEC-Q100, Grade 3

bq34210-Q1 fuel gauge, and how each is used to build a complete battery pack fuel gauge solution. For

further information, refer to the bq34210-Q1 Automotive 1-Series Cell System-Side CEDV Fuel Gauge for

Rarely Discharged Batteries Data Sheet (SLUSCG1).

Formatting in This Document

The following formatting convention is used in this document:

• SBS commands: italics with parentheses and no breaking spaces; for example, RemainingCapacity()

• Data memory: italics, bold, and breaking spaces; for example, Design Capacity

• Register bits and flags: italics and brackets; for example, [TDA]

• Data memory bits: italics and bold; for example, [LED1]

• Modes and states: ALL CAPITALS; for example, UNSEALED

Trademarks

MathCAD is a trademark of MathSoft, Inc.

All other trademarks are the property of their respective owners.

Read This First

SLUUBE8–September 2018

Preface

Glossary

http://www.ti.com provides a Battery Glossary on the Battery Management FAQ page and the TI Glossary.

Related Documentation from Texas Instruments

To obtain a copy of any of the following TI documents, click on the links below:

1. bq34210-Q1 Automotive 1-Series Cell System-Side CEDV Fuel Gauge for Rarely Discharged Batteries

Data Sheet (SLUSCG1)

2. Going to Production with the bq275xx Application Report (SLUA449)

3. Host System Calibration Method Application Report (SLUA640)

For more documentation and product information, go to the bq34210-Q1 product page or to the TI Web

site at www.ti.com.

6

Preface

Copyright © 2018, Texas Instruments Incorporated

SLUUBE8–September 2018

Submit Documentation Feedback

Page 7

Chapter 1

SLUUBE8–September 2018

General Description

The bq34210-Q1 fuel gauge incorporates gas gauging and an End-of-Service (EOS) Determination

function to use with a 1-series Li-Ion or Lithium Iron Phosphate (LiFePO4) rechargeable cell or a Nickel

metal hydride (NiMH) based pack with a configuration of 3-series cells.

The gas gauge uses Compensated End-of-Discharge Voltage (CEDV) gauging technology to accurately

predict the battery capacity and other operational characteristics of the battery. It can be interrogated by a

system processor to provide cell information, such as remaining capacity, full charge capacity (FCC), timeto-empty (TTE), and relative state-of-charge (RSOC), and provide an interrupt signal to the processor.

The integrated EOS Determination function is specifically intended for applications where the battery is

rarely discharged, such as eCall systems, uninterruptible power supplies (UPS), enterprise server backup

systems, and telematics or telecommunications backup modules. In such systems, the battery may remain

in a fully (or near fully) charged state for much of its lifetime, with it rarely or never undergoing a significant

discharge. If the health of the battery in such a system is not monitored regularly, then it may degrade

beyond the level required for a system backup/discharge event, and thus fail precisely at the time when it

is needed most. Monitoring the battery enables the system to take action before the failure occurs.

The EOS Determination function monitors the health of the battery by using infrequent learning phases,

which involve a controlled discharge of ~1% capacity, and provides an alert to the system when the

battery is approaching the end of its usable service. By coordinating battery charging with the learning

phases, the battery capacity available to the system can be maintained above a preselected level to avoid

compromising the ability for the battery to support a system discharge event.

Information is accessed through a series of commands, called Data Commands, and indicated by the

general format Command(). Read and write information within the device control and status registers, as

well as its data memory locations are accessed through these commands. Commands are sent from the

system to the gauge using the I2C serial communications engine, and can be run during application

development, system manufacturing, or end-equipment operation.

The fuel gauge measures charge and discharge activity by monitoring the voltage across a small-value

series sense resistor (5 mΩ to 20 mΩ, typical), which may be used in a low-side (at the CELL- connection)

or a high-side (at the CELL+ connection) configuration.

The external temperature sensing is optimized with the use of a high-accuracy negative temperature

coefficient (NTC) thermistor with 25°C resistance (R25) = 10.0 kΩ ±1% and beta value (B25/85, resistance

at 25°C and at 85°C) = 3435 kΩ ± 1% (such as Semitec NTC 103AT). Alternatively, the fuel gauge can be

configured to use its internal temperature sensor or receive temperature data from the host processor.

The fuel gauge uses temperature to monitor the battery-pack environment, which is used for gas gauging

and cell protection functionality.

To minimize power consumption, the fuel gauge has several power modes: INITIALIZATION, NORMAL,

SLEEP, and SHUTDOWN. The fuel gauge passes automatically between these modes (except for

SHUTDOWN exit, which needs an external stimulus), depending upon the occurrence of specific events,

though a system processor can initiate some of these modes directly. The device also includes a CONFIG

UPDATE mode, which is generally used during initial setup to update various RAM-based parameters

used by the gauge.

1.1 Gas Gauging

The bq34210-Q1 device features the Compensated End-of-Discharge Voltage (CEDV) gauging algorithm,

capable of gauging a maximum capacity of 32 Ah.

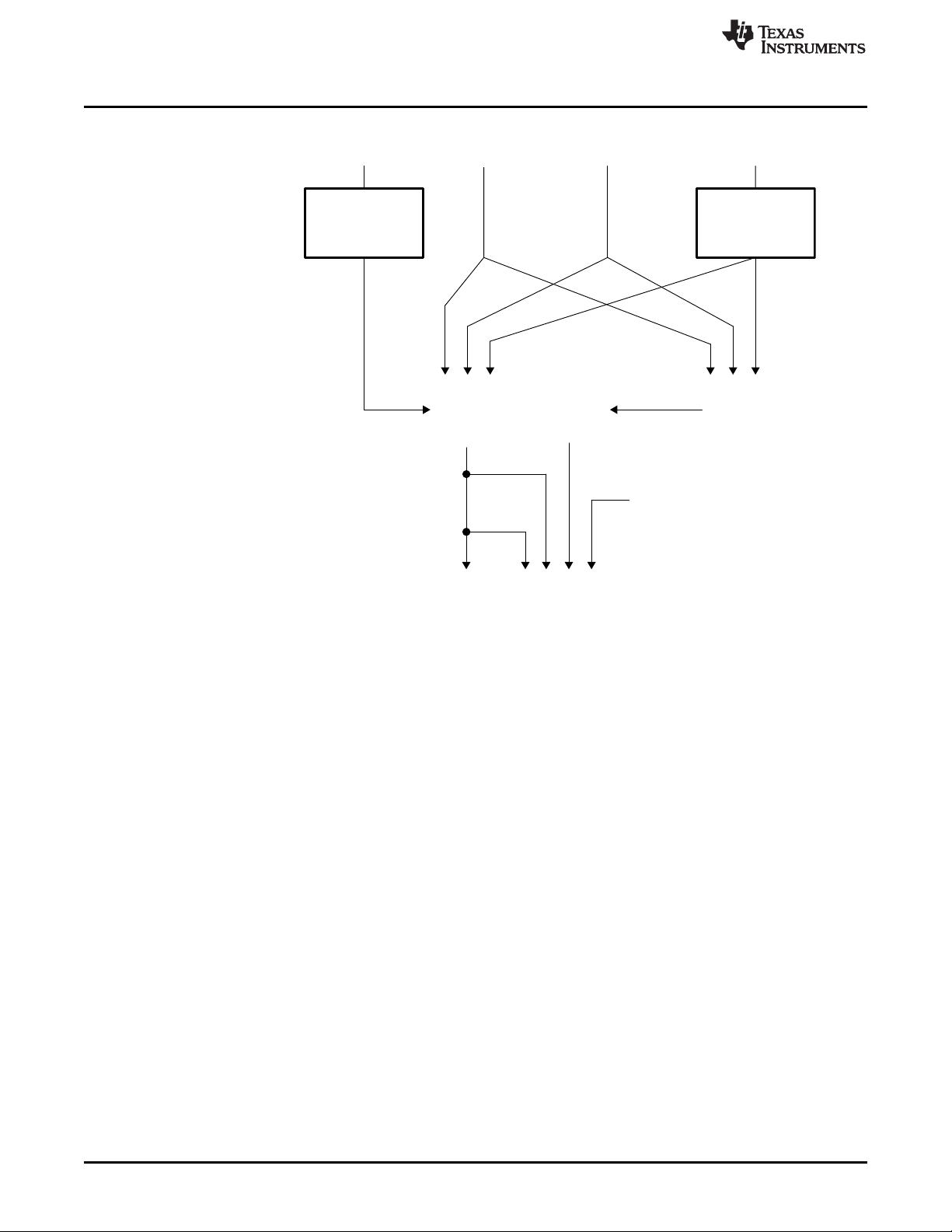

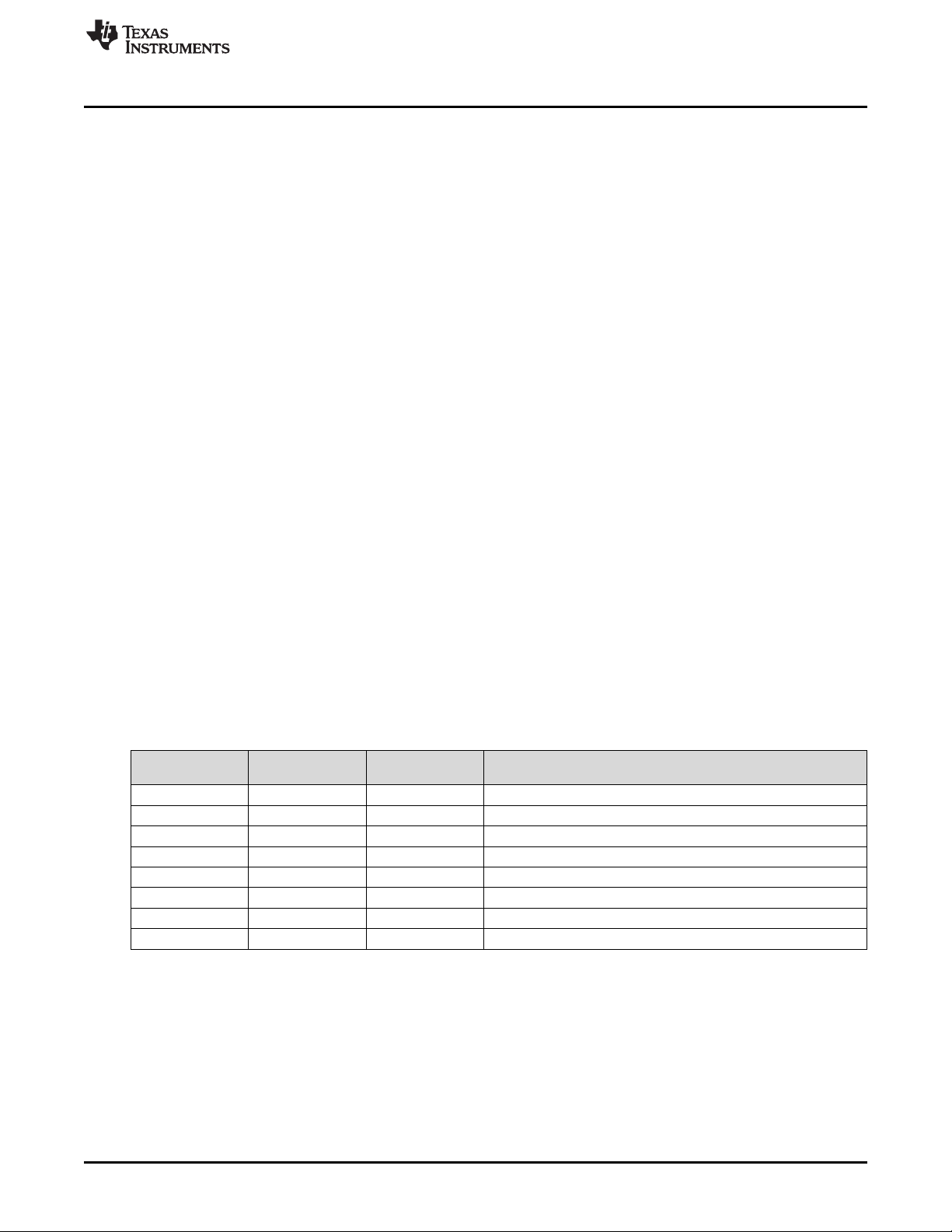

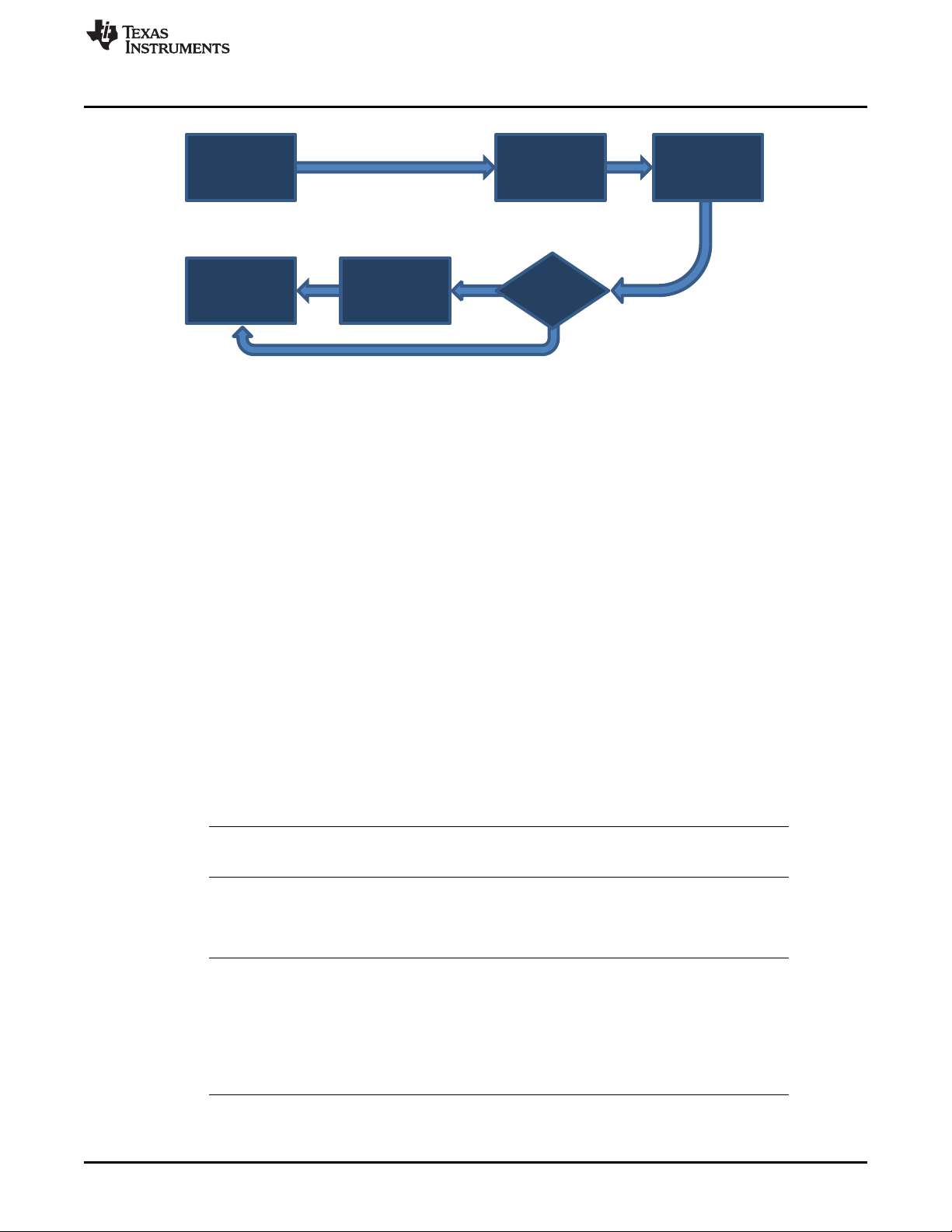

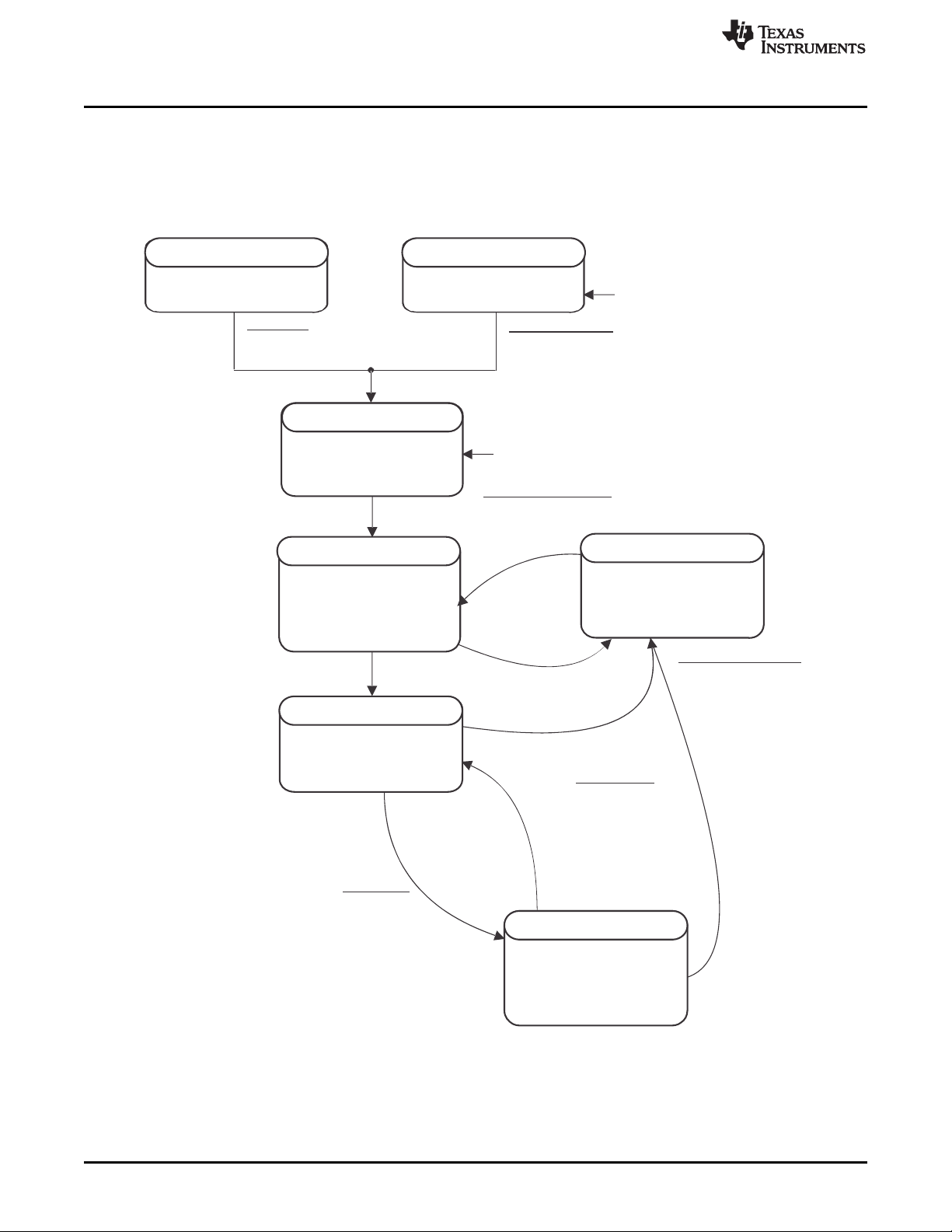

Figure 1-1 shows the operational overview of the bq34210-Q1 fuel gauge.

SLUUBE8–September 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

General Description

7

Page 8

Charge

Efficiency

Compensation

Charge

Current

+

Inputs

Remaining

Capacity

(RC)

Discharge

Current

Temperature

Compensation

Self-Discharge

Timer

– –

≤

+

Full

Charge

Capacity

(FCC)

Discharge

Count

Register

(DCR)

Qualified

Transfer

Temperature, Other Data

Main Counters and

Capacity Reference (FCC)

Outputs

Chip-Controlled

Available Charge

LED Display

Two-Wire

Serial Port

– ++

Battery Electronics

Load Estimate

Gas Gauging

www.ti.com

1.1.1 CEDV Gas Gauging Operational Overview

The bq34210-Q1 device accumulates the measured quantities of charge and discharge and estimates

self-discharge of the battery. The bq34210-Q1 device compensates the charge current measurement for

temperature and the state-of-charge of the battery. The device also adjusts the self-discharge estimation

based on temperature. The initial battery state-of-charge estimation on first insertion of the battery pack in

the system may display a factor of the true value; the system must go through a full charge and then a full

discharge cycle before the correct full-charge capacity (FCC) is estimated.

The main charge counter, RemainingCapacity() (RC) register, represents the available capacity or energy

in the battery at any given time. The bq34210-Q1 device adjusts RC for charge, self-discharge, and other

compensation factors. The information in the RC register is accessible through the I2C interface. The

FullChargeCapacity() (FCC) register represents the initial or last measured full discharge of the battery. It

is used as the battery full-charge reference for relative capacity indication. FCC is accessible through the

I2C interface.

1.1.2 Main Fuel Gauge Registers

Remaining Capacity (RC) — Remaining capacity in the battery

Figure 1-1. bq34210-Q1 CEDV Gas Gauging Operational Overview

RC represents the remaining capacity in the battery. The bq34210-Q1 device computes RC in units

of mAh.

RC counts up during charge to a maximum value of FCC and down during discharge and selfdischarge to a minimum of 0. In addition to charge and self-discharge compensation, the bq34210Q1 device calibrates RC at three low-battery-voltage thresholds, EDV2, EDV1, and EDV0. This

provides a voltage-based calibration to the RC counter.

8

Design Capacity (DC) — User-specified battery full capacity

General Description

Copyright © 2018, Texas Instruments Incorporated

SLUUBE8–September 2018

Submit Documentation Feedback

Page 9

www.ti.com

DC is the user-specified battery full capacity. It is calculated from Design Capacity mAh and is

represented in units of mAh. It also represents the full-battery reference for the absolute display

mode.

Full Charge Capacity (FCC) — Last measured discharge capacity of the battery

FCC is the last measured discharge capacity of the battery. It is represented in units of mAh. On

initialization, the bq34210-Q1 device sets FullChargeCapacity() to the data memory value stored in

Full Charge Capacity (FCC). During subsequent discharges, the bq34210-Q1 device updates

FullChargeCapacity() with the last measured discharge capacity of the battery. Once updated, the

bq34210-Q1 device writes the new FullChargeCapacity() value to data memory in mAh to Learned

Full Charge Capacity. FullChargeCapacity() represents the full battery reference for the relative

display mode and relative state-of-charge calculations.

1.1.3 Capacity Learning (FCC Update)

An FCC update occurs if the battery discharges from RC ≥ FCC – Near Full to the EDV2 voltage

threshold with the following conditions:

• No valid charge activity occurs during the discharge period. A valid charge is defined as a charge of

10 mAh into the battery.

• No more than 256 mAh of self-discharge or battery load estimation occurs during the discharge period.

• The temperature does not drop below the low temperature thresholds programmed in Low Temp

during the discharge period.

• The battery voltage reaches the EDV2 threshold during the discharge period and the voltage is greater

than or equal to the EDV2 threshold minus 256 mV when the bq34210-Q1 device detected EDV2.

• Current remains ≥ 3C/32 when EDV2 is reached.

• No overload condition exists when EDV2 threshold is reached or if RC has dropped to

Battery Low % × FCC.

The bq34210-Q1 device sets [VDQ] = 1 in OperationStatus() when a discharge begins. The bq34210-Q1

device sets [VDQ] = 0 if any disqualifying condition occurs. One complication may arise regarding the

state of [VDQ] if [CSYNC] is set in CEDV Gauging Configuration. When [CSYNC] is enabled,

RemainingCapacity() is written to equal FullChargeCapacity() on valid primary charge termination. This

capacity synchronization is done even if the condition RC ≥ FCC – Near Full is not satisfied at charge

termination.

FCC cannot be reduced by more than 256 mAh or increased by more than 512 mAh during any single

update cycle. If [FCC_LIMIT] is set in CEDV Gauging Configuration, then FCC cannot learn above the

Design Capacity mAh. The bq34210-Q1 device saves the new FCC value to the data memory within 4 s

of being updated.

Gas Gauging

1.1.4 End-of-Discharge (EDV) Thresholds and Capacity Correction

The bq34210-Q1 device monitors the battery for three low-voltage thresholds: EDV0, EDV1, and EDV2.

If the [EDV_CMP] bit in CEDV Gauging Configuration is clear, fixed EDV thresholds may be

programmed in Fixed EDV0, Fixed EDV1, and Fixed EDV2 in mV.

If the [EDV_CMP] bit in CEDV Gauging Configuration is set, automatic EDV compensation is enabled

and the bq34210-Q1 device computes the EDV0, EDV1, and EDV2 thresholds based on values stored in

the selected CEDV profile in data memory and the battery's current discharge rate and temperature. If the

[FIXED_EDV0] bit in CEDV Gauging Configuration is also set, then the EDV0 threshold will be set to the

programmed Fixed EDV0, and the EDV1 and EDV2 compensated thresholds will not go below the

programmed Fixed EDV0.

The bq34210-Q1 device disables EDV detection if current exceeds the Overload Current threshold. The

bq34210-Q1 device resumes EDV threshold detection after current drops below the Overload Current

threshold. Any EDV threshold detected is reset after charge is applied and [VDQ] is cleared after 10 mAh

of charge.

The bq34210-Q1 device uses the EDV thresholds to apply voltage-based corrections to the RC register

(see Table 1-1).

SLUUBE8–September 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

General Description

9

Page 10

Gas Gauging

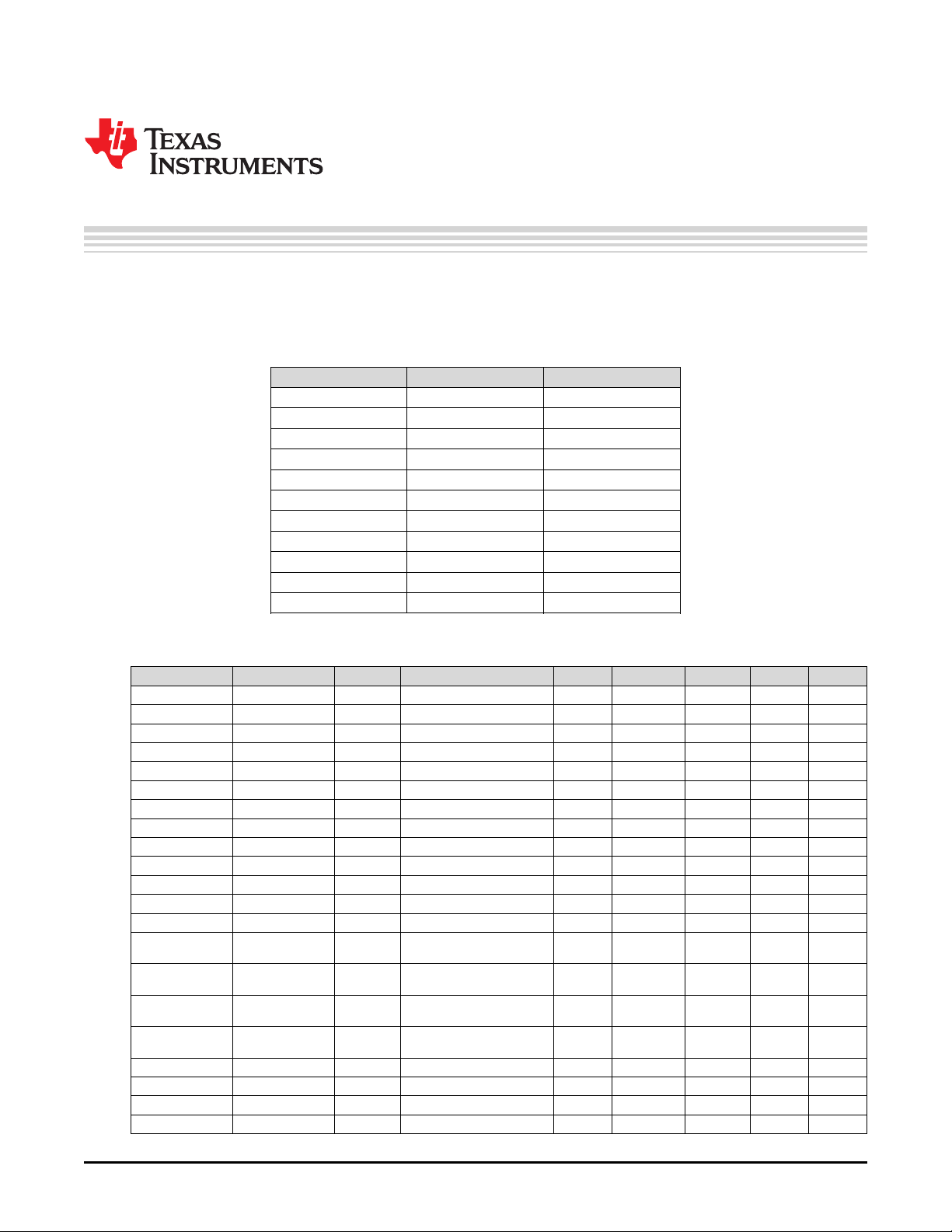

Table 1-1. State-of-Charge Based on Low Battery

Voltage

THRESHOLD RELATIVE STATE OF CHARGE

EDV0 0%

EDV1 3%

EDV2 Battery Low %

The bq34210-Q1 device performs EDV-based RC adjustments with current ≥ C/32. No EDVs are set if

current < C/32. The bq34210-Q1 device adjusts RC as it detects each threshold. If the voltage threshold is

reached before the corresponding capacity on discharge, the bq34210-Q1 device reduces RC to the

appropriate amount, as shown in Table 1-1.

If an RC % level is reached on discharge before the voltage reaches the corresponding threshold, then

RC is held at that % level until the threshold is reached. RC is only held if [VDQ] = 1, indicating a valid

learning cycle is in progress. If Battery Low % is set to 0, EDV1 and EDV0 corrections are disabled.

1.1.5 EDV Discharge Rate and Temperature Compensation

If EDV compensation is enabled, the bq34210-Q1 device calculates battery voltage to determine EDV0,

EDV1, and EDV2 thresholds as a function of battery capacity, temperature, and discharge load. The

general equation for EDV0, EDV1, and EDV2 calculation is as follows:

EDV0,1,2 = n (EMF × FBL – |I

• EMF is a no-load cell voltage higher than the highest cell EDV threshold computed. EMF is

programmed in mV in the CEDV profile EMF.

• I

is the current discharge load magnitude.

LOAD

• n = the number of series cells. In the bq34210-Q1 case, n = 1.

• FBL is the factor that adjusts the EDV voltage for battery capacity and temperature to match the noload characteristics of the battery.

FBL = f (C0, C + C1, T) (2)

• C (either 0%, 3%, or Battery Low % for EDV0, EDV1, and EDV2, respectively) and C0 are the

capacity-related EDV adjustment factors. C0 is programmed in the CEDV profile C0. C1 is the desired

residual battery capacity remaining at EDV0 (RC = 0). The C1 factor is stored in the CEDV profile C1.

• T is the current temperature in °K.

• R0 × FTZ represents the resistance of a cell as a function of temperature and capacity.

FTZ = f (R1, T0, C + C1, TC) (3)

• R0 is the first order rate dependency factor stored in the CEDV profile R0.

• T is the current temperature; C is the battery capacity relating to EDV0, EDV1, and EDV2.

• R1 adjusts the variation of impedance with battery capacity. R1 is programmed in the CEDV profile R1.

• T0 adjusts the variation of impedance with battery temperature. T0 is programmed in the CEDV profile

T0.

• TC adjusts the variation of impedance for cold temperatures (T < 23°C). TC is programmed in the

CEDV profile TC.

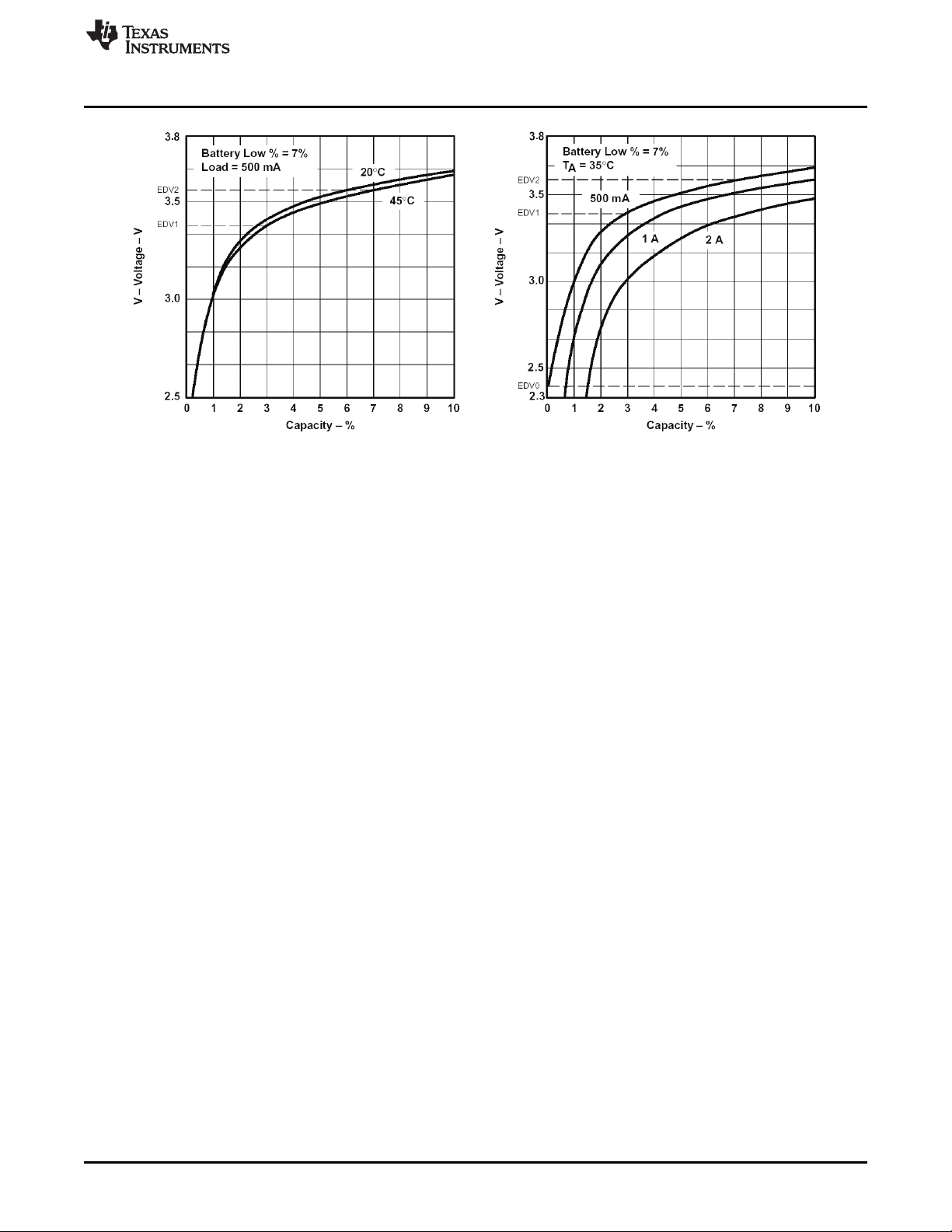

The graphs below show the calculated EDV0, EDV1, and EDV2 thresholds versus capacity using the

typical compensation values for different temperatures and loads for a Li-Ion 18650 cell. The

compensation values vary widely for different cell types and manufacturers and must be matched exactly

to the unique characteristics for optimal performance.

| × R0 × FTZ) (1)

LOAD

www.ti.com

10

General Description

Copyright © 2018, Texas Instruments Incorporated

SLUUBE8–September 2018

Submit Documentation Feedback

Page 11

www.ti.com

Gas Gauging

Figure 1-2. (a) EDV Calculations vs Capacity for Various Temperatures, (b) EDV Calculations vs Capacity

for Various Loads

1.1.6 EDV Age Factor

The EDV Age Factor enables the bq34210-Q1 device to correct the EDV detection algorithm to

compensate for cell aging. This parameter scales cell impedances as the cycle count increases. This new

factor is used to accommodate for much higher impedances observed in larger capacity and/or aged cells.

For most applications, the default value of 0 is sufficient; however, for some very specific applications, this

new aging factor may be required. In those cases, experimental data must be taken at the 0, 100, 200,

and 300 cycle-read points using a typical discharge rate while at ambient temperature. Entering this data

into a TI provided MathCAD™ program will yield the appropriate EDV Age factor value. Contact TI

Applications Support @ http://www-k.ext.ti.com/sc/technical-support/email-tech-support.asp?AAP for more

detailed information.

1.1.7 Self-Discharge

The bq34210-Q1 device estimates the self-discharge of the battery to maintain an accurate measure of

the battery capacity during periods of inactivity. The bq34210-Q1 device makes self-discharge

adjustments to RC every 1/4 second when awake and periodically when in SLEEP mode. The period is

determined by Sleep Current Time.

The nominal self-discharge rate, %PERDAY (% per day), is programmed in an 8-bit value Self-Discharge

Rate by the following relation:

Self-Discharge Rate = %PERDAY/0.0025

1.1.8 Battery Electronic Load Compensation

The bq34210-Q1 device can be configured to compensate for a constant load (as from battery electronics)

present in the battery pack at all times. The bq34210-Q1 device applies the compensation continuously

when the charge or discharge is below the digital filter. The bq34210-Q1 device applies the compensation

in addition to self-discharge. The compensation occurs at a rate determined by the value stored in

Electronics Load. The compensation range is 0 μA–765 μA in steps of approximately 3 µA.

The amount of internal battery electronics load estimate in μA, BEL, is stored as follows:

Electronics Load = BEL/3

SLUUBE8–September 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

General Description

11

Page 12

QuitCurrent

(–)QuitCurrent

Current

Time

RelaxationMode ChargeMode DischargeModeRelaxationMode ChargeMode DischargeMode RelaxationMode

ChgRelaxTime

DsgRelaxTime

1 10 1 1 10[DSG]

Gas Gauging

1.1.9 Initial Battery Capacity at Device Reset

The bq34210-Q1 device estimates the initial capacity of a battery pack at device reset, which is the case

when battery cells are first attached to the application circuit. The initial FullChargeCapacity() (FCC) is a

direct copy of the ROM CEDV profile parameter Full Charge Capacity. The initial RC and RSOC are

estimated using the open-circuit voltage (OCV) characteristics of the programmed Li-Ion (LiFePO4 or

NiMH) chemistry, DOD at EDV2, and Design Capacity (maximum chemical capacity). This gives a

reasonably accurate RC and RSOC; however, battery capacity learning is required in order to find the

accurate FCC, RC, and RSOC. During battery capacity learning, learned Full Charge Capacity, and DOD

at EDV2 will be learned and updated.

The determined value of remaining capacity can be further scaled, if needed, through the value of

RemCap Init Percent. Upon a reset, the final value of RemainingCapacity() is initialized from the

RemCap Init Percent value of the initial value correlated to the battery voltage table.

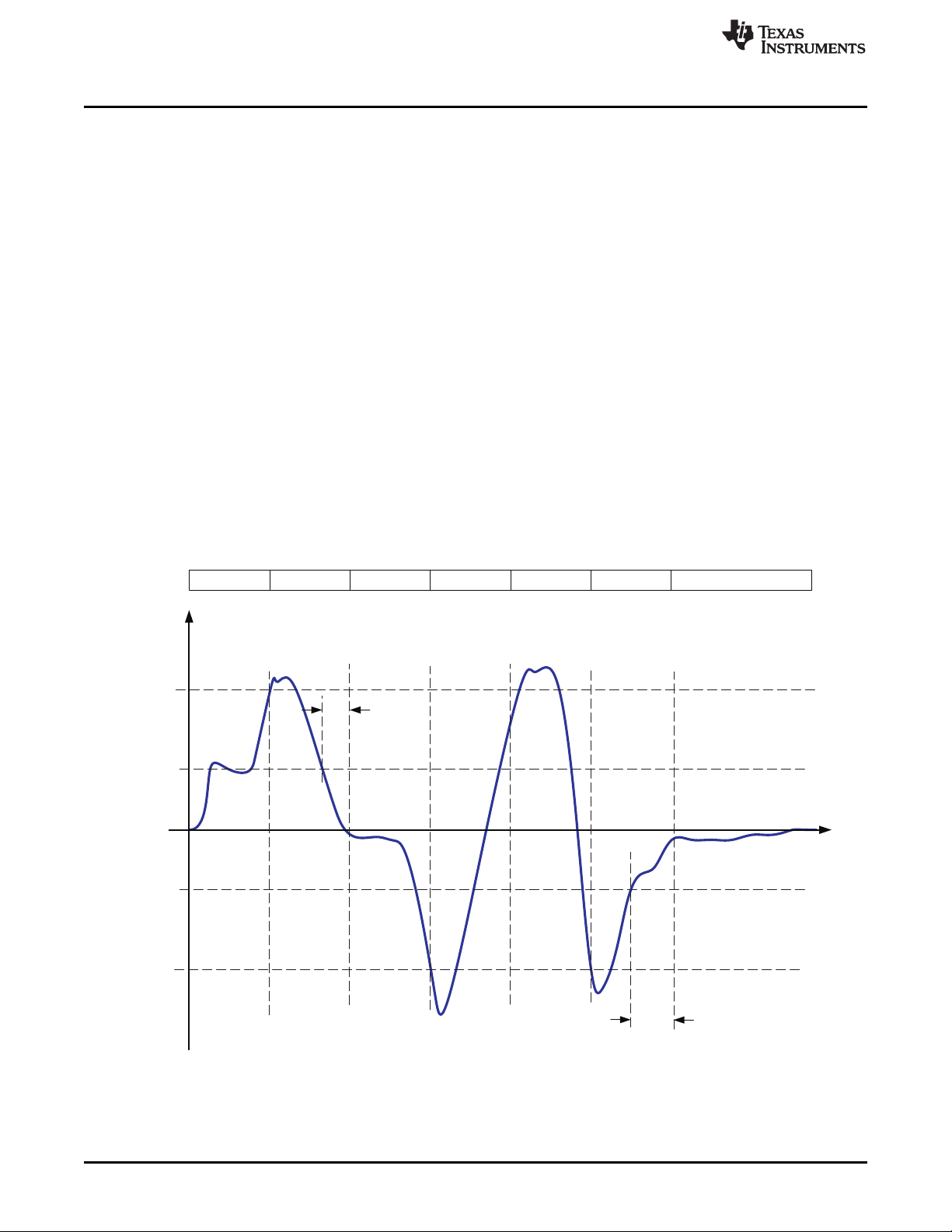

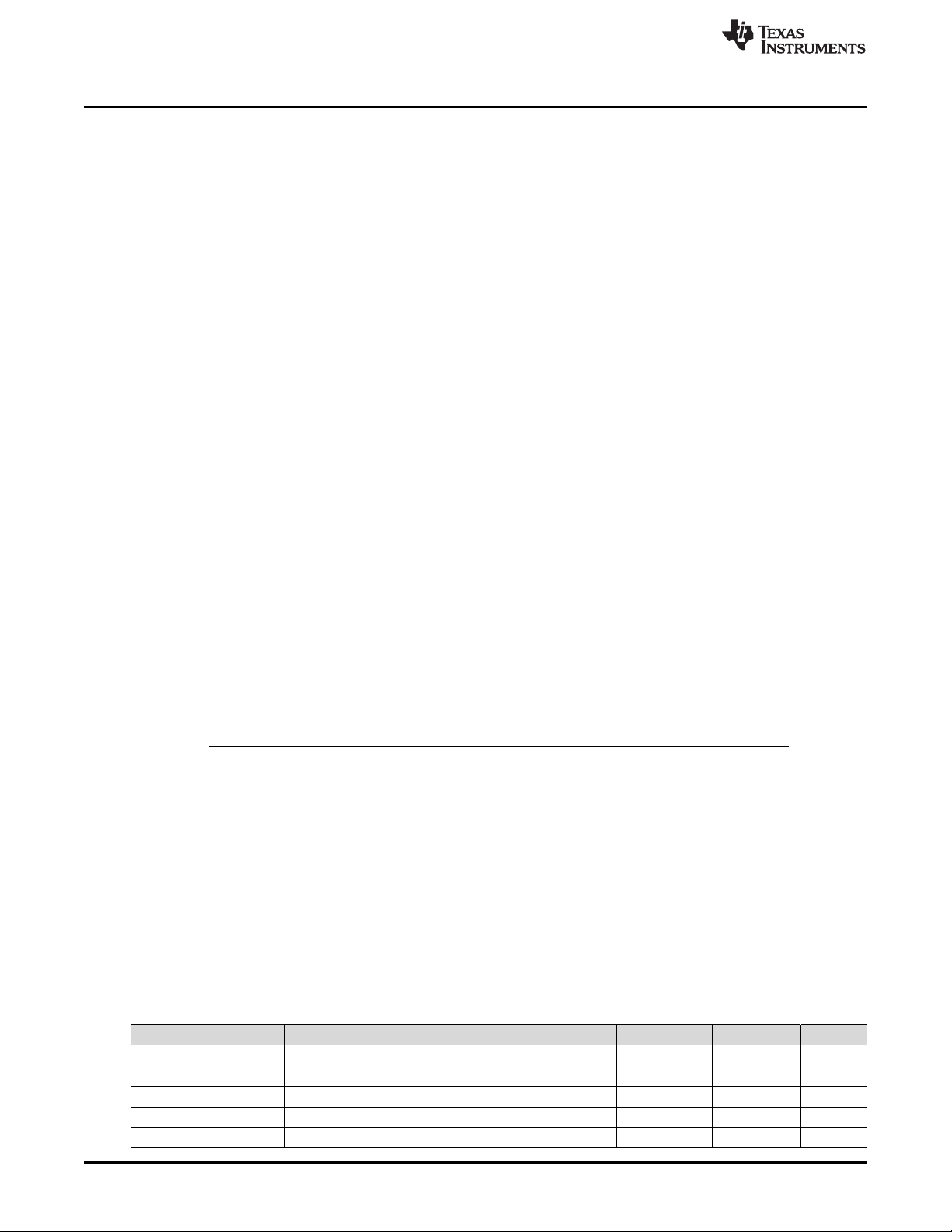

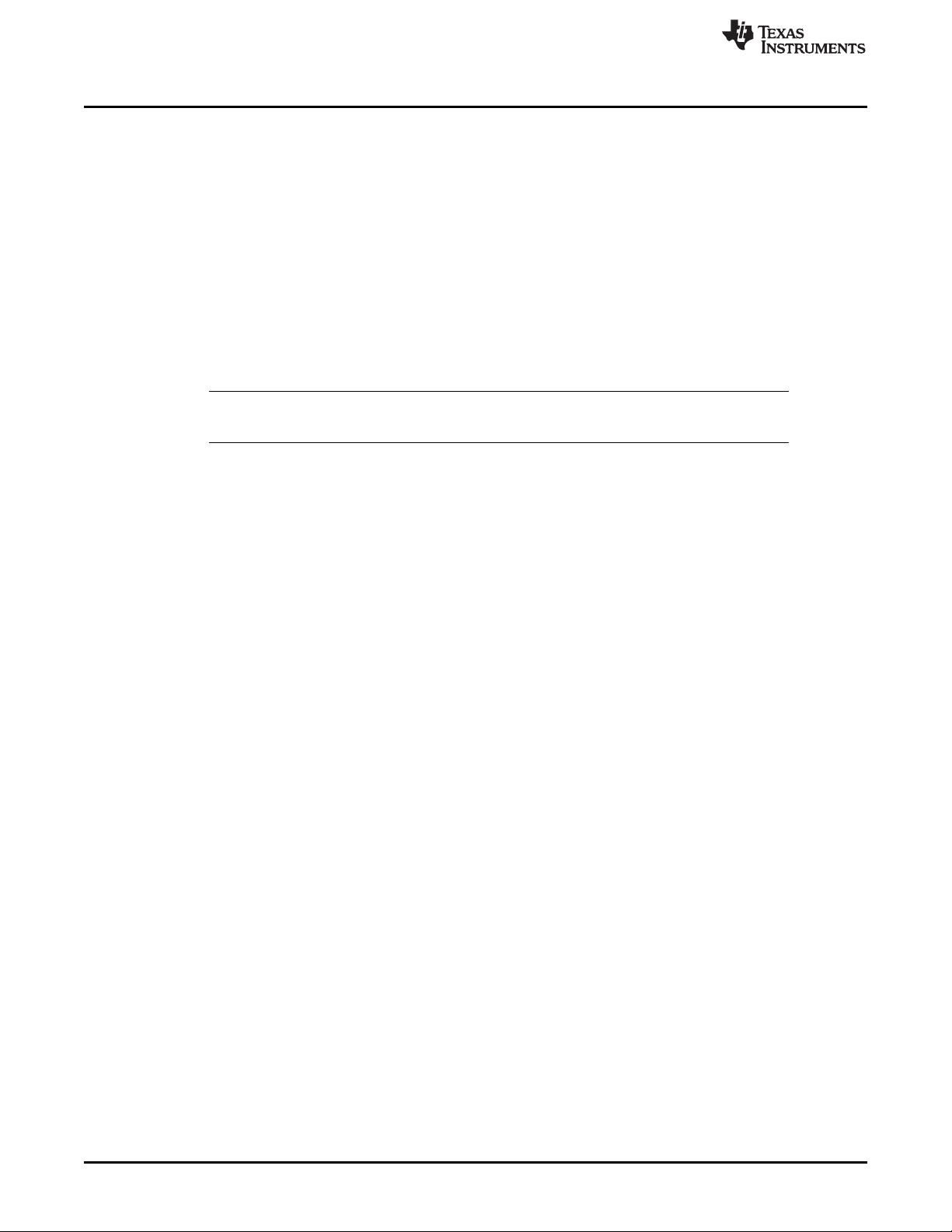

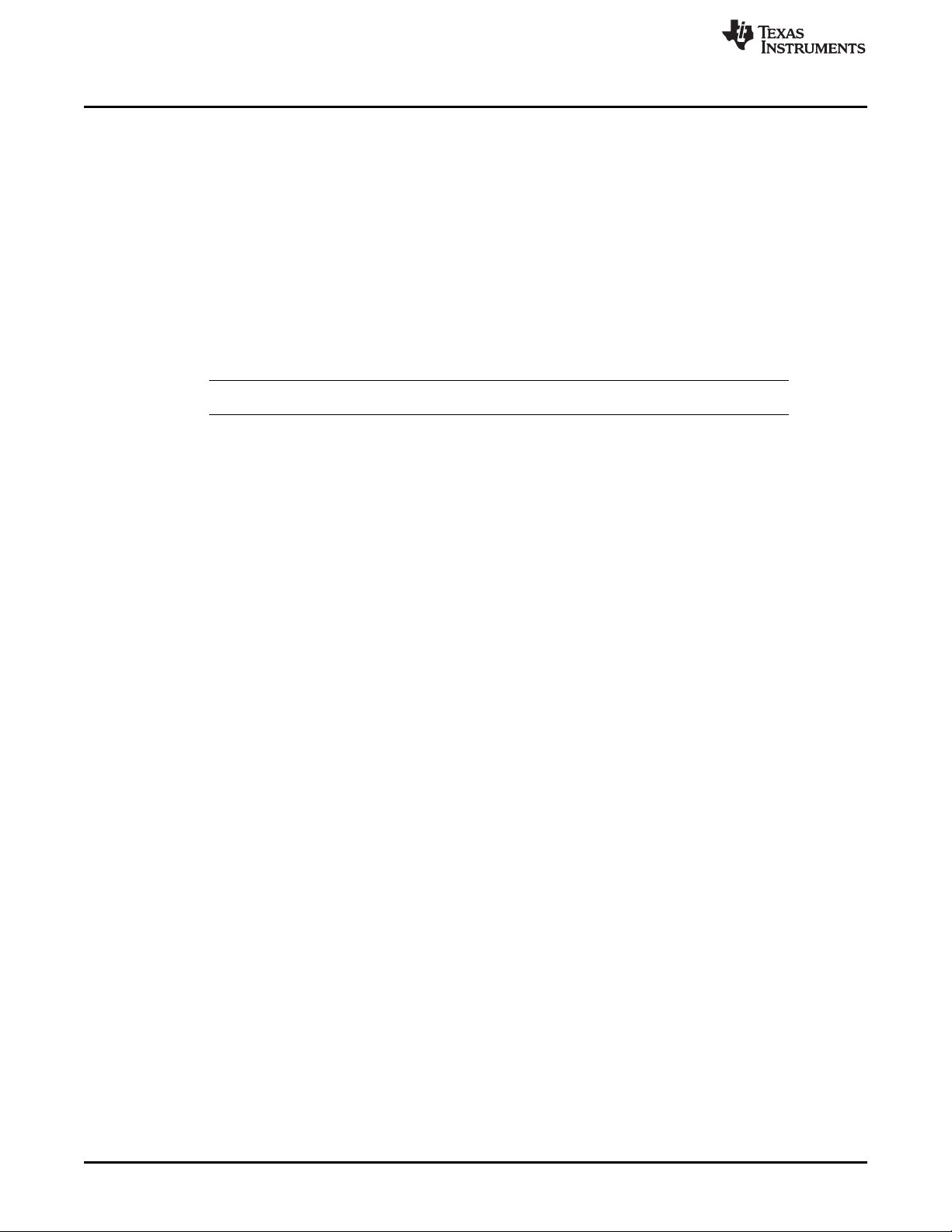

1.1.10 Fuel Gauge Operating Modes

Entry and exit of each mode is controlled by data memory parameters in the Current Thresholds

subclass. The [DSG] flag referenced below is from the MAC GaugingStatus() subcommand and is set in

RELAXATION and DISCHARGE modes. The [DSG] flag in BatteryStatus() is slightly different—it sets only

in DISCHARGE mode and not in RELAXATION mode.

CHARGE mode is exited and RELAXATION mode is entered when Current() goes below Quit Current for

a period of Charge Relax Time. DISCHARGE mode is entered when Current() goes below

(–)Dsg Current Threshold. DISCHARGE mode is exited and RELAXATION mode is entered when

Current() goes above (–)Quit Current threshold for a period of Discharge Relax Time. CHARGE mode is

entered when Current() goes above Chg Current Threshold.

www.ti.com

Figure 1-3. Fuel Gauge Operating Mode Example

12

General Description

Copyright © 2018, Texas Instruments Incorporated

SLUUBE8–September 2018

Submit Documentation Feedback

Page 13

www.ti.com

1.1.11 CEDV Smoothing

The bq34210-Q1 device has the ability to smooth the RemainingCapacity() during discharge in order to

avoid a drop in RelativeStateOfCharge() when the EDV thresholds are reached. This feature is enabled by

setting the Smoothing Config [SMEN] = 1 and configuring the Smoothing Start Voltage and

Smoothing Delta Voltage.

The smoothing will activate only when all of the following conditions are true:

• Current() < 0

• Voltage() < Smoothing Start Voltage

• EDV2 has been reached ([EDV2] = 1) OR (Voltage() – present EDV2 threshold) < Smoothing Delta

Voltage.

• Maximum Voltage() during the previous one minute is less than the maximum Voltage() during the

current minute (that is, "drop rate" is greater than 0).

• RemainingCapacity() is greater than the capacity at the next EDV point.

While smoothing is active, the "drop rate" is used to estimate the time to the EDV point under the

assumption that the rate is constant (linear). This information is then used to estimate how much current

would need to be applied in order to have RemainingCapacity() reach the expected capacity at the EDV

point. The actual Current() is then scaled by the "smoothing current." This will either speed up or slow

down the RemainingCapacity() accumulation to reach the EDV threshold at the correct time.

Whenever the RemainingCapacity() accumulation is actively scaled, the OperationStatus()[SMTH] bit will

be set.

Smoothing deactivates whenever an EDV threshold is reached until the rate to the next EDV threshold

can be calculated; however, smoothing past the EDV2 point only occurs if Smoothing Config [SMEXT] is

set to 1.

To improve smoothing at the end of discharge, the SME0 configuration bit provides additional flexibility.

This is particularly useful when FIXED_EDV0 is set and the calculated EDV2/EDV1 is lower than EDV0. In

this scenario, the State-of-Charge (SOC) smooths to EDV2, then to EDV1, and then to EDV0, leading to

SOC jumps. If the SME0 bit is set, then the SOC smooths directly to EDV0, leading to a smooth transition

to empty.

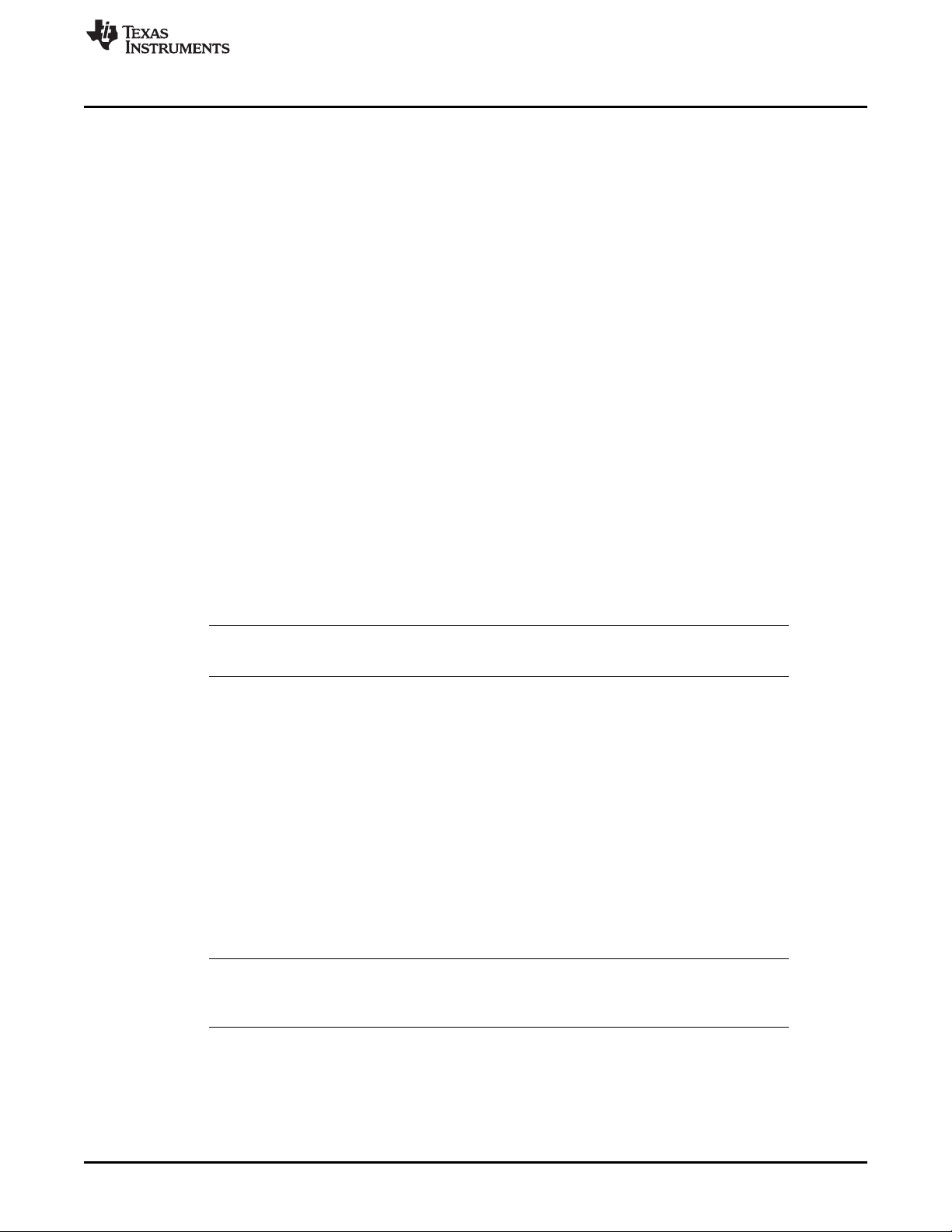

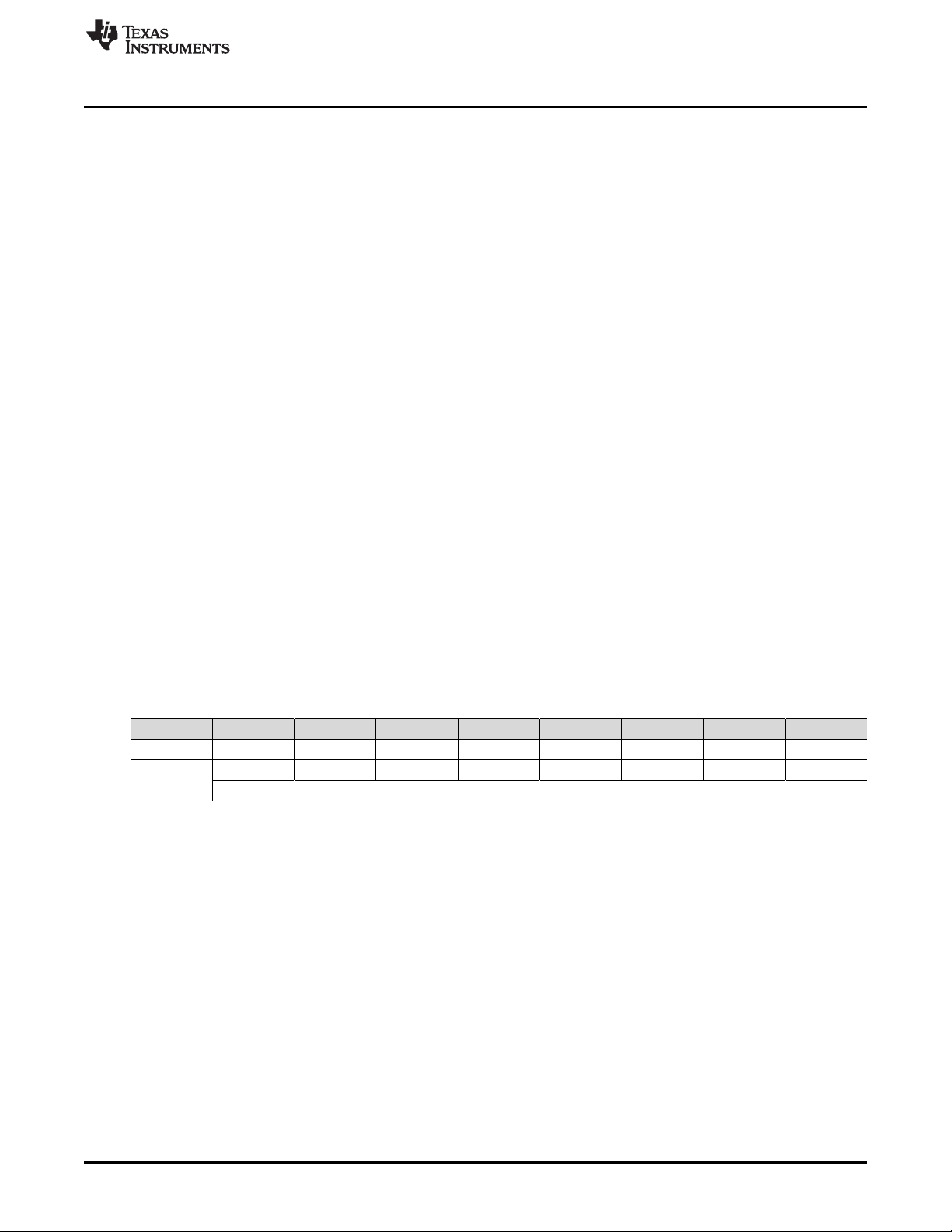

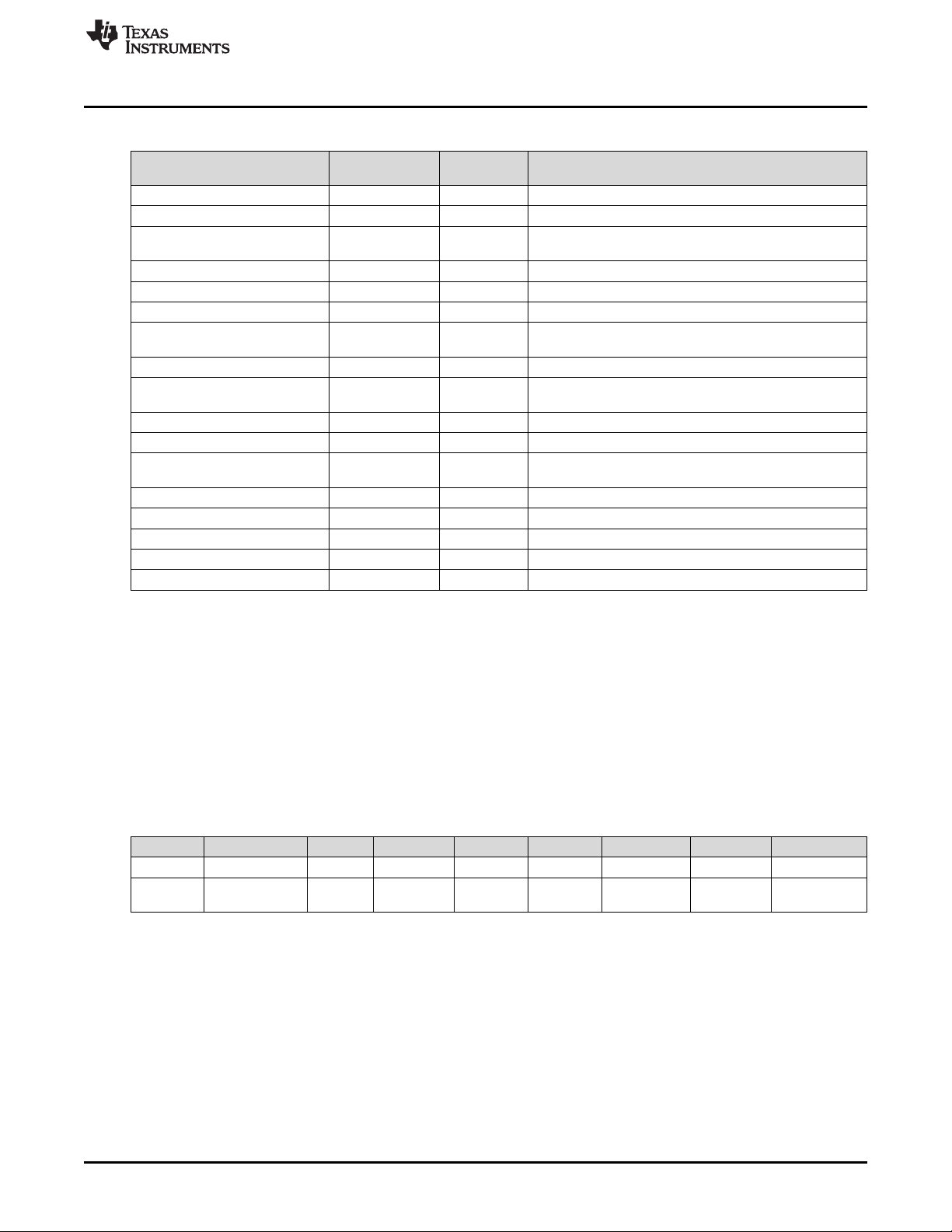

Table 1-2 shows the available smoothing configurations.

Gas Gauging

Smoothing Config

[SMEN]

0 0 0 No Smoothing

0 0 1 No Smoothing

0 1 0 No Smoothing

0 1 1 No Smoothing

1 0 0 Smoothing to EDV2

1 0 1 Smoothing to EDV0 if calculated EDV2/EDV1 is less than EDV0.

1 1 0 Smoothing to EDV2 ≥ EDV1 ≥ EDV0

1 1 1 Smoothing to EDV0 if calculated EDV2/EDV1 is less than EDV0.

Smoothing Config

The bq34210-Q1 device can also add smoothing during charging. In situations when the FCC is not

updated during a discharge cycle or on a subsequent charge cycle, if the valid charge termination is

reached, RSOC is synced to 100% regardless of the true RSOC. To help in scenarios like these, the

device enables the SMOOTHEOC_EN bit (default is enabled). When enabled, the RSOC value is

gradually increased to 100% instead of a sudden jump if the following are true:

a. Battery is charging.

b. Cell Voltage > Taper Voltage

c. Charge Current is decreasing AND is below the EOC Smooth Current threshold for EOC Smooth

Current Time.

SLUUBE8–September 2018

Submit Documentation Feedback

[SMEXT]

Table 1-2. Smoothing Configurations

CEDV Config

[SME0]

Copyright © 2018, Texas Instruments Incorporated

Description

General Description

13

Page 14

Accumulated Charge Measurement

1.2 Accumulated Charge Measurement

The bq34210-Q1 device integrates an Accumulated Charge function that measures the integrated

charge passed in or out of the cell since the integration is reset. This function can be used to generate an

alert to the host when a programmable threshold of Accumulated Charge is achieved.

The device also integrates the elapsed time since the integration began, assuming the timer was not

interrupted by a power cycle or put into SHUTDOWN mode. This time is read using the command

AccumulatedTime(). If an event has occurred that interrupted the timer, the value of AccumulatedTime()

will be fixed unchanging at 0 until the integration is reset.

The charge and time integration is reset at full charge termination or upon issue of the ACCUM_RESET

command. While the battery is discharging (that is, the measured Current() is negative), then the charge

integration counter increases. If the battery starts charging (that is, the measured Current() is positive),

then the charge integration counter decreases. The integrated charge value in mAh can be read by the

host using the command AccumulatedCharge(). The elapsed time (which does not decrease in value) is

read by issuing the AccumulatedTime() command.

The Accumulated Charge calculation uses the current measured across the sense resistor and, similar to

the coulomb counter integration, ignores currents below a programmed level controlled by CC Deadband.

In periods when the bq34210-Q1 device is in SLEEP mode, the Accumulated Charge integration

includes an estimate of the charge integrated based on analysis of the periodic measured current.

If the user prefers to include cell self-discharge in the integration, this capability can be enabled or

disabled using the [IGNORE_SD_EN] configuration bit.

The charge integration can also be limited to only include positive (charging) currents, only negative

(discharging) currents, or both, through setting the [ACCHG_EN] and [ACDSG_EN] configuration bits. If

both [ACCHG_EN] and [ACDSG_EN] are reset, then the timer is halted. These bits can be set using the

ACCUM_CHG_EN() and ACCUM_DSG_EN() commands.

When the cell is fully charged and the FC bit is set due to normal charge termination, then the integration

counter is again reset. At this point, the values of Accumulated Charge and time just before reset are

stored and can be read using LastAccumulatedCharge() and LastAccumulatedTime(). The values stored

in LastAccumulatedCharge() and LastAccumulatedTime() are cleared each time the command is issued

and the respective value is read. They are also overwritten whenever the integration counter is reset

again. The user can set thresholds to alert the host when AccumulatedCharge() reaches a particular level

in both the charge (positive) and discharge (negative) directions. These thresholds are set by Accum

Charge Positive Threshold and Accum Charge Negative Threshold.

www.ti.com

Due to the charge integration and timer information being stored in RAM, any the device's power cycles or

putting the device into SHUTDOWN will result in the loss of AccumulatedCharge(), AccumulatedTime(),

LastAccumulatedCharge(), and LastAccumulatedTime() data.

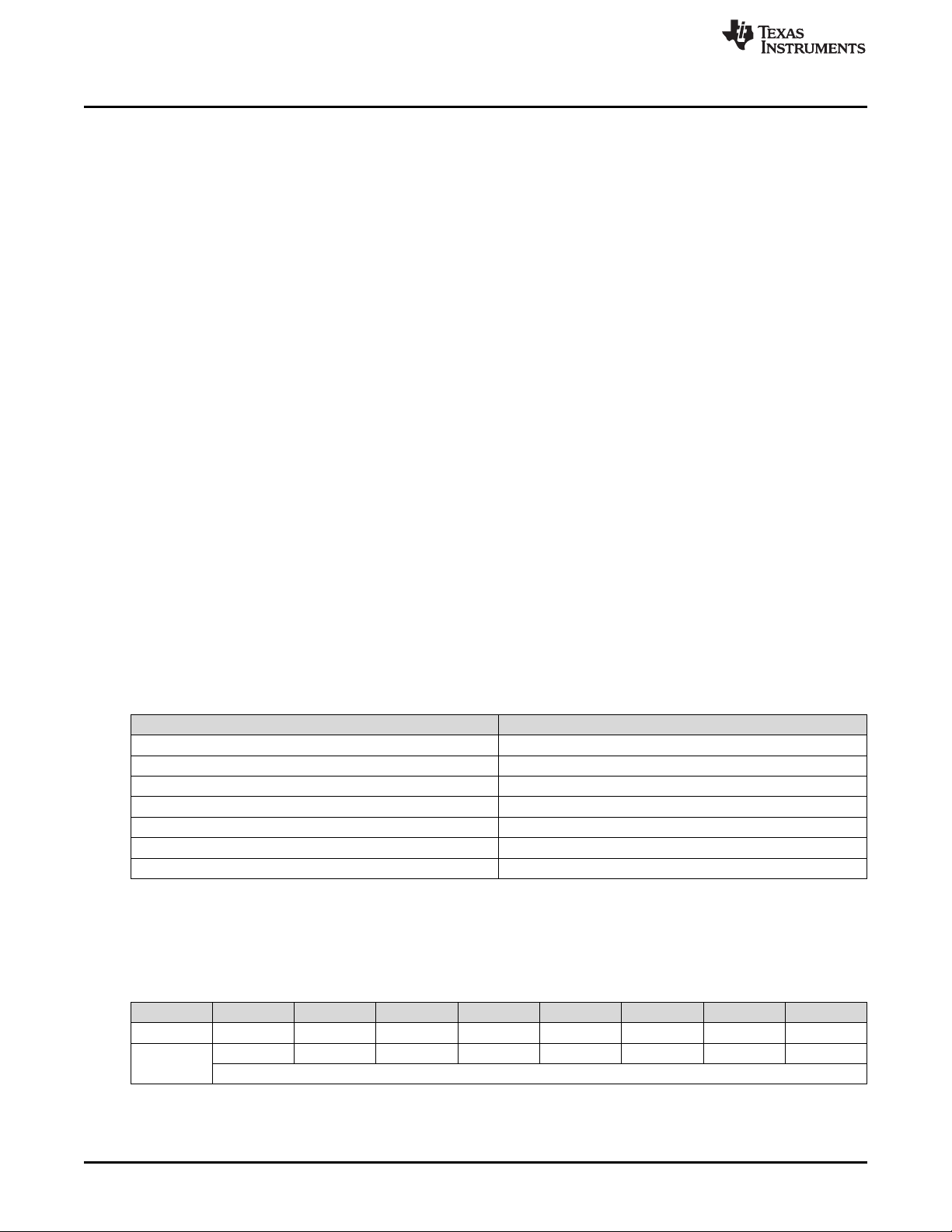

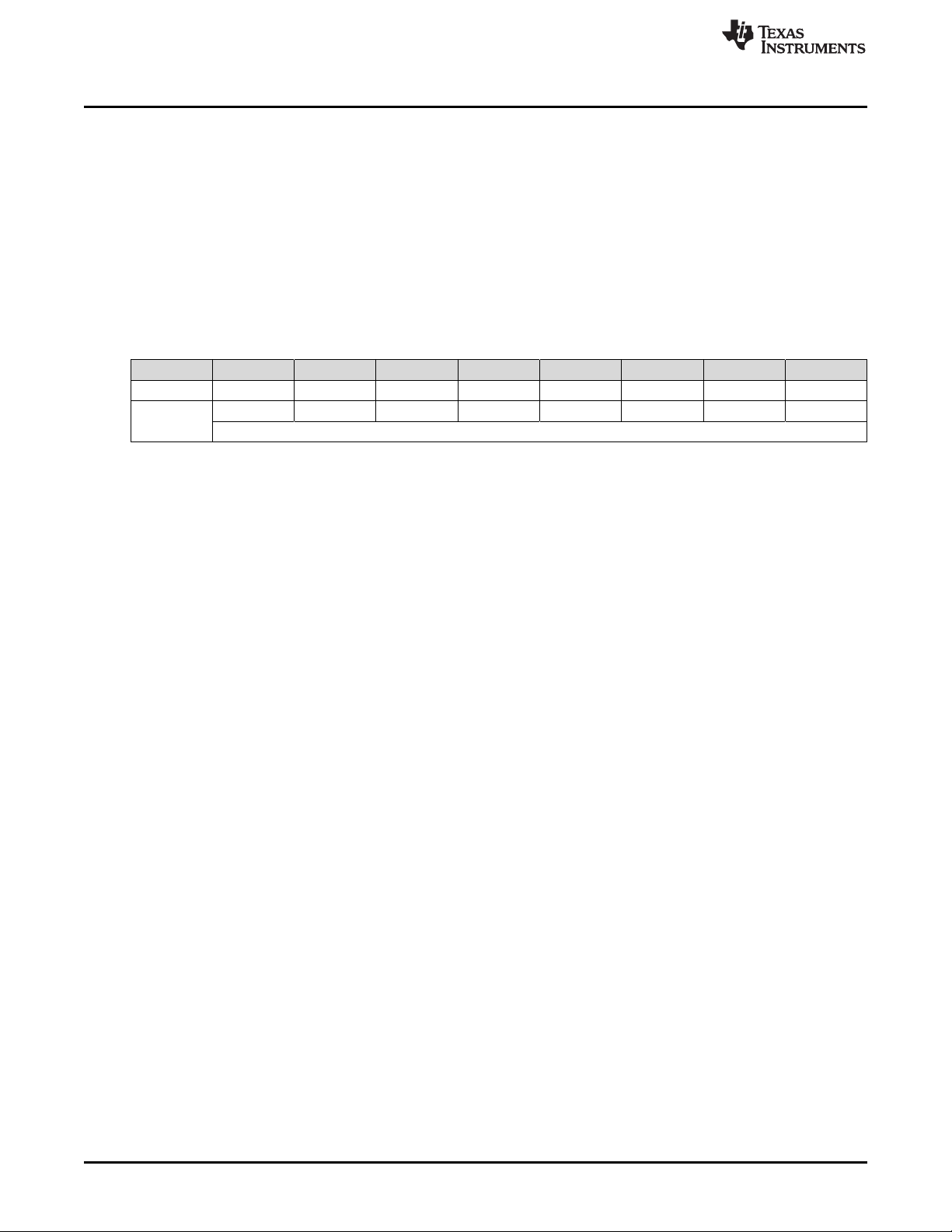

AccumulatedCharge() R Signed integer, 2 bytes –32767 32767 0 mAh

LastAccumulatedCharge() R Signed integer, 2 bytes –32767 32767 0 mAh

AccumulatedTime() R Unsigned integer, 2 bytes 0 65535 0 5 min

LastAccumulatedTime() R Unsigned integer, 2 bytes 0 65535 0 5 min

ACCUM_RESET W Boolean NA NA NA

14

General Description

NOTE: AccumulatedCharge() does not reset when a threshold is reached: The reset should be

initiated by the host using ACCUM_RESET. When a threshold is passed, a flag is set in

OperationStatus()[ACTHR].

It is possible for the integration counter to be reset at normal charge termination, but the

charger continues charging the battery for additional time until the charger ceases charging.

In this case, the integration counter would reset, then proceed to integrate this additional

charge. The user should be aware of this possibility and if it is a concern to plan for a

workaround, such as programming the integration to only accumulate discharging currents or

to detect when the charger stops charging, then issue an ACCUM_RESET command to

clear any residual charging integration.

Command R/W Type Min Max Default Units

SLUUBE8–September 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Page 15

www.ti.com

1.3 End-Of-Service Determination

The bq34210-Q1 device incorporates the End-of-Service (EOS) Determination function to determine the

end of useful service of the battery and to provide alerts based on this detection. Learning phases are

used to gather information about the present state of the battery through its cell resistance. Learning

cycles are coordinated by the bq34210-Q1 device with the host, which enables and disables the learning

load. LEN or LLEN is used to denote the Learning Load Enable function. The EOS Determination function

is enabled when [EOS_EN] in ManufacturingStatus() = 1. This bit can be toggled using the EOS_EN()

subcommand. The ManufacturingStatus[EOS_EN] bit should not be written directly during CONFIG

UPDATE mode, but instead should be done via the EOS_EN() subcommand. If the [EOS_EN] bit or other

data memory values related to this function are changed directly in data memory, they will not take effect

until a device reset is issued.

For best results, it is recommended that JEITA-based charging is not enabled when the EOS

Determination feature is used.

There are two ways to initiate a learning phase:

a. To have it automatically controlled by the device (recommended) based on when the internal Auto

Learn Time timer has expired since the last successful learning phase OR

b. To have it triggered by the host by writing a ManufacturerAccessControl() EOS_START_LEARN()

subcommand to the device.

Automatic learning is disabled if Auto Learn Time = 0. There is also a special test mode, which is entered

using the [LTEST] bit and sets several timers to short time durations.

The learning phase can be implemented in two ways, which are controlled by the [LSM] bit:

a. CHARGE-BEFORE-DISCHARGE: The system begins a Learn Charge Phase where it enables

charging to a voltage given by the charging voltage determined by the selected algorithm (JEITA, for

example) incremented by Learn Charge Voltage Delta. This increases charging from the level used

when not in a learning phase.

End-Of-Service Determination

NOTE: The data memory value of Last Charge Voltage Tx - Ty is not increased due to this Learn

Charge Phase.

After this charging is completed through normal charge termination, the device waits for the cell to

relax. It then initiates a Learn Discharge Phase, whereby an intended Learn Discharge Current is

enabled for a length of time given by Learn Discharge Time. When this time has expired, the device

disables the Learn Discharge Current. The bq34210-Q1 device analyzes the response of the battery

to this discharge current to estimate the status of the battery regarding its end of usable service.

If needed, the host continues discharging the battery until Voltage() reaches the appropriate voltage,

as determined by the charging algorithm selected, OR

b. DISCHARGE-BEFORE-CHARGE: The device begins by ensuring it is in a RELAXED state (typically

fully or near-fully charged).

The device begins a Learn Discharge Phase by enabling Learn Discharge Current for a length of

time given by Learn Discharge Time. When this time has expired, the device disables the Learn

Discharge Current.

The device can now be recharged to the appropriate voltage, as determined by the charging algorithm

selected, if needed.

NOTE: The learning discharge current value is set by external components and is not directly

controlled by the bq34210-Q1 device. However, this current is monitored throughout the

Learn Discharge Phase and evaluated to ensure it is close to the intended value.

SLUUBE8–September 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

General Description

15

Page 16

End-Of-Service Determination

The CHARGE-BEFORE-DISCHARGE approach described above in (a) is appealing in that the battery

voltage is not discharged below the appropriate charging voltage level by the learning phase. However, it

requires the use of a charger with programmable charging voltage, which may be a limitation in some

systems. For those cases, the DISCHARGE-BEFORE-CHARGE approach in (b) is provided, whereby a

charger with a fixed output voltage can be used with the tradeoff that the battery voltage will be

discharged below this level during the Learn Discharge Phase. However, the amount of this reduction in

battery voltage, and thus capacity, can be controlled and limited to acceptable levels through appropriate

device settings.

The response of the battery to the learning discharge current is analyzed and used to estimate the cell

resistance, Rcell, and this resistance estimate is used in two different methods to evaluate the cell EOS

status:

a. Direct Resistance Decisioning (DRD): This method uses the newly measured value of Rcell and

computes the ratio of Rcell with that of an Initial Rcell captured when the battery was first put into

service. The ratios are compared to thresholds to generate an alert and a warning.

• Alert if (Rcell/Initial Rcell) > DRD Alert Level

• Warning if (Rcell/Initial Rcell) > DRD Warning Level

b. Resistance Slope Decisioning: This method uses the changes with respect to time of Rcell,

comparing this to programmable thresholds to generate an alert and a warning.

Use of Resistance Slope Decisioning (RSD) requires an accurate measurement of the time between

consecutive learning phases for calculation of the slope of Rcell change with respect to time. This will not

be possible if the device is powered off between learning phases; in which case, Direct Resistance

Decisioning (DRD) can still be used. If the device is programmed to use Resistance Slope Decisioning

and a power cycle is detected (or anything that could impact the validity of the time measurement between

learning phases), then the device defaults to only using Direct Resistance Decisioning until the device is

continuously powered long enough to complete multiple learning phases and accurately evaluate the

Rcell change over time.

www.ti.com

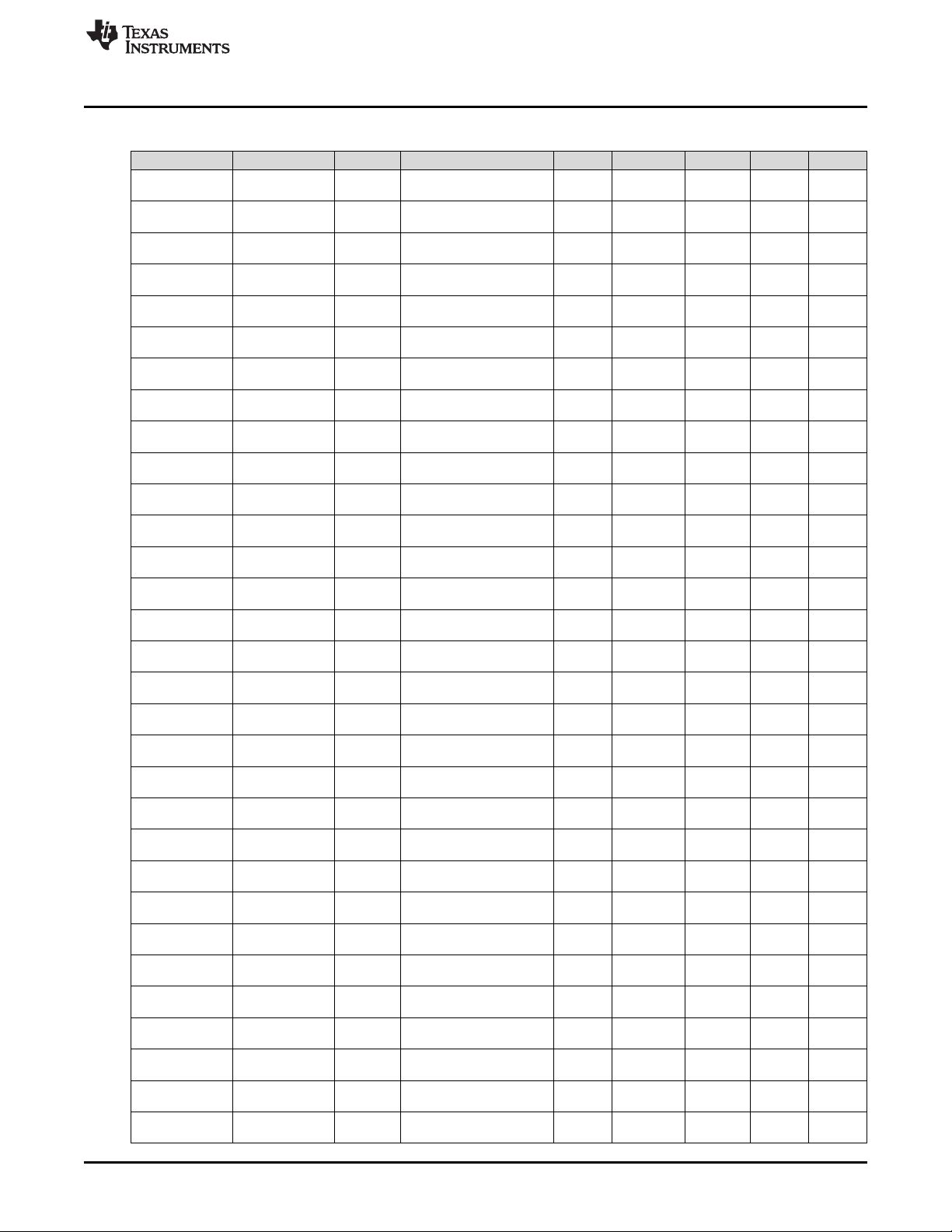

1.3.1 Alert Config Registers

The Alert registers are detailed in this section.

Alert_x Config Register Matching Register

Alert_0 Config Battery Status Low Byte

Alert_1 Config Battery Status High Byte

Alert_2 Config EOS Learn Status Low Byte

Alert_3 Config EOS Learn Status High Byte

Alert_4 Config EOS Status

Alert_5 Config EOS Safety Status Active Bits

Alert_6 Config Operation Status 2 bits

1.3.1.1 Alert_0 Config

This register matches the Battery Status register low byte.

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

SLEEP CHGINH FD FCSETV TCA TDA CHG DSG

Default

0 0 0 0 0 0 0 0

Table 1-3. Alert Config Registers

Table 1-4. Alert_0 Config Register Bit Definitions

0x00

16

General Description

Copyright © 2018, Texas Instruments Incorporated

SLUUBE8–September 2018

Submit Documentation Feedback

Page 17

www.ti.com

End-Of-Service Determination

SLEEP = Enables BatteryStatus()[SLEEP]

0 = Disabled (default)

1 = Enabled

CHGINH = Enables BatteryStatus()[CHGINH]

0 = Disabled (default)

1 = Enabled

FD = Enables BatteryStatus()[FD]

0 = Disabled (default)

1 = Enabled

FCSETV = Enables BatteryStatus()[FCSETV]

0 = Disabled (default)

1 = Enabled

TCA = Enables BatteryStatus()[TD]

0 = Disabled (default)

1 = Enabled

TDA = Enables BatteryStatus()[TDA]

0 = Disabled (default)

1 = Enabled

CHG = Enables BatteryStatus()[CHG]

0 = Disabled (default)

1 = Enabled

DSG = Enables BatteryStatus()[DSG]

0 = Disabled (default)

1 = Enabled

1.3.1.2 Alert_1 Config

This register matches the Battery Status register high byte.

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

RSVD SOCLOW UTC UTD OTC OTD BATHIGH BATLOW

Default

RSVD = Reserved

SOCLOW = Enables BatteryStatus()[SOCLOW]

UTC = Enables BatteryStatus()[UTC]

UTD = Enables BatteryStatus()[UTD]

OTC = Enables BatteryStatus()[OTC]

OTD = Enables BatteryStatus()[OTD]

Table 1-5. Alert_1 Config Register Bit Definitions

0 0 0 0 0 0 0 0

0x00

0 = Disabled (default)

1 = Enabled

0 = Disabled (default)

1 = Enabled

0 = Disabled (default)

1 = Enabled

0 = Disabled (default)

1 = Enabled

0 = Disabled (default)

1 = Enabled

SLUUBE8–September 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

General Description

17

Page 18

End-Of-Service Determination

BATHIGH = Enables BatteryStatus()[BATHIGH]

BATLOW = Enables BatteryStatus()[BATLOW]

1.3.1.3 Alert_2 Config

This register matches the EOS Learn Status register low byte.

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

LCT0 LFAULT LABRT LCMD LPER LRLX LCHG LDSG

Default

0 0 0 0 0 0 0 0

LCT0 = Enables EOSLearnStatus()[LCT0]

LFAULT = Enables EOSLearnStatus()[LFAULT]

LABRT = Enables EOSLearnStatus()[LABRT]

LCMD = Enables EOSLearnStatus()[LCMD]

LPER = Enables EOSLearnStatus()[LPER]

LRLX = Enables EOSLearnStatus()[LRLX]

LCHG = Enables EOSLearnStatus()[LDSG]

LDSG = Enables EOSLearnStatus()[LDSG]

www.ti.com

0 = Disabled (default)

1 = Enabled

0 = Disabled (default)

1 = Enabled

Table 1-6. Alert_2 Config Register Bit Definitions

0x00

0 = Disabled (default)

1 = Enabled

0 = Disabled (default)

1 = Enabled

0 = Disabled (default)

1 = Enabled

0 = Disabled (default)

1 = Enabled

0 = Disabled (default)

1 = Enabled

0 = Disabled (default)

1 = Enabled

0 = Disabled (default)

1 = Enabled

0 = Disabled (default)

1 = Enabled

1.3.1.4 Alert_3 Config

This register matches the EOS Learn Status register high byte.

18

General Description

Copyright © 2018, Texas Instruments Incorporated

SLUUBE8–September 2018

Submit Documentation Feedback

Page 19

www.ti.com

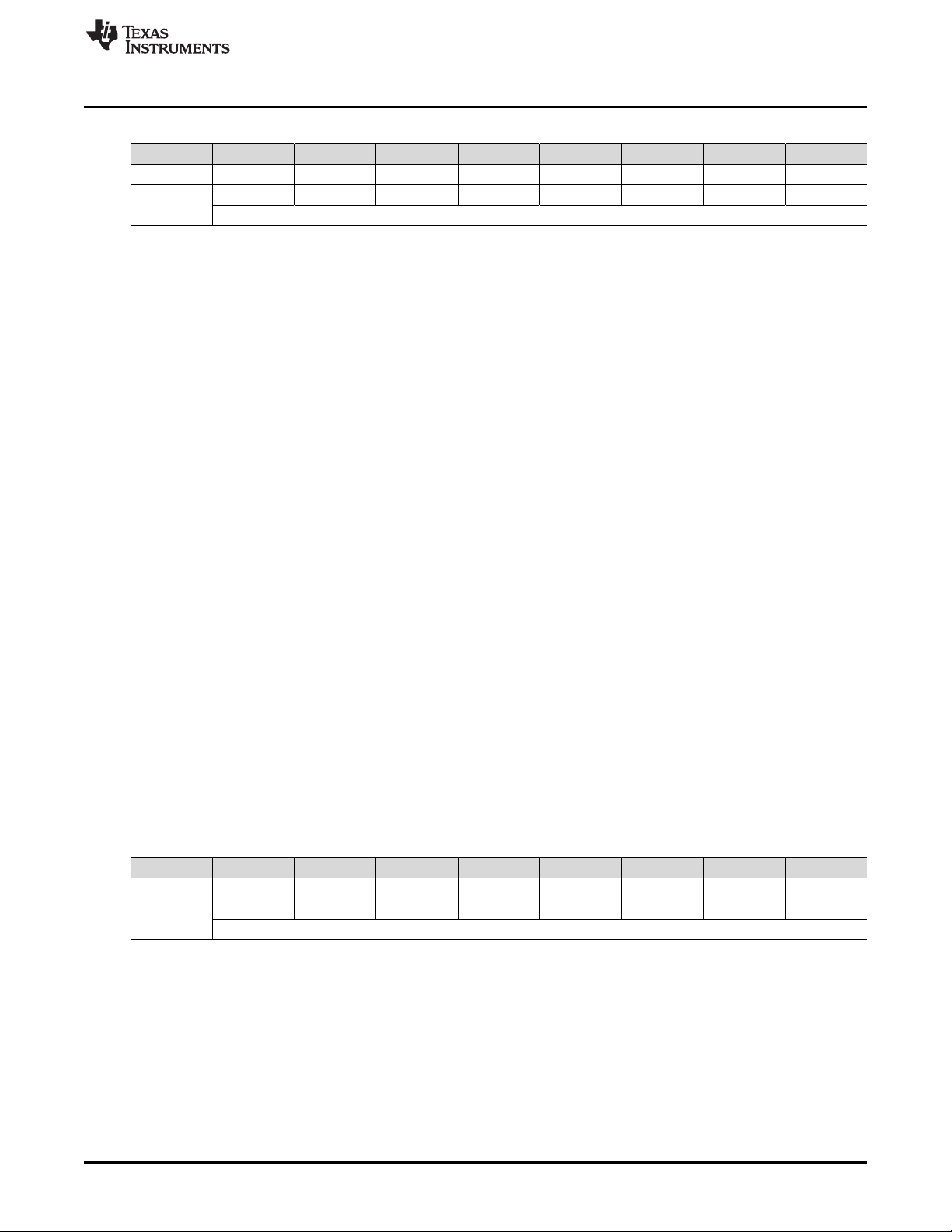

Table 1-7. Alert_3 Config Register Bit Definitions

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

LDONE LRES LRSTOR LCTLEDGE LUCD LDPAM LDPAT LDPAI

Default

LCTLEDGE = Enables EOSLearnStatus()[LCTLEDGE]

0 0 0 0 0 0 0 0

LDONE = Enables EOSLearnStatus()[LDONE]

0 = Disabled (default)

1 = Enabled

LRES = Enables EOSLearnStatus()[LRES]

0 = Disabled (default)

1 = Enabled

LRSTOR = Enables EOSLearnStatus()[LRSTOR]

0 = Disabled (default)

1 = Enabled

0 = Disabled (default)

1 = Enabled

LUCD = Enables EOSLearnStatus()[LUCD]

0 = Disabled (default)

1 = Enabled

LDPAM = Enables EOSLearnStatus()[LDPAM]

0 = Disabled (default)

1 = Enabled

LDPAT = Enables EOSLearnStatus()[LDPAT]

0 = Disabled (default)

1 = Enabled

LDPAI = Enables EOSLearnStatus()[LDPAI]

0 = Disabled (default)

1 = Enabled

End-Of-Service Determination

0x00

1.3.1.5 Alert_4 Config

This register matches the EOS Status register.

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

SRRL SRCL RSVD LTI RSDLI RCELLR IRRCOMP IRCOMP

Default

SLUUBE8–September 2018

Submit Documentation Feedback

0 0 0 0 0 0 0 0

SRRL = Enables EOSStatus()[SRRL]

SRCL = Enables EOSStatus()[SRCL]

RSVD = Reserved

LTI = Enables EOSStatus()[LTI]

Table 1-8. Alert_4 Config Register Bit Definitions

0x00

0 = Disabled (default)

1 = Enabled

0 = Disabled (default)

1 = Enabled

0 = Disabled (default)

Copyright © 2018, Texas Instruments Incorporated

General Description

19

Page 20

End-Of-Service Determination

RSDLI = Enables EOSStatus()[RSDLI]

RCELLR = Enables EOSStatus()[RCELLR]

IRRCOMP = Enables EOSStatus()[IRRCOMP]

IRCOMP = Enables EOSStatus()[IRCOMP]

1.3.1.6 Alert_5 Config

This register matches the EOS Safety Status register active bits. Bits 7:4 in the Alert_5 Config register

match the EOS Safety Status register's high byte, Bits 3:0. Bits 3:0 in the Alert_5 Config register match

the EOS Safety Status register's low byte, Bits 3:0.

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

RSVD RSDLWARN RSDWARN DRDWARN RSVD

Default

0 0 0 0 0 0 0 0

1 = Enabled

0 = Disabled (default)

1 = Enabled

0 = Disabled (default)

1 = Enabled

0 = Disabled (default)

1 = Enabled

0 = Disabled (default)

1 = Enabled

Table 1-9. Alert_5 Config Register Bit Definitions

0x00

RSDL

ALERT

www.ti.com

RSDALERT DRDALERT

RSVD = Reserved

RSDLWARN = Enables EOSSafetyStatus()[RSDLWARN]

RSDWARN = Enables EOSSafetyStatus()[RSDWARN]

DRDWARN = Enables EOSSafetyStatus()[DRDWARN]

RSVD = Reserved

RSDLALERT = Enables EOSSafetyStatus()[RSDLALERT]

RSDALERT = Enables EOSSafetyStatus()[RSDALERT]

DRDALERT = Enables EOSLearnStatus()[DRDALERT]

1.3.1.7 Alert_6 Config

This register matches two bits from the Operation Status low byte.

0 = Disabled (default)

1 = Enabled

0 = Disabled (default)

1 = Enabled

0 = Disabled (default)

1 = Enabled

0 = Disabled (default)

1 = Enabled

0 = Disabled (default)

1 = Enabled

0 = Disabled (default)

1 = Enabled

20

General Description

Copyright © 2018, Texas Instruments Incorporated

SLUUBE8–September 2018

Submit Documentation Feedback

Page 21

www.ti.com

Table 1-10. Alert_6 Config Register Bit Definitions

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

RSVD RSVD RSVD RSVD RSVD RSVD ACTHR BLT

Default

0 0 0 0 0 0 0 0

RSVD = Reserved

ACTHR = Enables OperationStatus()[ACTHR]

0 = Disabled (default)

1 = Enabled

BLT = Enables OperationStatus()[BLT]

0 = Disabled (default)

1 = Enabled

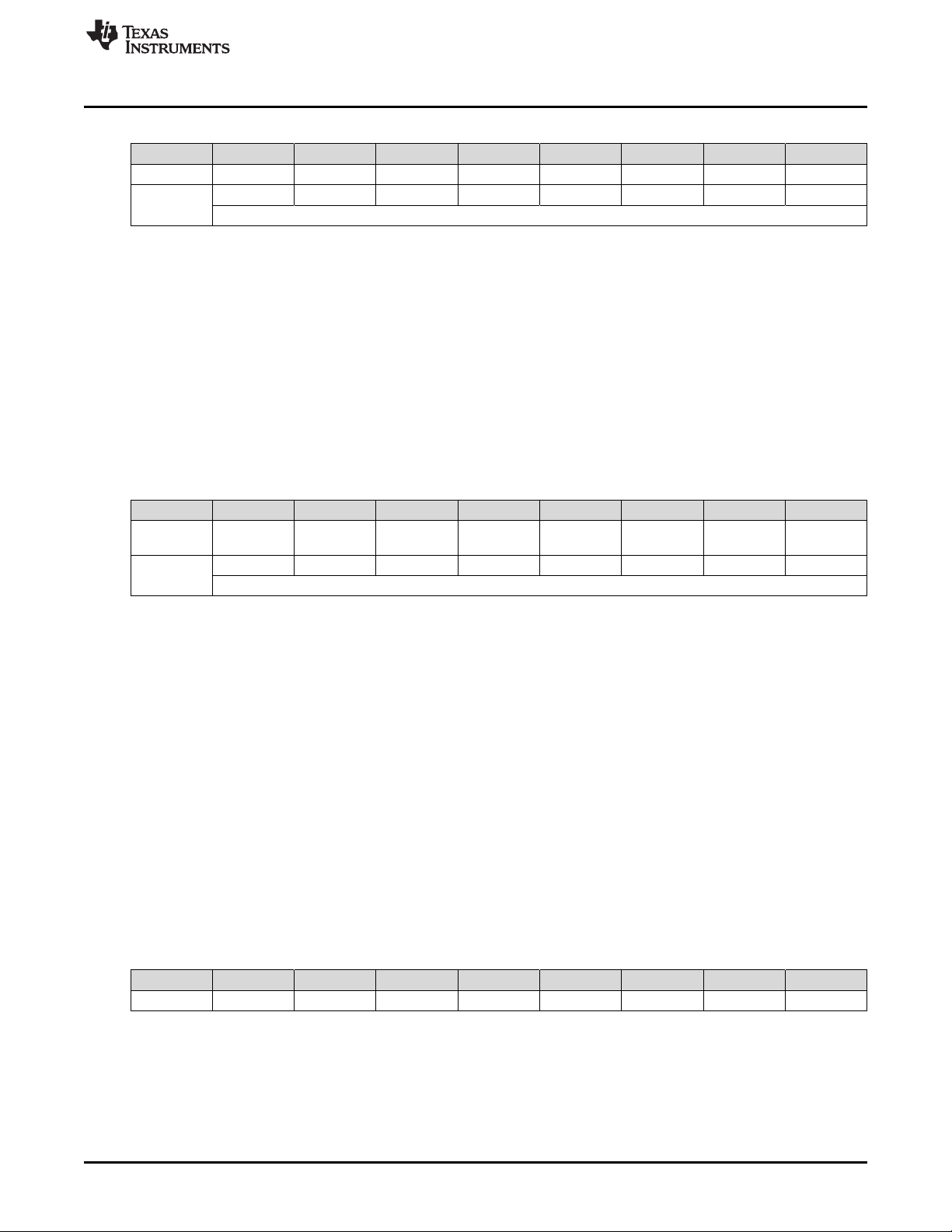

1.3.2 Smoothing Config Register

Table 1-11. Smoothing Config Register Bit Definition

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

RSVD RSVD RSVD RSVD

Default

0 0 0 0 0 0 0 0

0x00

0x00

SMOOTH

EOC_EN

End-Of-Service Determination

SMEXT VAVG SMEN

RSVD = Reserved

SMOOTHEOC_EN = Allows smoothing of RemCap once Current starts decreasing during the end of charge (EOC).

0 = End of charge smoothing is not enabled.

1 = End of charge smoothing is enabled (default).

SMEXT = When set to 1, smoothing continues to EDV1 and EDV0 points. When set to 0, smoothing stops at

VAVG = Enables smoothing to use average voltage

SMEN = Smoothing result is reported on RemainingCapacity().

EDV2. Default is 0.

When set to 1, smoothing uses average voltage. When set to 0 smoothing uses measured voltage.

Default is 0.

When set to 1, the smoothing result is reported on RemainingCapacity(). When set to 0, the normal

CEDV remaining capacity is reported. Default is 0.

1.3.3 End-Of-Service Determination—Detailed Description

The EOS Configuration data memory is used to configure certain settings associated with the EOS

Determination function.

Table 1-12. EOS Configuration

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

RSVD RSVD RSVD RSVD LTEST LVR LSM RSVD

Legend: RSVD = Reserved. Do not use.

LTEST = Learn Test Mode Control

This bit is used to put the device into a test mode for reduced timing testing of the EOS

Determination function.

When this bit is set = 1, the following values are set:

SLUUBE8–September 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

General Description

21

Page 22

Learn

Post-Relax

Phase

Learn

Charge

Phase

Learn

Pre-Relax

Phase

Learn

Discharge

Phase

Voltage

Restore?

yes

no

Voltage

Restore

Phase

Learning

Phase

Complete

End-Of-Service Determination

Auto Learn Time = 10 min

Auto Learn Retry Time = 5 min

Alert-Warn Learn Time = 10 min

Minimum Learn Time = 10 min

0 = The device uses the values programmed in data memory for the above parameters

(default).

LVR = Learn Voltage Restore Control

This bit determines whether the device continues discharging during Learn Discharge Phase

until Voltage() reaches the appropriate Last Charge Voltage Tx - Ty (when set = 1), or to

simply stop discharge when the timer reaches Learn Discharge Time (when set = 0).

1 = The device continues Learn Discharge Phase until Voltage() reaches the appropriate

Last Charge Voltage Tx - Ty.

0 = The device stops Learn Discharge Phase when the timer reaches Learn Discharge

Time (default).

LSM = Learn Sequence Mode Control

This bit determines whether the EOS algorithm uses CHARGE-BEFORE-DISCHARGE or

DISCHARGE-BEFORE-CHARGE mode.

1 = DISCHARGE-BEFORE-CHARGE mode is used.

0 = CHARGE-BEFORE-DISCHARGE mode is used (default).

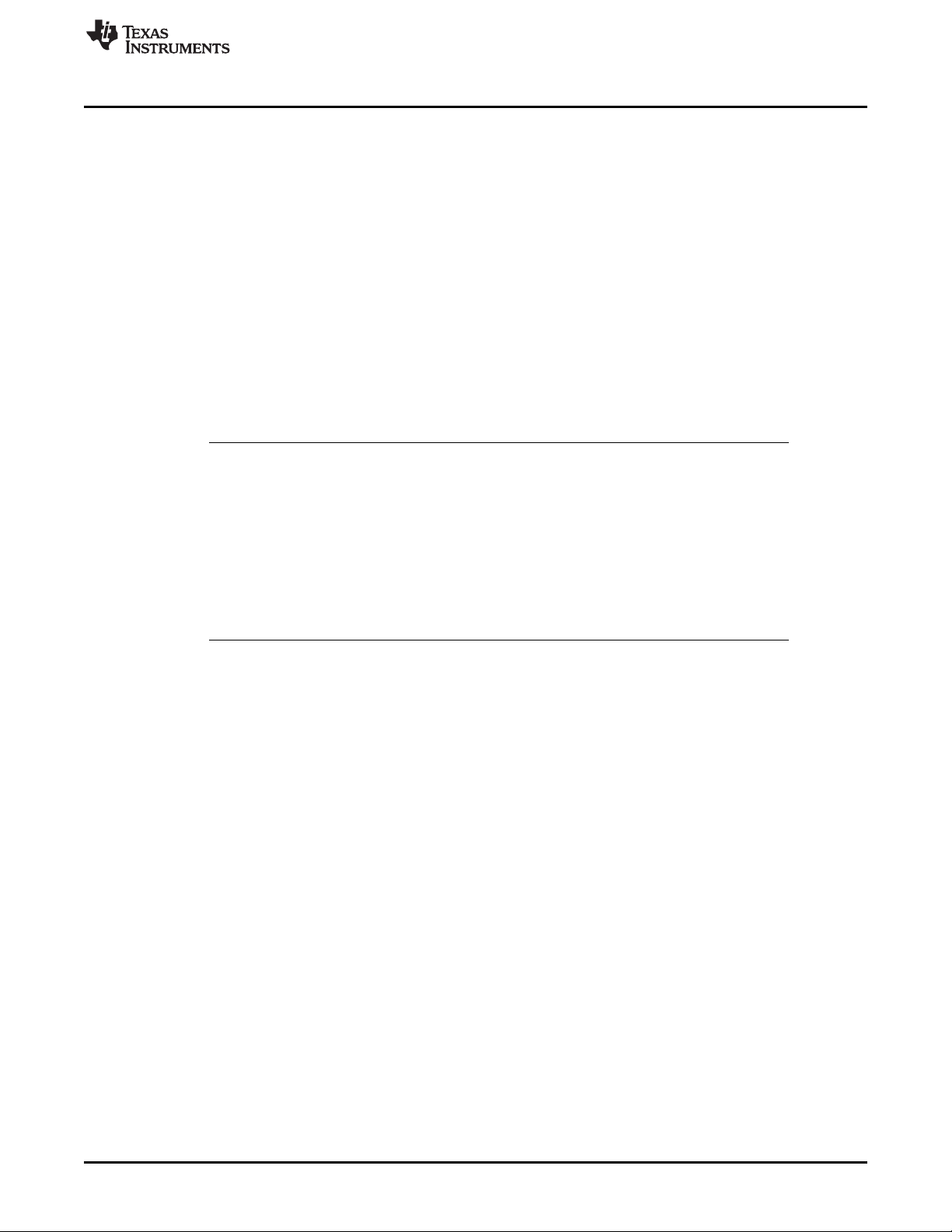

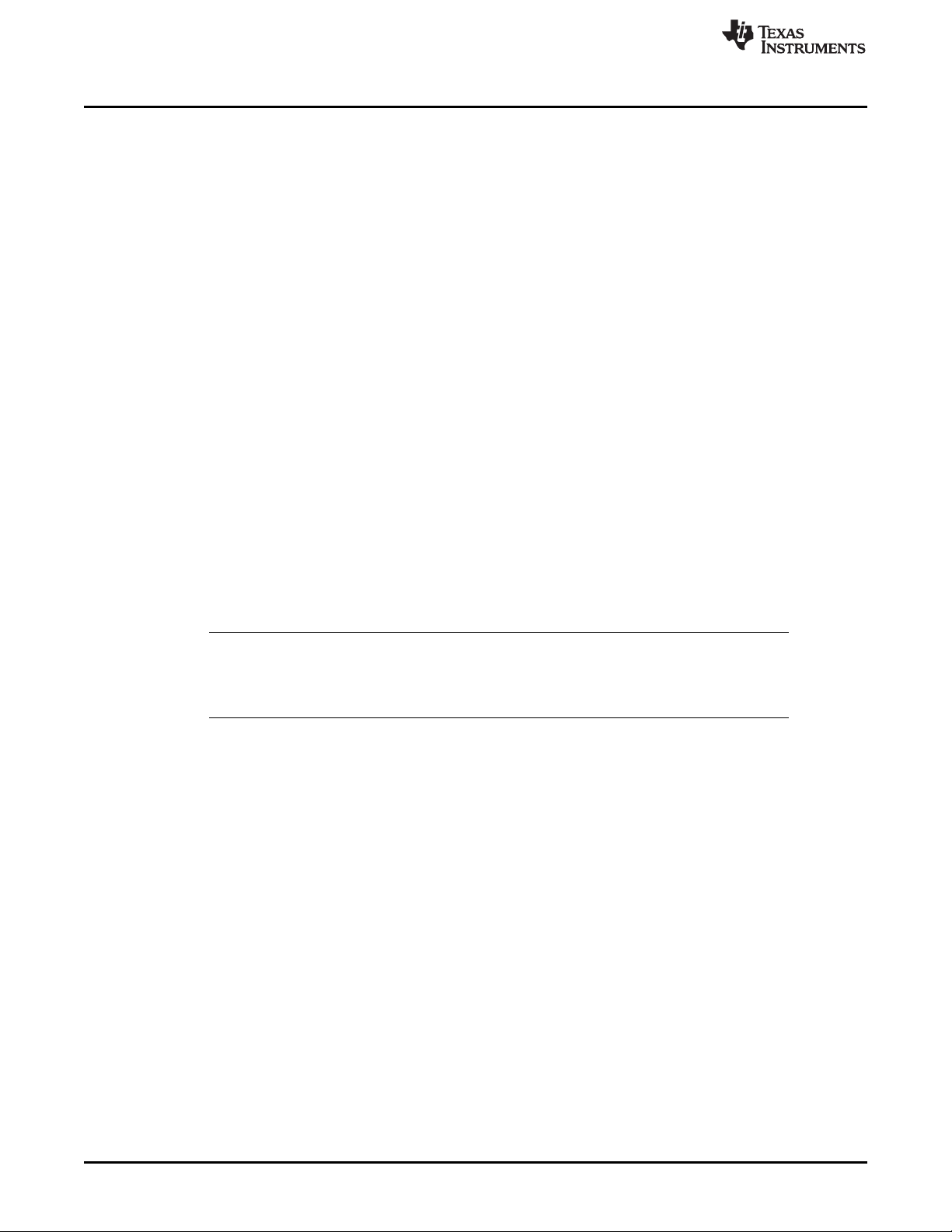

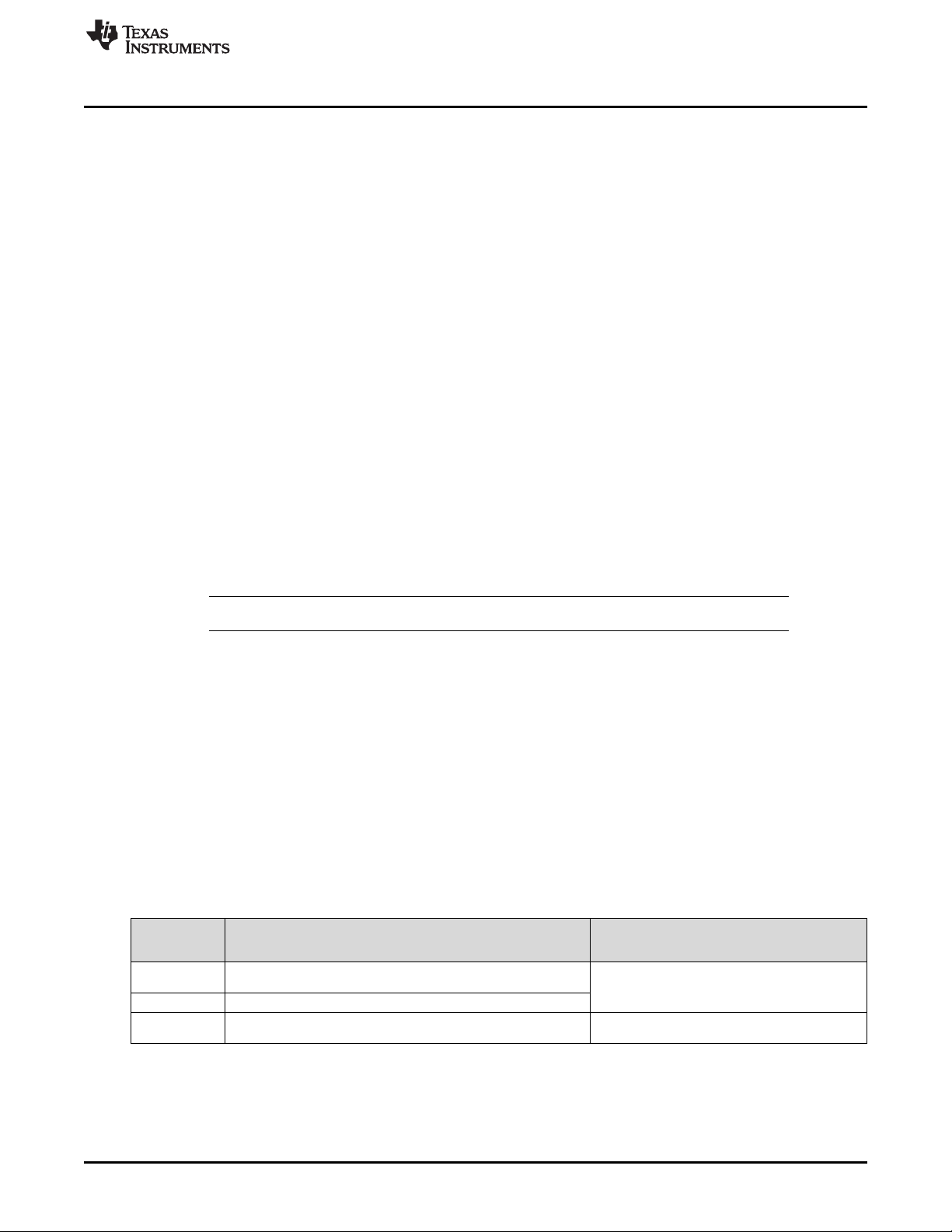

The device includes a variety of flags to provide visibility into the operation of the EOS Determination

Learning process. These are found in EOSLearnStatus(): 0x64 and 0x65.

The sequence of steps involved in a learning phase differs depending on the setting of [LSM]. These are

depicted in the following figures.

www.ti.com

22

General Description

Figure 1-4. State Diagram for LSM = 0

Copyright © 2018, Texas Instruments Incorporated

SLUUBE8–September 2018

Submit Documentation Feedback

Page 23

Learn

Post-Relax

Phase

Learn

Pre-Relax

Phase

Learn

Discharge

Phase

Voltage

Restore?

yes

no

Learn

Charge

Phase

Learning

Phase

Complete

www.ti.com

Figure 1-5. State Diagram for LSM = 1

1.3.3.1 Periodic and Manual Learn Command

For manual control of learning phases, the ManufacturerAccessControl() subcommand

EOS_START_LEARN() is used. When the device receives this command, it sets the [LCMD] flag and

initiates the learning phase if conditions permit: for example, charger present, no charging or safety faults,

and the temperature is within acceptable limits. The [LDPAT] and [LFAULT] flags will be set if the Learning

Discharge Phase is attempted but temperature conditions do not permit it.

If the device is in periodic (automatic) learning mode, then the [LPER] bit will be set while the device is in

a learning phase.

EOS_ABORT_LEARN(): This ManufacturerAccessControl() subcommand is used to abort a learning

phase that is in progress. Use of this command during a learning phase results in a failed learning phase

and setting the [LABRT] flag, whereupon the device will retry another learning phase after a time period of

Auto Learn Retry Time.

When the device attempts to initiate a learning phase, but conditions do not permit this, then the device

will wait for Auto Learn Retry Time to again attempt a learning phase. Note that this will occur whether

the device is configured in periodic learning or learning is initiated through a host command.

If the case occurs where an alert or warning is detected, either through Direct Resistance Decisioning or

Resistance Slope Decisioning, the Alert-Warn Learn Time is used to schedule a new learning phase. If

multiple fault events must be detected before the alert or warning flags are set, and an stopped learning

phase occurs after the first alert or warning is detected, then Alert-Warn Learn Time is used to schedule

future Rcell measurements rather than Auto Learn Retry Time.

End-Of-Service Determination

NOTE: If [LTEST] is set, special values override the selected timer values to facilitate device

operation testing in a shorter time scale.

To avoid interruption to the EOS Determination measurements and calculations, automatic offset

calibration is not initiated during a learning phase. While it is possible for the host to manually initiate a

calibration event during a learning phase, it is recommended that the host avoid this.

NOTE: Alert-Warn Learn Time has priority over Auto Learn Retry Time, so if multiple

occurrences must be detected before an alert or warning is triggered, and after the first

occurrence is detected that a fault occurred that invalidated a following attempted learning

phase, the Alert-Warn Learn Time will be used to determine the time to the next learning

phase attempt. It should also be noted that if Alert-Warn Learn Time is set to be lower than

Minimum Learn Time, then Minimum Learn Time will be used to determine the time to the

next learning phase attempt.

SLUUBE8–September 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

General Description

23

Page 24

End-Of-Service Determination

1.3.3.2 Learn Charge Phase

The operation of the device is first described for the case of [LSM] = 0, in which the device uses

CHARGE-BEFORE-DISCHARGE mode. In this mode, the device first enters Learn Charge Phase by

setting ChargingVoltage() to the appropriate charging voltage determined by the selected charging

algorithm (JEITA, for example) incremented by Learn Charge Voltage Delta. The [LCHG] flag is set and

charge terminates using standard charge termination criteria. Upon termination of charge, then [LCHG] is

cleared. Note that the data memory value of Last Charge Voltage Tx - Ty is not incremented due to this

Learn Charge Phase.

The time while [LCHG] is set is measured and compared against a threshold given by Learn Charge

Time Limit to identify an excessive charging time, which may indicate an issue in the system. When the

learn charging time exceeds this limit, the [LCTO] flag is set, learning is terminated, and the [LFAULT] flag

is set to indicate a fault has occurred. The [LCHG] flag is reset whenever the device exits from

CHARGING mode. If a learning fault occurs, the status flag ([LCHG] in this case) remains set to enable

the host to understand what mode the system was in when the fault occurred.

NOTE: The standard charge termination criteria voltage condition is relative to ChargingVoltage(), so