Features

➤

Safe charge of Li-Ion battery

packs

➤

Pulse-width modulation control

for current and voltage regulation

➤

Programmable high-side/low-side

current-sense

➤

Fast charge terminated by se

lectable minimum current; safety

backup termination at maximum

time

➤

Pre-charge qualification detects

shorted or damaged cells and

conditions battery

➤ Charging continuously qualified

by temperature and voltage limits

➤ Direct LED control outputs to

display charge status and fault

conditions

General Description

The bq2954 Li-Ion Charge-Manage

ment IC uses a flexible pulse-width

modulation regulator to control volt

age and current during charging.

The regulator frequency is set by an

external capacitor for design flexi

bility. The switch-mode design mini

mizes power dissipation.

For safety, the bq2954 inhibits fast

charging until the battery voltage

and temperature are within config

ured limits. If the battery voltage is

less than the low-voltage threshold,

the bq2954 provides low-current

conditioning of the battery.

For charge qualifiction, the bq2954

uses an external thermistor to measure battery temperature. Charging

begins when power is applied or the

battery is inserted

The bq2954 charges a battery in two

phases. First a constant-current

phase replenishes approximately

70% of battery capacity. Then a volt

age-regulation phase completes the

battery charge.

The bq2954 provides status indica

tions of all charger states and faults

for accurate determination of the

battery and charge-system condi

tions.

1

TM Time-out programming

input

CHG Charge active output

BAT Battery voltage input

VCOMP Voltage loop comp input

ICOMP Current loop comp input

I

TERM

Minimum current

termination select input

SNS Sense resistor input

TS Temperature sense input

1

PN295401.eps

16-Pin Narrow

DIP or SOIC

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

LED2/DSEL

LED1/CSEL

MOD

V

CC

V

SS

LCOM

BTST

TPWM

TM

CHG

BAT

VCOMP

ICOMP

I

TERM

SNS

TS

TPWM Regulator timebase input

BTST Battery test output

LCOM Common LED output

V

SS

System ground

V

CC

5.0V±10% power

MOD Modulation control

output

LED

1

/ Charge status output 1/

CSEL Charge sense select

input

LED2/ Charge status output 2/

DSEL Display select input

Pin Connections

Pin Names

SLUS064–OCTOBER 1998 B

Lithium Ion Charge Management IC

with Integrated Switching Controller

bq2954

Pin Descriptions

TM Time-out programming input

Sets the maximum charge time. The resistor

and capacitor values are determined using

Equation 5. Figure 10 shows the resistor/ca

-

pacitor connection.

CHG Charge active output

An open-drain output is driven low when the

battery is removed, during a temperature

pend, when a fault condition is present, or

when charge is done. CHG can be used to

disable a high-value load capacitor to detect

quickly any battery removal.

BAT Battery voltage input

Sense input. This potential is generally de

-

veloped using a high-impedance resistor di

-

vider network connected between the posi

tive and the negative terminals of the battery. See Figures 6 and 7 and Equation 1.

VCOMP Voltage loop compensation input

Connects to an external R-C network to stabilize the regulated voltage.

ICOMP Current loop compensation input

Connects to an external R-C network to stabilize the regulated current.

I

TERM

Charge full and minimum current termi

nation select

Three-state input is used to set I

FULL

and

I

MIN

for fast charge termination. See Table 4.

SNS Charging current sense input

Battery current is sensed via the voltage devel

oped on this pin by an external sense-resistor.

TS Temperature sense input

Used to monitor battery temperature. An exter

nal resistor-divider network sets the lower and

upper temperature thresholds. (See Figures 8

and 9 and Equations 3 and 4.)

TPWM Regulation timebase input

Uses an external timing capacitor to ground

to set the pulse-width modulation (PWM)

frequency. See Equation 7.

BTST Battery test output

Driven high in the absence of a battery in or

-

der to provide a potential at the battery ter

-

minal when no battery is present.

LCOM Common LED output

Common output for LED

1-2

. This output is

in a high-impedance state during initiali

zation to read programming input on DSEL

and CSEL.

V

SS

Ground

V

CC

VCCsupply

5.0V, ±10%

MOD Current-switching control output

Pulse-width modulated push/pull output used

to control the charging current to the battery.

MOD switches high to enable current flow and

low to inhibit current flow. (The maximum

duty cycle is 80%.)

LED

1

–

LED

2

Charger display status 1–2 outputs

Drivers for the direct drive of the LED display. These outputs are tri-stated during

initialization so that DSEL and CSEL can be

read.

DSEL Display select input (shared pin with

LED

2

)

Three-level input that controls the LED

1–2

charge display modes.

CSEL

Charge sense-select input (shared pin

with LED

1

)

Input that controls whether current is

sensed on low side of battery or high side of

battery. A current mirror is required for

high-side sense.

2

bq2954

Functional Description

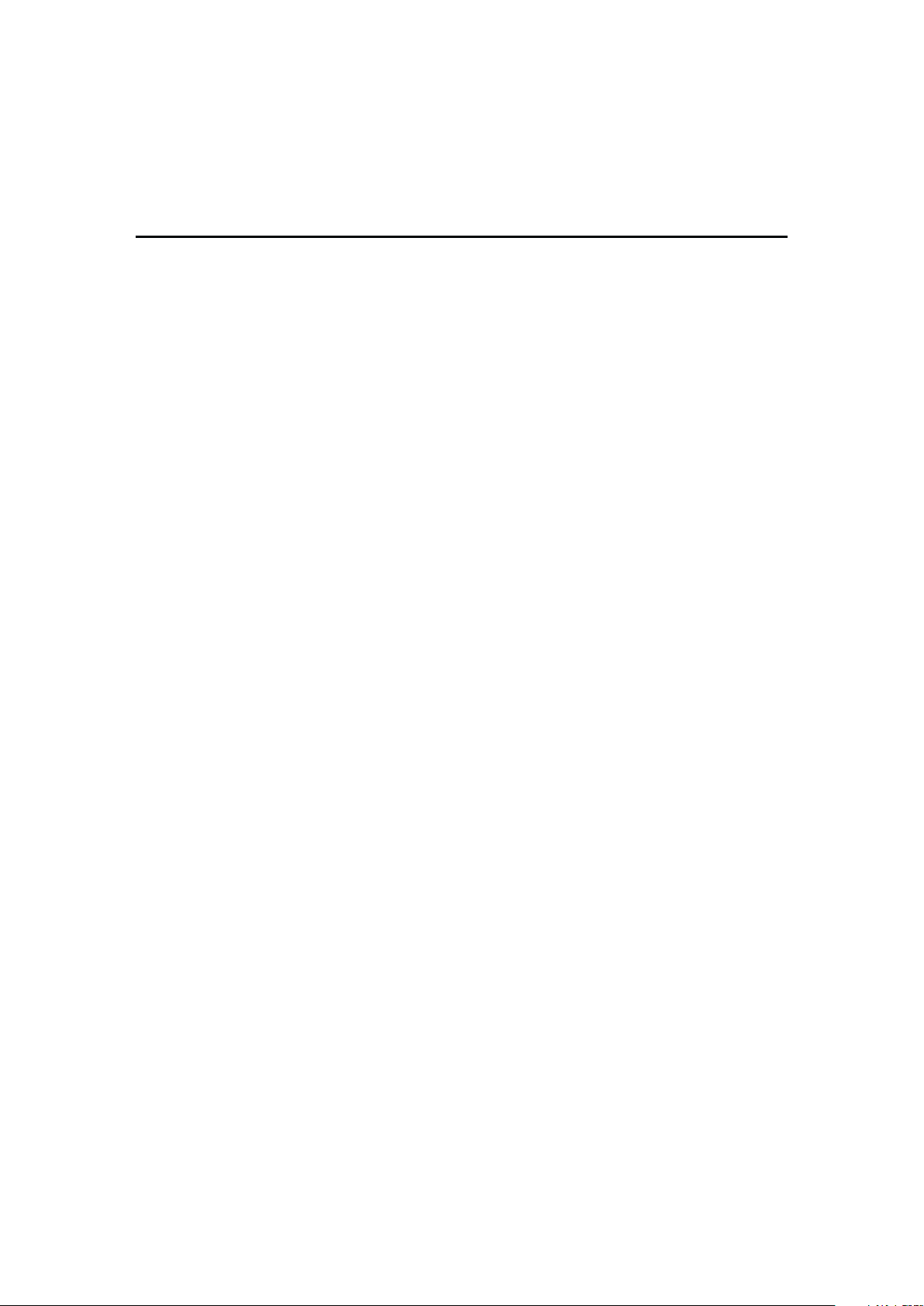

The bq2954 functional operation is described in terms of

the following (Figure 1):

■

Charge algorithm

■

Charge qualification

■

Charge status display

■

Configuring the display and termination

■

Voltage and current monitoring

■

Battery insertion and removal

■

Temperature monitoring

■

Maximum time--out

■

Charge regulation

■

Recharge after fast charge

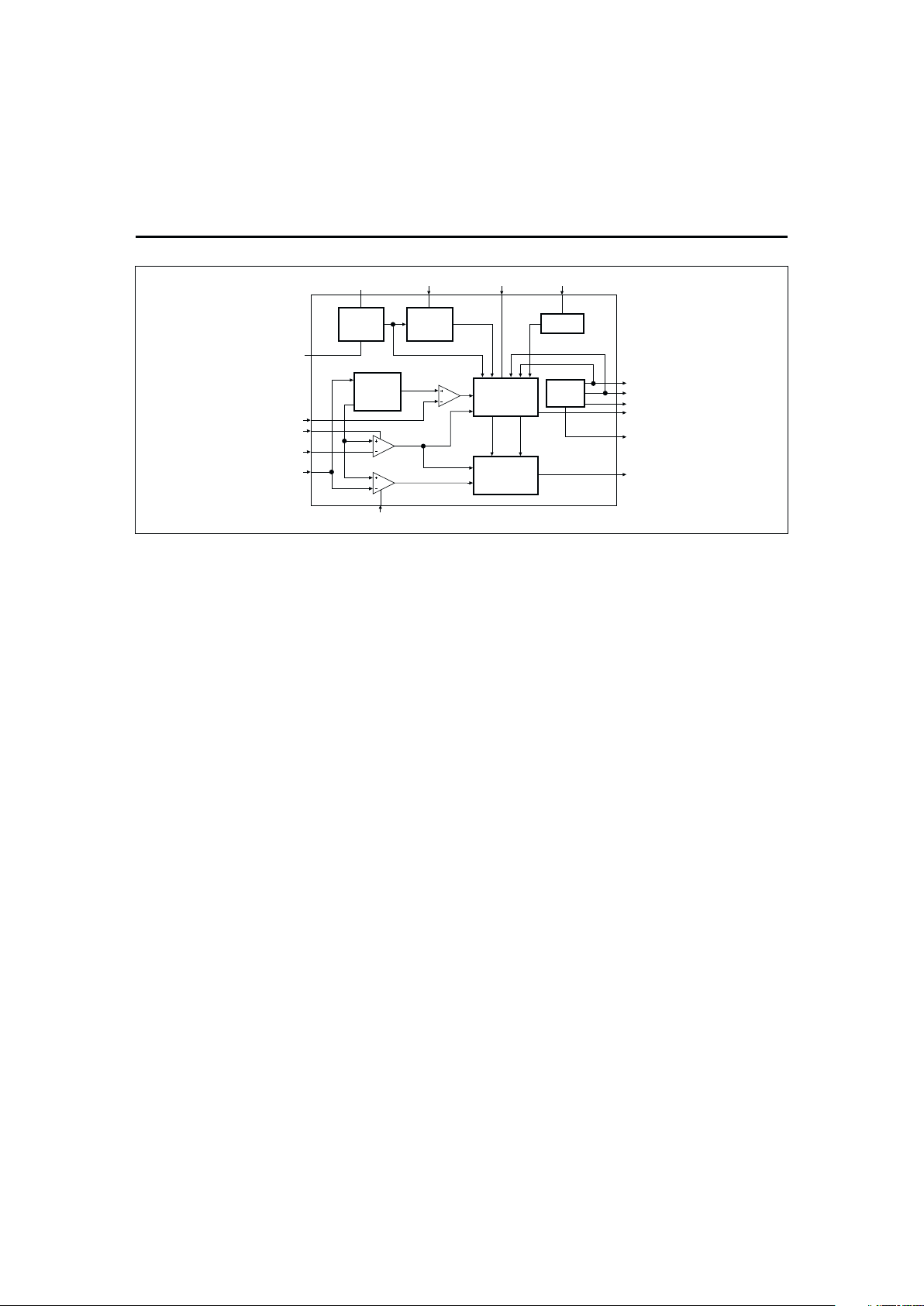

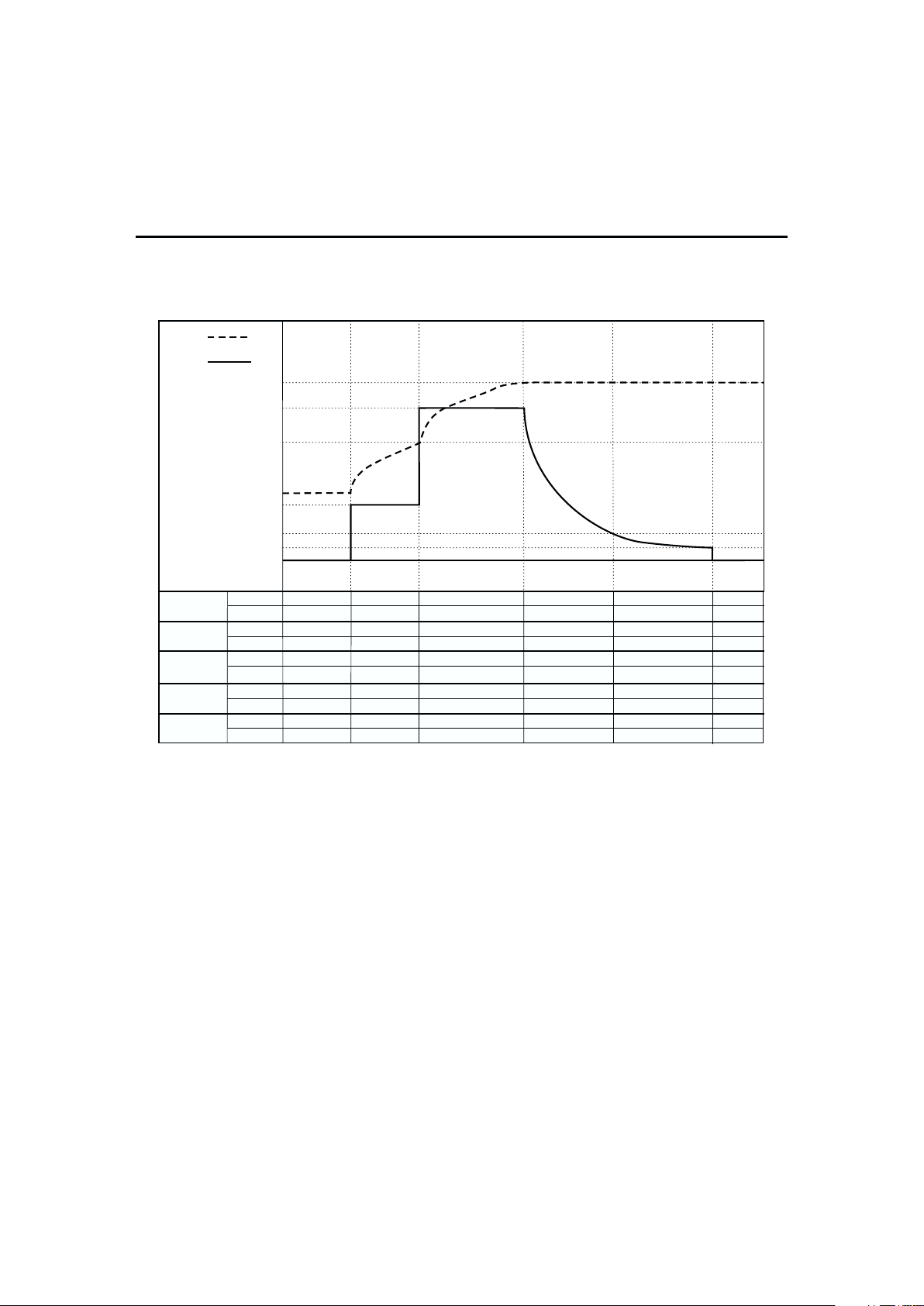

Charge Algorithm

The bq2954 uses a two-phase fast-charge algorithm. In

phase 1, the bq2954 regulates constant current until the

voltage on the BAT pin, V

BAT

, rises to the internal

threshold, V

REG

. The bq2954 then transitions to phase 2

and regulates constant voltage (V

BAT=VREG

) until the

charging current falls below the programmed I

MIN

threshold. Fast charge then terminates, and the bq2954

enters the Charge Complete state. (See Figure 2.)

Charge Qualification

The bq2954 starts a charge cycle when power is applied

while a battery is present or when a battery is inserted.

Figure 2 shows the state diagram for the bq2954. The

bq2954 first checks that the battery temperature is

within the allowed, user-configurable range. If the temperature is out of range, the bq2954 remains in the

QUALIFICATION state (S01) and waits until the battery

temperature and voltage are within the allowed range.

If during any state of charge, a temperature excursion

occurs HOT, the bq2954 proceeds to the DONE state

(S04) and indicates this state on the LED outputs and

provides no current. If this occurs, the bq2954 remains

in the DONE state unless the following two conditions

are met:

■

Temperature falls within valid charge range

■

V

BAT

falls below the internal threshold,V

RCHG

If these two conditions are met, a new charge cycle be

-

gins. During any state of charge, if a temperature ex

-

cursion occurs COLD, the bq2954 terminates charge and

returns to the QUALIFICATION state (S01). Charge re

-

starts if V

BAT

and temperature are in valid range.

When the temperature and voltage are valid, the bq2954

enters the CONDITIONING state (S02) and regulates

current to I

COND

(=I

MAX

/10). After an initial holdoff pe

-

riod t

HO

(which prevents the IC from reacting to tran

-

sient voltage spikes that may occur when charge current

is first applied), the IC begins monitoring V

BAT

.IfV

BAT

does not rise to at least V

MIN

before the expiration of

3

bq2954

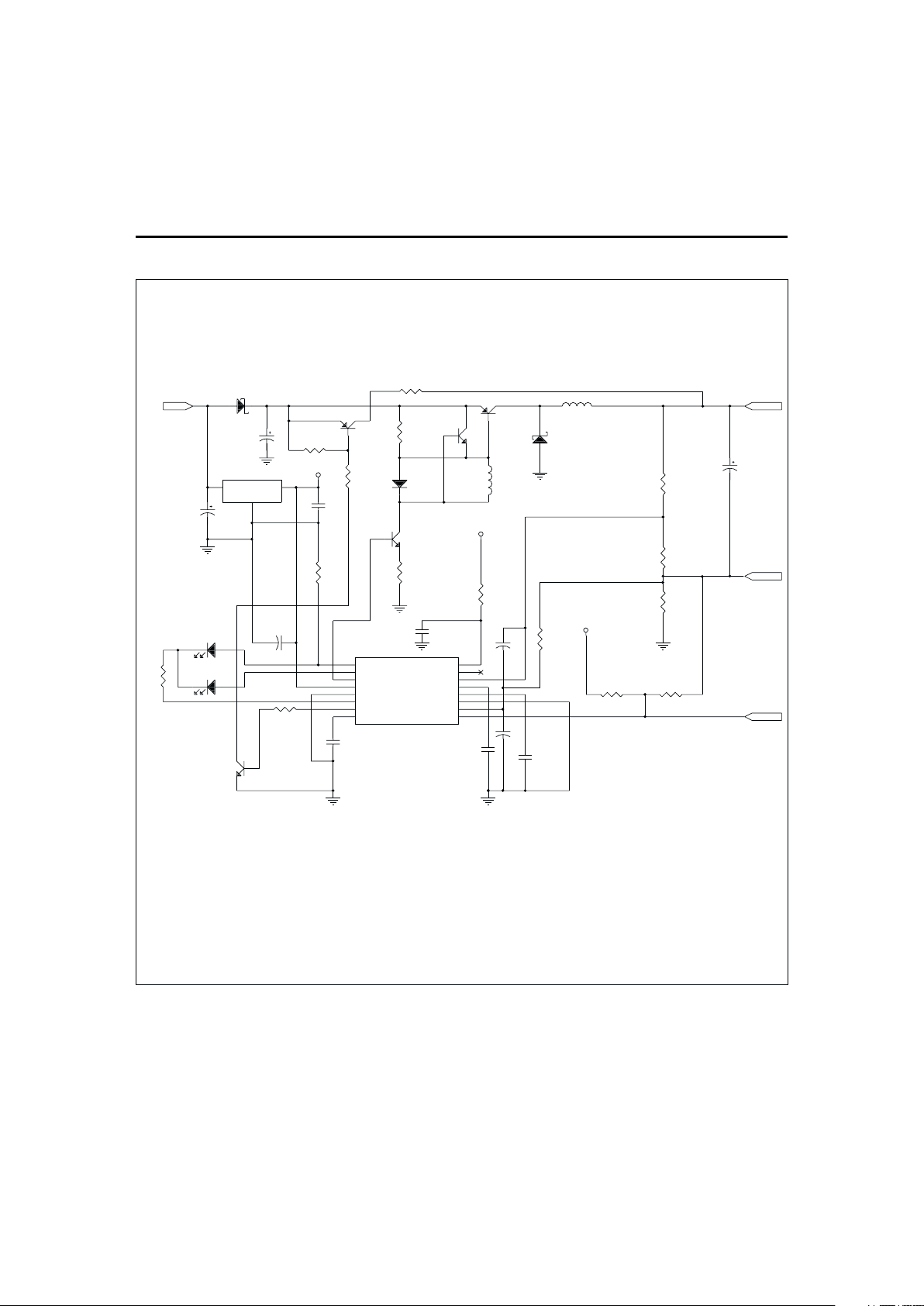

BD2954.eps

Voltage

Reference

Charge

Control

State

Machine

PWM

Regulator

Display

Control

Power-On

Reset

MTO

Timer

Oscillator

DSEL

CSEL

LED

1

LED

2

BTST

CHG

LCOM

MOD

ICOMP

V

CC

TM TPWMITERM

V

SS

TS

VCOMP

BAT

SNS

Figure 1. Functional Block Diagram

4

bq2954

Power-On

Reset

Fault

CHG = 0

Mod = 0 No Action

Latch DSEL/CSEL Inputs

Latch DSEL/CSEL Inputs

FGbg295401.eps

VCC "Up"

S01

S02

S03a

S03b

VOLTA GE

REGULATION

CURRENT

REGULATION

CONDITIONING

QUALIFICATION

DONE

Full Charge

Indication

I

SNS

= I

MIN

Temp Not Hot andV

BAT

V

RCHG

1s Hold Time after V

BAT

< V

RCHG

V

BAT

V

RCHG

V

BAT

> V

HCO

Volt Fault

V

BAT

> V

HCO

Volt Fault

V

BAT

> V

HCO

or T = MTO

Volt or Time Fault

T = MTO/25

Time Fault

Temp Not Valid

Temp Valid

Temp Not Valid

Temp Not Valid

Temp Not Valid

V

BAT

< 0.8V Reset Faults

0.8V > V

BAT

> V

HCO

Hold Time

Hold-off Faults

CHG = 0

Battst = 1

I

SNS

= I

MAX: VBAT

V

REG

T MTO

Hold Time

CHG = 1

V

BAT

< V

MIN: ISNS

= I

MAX/

10

Hold Time

CHG = 1

V

BAT

= V

REG: I

MAX

> ISNS

> I

TRMN

T MTO

CHG = 1

V

BAT

> V

RCHG

Hold-off MOD

V

RCHG

< V

BAT

< V

HCO

CHG = 1

V

HCO

< V

BAT

>0.8V

Reset MTO

V

BAT

V

MIN

Reset MTO

V

BAT

= V

REG

T = MTO

I

SNS

= I

TRM

Temp Hot

Battery Removal

Volt or

Time Fault

S04

<

<

<

<

<

>

V

BAT

Voltages:

V

RCHG

= 1.92V 0.5V

V

MIN

= 1.50V 0.5V

V

REG

= 2.05V

V

HCO

= 2.30V

Volt Fault: When V

BAT

> V

HCO

Time Fault: When T = MTO/4 in State S02 or T = MTO in S03a

Hold Time: A V

HCO

Fault or State charge held off for 0.740s to 1.12s

Figure 2. bq2954 Charge Algorithm

5

bq2954

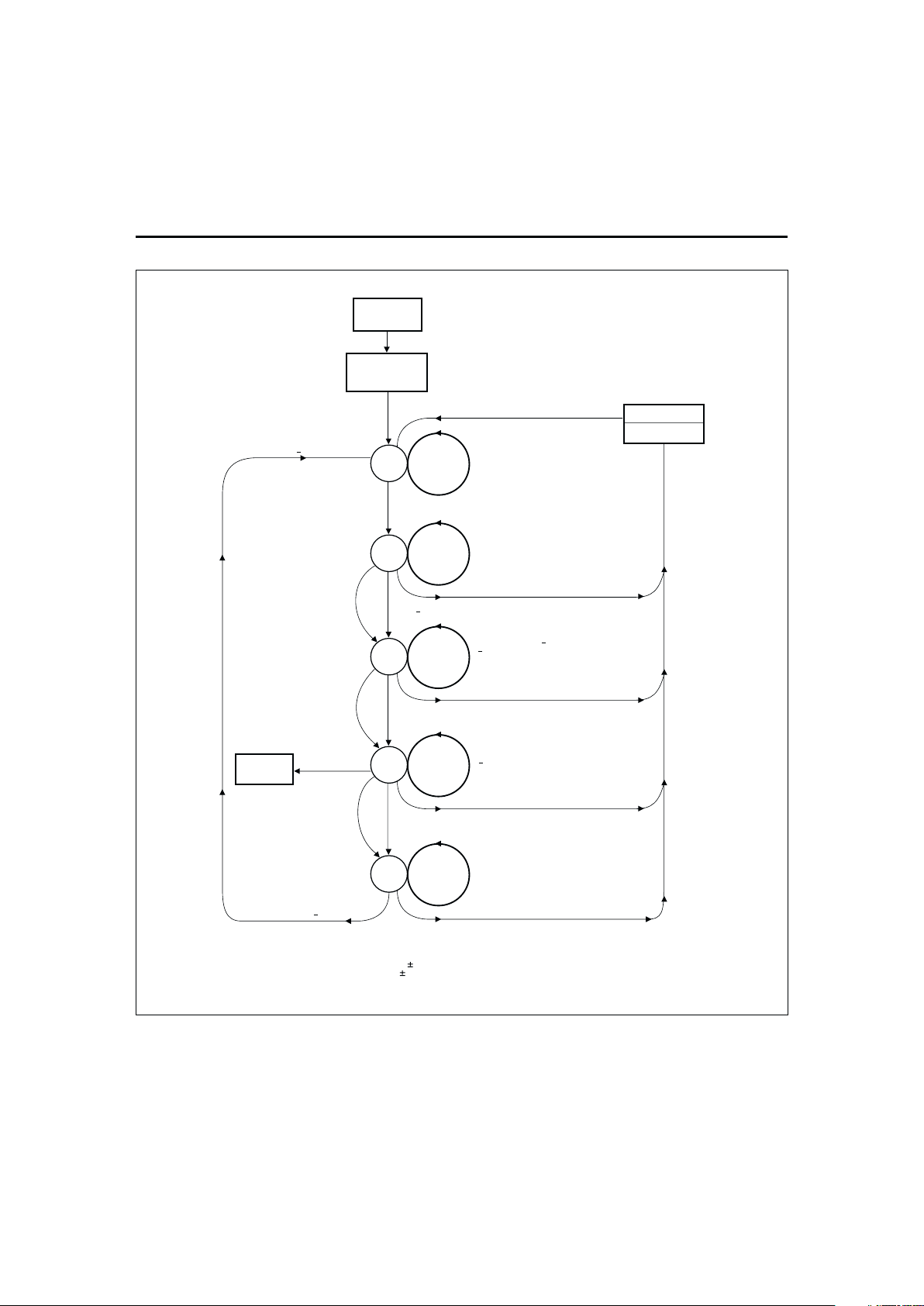

BAT+

R14

RB1

C11

10uF

20V

PCS4106

L2

47uH

D5

B130DI

L1

10 uH

R1

1K

5V

C2

1uF

R2

4.7K

R5

10K

Q1

FMMT3906

Q2

FMMt3904

Q5

FZT789A

D1

1N4148

VDC

C3

1uF

25V

R4

10K

C10

47uF

25V

OUT

G

N

D

IN

U2

ZMR500

D4

B130DI

8-24VDC ±10%

5V

C4

0.1 uF

R6

10K

R9

220

R10

62K

Q3

FMMT451

R7

1K

BAT-

R8

0.25 5%

0.5W

R15

RB2

TEM+

R12

8.45K

1%

C1

0.1uF

2954sch9/23/98

5V

C7

0.01uF

C8

1000pF

R11

4.32K

1%

TM

1

CHG

2

BAT

3

VCOMP

4

ICOMP

5

ITERM

6

SNS

7

TS

8

TPWM

9

BTST

10

LCOM

11

VSS

12

VCC

13

MOD

14

LED1/CSEL

15

LED2/DSEL

16

U1

bq2954

C5

0.1uF

C9

470pF

R3

10K

C6

0.1 uF

Q4

FMMT3904

R13

1K

D2

GRREN

D3

RED

3. TEMP = 0-45˚C,

4. Frequency = 200kHz

2. MTO = 3 HRS, I

FULL

= I

MAX

/5, I

TERM

= I

MAX

/10

1. I

MAX

= 1.0A, Vreg = 4.2V ± 1% PER CELL

Figure 3. High-Efficiency Li-Ion Charger for 1–4 Cells

time-out limit tQT(i.e., the battery has failed short), the

bq2954 enters the Fault state. Then t

QT

is set to 25% of

t

MTO

.IfV

MIN

is achieved before expiration of the time

limit, the bq2954 begins fast charging.

Once in the Fault state, the bq2954 waits until V

CC

is cy

cled or a new battery insertion is detected. It then starts a

new charge cycle and begins the qualification process again.

Charge Status Display

Charge status is indicated by the LED driver outputs

LED

1

–LED2. Three display modes (Tables 1– 3) are avail

able in the bq2954 and are selected by configuring pin

DSEL. Table 1 illustrates a normal fast charge cycle, Ta

ble 2 a recharge-after-fast-charge cycle, and Table 3 an ab

normal condition.

Configuring the Display Mode, I

FULL/IMIN

,

and I

SENSE

DSEL/LED

2

and CSEL/LED1are bi-directional pins

with two functions: as LED driver pins (output) and as

programming pins (input). The selection of pull-up,

pull-down, or no-resistor programs the display mode on

DSEL as shown in Tables 1 through 3. A pull-down or

no-resistor programs the current-sense mode on CSEL.

The bq2954 latches the programming data sensed on

the DSEL and CSEL input when V

CC

rises to a valid

level. The LEDs go blank for approximately 400ms (typi

-

cal) while new programming data are latched.

When fast charge reaches a condition where the charg

-

ing current drops below I

FULL

, the LED1 and LED2

outputs indicate a full-battery condition. Fast charge

terminates when the charging current drops below the

6

bq2954

GR295401.eps

V

BAT

I

BAT

V

REG

I

MAX

V

MIN

I

COND

I

FULL

I

MIN

Battery

Absent

Qualification

Charge

Complete

Low

Low

Low

Low

Low

Low

Low

High

Low

High

MTO

Fast Charge

Current

Regulate

LED1

LED2

LED1

LED2

LED1

LED2

CHG

BTST

CHG

BTST

High

Low

High

Low

High

Low

High

Low

High

High

High

Low

High

Low

High

Low

High

Low

High

Low

High

Low

High

Low

High

High

High

Low

High

Low

Low

High

Low

High

Low

High

High

Low

High

Low

Low

High

Low

High

Low

High

Low

Low

Low

Low

Mode 1

(DSEL = 0)

Mode 2

(DSEL = 1)

Mode 3

(DSEL = F)

Mode 1

and 2

Mode 3

Time

Voltage

Regulate

Current

Taper

I

FULL

Detect

Table 1. Normal Fast Charge Cycle

Loading...

Loading...