Features

ä

Power monitoring and switching

for 3-volt battery-backup applications

ä

Write-protect control

ä

2-input decoder for control of up

to 4 banks of SRAM

ä

3-volt primary cell inputs

ä

Less than 10ns chip-enable

propagation delay

ä

5% or 10% supply operation

General Description

The CMOS bq2204A SRAM Nonvolatile Controller Unit provides all

necessary functions for converting

up to four banks of standard CMOS

SRAM into nonvolatile read/write

memory.

A precision comparator monitors the 5V

V

CC

input for an out-of-tolerance condition. When out-of-tolerance is detected,

the four conditioned chip-enable outputs

are forced inactive to write-protect up to

four banks of SRAM.

During a power failure, the external

SRAMs are switched from the V

CC

supply to one of two 3V backup supplies. On a subsequent power-up, the

SRAMs are write-protected until a

power-validconditionexists.

During power-valid operation, a

two-input decoder transparently selects one of up to four banks of

SRAM.

1

Dec. 1992B

bq2204A

X4 SRAM Nonvolatile Controller Unit

1

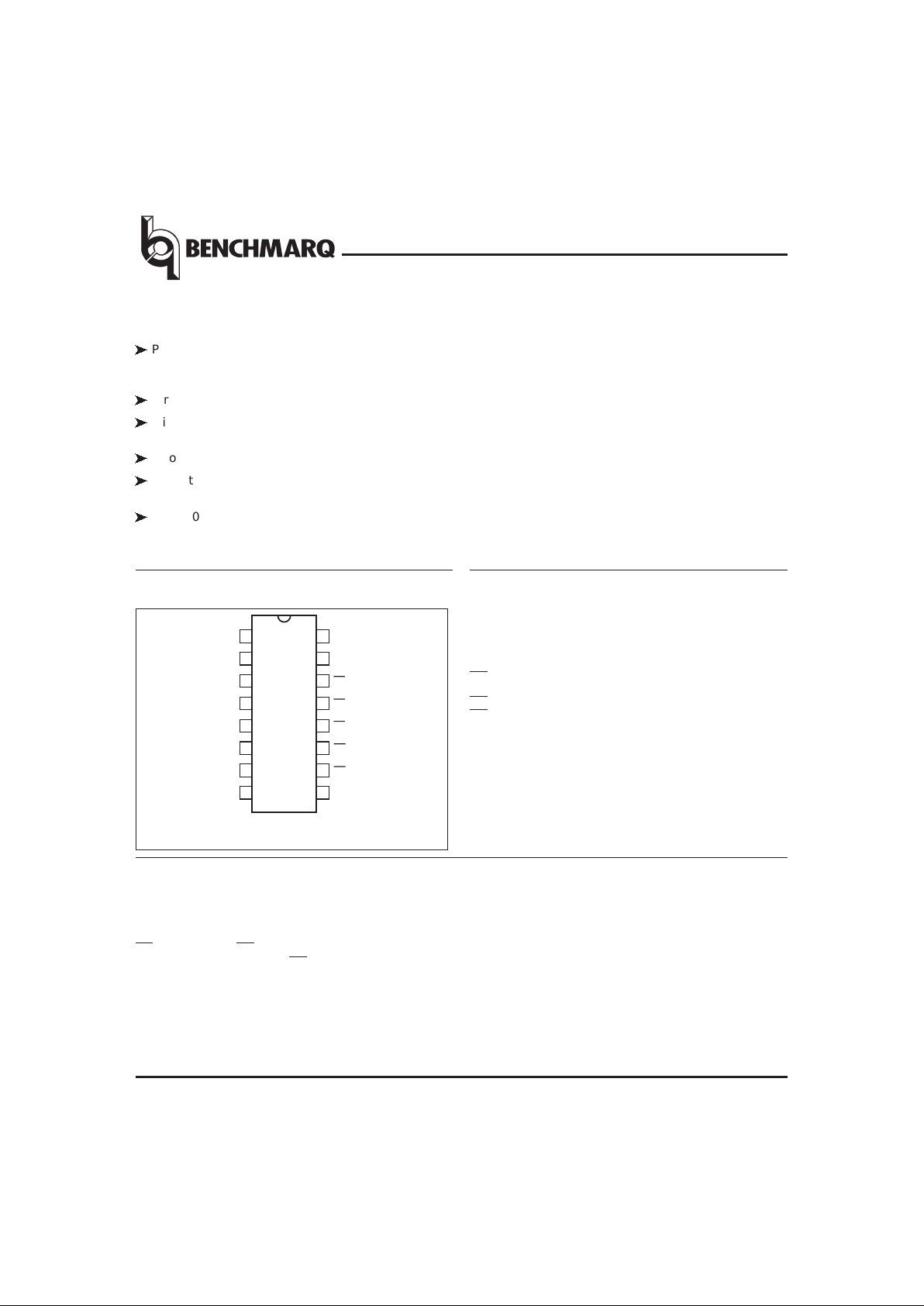

PN220401.eps

16-Pin Narrow DIP or SOIC

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

V

CC

BC

1

CE

CE

CON1

CE

CON2

CE

CON3

CE

CON4

NC

V

OUT

BC

2

NC

A

B

NC

THS

V

SS

Pin Names

V

OUT

Supply output

BC1–BC23 volt primary backup cell inputs

THS Threshold select input

CE chip-enable active low input

CE

CON1

– Conditioned chip-enable outputs

CE

CON4

A–B Decoder inputs

NC No connect

V

CC

+5 volt supply input

V

SS

Ground

Up to four banks of CMOS static RAM can be batterybacked using the V

OUT

and conditioned chip-enable output pins from the bq2204A. As VCCslews down during

a power failure, the conditioned chip-enable outputs

CE

CON1

through CE

CON4

are forced inactive independ-

ent of the chip-enable input CE

.

This activity unconditionally write-protects the external

SRAM as V

CC

falls below an out-of-tolerance threshold

V

PFD.VPFD

is selected by the threshold select input pin,

THS. If THS is tied to VSS, the power-fail detection occurs

at 4.62V typical for 5% supply operation.

If THS is tied to V

CC

, power-fail detection occurs at

4.37V typical for 10% supply operation. The THS pin

must be tied to VSSor VCCfor proper operation.

If a memory access is in process to any of the four external

banks of SRAM during power-fail detection, that memory

cycle continues to completion before the memory is writeprotected. If the memory cycle is not terminated within

time t

WPT

, all four chip-enable outputs are unconditionally

driven high,write-protectingthecontrolledSRAMs.

Pin Connections

Functional Description

As the supply continues to fall past V

PFD

, an internal

switching device forces V

OUT

to one of the two external

backup energy sources. CE

CON1

through CE

CON4

are

held high by the V

OUT

energy source.

During power-up, V

OUT

is switched back to the 5V supply as VCCrises above the backup cell input voltage

sourcing V

OUT

. Outputs CE

CON1

through CE

CON4

are

held inactive for time t

CER

(120ms maximum) after the

power supply has reached V

PFD

, independent of the CE

input,toallowforprocessorstabilization.

During power-valid operation, the CE

input is passed

through to one of the four CE

CON

outputs with a propagation delay of less than 10ns. The CE input is output

on one of the four CE

CON

output pins depending on the

level of the decode inputs at A and B as shown in the

Truth Table.

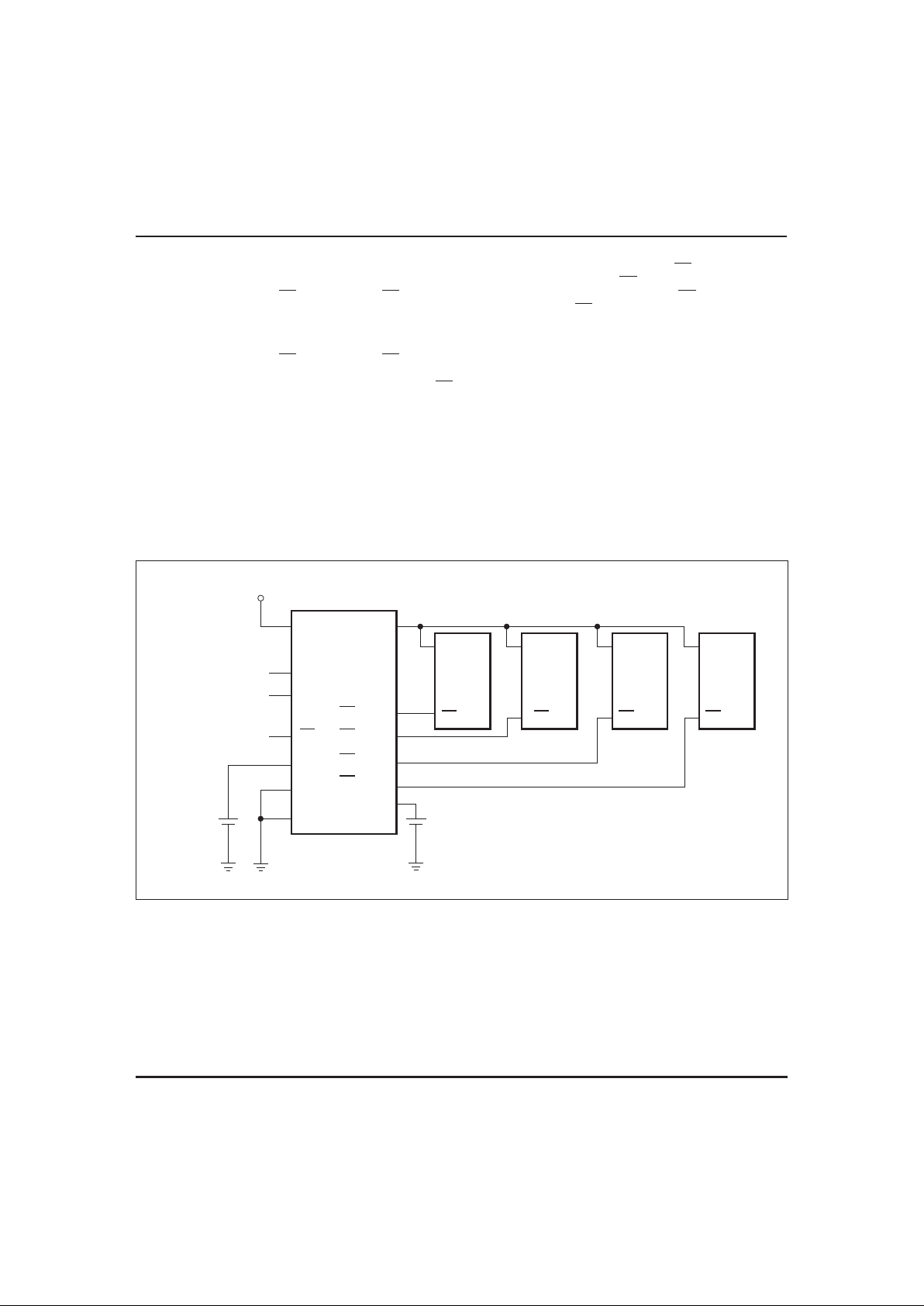

The A and B inputs are usually tied to high-order address pins so that a large nonvolatile memory can be designed using lower-density memory devices. Nonvolatility

and decoding are achieved by hardware hookup as shown

in Figure 1.

2

bq2204A

FG220401.eps

CE

BC

2

THS

V

SS

V

OUT

bq2204A

V

CC

CE

CMOS

SRAM

V

CC

5V

From Address

Decoder

CE

CON2

BC

1

CE

CON1

V

CC

CE

CMOS

SRAM

3V

Primary

Cell

3V

Primary

Cell

B

A

V

CC

CE

CMOS

SRAM

V

CC

CE

CMOS

SRAM

CE

CON3

CE

CON4

Figure 1. Hardware Hookup (5% Supply Operation)

Dec. 1992B

Energy Cell Inputs—BC1,BC

2

Two backup energy source inputs are provided on the

bq2204A. The BC1and BC2inputs accept a 3V primary

battery (non-rechargeable), typically some type of lithium chemistry. If no primary cell is to be used on either

BC1or BC2,theunusedinputshouldbetiedtoVSS.

V

CC

falling below V

PFD

starts the comparison of BC

1

and BC2. The BC input comparison continues until V

CC

rises above VSO. Power to V

OUT

begins with BC1and

switches to BC2only when V

BC1

is less than V

BC2

mi-

nus V

BSO

. The controller alternates to the higher BC

voltage only when the difference between the BC input

voltages is greater than V

BSO

. Alternating the backup

batteries allows one-at-a-time battery replacement and

efficient use of both backup batteries.

To prevent battery drain when there is no valid data to

retain, V

OUT

and CE

CON1-4

are internally isolated from

BC1and BC2by either of the following conditions:

■

Initial connection of a battery to BC1or BC2,or

■

Presentation of an isolation signal on CE.

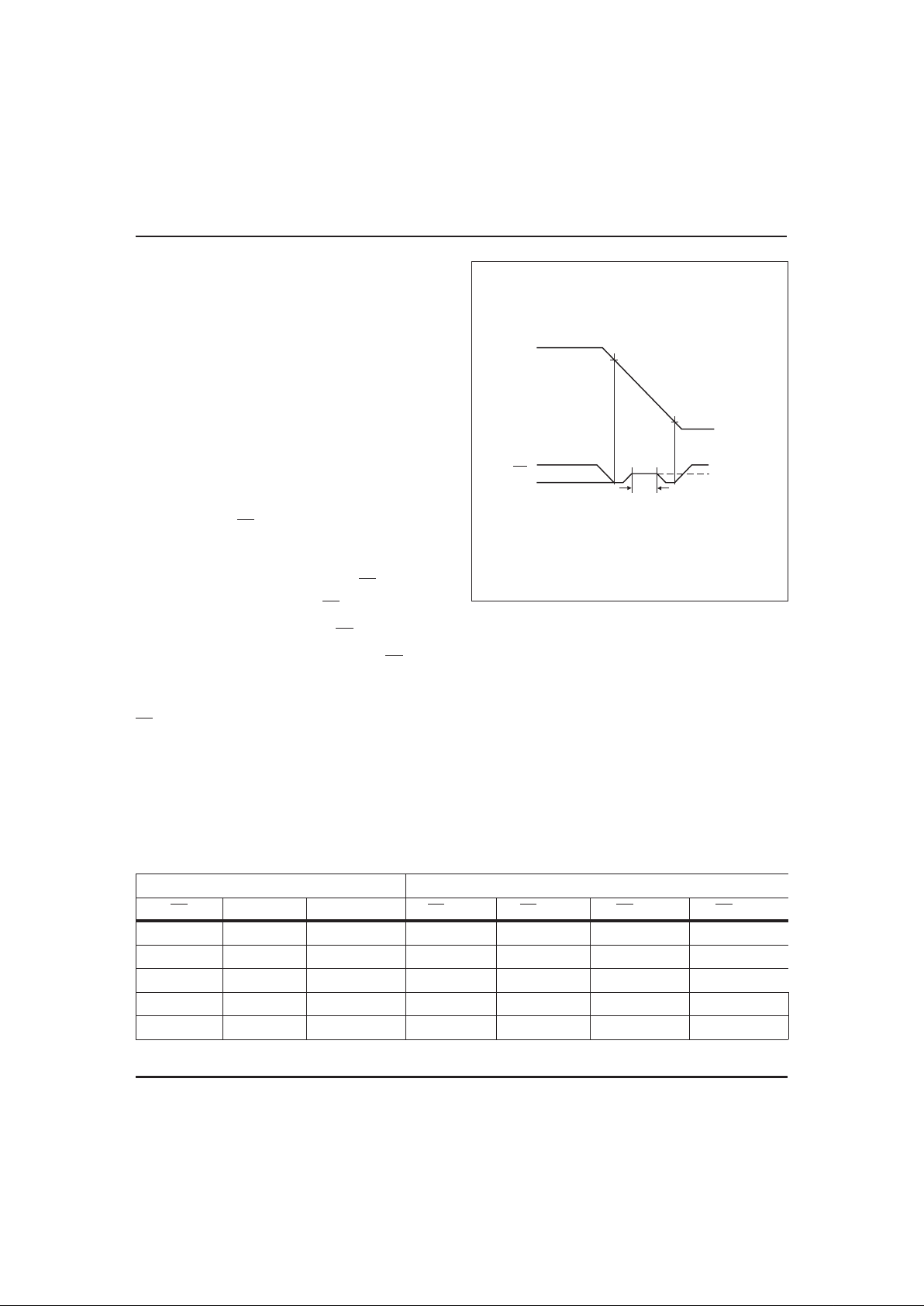

A valid isolation signal requires CE

low as VCCcrosses

both V

PFD

and VSOduring a power-down. See Figure 2.

Between these two points in time, CE must be brought

to the point of (0.48 to 0.52)*VCCand held for at least

700ns. The isolation signal is invalid if CE exceeds

0.54*VCCat any point between VCCcrossing V

PFD

and

VSO.

The appropriate battery is connected to V

OUT

and

CE

CON1–4

immediately on subsequent application and

removal of VCC.

3

TD220201.eps

V

CC

CE

V

PFD

V

SO

0.5 V

CC

700ns

Figure 2. Battery Isolation Signal

Dec. 1992 B

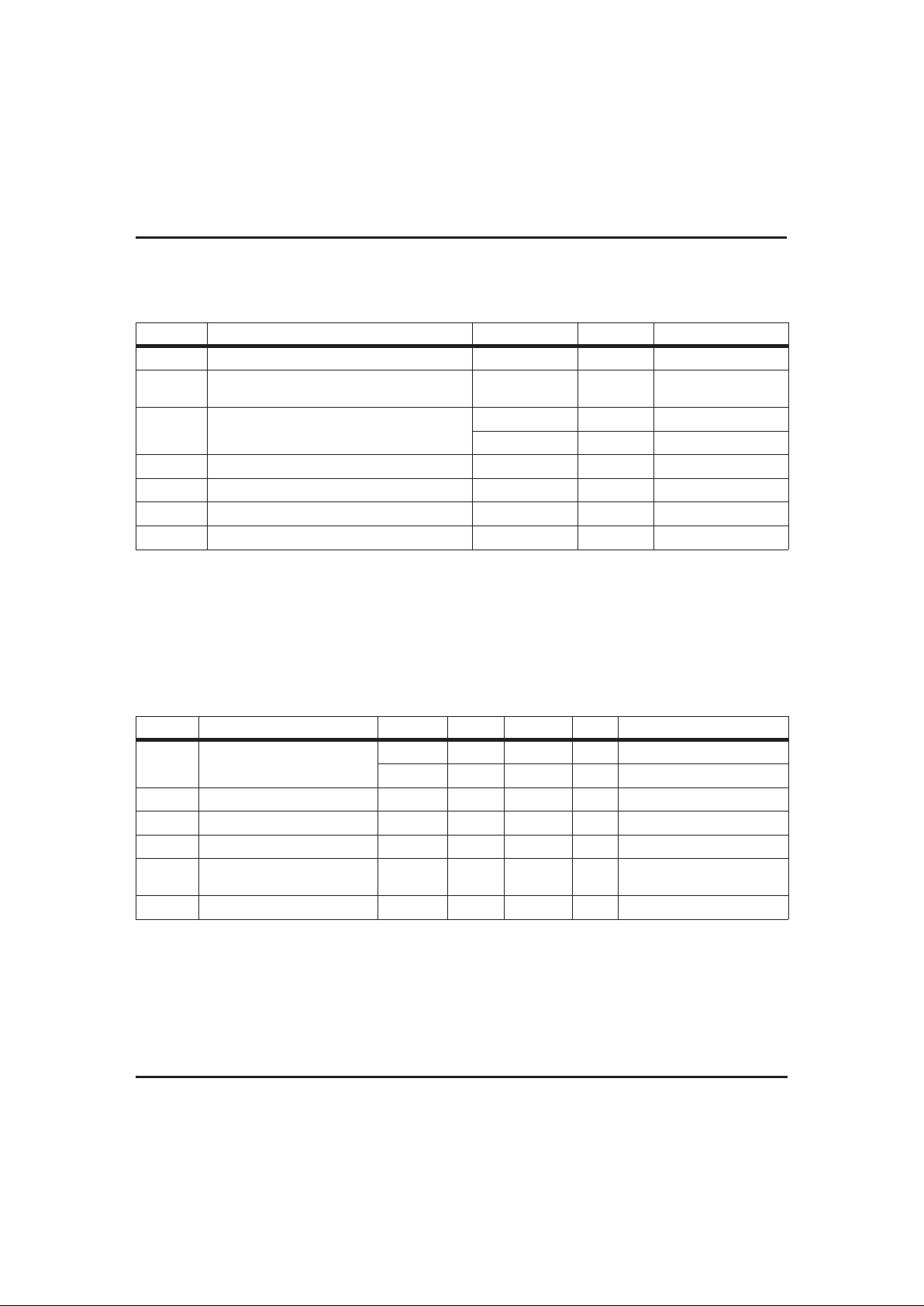

Truth Table

Input Output

CE ABCE

CON1

CE

CON2

CE

CON3

CE

CON4

HX X H H H H

LL L L H H H

LH L H L H H

LL H H H L H

LH H H H H L

bq2204A

4

bq2204A

Recommended DC Operating Conditions (T

A=TOPR

)

Symbol Parameter Minimum Typical Maximum Unit Notes

V

CC

Supply voltage

4.75 5.0 5.5 V THS = V

SS

4.50 5.0 5.5 V THS = V

CC

V

SS

Supply voltage 0 0 0 V

V

IL

Input low voltage -0.3 - 0.8 V

V

IH

Input high voltage 2.2 - VCC+ 0.3 V

V

BC1

,

V

BC2

Backup cell voltage 2.0 - 4.0 V VCC<V

BC

THS Threshold select -0.3 - VCC+ 0.3 V

Note: Typical values indicate operation at TA= 25°C, VCC=5VorVBC.

Absolute Maximum Ratings

Symbol Parameter Value Unit Conditions

V

CC

DC voltage applied on VCCrelative to V

SS

-0.3 to +7.0 V

V

T

DC voltage applied on any pin excluding V

CC

relative to V

SS

-0.3 to +7.0 V V

T

≤

V

CC

+ 0.3

T

OPR

Operating temperature

0 to 70 °C Commercial

-40 to +85 °C Industrial “N”

T

STG

Storage temperature -55 to +125 °C

T

BIAS

Temperature under bias -40 to +85 °C

T

SOLDER

Soldering temperature 260 °C For 10 seconds

I

OUT

V

OUT

current 200 mA

Note: Permanent device damage may occur if Absolute Maximum Ratings are exceeded.Functional operation

should be limited to the Recommended DC Operating Conditions detailed in this data sheet. Exposure to conditions beyond the operational limits for extended periods of time may affect device reliability.

Dec. 1992 B

Loading...

Loading...