Page 1

Instruction Manual

TCS101

SPI-3 and SPI-4.2 Bus Software Support

071-1171-01

www.tektronix.com

Page 2

Copyright © Tektronix, Inc. All rights reserved.

Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this public ation supercedes

that in all previously published material. Specifications and price c hange privileges reserved.

Tektronix, Inc., P.O. Box 500, Beaverton, OR 97077

TEKTRONIX and TEK are registered trademarks of Tektronix, Inc.

Page 3

SOFTWARE WARRANTY

Tektronix warrants that the media on which this software product is furnished and the encoding of the programs on

the media will be free from defects in materials and workmanship for a period of three (3) months from the date of

shipment. If a medium or encoding proves defective during the warranty period, Tektronix will provide a

replacement in exchange for the defective medium. Except as to the media on which this software product is

furnished, this software product is provided “as is” without warranty of any kind, either express or implied.

Tektronix does not warrant that the functions contained in this software product will meet Customer’s

requirements or that the operation of the programs will be uninterrupted or error-free.

In order to obtain service under this warranty, Customer must notify Tektronix of the defect before the expiration

of the warranty period. If Tektronix is unable to provide a replacement that is free from defects in materials and

workmanship within a reasonable time thereafter, Customer may terminate the license for this software product

and return this software product and any associated materials for credit or refund.

THIS WARRANTY IS GIVEN BY TEKTRONIX IN LIEU OF ANY OTHER WARRANTIES, EXPRESS

OR IMPLIED. TEKTRONIX AND ITS VENDORS DISCLAIM ANY IMPLIED WARRANTIES OF

MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. TEKTRONIX’

RESPONSIBILITY TO REPLACE DEFECTIVE MEDIA OR REFUND CUSTOMER’S PAYMENT IS

THE SOLE AND EXCLUSIVE REMEDY PROVIDED TO THE CUSTOMER FOR BREACH OF THIS

WARRANTY. TEKTRONIX AND ITS VENDORS WILL NOT BE LIABLE FOR ANY INDIRECT,

SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES IRRESPECTIVE OF WHETHER

TEKTRONIX OR THE VENDOR HAS ADVANCE NOTICE OF THE POSSIBILITY OF SUCH

DAMAGES.

Page 4

Page 5

Table of Contents

Getting Started

Preface ix...................................................

Manual Conventions ix..............................................

Contacting Tektronix x.............................................

Support Package Descri ption 1--1.......................................

Disassembly Support 1--1..........................................

Triggering Support 1--2...........................................

Logic Analyzer Software Compatibility 1--2..............................

Logic Analyzer Configuration 1--2......................................

Module Requirements 1--2.........................................

Probe Requirements 1--3..........................................

Requirements and Restrictions 1--3......................................

Hardware Reset 1--4..............................................

Clock Rate 1--4..................................................

Setup/Hold Time Requirements 1--4.................................

Nonintrusive Acquisition 1--4......................................

Limitations of the Support 1--4.........................................

Connecting the Logic Analyzer to a Target System 1--5.....................

Labeling P6880 and P6860 Probes 1--5...................................

Operating Basics

Setting Up the Support 2--1.....................................

Installing the Support Software 2--1.....................................

Support Package Setups 2--2...........................................

Clocking Options 2--2................................................

SPI3_TX and SPI3_RX 2--2........................................

SPI4 and SPI4_LVTTL 2--3........................................

Acquiring and Viewing Disassembled Data 2--5....................

Acquiring Data 2--5..................................................

Changing How Data is Displayed 2--5...................................

Optional Display Selections 2--6....................................

Bus Specific Fields 2--6...........................................

Labels for Bus Cycles 2--9.............................................

Viewing Disassembled Data 2--11........................................

All Display Format in SPI3_TX and SPI3_RX 2--11.....................

Packet Display Format in SPI3_TX and SPI3_RX 2--11...................

All Display Format in SPI4 and SPI4_LVTTL 2--12......................

Packet & Control Display Format in SPI4 and SPI4_LVTTL 2--12..........

Packet Only Display Format in SPI4 and SPI4_LVTTL 2--13..............

Trigger Programs 2--15..........................................

Loading Trigger Programs 2--15.........................................

SPI-3 Trigger Programs 2--15........................................

SPI-4.2 Trigger Programs 2--16......................................

TCS101 SPI-3 and SPI-4.2 Bus Software Support

i

Page 6

Table of Contents

Reference

SPI-4.2 Setup/Hold Time Adjustments 2--17........................

SPI4 Configurations and Settings 2--18....................................

SPI4 AutoDeskew Setup 2--18......................................

SPI4_LVTTL Configurations and Settings 2--18............................

SPI4_LVTTL AutoDeskew Setup 2--18...............................

Channel Group Definitions 3--1..................................

Channel Groups 3--1.................................................

Symbol and Channel Assignment Tables 3--5......................

Symbol Tables 3--5..................................................

Channel Assignment Tables 3--9........................................

SPI3_TX Channel Group Assignments 3--9............................

SPI3_RX Channel Group Assignments 3--14............................

SPI4 and SPI4_LVTTL Channel Group Assignments 3--18................

EasyTrigger Channel Assignments 3--29...............................

Clock and Qualifier Channel Assignments 3--35.........................

Signals Required for Clocking and Disassembly 3--37....................

Signal Source To Probe Connections 3--39.................................

Connections for SPI3_TX Support 3--40...............................

Connections for SPI3_RX Support 3--42...............................

Connections for SPI4 and SPI4_LVTTL Supports 3--44...................

Signal Acquisition 3--49.........................................

Signal Acquisition in SPI-3 3--49.....................................

Signal Acquisition in SPI-4.2 3--50...................................

Specifications

Index

Specification Table 4--1...............................................

ii

TCS101 SPI-3 and SPI-4.2 Bus Software Support

Page 7

List of Figures

Table of Contents

Figure 2--1: Example of All display format for the SPI4

support package 2--12.......................................

Figure 2--2: Example of Packet & Control display format for the

SPI4 support package 2--13...................................

Figure 2--3: Example of Packet Only display format for the SPI4

support package 2--14.......................................

Figure 3--1: Sample of P6860 High-Density probe land footprint 3--40..

Figure 3--2: Sample of P6880 Differential probe land footprint 3--45....

Figure 3--3: Example of a timing diagram for the transmit bus with

clocking option “Active Cycles” selected 3--49...................

Figure 3--4: Example of a timing diagram for the receive bus with

clocking option “Active Cycles” selected 3--50...................

Figure 3--5: Example of a timing diagram for the SPI-4.2 bus 3--51.....

TCS101 SPI-3 and SPI-4.2 Bus Software Support

iii

Page 8

Table of Contents

List of Tables

Table 1--1: Module requirements for the TCS101 product 1--3.......

Table 1--2: Probe requirements for the TCS101 product 1--3.........

Table 1--3: Setup/Hold time requirements for the TCS101

product 1--4..............................................

Table 2--1: Logic analyzer disassembly display options for SPI3_TX

and SPI3_RX support packages 2--6..........................

Table 2--2: Logic analyzer disassembly display options for SPI4 and

SPI4_LVTTL support packages 2--6..........................

Table 2--3: Bus specific fields for SPI3_TX and SPI3_RX support

packages 2--6.............................................

Table 2--4: Bus specific fields for SPI4 and SPI4_LVTTL support

packages 2--8.............................................

Table 2--5: Labels in Packet/Cell Details column for SPI3_TX and

SPI3_RX support packages 2--9..............................

Table 2--6: Labels in Packet/Cell Details column for SPI4 and

SPI4_LVTTL support packages 2 --10..........................

Table 2--7: Labels in FIFO Status column for SPI4 and

SPI4_LVTTL support packages 2 --10..........................

Table 3--1: SPI3_TX channel group names 3--1....................

Table 3--2: SPI3_RX channel group names 3--1....................

Table 3--3: SPI4 and SPI4_LVTTL channel group names 3--2........

Table 3--4: SPI3_TX_Ctrl group symbol table definitions 3--5........

Table 3--5: SPI3_TX_Trig_Ctrl group symbol table definitions 3--6...

Table 3--6: SPI3_TX Parity group symbol table definitions 3--6.......

Table 3--7: SPI3_RX_Ctrl group symbol table definitions 3--6........

Table 3--8: SPI3_RX_Trig_Ctrl group symbol table definitions 3--7...

Table 3--9: SPI3_RX Parity group symbol table definitions 3--8.......

Table 3--10: SPI4_Ctrl/SPI4_LVTTL_Ctrl group symbol table

definitions 3--8............................................

Table 3--11: Address group assignments for SPI3_TX support

package 3--10..............................................

Table 3--12: DAT group assignments for SPI3_TX support

package 3--10..............................................

Table 3--13: Control group assignments for SPI3_TX support

package 3--11..............................................

iv

TCS101 SPI-3 and SPI-4.2 Bus Software Support

Page 9

Table of Contents

Table 3--14: DTPA group assignments for SPI3_TX support

package 3--12..............................................

Table 3--15: Misc group assignments for SPI3_TX support

package 3--12..............................................

Table 3--16: Trig_Control group assignments for SPI3_TX support

package 3--12..............................................

Table 3--17: Trig_DAT[7:0] group assignments for SPI3_TX

support package 3--13.......................................

Table 3--18: Trig_DAT[31:0] group assignments for SPI3_TX

support package 3--13.......................................

Table 3--19: DAT group assignments for SPI3_RX support

package 3--14..............................................

Table 3--20: Control group assignments for SPI3_RX support

package 3--16..............................................

Table 3--21: Trig_Control group assignments for SPI3_RX support

package 3--16..............................................

Table 3--22: Trig_DAT[7:0] group assignments for SPI3_RX support

package 3--16..............................................

Table 3--23: Trig_DAT[31:0] group assignments for SPI3_RX support

package 3--17..............................................

Table 3--24: $CTL group assignments for SPI4 and SPI4_LVTTL

support packages 3--19......................................

Table 3--25: $DAT0 group assignments for SPI4 and SPI4_LVTTL

support packages 3--19......................................

Table 3--26: $DAT1 group assignments for SPI4 and SPI4_LVTTL

support packages 3--20......................................

Table 3--27: $DAT2 group assignments for SPI4 and SPI4_LVTTL

support packages 3--20......................................

Table 3--28: $DAT3 group assignments for SPI4 and SPI4_LVTTL

support packages 3--20......................................

Table 3--29: $DAT4 group assignments for SPI4 and SPI4_LVTTL

support packages 3--21......................................

Table 3--30: $DAT5 group assignments for SPI4 and SPI4_LVTTL

support packages 3--21......................................

Table 3--31: $DAT6 group assignments for SPI4 and SPI4_LVTTL

support packages 3--21......................................

Table 3--32: $DAT7 group assignments for SPI4 and SPI4_LVTTL

support packages 3--22......................................

Table 3--33: $DAT8 group assignments for SPI4 and SPI4_LVTTL

support packages 3--22......................................

Table 3--34: $DAT9 group assignments for SPI4 and SPI4_LVTTL

support packages 3--22......................................

TCS101 SPI-3 and SPI-4.2 Bus Software Support

v

Page 10

Table of Contents

Table 3--35: $DAT10 group assignments for SPI4 and SPI4_LVTTL

support packages 3--23......................................

Table 3--36: $DAT11 group assignments for SPI4 and SPI4_LVTTL

support packages 3--23......................................

Table 3--37: $DAT12 group assignments for SPI4 and SPI4_LVTTL

support packages 3--23......................................

Table 3--38: $DAT13 group assignments for SPI4 and SPI4_LVTTL

support packages 3--24......................................

Table 3--39: $DAT14 group assignments for SPI4 and SPI4_LVTTL

support packages 3--24......................................

Table 3--40: $DAT15 group assignments for SPI4 and SPI4_LVTTL

support packages 3--24......................................

Table 3--41: $STAT0 group assignments for SPI4 support

package 3--25..............................................

Table 3--42: $STAT1 group assignments for SPI4 support

package 3--25..............................................

Table 3--43: DATA group assignments for SPI4 and SPI4_LVTTL

support packages 3--25......................................

Table 3--44: CTL[1:0] group assignments for SPI4 and SPI4_LVTTL

support packages 3--27......................................

Table 3--45: STAT group channel assignments for SPI4 support

package 3--27..............................................

Table 3--46: STAT group channel assignments for SPI4_LVTTL

support package 3--27.......................................

Table 3--47: STAT_A group channel assignments for SPI4 support

package 3--28..............................................

Table 3--48: STAT_B group channel assignments for SPI4 support

package 3--28..............................................

Table 3--49: SCLK group channel assignments for SPI4_LVTTL

support package 3--28.......................................

Table 3--50: CTL_TYPE_A group EasyTrigger channel assignments

for SPI4 and SPI4_LVTTL support packages 3--29..............

Table 3--51: CTL_TYPE_B group EasyTrigger channel assignments

for SPI4 and SPI4_LVTTL support packages 3--29..............

Table 3--52: CTL_TYPE_AB group EasyTrigger channel assignments

for SPI4 and SPI4_LVTTL support packages 3--30..............

Table 3--53: DAT_PORT_A group EasyTrigger channel assignments

for SPI4 and SPI4_LVTTL support packages 3--30..............

Table 3--54: DAT_PORT_B group EasyTrigger channel assignments

for SPI4 and SPI4_LVTTL support packages 3--31..............

Table 3--55: DAT_AB group EasyTrigger channel assignments for

SPI4 and SPI4_LVTTL support packages 3--31.................

vi

TCS101 SPI-3 and SPI-4.2 Bus Software Support

Page 11

Table of Contents

Table 3--56: DAT_BA group EasyTrigger channel assignments for

SPI4 and SPI4_LVTTL support packages 3--32.................

Table 3--57: DAT_A group channel EasyTrigger assignments for

SPI4 and SPI4_LVTTL support packages 3--34.................

Table 3--58: DAT_B group EasyTrigger channel assignments for SPI4

and SPI4_LVTTL support packages 3--34......................

Table 3--59: Clock channel assignments for SPI3_TX support

package 3--35..............................................

Table 3--60: Qualifier channel assignments for SPI3_TX support

package 3--35..............................................

Table 3--61: Clock channel assignments for SPI3_RX support

package 3--36..............................................

Table 3--62: Qualifier channel assignments for SPI3_RX support

package 3--36..............................................

Table 3--63: Clock and qualifier channel assignments for SPI4

support package 3--36.......................................

Table 3--64: Clock and qualifier channel assignments for

SPI4_LVTTL support package 3--36...........................

Table 3--65: SPI-3 transmit signals required for clocking and

disassembly 3--37...........................................

T able 3--66: SPI-3 receive signals required for clocking and

disassembly 3--37...........................................

Table 3--67: SPI-4.2 signals required for clocking and disassembly

for SPI4 support package 3--37...............................

Table 3--68: SPI-4.2 signals required for clocking and disassembly

for SPI4_LVTTL support package 3-- 38........................

Table 3--69: Recommended pin assignments for a Mictor connector

(component side) 3--39.......................................

Table 3--70: Pin connections for SPI3_TX support package 3--40......

Table 3--71: Pin connections for SPI3_RX support package 3--42......

Table 3--72: Pin connections for SPI4 and SPI4_LVTTL support

packages (Probe#3) 3--45....................................

Table 3--73: Pin connections for SPI4 and SPI4_LVTTL support

packages (Probe#2) 3--46....................................

Table 3--74: Pin connections for SPI4 support package for FIFO

Status LVDS signals (Probe#1) 3--47...........................

Table 3--75: Pin connections for SPI4_LVTTL support package for

FIFO Status LVTTL signals (P6880) 3--47......................

Table 3--76: Pin connections for SPI4_LVTTL support package for

FIFO Status LVTTL signals (P6860) 3--48......................

T able 4--1: Electrical specifications 4--1...........................

TCS101 SPI-3 and SPI-4.2 Bus Software Support

vii

Page 12

Table of Contents

viii

TCS101 SPI-3 and SPI-4.2 Bus Software Support

Page 13

Preface

This instruction manual contains specific information about the TCS101 software

product for the SPI-3 and SPI-4.2 buses and is part of a set of information on

how to operate this product on compatible Tektronix logic analyzers.

If you are familiar with operating bus support packages on the logic analyzer for

which the TCS101 product was purchased, you will probably only need this

instruction manual to set up and run the support.

If you are not familiar with operating bus support packages, you will need to

supplement this instruction manual with information on basic operations to set up

and run the support.

Information on basic operations of bus support packages is included with each

product. Each logic analyzer includes basic information that describes how to

perform tasks common to support packages on that platform. This information

can be in the form of logic analyzer online help, an installation manual, or a user

manual.

This manual provides detailed information on the following topics:

H Connecting the logic analyzer to the target system

Manual Conventions

H Setting up the logic analyzer to acquire data from the target system

H Acquiring and viewing disassembled data

This manual uses the following conventions:

H The term “disassembler” refers to the software that disassembles bus cycles

into packets and control information.

H The phrase “basic operations” refers to the logic analyzer online help, or the

user manual that covers the basic operations of the bus support.

H The phrase “logic analyzer” refers to the Tektronix logic analyzer for which

this product was purchased.

TCS101 SPI-3 and SPI-4.2 Bus Software Support

ix

Page 14

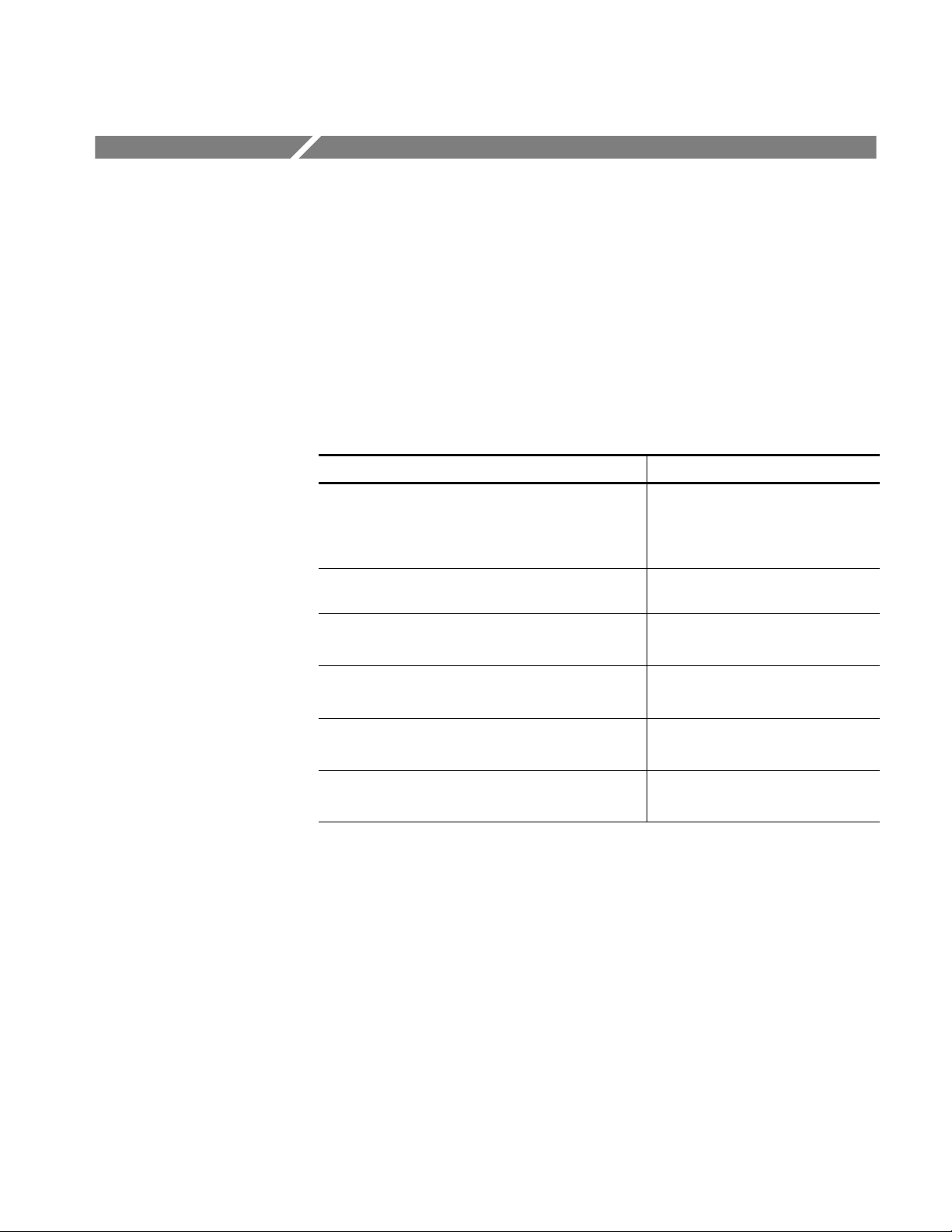

Contacting Tektronix

Preface

Phone 1-800-833-9200*

Address Tektronix, Inc.

Department or name (if known)

14200 SW Karl Braun Drive

P.O. Box 500

Beaverton, OR 97077

USA

Web site www.tektronix.com

Sales support 1-800-833-9200, select option 1*

Service support 1-800-833-9200, select option 2*

Technical support Email: techsupport@tektronix.com

1-800-833-9200, select option 3*

6:00 a.m. -- 5:00 p.m. Pacific time

* This phone number is toll free in North America. After office hours, please leave a

voice mail message.

Outside North America, contact a Tektronix sales office or distributor; see the

Tektronix web site for a list of offices.

x

TCS101 SPI-3 and SPI-4.2 Bus Software Support

Page 15

Getting Started

Page 16

Page 17

Getting Started

This section contains information on the TCS101 product and information on

connecting your logic analyzer to your target system.

Support Package Description

The TCS101 product acquires, decodes and displays the SPI-3 and SPI-4.2 bus

cycles. The support package allows you to acquire bus cycles with minimal

impact on the environment of the system.

The TCS101 product contains four acquisition support packages that have their

own setup software and disassemblers. A description of each support package is

listed here.

H SPI3_TX, for the SPI-3 Transmit Interface

H SPI3_RX, for the SPI-3 Receive Interface

H SPI4, for the SPI-4.2 Transmit and Receive interfaces with LVDS FIFO

Status signals

Disassembly Support

H SPI4_LVTTL, for the SPI-4.2 Transmit and Receive interfaces with LVTTL

FIFO Status signals

The disassembler decodes transmit and receive bus information of SPI-3 and

SPI-4.2 buses.

The SPI3_TX and SPI3_RX support packages acquire and decode bus behavior

at each clock cycle or at active clock cycles (see page 2--3). For SPI4 and

SPI4_LVTTL support packages, the bus behavior is acquired at all clock cycles

and decoded.

The disassembler decodes data in the following stages.

H Packet related information — start of packet, end of packet, payload (packet

data), physical port address, packet continuation and packet error (DIP-4)

H Control information, Training, and Idle information

H FIFO Status decoding in SPI4 and SPI4_LVTTL with DIP-2

The payloads are indexed with byte counts corresponding to a port address, so

that you can know how many bytes of data have been transmitted by or received

at a port.

TCS101 SPI-3 and SPI-4.2 Bus Software Support

1-- 1

Page 18

Getting Started

The ASCII characters corresponding to the payloads can be viewed by choosing

“Decode Payload as ASCII” option (on pages 2--8 and 2--9) in the bus specific

fields.

The SPI3_TX and SPI3_RX support packages display the calculated parity bit

for each valid 8-bit or 32-bit data on the data bus.

After acquisition, the TCS101 product supports filtering based on the physical

port address (see pages 2--7 and 2--8).

To use this support package efficiently refer to the following documents:

H System Packet Interface Level 3 (SPI-3): OC-48 System Interface for

Physical and Link Layer Devices {Optical Internetwork Forum, June 2000,

OIF-SPI3-01.0}

H POS-PHY Level 3, Saturn Compatible Packet Over SONET Interface

Specification for Physical and Link Layer Devices {PMC -Sierra Inc.,

Issue 4: June 2000, PMC-1980495}

H System Packet Interface Level 4 (SPI-4) Phase 2: OC-192 System Interface

for Physical and Link Layer Devices {Optical Internetwork Forum, January

2001, OIF-SPI4-02.0}

H POS-PHY Level 4, A Saturn Packet and Cell Interface Specification for

OC192 SONET/SDH and 10 Gigabit Ethernet {PMC-Sierra Inc., Issue 6:

February 2001, PMC-1991635}

Triggering Support

The SPI3_TX and SPI3_RX support packages provide an EasyTrigger library to

trigger on Port Address, control signals like Start -of-Packet and End-of-Packet,

Erroneous Packet, and 8-bit or 32-bit Packet Data. The SPI4 and SPI4_LVTTL

support packages provide an EasyTrigger library to trigger on control words and

packet data.

Logic Analyzer Software Compatibility

The label on the bus support CD-ROM states which version of logic analyzer

software this support package is compatible with.

Logic Analyzer Configuration

The TCS101 product allows a choice of required minimum module configurations.

Module Requirements

1-- 2 TCS101 SPI-3 and SPI-4.2 Bus Software Support

Table 1--1 shows the module requirements for the TCS101 product.

Page 19

Getting Started

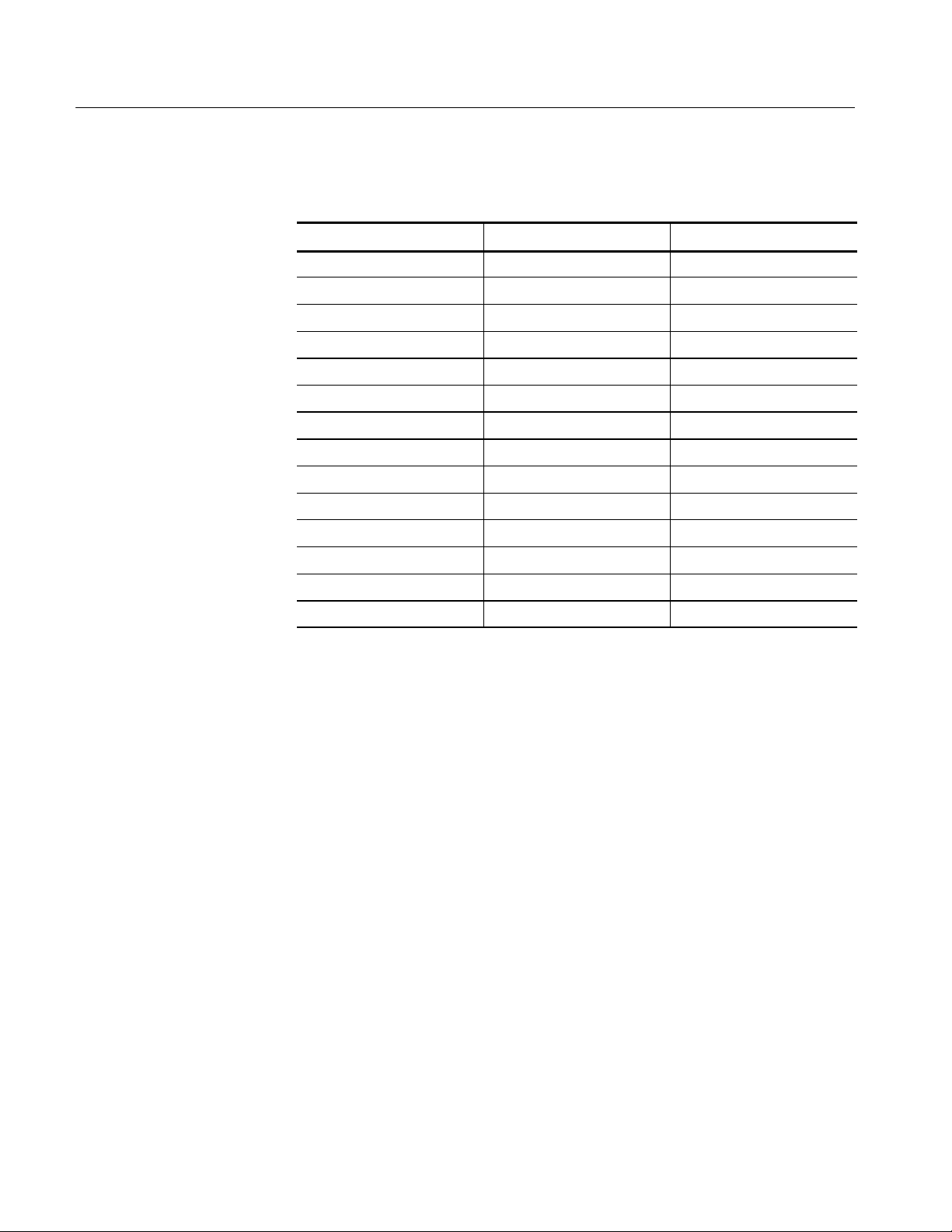

Table 1--1: Module requirements for the TCS101 product

Bus Module requirements Remarks

SPI-3 One module of :

TLA7xx logic analyzer module

at 200 MHz — 68 channel and

above

TLA6xx series logic analyzer

at 200 MHz — 68 channel and

above

TLA7Axx series logic analyzer

at 120 MHz — 68 channel and

above

SPI-4.2 One module of :

TLA7Axx logic analyzer module at 450 MHz — 102 channel

and above

* You cannot use a single 102 or 136 channel module for loading the TX and RX

interfaces together as the SPI3_TX and SPI3_RX support packages assume

independent clocks.

Minimum of one 68-channel

logic analyzer module each for

Transmit and Receive

interfaces

Minimum of one 102 channel

TLA7Axx module

Two 102 channel modules are

required for a Transmit and

Receive pair

*

Probe Requirements

Table 1--2 shows the probe requirements for the TCS101 product.

Table 1--2: Probe requirements for the TCS101 product

Bus

SPI-3 Two P6434 or P6860 probes -

SPI-4.2 Two or three P6880 probes Two P6880 probes are

Requirements and Restrictions

Review the electrical specifications in the Specifications section on page 4--1 in

this manual as they pertain to your target system, as well as the following

descriptions of TCS101 product requirements and restrictions.

Probes for TX or RX

interface

Description

required for data

One optional probe for FIFO

status — either a P6880 probe

for LVDS or LVTTL Status

or a P6860 probe for LVTTL

Status

TCS101 SPI-3 and SPI-4.2 Bus Software Support

1-- 3

Page 20

Getting Started

Hardware Reset

Clock Rate

FIFO Status Decoding

Setup/Hold Time

Requirements

If a hardware reset occurs in your target system during an acquisition, the

application disassembler might acquire an invalid sample.

The TCS101 product can acquire data from the SPI-3 bus operating at 104 MHz.

The TCS101 product can acquire data from the SPI-4.2 bus operating at

1

350 MHz

.

In the SPI4 and SPI4_LVTTL support packages, the FIFO Status decoding is

displayed correctly only under the following conditions.

H Port Address Filter option is set to “No” in the disassembly properties tab

H Show option is set to “All” in the disassembly properties tab

H Filter Idles option is set to “Is False” for the EasyTrigger that was used to

acquire the data

Table 1--3 lists the setup/hold time requirements for the different support

packages. For correct acquisition, the target system must provide a data valid

window meeting these requirements.

Table 1--3: Setup/Hold time requirements for the TCS101 product

Support package

name

SPI3_TX, SPI3_RX TLA6xx/7xx 2.5 ns 0ns

SPI3_TX, SPI3_RX TLA7Axx 750 ps 0ps

SPI4, SPI4_LVTTL TLA7Axx 750 ps 0ps

For SPI-4.2 supports, some of the target systems may require an adjustment in

the Setup/Hold time settings of logic analyzer to match their data valid window.

Nonintrusive Acquisition

The TCS101 product acquires bus cycles nonintrusively from the target system.

That is, the TCS101 product does not intercept, modify, or present signals back

to the target system.

Limitations of the Support

The TCS101 product does not decode the embedded protocols.

Logic analyzer/

module

Setup time Hold time

1-- 4

1

Specification at time of printing. Contact your Tektronix sales representative for

current information on the fastest bus supported.

TCS101 SPI-3 and SPI-4.2 Bus Software Support

Page 21

Getting Started

Connecting the Logic Analyzer to a Target System

You can use the channel probes and clock probes to make the connections

between the logic analyzer and your target system.

To connect the probes to the SPI-3 and SPI-4.2 bus signals described in the

TCS101 product channel assignment to the target system, follow the steps:

1. Power off your target system. It is not necessary to power off the logic

analyzer.

CAUTION. To prevent static damage, handle the target systems, probes, and the

logic analyzer module in a static-free environment. Static discharge can damage

these components.

Always wear a grounding wrist strap, heel strap, or similar device while

handling the target system.

2. Place the target system on a horizontal, static-free surface.

3. Use Tables 3--69 through 3--76 starting on page 3--39 to connect the channel

probes to the SPI-3 and SPI-4.2 signals in the target system.

Labeling P6880 and P6860 Probes

The TCS101 product relies on the channel mapping and labeling scheme for the

P6880 and P6860 Probes. Apply labels, using the instructions described in the

P6810, P6860, and P6880 Logic Analyzer Probes Instruction manual.

TCS101 SPI-3 and SPI-4.2 Bus Software Support

1-- 5

Page 22

Getting Started

1-- 6

TCS101 SPI-3 and SPI-4.2 Bus Software Support

Page 23

Operating Basics

Page 24

Page 25

Setting Up the Support

This section provides information on how to set up the software support and

covers the following topics:

H Installing the support software

H Support package setups

H Clocking options

The information in this section pertains to the specific operations and functions

of the TCS101 product on a Tektronix logic analyzer for which the support can

be used.

Before you acquire and display disassembled data, you need to load the support

package and specify the setups for clocking and triggering as described in the

logic analyzer online help under “Microprocessor support”. The support package

provides default values for each of these setups, but you can change the setups as

needed.

Installing the Support Software

NOTE. Before you install any software, it is recommended you verify that the bus

support software is compatible with the logic analyzer software.

To install the TCS101 product on your Tektronix logic analyzer, follow these

steps:

1. Insert the CD-ROM in the CD drive.

2. Click the Windows Start button, point to Settings, and click Control Panel.

3. In the Control Panel window, double-click Add/Remove Programs.

4. Follow the instructions on the screen for installing the software from the

CD-ROM. A copy of the instruction manual is available on the CD-ROM.

To remove or uninstall software, follow the above instructions and select

Uninstall. You need to close all windows before you uninstall any software.

The TCS101 product installs four different support packages.

TCS101 SPI-3 and SPI-4.2 Bus Software Support

2-- 1

Page 26

Setting Up the Support

Support Package Setups

The TCS101 product installs four acquisition support packages that have their

own setup software and disassemblers. A description of each support package is

listed here.

H SPI3_TX: Use this support package to acquire SPI-3 transmit bus traffic. The

H SPI3_RX: Use this support package to acquire SPI-3 receive bus traffic. The

H SPI4: Use this support package to acquire SPI-4.2 bus traffic. The support

H SPI4_LVTTL: Use this support package to acquire SPI-4.2 bus traffic. The

support package decodes the acquired data and labels the bus cycles in a

packet style display. The package supports 8-bit and 32-bit buses.

support package decodes the acquired data and labels the bus cycles in a

packet style display. The package supports 8-bit and 32-bit buses.

package acquires the FIFO Status bus using LVDS signaling. It can be used

with the transmit or receive interfaces. It decodes the acquired data and

labels the bus cycles in a packet style display.

support package acquires the FIFO Status bus using LVTTL signaling. It can

be used with the transmit or receive interfaces. It decodes the acquired data

and labels the bus cycles in a packet style display.

Clocking Options

SPI3_TX and SPI3_RX

The TCS101 product adds these four selections to the “Load Support Package”

dialog box, under the File pulldown menu.

A special custom clocking program is loaded into the module every time you

load one of the SPI3_TX, SPI3_RX, SPI4, and SPI4_LVTTL support packages

from the TCS101 product. Each support package offers different clocking

options. You may use the default clocking option or choose an alternate by

clicking the “More...” button in the logic analyzer setup window.

The software provides two custom clocking options for the SPI3_TX and

SPI3_RX support packages.

Cycles. The Cycles option provides the following choices:

H “All” is for storing data on every clock cycle (default).

H “Active Only” is for storing data only when the data bus is valid.

2-- 2

TCS101 SPI-3 and SPI-4.2 Bus Software Support

Page 27

Setting Up the Support

Physical Port. The Physical Port option provides the following choices:

H “Single-No InBand Addr” is for a single physical port without TSX or RSX

signals (default).

H “Single With InBand Addr” is for a single physical port with TSX or RSX

signals.

H “Multiple” is for multiple physical port interfaces. This option uses TSX or

RSX and PTPA signals, including byte level and packet level transfer modes.

SPI4 and SPI4_LVTTL

The software provides one custom clocking option for SPI4 and SPI4_LVTTL

support packages:

All Cycles. “All Cycles” is for storing data on every clock cycle.

TCS101 SPI-3 and SPI-4.2 Bus Software Support

2-- 3

Page 28

Setting Up the Support

2-- 4

TCS101 SPI-3 and SPI-4.2 Bus Software Support

Page 29

Acquiring and Viewing Disassembled Data

This section describes how to acquire data and view it disassembled. The

following information covers these topics and tasks:

H Acquiring data

H Changing the way data is displayed

H Labels for bus cycles

H Viewing disassembled data in various display formats

Acquiring Data

The TCS101 product for the SPI-3 and SPI-4.2 bus installs four different

supports: SPI3_TX, SPI3_RX, SPI4, and SPI4_LVTTL.

Once you load the support package, choose a clocking mode, and specify the

trigger, you are ready to acquire and disassemble data.

If you have any problems acquiring data, refer to information on basic operations

in your logic analyzer online help.

Changing How Data is Displayed

Common fields and features allow you to further modify displayed data to fit

your needs. You can make common and optional display selections in the

Disassembly property page.

You can make selections unique to the support package from the TCS101 product

to do the following tasks:

H Change how data is displayed across all display formats

H Change the interpretation of disassembled cycles

TCS101 SPI-3 and SPI-4.2 Bus Software Support

2-- 5

Page 30

Acquiring and Viewing Disassembled Data

Optional Display

Selections

Tables 2--1 through 2--2 show the disassembly display options for the SPI-3 and

SPI-4.2 support packages.

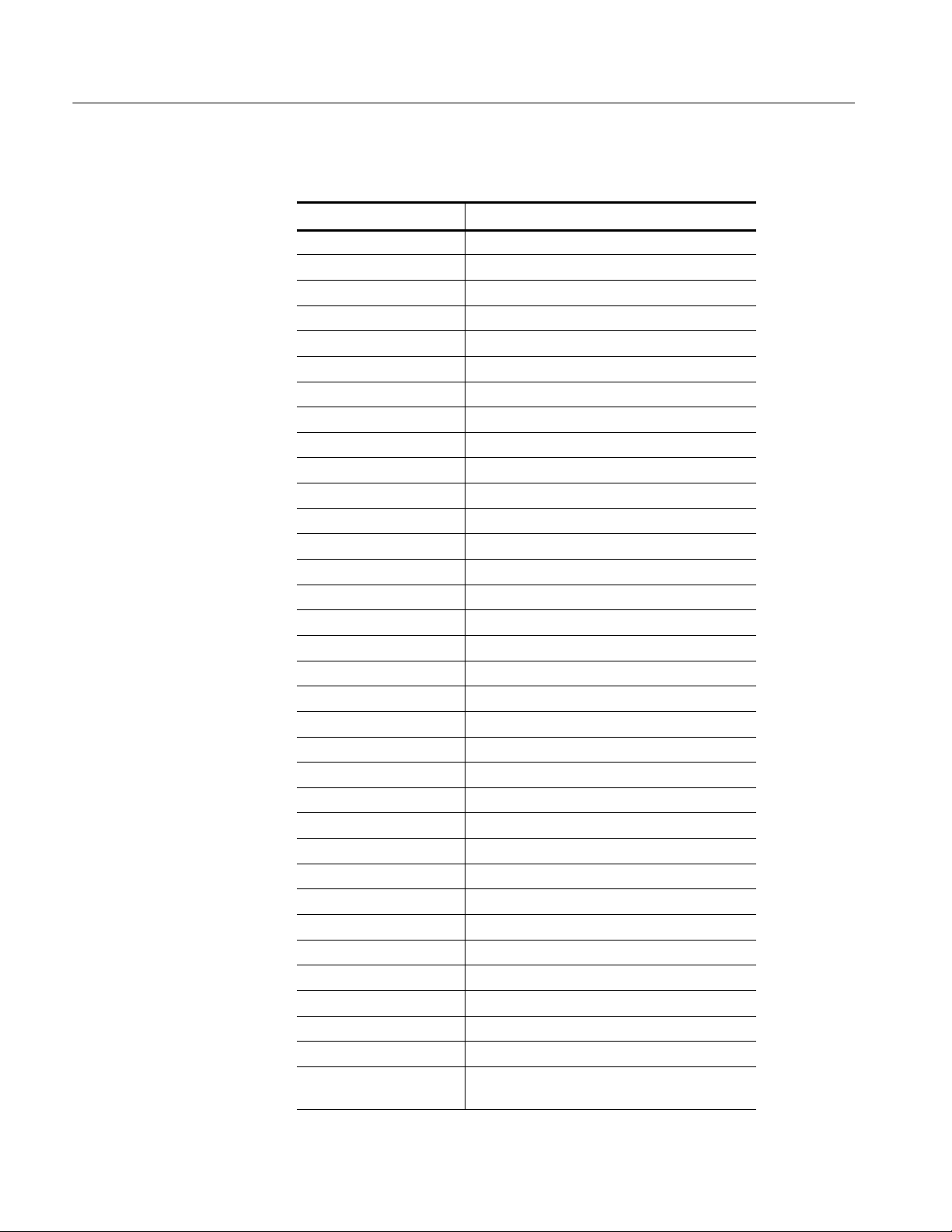

Table 2--1: Logic analyzer disassembly display options for SPI3_TX

and SPI3_RX support packages

Description Option

Show All (default)

Packet

Highlight All (default)

Disassemble Across Gaps Yes

No (default)

Table 2--2: Logic analyzer disassembly display options for SPI4 and

SPI4_LVTTL support packages

Description Option

Show All (default)

Packet & Control

Packet Only

Highlight All (default)

Bus Specific Fields

Disassemble Across Gaps Yes

No (default)

You can make optional selections for disassembled data. In addition to the

common selections (described in the information on basic operations), you can

change the displayed data in the following ways.

Table 2--3 lists the bus specific fields for SPI3_TX and SPI3_RX support

packages.

Table 2--3: Bus specific fields for SPI3_TX and SPI3_RX support

packages

Field Definition

Port Address Filter Choose whether to filter the acquired data sent

to or received from a port

Port Address Enter the port address in hexadecimal

Physical Port Configuration Select the physical port configuration

Cycles Select cycles to decode data

Data Bus Width Select the data bus width in bits

*

2-- 6

TCS101 SPI-3 and SPI-4.2 Bus Software Support

Page 31

Acquiring and Viewing Disassembled Data

Table 2--3: Bus specific fields for SPI3_TX and SPI3_RX support

packages (Cont.)

Field Definition

Decode Payload as ASCII Choose to decode payload information in

ASCII

*

Applicable only for the SPI3_RX support package

Port Address Filter. Select the Port Address Filter as one of the following:

No (default)

Yes

Set this option to Yes if you want to filter the acquired data sent to or received

from a selected physical port.

Port Address. Select the Port Address if you want to filter the acquired data sent

to or received from the port. The default value is 00.

You can enter a maximum value of FF in hexadecimal for the Port Address.

Physical Port Configuration. Select the Physical Port Configuration as one of the

following:

Single - No InBand Addr (default)

Single with InBand Addr

Multiple

For correct disassembly, set the Physical Port Configuration to match with the

custom clocking option selected during acquisition.

Cycles. Select the Cycles as one of the following:

All (default)

Active Only

Set this option to All to decode data on every clock cycle, and Active Only to

decode data only when the data bus is valid.

For correct disassembly, set the Cycles to match with the custom clocking option

selected during acquisition.

NOTE. The bus specific field Cycles is used only in the SPI3_RX support package.

TCS101 SPI-3 and SPI-4.2 Bus Software Support

2-- 7

Page 32

Acquiring and Viewing Disassembled Data

Data Bus Width. Select the Data Bus Width as one of the following:

8 bits (default)

32 bits

Decode Payload as ASCII. Select Decode Payload as ASCII as one of the

following options:

Yes (default)

No

Set this option to Yes if you want to see the payload information in ASCII.

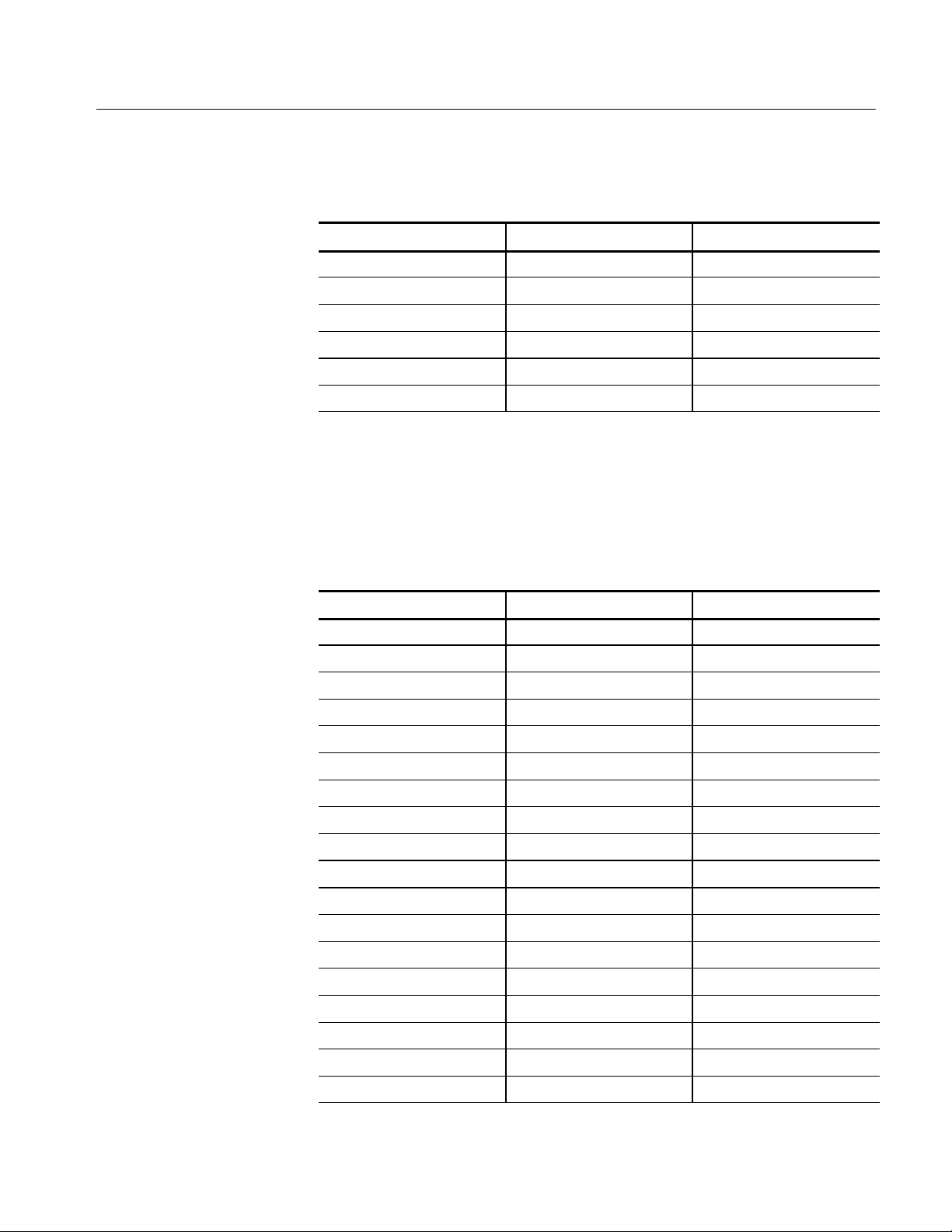

Table 2--4 lists the bus specific fields for SPI4 and SPI4_LVTTL support

packages.

Table 2--4: Bus specific fields for SPI4 and SPI4_LVTTL support

packages

Field Definition

Port Address Filter Choose whether to filter the acquired data sent

to or received from a port

Port Address Enter the port address in hexadecimal

Decode Payload as ASCII Choose to decode payload information in

ASCII

Calendar_LEN Enter the length of the calendar sequence

Calendar_M Enter the number of times a calendar

sequence is repeated between insertions of

framing pattern

Port Address Filter. Select the Port Address Filter as one of the following:

No (default)

Yes

Set this option to Yes if you want to filter the acquired data sent to or received

from a selected physical port.

Port Address. Select the Port Address if you want to filter the acquired data sent

to or received from the port. The default value is 00.

2-- 8

You can enter a maximum value of FF in hexadecimal for the Port Address.

TCS101 SPI-3 and SPI-4.2 Bus Software Support

Page 33

Labels for Bus Cycles

Acquiring and Viewing Disassembled Data

Decode Payload as ASCII. Select Decode Payload as ASCII as one of the

following options:

Yes (default)

No

Set this option to Yes if you want to see the payload information in ASCII.

Calendar_LEN. Enter the Calendar_LEN value. You can enter a maximum value

of 256 in decimal format. The default value is 1.

Calendar_M. Enter the Calendar_M value. You can enter a maximum value of 256

in decimal format. The default value is 1.

The TCS101 product decodes and displays the bus behavior in the Packet/Cell

Details (Mnemonic) column in SPI3_TX, SPI3_RX, SPI4 and SPI4_LVTTL

support packages.

Table 2--5 lists the labels displayed in the P acket/Cell Details column in the

listing window for the SPI3_TX and SPI3_RX support packages.

Table 2--5: Labels in Packet/Cell Details column for SPI3_TX and SPI3_RX support

packages

Label Description

INVALID DATA Invalid data on the SPI-3 data bus

PORT ADDRESS : (Port Address in hex) Physical port address

UNRECOGNIZED DATA Control group value of an acquired sample

does not match the control symbol table

SHORT LENGTH PACKET Packet data at which EOP and SOP signals

asserted at same clock edge

ERRONEOUS PACKET Packet data at which the TERR or RERR

signals are asserted

START OF PACKET Packet start

END OF PACKET Packet end

PAYLOAD : (Index in decimal):(Hex value of

the payload)

Packet data

TCS101 SPI-3 and SPI-4.2 Bus Software Support

2-- 9

Page 34

Acquiring and Viewing Disassembled Data

Table 2--6 lists the labels displayed in the Packet/Cell Details column in the

listing window for the SPI4 and SPI4_LVTTL support packages.

Table 2--6: Labels in Packet/Cell Details column for SPI4 and SPI4_LVTTL support

packages

Label Description

START OF PACKET (ADDR: port address in

hex)

END OF PACKET (ADDR: port address in hex) Packet end

PACKET CONTINUES (ADDR: port address in

hex)

VALID CONTROL WORD Valid control word

IDLE CONTROL WORD Idle control word

TRAINING Training word

Type : (Control word type) Control word “Type”

Port Address : (Port address in hex) Physical port address

DIP-4 : (DIP-Value) Diagonal Interleaved Parity Calculation (4-bit)

PAYLOAD (Index in decimal):(Hex value of

the Payload)

Packet start

Packet continuation

Payload details

Table 2--7 lists the labels displayed in the FIFO Status column in the listing

window for the SPI4 and SPI4_LVTTL support packages.

Table 2--7: Labels in FIFO Status column for SPI4 and SPI4_LVTTL support

packages

2-- 10

Label Description

STARVING Transfer up to Max Burst 1

HUNGRY Transfer up to Max Burst 2

SATISFIED FIFO is almost full

SYNC Calendar follows

DISABLED Disabled

TRAINING --

DISABLED/TRAINING Unidentified FIFO Status

DIP-2 Diagonal Interleaved Parity Calculation (2-bit)

CAL[Calendar_LEN index in decimal]: Calendar length prefixed to STARVING,

HUNGRY or SATISFIED

TCS101 SPI-3 and SPI-4.2 Bus Software Support

Page 35

Viewing Disassembled Data

You can view disassembled data for the SPI3_TX and SPI3_RX support

packages in two display formats:

All

Packet

You can view disassembled data for the SPI4 and SPI4_LVTTL support packages

in three display formats:

All

Packet & Control

Packet Only

Always select the All display format for viewing correctly disassembled FIFO

Status data.

The information on basic operations describes how to select the disassembly

display formats.

Acquiring and Viewing Disassembled Data

All Display Format in

SPI3_TX and SPI3_RX

Packet Display Format in

SPI3_TX and SPI3_RX

NOTE. You must set the selections in the Disassembly property page correctly for

your acquired data to be disassembled correctly. Refer to Changing How Data is

Displayed on page 2--5.

If a channel group is not visible, you must use Add Column or Ctrl+L to make

the group visible.

In this option, all valid and invalid data is acquired at the rising edge of the data

clock and displayed.

In this option, all valid packet data is acquired at the rising edge of the data clock

and displayed.

TCS101 SPI-3 and SPI-4.2 Bus Software Support

2-- 11

Page 36

Acquiring and Viewing Disassembled Data

All Display Format in SPI4

and SPI4_LVTTL

In this option, all the decoded information is displayed. Figure 2--1 shows an

example of the All display format for the SPI4 support package.

Figure 2--1: Example of All display format for the SPI4 support package

Packet & Control Display

Format in SPI4 and

In this option, the information related to packets and control words, are decoded

and displayed. Training related information is not shown.

SPI4_LVTTL

2-- 12

TCS101 SPI-3 and SPI-4.2 Bus Software Support

Page 37

Acquiring and Viewing Disassembled Data

Figure 2--2 shows an example of the Packet & Control display format for the

SPI4 support package.

Figure 2--2: Example of Packet & Control display format for the SPI4 support package

Packet Only Display

Format in SPI4 and

In this option, the information related to only packets are decoded and displayed.

Other information related to control words is not displayed.

SPI4_LVTTL

TCS101 SPI-3 and SPI-4.2 Bus Software Support

2-- 13

Page 38

Acquiring and Viewing Disassembled Data

Figure 2--3 shows an example of the Packets Only display format for the SPI4

support package.

Figure 2--3: Example of Packet Only display format for the SPI4 support package

2-- 14

TCS101 SPI-3 and SPI-4.2 Bus Software Support

Page 39

Trigger Programs

This section describes how to load trigger programs for SPI-3 and SPI-4.2

transmit and receive interfaces. The SPI3_TX, SPI3_RX, SPI4 and SPI4_LVTTL

support packages contain a library of EasyTrigger programs enabling you to

quickly trigger and qualify common aspects of the SPI-3 and SPI-4.2 bus

protocol.

The TCS101 product installs the trigger programs for each support package in

the following paths:

Loading Trigger Programs

To load a trigger program from any of the support packages, follow these steps:

1. Load the support package.

C:\ProgramFiles\TLA700\Supports\SPI3_TX\EasyTriggers

C:\ProgramFiles\TLA700\Supports\SPI3_RX\EasyTriggers

C:\ProgramFiles\TLA700\Supports\SPI4\EasyTriggers

C:\ProgramFiles\TLA700\Supports\SPI4_LVTTL\EasyTriggers

SPI-3 Trigger Programs

2. From the system window, click the

3. Click on the “EasyTrigger” tab. Scroll through the EasyTrigger window to

find the trigger programs that you need.

4. Select an EasyTrigger program from the list and fill in the fields.

You are now ready to trigger on the acquired data. For more information, refer to

the logic analyzer online help and the logic analyzer user manual.

The following list of EasyTrigger programs is common for the SPI3_TX and

SPI3_RX support packages and can be used independently. The trigger programs

are:

Trigger on control condition

Trigger on packet

Trigger on packet from a specific port

Trigger button.

TCS101 SPI-3 and SPI-4.2 Bus Software Support

2-- 15

Page 40

Trigger Programs

SPI-4.2 Trigger Programs

The following list of EasyTrigger programs is common for the SPI4 and

SPI4_LVTTL support packages and can be used independently. The trigger

programs are:

Trigger on control word

Trigger on a generic packet

2-- 16

TCS101 SPI-3 and SPI-4.2 Bus Software Support

Page 41

SPI-4.2 Setup/Hold Time Adjustments

Some devices will require an adjustment of the Setup/Hold values in the TLA700

Application to get valid test results. The logic analyzer application provides

AutoDeskew to automatically deskew and verify the logic analyzer Setup/Hold

window. AutoDeskew can also be used to test Setup/Hold violations of the

current setting. For more information on AutoDeskew, refer to the logic analyzer

online help.

The Setup/Hold adjustments can be made for each channel. You can use custom

clock setups and different Setup/Hold settings for each type of clocking. The

AutoDeskew capability to analyze the Setup/Hold violations allows you to test

for violations that occur with current Setup/Hold settings. You can automatically

convert a test setup to a trigger setup for use with the logic analyzer trigger

system. This allows you to determine exactly which channels may be failing the

Setup/Hold requirements.

AutoDeskew is preconfigured for the support packages SPI4 and SPI4_LVTTL.

Follow these steps to use AutoDeskew:

1. Load the support package and click the AutoDeskew button on the tool bar to

open the AutoDeskew window.

2. Click the Define Setup button to display the AutoDeskew Setup dialog.

3. Select Custom under AutoDeskew mode. Based on the loaded support

package, the AutoDeskew configurations and settings show different options.

4. Choose the appropriate options for the AutoDeskew configuration and

settings.

5. Click the Analyze button to start analysis.

6. After the analysis is complete, the results are displayed.

7. Click the Apply button to apply the analyzed results. You can manually

examine the window choices and move the sample point if needed before

clicking the Apply button.

Each support has several AutoDeskew configurations based on the clock signal

that is used as a source clock for acquisition. Each configuration has several

settings corresponding to the channels to be analyzed.

TCS101 SPI-3 and SPI-4.2 Bus Software Support

2-- 17

Page 42

SPI-4.2 Setup/Hold Time Adjustments

SPI4 Configurations and Settings

You can select the following configurations and settings for the SPI4 support

package.

SPI4 AutoDeskew Setup

The following setting is available for SPI4 AutoDeskew:

H Analyze SPI4 Signals

SPI4_LVTTL Configurations and Settings

You can select the following configurations and settings for the SPI4 support

package.

SPI4_LVTTL AutoDeskew

Setup

The following settings are available for SPI4_LVTTL AutoDeskew:

H Analyze SPI4_LVTTL Status Signals

H Analyze SPI4_LVTTL Data & Control Signals

2-- 18

TCS101 SPI-3 and SPI-4.2 Bus Software Support

Page 43

Reference

Page 44

Page 45

Channel Group Definitions

This section lists the channel group definitions for the TCS101 product required

for disassembly.

Channel Groups

The software automatically defines channel groups for the support package.

Tables 3--1 through 3--3 show the channel groups for the TCS101 product for the

SPI3_TX, SPI3_RX, SPI4, and SPI4_LVTTL support packages.

Table 3--1: SPI3_TX channel group names

Group name Display radix

Address Hexadecimal

DAT Hexadecimal

Packet/Cell details None (disassembly generated text)

Control Symbol

DTPA Off

Parity Symbol (disassembly generated text)

Misc Hexadecimal

Trig_Control Off (Trigger Group)

Trig_DAT[7:0] Off (Trigger Group)

Trig_DAT[31:0] Off (Trigger Group)

Timestamp

Table 3--2: SPI3_RX channel group names

Group name Display radix

DAT Hexadecimal

Packet/Cell details None (disassembly generated text)

Control Symbol

Parity Symbol (disassembly generated text)

Trig_Control Off (Trigger Group)

Trig_DAT[7:0] Off (Trigger Group)

Trig_DAT[31:0] Off (Trigger Group)

Timestamp

TCS101 SPI-3 and SPI-4.2 Bus Software Support

3-- 1

Page 46

Channel Group Definitions

Table 3--3: SPI4 and SPI4_LVTTL channel group names

Group name Display radix

$CTL Off (Calibration Group)

$DAT0 Off (Calibration Group)

$DAT1 Off (Calibration Group)

$DAT2 Off (Calibration Group)

$DAT3 Off (Calibration Group)

$DAT4 Off (Calibration Group)

$DAT5 Off (Calibration Group)

$DAT6 Off (Calibration Group)

$DAT7 Off (Calibration Group)

$DAT8 Off (Calibration Group)

$DAT9 Off (Calibration Group)

$DAT10 Off (Calibration Group)

$DAT11 Off (Calibration Group)

$DAT12 Off (Calibration Group)

$DAT13 Off (Calibration Group)

$DAT14 Off (Calibration Group)

$DAT15 Off (Calibration Group)

$STAT0 Off (Calibration Group)

$STAT1 Off (Calibration Group)

CTL_TYPE_A Off (EasyTrigger Group)

CTL_TYPE_B Off (EasyTrigger Group)

CTL_TYPE_AB Off (EasyTrigger Group)

DAT_PORT_A Off (EasyTrigger Group)

DAT_PORT_B Off (EasyTrigger Group)

DAT_AB Off (EasyTrigger Group)

DAT_BA Off (EasyTrigger Group)

DAT_A Off (EasyTrigger Group)

DAT_B Off (EasyTrigger Group)

CTL[1:0] Off

DATA Off

STAT Off

STAT_A Off

STAT_B Off

CTL Binary (Numeric group generated by disassem-

bly)

3-- 2

TCS101 SPI-3 and SPI-4.2 Bus Software Support

Page 47

Channel Group Definitions

Table 3--3: SPI4 and SPI4_LVTTL channel group names (Cont.)

Group name Display radix

DAT Hexadecimal (Numeric group generated by

disassembly)

Packet/Cell Details None (disassembly generated text)

STAT[1:0] Binary (disassembly generated text)

FIFO Status None (disassembly generated text)

Timestamp

NOTE. The groups $STAT0 and $STAT1 are used only in the SPI4 support

package.

TCS101 SPI-3 and SPI-4.2 Bus Software Support

3-- 3

Page 48

Channel Group Definitions

3-- 4

TCS101 SPI-3 and SPI-4.2 Bus Software Support

Page 49

Symbol and Channel Assignment Tables

This section lists the symbol tables, channel assignment tables for disassembly

and timing, and signal acquisition for each of the support packages.

Symbol Tables

The TCS101 product supplies three symbol table files for the SPI3_TX and

SPI3_RX supports and one each for SPI4 and SPI4_LVTTL support packages.

Tables 3--4 through 3--10 show the definitions for the symbol, bit pattern, and

meaning of the group symbols in the control symbol tables. The symbol table

file for SPI3_TX support package is SP I3_TX_Ctrl.

Table 3- 4: SPI3_TX_Ctrl group symbol table definitions

Ctrl group value

TSX TERR

TENB TPRTY

Symbol

DATA 0000 XXXX Valid data on TDAT bus

EOP 0001 0XXX Sample at which TEOP is

SOP 0010 XXXX Sample at which TSOP is

ERROR 00X1 1XXX Erroneous packet

PORT_ADDRESS 1100 XXXX Physical port address

SOP&EOP X0 1 1 XXXX Sample at which TSOP

TSOP TMOD1

TEOP TMOD0

Description

asserted

asserted

transmitted over TDAT bus

and TEOP are asserted

NOTE. Binary values are displayed for those control group words that do not

have any symbols assigned to them.

TCS101 SPI-3 and SPI-4.2 Bus Software Support

3- 5

Page 50

Symbol and Channel Assignment Tables

Table 3--5 shows the definitions for the symbol, bit pattern, and meaning of the

group symbols in the EasyTrigger symbol table for the SPI3_TX support

package. The EasyTrigger symbol table file name SPI3_TX_Trig_Ctrl.

Table 3- 5: SPI3_TX_Trig_Ctrl group symbol table definitions

Symbol

Any control XXX -

SOP 1XX Start of packet

EOP X1 X End of packet

ERROR X1 1 Erroneous packet

Table 3--6 shows the definitions for the symbol, bit pattern, and meaning of the

group symbols in the Parity symbol table for the SP I3_TX support package. The

Parity symbol table file name S PI3_TX_Parity.

Trig_Control group

value

TSOP

TEOP

TERR

Description

Table 3- 6: SPI3_TX Parity group symbol table definitions

Parity group value

Symbol

TPRTY

Description

Parity_0 0 Parity signal is low

Parity_1 1 Parity signal is high

The symbol table file for SPI3_RX support package is SPI3_RX_Ctrl.

Table 3- 7: SPI3_RX_Ctrl group symbol table definitions

Ctrl group value

RSX REOP RMOD0

RVAL RERR

Symbol

DATA 01X0 0XXX X Valid data on

SOP 01X1 0XXX X Sample at which

PORT_ADDRESS 10X0 0XXX X Physical port

RENB RPRTY

RSOP RMOD1

Description

RDAT bus

RSOP is

asserted

address

TCS101 SPI-3 and SPI-4.2 Bus Software Support3- 6

Page 51

Symbol and Channel Assignment Tables

Table 3- 7: SPI3_RX_Ctrl group symbol table definitions ( Cont.)

Ctrl group value

RSX REOP RMOD0

RVAL RERR

Symbol Description

RENB RPRTY

RSOP RMOD1

EOP 01X0 10XX X Sample at which

REOP is

asserted

ERROR 01XX 11XX X Erroneous packet

received over

RDAT bus

SOP&EOP X1 X1 1 XXX X Sample at which

RSOP and

REOP are

asserted

NOTE. Binary values are displayed for those control group words that do not

have any symbols assigned to them.

Table 3--8 shows the definitions for the symbol, bit pattern, and meaning of the

group symbols in the EasyTrigger symbol table for the SPI3_RX support

package. The EasyTrigger symbol table file name SPI3_RX_Trig_Ctrl.

Table 3- 8: SPI3_RX_Trig_Ctrl group symbol table definitions

Trig_Control group

value

RSOP

Symbol

Any control XXX

SOP 1XX Start of packet

EOP X1 X End of packet

ERROR X1 1 Erroneous packet

REOP

RERR

Description

TCS101 SPI-3 and SPI-4.2 Bus Software Support

3- 7

Page 52

Symbol and Channel Assignment Tables

Table 3--9 shows the definitions for the symbol, bit pattern, and meaning of the

group symbols in the Parity symbol table for the SP I3_RX support package. The

Parity symbol table file name SPI3_RX_Parity.

Table 3- 9: SPI3_RX Parity group symbol table definitions

Parity group value

Symbol

RPRTY

Description

Parity_0 0 Parity signal is low

Parity_1 1 Parity signal is high

Table 3--10 shows the definitions for the symbol, bit pattern, and meaning of the

group symbols in the control symbol table for the SPI4 and SPI4_LVTTL

support packages. The symbol table file for SPI4 and SPI4_LVTTL support

packages is SPI4_Ctrl and SPI4_LVTTL_Ctrl. Use these symbols for triggering

packet and control word information. By default, the group is off.

Table 3- 10: SPI4_Ctrl/SPI4_LVTTL_Ctrl group symbol table definitions

Ctrl group value

CTL_DM/CTL DAT12/DAT28

DAT15/DAT31

Symbol

(Any_Word) 1XXX X --

(Generic_SOP) 110X 1 Packet start

(Generic_EOP) 1X1X X Packet end

(Generic_Abort) 1X01 X Packet end abort

0: Idle, not_EOP, training_control

1: Reserved 1000 1 Reserved

2: Idle, Abort_last_packet 1001 0 Idle control word, abort

3: Reserved 1001 1 Reserved

4: Idle, EOP_with_2_bytes_valid

5: Reserved 1010 1 Reserved

6: Idle, EOP_with_1_byte_val-id1011 0 Idle control word, EOP,

7: Reserved 1011 1 Reserved

8: Valid, no_SOP, no_EOP 1100 0 Valid packet, not SOP and

DAT14/DAT30

DAT13/DAT29

Description

1000 0 Training control word

1010 0 Idle control word, EOP,

both the bytes valid

one byte valid

EOP

TCS101 SPI-3 and SPI-4.2 Bus Software Support3- 8

Page 53

Symbol and Channel Assignment Tables

Table 3- 10: SPI4_Ctrl/SPI4_LVTTL_Ctrl group symbol table definitions (Cont.)

Ctrl group value

CTL_DM/CTL DAT12/DAT28

DAT15/DAT31

Symbol Description

9: Valid, SOP, no_EOP 1100 1 Valid packet, SOP and not

A: Valid, no_SOP, abort 1101 0 Valid packet, not SOP and

B: Valid, SOP, abort 1101 1 Valid packet, SOP and

C: Valid, no_SOP,

EOP_w/2_bytes_valid

D: Valid, SOP, EOP_w/2_bytes_valid

E: Valid, no_SOP,

EOP_w/1_byte_valid

F: Valid, SOP,

EOP_w/1_byte_valid

DAT14/DAT30

DAT13/DAT29

EOP

abort

abort

1110 0 Valid packet, not SOP and

EOP with both the bytes

valid

1110 1 Valid packet, SOP and

EOP with both the bytes

valid

1111 0 Valid packet, not SOP and

EOP with one byte valid

1111 1 Valid packet, SOP and

EOP with one byte valid

Information on basic operations describes how to use symbolic values for

triggering and for displaying other channel groups symbolically.

Channel Assignment Tables

Channel assignments shown in Table 3--11 through Table 3--68 use the following

conventions:

H All signals are required by the support package, unless indicated otherwise.

H Channels are shown starting with the most significant bit (MSB), descending

to the least significant bit (LSB).

H Channel group assignments are for all modules, unless otherwise noted.

H Any SPI-3 signal ending with the letter “B” indicates that the signal is

asserted low.

SPI3_TX Channel Group

Assignments

Tables 3--11 through 3--18 show the channel assignments for the logic analyzer

groups for the SPI3_TX support package and the bus signal to which each

channel connects.

TCS101 SPI-3 and SPI-4.2 Bus Software Support

3- 9

Page 54

Symbol and Channel Assignment Tables

Table 3--11 shows the probe section and channel assignments for the Address

group and the bus signal to which each channel connects. By default, this

channel group is displayed in hexadecimal.

Table 3- 11: Address group assignments for SPI3_TX support package

Bit order Logic analyzer channel SPI-3 transmit signal name

1 (MSB) C3:7 TADR1

0 C3:6 TADR0

Table 3--12 shows the probe section and channel assignments for the DAT group

and the bus signal to which each channel connects. By default, this channel

group is displayed in hexadecimal.

Table 3- 12: DAT group assignments for SPI3_TX support package

Bit order Logic analyzer channel SPI-3 transmit signal name

31 (MSB) D1:7 TDAT31

30 D1:6 TDAT30

29 D1:5 TDAT29

28 D1:4 TDAT28

27 D1:3 TDAT27

26 D1:2 TDAT26

25 D1:1 TDAT25

24 D1:0 TDAT24

23 D0:7 TDAT23

22 D0:6 TDAT22

21 D0:5 TDAT21

20 D0:4 TDAT20

19 D0:3 TDAT19

18 D0:2 TDAT18

17 D0:1 TDAT17

16 D0:0 TDAT16

15 A1:7 TDAT15

14 A1:6 TDAT14

13 A1:5 TDAT13

12 A1:4 TDAT12

TCS101 SPI-3 and SPI-4.2 Bus Software Support3- 10

Page 55

Symbol and Channel Assignment Tables

Table 3- 12: DAT group assignments for SPI3_TX support package (Cont.)

Bit order SPI-3 transmit signal nameLogic analyzer channel

11 A1:3 TDAT11

10 A1:2 TDAT10

9 A1:1 TDAT9

8 A1:0 TDAT8

7 A0:7 TDAT7

6 A0:6 TDAT6

5 A0:5 TDAT5

4 A0:4 TDAT4

3 A0:3 TDAT3

2 A0:2 TDAT2

1 A0:1 TDAT1

0 (LSB) A0:0 TDAT0

Table 3--13 shows the probe section and channel assignments for the Control

group and the bus signal to which each channel connects. By default, this

channel group is displayed in symbols. The symbol table file name is

SPI3_TX_Ctrl.

Table 3- 13: Control group assignments for SPI3_TX support package

Bit order Logic analyzer channel SPI-3 transmit signal name

7 (MSB) C2:3 TSX

6 C2:2 TENB

5 C2:0 TSOP

4 C2:1 TEOP

3 C3:1 TERR

2 C3:3 TPRTY

1 C3:5 TMOD1

0 (LSB) C3:4 TMOD0

TCS101 SPI-3 and SPI-4.2 Bus Software Support

3- 11

Page 56

Symbol and Channel Assignment Tables

Table 3--14 shows the probe section and channel assignments for the DTPA

group and the bus signal to which each channel connects. By default, this

channel group is displayed in hexadecimal.

Table 3- 14: DTPA group assignments for SPI3_TX support package

Bit order Logic analyzer channel SPI-3 transmit signal name

3 (MSB) C2:7 DTPA3

2 C2:6 DTPA2

1 C2:5 DTPA1

0 (LSB) C2:4 DTPA0

Table 3--15 shows the probe section and channel assignments for the Misc group

and the bus signal to which each channel connects. By default, this channel

group is displayed in hexadecimal.

Table 3- 15: Misc group assignments for SPI3_TX support package

Bit order Logic analyzer channel SPI-3 transmit signal name

1 (MSB) C3:2 PTPA

0 C3:0 STPA

Table 3--16 shows the probe section and channel assignments for the Trig_Control group and the bus signal to which each channel connects. By default, this

channel group is off.

Table 3- 16: Trig_Control group assignments for SPI3_TX support package

Bit order Logic analyzer channel SPI-3 transmit signal name

2 (MSB) C2:0 TSOP

1 C2:1 TEOP

0 (LSB) C3:1 TERR

TCS101 SPI-3 and SPI-4.2 Bus Software Support3- 12

Page 57

Symbol and Channel Assignment Tables

Table 3--17 shows the probe section and channel assignments for the

Trig_DAT[7:0] group and the bus signal to which each channel connects. By

default, this channel group is off.

Table 3- 17: Trig_DAT[7:0] group assignments for SPI3_TX support package

Bit order Logic analyzer channel SPI-3 transmit signal name

7 (MSB) A0:7 TDAT7

6 A0:6 TDAT6

5 A0:5 TDAT5

4 A0:4 TDAT4

3 A0:3 TDAT3

2 A0:2 TDAT2

1 A0:1 TDAT1

0 (LSB) A0:0 TDAT0

Table 3--18 shows the probe section and channel assignments for the

Trig_DAT[31:0] group and the bus signal to which each channel connects. By

default, this channel group is displayed in hexadecimal.

Table 3- 18: Trig_DAT[31:0] group assignments for SPI3_TX support

package

Bit order Logic analyzer channel SPI-3 transmit signal name

31 (MSB) D1:7 TDAT31

30 D1:6 TDAT30

29 D1:5 TDAT29

28 D1:4 TDAT28

27 D1:3 TDAT27

26 D1:2 TDAT26

25 D1:1 TDAT25

24 D1:0 TDAT24

23 D0:7 TDAT23

22 D0:6 TDAT22

21 D0:5 TDAT21

20 D0:4 TDAT20

19 D0:3 TDAT19

18 D0:2 TDAT18

TCS101 SPI-3 and SPI-4.2 Bus Software Support

3- 13

Page 58

Symbol and Channel Assignment Tables

Table 3- 18: Trig_DAT[31:0] group assignments for SPI3_TX support

package (Cont.)

Bit order SPI-3 transmit signal nameLogic analyzer channel

17 D0:1 TDAT17

16 D0:0 TDAT16

15 A1:7 TDAT15

14 A1:6 TDAT14

13 A1:5 TDAT13

12 A1:4 TDAT12

11 A1:3 TDAT11

10 A1:2 TDAT10

9 A1:1 TDAT9

8 A1:0 TDAT8

7 A0:7 TDAT7

SPI3_RX Channel Group

Assignments

6 A0:6 TDAT6

5 A0:5 TDAT5

4 A0:4 TDAT4

3 A0:3 TDAT3

2 A0:2 TDAT2

1 A0:1 TDAT1

0 (LSB) A0:0 TDAT0

Tables 3--19 through 3--23 show the channel assignments for the logic analyzer

groups for the SPI3_RX support package and the bus signal to which each

channel connects.

Table 3--19 shows the probe section and channel assignments for the DAT group

and the bus signal to which each channel connects. By default, this channel

group is displayed in hexadecimal.

Table 3- 19: DAT group assignments for SPI3_RX support package

Bit order Logic analyzer channel SPI-3 receive signal name

31 (MSB) D1:7 RDAT31

30 D1:6 RDAT30

29 D1:5 RDAT29

28 D1:4 RDAT28

TCS101 SPI-3 and SPI-4.2 Bus Software Support3- 14

Page 59

Symbol and Channel Assignment Tables

Table 3- 19: DAT group assignments for SPI3_RX support package (Cont.)

Bit order SPI-3 receive signal nameLogic analyzer channel

27 D1:3 RDAT27

26 D1:2 RDAT26

25 D1:1 RDAT25

24 D1:0 RDAT24

23 D0:7 RDAT23

22 D0:6 RDAT22

21 D0:5 RDAT21

20 D0:4 RDAT20

19 D0:3 RDAT19

18 D0:2 RDAT18

17 D0:1 RDAT17

16 D0:0 RDAT16

15 A1:7 RDAT15

14 A1:6 RDAT14

13 A1:5 RDAT13

12 A1:4 RDAT12

11 A1:3 RDAT11

10 A1:2 RDAT10

9 A1:1 RDAT9

8 A1:0 RDAT8

7 A0:7 RDAT7

6 A0:6 RDAT6

5 A0:5 RDAT5

4 A0:4 RDAT4

3 A0:3 RDAT3

2 A0:2 RDAT2

1 A0:1 RDAT1

0 (LSB) A0:0 RDAT0

TCS101 SPI-3 and SPI-4.2 Bus Software Support

3- 15

Page 60

Symbol and Channel Assignment Tables

Table 3--20 shows the probe section and channel assignments for the Control

group and the bus signal to which each channel connects. By default, this

channel group is displayed in symbols. The symbol table file name is

SPI3_RX_Ctrl.

Table 3- 20: Control group assignments for SPI3_RX support package

Bit order Logic analyzer channel SPI-3 receive signal name

8 C2:3 RSX

7 Clock:1 RVAL

6 C2:2 RENB

5 C2:0 RSOP

4 C2:1 REOP

3 C3:1 RERR

2 C3:3 RPRTY

1 C3:5 RMOD1

0 (LSB) C3:4 RMOD0

Table 3--21 shows the probe section and channel assignments for the Trig_Control group and the bus signal to which each channel connects. By default, this

channel group is off.

Table 3- 21: Trig_Control group assignments for SPI3_RX support package

Bit order Logic analyzer channel SPI-3 transmit signal name

2 (MSB) C2:0 RSOP

1 C2:1 REOP

0 (LSB) C3:1 RERR

Table 3--22 shows the probe section and channel assignments for the

Trig_DAT[7:0] group and the bus signal to which each channel connects. By

default, this channel group is off.

Table 3- 22: Trig_DAT[7:0] group assignments for SPI3_RX support

package

Bit order Logic analyzer channel SPI-3 transmit signal name

7 (MSB) A0:7 RDAT7

6 A0:6 RDAT6

TCS101 SPI-3 and SPI-4.2 Bus Software Support3- 16

Page 61

Symbol and Channel Assignment Tables

Table 3- 22: Trig_DAT[7:0] group assignments for SPI3_RX support

package (Cont.)

Bit order SPI-3 transmit signal nameLogic analyzer channel

5 A0:5 RDAT5

4 A0:4 RDAT4

3 A0:3 RDAT3

2 A0:2 RDAT2

1 A0:1 RDAT1

0 (LSB) A0:0 RDAT0

Table 3--23 shows the probe section and channel assignments for the

Trig_DAT[31:0] group and the bus signal to which each channel connects. By

default, this channel group is displayed in hexadecimal.

Table 3- 23: Trig_DAT[31:0] group assignments for SPI3_RX support

package

Bit order Logic analyzer channel SPI-3 transmit signal name

31 (MSB) D1:7 RDAT31

30 D1:6 RDAT30

29 D1:5 RDAT29

28 D1:4 RDAT28

27 D1:3 RDAT27

26 D1:2 RDAT26

25 D1:1 RDAT25

24 D1:0 RDAT24

23 D0:7 RDAT23

22 D0:6 RDAT22

21 D0:5 RDAT21

20 D0:4 RDAT20

19 D0:3 RDAT19

18 D0:2 RDAT18

17 D0:1 RDAT17

16 D0:0 RDAT16

15 A1:7 RDAT15

14 A1:6 RDAT14

TCS101 SPI-3 and SPI-4.2 Bus Software Support

3- 17

Page 62

Symbol and Channel Assignment Tables

Table 3- 23: Trig_DAT[31:0] group assignments for SPI3_RX support

package (Cont.)

Bit order SPI-3 transmit signal nameLogic analyzer channel

13 A1:5 RDAT13

12 A1:4 RDAT12

11 A1:3 RDAT11

10 A1:2 RDAT10

9 A1:1 RDAT9

8 A1:0 RDAT8

7 A0:7 RDAT7

6 A0:6 RDAT6

5 A0:5 RDAT5

4 A0:4 RDAT4

3 A0:3 RDAT3

SPI4 and SPI4_LVTTL

Channel Group

Assignments

2 A0:2 RDAT2

1 A0:1 RDAT1

0 (LSB) A0:0 RDAT0

The SPI-4.2 supports are common to both the SPI-4.2 Transmit and Receive

buses. Therefore:

H TDAT and RDAT are referred to as DAT

H TCTL and RCTL are referred to as CTL

H TSCLK and RSCLK are referred to as SCLK

H TDCLK and RDCLK are referred to as DCLK

TCS101 SPI-3 and SPI-4.2 Bus Software Support3- 18

Page 63

Symbol and Channel Assignment Tables

When you use the SPI4 and SPI4_LVTTL supports, do not connect the following

logic analyzer channels to any signals because they are demuxed.

Qual:0

D3:7-0

D1:7-0

C1:7

C1:6

Tables 3--24 through 3--49 show the channel assignments for the groups of the

SPI4 and SPI4_LVTTL support packages and the bus signal to which each

channel connects.

Table 3--24 shows the probe section and channel assignments for the $CTL

group and the bus signal to which each channel connects. By default, this

channel group is off.

Table 3- 24: $CTL group assignments for SPI4 and SPI4_LVTTL support

packages

SPI4/SPI4_LVTTL support

Bit order Logic analyzer channel

1 (MSB) Clock:1 CTL

0 Qual:0 CTL_DM

package signal name

Table 3--25 shows the probe section and channel assignments for the $DAT0

group and the bus signal to which each channel connects. By default, this

channel group is off.

Table 3- 25: $DAT0 group assignments for SPI4 and SPI4_LVTTL support

packages

SPI4/SPI4_LVTTL support

Bit order Logic analyzer channel

1 (MSB) A3:0 DAT0

0 D3:0 DAT16

package signal name

TCS101 SPI-3 and SPI-4.2 Bus Software Support

3- 19

Page 64

Symbol and Channel Assignment Tables

Table 3--26 shows the probe section and channel assignments for the $DAT1

group and the bus signal to which each channel connects. By default, this

channel group is off.

Table 3- 26: $DAT1 group assignments for SPI4 and SPI4_LVTTL support

packages

Bit order Logic analyzer channel

1 (MSB) A3:1 DAT1

0 D3:1 DAT17

Table 3--27 shows the probe section and channel assignments for the $DAT2

group and the bus signal to which each channel connects. By default, this

channel group is off.

Table 3- 27: $DAT2 group assignments for SPI4 and SPI4_LVTTL support

packages

SPI4/SPI4_LVTTL support

package signal name

SPI4/SPI4_LVTTL support

Bit order Logic analyzer channel

1 (MSB) A3:2 DAT2

0 D3:2 DAT18

package signal name

Table 3--28 shows the probe section and channel assignments for the $DAT3

group and the bus signal to which each channel connects. By default, this

channel group is off.

Table 3- 28: $DAT3 group assignments for SPI4 and SPI4_LVTTL support

packages

SPI4/SPI4_LVTTL support

Bit order Logic analyzer channel

1 (MSB) A3:3 DAT3

0 D3:3 DAT19

package signal name

TCS101 SPI-3 and SPI-4.2 Bus Software Support3- 20

Page 65

Symbol and Channel Assignment Tables

Table 3--29 shows the probe section and channel assignments for the $DAT4

group and the bus signal to which each channel connects. By default, this

channel group is off.

Table 3- 29: $DAT4 group assignments for SPI4 and SPI4_LVTTL support

packages

SPI4/SPI4_LVTTL support

Bit order Logic analyzer channel

1 (MSB) A3:4 DAT4

0 D3:4 DAT20

package signal name

Table 3--30 shows the probe section and channel assignments for the $DAT5

group and the bus signal to which each channel connects. By default, this