Sun SME1701PGA-500 (UltraSPARC IIe 500MHz) UltraSPARC IIe Processor User's Manual (Version 1.1)

UltraSPARC®IIe Processor

l

User’s Manual

Supplement to the UltraSPARC IIi User’s Manua

Version 1.1 (Internal)

February 2003

Sun Proprietary/Confidential: Need-To-Know

Copyright © 2003 Sun Microsystems, Inc., 4150 Network Circle, Santa Clara, California 95054, U.S.A.

All rights reserved.

Sun, Sun Microsystems, the Sun logo, Netra, Ultra, Sun Blade, Netra, VIS and Sun Enterprise are

trademarks or registered trademarks of Sun Microsystems, Inc. in the U.S. and other countries.

All SPARC trademarks are used under license and are trademarks or registered trademarks of SPARC

International, Inc. in the U.S. and other countries. Products bearing SPARC trademarks are based upon

architecture developed by Sun Microsystems, Inc.

DOCUMENTATION IS PROVIDED "AS IS" AND ALL EXPRESS OR IMPLIED CONDITIONS,

REPRESENTATIONS AND WARRANTIES, INCLUDING ANY IMPLIED WARRANTY OF

MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT, ARE

DISCLAIMED, EXCEPT TO THE EXTENT THAT SUCH DISCLAIMERS ARE HELD TO BE

LEGALLY INVALID.

Table of Contents

Table of Contents i

List of Figures iii

List of Tables v

Preface vii

1. UltraSPARC IIe Processor Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 UltraSPARC IIe Processor Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

1.2 Processor Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

1.3 System Perspective . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

1.4 Software Perspective . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

2. Clocks, System Timer, GPO, and Resets. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.1 Clocks. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.2 Clock Frequency Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

2.3 System Interrupt Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.4 General Purpose Outputs (GPO) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

2.5 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3. Level 2 Cache Subsystem . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.1 Level 2 Cache Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.2 Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

3.3 Cache Operating Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.4 Memory Requests . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

3.5 Level 2 Cache Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

3.6 Level 2 Cache Control Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

3.7 Level 2 Cache Flush Procedure - Programming Guide . . . . . . . . . . . . . . . . . . . . . . . . 31

3.8 Level 2 Cache Initialization - Programming Guide . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

3.9 Level 2 Cache Control and Status Registers (CSRs) . . . . . . . . . . . . . . . . . . . . . . . . . . 32

4. Memory Address Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

4.1 Memory Interface Unit (MIU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Sun Proprietary/Confidential: Internal Use Only

Table of Contents − i

4.2 SDRAM Memory Control Unit (MCU). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

4.3 Memory Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

5. Memory Control Unit (MCU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

5.1 SDRAMs and DIMMs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

5.2 SDRAM Command Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

5.3 DIMM Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

5.4 Control and Status Registers (CSRs) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

5.5 Physical Address Mapping of DIMMs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

6. PCI Bus Subsystem . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

6.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

6.2 PCI Bus Subsystem Functional Units . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

6.3 PIO Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

6.4 DMA Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

6.5 PCI Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

6.6 PCI Bus Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

6.7 PCI Bus Protocol Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

6.8 PCI Bus Arbitration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

6.9 PCI Bus Error Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

6.10 Processor Boot ROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

6.11 Endian Support. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

7. INT_NUM Bus Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

7.1 Supported INO Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

7.2 Bus Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .74

7.3 Bus Protocol Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

8. Clocks, Resets and MCU Initialization Content . . . . . . . . . . . . . . . . . . . . . . . 77

8.1 Clocks. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

8.2 MCU Power-Up Operation and Register Initialization Programming. . . . . . . . . . . . . 83

ii − UltraSPARC IIe Processor User’s Manual

Sun Proprietary/Confidential: Internal Use Only

List of Figures

FIGURE 1-1 Simplified Processor Block Diagram and I/O Signals . . . . . . . . . . . . . . . . . . . . . . 4

FIGURE 1-2 Typical System Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

FIGURE 2-1 Clocks Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

FIGURE 2-2 Power Management State Transitions Driven by Software . . . . . . . . . . . . . . . . . 14

FIGURE 2-3 Energy Star Register Data Field . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

FIGURE 2-4 General Purpose Outputs Data Field. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

FIGURE 3-1 Subsystem Interfaces Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

FIGURE 3-2 Physical Address, Cache Line, and Register Formats . . . . . . . . . . . . . . . . . . . . . 23

FIGURE 3-3 RAM Array Configurations for 4-Way and Direct-Mapped Modes . . . . . . . . . . 24

FIGURE 3-4 Direct-Mapped Cache Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

FIGURE 3-5 4-Way Set-Associative Cache Mode - Tag RAM Operation . . . . . . . . . . . . . . . . 28

FIGURE 3-6 4-Way Set-Associative Cache Mode - Data RAM Access. . . . . . . . . . . . . . . . . . 29

FIGURE 3-7 UPA_Config Data Field . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

FIGURE 3-8 Level 2 Cache Diagnostics Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

FIGURE 3-9 Level 2 Cache Tag RAM Diagnostic Register Formats . . . . . . . . . . . . . . . . . . . . 34

FIGURE 3-10 Level 2 Cache Data RAM Diagnostic Register Formats . . . . . . . . . . . . . . . . . . . 35

FIGURE 4-1 Memory Request Paths . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

FIGURE 4-2 MCU Memory Requests . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

FIGURE 5-1 Example Address Field Using 128 Mb SDRAMs on Double-Banked DIMM . . 53

FIGURE 6-1 Simplified Processor Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

FIGURE 6-2 PCI Bus Subsystem Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

FIGURE 6-3 DMA Address Translations from PCI to Main Processor Memory . . . . . . . . . . . 61

FIGURE 6-4 Endian Byte Swapping Datapaths. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

FIGURE 6-5 ROM Instruction Fetch Datapath . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

FIGURE 7-1 INO Packets on INT_NUM Bus in 1x Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

FIGURE 7-2 INO Packets on INT_NUM Bus in 2x Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

FIGURE 8-1 Simplified Reset Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

FIGURE 8-2 Processor Hard Reset Timing Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

FIGURE 8-3 Processor Soft Reset Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

FIGURE 8-4 Avoid Test Reset Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Sun Proprietary/Confidential: Internal Use Only

List of Figures − iii

iv − UltraSPARC IIe Processor User’s Manual

Sun Proprietary/Confidential: Internal Use Only

List of Tables

TABLE 0-1 Documentation List. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . viii

TABLE 1-1 Processor Implementation Comparison . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

TABLE 2-1 Energy Star Register Data Field . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

TABLE 2-2 STICK Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

TABLE 2-4 General Purpose Outputs Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

TABLE 2-3 STICK Compare Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

TABLE 3-1 Level 2 Cache Related CSR Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

TABLE 3-2 UPA_Config Register Data Fields . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

TABLE 3-3 L2-Cache Tag RAM Diagnostics Data Field . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

TABLE 3-4 Level 2 Cache Asynchronous Fault Status Register (AFSR) Addendum. . . . . . . 36

TABLE 4-1 Accessible Memory Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

TABLE 4-2 Physical Address Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

TABLE 4-3 I/O Subsystem Address Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

TABLE 4-4 Processor Subsystems Memory Mapped CSRs . . . . . . . . . . . . . . . . . . . . . . . . . . 41

TABLE 5-1 SDRAM Memory Commands Supported . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

TABLE 5-2 MRS Field . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

TABLE 5-3 MCU Control and Status Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

TABLE 5-4 Memory_Control_0 (MC0) Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

TABLE 5-5 Memory_Control_0 (MC0) Register Bit Definitions . . . . . . . . . . . . . . . . . . . . . . 47

TABLE 5-6 Memory_Control_1 (MC1) Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

TABLE 5-7 Memory_Control_1 (MC1) Register Bit Definitions: DIMM Chip Select . . . . . 48

TABLE 5-8 MC1 DIMM Chip Select Base Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

TABLE 5-9 MC1 DIMM Chip Select Base Address - Examples . . . . . . . . . . . . . . . . . . . . . . 49

TABLE 5-10 Memory_Control_2 (MC2) Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

TABLE 5-11 Memory_Control_2 (MC2) Register Bit Definitions: Miscellaneous . . . . . . . . . 49

TABLE 5-12 Memory_Control_3 (MC3) Register Address . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

TABLE 5-13 Memory_Control_3 (MC3) Register Bit Definitions: I/O Buffer Strength . . . . . 50

TABLE 5-14 SDRAM Row/Column Address Multiplexing . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

TABLE 5-15 Address Bit Usage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

TABLE 5-16 SDRAM Parameters for DIMM Configurations. . . . . . . . . . . . . . . . . . . . . . . . . . 53

TABLE 6-1 PCI Bus Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

TABLE 6-2 PCI Bus Protocol Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

TABLE 6-3 PCI Bus Error Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

TABLE 7-1 Incompatible INO Values When Using IChip2 . . . . . . . . . . . . . . . . . . . . . . . . . . 73

TABLE 8-1 Effects of Hard and Soft Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Sun Proprietary/Confidential: Internal Use Only

List of Tables − v

TABLE 8-2 Reset Sources and Effects . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

TABLE 8-3 Reset Propagation Times. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

vi − UltraSPARC IIe Processor User’s Manual

Sun Proprietary/Confidential: Internal Use Only

Preface

The UltraSPARC®IIe processor manual contains information about the architecture and programming

of the UltraSPARC IIe processor. It describes the details of the processor’s new features.

The UltraSPARC IIe processor is part of Sun Microsystems’ UltraSPARC II Processor family, an

enhanced 64-bit, SPARC V9 architecture implementation. The UltraSPARC IIe processor includes an

SDRAM memory controller that supports SDRAM DIMMs and a 32-bit, 66 MHz PCI bus interface,

compatible with the PCI Specification, Version 2.1. The processor integrates a 256 KB L2-cache onto

the chip, includes a clock frequency controller and new STICK timer, and operates at a lower processor

core voltage than previous processors.

SPARC V9 Architecture Manual

The SPARC Architecture Manual, Version 9 defines the processor architecture and is available from

many technical bookstores or directly from its copyright holder:

SPARC International, Inc., 535 Middlefield Road, Suite 210

Menlo Park, CA 94025, (415) 321-8692

The SPARC Architecture Manual, Version 9 provides a complete description of the SPARC V9

architecture. Since SPARC V9 is an open architecture, many of the implementation decisions have been

left to the manufacturers of SPARC-compliant processors. These “implementation dependencies” are

introduced in The SPARC Architecture Manual, Version 9.

UltraSPARC IIi User’s Manual

Since the UltraSPARC IIe processor is very similar to the UltraSPARC IIi processor, the UltraSPARC IIi

User’s Manual is a necessary companion to UltraSPARC IIe User’s Manual Supplement.

UltraSPARC I/II User’s Manual

The original UltraSPARC IIs-series processor is described in the UltraSPARC I/II User’s Manual. In

some cases, this manual may provide additional information concerning the operation of the processor.

Normally, the UltraSPARC IIi User’s Manual is sufficient as a supplement.

Other UltraSPARC User’s Manuals

All other processor UltraSPARC II User Manuals may be helpful.

Preface − vii

Sun Proprietary/Confidential: Internal Use Only

Textual Conventions

Font Usage:

• Italic font is used for emphasis, book titles, and the first instance of a word that is defined. Italics are

also used for Assembly Language terms.

• Courier font is used for register fields (named bits), instruction fields, signals, and read-only

register fields. Courier is also used for literals, instruction names, and software examples.

• Bold font is used for emphasis.

• UPPERCASE items are acronyms, instruction names, or writable register fields, and external signals.

Note: Names of some instructions contain both uppercase and lowercase letters.

• Underbar character (_) joins words together in registers, register fields, and signal names.

Notation:

• Square brackets ‘[ ]’ indicate the bits of a register field or external signal name.

• Angle brackets ‘< >’ indicate a textual substitution.

• h7’03C indicates first 7 least significant bits in the hex number 03C are relevant.

Examples:

• SIGNAL_NAME, BUS_SIGNALS[31:0], ACTIVE_LOW_SIGNAL_L

• Register_Bit_Field, Range_Of_Bits[3:0]

• <enter_filename>, Emphasis

• BERR bit

Where to Find Things

The following table can be used to find discussions about the UltraSPARC IIe processor.

The UltraSPARC II processor User’s Manual includes the UltraSPARC IIi User’s Manual and the

UltraSPARC I/II User’s Manual.

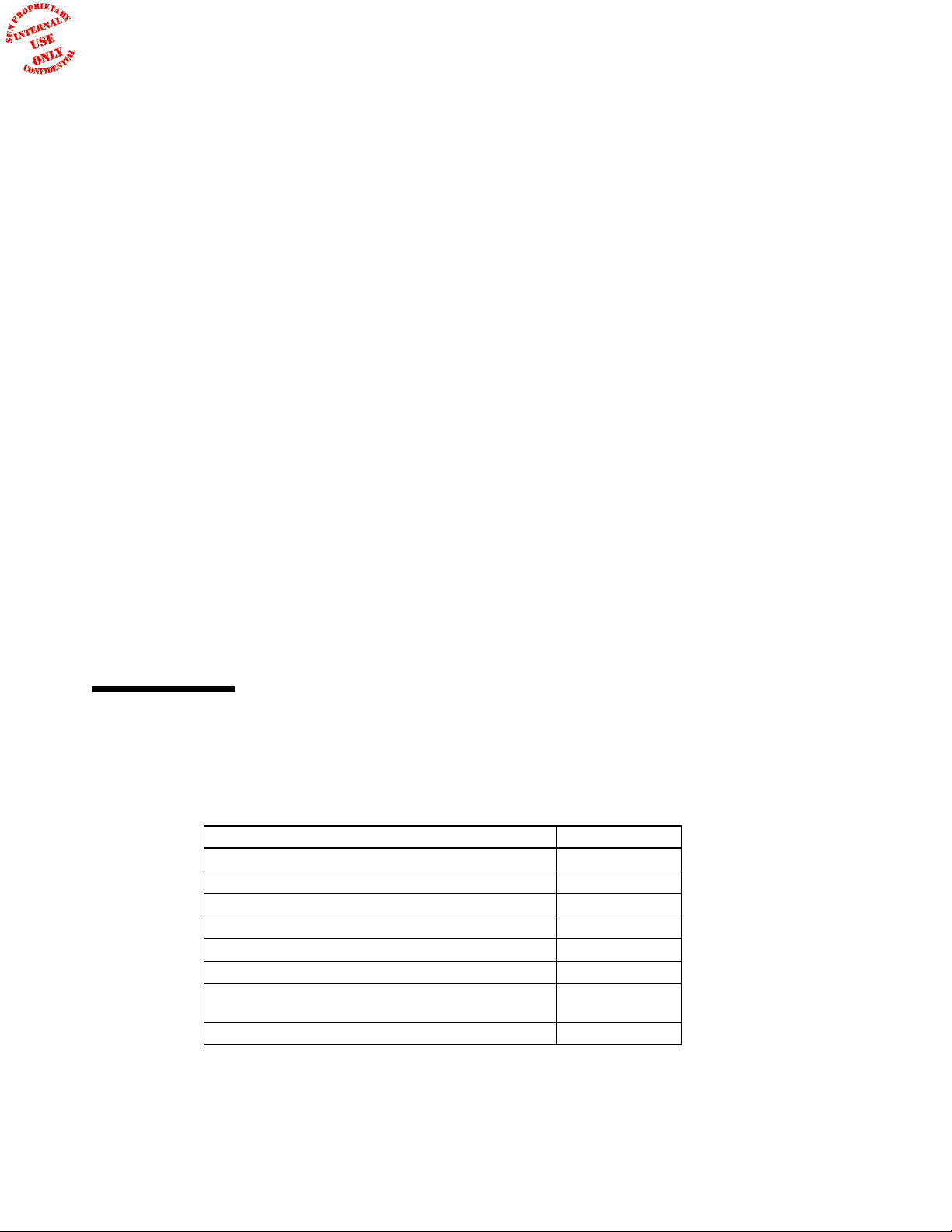

TABLE 0-1 Documentation List

Item

Architecture, Operation, and CSRs of

processor/MMU

Architecture, Operation, and CSRs of

L1-caches

Architecture, Operation, and CSRs of

L2-caches

viii − UltraSPARC IIe Processor User’s Manual

Sun Proprietary/Confidential: Internal Use Only

Document

Name

Chapter/Section

User’s Manual

User’s Manual

User’s Manual

UltraSPARC II

UltraSPARC II

UltraSPARC IIe

Reference

Chapter 3, Level 2 Cache Subsystem,

page 19

TABLE 0-1 Documentation List (Continued)

Document

Item

Architecture, Operation, and CSRs of

Memory Controller

Architecture, Operation, & CSRs of PCI

Subsystem

Clock Operations User’s Manual

Errata upto UltraSPARC IIi User’s Manual

Glossary User’s Manual

Interrupts and Traps User’s Manual UltraSPARC II

Memory ASI Definitions User’s Manual

Memory Transaction Ordering User’s Manual

Power Management Energy Star (E-Star)

Operation

Programming Code Generation Guidelines User’s Manual

Programming Grouping Rules and Stalls User’s Manual

System Memory Map User’s Manual

Name

Chapter/Section

User’s Manual

User’s Manual

User’s Manual

UltraSPARC IIe

UltraSPARC IIi

UltraSPARC IIe Section 2.1, Clocks, on page 11

UltraSPARC II

UltraSPARC II

UltraSPARC II

UltraSPARC II

UltraSPARC IIe

UltraSPARC II

UltraSPARC II

UltraSPARC IIe Section 4.3, Memory Space, on page 39

Reference

Chapter 5, Memory Control Unit

(MCU), page 43

UltraSPARC IIi User’s Manual,

Chapter 19

UltraSPARC II

Appendix K

UltraSPARC II

Chapter 11

UltraSPARC II

Chapter 6 and this document

Section 2.2, Clock Frequency Control,

on page 13

UltraSPARC II

Chapter 21

UltraSPARC II

Chapter 22

i User’s Manual,,

i User’s Manual,,

i User’s Manual,,

i User’s Manual,,

i User’s Manual,,

Sun Proprietary/Confidential: Internal Use Only

Preface − ix

x − UltraSPARC IIe Processor User’s Manual

Sun Proprietary/Confidential: Internal Use Only

CHAPTER

1

UltraSPARC IIe Processor Overview

The UltraSPARC IIe processor integrates a 256 KB L2-cache, an SDRAM memory controller, a 66 MHz

32-bit PCI Bus Interface, and a power management feature. The processor is very similar to all other

UltraSPARC II processors. It implements the 64-bit SPARC V9 architecture and the VIS

set. The SPARC V9 architecture provides binary compatibility across all SPARC processors. The VIS

instruction set performs parallel execution on multiple pixel data widths of 8 and 16 bits to accelerate

the most common operations related to processing, 2D and 3D graphics, compression algorithms, and

numerous network operations. The VIS instruction set enables high bandwidth for memory-to-processor

and memory-to-memory transfers by providing 64-byte block load and block store operations.

Integrated Features

The SDRAM DIMM memory controller supports up to 2 GB of memory using four double-sided,

512 MB DIMMs with 128 Mb SDRAMs or four single sided, 512 MB DIMMs with 256 Mb SDRAMs.

TM

instruction

The PCI Bus subsystem provides command and data buffering, and an I/O memory management unit

(IOM) for PCI bus masters accessing main memory. The processor’s host bus interface is PCI Bus 2.1

compatible, 32 bits wide, operates at up to 66 MHz, sends and receives 3.3 V signals, and is often

connected to Sun’s Advanced PCI Bridge (APB). The APB extends the PCI Bus structure to include two

additional bus segments of 32 bits at 33 MHz with 3.3 or 5.0 V signaling.

The fully integrated L2-cache contains up to 256 KB of space for instructions and data. The L2-cache

allocates space in 4-way set-associative and direct-mapped mode.

Power Management Logic provides a mechanism to slow down the processor clock rate. This reduces

power consumption while running the operating system.

The JTAG interface supports boundary scan for systemboard interconnect testing.

Each functional area on the UltraSPARC IIe processor maintains decentralized control, allowing many

activities to overlap.

Chapter 1 • UltraSPARC IIe Processor Overview − 1

Sun Proprietary/Confidential: Internal Use Only

1.1 UltraSPARC IIe Processor Implementation

1.1.1 New Features

The following list of items are features in the UltraSPARC IIe processor that are not necessarily found

in previous UltraSPARC processors (s-series and II), but will impact the system software and some of

the application software.

• Memory Controller (SDRAM) − New, impacts initialization code (firmware)

• Clock Control Unit (1/2 and 1/6 frequency modes) − New, enables Energy Star (E-Star) mode

• STICK Timer − New, impacts Operating System (OS) time base when E-Star mode is used

• Traps − Minor software changes for the STICK timer support

• L2-cache − New internal 256 KB cache replaces external L2-cache. New cache flushing method

required, no other impact to software code

• Four General Purpose Output (GPO) signals − New, available for PCI clock control or other

functions

1.1.2 Features Removed

The following list of items are not supported in the UltraSPARC IIe processor that were supported in

previous UltraSPARC processors.

• UPA Bus (all port types, including UPA64S)

• External tag and data L2-cache SRAMs (replaced by internal cache RAM arrays)

• EDO DRAM memory controller (replaced by SDRAM memory controller)

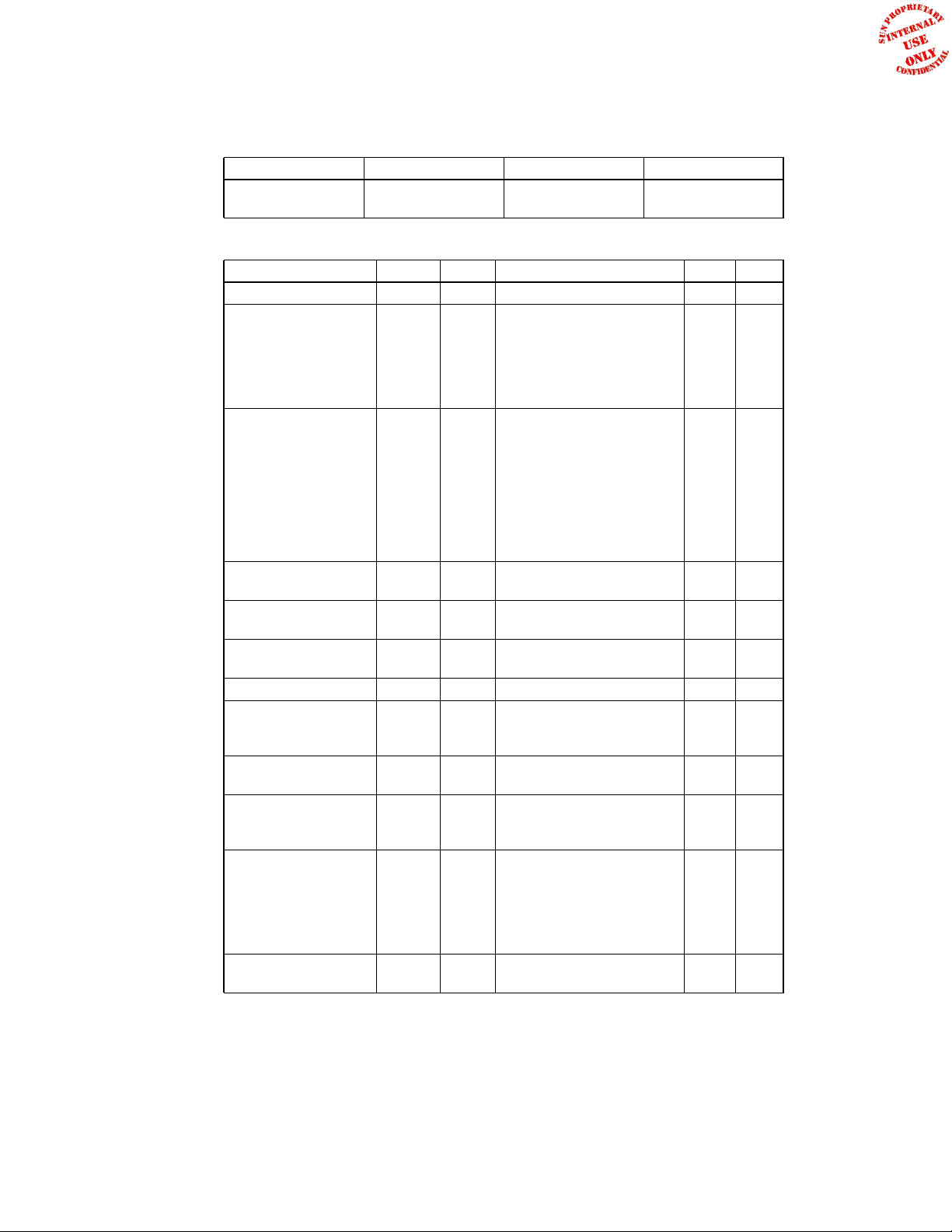

1.1.3 Processor Comparison

All processors listed below include the UltraSPARC II pipeline and the VIS instruction set. The MMU

and L1-caches structures are very similar.

TABLE 1-1 Processor Implementation Comparison

UltraSPARC IIs-series UltraSPARC IIi UltraSPARC IIe

TM

Sun Platforms

Year of first system 1996 1998 2000

Clock Frequency 167 to 480 MHz 270 to 440 MHz 400, 500 MHz

Process Technology 0.35 and 0.25 µm Al 0.35 and 0.25 µm Al 0.18 µmAl

System Bus UPA64M (up to 64-way) UPA64S (graphics only) PCI

I/O Bus

Memory Bus EDO DRAM EDO DRAM SDRAM

2 − UltraSPARC IIe Processor User’s Manual

Ultra

Sun Enterprise

S-bus and PCI bus via

UPA system bridge

1, Ultra 2,

TABLE 1-1 shows a comparison of processor implementations.

TM

TM

t1120, t1125,

100,

TM

Servers

Ultra 10, Ultra 20,

UltraAXi

PCI 66 MHB, 32-bit

Sun Blade

Netra

t1400, t1405,

CP2060, CP2080,

AX1105

Sun Proprietary/Confidential: Internal Use Only

TABLE 1-1 Processor Implementation Comparison (Continued)

UltraSPARC IIs-series UltraSPARC IIi UltraSPARC IIe

Maximum Memory 1 GB 2 GB

L2-cache

Energy Star Mode No No 1/2 and 1/6

1 to 8 MB, external,

module dependent

256 KB to 1 MB, external,

module dependent

1.2 Processor Architecture

The UltraSPARC IIe processor consists of six major components. The components are listed with their

interconnections in

The central compute engine and primary caches in the UltraSPARC IIe processor provides very similar

functionality as all other UltraSPARC II processors. The UltraSPARC IIe processor has integrated

features to further reduce systemboard size, board cost, and power dissipation.

1.2.1 Processor/MMU/Primary Level 1 Caches

FIGURE 1-1.

256 KB On-Chip,

4-way Set-Associative

Compatibility Note – The primary level 1 caches are the same as all other UltraSPARC II

processors, with an enhancement for trap generation to serve the new STICK timer.

Documentation Note – See the other UltraSPARC II processor manuals for the description of the

processor, MMU, and primary caches.

1.2.2 Integrated Level 2 Cache

• Secondary Cache (L2-Cache) − Unified Instruction-Data Memory, 256 KB, 4-way set-associative or

direct-mapped mode

• Cache Control Unit (ECU) − Interfaces the L2-cache to the processor, Memory, and PCI subsystems

1.2.3 SDRAM Memory Subsystem

• Memory Interface Unit (MIU) − Accepts, buffers, checks for data coherency, and arbitrates memory

requests

• SDRAM Memory Control Unit (MCU) − 72-bit interface

Chapter 1 • UltraSPARC IIe Processor Overview − 3

Sun Proprietary/Confidential: Internal Use Only

UltraSPARC IIe Processor

processor/MMU/Caches

• Integer Execution Unit (IEU)

• Floating Point Unit / VIS Execution

• Prefetch and Decode Unit (PDU)

• Load/Store Unit (LSU)

Cache Control Unit (ECU)

processor/MMU/

I-Cache

MMU

PDU

Cache Control Unit

L2-cache

Memory

TAG

256

KB

D-Cache

LSU

(ECU)

Clocks, Resets

• Clock Control Unit

• Energy Star Logic

• Reset Logic

L2-cache Memory

• Tag RAM Array

• Data RAM Array (256 KB)

Clocks, Resets

IEUs

FPUs

VIS

Memory Subsystem

PCI Bus Subsystem

PDP

PIE

IOMPBM

CCU

ESTAR

Resets

MIU

MCU

Memory Subsystem

• Memory Interface Unit

• Memory Control Unit

PCI Bus Subsystem

• PCI Data Path (PDP)

• PCI Bus Module (PBM)

• I/O Memory Management Unit (IOM)

• Resets, Interrupts, Error (PIE)

Clock, Reset, Mode Signals

• CLKA & CLKB

• SYS_RESET_L,

• P_RESET_L, X_RESET_L

• RMTV_SEL

• VID

• GPO

Power, Ground

• Vdd_IO

• Vdd_core

• V

DD_PLL,VDD_DIFF

• VSS,V

SS_PLL

SDRAM Signals

• MEM_CLK/CLKE

• MEM_CS/WE

• MEM_RAS/CAS

• MEM_ADDR/BANK

• MEM_DATA/ECC

• MEM_SCLK_OUT/IO_SCLK

JTAG Test Signals

• TCK

• TRST_L

• TMS

• TDI, TDO

PCI Bus Signals

• PCI_AD

• PCI_CBE_L

• PCI_FRAME_L

• PCI_I/TRDY_L

• PCI_REQ/GNT_L

• PCI_DEVSEL_L

• PCI_P/SERR_L

FIGURE 1-1 Simplified Processor Block Diagram and I/O Signals

• PCI_RST_L

• PCI_CLK, PCI_REF_CLK

• INT_NUM

• SB_DRAIN

• SB_EMPTY

• SYNC_3TO1

• PCI_STOP_L, PAR

1.2.4 PCI Bus Subsystem

Compatibility Note – The PCI Bus subsystem is same as the UltraSPARC IIi processor.

The major blocks of the PCI Subsystem includes:

• PCI Bus Module (PBM) − 33/66 MHz, 32-bit, 3.3 V PCI Host Bus Interface

• I/O Memory Management Unit (IOM) − Translates PCI addresses to memory’s physical address

4 − UltraSPARC IIe Processor User’s Manual

Sun Proprietary/Confidential: Internal Use Only

Test Signals

• PLLBYPASS, EPD

• CPU_L5CLK, PCI_L5CLK

• RAM_TEST, ITB_TEST

• PMO

• TEMP_SENSE

• EXT_EVENT

• OBSRV_MCU

• PCI Data Path (PDP) − Dual 64-byte data buffer (one for PIO and one for DMA)

• PCI Resets, Interrupts, and Error (PIE) −Εxternal interrupts processed

The PCI Subsystem is clocked independently from the processor. A 2-entry, bidirectional command

buffer is at the PCI to processor clock domain boundary to decouple activities from the processor to

improve PCI data transfer bandwidth.

1.2.5 System Control

Clocks

• Processor Clock Input − Differential CLKA/B

• New: Clock Control Unit (CCU) − PLL, 1/2 and 1/6 divider select

• Internal Clock Distribution − Utilizes internal PLL to reduce on-chip clock skew

• Memory Clock derived from CLKA/B − Programmable divider

• PCI Clock − 66 MHz Subsystem Clock, 33/66 MHz PCI Interface Clock

Resets

• POR, system (hardware), and XIR (software)

• Red_State Mode Trap Address Vector Select (RMTV_SEL)

• Test Interfaces: JTAG, Factory Tests

Diagnostics

• Control Status Registers (CSRs) − Most processor subsystems

• TAP Controller, JTAG − Boundary Scan

1.3 System Perspective

The UltraSPARC IIe processor interfaces directly to industry standard SDRAM DIMMs for memory.

The processor also contains a PCI 2.1 compatible bus interface for system I/O functions. These

interfaces provide a high degree of compatibility with standard design practices and device interfacing.

The entire system is memory mapped with Address Space Identifiers (ASI) that add functionality to each

load/store transaction from the processor. This expands the effective address space of the processor and

reveals special registers for system control.

Sun offers and recommends a number of system devices, including:

• Advanced PCI Bridge (APB) that expands the UltraSPARC IIe PCI Bus Interface to two PCI Bus

segments.

• PCIO-2 Multifunction PCI I/O controller that supports Ethernet, Sun’s 8-bit E-Bus, USB, and

IEEE1394

• IChip2 System ASIC for I/O interrupt concentration, and PCI clocks

Older devices compatible with the UltraSPARC IIe processor includes:

Chapter 1 • UltraSPARC IIe Processor Overview − 5

Sun Proprietary/Confidential: Internal Use Only

• PCIO Multifunction PCI I/O controller that supports Ethernet and Sun’s 8-bit E-Bus

• RIC System ASIC for I/O interrupt concentration, reset control, and JTAG clocks

These devices provide Sun-proven hardware and software compatibility. System designers can choose

from a number of architectures based on these and standard PCI devices. Design requirements and

software efforts need to be considered in addition to device functionality when choosing the best

devices for an architecture.

FIGURE 1-2 illustrates a typical system block diagram.

Clocks

&

Resets

JTAG

RIC or

IChip

Concentrator

External Interrupts

Primary PCI System Bus

32-bit, 33/66 MHz, 3.3 V

PCI Devices on

Primary Bus

A Sun Architecture is shown.

Other architectures are possible

using industry-standard PC devices.

INT_NUM

FIGURE 1-2 Typical System Block Diagram

UltraSPARC IIe

Processor

Advanced PCI

Bridge (APB)

PCI Devices on

Secondary Bus

64-bit Data

plus 8-bit ECC

Sun I/O

Controller

(PCIO-2)

A

B

8-bit E-Bus

SDRAM DIMMs

16 MB - 2 GB

PC-100 Compatible

32-bit, 33 MHz, 3.3/5 V

32-bit, 33 MHz, 3.3/5 V

Super I/O

Chip

Boot Flash ROM

NVRAM/RTC

Keyboard/Mouse

Floppy

Serial/Parallel

IR/USB/GPIO

1.3.1 Power Management

The processor can be slowed to 1/2 and under certain operating conditions, 1/6 the normal operating

frequency. The memory controller can put the SDRAMs into Self Refresh mode. Software can further

reduce system power consumption by controlling system devices with power down capabilities.

1.3.2 Memory Subsystem

The processor supports up to four double-sided PC-100 style SDRAM DIMMs (8 banks, total). The

processor clock to SDRAM clock ratio is selectable (4 to 7).

6 − UltraSPARC IIe Processor User’s Manual

Sun Proprietary/Confidential: Internal Use Only

Each DIMM can have one or two physical banks and they can all be of a different address size and

configuration. Modes and timing parameters are shared across the DIMMs. The memory interface has

programmable I/O buffer strengths to adjust the DC current output drive on separate groups of signals to

optimize signal transmission integrity over various capacitive loading conditions. SDRAM memories

can be operated in Self Refresh mode to reduced power consumption.

1.3.3 PCI Bus Architecture

The PCI Bus subsystem directly interfaces the processor to a 32-bit, Version 2.1 compliant PCI Bus

running at speeds up to 66 MHz (which yields a maximum theoretical transfer rate of 264 MB/s). The

PCI Bus Arbiter can support up to four external PCI Bus Masters. The number of devices that can be

attached depends on the physical limits and the bus clock frequency. A built-in I/O Memory

Management Unit (IOM) will translate PCI memory space addressees from the PCI Bus Master to the

physical addresses of the main memory. The processor is a PCI Slave in this DMA transfer mode to and

from memory. The IOM also supports hardware tablewalk in the case of a TLB miss in the IOM. All

memory reads and writes initiated by a PCI Bus Master (DMA) are cache coherent with the processor.

The processor boots by initiating a 32-bit memory read request on the PCI Bus Interface. The

UltraSPARC IIe processor has two sets of trap vectors to be compatible with Sun and the PC boot

address modes.

Advanced PCI Bridge (APB) Chip

The APB extends the UltraSPARC IIe PCI Bus to two PCI 2.1 bus segments of 33 MHz, 32-bit each.

The APB drives to 3.3 V levels. The secondary bus segments have configurable I/O buffers to be 5 V

tolerant. The APB supports DMA from up to four bus masters on each secondary bus segment.

The APB interfaces seamlessly with the UltraSPARC IIe processor. Software is available to support the

APB and the 2115x class of PCI bridges.

System Interrupts (INT_NUM Bus)

The PCI subsystem processes I/O interrupts from the systemboard that are received on its 6-bit

INT_NUM bus. Dozens of interrupt lines are scanned, encoded or concentrated onto the INT_NUM bus

by a system ASIC containing an “Interrupt Concentrator.” The UltraSPARC IIe processor uses software

interlocks and hardware write buffer (store buffer) flushing logic to synchronize a DMA transfer to the

interrupt handler.

System interrupts are considered part of the PCI Subsystem because they service PCI devices or devices

indirectly attached to the PCI Bus.

PCIO Multifunction PCI I/O Controller

The PCI I/O controller (PCIO, STP2003QFP) chip is a multifunction PCI Controller that includes a 10/

100 Ethernet interface and an E-Bus host controller.

PCIO-2 Multifunction PCI I/O Controller (Enhanced)

The second generation PCI I/O Controller (PCIO-2, SME2300BGA) chip is a multifunction PCI

Controller that includes a 10/100 Ethernet interface, an E-Bus host controller, an IEEE 1394 Firewire

Interface, and four USB bus interfaces.

Chapter 1 • UltraSPARC IIe Processor Overview − 7

Sun Proprietary/Confidential: Internal Use Only

1.3.4 System ASICs

RIC Reset/Interrupt/Clock ASIC

The RIC System Controller (SME2210) supports the system resets, system interrupts, system scans, and

system clock control functions for UltraSPARC II s-series processors. Its features includes:

• Resets from power supply, reset buttons, and scan chain

• Interrupt Concentrator − 41 signals in, 6-bit encoded INT_NUM bus out

• Directs scan inputs and outputs through scan chains

• Combinational logic for UPA bus speed

• 160 pin PQFP

IChip2 Interrupt Controller ASIC (Enhanced)

The IChip2 System Controller (SME2212QFP) provides similar Interrupt Concentrator function as the

RIC chip. The rest of the IChip2 includes a PCI clock controller requiring a differential voltage input

signal.

• Interrupt Concentrator − 48 signals in, 6-bit encoded INT_NUM bus out

• PCI Clock Controller − Compatible with asynchronous dual bus structures

• 128-pin TQFP package

• Newer device than RIC

The IChip and IChip2 controllers are functionally equivalent. The IChip System Controller is packaged

in a 120-pin MQFP.

1.4 Software Perspective

There are new ASIs for accessing the memory controller, the L2-cache RAMs, and the PCI Bus

Interface Controllers. Main memory (SDRAMs) is mapped as cacheable. All the PCI memory spaces

are non-cacheable memory mapped. This includes configuration, I/O, and memory.

Compatibility Note – The processor architecture is similar to the processor architecture of all other

UltraSPARC II processors.

The PCI Bus architecture is similar to the PCI architecture in the UltraSPARC IIi processor.

Endianess Note

The UltraSPARC IIe processor uses the big-endian addressing format. The code space and all processor

registers are big-endian except the PCI Configuration Space Header in the PCI subsystem and the PCI

Bus itself.

The processor supports little-endian data structures using a combination of the byte swapper in the PCI

Bus subsystem and the ASI descriptors of the processor.

8 − UltraSPARC IIe Processor User’s Manual

Sun Proprietary/Confidential: Internal Use Only

System Bus Hierarchy Model Note

The UltraSPARC system architecture is bus hierarchy-based. The processor’s I/O system bus is the PCI

Bus Interface. The optional Advanced PCI Bridge (APB) provides two secondary PCI Bus segments.

Sun’s PCIO-2 PCI Multifunction I/O Controller provides an interface to Ethernet, IEEE 1394, E-Bus

and USB type busses to further define the system’s bus hierarchy which originates at the processors

primary Host PCI Bus Interface.

Chapter 1 • UltraSPARC IIe Processor Overview − 9

Sun Proprietary/Confidential: Internal Use Only

10 − UltraSPARC IIe Processor User’s Manual

Sun Proprietary/Confidential: Internal Use Only

CHAPTER

2

Clocks, System Timer, GPO, and Resets

2.1 Clocks

There are three root clock domains in normal operation.

• Processor clock (CLKA, CLKB, differential signal pair, 400/500 MHz)

• PCI (PCI_CLK LVTTL signal, 66 MHz)

• JTAG (JTAG_TCK LVTTL signal)

All three sets of clocks are normally asynchronous to each other. Synchronizers are used to transfer

address data, and control signals between the PCI and processor clock domains.

clocks block diagram.

FIGURE 2-1 illustrates a

CLKA

CLKB

PCI_CLK

PCI_REF_CLK

JTAG_CLK

ESTAR_Mode[1:0]: E_Star_Mode

Clock Control Unit

Multiply/Divide

Logic

PLL

Processor Clock Domain

PCI Clock Domain

PLL

PCI Bus I/F

FIGURE 2-1 Clocks Block Diagram

Control

ú12

PCI to processor

Synchronizer

en

Processor Clock

Clock Buffer and

Distribution Tree

JTAG Clock Domain

Mem_Control_0[30:29]: Clock_Ratio

4, 5, 6, 7

Latch Read Data

Processor Core Logic

TIC

Logic

en

STICK

Logic

JTAG Logic

INT level 14

INT level 14

SDRAM

Clocks

TO

SDRAMs

Chapter 2 • Clocks, System Timer, GPO, and Resets − 11

Sun Proprietary/Confidential: Internal Use Only

2.1.1 CLKA and CLKB Processor Clock Signal

The CLKA and CLKB clock pair are driven continuously and at a constant rate of 1/2 the processor’s

normal operating frequency.

Clock Control Unit (CCU)

The processor clock input signal on the processor is a differential signal pair. The Clock Control Unit

(CCU) converts this to a CMOS signal, uses it to drive its PLL, and operates high speed dividers to

provide three processor frequency mode settings to reduce power dissipation.

The processor clock is driven at a constant frequency by system logic and runs continuously while

operating the processor. The clock is driven at one-half the processor operating frequency in normal

operating mode. The processor frequency can be reduced to 1/2 (same frequency as input clock signal)

or 1/6 the normal operating frequency, by writing to the Energy Star (E-Star) register.

Timebase for Software − TICK and STICK

The processor contains two clock timers that can be read by software or be used to generate interrupts

at fixed intervals of time. Each timer contains a counter, a count value register, and a compare register.

The counter updates the count value register. When the count value register equals the compare register

value, an interrupt is generated. The TICK logic is incremented by the processor clock.

The STICK logic (new in the UltraSPARC IIe processor) uses the PCI clock for a constant time base.

The PCI clock provides a constant time base to the processor STICK logic when the TICK logic is

affected by the switch in processor frequency. The PCI_REF_CLK clock input must remain at a

constant rate for the STICK logic to keep good time. The system software can use the original TICK or

the new STICK logic, or a combination of both to maintain a time reference. The TICK logic is affected

by the processor operating frequency and the STICK logic is affected by the PCI clock frequency.

The operation of TICK timer is described in the UltraSPARC IIi User’s Manual.

2.1.2 Memory Clocks

The MEM_SCLK[7:0] signals are derived by dividing the processor clock by 4, 5, 6, or 7. The memory

controller is discussed in detail in Chapter 5, Memory Control Unit (MCU), page 43.

2.1.3 PCI Subsystem Clocks

The PCI_CLK clock is driven at the PCI Bus Interface frequency, typically 66 MHz or 33 MHz,

although intermediate frequencies are also supported.

The PCI_CLK clock is divided and synchronized to the processor clock for the STICK logic. The

STICK logic is read by software to maintain accurate time using the PCI clock as a time basis

(independent of power down states in a processor).

2.1.4 JTAG Clock

The JTAG clock is independent of the other two clock domains.

12 − UltraSPARC IIe Processor User’s Manual

Sun Proprietary/Confidential: Internal Use Only

2.2 Clock Frequency Control

Power Management consists of software detecting a system that has been idle for a prolonged period of

time and then lowering the processor clock frequency to 1/2 or 1/6 the normal operating mode and

optionally programming the SDRAM devices into their power down, self-refresh mode. Additional

power savings in the system I/O is possible.

2.2.1 PCI/Processor Frequency Restrictions

The processor core frequency must be at least twice the frequency of the primary PCI Bus to ensure that

the processor core correctly detects signals driven by the PCI data path inside the processor. This is

further explained in the datasheet.

This requirement makes the 1/6 mode unusable when the primary bus frequency is 66 MHz.

2.2.2 Frequency Transitions

An example of state transitions for power management are shown in FIGURE 2-2. Consider the need to

set a new auto-refresh interval with each change of processor frequency. After software changes the

processor frequency, the software should, as a precaution, execute enough NOP instructions so at least

16 processor clocks occur before any memory or PCI references take place. The PCI subsystem should

also be quiescent. There is no transition supported from 1/1 to 1/6 mode or visa-versa.

Impact of PLL Enabled DIMMs

The buffered and registered DIMM types contain PLL circuits on the DIMM to reduce clock skew.

When the processor changes frequency, the memory clock frequencies changes, too. If this happens, the

PLL enabled DIMMs lose their PLL lock causing the DIMM to be unusable until it stabilizes. Since

there is no way to block memory accesses, one may occur while the PLL is locking. If this happens

there is a chance the memory transaction gets corrupted and the system fails.

For this reason, we recommend not using the power down modes with registered and buffered DIMMs.

Use unbuffered DIMMs when power management is required.

Chapter 2 • Clocks, System Timer, GPO, and Resets − 13

Sun Proprietary/Confidential: Internal Use Only

Normal Operating

Mode

1. Set ESTAR: 1/1 Mode

2. Wait 16 processor clocks.

3. Set refresh interval.

1. Set refresh interval.

2. Set EST AR: 1/2 Mode

3. Wait 16 processor Clocks

FIGURE 2-2 Power Management State Transitions Driven by Software

1/2 Frequency

No Self Refresh

1. Consider external devices

2. Set MC0: Self Refresh

Set EST AR: 1/6 mode

1. Clear MC0: Self Refresh

2. Consider external devices

1/2 Frequency

Self Refresh

Set EST AR: 1/2 mode

1/6 Frequency

Self Refresh

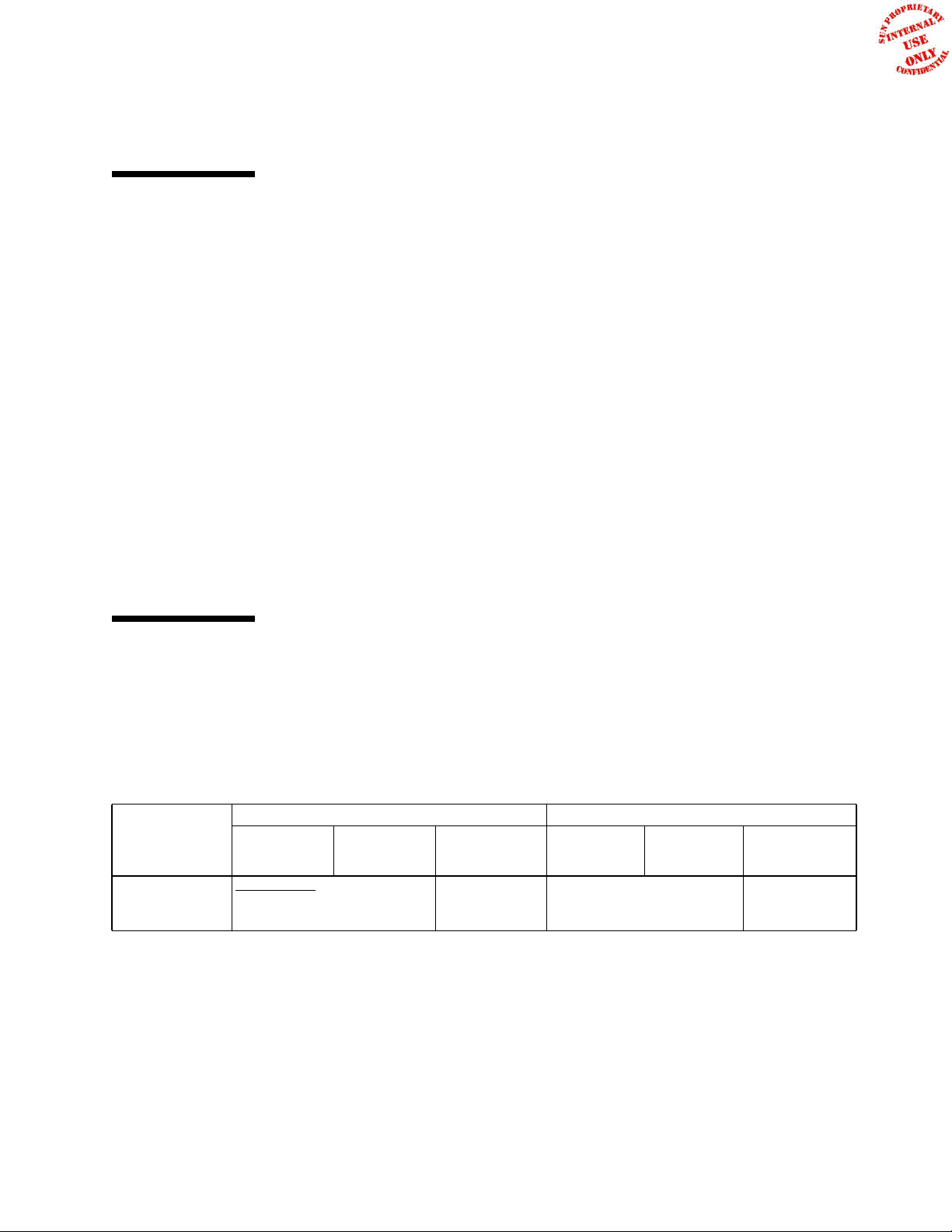

2.2.3 Power Management (Energy Star Register)

Power Management is controlled by writing to the E-Star register.

Note – The UltraSPARC IIe processor clocking must be kept active (1/1, 1/2, or 1/6 mode). The PCI

clock to the UltraSPARC IIe processor must remain active, but the PCI clock to the system devices can

be stopped if proper care is taken with the PCI Bus system devices. Control of the PCI clock generator

can be done by using two of the GPO signals that are driven directly by the UltraSPARC IIe processor

and controlled by software. Some of Sun’s architectures use GPO[1:0] for this purpose.

FIGURE 2-3 and TABLE 2-1 illustrates and describes the E-Star register data field, respectively.

E-Star Register Data Field

00000000000000000000000000000000000000000000000000000000000000

63

FIGURE 2-3 Energy Star Register Data Field

14 − UltraSPARC IIe Processor User’s Manual

Sun Proprietary/Confidential: Internal Use Only

Read/write: 0x01FE.0000.F080

E-Star

1

02

TABLE 2-1 Energy Star Register Data Field

Field Bits Description POR Type

Reserved 63:02 Reserved

00: Full Operating Frequency

E_Star_Mode 1:0

01: 1/2 Operating Frequency

10: 1/6 Operating Frequency

11: Reserved

2.3 System Interrupt Timer

When the processor frequency is lowered (via E-Star modes) the time base for the TICK logic in the

processor is affected. A new STICK timer has been created that is driven at the PCI_CLK signal input

frequency rate which must remain constant for the PCI Bus Interface Clock PLL.

The System Tick (STICK) can provide a constant time base for the operating system because the

PCI_CLK must be driven at a constant rate.

The STICK has an associated compare register (STICK_CMP ) to generate a periodic interrupt for the

operating system. The STICK alarm signal is gated with the TICK alarm signal. Either alarm (if

enabled) will generate a level-14 (0x4e offset) trap.

Documentation

Reference

00 R/W

The functionality is similar to the processor Tick (TICK) and Tick Compare (TICK_CMP) logic except

it is not subject to variations in the processor clock rate.

The STICK counter is clocked by the internal processor clock, but is enabled by a pulse derived from a

constant PCI Bus clock source. This means the PCI clock must remain on and at a known constant rate

for the operating software to maintain accurate time when using STICK. Similarly the processor clock

must remain active, but can be at a reduced rate.

The PCI clock is divided by 12 and fed into a synchronizer. The synchronizer issues an enabling pulse

to the STICK counter at 1/12 the PCI Bus clock speed and does so in the processor clock domain. The

enable rate is 5.5 MHz using a 66 MHz PCI Bus. The pulse is used to enable the STICK to make one

count. The processor clock rate is 67 MHz for a 400 MHz processor in 1/6 power down mode so the

enabling pulses from the synchronizer are always detected.

When the STICK_CMP logic determines that the timer has timed out, a level-14 interrupt

(STICK_ALARM) is generated to cause a trap in the processor, same as the TICK_CMP logic, only

separate. One, both, or neither timer can be enabled. We recommend enabling one timer at a time to

simplify software.

TABLE 2-2 and TABLE 2-3 describes the STICK Register and the STICK Compare Register, respectively.

TABLE 2-2 STICK Register

Field Bits Description POR Type

Reserved 63 Reads 0, No Write 0 R

Stick_Count 62:0 STICK Register Count Value 0 R/W

Chapter 2 • Clocks, System Timer, GPO, and Resets − 15

Sun Proprietary/Confidential: Internal Use Only

TABLE 2-3 STICK Compare Register

Field Bits Description POR Type

Stick_Alarm_Enable 63

Stick_Compare_Value 62:0

0 = Enable Stick Alarm (Int 14h)

1 = Disable Stick Alarm

Field is compared to Stick_Count.If

alarm is enabled and count matches, then

Int 14h is asserted.

2.4 General Purpose Outputs (GPO)

The UltraSPARC IIe processor has four general purpose output signals that come directly from the

processor and are controlled by software writable registers. Two of these outputs are designated by Sun

software for PCI clock control, but can otherwise be used for any purpose.

For software controlled output signals, set to 1 to drive output to 3.3 V. Set to 0 to drive output to 0 V.

Output is clocked by CLKA/CLKB.

FIGURE 2-4 and TABLE 2-4 illustrates and describes the general purpose outputs data field and register,

respectively.

0R

0 R/W

General Purpose Output (GPO) Data Field

0000000000000000000000000000000000000000000000000000000000000000

FIGURE 2-4 General Purpose Outputs Data Field

TABLE 2-4 General Purpose Outputs Register

Field Bits Description POR Type

Reserved 63:4 Reads 0, No Write 0 RO

GPO3 3 Controls state of GP3 signal 1 R/W

GPO2 2 Controls state of GP2 signal 1 R/W

GPO1 1 Controls state of GP1 signal 1 R/W

GPO0 0 Controls state of GP0 signal 1 R/W

2.5 Resets

Note: Bits [63:4] are not physically implemented.

These bits return zero when accessed.

GPO2GPO3

3

GPO1

1

GPO0

02463

The processor has two groups of resets − power-on and system resets, and software resets. The

power-on and system resets affect the entire processor and PCI Bus subsystem. A software reset simply

causes a processor trap. In each case, the cause of the reset is recorded in the Reset Control (RC)

register, the processor is put into its RED_State condition, and the processor code execution jumps to

non-cacheable ROM memory space.

16 − UltraSPARC IIe Processor User’s Manual

Sun Proprietary/Confidential: Internal Use Only

The Reset Control (RC) register contains bits to enable software to generate soft resets and to record the

highest level reset which the processor is responding to and recovering from.

Documentation Note – All of the Processor Reset information in this section is provided as an

overview. The operation of resets has not changed significantly from that of the UltraSPARC IIi

processor. The manual for this processor provides an additional source of information about processor

resets.

POR Reset (Hardware Reset)

The POR Reset is a hard reset that resets the processor and PCI Bus subsystem. The POR Reset is

caused by the assertion of the SYS_RESET_L signal pin, the P_RESET_L signal pin, or by writing to

the Soft_POR bit in the Reset Control Register. The POR Reset affects most of the processor and

propagates out to the PCI_RST_L signal pin to reset the PCI Bus subsystem.

The POR Reset causes the processor to immediately stop its current activity. The de-assertion of reset

allows a sequence of events to occur. During this sequence, the hardware is initialized, the processor is

put in its RED_State condition, the PCI_RST_L signal is released, and the processor begins

instruction execution to ROM memory space.

Chapter 2 • Clocks, System Timer, GPO, and Resets − 17

Sun Proprietary/Confidential: Internal Use Only

18 − UltraSPARC IIe Processor User’s Manual

Sun Proprietary/Confidential: Internal Use Only

CHAPTER

3

Level 2 Cache Subsystem

The Level 2 Cache (L2-cache) subsystem includes the L2-tag and L2-data memory arrays and various

Control, Status, and Diagnostic registers (CSRs). The L2-cache responds to the commands of the

“ECU.” The ECU manages the flow of the data and control signals and is driven by memory requests

and the cache states.

The ECU controls write buffers and monitors the addresses they contain in order to maintain data

coherency with the caches and main memory. The ECU interfaces to the PCI subsystem to support DMA

transfer requests from the PCI Bus into the coherent data domain of the processor memory.

The L2-cache memory is physically indexed and physically tagged. The cache line size in the L2-cache

and main memory is 64 bytes. The L2-cache can operate in 4-way set-associative mode, or

direct-mapped mode. The purpose of having two modes is to provide flexibility in operation for

performance considerations (4-way), predictable behavior (direct-mapped), and to flush the cache of

modified data (direct-mapped).

The L2-cache operates in a write-back mode. The primary I-cache and D-cache operate in write-through

mode.

Compatibility Note – The UltraSPARC IIe processor includes the L2-cache tag and Data RAM

arrays. Previous processors, like the UltraSPARC IIi processor, contain a cache controller that interfaces

to external tag and Data SRAMs. In addition, the L2-cache in the UltraSPARC IIe processor is enhanced

with a 4-way set-associative operating mode.

Documentation Note – The UltraSPARC IIi Processor User’s Manual contains information for the

processor, MMU, I-cache/PDU, D-cache/LSU, the cache controller (ECU), and the PCI Bus subsystem.

Since the operation of the UltraSPARC IIe processor is nearly identical to the UltraSPARC IIi processor

for these functions, please refer to the UltraSPARC IIi Processor User’s Manual. The L2-cache in the

UltraSPARC IIe processor is unique and not found on other processors.

3.1 Level 2 Cache Features

• 256 KB of Data Storage

■ Cache address space − PA[30:0] = 2 GB

■ Line Entry − 64-byte (8 data transfers)

■ Diagnostic Organization − 8192 64-bit data words per bank × 4banks

Sun Proprietary/Confidential: Internal Use Only

Chapter 3 • Level 2 Cache Subsystem − 19

• Tag RAM Array:

■ Line Entry − 15-bit tag + 2-bit status + 2-bit parity (single transfer)

■ Organization − 1024 cache line entries per bank × 4 physical banks × 20 bits

• Line Replacement Selection RAM Array (Rand Array):

■ Usage − 4-way set-associative mode only

■ Line Entry − 2-bit random replacement number (Rand)

■ Organization − 1024 cache line entries per bank × 4 banks × 64-byte cache line

Performance Features

The L2-cache is pipelined and operates in the 2-2 mode as defined by previous UltraSPARC products.

This enables the L2-cache to sustain the bandwidth of one 64-bit data transfers every two processor

clocks from the Data RAM array. The 64-bit datapath width exists throughout the L2-Cache subsystem.

■ Separate Tag and Data memory arrays support simultaneous access

■ Supports delayed write, byte-write, and bank-write

■ Access mode − 2-2 mode

The read access time of the tag RAM array is optimally designed to enable quick lookups of the

L2-cache.

The Cache Control Unit (ECU) is fully pipelined. For programs with large data sets, instructions are

scheduled with load latencies based on the L2-cache latency, therefore, the L2-cache acts as a large

primary cache. Floating-point applications use this feature to effectively “hide” D-cache misses.

Separate L2-cache miss and hit operations can overlap. Stores that hit the L2-cache can proceed while a

load miss is being processed. The L2-cache controller is also capable of processing reads and writes

without a bus turnaround penalty.

Block loads and block stores (these load or store a 64-byte line of data from memory or L2-cache to the

floating-point register file) provide high transfer bandwidth. By not caching block load/store operations

(they are still in the data coherent domain) into the L2-cache on a miss, the cache is available for other

data structures that are expected to be accessed more than once.

The ECU also provides support for multiple outstanding data transfer requests to the Memory

subsystem and the PCI subsystem.

The peak internal bandwidth to and from the processor and the I-cache or D-cache is 2.0 GB/s at

500 MHz.

The 4-way set-associative mode tends toward better performance. The direct-mapped mode has other

advantages, including a more friendly debug environment, and provides the mode to flush the cache

lines to main memory.

3.2 Architecture

The L2-tag array contains cache control and tag bits for the contents of the L2-data array. The L2-data

array contains 256 KB of data in four physical banks. These become a linear address space in

direct-mapped mode and each bank maps to one of the four ways in a 4-way set-associative mode.

A high-level diagram of the L2-cache in the UltraSPARC IIe processor is shown in

operation of the L2-cache is explained in Section 3.3, Cache Operating Modes, on page 23.

20 − UltraSPARC IIe Processor User’s Manual

FIGURE 3-1. The

Sun Proprietary/Confidential: Internal Use Only

UltraSPARC IIe Processor

MEMORY REQUESTS

I-cache

pro-

PDU

cessor

and

D-cache

MMU

LSU

Diagnostic

Access

CSRs

FIGURE 3-1 Subsystem Interfaces Block Diagram

Cache Control

Unit (ECU)

PCI Subsystem

(IOM, PBM)

ECU COMMANDS

L2-cache Control

Data Tag

Memory

Subsystem

Primary

PCI Bus

Main

Memory

3.2.1 Physical Address

There is no virtual address or context information in the L2-cache. The ASIs are decoded before

reaching the ECU. The fully pipelined L2-cache interface supports speculative loads and instruction

prefetch requests.

The L2-cache responds to the entire main memory address range and wraps above the 2 GB physical

address limit of the UltraSPARC IIe processor back to 0. See

map.

TABLE 4-2 on page 40 for a system memory

Chapter 3 • Level 2 Cache Subsystem − 21

Sun Proprietary/Confidential: Internal Use Only

3.2.2 CSR Summary Table

All L2-cache control, status and diagnostic registers are accessed as 64-bit data quantities. A non-64-bit

access causes a mem_access_exception trap. A non-aligned access causes a mem_address_not_aligned

trap. The CSR registers are listed in

64-bit load and store operations.

TABLE 3-1 Level 2 Cache Related CSR Registers

Register Name

LSU Control 0x45 0 No

UPA_Config 0x4A 0 Yes

Tag RAM Diagnostic

Data RAM

Diagnostics

Async Fault Address 0x4D (r/w) 0 No

Async Fault Status 0x4C (r/w) 0 Minor

1. Changed refers to differences between the UltraSPARC IIi processor and the

Access Method

ASI VA[40:0]

0x7E (read)

0x76 (write)

0x7E (read)

0x76 (write)

TABLE 3-1. The registers are not 64-bit wide, but are accessed with

Changed

[40:39] = 10 Yes

[40:39] = 01 Yes

1

Documentation Manual Section

UltraSPARC IIi

Manual

UltraSPARC IIe

Manual

UltraSPARC IIe

Manual

UltraSPARC IIe

Manual

UltraSPARC IIi

Manual

UltraSPARC IIe

Manual

UltraSPARC IIi

Manual

UltraSPARC IIe processor.

Appendix A.6

Section 3.6.1

Section 3.9.1

Section 3.9.2

Section 16.6.3

Section 3.9.3

Section 16.6.2

3.2.3 Diagnostic Support

Each RAM array is accessible for diagnostics as described in Section 3.9, Level 2 Cache Control and

Status Registers (CSRs), on page 32.

All the CSRs are listed in the UltraSPARC IIi Processor User’s Manual. A subset of CSRs for the

L2-cache are listed in

TABLE 3-1.

3.2.4 Data Formats

The L2-cache uses the physical address, cache line, and register formats shown in FIGURE 3-2.

22 − UltraSPARC IIe Processor User’s Manual

Sun Proprietary/Confidential: Internal Use Only

32-bit Physical Address (from processor/MMU or PCI)

64-bit

Index

Byte

64-bit

0

Page

Data Cache Line (64 Bytes)

64-bit

64-bit 64-bit

Control and Status Registers (CSRs) (Access w/ ASI, 64 bits)

CSR Register Fields

63

Diagnostic Registers (Access w/ ASI, 64 bits)

Tag RAM Fields

Data RAM Fields

63

FIGURE 3-2 Physical Address, Cache Line, and Register Formats

3.3 Cache Operating Modes

031

64-bit

0

0

64-bit

64-bit

The L2-cache has two normal operating modes: 4-way set-associative and direct-mapped. The L2-cache

also supports a diagnostic access path.

The L2-cache can operate completely in one mode or in a split mode operation. The cache mode defines

the cache line replacement algorithm.

To flush a cache operating in 4-way set-associative mode, program the L2-cache so that the D-cache/

LSU requests use the cache in direct mode temporarily. I-cache/PDU requests allocate in 4-way

set-associative mode.

The mode selection for instruction and data are controlled separately by the UPA_Config<37:36>

register bits (dm_instruction and dm_data).

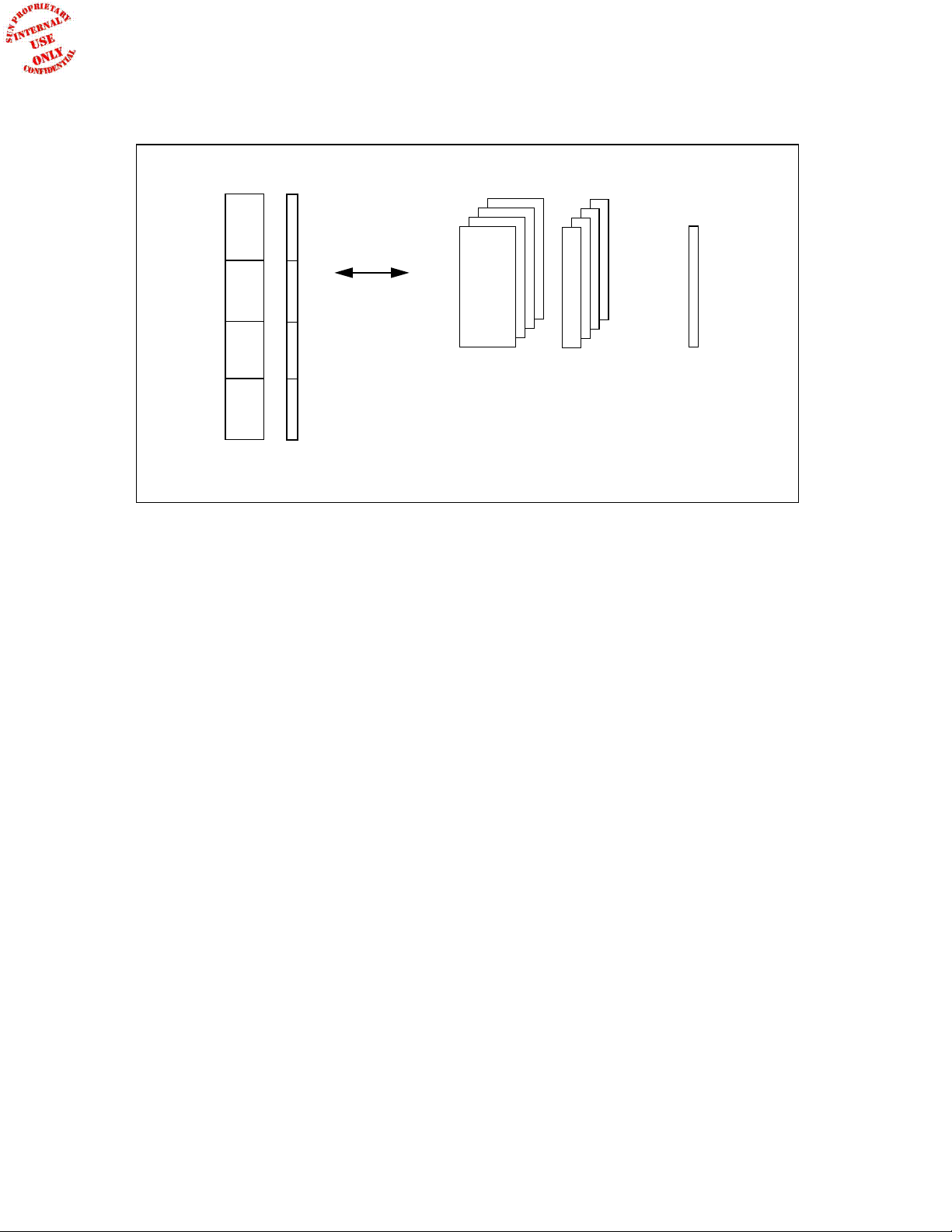

A comparison in the arrangement of the cache arrays in 4-way set-associative and direct-mapped mode

are shown in

FIGURE 3-3.

The Physical Address (PA) mapping into the RAM arrays using diagnostics accesses is shown in

FIGURE 3-8 on page 33.

Chapter 3 • Level 2 Cache Subsystem − 23

Sun Proprietary/Confidential: Internal Use Only

Direct-Mapped Mode

PA[17:0]

3FFFFh

2FFFFh

4-Way Set-Associative Mode

PA[15:0]

FFFFh

The cache mode for

instruction and data

1FFFFh

FFFFh

0h

64-bit 20-bit

256 KB

Data

FIGURE 3-3 RAM Array Configurations for 4-Way and Direct-Mapped Modes

requests can be changed

separately during

processor operation, but

care must be taken to

quiescent the associated

cache activity.

~12 KB

Tag

The direct-mapped representation

is shown with physical banks, but is

actually a seamless linear address space.

0h

64-bit

256 KB

Data

3.3.1 Cache Line Tag RAM Entries

Tag Value Field

The Tag value is compared to the index field of the physical address.

20-bit

~12 KB

Tag

PA[17:16]

WAY3

WAY2

WAY1

WAY0

2-bit

~0.25 KB

Rand

The Rand register is only used

in 4-way set-associative mode and

is the length of one way.

In 4-way set-associative mode,

each way corresponds to a physical

bank of RAM.

Line State (V and M bits)

The cache lines are in one of three states: modified, exclusive or invalid.SeeTABLE 3-3 on page 35.

A modified state means the data line is valid and has the latest copy of the data. In this case, the

L2-cache will source the data on a read hit. When a line replacement is needed, a modified line is

flushed to memory.

Exclusive is an older term. In the case of the UltraSPARC IIe processor, it means the data line is valid

and has not been modified.

Invalid cache lines do not contain valid data and are immediately available for a new entry. All cache

lines need to be initiated after reset to the invalid state after reset or power-up.

Parity Bits

The tag line is odd parity protected as is described in Section 3.9.3, Asynchronous Fault Status Register

Addendum, on page 36.

24 − UltraSPARC IIe Processor User’s Manual

Sun Proprietary/Confidential: Internal Use Only

Rand Bits

The Rand bits selects the way in 4-way set association replacement. The two Rand bits are considered

part of the tag line and determine the next way when a displacement is required.

3.3.2 Data RAM Organization

An L2-cache line consists of a 64-byte quantity that is accessed from the Data RAM array using eight

64-bit transactions.

There is one line state per 64-byte cache line (invalid, exclusive, or modified). If any byte is modified in

a cache line, then the whole cache line is considered modified.

3.4 Memory Requests

Requests to the L2-cache are generated by the ECU on behalf of the I-cache/PDU and D-cache/LSU,

and by the PCI Bus subsystem: all are cacheable.

Non-cacheable requests are forwarded to the PCI subsystem by the ECU.

When a cache line is displaced to allocate a new one, the old one is written to memory if it is in the

modified state. Otherwise the cache line is simply overwritten.

Documentation Note – Below are short descriptions on the types of requests serviced by the

L2-cache. Refer to the UltraSPARC IIi Processor User’s Manual for complete and detailed discussions

about these topics.

3.4.1 Instruction Cache/PDU Read Request

All cacheable instruction requests (including prefetch instruction fetches) that miss in the I-cache

become an I-cache/PDU read request to the L2-cache. This I-cache line fill operation is always 32 bytes.

The I-cache/PDU requests read-only accesses.

3.4.2 Data Cache/LSU Read and Write Requests

Load

Load instructions that miss in the D-cache are forwarded to the L2-cache.

A hit in the L2-cache generates a 16-byte read using two consecutive 8-byte accesses to support cache

line fills in the D-cache sub-block.

A miss causes the L2-cache to request a 64-byte cache line read of main memory. The 16 bytes of data

requested by the D-cache are sourced to the D-cache and the entire 64-byte cache line from memory is

put in the L2-cache, displacing an existing line.

Chapter 3 • Level 2 Cache Subsystem − 25

Sun Proprietary/Confidential: Internal Use Only

Block Load

Block load operations behave slightly different than load operations.

A hit in the L2-cache will cause the L2-cache to source the 64 bytes of data. No change to the cache

state is made.

A block load miss is forwarded to main memory and the data is returned to the processor without

allocating in the L2-cache.

Programming Note – Block load operations do not allocate cache memory space. Block loads are

always 64 bytes and aligned to a cache line boundary. Block loads are not ordered, but are within the

data coherent domain. Use the MEMBAR#Sync instruction to order block loads, if necessary.

Store

Cacheable stores are queued in the LSU and update both the D-cache and the L2-cache.

Store operations are 1, 2, 4, 8, or 16 bytes long. These transactions are always aligned on their natural

boundary.

A miss in the L2-cache will cause a fetch of a 64-byte cache line from memory and displacement of an

existing cache line. The L2-cache is then updated with the byte(s) waiting to be written.

Block Store

Block store operations behave slightly differently than store operations. Block store operations do not

allocate space in the L2-cache. The L2-cache is checked to see if there is a hit.

A hit will cause the data to be written into the L2-cache.

A miss causes the request to go directly to the memory and the cache is not allocated.

Block stores are always 64 bytes and aligned to a cache line boundary. Block stores are not ordered.

Block stores with commit force the data to be written to memory and invalidate copies in all caches, if

present.

Programming Note – Execute a MEMBAR#Sync after a block store and before using a load

instruction that references the data from the block store. Alternatively, a second block store will force

the previous block store into memory.

3.4.3 PCI DMA Read Request

The L2-cache will source data for DMA reads generated by a PCI Bus Master when a hit in the

L2-cache is detected. On a hit, the access does not affect main memory.

On a miss, the access is forwarded to main memory where the memory read transaction takes place.

There is no further involvement from the L2-cache.

26 − UltraSPARC IIe Processor User’s Manual

Sun Proprietary/Confidential: Internal Use Only

3.4.4 PCI DMA Write Request

When a hit is detected and the cache line is modified, then the PCI DMA data byte(s) are written to the

L2-cache.

When a miss occurs, the write request is forwarded to main memory and the L2-cache is unaffected.

3.5 Level 2 Cache Operating Modes

3.5.1 Direct-Mapped Mode

Direct-Mapped Operation of the Tag and Data RAM Array

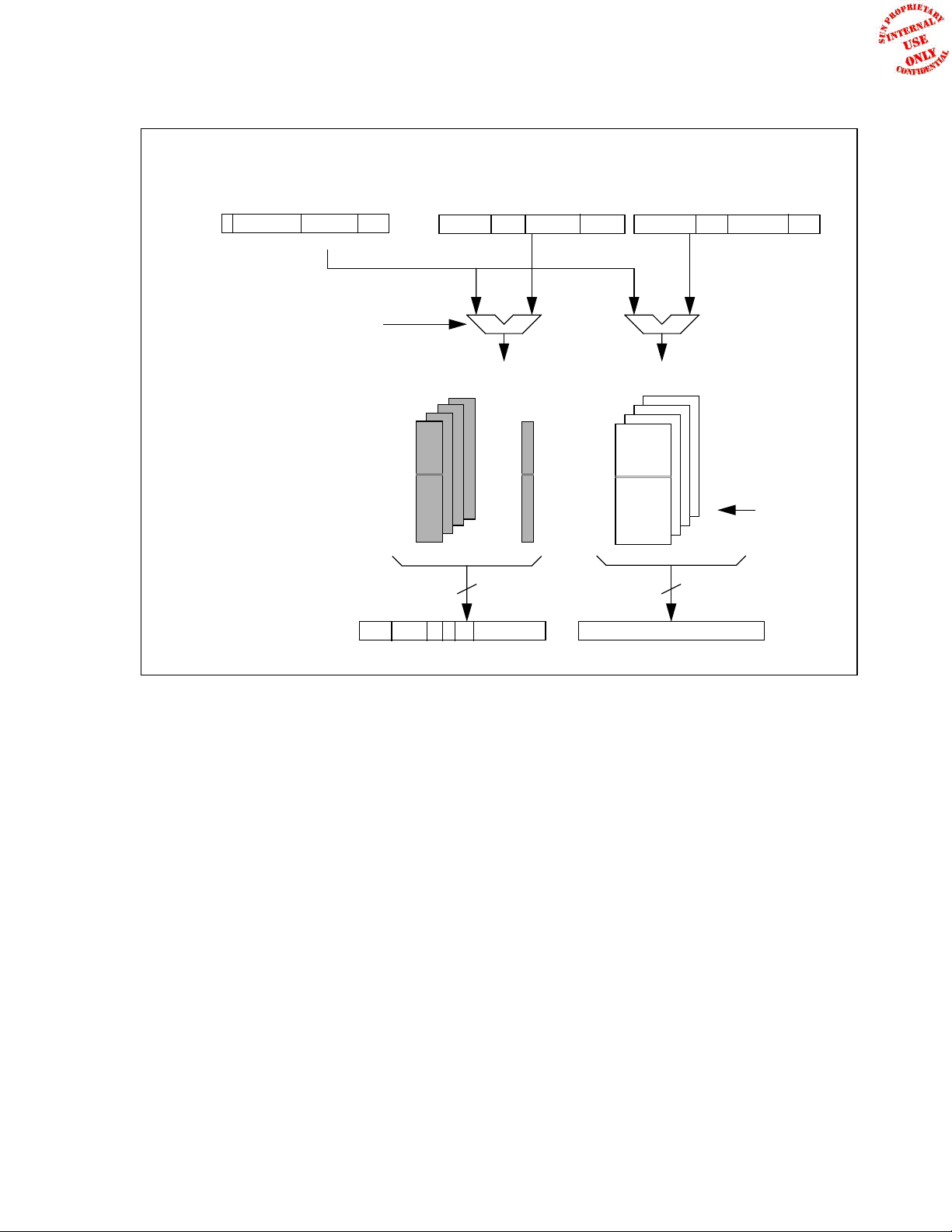

A simplified diagram for the direct-mapped cache mode is shown in FIGURE 3-4.

On a read or write hit, the cache line can be in one of four locations regardless of the cache mode. This

is because the cache line could be written to the cache when the cache was in 4-way mode.

Physical Address (from processor/MMU)

0

Page

13

Index

12

PA[17,16]

Byte

6

PA[17:6] tag_addr

Tag RAM Entry

Tag

0

M1V

Par

1

2

15

1

HIT: (Page == Tag) & V

FIGURE 3-4 Direct-Mapped Cache Mode

Direct-Mapped Cache Line Replacement Algorithm

The allocation of a new cache line for misses is determined by the cache mode. The direct-mapped

cache line replacement algorithm has only one location that it can use. This is defined by the PA[17:6]

offset address.

4096

Tag RAM

1

20-bit

Data RAM

4096

1

NOTE: This shows the

logical RAM layout.

Cache Lines

L2-cache_data

64-Byte Cache Line

512-bit

Data at this location must be displaced before writing the new cache line. This may involve writing the

old cache line to memory (if modified), or simply invalidated.

Chapter 3 • Level 2 Cache Subsystem − 27

Sun Proprietary/Confidential: Internal Use Only

Cache lines can also be systematically flushed out to memory under software control using a flush

displacement algorithm with the cache in direct-mapped mode. This is explained in the Section 3.7,

Level 2 Cache Flush Procedure - Programming Guide, on page 31.

3.5.2 4-Way Set-Associative Mode

4-Way Set-Associative Operation of the Tag RAM Array

In 4-way set-associative mode, the PA[15:6] physical address points to an offset in each of the 4 ways.

In parallel, the tag value in each of these line entries are compared to the PA[30:16] page address.

A hit to a way causes that way to be selected for the subsequent operation.

FIGURE 3-5 illustrates the 4-Way Set-Associative Operation of the Tag RAM Array.

Physical Address (from processor/MMU)

0

Page

15

Index

Byte

10

6

PA[15:6] tag_addr, rand_addr

Tag RAM

1024

Rand Field

1024

Tag RAM Entries (all 4 ways)

Tag

0

M1V

Par

2

1

15

1

HIT: (Page == Tag) & V

FIGURE 3-5 4-Way Set-Associative Cache Mode − Tag RAM Operation

1

20-bit

WAY Selection

for HIT

WAY Selection

for MISS

1

2-bit

4-Way Set-Associative Cache Line Replacement Algorithm

In the 4-way set-associative mode, the cache line can be stored in one of four places (for example, way

within the cache). The Rand value selects which way to replace when room for a new cache line is

needed.

Cache Lines

4-Way Set-Associative Operation of the Data RAM Array

FIGURE 3-6 illustrates the 4-Way set-associative operation of the Data RAM access.

28 − UltraSPARC IIe Processor User’s Manual

Sun Proprietary/Confidential: Internal Use Only

Level 2 CacheData RAM − 4-Way Set-Associative Cache Mode

Selection

Physical Address (from processor/MMU)

WAY

0

Page

15

FIGURE 3-6 4-Way Set-Associative Cache Mode − Data RAM Access

Index

Byte

10

6

PA[15:6] tag_addr

1024

1

512- bit

3.6 Level 2 Cache Control Bits

There are two separate mode bits to control the allocation algorithm of the L2-cache. One bit provides

the mode for I-cache/PDU requests. The other mode is for D-cache/LSU and PCI DMA memory

requests.

The two bits allow the instruction fetches to allocate in 4-way mode while the cache allocates in

direct-mapped mode for D-cache/LSU requests. This is often the case when the cache lines are being

flushed.

MUX

64-Byte Cache

Line

The mode bit fields are defined in Section 3.6.1, UPA Configuration Register, on page 29.

3.6.1 UPA Configuration Register

Compatibility Note – The UltraSPARC IIe processor does not include a UPA bus interface.

Previously unassigned bit fields in the UPA_Config Register have been assigned to control the L2-cache.

Other bit fields are no longer used.

FIGURE 3-7 illustrates the UPA_Config data field.

UPA_Config Data Field

00000000000000000000000000000

FIGURE 3-7 UPA_Config Data Field

The UPA_Config register fields are described in TABLE 3-2.

rr

dm_i

Read/write: ASI_UPA_CONFIG_REG (0x04A), VA = 0

dm_d

3639 353738

elim

pcon

33

mid

pcap

16

0172263 32 21

Chapter 3 • Level 2 Cache Subsystem − 29

Sun Proprietary/Confidential: Internal Use Only

TABLE 3-2 UPA_Config Register Data Fields

Field Bits Description POR Type Documentation Reference

Reserved 63:39 Reserved Unknown RZ

rr 38

dm_instruction 37

dm_data 36

elim 35:33

pcon 32:22

pcap 16:0

Normally set to 0 to enable the random line

replacement number for the Rand RAM

array. Set to 1 to hold the number generator

in its reset state.

Determines L2-cache line control mode for

instruction misses:

0: 4-way set-associative

1: Direct-mapped

Determines L2-cache line control mode for