1

Characteristics subject to change without notice

2033 8.1 10/04/01

SMD1102 / 1103 / 1113

SUMMIT

MICROELECTRONICS, Inc.

©SUMMIT MICROELECTRONICS, Inc., 2001 • 300 Orchard City Dr., Suite 131 • Campbell, CA 95008 • Phone 408-378-6461 • FAX 408-378-6586 • www.summitmicro.com

Preliminary

!!

!!

! Complete Data Acquisition System

""

""

" 10-Bit A/D Converter Resolution

""

""

" 75µs Acquisition plus Conversion Time

""

""

" Alarm Limits for Each Input Channel

""

""

" Auto-Increment of Input Channels

""

""

" Two Wire I2C Serial Data Interface

""

""

" System Management Bus (SMBus) Compat-

ible

""

""

" Auto-Monitor with SMB

ALERT

Output

""

""

" Low Quiescent Current of 50µA

""

""

" Wide Supply Voltage Range: 2.7V to 5.5V

10-Bit Data Acquisition System for

Autonomous Environmental Monitoring

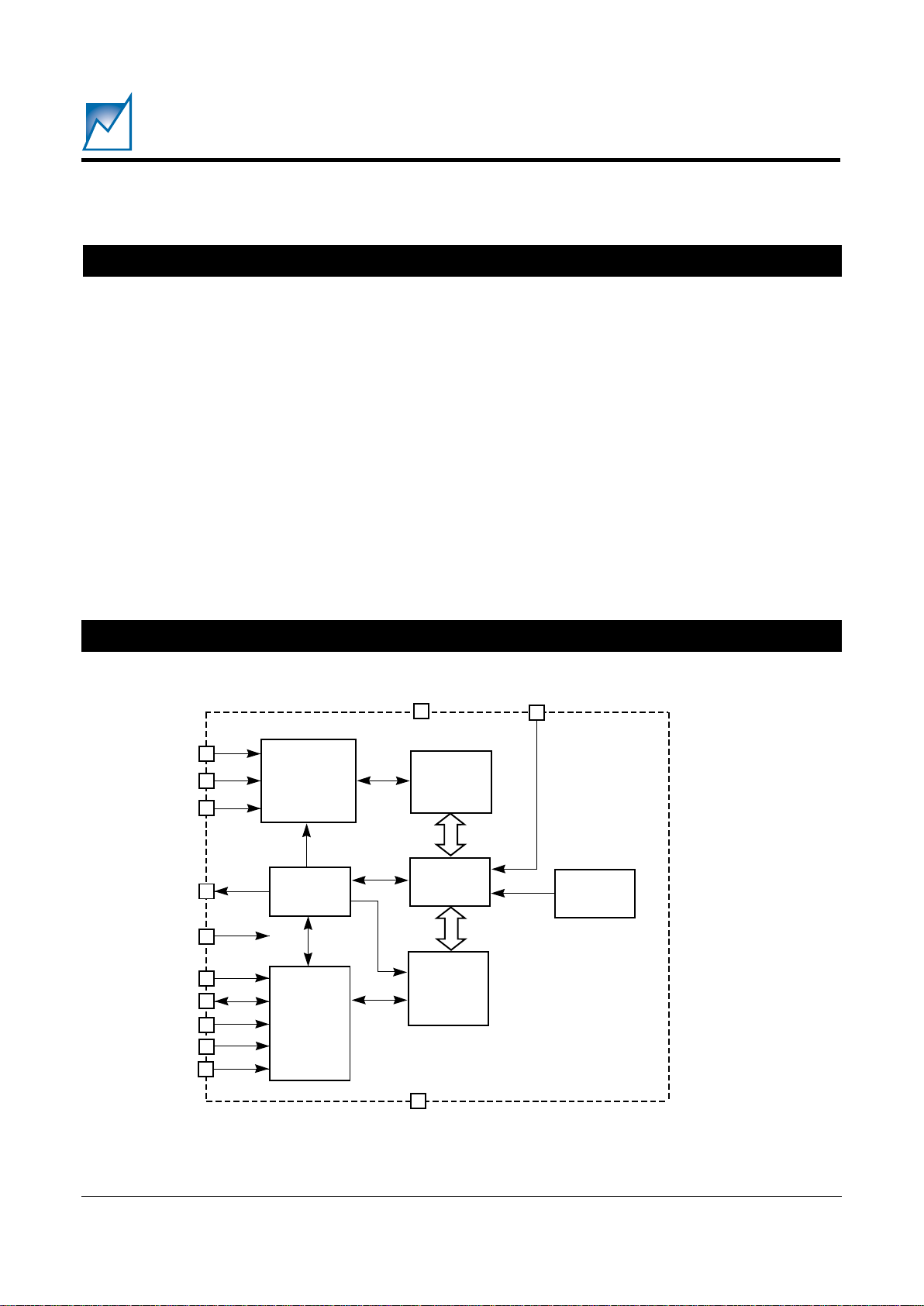

FUNCTIONAL BLOCK DIAGRAM

FEATURES

!!

!!

! SMD1102

""

""

" 2-Channel Analog Input

""

""

" External Voltage Reference Input Provided for

Absolute Measurements

!!

!!

! SMD1103

""

""

" 3-Channel Analog Input

""

""

" Reference Voltage Input for the A/D Converter

is Connected to V

DD

for Ratiometric Measure-

ments

!!

!!

! SMD1113

""

""

" Extended I

2

C Operation

""

""

" 3-Channel Analog Input

""

""

" External Voltage Reference Input Provided

for Absolute Measurements

GND

V

DD

CONVERTER

CLOCK

SCL

SDA

2033 BD 7.0

CONTROL

LOGIC

2-WIRE

SERIAL

INTERFACE

ANALOG

MULTIPLEXER

10-BIT A/D

CONVERTER

E2PROM

ALARM LIMIT

REGISTERS

SAMPLE

AND

HOLD

SMB

ALERT

#

AIN2

X

AIN1

AIN0

(1103,

1113)

REF

IN

(1102,

1113)

X

CE#

A2

A1

A0

(1113)

(1113)

(1113)

(1113)

Note: See Pin

Configuration

drawings for

pinouts

2

SMD1102 / 1103 / 1113

2033 8.1 10/04/01

SUMMIT MICROELECTRONICS, Inc.

PIN CONFIGURATION

The SMD1102, SMD1103 and SMD1113 each contain a

10-Bit data acquisition system (DAS) with dedicated EEPROM alarm limit storage. The three devices communicate with the host µP via a standard two-wire I2C serial

interface. After initialization the SMD1102/1103/1113 can

INTRODUCTION

PIN NAMES

automatically monitor one or more analog input channels.

If any input signal moves beyond its user-programmed

limits the host is notified by the SMB

ALERT

# output, enabling

fault prediction in telecom line card applications, as an

example.

1102

A

IN

0, AIN1 Analog channel inputs

GND Power supply return

REF

IN

Reference input

SCL Serial Clock

SDA Serial Data

SMB

ALERT

# Interrupt output

V

DD

Power Supply

1103

AIN0, AIN1, AIN2 Analog channel inputs

GND Power supply return

SCL Serial Clock

SDA Serial Data

SMB

ALERT

# Interrupt output

V

DD

Power Supply

1113

CE# Chip Enable

A2, A1, A0 I2C Address select inputs

AIN0, AIN1, AIN2 Analog channel inputs

GND Power supply return

REF

IN

Reference input

SCL Serial Clock

SDA Serial Data

SMB

ALERT

# Interrupt output

V

DD

Power Supply

A0

A1

A2

AIN2

AIN1

A

IN

0

GND

V

DD

CE#

REF

IN

NC

SMB

ALERT

#

SCL

SDA

1

2

3

4

5

6

7

14

13

12

11

10

9

8

2033 14 PCon

14-Pin SOIC

SMD1113

2033 8 PCon-2

REF

IN

AIN1

A

IN

0

GND

V

DD

SMB

ALERT

#

SCL

SDA

1

2

3

4

8

7

6

5

8-Pin PDIP

or 8-Pin SOIC

SMD1102

AIN2

AIN1

AIN0

GND

V

DD

SMB

ALERT

#

SCL

SDA

1

2

3

4

8

7

6

5

8-Pin PDIP

or 8-Pin SOIC

SMD1103

2033 8 PCon-3

3

2033 8.1 10/04/01

SMD1102 / 1103 / 1113

SUMMIT MICROELECTRONICS, Inc.

*COMMENT

Stresses listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions

outside those listed in the operational sections of this specification is not

implied. Exposure to any absolute maximum rating for extended

periods may affect device performance and reliability.

Temperature Under Bias ...................... –55°C to 125°C

Storage Temperature ........................... –65°C to 150°C

Lead Solder Temperature (10 seconds) ............. 300 °C

Terminal Voltage with Respect to GND:

All......................................... –2V to 7V

DC OPERATING CHARACTERISTICS

ABSOLUTE MAXIMUM RATINGS*

(Over Recommended Operating Conditions; Voltages are relative to GND)

2033 Elect Table

RECOMMENDED OPERATING CONDITIONS

Temperature –40ºC to 85ºC.

Voltage 2.7V to 5.5V

lobmySretemaraPsnoitidnoC )1etoN( .niM.pyT.xaMstinU

V

CC

egatloVylppuS7.25.5V

I

CC

tnerruCylppuSnepostuptuollA3Am

I

BS

tnerruCybdnatS

,eldiCDA,nepostuptuollA

ssecorpnietirwyromemon

05Aµ

I

IL

tnerrucegakaeltupnIV

NI

VotV0=

CC

2Aµ

I

OL

tuOtnerrucegakaeltupV

TUO

VotV0=

CC

01Aµ

V

LO

egatlovwoltuptuO

V

CC

I,V5=

LO

Am1.2=4.0

V

V

CC

I,V5.4<

LO

Am1=2.0

V

HO

egatlovhgihtuptuO

V

CC

I,V5=

LO

Aµ004–= 4.2

V

V

CC

I,V5.4<

LO

Aµ001–=V

CC

2.0–

V

LI

egatlovwoltupnI1.0– 3.0 × V

CC

V

V

HI

egatlovhgihtupnI7.0 × V

CC

V

CC

7.0+V

stupnIgolanA

V

NIFER

V

FER

egatlovtupni1V

CC

V

V

NI

AnoegatlovtupnI

NI

0

Ahguorht

NI

2

05.5V

4

SMD1102 / 1103 / 1113

2033 8.1 10/04/01

SUMMIT MICROELECTRONICS, Inc.

PIN DESCRIPTIONS

Serial Clock (SCL)

The SCL input is used to clock data into and out of the

device. In the WRITE mode data must remain stable while

SCL is HIGH. In the READ mode data is clocked out on

the falling edge of SCL.

Serial Data (SDA)

The SDA pin is a bidirectional pin used to transfer data into

and out of the device. Data may change only when SCL

is LOW, except during START and STOP conditions. It is

an open-drain output and may be wire-ORed with any

number of open-drain or open-collector outputs.

SMB

ALERT

#

This interrupt output pin signals the host when an out-oflimit condition is detected by one of the EEPROM limit

registers. The SMB

ALERT

open-drain output is active low.

REF

IN

Voltage reference input for 10-Bit A/D converter. This

signal is only on the SMD1102 and SMD1113.

A

IN

0, AIN1, AIN2

Multiplexer input pins for channels 0, 1, and 2, respectively. AIN2 is only available on the SMD1103 and

SMD1113. These pins may be left unconnected if they are

not used. However, the Alert Regions must be set

accordingly (see the section "Alert Conditions").

A0, A1, A2

The address inputs are only available on the SMD1113.

Multiple SMD1113s can be used on a single bus by setting

different device addresses. A2 has a 50kΩ pull-up

resistor, and A1 and A0 have 50kΩ pull-down resistors.

Do not set the address to all zeroes because it would

cause a conflict with the SMB Alert Response.

CE#

Chip Enable/disable input must be held low to enable I

2

C

communications. It has a 50kΩ pull-down resistor and is

only available on the SMD1113.

V

DD

Power supply input.

GND

Power supply return.

5

2033 8.1 10/04/01

SMD1102 / 1103 / 1113

SUMMIT MICROELECTRONICS, Inc.

DEVICE OPERATION

The SMD1102, SMD1103 and SMD1113 Data Acquisition

Systems (DAS) are each comprised of: an analog input

multiplexer, sample-and-hold circuit, 10-Bit successive

approximation Analog-to-Digital (A/D) Converter, and

nonvolatile EEPROM memory to store upper and lower

alarm-limits for each input channel. The user programs

the alarm limits via the industry-standard I2C interface. An

SMB

ALERT

# interrupt output signals if any of the analog

inputs move outside these limits.

DAS Modes of Operation

The SMD1102/1103/1113 have four user-selectable

modes of operation. These modes are: a single conversion of one channel, successive conversions on the same

channel, sequential conversions on all three channels, or

autonomous conversions of the same or all channels.

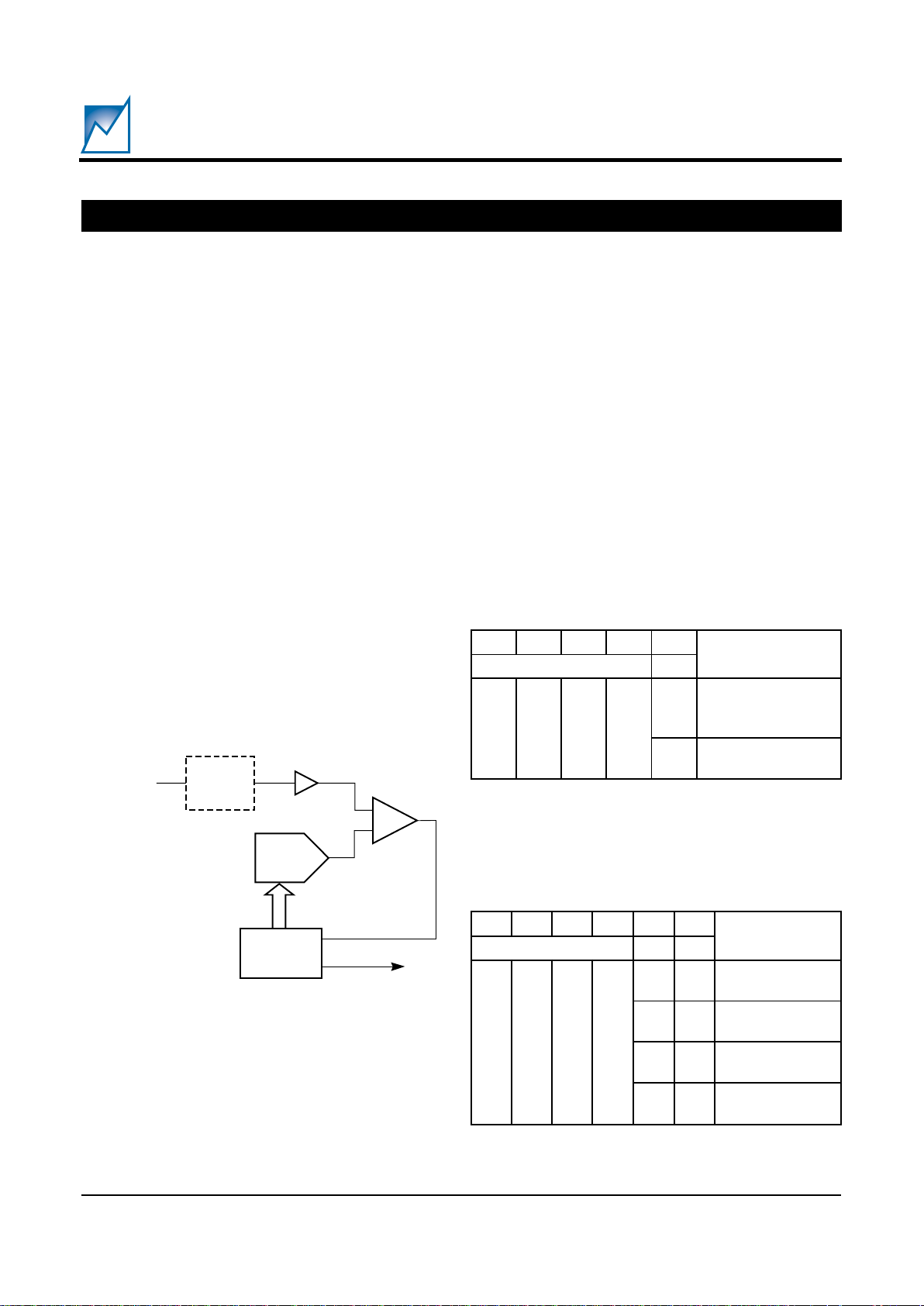

Sample-and-Hold Operation

The channel switching and sampling architecture of the A/

D’s comparator is illustrated in the equivalent input circuit

diagram in Figure 1. During acquisition the selected

channel charges a capacitor in the sample-and-hold circuit. The acquisition interval spans the Acknowledge

period following the command byte and ends on the rising

edge of the next clock. At the end of the acquisition phase

the analog input is disconnected, retaining charge on the

hold capacitor as a sample of the signal.

Figure 1. Sample/Hold and SAR

+

–

2033 Fig01 2.0

Analog In

Buffer

DAC

SAR

Sample

& Hold

SDA

The next bit in the addressing sequence is the EEPROM/

Conversion (E/C) bit; when set to zero the device is

instructed to perform an A/D conversion, and when set to

logic one the EEPROM limit register will be addressed.

See Table 1A.

The next two bits are the channel select bits. Autoincrement is enabled if the channel select bits are set to

11

BIN

and the conversion bit is set to zero. In the autoincrement mode conversions are performed on successive channels, starting with channel 0. After channel 2 is

converted (channel 1 on the SMD1102) the address will

wrap around to channel 0. See Table 1B.

The last bit is the Read/Monitor bit. When the bit is set

to logic one, data can be read from a conversion or from

one of the EEPROM limit registers, depending on the state

of the EEPROM/Conversion bit. When the bit is logic zero

either the auto-monitor mode is entered or the EEPROM

limit register is programmed, again depending on the state

of the EEPROM/Conversion bit. See Table 1C.

Addressing and Command Sequence

All operations of the DAS are preceded first by the start

condition and then by the addressing command sequence. For the SMD1102 & SMD1103 this is 1001

BIN.

For

the SMD1113 it is the binary values of A2, A1, A0, and a

one — a four bit number.

Table 1A. Address Byte — EEPROM/Conversion

7BD6BD5BD4BD3BD

noitcnuF

reifitnedIepyTeciveDC/E

2A

ro

*1

1A

ro

*0

0A

ro

*0

1

0

-nocD/AmrofreP

detcelesnonoisrev

)s(lennahc

1

MORPEEsserddA

retsigertimil

2033 Table01A

* Denotes SMD 1102 & SMD1103. Ax bits are for the SMD1113.

Table 1B. Address Byte — Channel Select

2033 Table01B

* Denotes SMD 1102 & SMD1103. Ax bits are for the SMD1113.

7BD6BD5BD4BD2BD1BD

noitcnuF

reifitnedIepyTeciveD1HC0HC

2A

ro

*1

1A

ro

*0

0A

ro

*0

1

00

0lennahC

detceles

01

1lennahC

detceles

10

2lennahC

detceles

11

fitnemercni-otuA

0=C/E