Page 1

RXQB

RXQA

RXIB

RXIA

IDATA

QDATA

DCLK

TESTOUT

DCDC_PA

WPAVDC

VLOOP

RTEMP

WRFLOOP

BTCLKREQ

BTRX

BTCTS

VBATI

DCDC_PA

WPAVDC

Pages 10-15

Pages 10-15

VBATI

VDIG

VDDE18

VMSPICO

VBACKUP

DCDC_PA

WPAVDC

VLOOP

RTEMP

WRFLOOP

BTCLKREQ

BTRX

BTCTS

MEMRESn

VAD

FLASH_STROBE

SPL

SPR

MIDREF

ANT

SW3_1V8

WSTR_15

Operation & Services

Operation & Services

MPX1_OFF

VGA_OFF

KBDIM

NAVDIM

AMPCTRL

ICN/AUXinR

M

MICP/AUXinL

I2CDAT1

I2CCLK1

BTRTS

WPABIAS

VCXOCONT

VBUS

DCIO_ON

VBT_EN

CAM_27_EN

SERVICEn

ANTSW3

WSTR

Pages 16-18

Pages 16-18

WSTR_15

VDIG

VDDE18

RXQB

VCAM12

VCAM18

MPX1_OFF

VGA_OFF

KBDIM

NAVDIM

I2CDAT1

I2CCLK1

BTTX

VPP

DCIO

VBATI

VDIG

VCAM27

VCAM12

VCAM18

VDDE18

MPX1_OFF

VGA_OFF

KBDIM

M

NAVDI

AMPCTRL

MICN/AUXinR

MICP/AUXinL

I2CDAT1

I2CCLK1

CAMSYSCLK

DCIOint

MMI

MMI

ANTSW3_1V8

Pages 19-23

Pages 19-23

FLASH_STROBE

ANTSW3

WSTR

WSTR_15

PCMDATA

PCMDATB

PCMSYN

PCM

MIDREF

ONSWA

CLK

VAD

SPL

SPR

RXQA

RXIB

RXIA

IDATA

QDATA

DCLK

TESTOUT

UMTS Access

UMTS Access

WDAT

WCLK

TXQB

TXQA

RADST

RADDAT

RADCLK

TXON

MODA

MODB

MODC

MODD

ANTSW0

ANTSW1

ANTSW2

ANTSW3_1V8

TXIA

TXIB

R

VccAVccB

VAPC

WSTR

WDAT

WCLK

RADSTR

RADDAT

RADCLK

MODA

MODB

MODC

MODD

ANTSW0

ANTSW1

ANTSW2

ANTSW3

PCMDATA

PCMDATB

PCMSYN

PCMCLK

BTRTS

WPABIAS

VCXOCONT

VBATI

VRTC13

VBT27

VDDE18

TXQB

TXQA

TXON

BTTX

VDIG

VAPC

VccA

VccB

TXIA

TXIB

CLKREQ

MCLK

VDDE18

VCORE15

CLKREQ

MCLK

SERVICEn

ONSWAn

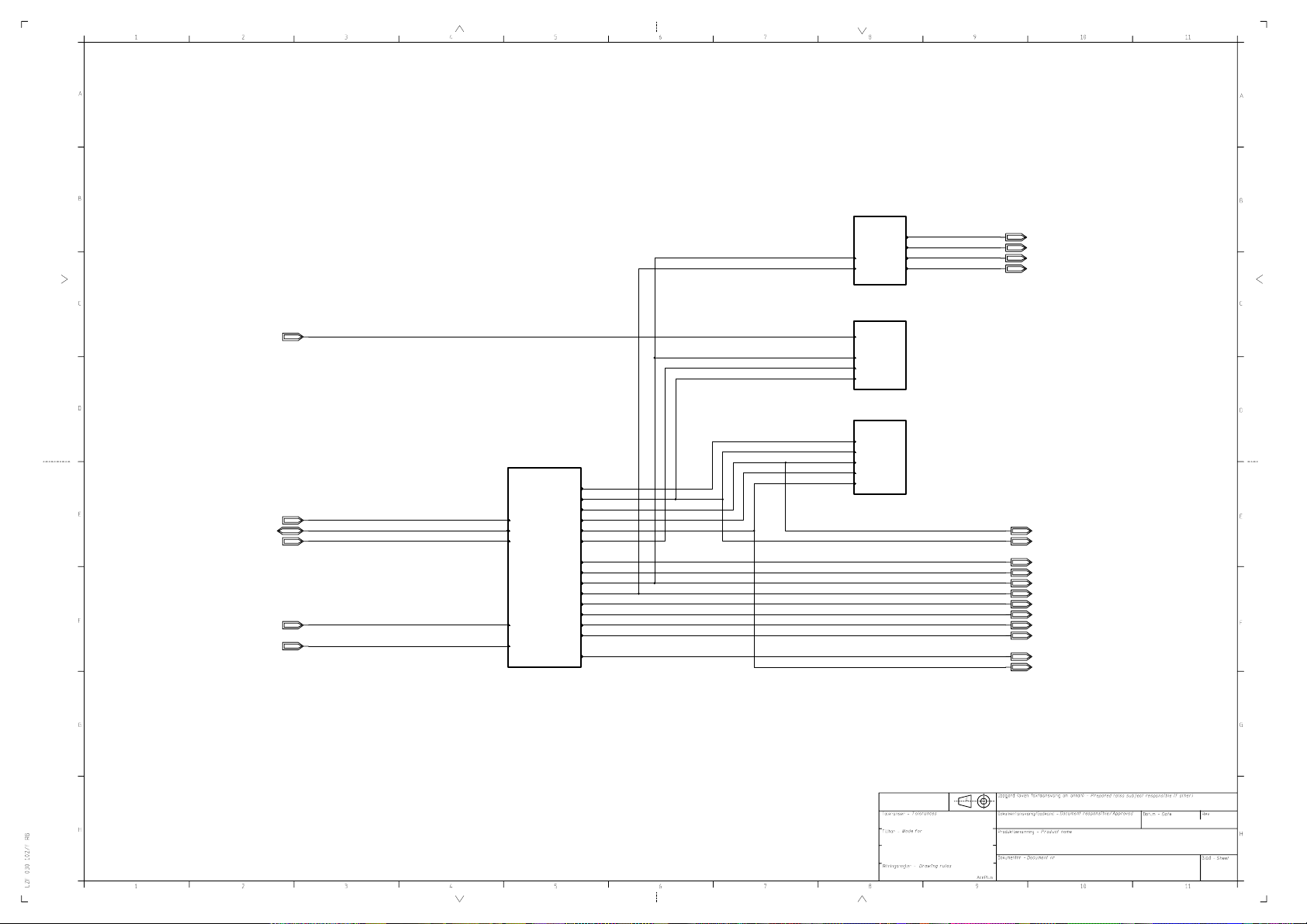

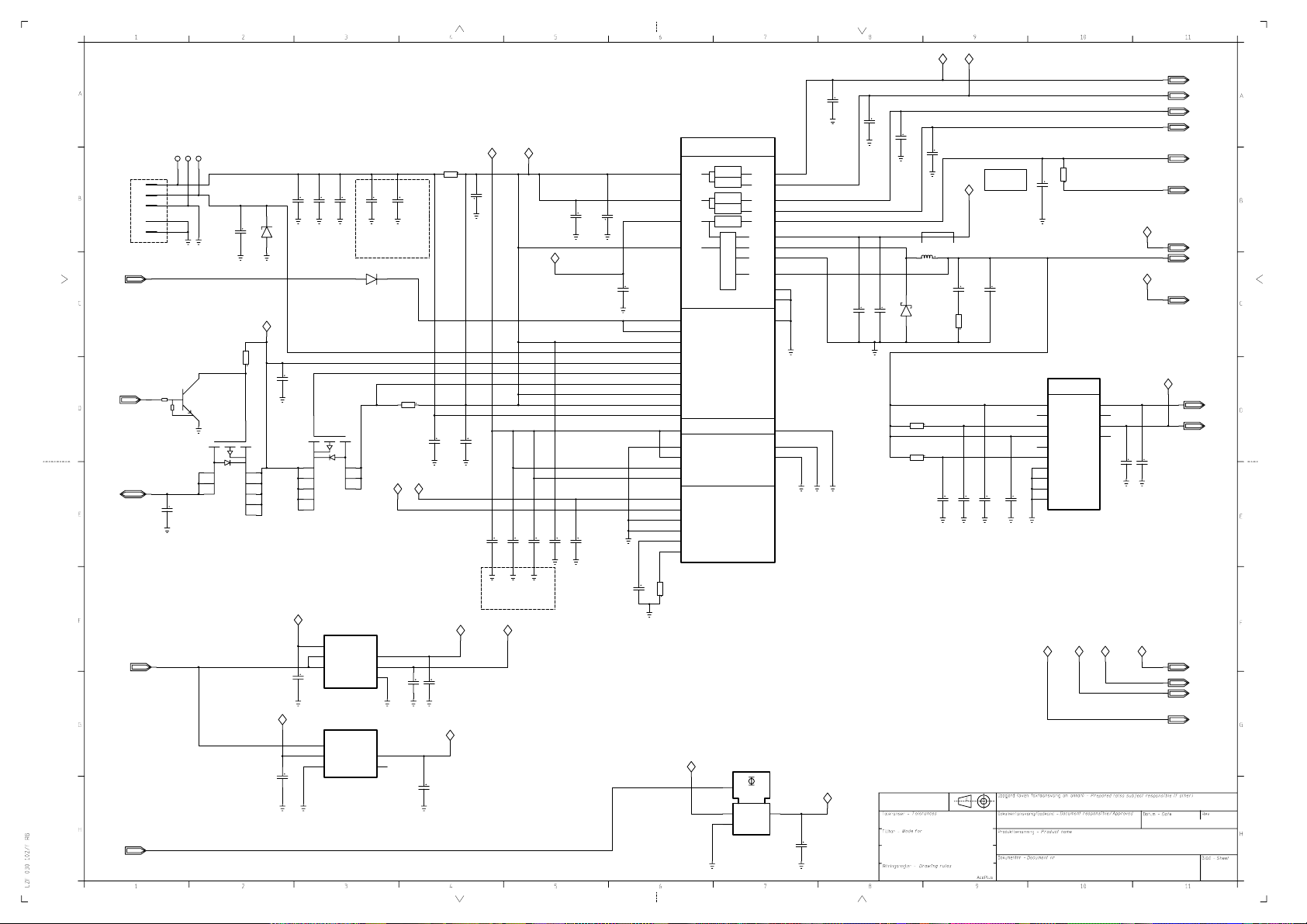

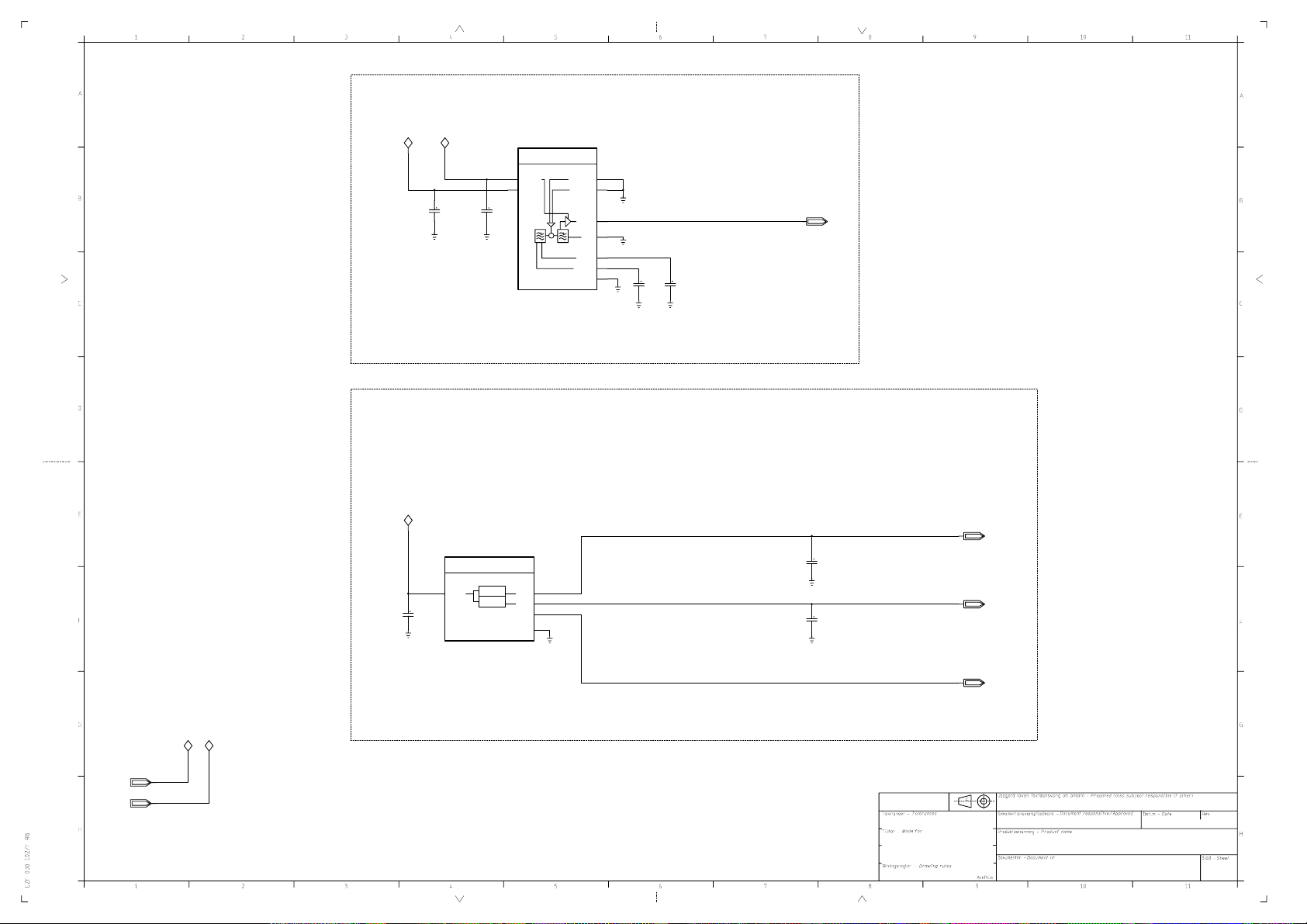

System Control

System Control

Pag

Pag

es 2-4

es 2-4

MEMRESn

BTRESn

RTCCLK

CAMSYSCLK

Pages 5-9

Pages 5-9

VPP

VBUS

DCIO

DCIO_ON

VBT_EN

CAM_27_EN

Power

Power

VBATI

VBT27

VDDE18

VBACKUP

VCAM27

VCAM12

VCAM18

VMSPICO

DCIOint

VRTC13

VCORE15

XTLDO

VAPC

BTRESn

VCAM12

VDIG

VccA

VccB

VccB

XTLDO

VAPC

Confidential

Approved according to 00021-LXE 107 42/1

Sony Ericsson

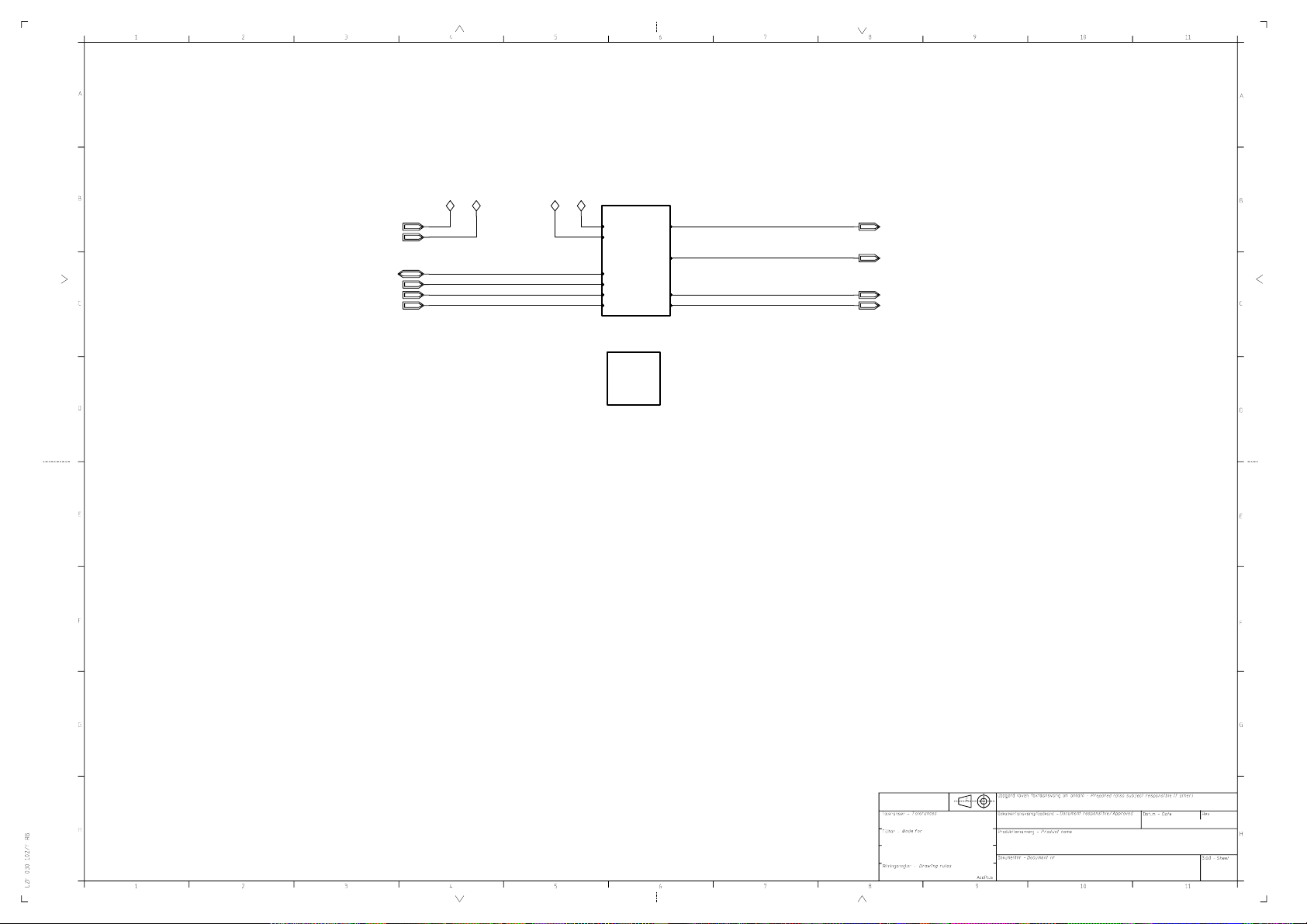

BASEBAND

Logic Top

SEMCJ/ Kensuke Katsuta

SEMCJ/ Ken Ikuno

Ai Main Board

VccA

VCAM18

2/1911-ROA 128 2071/2

RTCCLK

XTLDO

VAPC

DIAGRAMSCHEMA

2006/12/14

E

01 of 23

Page 2

VDDE18

VCORE15

CLKREQ

MCLK

SERVICEn

ONSWAn

VDDE18 VCORE15 VDDE18VCORE15

CLKREQ

MCLK

SERVICEn

ONSWAn

VDDE18

RE15

VCO

CLKREQ

MCLK

CEn

SERVI

ONSWAn

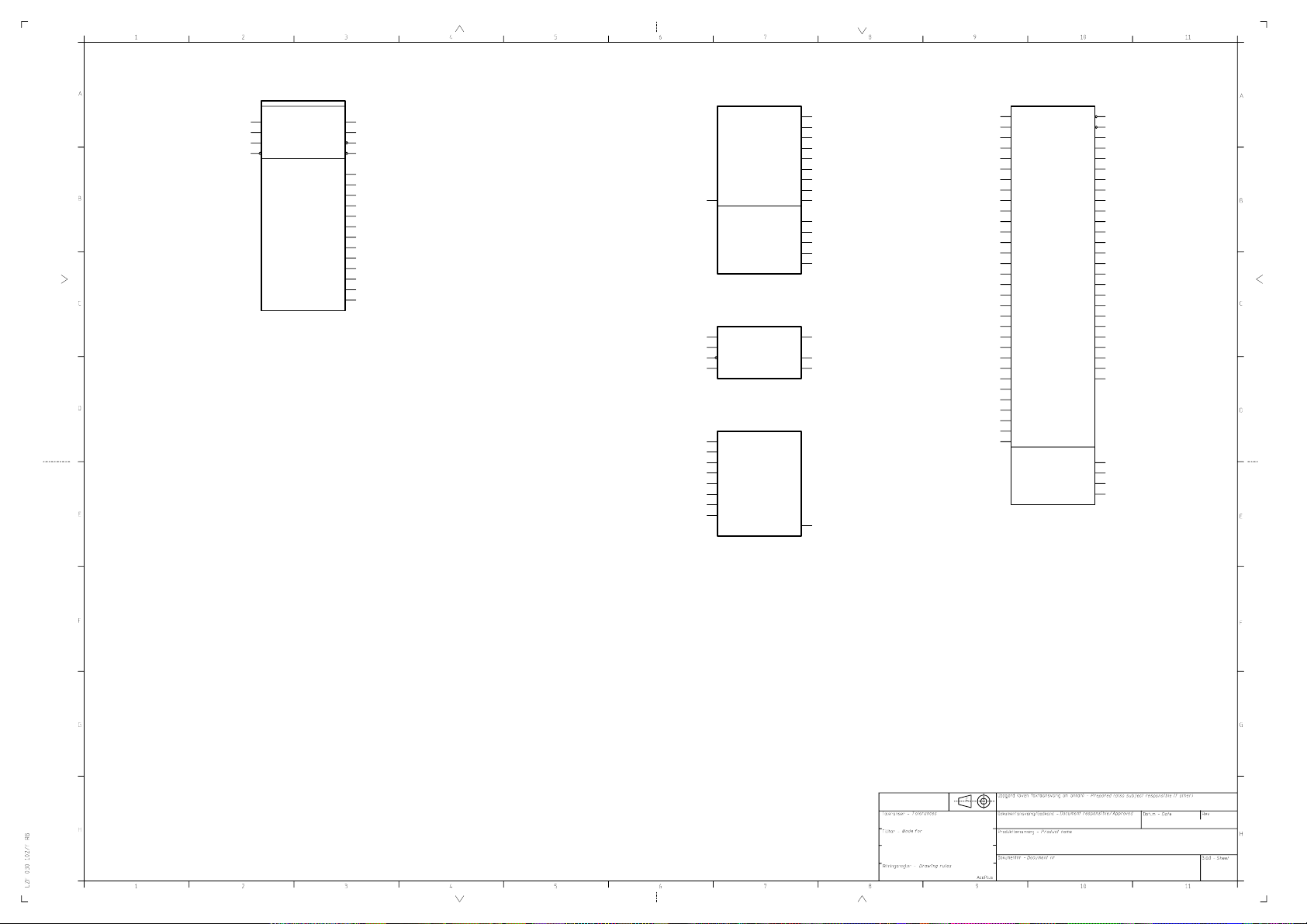

Clocks & Resets

Clocks & Resets

Page 4

Page 4

TestTest

Page 3

Page 3

CAMSYSCLK

RTCCLK

MEMRESn

BTRESn

RTCCLK

CAMSYSCLK

MEMRESn

BTRESn

RTCCLK

CAMSYSCLK

MEMRESn

BTRESn

Confidential

Approved according to 00021-LXE 107 42/1

Sony Ericsson

BASEBAND

System Control

Top

SEMCJ/ Zhang Zongyao

SEMCJ/ Ken Ikuno

Ai Main Board

2/1911-ROA 128 2071/2

DIAGRAMSCHEMA

2006/12/14

E

02 of 23

Page 3

RTCCLK_1

SERVICEn

CLKREQ

ONSWAn

MCLK

Actual net on system

connector page...

R2102

100ohms

B2100

RTM501911/2

R1A

C2C1

C2102

22p

C2104 & C2106 mounted close to D2000

C2104

1nF

C2100

1nF

C2106

NM

10pF

SERVICEn

CLKREQ_1

ONSWAn ONSWAn

VDDE18

32768k

F

Connect to ground pla ne in one single point

D2000

RTC

RTCIN

V3

RTCBDIS_N

W3

RESPOW_N RESOUT0_N

T8

MCLK_M SYSCLK0

E15

IRQ0_N

D15

RQ1_N

I

C16

SERVICE_N

AA6

CLKREQ

DB2030

ROP1013112/1

Resets

Clocks

Control

R1A

RTCOUT

RTCCLK

RTCDCON

RESOUT1_N

RESOUT2_N

SYSCLK1

SYSCLK2

RREQ0_N

PW

PWRREQ1

(REQ3234U)

27pF

C2103

E16

D16

AB6

AC6

AC5

AB5

Use for

dumping resister

47ohm

T2V2

W4

Y4

Y6

Y7

VCORE15

R2101

100Kohms

R2100

0oh

C2101

1nF

ms

R2105

10Kohms

R2104

47ohms

R2104 mounted

close to D2000

RTCCLK

MEMRESn

BTRESn

CAMSYSCLK

PWR_IRQ

PWRRST

MCLK_WANDA

RTCDCON

PWRREQn

CLKREQ_1

MCLK

RTCCLK_1

D2000

V21

CLK32

U9

MCLK_W

U3

HCLK

DB2030

ROP1013112/1

N2000

ERICSSON AB 2010

SYSTEM CONTROL

POWER ON/RESET

C4

ONSWA

C5

ONSWB

A7

ONSWC

C10

SLEEP

K3

CLKREQ

K9

MCLK

M1

XTAL1

ERICSSON_AB2012

ROP1013066/6

CONTROL

RTCCLK

MEMRESn

BTRESn

CAMSYSCLK

B8

RRST

PW

C1

IRQ

R1A

VDDE18

VCORE15

VDDE18 VCORE15

Confidential

Approved according to 00021-LXE 107 42/1

Sony Ericsson

BASEBAND

System Control

Clocks & Resets

SEMCJ/ Zhang Zongyao

SEMCJ/ Ken Ikuno

Ai Main Board

2/1911-ROA 128 2071/2

DIAGRAMSCHEMA

2006/12/14

E

03 of 23

Page 4

AB7

AA7

AA8

D2000

TDI_M

TMS_M

TCK_M

TRST_N_M

DB2030

ROP1013112/1

JTAG_IF

ETM_IF

TDO_M

RTCK_M

TEMU0_N_M

TEMU1_N_M

ETMPSTAT0

ETMPSTAT1

ETMPSTAT2

ETMSYNC

ETMCLK

ETMPKT0

ETMPKT1

ETMPKT2

ETMPKT3

ETMPKT4

ETMPKT5

ETMPKT6

ETMPKT7

D2000

Y8AC7

AB8

AD8

Y9

AB11

AC10

Y12

AA12

AB12

AC12

AA13

AB13

AC13

Y14

AA14

AB14

AC14

UART_RX

DSPINTERRUPT

DB2030

ROP1013112/1

D2000

TDI_W

M20

TMS_W

P21

TRST_N_W

N20 H20

TC

K_W

DB2030

ROP1013112/1

D2000

U12

BOOTMODE0

R11

BOOTMODE1

U15

BOOTMODE2

F20

BOOTMODE3

AD23

TESTMODE

T14

ANALOG_ENABLE

T15

APLL_BYPASS

T16

CS_BYPASS

DB2030

ROP1013112/1

GPO0

GPO1

GPO2

GP

GPO4

GPO5

GPO6

GPO7

UART_TX

CPU_IACK

CPU_XF

CPU_IRQ1

CPU_IRQ0

CPU_CLKOUT

TDO_W

EMU0_W

EM

U1_W

APLL_ATEST1

T10

U4

P12

R12

O3

T12

P11

U14

T13

E22D22

N10

P9

H4

H3

T11

K20L20

G20

N9

D2000

J16

H16

K15

J15

M14

L14

K14

J14

H14

M13

L13

K13

J13

M12

L12

K12

J12

H12

M11

L11

K11

J11

N12

M10

L10

K10

J10

H10

N11

L9

K9

J9

DB2030

ROP1013112/1

EMIF_D0

EMIF_D1

EMIF_D2

EMIF_D3

EMIF_D4

EMIF_D5

EM

IF_D6

EMIF_D7

EMIF_D8

EMIF_D9

EMIF_D10

EMIF_D11

EMIF_D12

EMIF_D13

EMIF_D14

EMIF_D15

EMIF_D16

EMIF_D17

EMIF_D18

EMIF_D19

EMIF_D20

EMIF_D21

EMIF_D22

EMIF_D23

EMIF_D24

EM

IF_D25

EMIF_D26

EMIF_D27

EMIF_D28

EM

IF_D29

EMIF_D30

EMIF_D31

EMIF_AWE

EMIF_ARE

EMIF_ARE_ADY

EMIF_A1

EMIF_A2

EMIF_A3

EMIF_A4

EMIF_A5

EMIF_A6

EMIF_A7

EMIF_A8

EMIF_A9

EMIF_A10

EMIF_A11

EMIF_A12

EMIF_A13

EMIF_A14

EMIF_A15

EMIF_A16

EMIF_A17

EMIF_A18

EMIF_A19

EMIF_A20

EMIF_A21

EMIF_A22

EMIF_A23

EXT_MEM_UBUS10

EXT_MEM_UBUS11

EXT_MEM_UBUS12

EXT_FRZME_STOROBE

T4

M9

K8

R16

R15

R14

R13

R17

P16

P15

P14

P13

N17

N16

N15

N14

N13

M16

M15

L17

L16

L15

A23

K17

B24

K16

P10

R10

R9

J20

Confidential

Approved according to 00021-LXE 107 42/1

Sony Ericsson

BASEBAND

System Control

Test

SEMCJ/ Zhang Zongyao

SEMCJ/ Ken Ikuno

Ai Main Board

2/1911-ROA 128 2071/2

DIAGRAMSCHEMA

2006/12/14

E

04 of 23

Page 5

VBUS

DCIO

DCIO_ON

CAM_27_EN

VBT_EN

Page 7

Page 7

VAPC

XTLDO

VccA

VBATI

VccB

VDIG

RF Power

RF Power

Page 9

VPP

VPP VPP

Page 6

Page 6

VDDF13

VDDE18

VBUS

DCIO

DCIO_ON

CAM_27_EN

VBT_EN

VBUS

DCIO

DCIO_ON

CAM_27_EN

VBT

Regulators & Char ging

Regulators & Char ging

VRTC13

VCORE13

VCORE15

VCORE18

VBT27

VBACKUP

VBATI

VDIG

VCAM27

VCAM12

VCAM18

VMSPICO

_EN

DCIOint

VBATI

VCORE18

VDDE18

VDDF13

VDDE18

VRTC13

VCORE13

VCORE15

VDDE18

VBT27

VBACKUP

VBATI

VDIG

VCAM27

VCAM12

VCAM18

VMSPICO

DCIOint

VPP

VBATI

VCORE18

VDDE18

Memories

Memories

VDDF13

VDDE18

VRTC13

VCORE13

VCORE15

Power Asics

Power Asics

Page 9

Page 8

Page 8

VAPC

XT

LDO

VccA

VccB

VAPC

XTLDO

VccA

VccB

VDDE18

VBT27

VBACKUP

VBATI

VDIG

VMSPICO

DCIOint

VCORE15

VRTC13

VCAM27

VCAM12

VCAM18

Confidential

Approved according to 00021-LXE 107 42/1

Sony Ericsson

BASEBAND

Power

Top

SEMCJ/ Kensuke katsuta

SEMCJ/ Ken Ikuno

Ai Main Board

2/1911-ROA 128 2071/2

DIAGRAMSCHEMA

2006/12/14

E

05 of 23

Page 6

NC

NC

Ch

arge sense lines, pin D2 and D3 on

N2000, should be routed together and

connected directly to pads for R2201

(no current conducting via allowed

between connection point and pad).

NM

C2236

1uF

(REQ3312U)

FG sense lines, pin F11 and F12 on N2000,

should be routed together and connected

directly to pads for R2200 (no

current conducting via allowed between

connection point and pad).

C2289

C2284

C2283

1uF

10nF

1uF

(REQ3312U)

Mount C2211 and C2212

close to battery connector

This components MUST BE fit

into RF layout side.

(REQ3317U)

Place C2206 and C2207

close to N2000

C2286

NM

1uF

NM

C2237

100nF

10uF

NM

C2201

C2200

10uF

Local ground plane

Connect local gro und plane to

main ground plane in one poi nt only

L2201

12

(REQ3254U)

C2218 close

to N2000

REG70618/18

BLM15EG121SN1

1Ghz

NC2

HEAT1

HEAT2

(REQ3200U)

VROUT1

VROUT2

NC3

NC4

Should be separated

from surface GND

N2000 reference.

Mount close to N2000

BASEBAND

Power

Regulators & Charging

06 of 23

Page 7

PA Control

VBATI

VDIG

C1100

10nF

Power Supply

VBATI

N2000

C1103

10uF

ERICSSON_AB2012

ROP1013066/6

C1108

100nF

GND

ERICSSON AB 2010

POWER

RADIO

LDO_A

LDO_B

N2000

C12

VDDBUF

G12

VDDPA

ERICSSON_AB2012

ROP1013066/6

VDDAVBATA

VDDB

EXTLDO

VSSA

ERICSSON AB 2010

UM

TS ACCESS

PA CONTROL

B12A12

A11

C11

H10

PASENSE+

PASENSE-

PAREG

FF_IN

EXPOUT

VSSPA

E12

E11

D11

D12

IOUT

F10

G10

E10

C1101

470pF

C1102

470pF

VAPC

C1106

C1107

4.7uF

VccA

4.7uF

VccB

VBATI

VDIG

VBATI VDIG

XTLDO

Confidential

Approved according to 00021-LXE 107 42/1

Sony Ericsson

BASEBAND

Power

RF

SEMCJ/ Kensuke katsuta

SEMCJ/ Ken Ikuno

Ai Main Board

2/1911-ROA 128 2071/2

DIAGRAMSCHEMA

2006/12/14

E

07 of 23

Page 8

VCORE13

VDDF13

VRTC13

VCORE15

VDDE18

VCORE15

VRTC13VDDF13

VDDE18

VDDF13

VRTC13

VCORE13

VCORE15

C2233

C2231

C2229

C2227100nF

100nF

100nF

100nF

C2226100nF

C2232

C2228

100nF

100nF

VDDE18 VDDF13 VRTC13 VCORE13VCORE15

C2234

100nF

C2235

100nF

C2239

100nF

C2240

100nF

C2241

100nF

A13

B9

J1

L1

AD4

AD7

V24

R24

M24

AD9

AB23

W24

AD5

AC9

A9

E1

F1

A12

A10

A16

A14

R23

K24

V1

D2000

VDDC0

VDDC1

VDDC2

VDDC3

VDDC4

VDDC5

VDDC6

VDDC7

VDDC8

VDDCARM0

VDDCARM1

VDDCARM2

VDDCTCM0

VDDCTCM1

VDDCGSM0

VDDCGSM1

VDDCGSM2

VDDCRAM0

VDDCRAM1

VDDCUMA0

VDDCUMA1

VDDCUMA2

VDDCUMA3

VDDCPLL

B2030

D

ROP1013112/1

Core-1.3V

ARMCore-1.3V

TCMCore-1.3V

GSMCore-1.3V

RAMCore-1.3V

UMACore-1.3V

DPLL-1.3V

C2256

100nF

N2000

ERICSSON AB 2010

POWER

THERMAL GROUNDS

ERICSSON_AB2012

ROP1013066/6

C2257100nF

VSSTH1

VSSTH2

VSSTH3

VSSTH4

VSSTH5

VSSTH6

VSSTH7

VSSTH8

VSSTH9

VSSTH10

VSSTH11

VSSTH12

VSSTH13

VSSTH14

VSSTH15

VSSTH17

VSSTH18

VSSTH19

VSSTH21

VSSTH22

VSSTH25

VSSTH26

VSSTH27

VSSTH30

C2258

100nF

D2000

VDDEE00

VDDEE01

VDDEE02

VDDEE03

VDDEE04

VDDEE05

VDDEE06

VDDEE07

VDDEE08

VDDEE09

VDDEE10

VDDEE11

VDDEE12

VDDEE13

VDDEE14

VDDEE15

VDDEE16

VDDEE17

VDDEE18

VDDEE19

VDDEE20

VDDEE21

VDDEWL0

VDDEWL1

VDDRTC

VPPSTD0

VPPSTD1

VPPSTDSENSE

NotConnected_Balls

NC_1

NC_

2

NC_3

NC_4

NC_5

NC_6

NC_7

DB2030

ROP1013112/1

I/O-1.8V

I/O-1.5/1.8V

RTC-1.3V

Analog-1.3V

Efuse

A20

A18

B18

A15

A11

A8

D1

D2

G1

G2

AD3

AD6

AC11

AD12

AD11

AD22

AD21

AA23

U24

P24

C2244100nF

C2246

100nF

C2243

100nF

F7

G7

G6

E5

E6

E7

E8

F8

G8

H8

H7

H6

H5

G5

F5

D6

D7

D8

F9

G9

J7

J6

J5

F4

C2248

100nF

C2249100nF

C2251

100nF

C2252100nF

C2253

100nF

C2254

100nF

C2255

100nF

H24

H23

N1

AC3

N2

L2

AD1

AC1

AD2

A2

A1

B1

F6

A24

AC24

AD24

VSS00

VSS01

VSS02

VSS03

VSS04

VSS05

VSS06

VSS07

VSS08

VSS09

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSSAVDDA

M17

Y5

Y20

Y13

W5

U5

U20

U16

U13

U11

U10

T17

T9

R8

P17

J8

J17

H15

H13

H11

H9

G5

F5

E20

E13

E6

M8

C2268

C2270

100nF

100nF

C2263

C2265

C2267

100nF

100nF

100nF

Confidential

Approved according to 00021-LXE 107 42/1

Sony Ericsson

BASEBAND

Power

ASICs

C2271

100nF

C2273

100nF

SEMCJ/ Zhang Zongyao

SEMCJ/ Ken Ikuno

Ai Main Board

2/1911-ROA 128 2071/2

C2277

100nF

W1

W2

Y1

Y2

AD15

AD14

AD18

AD19

AD13

AC17

AB24

U2

U1

F24

F23

B3

A3

A6

AD17

C24

C23

B6

A4

A21

AD20

AB2

AB1

C1

D2000

VDD_TX

VDD_

RX

VDD_BG

VDD_CS_ADPLL

VDD_DPLL

VDD_

CLK32

VDD_1

VDD_2

VDD_3

VDD_4

VDD_5

VDD_6

VDD_7

VDD_8

VDD_9

VD

D_10

VDD_11

VDD_12

VDD_13

VDD_14

VDD_15

VDD_16

VDD_17

VDD_18

VDD_19

VDD_20

VDD_21

VDD_22

DB2030

R

OP1013112/1

VSSCOMPLEX_IO1

VSSCOMPLEX_IO2

DI

GITALSUPPLY

VSS_TX

VSS_RX

VSS_BG

VSS_CS_ADPLL

BG_REF

2006/12/14

L8

L5

N8

T5

V5

K5

P8

C2279

100nF

DIAGRAMSCHEMA

E

08 of 23

Page 9

VCORE18

VDDE18

VBATI

VCORE18 VDDE18 VBATI

VDDE18 VCORE18

VPP

Standard memory solution

VBATI

R2214

1Mohms

1KohmsR2206

D2300

X16D_POWER

X16D_POWER

D4

F-VCC

C2288

100nF

F-VCC

D6

F-VCC

F-VCC

J4

F-VCC

F-VCC

J6

F-VCC

F-VCC

D3

D-VCC

D-VCC

C5

D-VCC

D-VCC

D7

D-VCC

D-VCC

J2

VCCQ

VCCQ

J3

VCCQ

VCCQ

J7

VCCQ

VCCQ

J8

VCCQ

VCCQ

J1

F-VPP

D2

S-VCC

PF38F5060M0Y0B0

RYT118953/1

R1A

E

V2206

B

2SA2079

C

RYN120910/1

(REQ3278U)

V2207

PMEG3002AEL

RKZ123927/1

(REQ3254U)

RJC5163636/22

C2298

220nF

C2282

2.2uF

C2285

100n

F

C2287

100nF

C2

VSS

VSS

C3

VSS

VSS

C4

VSS

VSS

C6

VSS

VSS

C7

VSS

VSS

C8

VSS

VSS

K2

VSS

VSS

K3

VSS

VSS

K4

VSS

VSS

K6

VSS

VSS

K7

VSS

VSS

K8

VSS

VSS

Confidential

Approved according to 00021-LXE 107 42/1

Sony Ericsson

BASEBAND

Power

Memories

SEMCJ/ Zhang Zongyao

SEMCJ/ Ken Ikuno

Ai Main Board

2/1911-ROA 128 2071/2

DIAGRAMSCHEMA

2006/12/14

E

09 of 23

Page 10

Page 13

Page 13

VDDE18

WPAVDC

RTEMP

VLOOP

DCDC_PA

WRFLOOP

VAD I2CDAT1

VBACKUP

MIDREF

SPL

SPR

FLASH_STROBE

WSTR_15

ANTSW3_1V8

BTRX

BTCTS

BTCLKREQ

MEMRESn

VDIG

VDDE18

VMSPICO

VBATI

VBATI

BTCLKREQ

VBATI

WPAVDC

DCDC_PA

WRFLOOP

VAD

MIDREF

SPL

SPR

FLASH_STROBE FLASH_STROBE_27

WSTR_15

ANTSW3_1V8

BT

RX

BTCTS

Pag

Pag

e 14

e 14

VMSPICO

VDDE18

MSDETECT

VBATI

VBACKUP

SIM & MS Pico

SIM & MS Pico

MSDETECT

R2330

100Kohms

CTMS

DTMS

USBRCV

USBVALID

BTRX

BTCTS

BTCLKREQ

MSDETECT

GPIO

GPIO

Page 12

Page 12

CFMS_AID_18

DFMS

MPX1_OFF

KBDI

NAVDIM

VGA_OFF

AMPCTRL

VBT_EN

CAM_27_EN

BTRTS

DCIO_ON

MEMDPD

C2405

BTTX

33pF

VDDE18

R2309

10Kohms

M

33pF

C2406

33pF

C2407

VDDE18

33pF

C2408

WPAVDC

RTEMP

VLOOP

DCDC_PA

W

RFLOOP

VAD

I2CDAT1

I2CCLK1

VBACKUP

WPABIAS

AID_AD

VCXOCONT

ADC/DAC & MP-PCM & I2C

ADC/DAC & MP-PCM & I2C

N2402

VCCB

C7

B1

C5

B2

C3

B3

C1

B4

B2

GND

100nF

ST4G3234

RYT113995/1

C2401

MEMDPD

VCCA

I2CDAT1

I2CCLK1

AID_AD

USBVALID

USBRCV

DTMS

CTMS

VDIGVDDE18

VDIG

B6B4

A7

A1

A5

A2

A3

A3

A1

A4

C2402

100nF

Page 11Page 11

MEMDPD

MEMRESn

Memories

Memories

CFMS_AID

DFM

S

VDIG

VDDE18

MIDREF

SPL

SPR

FLASH_ST

CFMS_AID

S

DFM

Connectivity

Connectivity

Page 15

Page 15

ROBE_27

MPX1_OFF

KBDIM

NAVDIM

VGA_OFF

AMPCTRL

VBT_EN

CAM_27_EN

BTTX

BTRTS

D

CIO_ON

CTMS

DTMS

USBRCV

USBVALID

D_AD

AI

DCIO

MICN/AUXinR

MICP/AUXinL

VBUS

VPP

SERVICEn

Confidential

Approved according to 00021-LXE 107 42/1

Sony Ericsson

BASEBAND

Operation & Services

Top

DCIO

BUS

WSTR

ANT

SW3

SEMCJ/ Ikunori Kannou

SEMCJ/ Ken Ikuno

Ai Main Board

2/1911-ROA 128 2071/2

I2CCLK1

WPABIAS

VCXOCONT

DCIO

MICN/AUXinR

MICP/AUXinL

VBUS

VPP

SERVICEn

WSTR

ANTSW3

MPX1_OFF

KBDIM

NAVDIM

VGA_OFF

AMPCTRL

VBT_EN

CAM_27_EN

BTTX

BTRTS

DCIO_ON

2006/12/14

DIAGRAMSCHEMA

E

10 of 23

Page 11

D2000

Data_and_Address_Bus

EMIF_DATA[0]

EMIF_DATA[1]

EMIF_DATA[2]

EMIF_DATA[3]

EMIF_DATA[4]

EMIF_DATA[5]

EMIF_DATA[6]

EMIF_DATA[7]

EMIF_DATA[8]

EMIF_DATA[9]

EMIF_DATA[10]

EMIF_DATA[11]

EMIF_DATA[12]

EMIF_DATA[13]

EMIF_DATA[14]

EMIF_DATA[15]

MEM_CLK

WEn

MEMRESn

MEMDPD

MEMRESn

MEMDPD

U22

D0

N21

D1

T22

D2

N22

D3

R22

D4

M22

D5

M21

D6

P22

D7

L21

D8

K21

D9

L22

D10

K22

D11

H21

D12

J21

D13

G21

D14

J22

D15

B22

VINTHI

E21

MEMCLKRET

M23

ME

F21

SDR_CLKRET

C22

NF_D0

D21

NF_D1

C21

NF_D2

D20

NF_D3

C20

NF_D4

E19

NF_D5

D19

NF_D6

C19

NF_D7

C17

NF_R/B

DB2030

ROP1013112/1

Memory_ControL

MWAIT_N

NAND_Flash_IF

CS0_N

CS1_N

CS2_N

CS3_N

WE_N

OE_N

MEMBE0_N

MEMBE1_N

MEMADV_N

MEMCLK

SDR_CS_N

SDR_CLK

SDR_CKE

SDR_CAS_N

SDR_RAS_N

NF_RE_N

NF_WE_N

NF_ALE

NF_CLE

NF_CS_N

AC18

A1

AC19

A2

AC20

A3

AC21

A4

AC22

A5

Y23

A6

AC23

A7

W23

A8

V23

A9

U23

A10

T24

A11

T23

A12

P23

A13

N24

A14

N23

A15

L24

A16

L23

A17

K23

A18

J24

A19

J23

A20

G23

A21

G24

A22

E23

A23

E24

A24

D23

A25

A19

CS0n

B17

CS1n

B15

A17

D24

OEn

A22

MEM_BE0n

B23

MEM_BE1n

B21

MEM_ADVn

AD16

MEM_CLK

F22

SDR_CSn

B20

SDR_CLK

H22

SDR_CKE

G22

SDR_CASn

SDR_RASn

B16

B19

E18

D18

C18

E17

D17

SDR_CLK

MEM_CLK

EMIF_ADDRESS[1:25]

EMIF_ADDRESS[1]

EMIF_ADDRESS[2]

EMIF_ADDRESS[3]

EMIF_ADDRESS[4]

EMIF_ADDRESS[5]

EMIF_ADDRESS[6]

EMIF_ADDRESS[7]

EMIF_ADDRESS[8]

EMIF_ADDRESS[9]

EMIF_ADDRESS[10]

EMIF_ADDRESS[11]

EMIF_ADDRESS[12]

EMIF_ADDRESS[13]

EMIF_ADDRESS[14]

EMIF_ADDRESS[15]

EMIF_ADDRESS[16]

EMIF_ADDRESS[17]

EMIF_ADDRESS[18]

EMIF_ADDRESS[19]

EMIF_ADDRESS[20]

EMIF_ADDRESS[21]

EMIF_ADDRESS[22]

EMIF_ADDRESS[23]

EMIF_ADDRESS[24]

EMIF_ADDRESS[25]

Layout notice:

SDR_CLKRET and MEM_CLKRET should be connected

as close as possible to D2300 clock input pad on the PCB.

SDR_CLK and SDR_CLKRET should be routed differentially.

MEM_CLK and MEM_CLK RET should be routed diff erentially.

EMIF_ADDRESS[1]

EMIF_ADDRESS[2]

EMIF_ADDRESS[3]

EMIF_ADDRESS[4]

EMIF_ADDRESS[5]

EMIF_ADDRESS[6]

EMIF_ADDRESS[7]

EMIF_ADDRESS[8]

EMIF_ADDRESS[9]

EMIF_ADDRESS[10]

EMIF_ADDRESS[11]

EMIF_ADDRESS[12]

EMIF_ADDRESS[13]

EMIF_ADDRESS[14]

EMIF_ADDRESS[15]

EMIF_ADDRESS[16]

EMIF_ADDRESS[17]

EMIF_ADDRESS[18]

EMIF_ADDRESS[19]

EMIF_ADDRESS[20]

EMIF_ADDRESS[21]

EMIF_ADDRESS[22]

EMIF_ADDRESS[23]

EMIF_ADDRESS[24]

EMIF_ADDRESS[25]

D2300

D1

A1

C1

A2

B1

A3

B2

A4

A2

A5

B3

A6

A3

A7

A4

A8

G8

A9

F8

A10

E8

A11

G9

A12

F9

A13

E9

A14

D9

A15

C9

A16

B9

A17

B4

A18

B5

A19

A5

A20

F7

A21

E7

A22

B7

A23

A6

A24

A7

A25

A8

A26

B8

A27

PF38F5060M0Y0B0

RYT118953/1

X16D_IO

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

K5

D5

G7

E1

F1

E2

H7

G3

G2

H3

E6

F2

H9

H8

J5

H5

G6

H6

G4

H4

F3

F4

M7

M3

M2

L1

K1

L2

M4

L3

L4

L5

M5

L6

M6

L7

L8

K9

L9

M8

D2300

F-CLK

F-ADV

F-RST

F-WP1

F-WP2

F-WE

F-OE

F1-CE

F2-CE

F3-CE

F4-CE/A28

D1-CS

D-DM0

D-DM1

D-CLK

/D-CLK

D-CKE

D-WE

D-BA0

D-BA1

D-CAS

D-RAS

D-UDQS

D-LDQS

PF38F5060M

RYT118953/1

EMIF_DATA[0]

EMIF_DATA[1]

EMIF_DATA[2]

EMIF_DATA[3]

EMIF_DATA[4]

EMIF_DATA[5]

EMIF_DATA[6]

EMIF_DATA[7]

EMIF_DATA[8]

EMIF_DATA[9]

EMIF_DATA[10]

EMIF_DATA[11]

EMIF_DATA[12]

EMIF_DATA[13]

EMIF_DATA[14]

EMIF_DATA[15]

X16D_CONTROL

0Y0B0

NC_F-DPD

NC_D2-CS

NC_S-CS1

NC_S-CS2

NC_N-ALE

NC_N-CLE

NC_N-RY/BY

J9

WAIT

B6

E3

F6

H2

D8

E5

H1

G1

RFU

A1

DU_1

A9

DU_2

M1

DU_3

M9

DU_4

Confidential

Approved according to 00021-LXE 107 42/1

Sony Ericsson

BASEBAND

Operation & Services

Memories

SEMCJ/ Zhang Zongyao

SEMCJ/ Ken Ikuno

Ai Main Board

2/1911-ROA 128 2071/2

DIAGRAMSCHEMA

2006/12/14

E

11 of 23

Page 12

MSDETECT

BTCTS

BTRX

MSDETECT

BTCTS

BTRX

BTCLKREQ

CTMS

USBVALID

USBRCV

DTMS

BTCLKREQ

CTMS

USBVALID

USBRCV

DTMS

D2000

DB2030

ROP1013112/1

GenPurposeI/O

GPIO00

GPIO01

GPIO02

GPIO03

GPIO04

GPIO05

GPIO06

GPIO07

GPIO10

GPIO11

GPIO12

GPIO13

GP

GPIO15

GPIO16

GPIO17

GP

GPIO21

GPIO22

GPIO23

GPIO24

GPIO25

GPIO26

GPIO27

GPIO30

GPIO31

GPIO32

GPIO33

GPIO34

GPIO35

GPIO36

GPIO37

GPIO40

GPIO41

GPIO42

GPIO43

GPIO44

GPIO45

GPIO46

GPIO47

D9

C9

B8

E8

C8

D8

B7

E7

D6

C7

A7

A5

B5

IO14

B4

D7

C6

B2

IO20

C5

C4

C3

D5

D4

D3

E5

E3

C2

E2

E4

F3

J3

F2

F4

G4

G3

H2

J2

H1

J4

K3

L4

DFMS

CFMS_AID_18

AMPCTRL

BTRTS

MPX1_OFF

VGA_OFF

CAM_27_EN

MEMDPD

BTTX

DCIO_ON

VBT_EN

DFMS

CFMS_AID_18

AMPCTRL

BTTX

BTRTS

MPX1_OFF

VGA_OFF

DCIO_ON

KBDIM

NAVDIM

VBT_EN

CAM_27_EN

MEMDPD

Confidential

Approved according to 00021-LXE 107 42/1

Sony Ericsson

BASEBAND

Operation & Services

GPIO

SEMCJ/ Zhang Zongyao

SEMCJ/ Ken Ikuno

Ai Main Board

2/1911-ROA 128 2071/2

DIAGRAMSCHEMA

2006/12/14

E

12 of 23

Page 13

RTEMP

VLOOP

DCDC_PA

WRFLOOP

VAD

WPAVDC

VBACKUP

AID_AD

D2000

DB2030

ROP1013112/1

DACCLK

DACDAT

DACSTR

ADCSTR

DAC_DAT

DAC_STR

DAC_CLK

RTEMP

VLOOP

DCDC_PA

WRFLOOP

VAD

WPAVDC

VBACKUP

AID_AD

R21

P20

R20

VDDE18

ADCSTR

N2000

ERICSSON AB 2010

OP AND SERVICES

ADC

L10

GPA1

K10

GPA2

L11

PA3

G

K11

GPA4

K12

GPA5

J11

GPA6

J10

GPA7

J9

GPA12

D9

GPA13

C7

ADSTR

ERICSSON_AB2012

ROP1013066/6

GND

N2000

ERICSSON AB 2010

OP AND SERVICES

DAC

B5C9

DACO1

DACDAT

A10

B10 H11

C8

B9

DACCLK

DACSTR

I2C IF

SDA

SCL

ERICSSON_AB2012

ROP1013066/6

DAC02/4

DACO3

G11

WPABIAS

VCXOCONT

WPABIAS

VCXOCONT

VDDE18

VDDE18

D2000

DB2030

ROP1013112/1

D2000

DB2030

ROP1013112/1

I2CSCL0

I2CSDA0

I2CSCL1

I2CSDA1

DACCLK

DACDAT

DACSTR

ADCST

R2311

10Kohms

AA10

AB10

E12

D12

AA2

AC2

Y3

AA1

R

R2312

10Kohms

I2CCLK1

I2CDAT1

Confidential

Approved according to 00021-LXE 107 42/1

Sony Ericsson

BASEBAND

Operation & Services

ADC & DAC

SEMCJ/ Satoru Matsumoto

SEMCJ/ Ken Ikuno

Ai Main Board

2/1911-ROA 128 2071/2

I2CCLK1

I2CDAT1

DIAGRAMSCHEMA

2006/12/14

E

13 of 23

Page 14

D2000

DB2030

ROP1013112/1

MemoryCardIF

SIM_IF

MMCDAT0

MMCDAT1

MMCDAT2

M

MCDAT3/CD

MMCCLK

MMCCMD

MMCCMDDIR

MMCDATDIR

SIMRST_N

SIMCLK

SIMDAT

VBATI

B14

D13

C13

B13

D14

C14

C15

E14

AD10

AA11

Y11

MSSCLK

R2307

0ohms

R2307 close to Marika

100Kohms

100Kohms

R2317

R2318

R2319

100Kohms

R2320

100Kohms

These resistors must be put between capacitors and Marika

VMSPICO

0ohmsR2332

NM

R2331

100Kohms

NM

N2300

LDO REGULATOR

A1

EN

B2

TPS79918YZU

RYT1137816/4

NM

0ohmsR2333

C1C3

OUTIN

A3

NRGND

C2334

2.2uF

NM

NM

R2334 0ohms

C2335

NM

2.2uF

MSSDIO0

MSSDIO1

MSSDIO2

MSSDIO3

MSSCLK_1

MSBS

C2316

56pF

C2316 close to X2512

VDDE18

R2305

1Mohms

X2512

MSDETECT

AA03-S024VA1

RNV799028/24

(REQ3246U)

6

5

7

8

9

10

11

13

C2319

R1A

56pF

C2319 close to X2512

MSDETECT

VMSPICO

VDDE18

VBACKUP

VBATI

VMSPICO VDDE18

VBACKUP

VBATI

VDDE18

R2326

10Kohms

C2325

100pF

N2000

C2

SIMOFF

H2

SRST

J3

SCLK

H1

SDAT

ERICSSON_AB2012

ROP1013066/6

ERICSSON AB 2010

OP AND SERVICES

SIM IF

SIMVCC

SIMRST

SIMCLK

SIMDAT

SI

MVCC

SIMRSTn

C2332

22pF

C2333

22pF

SIMCLK

SIMDAT

VBACKUP

C2317 close to X2512

56pF

F1

G2

G1

H3

C2309

1uF

R2308

8.2Kohms

C2309, R2306

close to Vincenne

C2331

22pF

C2317

1

2

3

4

15

12

14

16

18

Chassis

25

Chassis

26

Chassis

27

Chassis

28

Camera FLEX Connector (L)

Confidential

Approved according to 00021-LXE 107 42/1

Sony Ericsson

BASEBAND

Operation & Services

MS Pico and SIM

SEMCJ/ Zhang Zongyao

SEMCJ/ Ken Ikuno

Ai Main Board

2/1911-ROA 128 2071/2

DIAGRAMSCHEMA

2006/12/14

E

14 of 23

Page 15

CFMS_AID

FLASH_STROBE_27

DFMS

MIDREF

SPL

SPR

DCIO

VDIG

VDDE18

R2310

100Kohms

GND

D2000

USBDP

USBDM

DB2030

ROP1013112/1

USB_IF

USBSUSP

USBPUEN

Y24 W22

AA24

VDIG VDDE18

CFMS_AID

FLASH_STROBE_27

USBDM

USBDP

USBOE

DFMS

Y22

V22

C2306

47pF

C2308

47pF

100nF

C2301

USBRCV

USBVALID

DTMS

VDIG

43

SD

RYN901918/2

V2300

5

G

V2304

RKZ123927/1

PMEG3002AEL

(REQ3254U)

R2301

21

AC

(REQ3250U)

RKZ223921/1

BZX884-C15

1Kohms

C2318

R2321

2

3

VDDE18VDIG

D2304

C2302

100nF

C2300

100nF

R2350

22Kohms

MAX3349E

D1

VBUS

B1

VL

A1

VUART

A3

TX_DFMS

C2

ENUM

A4

VBUSDET

B3

VP

B2

VM

B4

RCV

C3

SUSP

C4

OE

MAX3349E

RYT109922/1

VBUS VBUS

MIDREF

A2

RX_DTMS

D2

D+

D3

D-

C1

VTERM

C2303

1u

F

D4

GND

SPL

SPR

DCIO

C2321

C2320

220nF

220nF

1Mohms

R2328

C2322

1uF

2

1Mohms

R2329

V2307 close to X2300

21

AC

RKZ223921/1

BZX884-C15

V2204

1

3

(REQ3250U)

V2307

RKZ223922/1

(REQ3252U)

ESDALC6V1M3

V2305

AID/ACB/VPP_1

R2302

560ohms

V2300

RYN901918/2

C2328

10nF

VPP

DPext/DTMS

DMext/DFMS

SPREF

L2300

Mic+/AUXinL

L2301

Mic-/AUXinR

L2302

SPL

L2303

SPR

L2304

VIDEO/STROBE

L2305

DCIO

C2323 close to X2300

DS

6

1

47pF

G

1Kohms

1

2

C2327

10nF

REG70618/19

REG70618/19

REG70618/19

REG70618/19

REG70618/19

REG70618/19

V2303

(REQ3252U)

RKZ223922/1

ESDALC6V1M3

Confidential

Approved according to 00021-LXE 107 42/1

C2323

1uF

VDDE18

R2303

4.7Kohms

R2304

470ohms

MICN/AUXinR

MICP/AUXinL

V2306

C2326 and V2306

close to X2300

Sony Ericsson

BASEBAND

Operation & Services

Connectivity

3

V2301

(REQ3316U)

C2326

DF2S8.2CT

RKZ223923/1

UNRF2A7

RYN121918/1

2

R2316 47Kohms

1uF

1

SEMCJ/ Hu Xueliang

SEMCJ/ Ken Ikuno

Ai Main Board

VPP

X2300

SXA1097055/12

(REQ3244U)

2/1911-ROA 128 2071/2

R1A

SERVICEn

AID_AD

VBUS

1

SPREF

2

Mic+/AUXinL

3

Mic-/AUXinR

4

SPL

5

SPR

6

VIDEO/STROBE

7

AID/ACB/VPP

8

D+/DTMS

10

D-/DFMS

11

DCIO

12

GND

9

Chassis

Z1

Chassis

Z2

USBRCV

USBVALID

DTMS

C2329

CTMS

C2330

System connector

CSS5012-8F01E

2006/12/14

SERVICEn

33pF

CTMS

33pF

VPP

AID_AD

VBUS

MICN/AUXinR

MICP/AUXinL

DIAGRAMSCHEMA

E

15 of 23

Page 16

RXQB

RXQA

RXIA

RXIB

IDATA

QDATA

DCLK

TESTOUT

RX

RXQA

RXIA

RXIB

IDATA

QDATA

DCLK

TESTOUT

Page 17

Page 17

WSTR_15

WDAT

WCLK

TXQB

Page 18

Page 18

ANTSW3_1V8

RADSTR

RADDAT

RADCLK

TXON

MODA

MODB

MODC

MODD

ANTSW0

ANTSW1

ANTSW2

TXQA

TXIA

TXIB

QB

RXQB

RXQA

RXIA

RXIB

WCDMA

WCDMA

VDDE18VDIG

VDDE18

G

VDI

IDATA

QDATA

DCLK

TESTOUT

GSM

GSM

WSTR_15

WDAT

WCLK

TXQB

TXQA

TXIA

TXIB

RADSTR

RADDAT

RADCLK

TXON

MODA

MODB

MODC

MODD

ANTSW0

ANTSW1

ANTSW2

ANTSW3_1V8

WSTR_15

WDAT

WCLK

TXQB

TXQA

TXIA

TXIB

RADSTR

RADDAT

RADCLK

TXON

MODA

MODB

MODC

MODD

ANTSW0

ANTSW1

ANTSW2

ANTSW3_1V8

VDIG

VDDE18

VDIG VDDE18

Confidential

Approved according to 00021-LXE 107 42/1

Sony Ericsson

BASEBAND

UMTS Access

Top

SEMCJ/ Kensuke Katsuta

SEMCJ/ Ke

Ai Main Board

2/1911-ROA 128 2071/2

n Ikuno

DIAGRAMSCHEMA

2006/12/14

E

16 of 23

Page 17

RXQB

RXQA

RXIA

RXIB

RXQB

RXQA

RXIA

RXIB

D2000

P5

ADC_Q_IN_INV

P4

ADC_Q_IN

R5

ADC_I_IN

R4

ADC_I_IN_INV

DB2030

ROP1013112/1

RADI

O_STR

RADIO_DAT

RADIO_CLK

ADC_RXEXT_P

ADC_RXEXT_N

DAC_Q_OUT_INV

DAC_Q_OUT

DAC_I_OUT

DAC_I_OUT_INV

DAC_RXEXTRES

T21

T20

U21

T1

R1

H5

J5

N5

N4

K4

C2400

100nF

Close to D2000

43KohmsR2400

Close to D2000

WSTR_15

WDAT

WCLK

TXQB

TXQA

TXIA

TXIB

WSTR_15

WDAT

WCLK

TXQB

TXQA

TXIA

TXIB

Confidential

Approved according to 00021-LXE 107 42/1

Sony Ericsson

BASEBAND

UMTS Access

WCDMA

SEMCJ/ Kensuke Katsuta

SEMCJ/ Ken Ikuno

Ai Main Board

2/1911-ROA 128 2071/2

DIAGRAMSCHEMA

2006/12/14

E

17 of 23

Page 18

ANTSW0_1V8

TESTOUT

IDATA

QDATA

DCLK

TESTOUT

IDATA

QDATA

DCLK

TXON

VDDE18

R2409

10Koh

ms

NM

R3

T3

R2

AB3

AA4

D2000

IDATA

QDATA

DCLK

HSSLRX

HSSTXCLK

DB2030

ROP1013112/1

GSMRadio_IF

InterSystem_IF

UMTS-HSSL_IF

DIRMOD0

DIRMOD1

DIRMOD2

DIRMOD3

DIRMODCLK

RFCLK

RFSTR

RFDAT

BANDSEL

ANTSW0

ANTSW1

ANTSW2

ANTSW3

ISSYNC_N

ISEVENT_N

HSSLTX

HSSLRXCLK

M5

MODA MODA

M4

P1

P2

TESTOUT

M3

RADCLK

N3

P3

RADSTR

RADDAT

V4

TXON

L3

K1

ANTSW1_1V8

K2

ANTSW2_1V8

M1

M2

ANTSW3_1V8

AC4

AA5

AB4

AA3

C2403

100nF

VDDE18

N2400

VCCBA1VCCA

C7

B1

C5

B2

C3

B3

C1

B4A2A4

B2

GND

ST4G3234

RYT113995/1

VDIG

B6B4

A7

A5

A3

A3

A1

C2404

100n

F

RADSTR

RADCLK

RADDAT

MODBMODB

MODCMODC

MODDMODD

ANTSW0

ANTSW1

ANTSW2

TXON

RADCLK

RADDAT

MODA

MODB

MODC

MODD

ANTSW0

ANTSW1

ANTSW2

RADSTR

ANTSW3_1V8

VDDE18

VDIG

VDDE18

VDIG

Confidential

Approved according to 00021-LXE 107 42/1

Sony Ericsson

BASEBAND

UMTS Access

GSM

SEMCJ/ Kensuke Katsuta

SEMCJ/ Ken Ikuno

Ai Main Board

2/1911-ROA 128 2071/2

DIAGRAMSCHEMA

2006/12/14

E

18 of 23

Page 19

KBDIM

NAVDIM

KBDIM

NAVDIM

DCIOint

VDDE18

VBATIVDIG

VBATI

VDDE18

VDIG

DCIOint

KBDIM

NAVDIM

splay

splay

Di

Di

Page 21

Page 21

MICN/AUXinR

MICP/AUXinL

AMPCTRL

VCAM18

VGA_OFF

MPX1_OFF

I2CCLK1

I2CDAT1

CAMSYSCLK

MICN/AUXinR

MICP/AUXinL

AMPCTRL

VCAM18

VGA_OFF

MPX1_OFF

I2CCLK1

I2CDAT1

CAMSYSCLK

VCAM12

VCAM27

VBATI

VBATI

MICN/AUXinR

ICP/AUXinL

M

PCTRL

AM

Audio

Audio

Keyboard

Keyboard

VCAM27

VCAM12

VCAM18

VGA_OFF

MPX1_OFF

I2CCLK1

I2CDAT1

CAMSYSCLK

Camera

Camera

Page 22

Page 22

Page 20

Page 20

Page 23

Pag

PCMDATA

PCMDATB

PCMSYN

PCMCLK

VAD

SPL

SPR

MIDREF

ONSWAn

e 23

FLASH_STROBE

PCMDATA

PCMDATB

PCMSYN

PCMCLK

VAD

SPL

SPR

MIDREF

ONSWAn

FLASH_STROBE

PCMDATA

PCMDATB

PCMSYN

PCMCLK

MIDREF

ONSWA

FLASH_STROBE

VAD

SPL

SPR

DCIOint

VBATI

VDIG

VDDE18

VCAM27

VCAM12

VBATI VDIG VDDE18 VCAM27

DCIOint

VCAM12

Confidential

Approved according to 00021-LXE 107 42/1

Sony Ericsson

BASEBAND

MMI

Top

SEMCJ/ Sa

SEMCJ/ Ken Ikuno

Ai Main Board

2/1911-ROA 128 2071/2

toru Matsumoto

DIAGRAMSCHEMA

2006/12/14

E

19 of 23

Page 20

V2506

V2504

CA

RKZ323916/1

1SS400CS

(REQ3222U)

RKZ223922/1

(REQ3252U)

ESDALC6V1M3

V2506 close to X2591

2

1

3

ONSWAn

AA03-S024VA1

RNV799028/24

X2512

(REQ3246U)

KOUT0

19

KIN0

17

Camera FLEX Connector (L)

ONSWAn

KOUT5

D2000

E10

D10

C10

B10

E9

DB2030

ROP1013112/1

KEYIN0_N

KEYIN1_N

KEYIN2_N

KEYIN3_N

KEYIN4_N

Keyboard_IF

KEYOUT0_N

KEYOUT1_N

KEYOUT2_N

KEYOUT3_N

KEYOUT4_N

KEYOUT5_N

R2517

R2513

R2516

R2518

R2514

C12

B12

E11

D11

C11

B11

1Kohms

1Kohms

1Kohms

1Kohms

1Kohms

C3003

470pF

C3004

C3002

470pF

470pF

T

hese capacitors must be put between zener diode and Marika

KOUT0 KOUT0

KOUT1 KOUT1

KUOT2

C3001

470pF

C3005

470pF

V2509

2

1

3

V2507

V2509,V2507,V2500

close to X2591

RKZ223922/1

(REQ3252U)

ESDALC6V1M3

1

2

1

3

DF3A3FV

RKZ223918/1

V2500

2

1

DF3A3FV

RKZ223918/1

3

V2510

2

ESDALC6V1M3

3

C3000

470pF

V2508

RKZ223922/1

(REQ3252U)

KOUT2

KOUT3KOUT3

KOUT4

KIN4

KIN3

KIN2

KIN1

KIN0

1

2

V2510,V2508 close to X2511

DF3A3FV

RKZ223918/1

3

Confidential

Approved according to 00021-LXE 107 42/1

Sony Ericsson

BASEBAND

Keypad

MMI

SEMCJ/ Hu Xueliang

SEMCJ/ Ken Ikuno

Ai Main Board

2/1911-ROA 128 2071/2

GND

Keyboard connector

X2591

ONSWA

18

KOUT1

8

KOUT2

3

KOUT3

5

KOUT4

7

KOUT5

10

14

16

11

13

9

1

2

19

20

Chassis

21

Chassis

22

Chassis

23

Chassis

24

X2511

RNV799031/28

KO

27

26

28

Camera FLEX Connector (R)

KIN4

KIN3

KI

KIN1

KIN0

KIN2

KIN1

N2

UT0

2-1871566-0

RPV79968/20

(REQ3261U)

2-1747769-8

(REQ3264U)

R1A

2006/12/14

DIAGRAMSCHEMA

E

20 of 23

Page 21

N2000

ERI

CSSON AB 2010

ERICSSON_AB2012

ROP1013066/6

BOOST

VDIG

DCIOint

VBATI

VDDE18

SWBOOST

ISENSE+

ISENSE-

V

BOOST

VDDE18

VBATI

DCIOintVDIG VDDE18

LCD CONNECTOR

502078-21

X2590

SXA1097083

(REQ3248U)

D7

15

D5

13

D3

11

D1

9

D6

14

D4

12

D2

10

D0

8

S

N3101

SCH2819

RYN901936/1

(REQ3267U)

D1G

D2

CA

C3104

1uF

25V

VBATI

22uH

L3103

C3100

2.2uF

L3102

100MHz

A4

REG70630/1

B4

A5

D5

FB+

E4

The LED driver should have a

separate groundplane. It should be

connected to phone gr ound in

one point. This is the ISENSEnode.

R3101

43ohms

R3102

150mohms

Z3100

EMI-FILTER

5

6

O2-2

7

O3-2

8

O4-2

GND_2 GND_1

KNA16400

REV50146/1

Z3101

EMI-FILTER

5

6

O2-2

7

O3-2

8

O4-2

910

GND_2 GND_1

KNA16400

REV50146/1

12

CA

NM

V3104

place V3104 close to

X2591 and X2590

(REQ3250U)

BZX884-C15

RKZ223921/1

1

I1-1O1-2

2

I2-1

3

I3-1

4

I4-1

109

1

I1-1O1-2

2

I2-1

3

I3-1

4

I4-1

C3102

33pF

C3102 close to X2591

C3107

33pF

C3107 close to X2590

X2591

Keyboard connecto r

X2590

X2590

LCD_BL_K

20

H2H Connector, LED

Cathode LCDt

17

21

2-1871566-0

RPV79968/20

KEY_BL_A

502078-21

SXA1097083

LCD_BL_A

502078-21

SXA1097083

D2000

Display_IF

AC16 Y15

AA17

Y17

Y18

AA18

AB17

Y19

AB18

PID0

PID1

PID2

PID3

PID4

PID5

PID6

PID7

DB2030

ROP1013112/1

PIDRES_N

PIDC0

PIDC1

PIDC2

PIDC3

PIDC4

PIDC5

N2000

ERICSSON AB 2010

MMI

LED

VIBRATOR

ERICSSON_AB2012

ROP1013066/6

AC15

AA15

AB15

AB16

Y16

AA16

CHARGE_LED_K

A6

LED1

B6

LED2

B3

VIBR

C3116

1uF

VDIG

C3120

NM

56pF

GND

Z3102

EMI-FILTER

1

I1-1 O1-2

2

I2-1

3

I3-1

4

I4-1

10 9

KNA16400

REV50146/1

DCIOint

GND_2GND_1

X2591

O2-2

O3-2

O4-2

Vibrator

VIBR

For ESD

countermeasure

5

6

7

8

2-1871566-0

RPV79968/20

6

4

Keyboard connecto r

LCD CONNECTOR

0ohmsR3116

C3106

56pF

C3118

1uF

C3118 close to B2506

X2590

LCD_FSYNC is input to Marika

BKE90340

BSY-3089

GND

3

B

2

A

1

VIBRATOR

B2506

502078-21

SXA1097083

(REQ3248U)

VCC

16

17

VCCIO

RESET

3

5

7

4

6

GND

1

GND

2

GND

18

GND

19

Chassis

Z1

Chassis

Z2

H2H connector, PDI

R1A

(REQ3282U)

R1A

RS

RD

CS

WR

KBDIM

NAVDIM

KBDI

NAVDIM

2-1871566-0

X2591

RPV79968/20

KEY_BL_LOWER

6

M

5

3

V3161

RN1970FS

RYN121935/1

(REQ3277U)

1

4

V3161

RN1970FS

RYN121935/1

(REQ3277U)

2

KEY_BL_UPPER

KEY_BL_LOWER

15

KEY_BL_UPPER

12

Keyboard connector

Confidential

Approved according to 00021-LXE 107 42/1

Sony Ericsson

BASEBAND

Display

MMI

SEMCJ/ Satoru Matsumoto

SEMCJ/ Ken Ikuno

Ai Main Board

2/1911-ROA 128 2071/2

SCHEMA DIAGRAM

2006/12/14

E

21 of 23

Page 22

V_MIC

MICP/AUXinL

MICN/AUXinR

R4132 1Kohms

C4147

33pF

R4103

1Koh

ms

AMPCTRL

L4106

REG70618/22

12

L4107

REG70618/22

C4146

C4145

33pF

33pF

MICP/AUXinL

C4106

33pF

NM

MICN/AUXinR

C4104

33pF

NM

C4105

33pF

NM

21

1

2

RF components

L4104

3

REG70618/22

V4107

RKZ223922/1

ESDALC6V1M3

12

2

1

L4105

REG70618/22

3

V4106

RKZ223922/1

ESDALC6V1M3

N4202

ATTE3

TJATTE3

TJ

A5

B3

B5

D2 A1

D3 A2

D4 A3

D5 A4

V_MIC

INTMICint

INTMIC

MICP

MICN

SPL

SPR

TJATTE3

SP_ref

MICP_int

MICN_int

SPL_int

SPR_int

COO

VAD

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

R1AROP1013074/1

B4101

1

OUT

2

R4131

NM

C4138

33pF

C4108

33pF

GND

RLC509429/11

KUS0223-010140

C4137

10uF

C4109

10uF

R4100 close to N2000

R4100

15Kohms

C4107

100nF

R4104

C4112

100nF

R4104,C4114 and C4111

close to N2000

15Kohms

21

CCO_1

C4102

100nF

C4155

100nF

B2

MIDREF

D1

MIC_P_Int

MIC_N_Int

B1

C1

C2

C3

C4

C5

B4

D2000

AC8

PCMDATA

Y10

PCMDATB

R1A

DB2030

ROP1013112/1

CCO

R4130

180ohms

R4102

180ohms

MIC1P

MIC1N

AUXI2P

AUXI3P

C4114

C4115

33pF

33pF

C4116

33pF

<NM>

C4111

33pF

<NM>

C4103

33pF

C4103 and C4117 close to N2000

PCMCLK

PCMSYN

C4117

33pF

AA9

AB9

AUXI1P

AUXI1N

C4118 100nF

C4119

100nF

C4136

33nF

PCMDATB

PCMDATA

PCMCLK

PCMSYN

N2000

ERICSSON AB 2010

PCMI

K1

PCMSYNK

J1

PCMCLK

M8

MIC1P

L8

MIC1N

M6

AUXI1P

K6

AUXI1N

L6

AUXI2P

L7

AUXI2N

M7

AUXI3P

K7

AUXI3N

L9

CCO

ERICSSON_AB2012

ROP1013066/6

AMPCTRL

MMI

MP_PCM IF

AUDIO IF

MIDREF

AUXO2

AUXO1

MIDREF

VAD

SPR

SPL

R4120

100Kohms

PCMO

BEARP

BEARN

AUXO1

AUXO2

LINEP

LINEN

DEC0

DEC3

DEC4

PCMDATB

PCMDATA

PCMCLK

PCMSYN

K2J2

BEARP

M4

L3

BEARN

AUXO1

L4

J4

AUXO2

L1

LINEP

M2

MIDREF

L5

DEC0

H4

G4

C4125

47n

F

C4120

100nF

Sensitive node

C4126

LINEP_1

470nF

R4112

PA_IN_P

C4128

470nF

R4114

2.2Kohms

470ohms

PA_BY

Sensitive node

C4127

33pF

R4113

470ohms

Mount L4100, L4101,

C4140 and C4141

close to N2000

NFB

N4100

LINEP_2

A1

A3

C1

C3

NCP2890FCT1_LEADFREE

RYT101947/2

IN-

IN+

Bypass

SHDN

C4140

33pF

AUDIO_PA

C4133

56pF

L4102

1GHz

L4103

1GHz

TP3200

2

1

V4100

3

SPP_2

C4134

33pF

<NM>

SPN_2

2

L4100

1GHz

L4101

1G

Hz

C4141

33pF

VBATI

B3

VBATI

VDD

SPP

A2

Vo1

SPN

C2

V02

B1

GND

B2

GN

D

10uF

C4131

C4142

33pF

close to connector

R4115

10Kohms

BEARP_1

BEARN_1

C4143

33pF

Mount L4102 and L4103

close to N4100

C4132

56pF

X2512

23

24

Camera FLEX Connector (L)

RKZ223922/1

(REQ3252U)

ESDALC6V1M3

TP4105

1

RKZ223922/1

V4101

ESDALC6V1M3

3

AA03-S024VA1

RNV799028/24

(REQ3246U)

MIDREF

VAD

SPR

SPL

AA03-S024VA1

RNV799028/24

X2512

(REQ3246U)

21

22

Camera FLEX Connector (L)

(REQ3252U)

Radio Components

VBATI

VBATI

Confidential

Approved according to 00021-LXE 107 42/1

Sony Ericsson

BASEBAND

MMI

Audio

SEMCJ/ Ikunori Kannou

SEMCJ/ Ken Ikuno

Ai Main Board

2/1911-ROA 128 2071/2

DIAGRAMSCHEMA

2006/12/14

E

22 of 23

Page 23

VGA_OFF

CAMSYSCLK

I2CCLK1

R3232

VCAM18

R3233

3.3Kohms

3.3Kohms

VCAM12

R3226

For

Sensitivity

suppression

100Kohms

VCAM27

VCAM18

C3301

56pF

I2CCLK1

GND

C3302

CIRES_N

Camera FLEX Connector (R)

X2511

RNV799031/28

0ohmsR3228

C3300

15pF

7

2

3

1

9

5

11

C3146

56pF

C3303

56pF

56pF

2-1747769-8

(REQ3264U)

R1A

4

6

8

10

12

Chassis

29

Chassis

30

Chassis

31

Chassis

32

GND

D2000

W20

AB21

V20

W21

AA21

AB22

AB20

AA22

AA20

AA19

Y21

CID0

CID1

CID2

CID3

CI

D4

CID5

CID6

CID7

CIPCLK

CIVSYNC

CIHSYNC

DB2030

ROP1013112/1

Camera_IF

CIRES_N

AB19

R3227

470Kohms

GND

RCLK

HREF

D0

15

D1

16

D2

17

D3

18

D4

19

D5

20

D6

21

D7

22

R3234 47ohms

14

VS

24

23

CID0

CID1

CID2

CID3

CID4

CID5

CID6

CID7

CIPCLK

CIVSYNC

CIHSYNC

C3135

27pF

C3136

27pF

C3137

27pF

C3138

27pF

C3139

27pF

C314315pF

C3144

33pF

C3145

33pF

C3141

C314027pF

C3142

27pF

27pF

VCAM12

VCAM27

VCAM18

VCAM12

VCAM27

I2CDAT1

MPX1_OFF

VCAM18

I2CDAT1

MP

X1_OFF

R3225

100Kohms

13

25

RNV799028/24

X2512

(REQ3246U)

STROBE

Camera FLEX Connector (L)

AA03-S024VA1

20

56pF

C3147

FLASH_STROBE

Confidential

Approved according to 00021-LXE 107 42/1

Sony Ericsson

BASEBAND

Camera

MMI

SEMCJ/ Satoru Matsumoto

SEMCJ/ Ken Ikuno

Ai Main Board

2/1911-ROA 128 2071/2

DIAGRAMSCHEMA

2006/12/14

E

23 of 23

Loading...

Loading...