Page 1

TV A0402

Page 2

Televisores de Plasma

Índice

1. TECNOLOGÍA DEL PLASMA.......................................3

1.1 Funcionamiento del plasma................................................3

1.2. Dentro de la pantalla...........................................................4

2. PERFIL..........................................................................7

2. PERFIL..........................................................................7

3. TABLETA B...................................................................8

3. TABLETA B...................................................................8

3.1. Operación y descripción de la tableta B............................8

3.1.1. Perfil.........................................................................8

3.1.2. Bloque relacionado a la descodificación de color..10

3.1.3.- Circuito de imagen dinámica................................12

3.1.3.1. Características del circuito de imagen AGC.......13

3.1.4.- Conversor A/D......................................................15

3.2.5.- IC del sistema........................................................17

3.1.6.- Scan Converter......................................................19

3.1.7.- Circuito de separación de sincronía......................21

3.1.8.- PLD.......................................................................23

3.1.9.- Señales de tiempo tales como reloj o señal de sincronía

..........................................................................................25

3.2.- Funciones de la microcomputadora...............................27

3.3. Scan Converter...................................................................32

3.3.1. Perfil.......................................................................32

3.3.2. Configuración........................................................32

3.3.3. Bloque de interfase de CPU...................................34

3.3.4. Bloque de interfase de memoria para

almacenamiento de imagen..............................................34

3.3.5. Bloque de entrada/reducción de imagen................34

3.3.6. Bloque de salida/expansión de imagen..................34

3.3.7. Bloque de control de bus interno...........................34

4. TARJETA Q.................................................................35

4.1 Descripción de la operación del circuito de la

tarjeta Q.....................................................................................35

4.2 Diseño del bloque Q............................................................37

4.2.1 Configuración del circuito de la tarjeta Q...............37

4.2.2 Diagrama a bloques de la tarjeta Q.........................37

4.3 Operación del circuito, descripción de cada

bloque.........................................................................................38

4.3.1 Interfase de entrada y Salida...................................38

4.3.2. Bloque de video.....................................................38

4.3.2.1 Entrada se señal compuesta de video...................39

4.3.2.2 Señal de entrada Y(C (terminal S).......................40

4.3.2.3.Entrada de señal por componentes.......................40

4.3.3 Bloque de Audio.....................................................41

4.3.3.1 Circuito de selección de entrada..........................43

4.3.3.2 Circuito de salida de Audio..................................43

4.3.3.3. Circuito de TruSurround.....................................43

4.3.3.4. Procesador de Audio...........................................44

4.3.3.5 Amplificador de Audífonos.................................44

Customer Services Latin América - 1 -

Page 3

Televisores de Plasma

4.3.3.6 Amplificador de Audio.........................................44

4.3.3.7 Salida de Sub_Woofer..........................................45

4.3.3.8 Circuito de control de silenciamiento...................45

4.3.4 Circuito de control de Ventilador............................45

4.3.5 Control S.................................................................45

5. TARJETA DE TU.........................................................48

5.1 Bloque de proceso de video................................................48

5.1.1 Diagrama a bloques del circuito de proceso de video.48

5.1.2 Circuito para el proceso de la Sincronía Horizontal.49

5.1.3 Circuito para el proceso de sincronía Vertical........49

5.1.4. Circuito de procesamiento de video.......................49

5.2 Circuito de proceso de audio.............................................51

5.2.1 Diagrama a bloques del circuito de audio...............51

5.2.2 Circuito de procesamiento de Audio.......................51

5.3. Bloque del Microcontrolador para control del Tuner...51

6. ADVERTENCIAS DEL DISPLAY................................55

7.5 Remoción de la tableta H1.................................................58

7.6 Remoción de la tableta H2.................................................58

7.7 Remoción de la pantalla de Plasma...................................58

7.- DESENSAMBLE........................................................56

7.1. Cubierta trasera................................................................56

7.2. Remoción de las tabletas Q, Q2 y TU..............................56

7.3. Remoción del blindaje principal......................................57

7.4. Remoción de la tableta B..................................................57

Customer Services Latin América - 2 -

Page 4

Televisores de Plasma

1. Tecnología del Plasma

Durante los últimos 75 años, la gran mayoría de los televisores se

han construido con la misma tecnología, el tubo de rayos

catódicos (CRT). En una televisión de CRT, una pistola dispara

un haz de electrones (partículas cargadas negativamente) dentro

de un tubo largo de vidrio. Los electrones excitan átomos de

fósforo a lo largo del lado ancho del tubo (la pantalla), lo cual

causa que los átomos de fósforo se iluminen. La imagen en la

televisión se produce al iluminar distintas áreas de la capa de

fósforo con distintas intensidades.

Los tubos de rayos catódicos producen imágenes precisas, pero

tienen un serio inconveniente: Son voluminosos. Para aumentar

el tamaño de la pantalla en un CRT, también se tiene que

aumentar la longitud del tubo (para dar a la pistola de scanneo de

electrones la distancia para alcanzar toda la pantalla).

Consecuentemente, cualquier televisión con un gran CRT va a

pesar mucho y ocupar un gran espacio en un cuarto.

Recientemente, una nueva alternativa ha empezado a aparecer en

el mercado: los televisores de pantalla plana de plasma. Estos

televisores tienen pantallas anchas, comparables con los equipos

de CRT más grandes, pero con solo 6” de ancho.

La idea básica de las pantallas de plasma es iluminar pequeñas

luces fluorescentes de colores para formar imágenes. Cada píxel

esta formado por tres luces fluorescentes (RGB), al igual que en

los televisores de CRT, las pantallas de plasma varían la

intensidad de las diferentes luces para producir un rango

completo de colores.

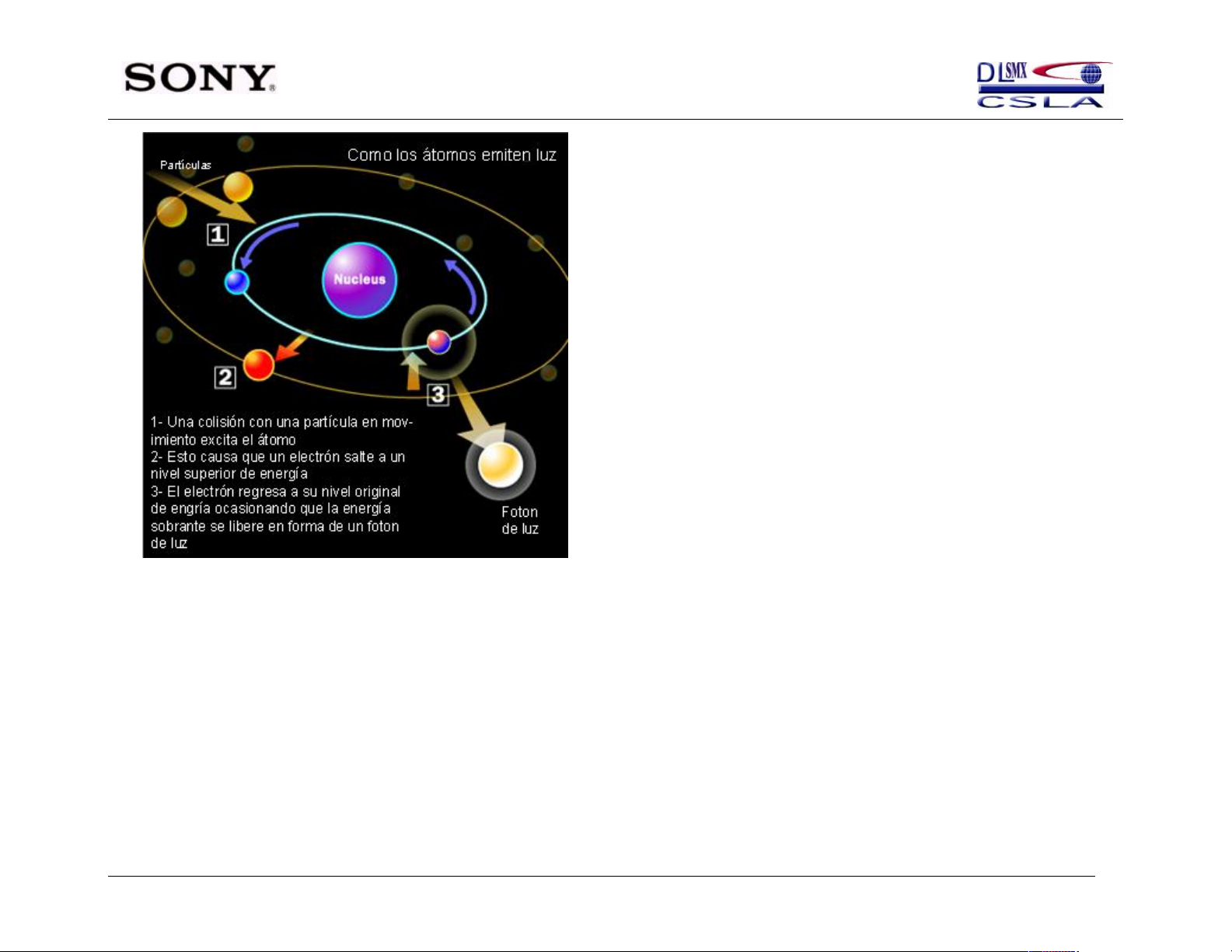

1.1 Funcionamiento del plasma

El elemento central en una luz fluorescente es el

plasma, un gas formado por iones libres (átomos

eléctricamente cargados) y electrones (partículas

negativamente cargadas). Bajo condiciones normales,

el gas es principalmente formado de partículas sin

carga. Esto es que los átomos individuales del gas

incluyen igual número de protones y electrones. Los

electrones cargados negativamente forman un

balance perfecto con los protones cargados

positivamente, con lo cual el átomo tiene una carga

de cero.

Al introducir muchos electrones libres en el gas al

establecer un voltaje eléctrico a través de el, la

situación cambia rápidamente. Los electrones libres

chocan con los átomos, forzándolos a perder otros

electrones. Con electrones faltantes, un átomo pierde

su balance. Este tiene una carga positiva,

convirtiéndolo en un ion.

En un plasma con una corriente eléctrica corriendo a

través de el, las partículas cargadas negativamente se

precipitan contra el área cargada positivamente del

plasma y las partículas cargadas positivamente se

precipitan contra el área cargada negativamente.

Customer Services Latin América - 3 -

Page 5

Televisores de Plasma

En esta precipitación, las partículas están constantemente

chocando entre ellas. Estas colisiones excitan los átomos de gas

en el plasma, causando que se liberen fotones de energía.

Los átomos de Xenón y Neon, átomos usados en las pantallas de

plasma liberan fotones de luz cuando están excitados. La mayoría

de estos átomos son fotones de luz ultravioleta, la cual es

invisible para el ojo humano. Pero los fotones ultravioletas

pueden ser usados para excitar fotones de luz visible.

1.2. Dentro de la pantalla

El gas xenón y neon en una televisión de plasma esta

contenido en cientos de miles de pequeñas celdas

posicionadas entre dos platos de vidrio. Largos

electrodos están también entre las placas de vidrio.

Los electrones de la pantalla transparente, los cuales

están rodeados por un material dieléctrico aislado y

cubierto por una capa protectora de oxido de

magnesio, están montadas encima de la celda, delante

de la placa frontal de vidrio.

Estos conjuntos de electrones se extienden a lo largo

de la pantalla. Los electrodos de la pantalla están

ordenados en filas horizontales a lo largo de la

pantalla y los electrodos de dirección están ordenados

en columnas verticales. Como se puede ver en el

diagrama a continuación, los electrodos verticales y

horizontales de una cuadricula básica.

Customer Services Latin América - 4 -

Page 6

Televisores de Plasma

se calienta. Cuando el electrón regresa a su nivel normal,

este libera energía en forma de un foton de luz visible.

Para ionizar el gas en alguna celda en particular, la computadora de la

pantalla de plasma carga los electrodos que se intersectan en esa

celda. Haciendo esto miles de veces en una pequeña fracción de

segundo, cargando cada celda en turno.

Cuando los electrodos que se intersectan están cargados (con una

diferencia de voltaje entre ellos), una corriente eléctrica fluye a través

del gas en la celda. Como vimos en la última sección, la corriente crea

un rápido flujo de partículas cargadas, el cual estimula los átomos de

gas para soltar fotones ultravioletas.

Los fotones ultravioleta desprendidos interactúan con el material de

fósforo revestido en la pared interna de la celda. El fósforo es una

sustancia que emite luz cuando esta expuesto a otra luz. Cuando un

foton ultravioleta golpea un átomo de fósforo en la celda, uno de los

electrones del fósforo salta a un nivel superior de energía y el átomo

Customer Services Latin América - 5 -

El fósforo en una pantalla de plasma emite luz de

color cuando es excitado. Cada píxel esta formado de

3 celdas separadas, cada una de un color diferente.

Un subpíxel tiene fósforo de luz roja, otro verde y

otro azul. Estos colores se mezclan para crear en

conjunto el color del píxel.

Al variar los pulsos de corriente fluyendo a través de

las distintas celdas, el sistema de control puede

incrementar o decrementar la intensidad del color de

cada subpixel para crear cientos de distintas

combinaciones de rojo, verde y azul. De esta manera

Page 7

Televisores de Plasma

el sistema de control puede producir colores a través del espectro

entero.

La principal ventaja de la tecnología de pantallas de plasma es

que se puede producir una pantalla muy ancha usando materiales

extremadamente delgados. Y debido a que cada píxel es

iluminado individualmente, la imagen es muy brillante y se ve

bien desde casi cualquier ángulo. La calidad de la imagen no es

muy superior a la de la mayoría de los equipos estándares de

tubos de rayos catódicos, pero ciertamente alcanza las

expectativas de la mayoría de la gente.

La mayor desventaja de esta tecnología es el precio. Con precios

de hasta $200,000.00 no son muy comerciales. Pero con los

precios cayendo y la tecnología avanzando, empezaran a sustituir

a los televisores de CRT. En el futuro cercano, acomodar una

televisión va a ser tan fácil como colgar un cuadro.

Customer Services Latin América - 6 -

Page 8

Televisores de Plasma

2. Perfil

Las pantallas de plasma de 32 y 42 pulgadas son prácticamente

iguales en cuanto a circuiteria a pesar de tener distinta resolución en el

PDP (Plasma Display Panel).

Las tabletas principales son la Q, B y TU.

Las funciones principales de la tableta Q son un selector de

audio/video, preamplificador de audio, amplificador de poder,

amplificador de audífonos y control de ventilador.

Las principales funciones de la tableta B son el procesamiento de

video tales como decodificador de color, separación de sincronía,

convertidor A/D, conversión IP, scan converter, interfase de PDP y

sintetizacion de OSD.

Las principales funciones de la tableta TU son el sintonizador de TV y

CATV y un circuito de reducción de fantasmas.

Customer Services Latin América - 7 -

Page 9

Televisores de Plasma

3. Tableta B

3.1. Operación y descripción de la tableta B

3.1.1. Perfil

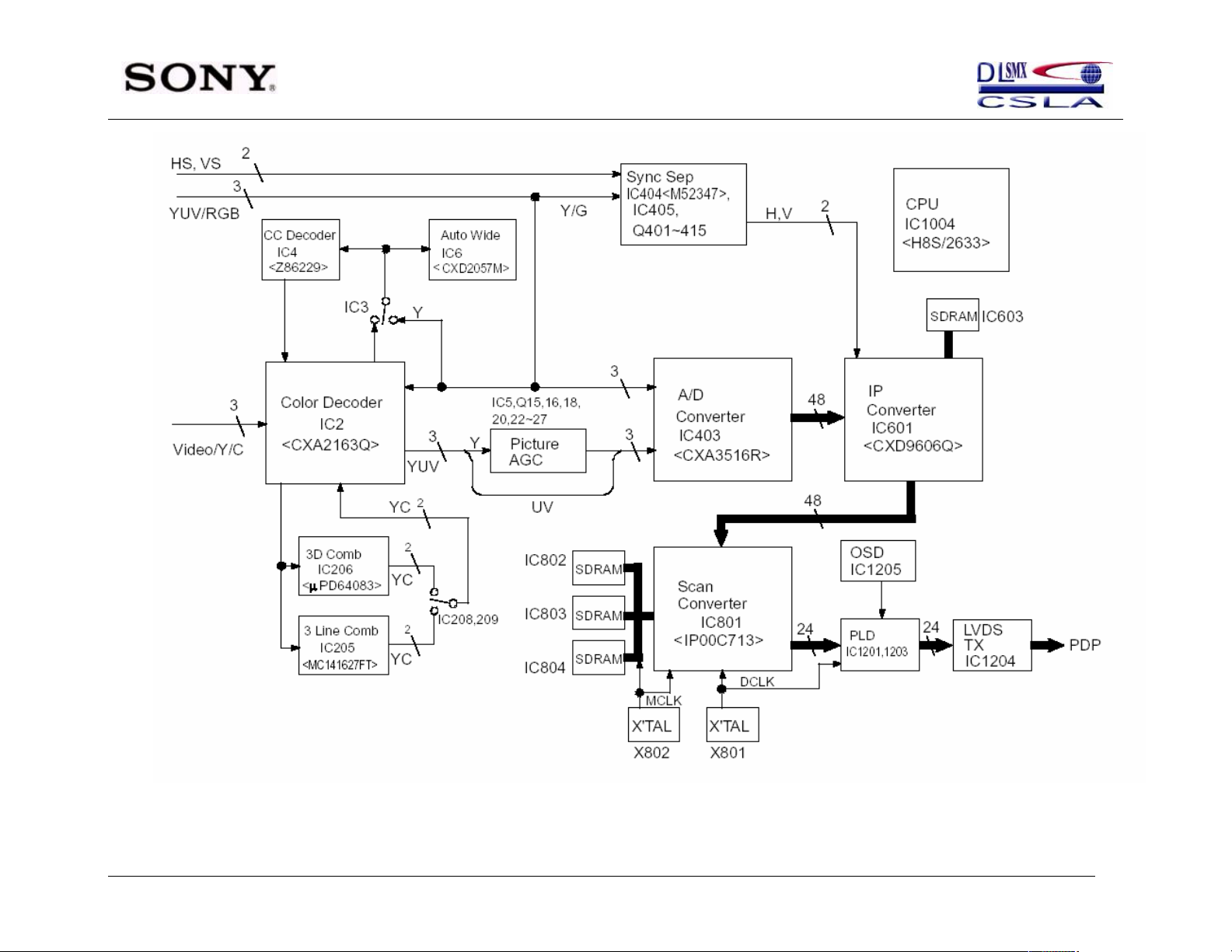

El diagrama a bloques general de la tableta B se muestra en la figura.

Hay señales YUV/RGB y compuestas/Y/C como señales de entrada de

la tableta B. La señal YUV/RGB es una señal de DTV o PC. La señal

de el sistema convencional de color para NTSC, PAL y SECAM es la

señal compuesta/Y/C. la señal compuesta/Y/C es decodificada a una

señal YUV usando un decodificador de color. Las señales YUV/RGB y

compuestas/Y/C son seleccionadas usando un switch en un

convertidos A/D.

En el convertidor A/D, las señales YUV y RGB pueden ser usadas. En

la etapa análoga, por lo tanto no es necesario convertir la señal YUV

en RGB. La señal convertida a digital usando el convertidor A/D es

entregada a el IC de sistema, donde una señal de interfase de 15 kHz

pasa por el convertidor IP y luego convertida en una señal

progresiva de 31.5 Khz. En el IC del sistema, la señal

RGB es directamente entregada sin ser convertida. La

señal procesada usando una señal YUV es procesada en

color, tinte, mejora de croma transitoria, y nitidez,

finalmente convertida en una señal de RGB, y entregada

en el scan converter de la siguiente etapa.

En el scan converter, la resolución es convertida de

acuerdo a la resolución de la PDP. Para una pantalla de

32 pulgadas, la resolución es entregada usando una señal

progresiva de 852 x 1024 puntos. Para una pantalla de 42

pulgadas, es entregada usando una señal progresiva de

1024 x 1024 puntos.

Debido a que el PDP es un panel entrelazado basado en

un sistema Alis, la señal progresiva del scan converter es

convertida a PI usando el PLD en la siguiente etapa. En

PLD, el OSD es insertado y una señal de prueba es

generada, en adición a la conversión PI.

La interfase de señal con el PDP es LVDS. Por lo tanto, la

señal de salida del PLD es introducida al transmisor

LVDS, convertida a LVDS y entregada al PDP.

Customer Services Latin América - 8 -

Page 10

Televisores de Plasma

Diagrama a Bloques de la tableta B

Customer Services Latin América - 9 -

Page 11

Televisores de Plasma

3.1.2. Bloque relacionado a la descodificación de color

El decodificador de color usa el CXA2163Q (IC2) el cual puede

decodificar NTSC, PAL, SECAM, NTSC443, PAL-M, PAL-N y PAL60.

El diagrama a bloques relacionado al decodificador de color es

mostrado en la figura. Hay varios switches en la figura. Las funciones

de estos switches son las siguientes:

SW1 y SW2 : Selecciona una señal de video compuesta y

señal Y/C. (a: Señal de video compuesta, b: señal Y/C)

SW3 y SW4 : Selecciona si separar las señales usando

una interrupción interna y un filtro pasa banda o el comb filter externo.

(a: interrupción interna y filtro pasa banda, b: Comb filter externo)

SW5 y SW6: :Selecciona un comb filter 3D y un comb filter

de 3 líneas (a:comb filter 3D, b:comb filter 3 líneas)

SW7, SW8 y SW9 : selecciona señales compuestas, Y/C y por

componentes (YCbCr). (a: compuesta y Y/C, b: componentes)

Customer Services Latin América - 10 -

Page 12

Televisores de Plasma

Diagrama a bloques de decodificador de color

Customer Services Latin América - 11 -

Page 13

Televisores de Plasma

El estado de estos switches para cada señal de entrada se muestra en

la tabla.

Por ejemplo una señal compuesta en el caso de NTSC es descrita a

continuación. SW1 y SW2 son puestos en posición “a”. La señal que

entra en el pin 1 del IC2 sale por el pin 3 y pasa a través de un

amplificador a 6 dB y de un filtro pasa bajas al comb filter 3D (IC206) y

el comb filter de 3 líneas (IC205). Para NTSC, un comb filter 3D es

usado. Por lo tanto las señales de salida de Y y C del comb filter 3D

son enviadas a través de un filtro pasa bajas nuevamente al

decodificador con los switches (SW5 y SW6) para la selección de

comb filter se pone la posición “a” (la señal Y es enviada de el pin 5 y

la señal Y de el pin 7). La señal de C es después decodificada usando

un bloque de proceso de croma para producir las señales Cb y Cr. La

señal de Y es enviada al bloque de proceso Y en el IC, y

simultáneamente, también entregado por el pin 11 a la salida de IC. La

señal resultante pasa a través del SW9 (IC3) puesto en posición “a” y

enviado al decodificador de closed caption IC4. una señal de RGB con

caracteres y su marco salen del decodificador de closed caption y

entran a los pines del 33 al 36 del decodificador de color. La señal de

caracteres en RGB es convertida en una señal TCbCr e insertada en

la señal de video.

SW1,2 SW 3,4 SW 5,6 SW

7,8,9

Y/C b a X a

NTSC a b a a

PAL a b b a

SECAM a a X a

NTSC443 a a X a

PAL-M a b b a

PAL-N a b b a

PAL60 a a X a

YCbCr X X X b

Estados de los switches para señales de entrada (X significa no

importa).

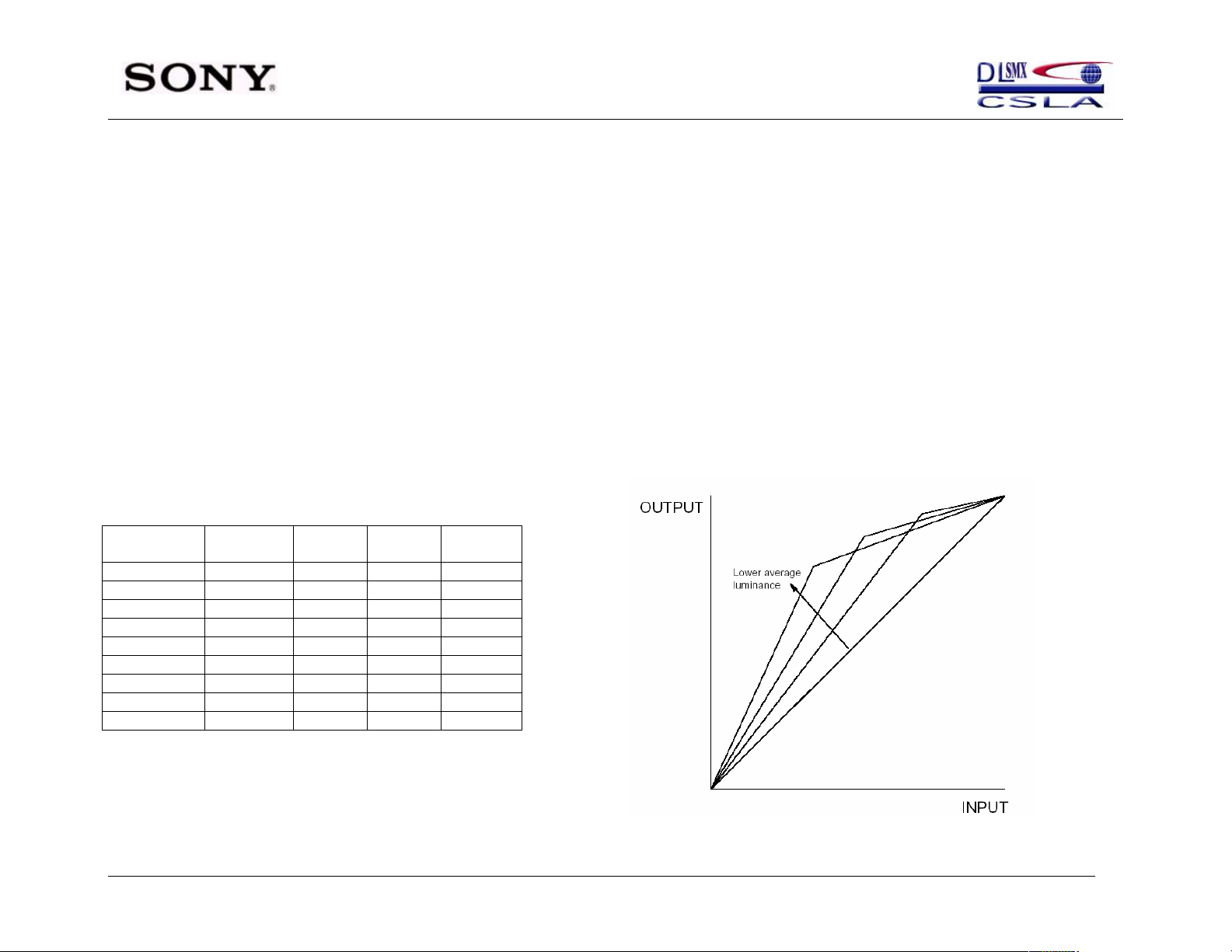

3.1.3.- Circuito de imagen dinámica

Incluso en una imagen de bajo contraste, un circuito de

imagen dinámica es instalado para mejorar los blancos y

negros y reproduce una imagen más clara y más obscura

con alto contraste. Esta función era realizada a través del

uso combinado de un circuito de extensión de negro con

un decodificador de color y un “circuito de imagen AGC”.

El circuito de imagen AGC consiste de IC5, Q15, Q16,

Q18, Q20, y Q22 a Q27. Este circuito detecta la

luminancia promedio de la imagen y dinámicamente

cambia una curva de gamma para que la luminancia de

un medio tono se incremente cuando la luminancia

promedio es baja. La curva de gamma es obtenida

controlando la inclinación de una línea poligonal y el punto

de rizo.

La figura muestra las características del circuito de

imagen AGC.

Customer Services Latin América - 12 -

Page 14

Televisores de Plasma

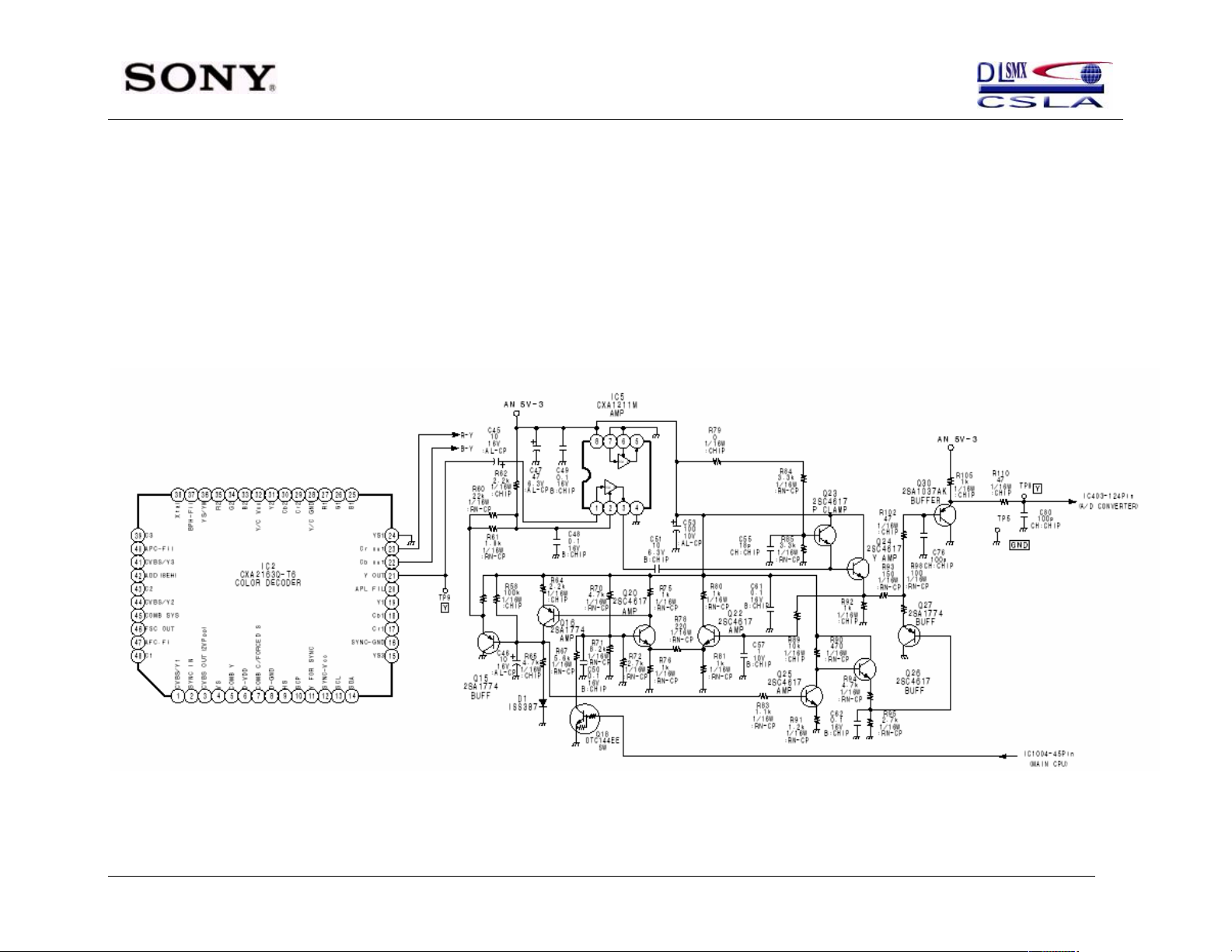

3.1.3.1. Características del circuito de imagen AGC

La operación del circuito de imagen AGC se describe a continuación.

La señal de entrada Y de el decodificador de color es ingresada a al

pin de entrada (pin 1) de el amplificador de control de ganancia IC5 y

sacado de el pin 3. La señal de entrada es sujeto al pedestal por

medio de Q23 y pasado a través de de el seguidor del emisor Q24. La

señal de salida de el Q24 es integrado usando R89 y C57 para

producir un voltaje de luminancia promedio y enviado a el comparador

de voltea usando Q22, Q20 y Q16. la señal es entonces enviada a

través de Q15 al pin de control de ganancia (pin 2) del IC5. en el ciclo

de campo trasero, la ganancia se incrementa cuando la luminancia

promedio decrece. La ganancia es 1 cuando la luminancia promedio

tiene suficiente luz. El voltaje de control de un comparador

de voltaje es enviado al circuito de control de línea

poligonal el cual consiste de Q25, Q26 y Q27. el punto de

rizo de una línea poligonal se vuelve bajo cuando la

luminancia promedio decrece. Como resultado, las

características mostradas en la figura son obtenidas al

controlar el amplificador de control de ganancia y el

circuito de control de línea poligonal usando un voltaje de

luminancia promedio.

Diagrama Esquemático de AGC

Customer Services Latin América - 13 -

Page 15

Televisores de Plasma

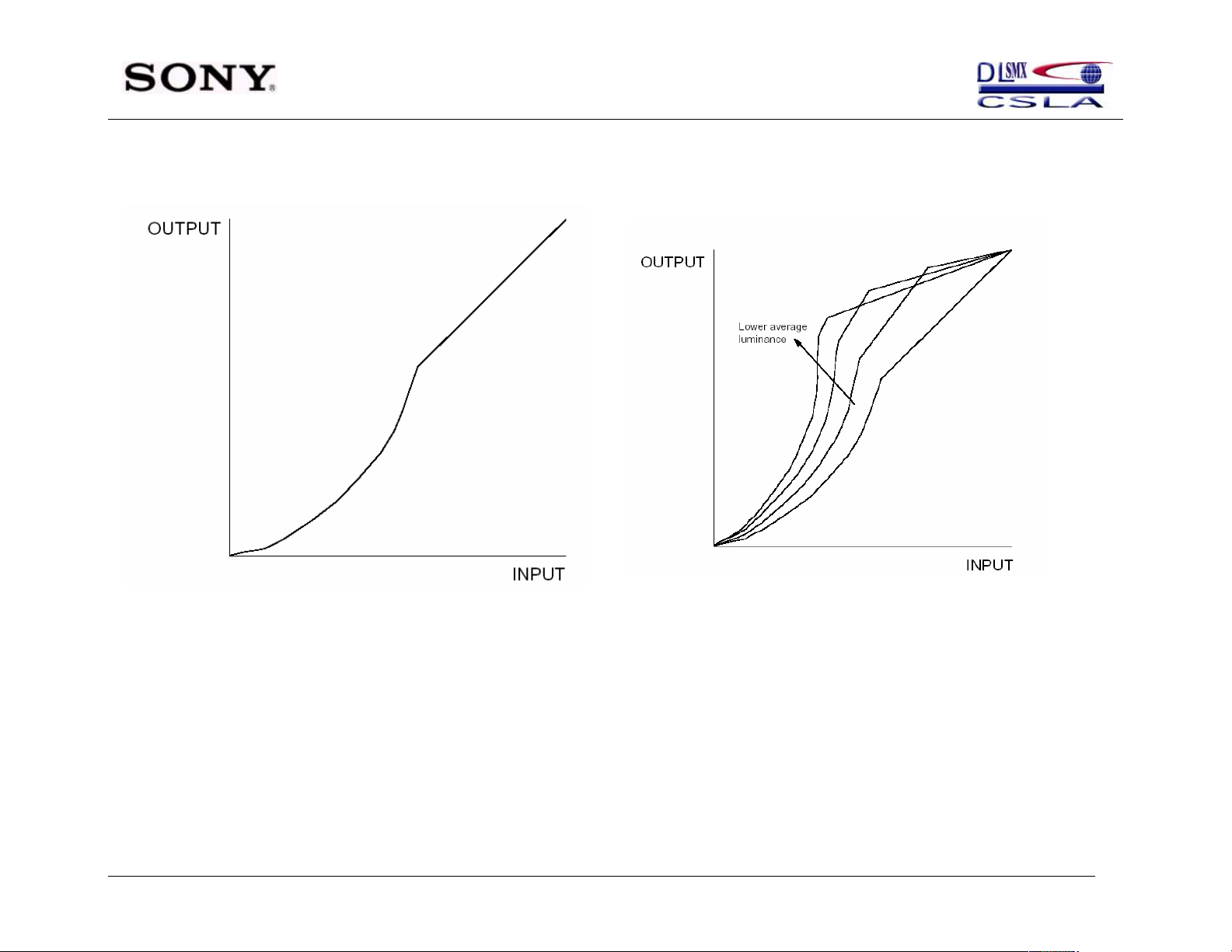

Las características del circuito de extensión de negro en un

decodificador de color se muestran en la figura.

Características del circuito de extensión de negros.

Las características de un circuito de imagen dinámica en

el cual el circuito de extensión de negros y el circuito

AGC son combinados se muestra en la figura.

Características del circuito de imagen dinámica

Customer Services Latin América - 14 -

Page 16

Televisores de Plasma

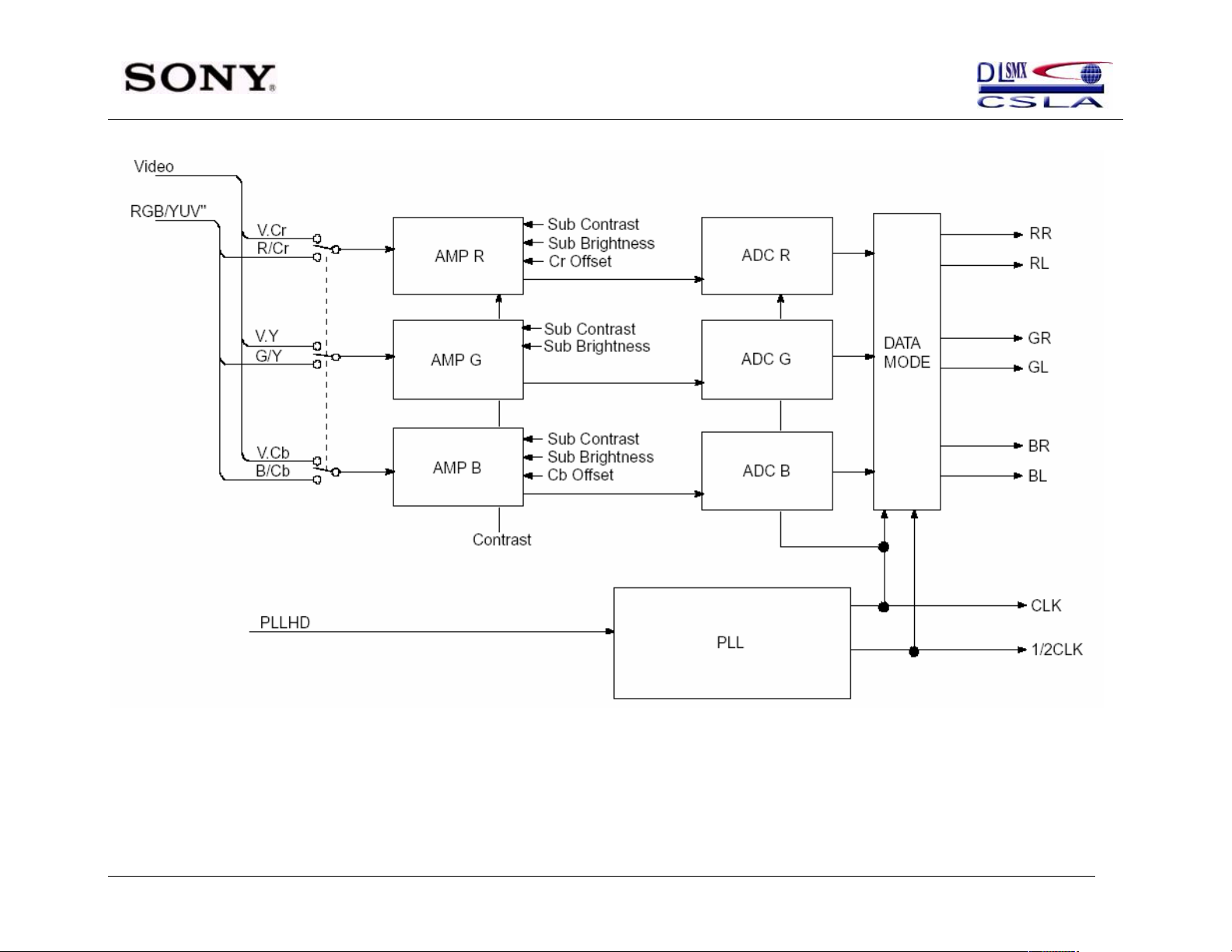

3.1.4.- Conversor A/D

El diagrama de bloque del convertidor A/D (IC403) es mostrado en la

figura. El convertidor A/D tiene 2 rutas de entrada. Este incorpora

switches de video de banda ancha. La señal de video que pasa a

través de un decodificador de color es enviada a la entrada 1 (pines

124, 133 y 139), y la señal RGB/YUV es enviada a la entrada 2 (pines

126, 136 y 141). Los amplificadores que pueden cambiar la ganancia o

la discriminación están incorporados en la etapa final de los switches

de video. Durante los ajustes de calibración AD, la ganancia y la

discriminación de los tres amplificadores son ajustados para que los

datos digitales de RGB en la etapa final PLD sean ordenados

correctamente. Las señales de video y RGB/YUV son convertidas A/D

después de pasar a través de estos amplificadores. En los 3 canales

hay salidas en 2 fases para producir datos digitales de 48 bits en total.

El convertidor A/D tiene un circuito interno PLL. Un reloj es generado

usando el circuito interno cuando el pulso de HD en una señal de video

es metido en los pines 111 y 112. ya que los datos digitales salen en 2

fases, un pulso de 1/” CLK es entregado por el pin 101 a el IC de

sistema en la etapa siguiente como un reloj.

Customer Services Latin América - 15 -

Page 17

Televisores de Plasma

Diagrama a bloque del Convertidor A/D

Customer Services Latin América - 16 -

Page 18

Televisores de Plasma

3.2.5.- IC del sistema

El diagrama de bloques del IC de sistema (IC601) es mostrado en la

figura. IC 601 ejecuta procesos tales como conversión IP, control de

color, control de matiz, control de detalle y separación digital de

sincronía. La señal digital de entrada es sujetada y enviada al “circuito

de matriz de entrada”, donde la señal digital no es convertida y

enviada al “circuito de mejora de croma transitorio” en la siguiente

etapa.

Si la señal de entrada es una señal RGB, esta no es procesada en el

circuito de mejora de croma transitoria e ingresado en el “circuito

selector de detalle en la siguiente etapa”. La señal de entrada tampoco

es procesada en el selector de detalle horizontal e ingresa en el

“circuito de matriz de salida en la siguiente etapa”. Además, la señal

de entrada no es procesada en la salida del circuito de matriz y es

entregada directamente. Para una señal de entrada RGB, en otras

palabras, ningún proceso es llevado fiera del IC del sistema, y las

señales son entregadas directo sin ningún procesamiento.

Si la señal de entrada es una señal YUV, el transitorio de croma es

mejorado. Una señal entrelazada de 15 KHz es ingresada en el

“circuito convertidor de entrelazado a progresivo/detalle V” para la

conversión IP y el detalle V y después ingresada en el “circuito de

detalle horizontal/selector” en la siguiente etapa para detalle H.

Las señales de entrada distintas a una entrelazada de 15KHz son

inmediatamente ingresadas al “circuito de detalle horizontal/selector”

para el detalle horizontal sin pasar por el “circuito convertidor de

entrelazado a progresivo/detalle V”.

La señal YUV que sale del “circuito de detalle horizontal/selector” es

convertida a RGB usando un “circuito de salida de matriz” en la

siguiente etapa. La matriz en el circuito matriz es una matriz de 3 x 3,

consultando 9 registros en total. El color y matiz puede ser controlado

calculando y cambiando estos valores usando una microcomputadora.

Customer Services Latin América - 17 -

Page 19

Televisores de Plasma

Diagrama a bloques de IC del sistema

Customer Services Latin América - 18 -

Page 20

Televisores de Plasma

3.1.6.- Scan Converter

En el scan converter (IC801), la resolución es convertida dependiendo

de la resolución del PDP. Para una pantalla de 32”, la resolución es

entregada usando una señal progresiva de 852 x 1024 puntos. Para

una pantalla de 42”, es presentada usando una señal progresiva de

1024x1024 puntos. El scan converter es controlado por muchos

registros internos y una microcomputadora.

Una señal de entrada es abastecida desde el IC del sistema en 2 fases

(42 bits). Sin embargo, la señal de salida del scan converter es

enviada al PLD de la siguiente etapa en una fase (42 bits). El reloj de

punto es de 65 MHz para una pantalla de 32” y 80 MHz para una de

42”.

El diagrama a bloque del scan converter se muestra en la figura.

Customer Services Latin América - 19 -

Page 21

Televisores de Plasma

Diagrama a Bloques del Scan converter

Customer Services Latin América - 20 -

Page 22

Televisores de Plasma

3.1.7.- Circuito de separación de sincronía

el diagrama de bloques del circuito de separación de sincronía se

muestra en la figura. El circuito de separación de sincronía IC404

(M52347) tiene un pin de entrada CS/HS externa (pin 6), pin de

entrada VS (pin 8) y un pin de entrada de sincronía encendida G/Y (pin

4). Para la señal de sincronía de salida (pines 13 y 14), una señal

externa tiene prioridad sobre una señal de encendido de sincronía G/Y

durante la salida. En IC404, la función de la separación de sincronía

de la señal de entrada de encendido de sincronía G/Y es ligeramente

baja para una señal de sincronía baja de 1080i o 720p. La

sincronización puede ser en algunas ocasiones desestabilizada. Por

eso, un circuito para reforzar el desempeño es insertado en la etapa

anterior. En este caso, la punta de sincronía es amarrada para corregir

el nivel DC. Además, la amplitud es ligeramente amplificada para

cortar la porción de video, y solamente la señal de sincronía es

ingresada en el circuito de separación de sincronía. Esto previene la

influencia de la fluctuación de APL de una señal de video o de una

macro-visión de 480p y permite una separación de sincronía estable.

Señales de sincronía externas de H y V corresponden a una amplitud

de 1 a 5 V, pero son ingresadas en el circuito de separación de

sincronía después de que la amplitud es establecida a

aproximadamente 0.6 V usando un circuito recortador.

En esta unidad, una señal de video compuesta puede ser usada como

una señal de sincronía. En este caso, una señal de video compuesta al

pin de H externa.

SW1, SW2 y SW3 se ponen en posición “b” cuando el modo de

sincronía es establecido en “señal de video”. Una señal de video

compuesta es entonces ingresada en el pin de encendido de sincronía

G/Y, unas señales de entradas externas CS/HS y VS se conectan a

tierra y no hay salida. En el circuito de separación de sincronía, las

señales de entrada de la señal de encendido de sincronía G/Y es

separada en sincronía y entregada.

Customer Services Latin América - 21 -

Page 23

Televisores de Plasma

Diagrama a bloques del circuito de separación de sincronía

Customer Services Latin América - 22 -

Page 24

Televisores de Plasma

3.1.8.- PLD

El diagrama a bloques del PLD (IC203) es mostrado en la figura. La

entrada de la señal de RGB es primero PI (Progresiva a Entrelazada)

usando un circuito [intl] e ingresado a un circuito [solo_azul] para

seleccionar solo el azul.

En la siguiente etapa en un circuito [siggen], una señal de prueba es

generada en el PLD y switcheada a una señal ordinaria.

La señal resultante e entregada al circuito [osd_ins], donde la señal de

OSD del OSD (IC205) es insertada. Finalmente, la señal es

blanqueada usando un circuito [blank_d1] y entregada a través de un

slip-flop tipo D. Un circuito [relieve] se comunica con la

microcomputadora. Este realiza cada operación de control de acuerdo

con la instrucción de la microcomputadora o lee el nivel de la señal de

RGB para enviar datos a la microcomputadora.

Un circuito [c_blk] genera una señal compuerta de blanqueo y pulsos

de blanqueo V.

Un circuito [osd_sync] genera una señal de tiempo de sincronía HV

requerida en el OSD.

Customer Services Latin América - 23 -

Page 25

Televisores de Plasma

Diagrama a bloques del PLD

Customer Services Latin América - 24 -

Page 26

Televisores de Plasma

3.1.9.- Señales de tiempo tales como reloj o señal de sincronía

El flujo de las señales de tiempo tales como reloj o señal de sincronía

se muestran en la figura.

En el bloque relacionado al decodificador de color, IC2 genera un reloj

Fsc basado en todos los sistemas de color usando el oscilador X1

(16.2 MHz).

El reloj Fsc generado es enviado al comb filter 3D (IC 206) y el comb

filter de 3 líneas (IC205).

Un circuito automático de ancho de banda (IC6) requiere un reloj 4Fsc

basado en NTSC. El reloj 4Fsc es suministrado por el oscilador X2

(14.3 MHz). Para PAL, IC6 también opera usando un reloj idéntico.

Las señales de tiempo de un convertidor A/D (IC403) son generadas

usando un PLL en un convertidor A/D y un DSS (Digital Sync

Separador) en el IC de sistema. Una señal de sincronía RGB/YUV (en

los pines 17 y 18) y una señal de sincronía de video/Y/C (en los pines

14 y 15) son entregadas al DSS para selección. Las señales

resultantes son separadas en señales H y V de sincronía puras

cuando una señal de entrada HCS (sincronía Horizontal o Compuesta)

es una señal compuesta. Como resultado un pulso de amarre para un

convertidor A/D es generado, entregado por el pin 3, y enviado al pin

113 de un convertidor A/D (IC403). Además, un pulso HD (PLLHD)

para PLL es generado, entregado en la salida del pin 4, y enviado a los

pines 111 y 112 del convertidor A/D (IC403 a el PLL interno. El reloj de

punto (CLK) del convertidor A/D es generado en este PLL. Como fue

descrito anteriormente, los datos son enviados en 2 fases, entonces el

reloj (DATACK) enviado al IC del sistema es entregado por el pin 101

como un 1/2CLK.

En el DSS, las señales de sincronía (SYS_HS y SYS_VS) para la

discriminación del sistema son también generadas, saliendo de los

pines 29 y 30 y enviados a la microcomputadora.

El reloj del IC del sistema (IC601) es suministrado usando un oscilador

X601 (70 MHz).

Este reloj es también usado como el reloj de un SDRAM externo. En el

generador de salida de la señal de tiempo en el IC de sistema, un reloj

(PICLK), señal de sincronía horizontal (PIHS), señal de sincronía

vertical (PIVS), y el pulso de discriminación de campo (PIFLD) son

generados e ingresados al scan converter en la siguiente etapa.

Hay X802 (80 MHz: 32”, 100 MHz: 42”) y X801 (65 MHz:

32”, 80 MHz: 42”) como un oscilador subministrado para

el scan converter. El oscilador X802 es usado para el reloj

de memoria, y el oscilador X801 es usado para la

generación de la señal de salida de tiempo.

La señal de oscilación de salida del X801 es directamente

enviada al pin 91 del PLD de la siguiente etapa como el

reloj de salida del scan converter. Debido a que, en el

PLD, la señal progresiva del scan converter es convertida

en una señal entrelazada, el reloj y la señal de sincronía

horizontal son divididas en frecuencia. En otras palabras,

la frecuencia de una señal PCLK se es la mitad de la

frecuencia de la señal POCLK, y la frecuencia de la señal

PHS es la mitad de la frecuencia de la señal POHS. PLD

también genera una señal de tiempo para el OSD (IC1205

y la suministra.

En el bloque relacionado al CPU, la señal de tiempo es

suministrada del oscilador X1002 (12.3 MHz) como un

reloj de CPU. El oscilador X1001 (32.8 KHz) es usado

para la oscilación del reloj de un contador interno.

Customer Services Latin América - 25 -

Page 27

Televisores de Plasma

Customer Services Latin América - 26 -

Page 28

Televisores de Plasma

3.2.- Funciones de la microcomputadora

H8S/2633 Ref IC1004 (Fabricado por Hitachi)

Funciones

Las funciones de control de una microcomputadora están

principalmente clasificados en 6 bloques.

1) Control de cada dispositivo por la salida I/O

2) Control del circuito de ventilador por la salida PWM

3) Detección del estado por la entrada A/D

4) Control del LED por la salida D/A

5) Control de cada dispositivo en el bus I2C

6) Control del scan converter por el bus serial de cuatro cables

La información requerida para cada control descrito a continuación es

leída desde un bus o in control de entrada y procesada por software.

La asignación de pines de la microcomputadora es mostrada en la

tabla a continuación.

Customer Services Latin América - 27 -

Page 29

Televisores de Plasma

# Puerto Función Nombre Explicación

1 PC0/A0 O PDP_CPU Panel del pin de señal de salida del panel CPU-GO H: On, L: Off

2 PC1/A1 O PDP_ACT Panel del pin de señal de salida del panel PDP-GO H: On, L: Off

3 PC2/A2 O SYSTEM_RESET Pin de salida de la señal de reset del equipo L:Reset

4 PC3/A3 O VIDE_MUTE Pin de señal de salida de la señal de mute de video H:Mute

5 Vss - Vss GND

6 PC4/A4 - - Sin Uso

7 Vcc - Vcc 3.3V

8 PC5/A5 - - Sin Uso

9 PC6/A6/PWM0 O PWM0 Pin del pulso de salida PWM para el drive de ventilador

10 PC7/A7/PWM1 - PWM1 Sin Uso

11 Vss - Vss GND

12 PB0/A8/TIOCA3 I POWER SW Pin receptor de la señal de encendido/apagado H:On, L:Off

13 PVcc1 - PVcc1 5V

14 PB1/A9/TIOCB3 O INPUT SELECT Pin de salida de selección de entrada H: pin RCA, L: pin D4

15 PB2/A10/TIOCC3 O LINE MUTE Pin de salida de la señal mute para una salida de audio externa

H: Mute

16 PB3/A11/TIOCD3 O AMUTE Pin de salida de la señal de mute de audio H: Mute

17 PB4/A12/TIOCA4 O LPF_SW Pin de salida de la señal de elección LPF H: A través, L: LPF

activo

18 PB5/A13/TIOCB4 I SIRCS Pin de recepción de código Sircs

19 PB6/A14/TIOCB5 O SC PLL SW Pin de la señal de entrada de Encendido/Apagado del PLL en el

scan converter H: On L: Off

20 PB7/A15/TIOCB5 - NC Sin Uso

21 PA0/A16 - - Sin Uso

22 PA1/A17/TxD2 O TXD2 (FWR) Pin de salida de datos (usado para escribir el software)

23 PS2/A18/RxD2 I TXD2 (FWR) Pin de entrada de datos (usado para escribir software)

24 PS3/A19/SCK2 - NC Sin uso

25 Vss - Vss GND

26 P10/PO8/TIOCA0 DACK0/A20 I - Pin de entrada de la señal de discriminación del panel

27 P11/PO9/TIOCB0 DACK1/A21 I - Pin de entrada de la señal de discriminación del panel

28 P12/PO10/TIOCC0 TCLKA/A22 O POWER Sin Uso

29 P13/PO11/TIOCD0 TCLKB/A23 I H:SYNC Pin receptor de sincronía H

30 P14/PO12/TIOCA1 IRQ0 I V.BLK Pin receptor de blanqueo V

31 P15/PO13/TIOCB1 TCLCKC I - Pin de señal de entrada de discriminación de modelo

Customer Services Latin América - 28 -

Page 30

Televisores de Plasma

32 P16/PO14/TIOCA2 PWM2/IRQ1 I - Pin de señal de entrada de discriminación de modelo

33 P17/PO15/TIOCB2 PWM3/TCLKD I V.SYNC Pin receptor de sincronía V

34 PE0/D0 I/O - Pin de prueba

35 PE1/D1 I/O - Pin de prueba

36 PE2/D2 I/O - Pin de prueba

37 PE3/D3 I/O - Pin de prueba

38 PE4/D4 O - Pin de salida se la señal de discriminación de 15 KHz durante la

entrada de RGB. Alto en 15 KHz.

39 PE5/D5 O - Pin de salida para habilitar la transmisión y recepción del bus

I2C. H: Habilitado

40 PE6/D6 O - Pin de salida de selección de la señal de modo de sincronía H:

video L: H/Comp

41 PE7/D7 O - Pin de salida de activación de Decodificador L: Activado

42 Vss - Vss GND

43 D8 O CC VID/YUV Pin de salida de selección de señal de closed caption H: vides L:

YUV

44 PVcc1 - PVcc1 5V

45 D9 O PICTURE AGC Pin de salida de Encendido/Apagado de la señal de imagen

dinámica H: OFF, L: On

46 D10 O NTSC/PAL Pin de salida de la señal de discriminación NTSC/PAL H: NTSC

L: PAL

47 D11 O COL SYS N/M Pin de salid ad e la señal de discriminación de color H: NT/PAL

L: N/M

48 D12 O VEH1 Pin de salida de la señal de control del comb filter de tres líneas

49 D13 O VEH2 Pin de salida de la señal de control del comb filter de tres líneas

50 D14 O VEH3 Pin de salida de la señal de control del comb filter de tres líneas

51 D15 O COMF SW Pin de salida de selección de comb filter H: 3D, L: 3L

52 P30/TxD0/IrTxD - - Sin Uso

53 P31/RxD0/IrRxD I/O SDA_LS Pin de envío/recepción de los datos del bus I2C (usado para

baja velocidad)

54 PVcc2 - PVcc2 5V

55 P32/SCK0/SDA1 IRQ4 O SCL_LS Pin de salida del reloj del bus I2C (usado para baja velocidad)

56 Vss - Vss GND

57 P33/TxD1/SCL1 I/O SDA_HS Pin de envío/recepción de datos del bus I2C (usado para alta

velocidad)

58 P34/RxD1/SDA0 O SCL_HS Pin de salida de reloj del bus I2C (usado para alta velocidad)

59 P35/SCK1/SCK4 SCL0/IRQ5 O TU_CLK Pin de salida del reloj serial para el tuner de la

Customer Services Latin América - 29 -

Page 31

Televisores de Plasma

microcomputadora

60 P36/RxD4 I TU_RX Pin de recepción de datos seriales para el tuner de la

microcomputadora

61 P37/TxD4 O TU_TX Pin de envío de datos seriales para el tuner de la

microcomputadora

62 PG0/CAS/IRQ6 O . Pin de envío de señal de interrupción para el tuner de la

microcomputadora

63 PG1/CS3/OE/IRQ7 O SOG DUTY2 Pin de salida de la señal de control de deberes de la señal de

sincronía

64 PG2/CS2 O SOG DUTY1 Pin de salida de la señal de control de deberes de la señal de

sincronía

65 PG3/CS1 I H STATUS Pin de discriminación de la polaridad de sincronía H

66 PG4/CS0 I V STATUS Pin de discriminación de la polaridad de sincronía H

67 WDTOVF O WDTOVF Pin de salida de sobre flujo de la señal de WDT

68 PLLVCC - PLLVCC Pin de poder para el oscilador interno PLL (3.3V)

69 PLLCAP - PLLCAP Pin de capacidad externa para el oscilador PLL interno

70 PLLVSS - PLLVSS Pin de aterrizaje para el oscilador PLL interno

71 RES I RES Pin de entrada de la señal reset L: Reset

72 NMI I NMI Sin Uso

73 STBY I STBY Sin Uso

74 FWE I FWE Pin de entrada de habilitación de escritura flash

75 XTAL I XTAL Pin de entrada de la señal del cristal de oscilación

76 Vcc - Vcc 3.3 V

77 EXTAL I EXTAL Pin de entrada de la señal del cristal de oscilación

78 Vss - Vss GND

79 OSC1 - OSC1 Sin Uso

80 OSC2 - OSC2 Sin Uso

81 PVcc1 - PVcc1 5V

82 PF7/É” - - Sin Uso

83 Vss - Vss GND

84 AS/LCAS O TUNER RESET Pin de salida la señal de reset del tuner de la microcomputadora

L: Reset

85 RD O RGB3 Sin Uso

86 HWR O CONT1 Sin Uso

87 PF3/LWR/ADTRG IRQ3 I NC Pin de detección instantánea de 5V digitales

88 PF2/LCAS/WAIT BREQ0 - NC Sin Uso

89 PF1/BACK/BUZZ ¡ NC Pin de detección de ventilador detenido H: Stop

Customer Services Latin América - 30 -

Page 32

Televisores de Plasma

90 PF0/BREQ/IRQ2 O RTC-IRQ Pin de salida de la señal de interrupción de reloj de tiempo real

91 AVcc - AVcc 5V

92 Vref I VREF Pin de entrada del voltaje de referencia para los convertidores

A/D y D/A (5V)

93 P40/AN0 A/D - Sin Uso

94 P41/AN1 A/D - Sin Uso

95 P42/AN2 A/D - Pin de detección de aspecto del pin D

96 P43/AN3 A/D - Sin Uso

97 P44/AN4 A/D - De detección del switch de control

98 P45/AN5 A/D - Sin Uso

99 P46/AN6/DA0 D/A - Pin de control del LED Verde

100 P47/AN7/DA1 D/A - Pin de control del LED Rojo

101 P90/AN8 A/D - Sin Uso

102 P91/AN9 A/D - Pin de detección del voltaje de drive del ventilador

103 P92/AN10 A/D - Pin de detección de 5V digital

104 P93/AN11 A/D - Pin de detección de 3.3V digital

105 P94/AN12 A/D - Pin de detección de 6V análogos

106 P95/AN13 A/D - Pin de detección de temperatura en la tableta de fuente

107 P96/AN14/DA2 - - Sin Uso

108 P97/AN15/DA3 - - Sin Uso

109 A vss - A vss GND

110 P70/TMRI01/TMCI01/DREQ0 CS4 - - Sin Uso

111 P72/TMTI23/TMCI23/DREQ1/CS5 O RTC_CS Pin de selección del chip de reloj de tiempo real

112 P72/TMO0/TEND0 CS6/SYNCI O OSD_CS Pin de selección del chip OSD

113 P73/TMO1/TEND1 CS7 O PLD_CS Pin de selección del chip PLD

114 P74/TMO2/MRES O SC_CS Pin de selección del chip de scan converter

115 P75/TMO3/SCK3 O 4W_CLK Pin de salida del reloj de bus de datos serial de cuatro cables

para SC

116 P76/RxD3 I 4W_RX Pin receptor de datos del bus serial de cuatro cables para SC

117 P77/TcD3 O 4W_TX Pin de envío de datos del bus serial de cuatro cables para SC

118 MD0 I MD0 Pin de selección de modo de operación MPU

119 MD1 I MD1 Pin de selección de modo de operación MPU

120 MD2 I MD2 Pin de selección de modo de operación MPU

Customer Services Latin América - 31 -

Page 33

Televisores de Plasma

3.3. Scan Converter

IP00C714 Ref IC801 (Fabricado por i-chips)

3.3.1. Perfil

Este Scan Converter es un LSI que expande y reduce el color de la

imagen en tiempo real. Un controlador de memora que usa SDRAM

como un marco de memoria, un filtro interpolado de cuatro símbolos

usado para expansión y reducción, y una memoria lineal están

integrados en un chip.

Las señales de entrada y salida de imagen contienen un reloj

independiente y una señal de sincronía. Estos operan de forma

independiente y asincronía. Una interfase serial de cuatro alambres es

usada para controlar el scan converter.

3.3.2. Configuración

Este Scan converter esta dividido en un bloque de interfase con el

CPU, un bloque de interfase de memoria para almacenamiento de

imagen, un bloque de reducción de entradas de imagen, un bloque de

expansión de salidas de imagen, y un bloque de control de bus interno.

Customer Services Latin América - 32 -

Page 34

Televisores de Plasma

Customer Services Latin América - 33 -

Page 35

Televisores de Plasma

3.3.3. Bloque de interfase de CPU

El bloque de interfase de CPU recibe señales (SCLK al pin 252, SS al

pin 253, SI al pin 254, y SO al pin 1) desde una microcomputadora y

controla el acceso a un registro interno. Este bloque es usado como

una interfase serial de cuatro cables. Esto hace un registro de acceso

en sincronización con un reloj SCLK (reloj serial) cuando el pin SS

(selección de chip) es establecido en bajo.

3.3.4. Bloque de interfase de memoria para almacenamiento de

imagen

El bloque de interfase de memoria para almacenamiento de imagen

entrega datos al bus de memoria de almacenamiento de imágenes de

acuerdo con las instrucciones de un control de bus interno o lee una

señal de entrada del bus de memoria de almacenamiento de

imágenes. Este bloque opera con la señal MCLK (pin 97) como reloj.

El SDRAM K4S161622D (IC802, IC803, e IC804)(Samsung) es usado

como memoria, y una memoria de marco de 6 Mb en total es

constituida en unidades de 2 Mb por color (R,G,y B).

3.3.5. Bloque de entrada/reducción de imagen

El bloque de entrada/reducción de imagen lee los datos de un puerto

de entrada de imagen en unidades de campos de acuerdo al comando

del CPU y los reduce. Después de eso, este bloque los solicita al

bloque de bus de control interno, de acuerdo con una entrada de buffer

de datos, cuyos datos de entrada son transferidos a la memoria de

almacenamiento de imagen. Este bloque opera con la señal PICLK

(pin 248) como un reloj.

3.3.6. Bloque de salida/expansión de imagen

El bloque de salida/expansión de imagen las solicita al

bloque interno de bus de control, de acuerdo al estado de

una salida del buffer de datos, cuyos datos a la salida son

transferidos a la memoria de almacenamiento de

imágenes al puerto de salida y luego expande los datos

de salida. Este bloque opera con la señal PLOCK (pin

109) como un reloj. El bloque de entrada y salida de

imagen pueden operar simultáneamente.

Bloque de ajuste de calidad de imagen.

El bloque de ajuste de calidad de imagen enfatiza los

límites de las imágenes (en dirección horizontal) con

respecto a la calidad de la imagen.

3.3.7. Bloque de control de bus interno

El bloque de control de bus interno alinea el bus de

almacenamiento de memoria de imagen de acuerdo a la

salida de señal de demanda del bus de cada bloque y

genera la dirección de memoria de almacenamiento de

imagen requerida.

En el circuito de alineación del bus, el buffer de

entrada/salida de imagen no llega a sobre flujo ni a

subflujo incluso si los puertos de entrada y salida operan

simultáneamente. En este caso, no es necesario aplicar

peso a la entrada y salida de datos de imagen de cada

puerto de imagen.

Este bloque opera con la señal MCLK (pin 97) como reloj.

Customer Services Latin América - 34 -

Page 36

Televisores de Plasma

4. Tarjeta Q

4.1 Descripción de la operación del circuito de la tarjeta Q.

El diagrama a bloques de la tarjeta Q se muestra en la figura.

El selctor de función de RGB /YUV es el primer bloque se describe.

Las señales componente 1 y componente 2/RGB entran y son

seleccionadas por medio del IC3001 selector de video y son enviadas

a una filtro pasa bajos por la limitación de banda de las señal YUV.

Las señales que pasan y las que no pasan a través del filtro pasa

bajos son seleccionadas por medio del selector de video IC3011 y

enviadas hacia la tarjeta B.

La señal de sincronía externa de una señal RGB/YUV es montada

usando D3003 y D3004 y es sacada hacia la tarjeta B para solo una de

las señales componentes 2/RGB usando un interruptor de sincronía

en la siguiente etapa.

El selector de función, de una señal de video de 25 Khz. es descrito a

continuación. Las señales de Sintonización, video 1/YC1 y video YC2

son seleccionadas usando un interruptor de AV IC3014 y son enviadas

a la tarjeta B.

En el selector de funciones de señal de audio, las tres señales de

audio contenidas en 15khz de la señal de video son seleccionadas

usando un interruptor de AV IC3014 y son enviadas al interruptor de

audio IC3016. En el IC 3016 la señal COMP1, COMP2/RGB y las tres

señales de audio contenidas en la señal de video de 15khz son

seleccionadas.

La señal de salida de audio sale a través de un reforzador IC3015 y

después es enviada desde el IC3006.

La señal de audio seleccionada usando el IC3006 es enviada la

IC2003. La señal es procesada como trusurround cuando le modo de

surround es puesto en “TS”. La señal procesada es enviada hacia el

preamplificador IC2002, en donde se controlan tanto el volumen ,

balance, bass y treble y en donde los modos hall y simulate son

procesados en el modo surround.

Las señales del canal Izquierdo y derecho que salen del

preamplificador, son enviadas hacia los amplificadores de

poder IC2002 y IC2001. Estos amplificadores de poder

son clase D. Las señales L y R son moduladas de PWM a

una señal triangular de aproximadamente 100KHz y

después son sacadas. Estas mismas señales, son

pasadas a través de un filtro pasa bajos en la siguiente

etapa como una señal análoga de audio para que pueda

manejar las bocinas.

Las señales L y R que salen del amplificador son

enviadas simultáneamente hacia el amplificador de señal

para audífonos IC3010, y la señal de salida es conectada

a la terminal para los audífonos.

Además una suma del canal izquierdo y el canal derecho

proveniente del amplificador es conectada a la terminal de

salida del sub-woofer a través de un filtro pasa bajos

IC3016. El circuito de control de giro del ventilador esta

también montada en la tarjeta Q.

Customer Services Latin América - 35 -

Page 37

Televisores de Plasma

Diagrama a Bloques de la tableta Q

Customer Services Latin América - 36 -

Page 38

Televisores de Plasma

4.2 Diseño del bloque Q

4.2.1 Configuración del circuito de la tarjeta Q

El bloque Q de la KZ42TS1, consiste en una interfase de entrada y

salida bloque de audio, bloque de video y control de FAN. La tarjeta Q

selecciona una señal de entrada como el bloque de video. Esta es

completada en el bloque Q como en el bloque de audio. La tarjeta Q

ejecuta todas las funciones de audio desde que se

selecciona una señal de entrada hasta que se saca esta.

4.2.2 Diagrama a bloques de la tarjeta Q.

La figura muestra el diagrama a bloques funcional de la

tarjeta Q.

Diagrama a bloques funcional de la tableta Q

Customer Services Latin América - 37 -

Page 39

Televisores de Plasma

4.3 Operación del circuito, descripción de cada bloque.

La operación del circuito es descrita a continuación.

4.3.1 Interfase de entrada y Salida

La tarjeta Q es también usada como tarjeta terminal. Esta contiene

tolas las terminales de entrada y salida. Las terminales de entrada de

Audio y video tienen dos canales de video compuesto con una terminal

S, un canal por componentes( terminal CA) y una por componentes

separadas (RCA). Una salida de audio( Mezclada)y la terminal de

salida de Sub woofer y esta destinada para usarse como salida. Una

terminal bidireccional de control S esta también presente. La figura

muestra la ubicación de cada terminal en la tarjeta.

Arreglo de terminales

4.3.2. Bloque de video

En el bloque de video la tarjeta Q tiene la función de seleccionar las

señales de entrada.

La figura tres muestra el diagrama a bloques del proceso de video. En

esta unidad, la ruta de la señal varia dependiendo de las señales de

entrada ya sea compuesta, S video o por componentes separadas

como lo muestra la figura 4.La operación del circuito de video es

descrita abajo para cada ruta.

Customer Services Latin América - 38 -

Page 40

Televisores de Plasma

Diagrama a bloques de la señal de video

4.3.2.1 Entrada se señal compuesta de video.

Una de las señales compuestas de video (Video1 y video 2) que entra

por J3000 y la señal compuesta TUNER-VID(Introducida por el

CN3004) proveniente de la tarjeta del tuner es seleccionada usando el

interruptor IC3014. La señal seleccionada es sacada por la terminal 40

Customer Services Latin América - 39 -

del IC3014. El IC 3014 tiene internamente un amplificador

de video a 6 bB.

La señal que sale por la terminal 40 es amplificada en 6

dB. Por tanto, la señal que sale por la terminal 40 es

atenuada en –6dB usando un divisor de voltaje formado

por R3205 y R3206 para dar una ganancia total de 0dB.la

señal atenuada es reforzada usando el emisor seguidor

Page 41

Televisores de Plasma

Q3027 y esta es sacada por le conector CN3001(VID_SIG en la

terminal 10) hacia la tarjeta B.

El IC 3014 es un interruptor de TV de Audio / video de 5 entras dos

salidas que es de acuerdo al estándar de 2S. En esta unidad, EL

IC3014 es usado para la sección de la señal de entrada de video1/2

señal compuesta, señal Y/S(Terminal de entrada S), salida de tuner y

la señal de audio como se muestra en la figura 3. también el IC 3014se

comunica con la microcomputadora IC1004 en la tarjeta B usando para

esto el bus I2C para operaciones de control.

El funcionamiento del circuito de señal Y/C y audio será descrita mas

adelante.

4.3.2.2 Señal de entrada Y(C (terminal S).

Una de las entradas de señal de video1/2 Y/C provenientes del

conector S terminal de conector J3000, es seleccionado usando el

selector de AVIC3014. La señal y seleccionada, es sacad por la

terminal 43, y la señal seleccionada C es sacada por la terminal 45.

las salidas son amplificadas 6dB y después atenuadas –6dB de la

misma manera que la señal compuesta de video. La señal Y es

reforzada usando un emisor seguidor Q3026, y la señal c es reforzada

usando Q3025. Después de esto las señales obtenidas son sacadas

por le conector CN3001(Y_SIG por la terminal 8 para Y y por la

terminal 6 C_SIG para la señal C) hacia la tarjeta B.

La señal de salida es abierta cuando la termina S no esta conectada.

Una señal en la terminal 7 del IC3014 es internamente llevada a 5V.la

señal es detectada como una señal del tipo S(Y/C) cuando esta es

menor que 3.5V. esta es detectada como una señal compuesta de

video cuando el voltaje es a mayor que 3.5V. La detección que resulta,

es escrita en un registro de estado y es enviada a través del Bus I2C

hacia la microcomputadora.

La señal de DC, conforme al estándar 2S, sumada la señal C es

detectada en la terminal 6 del IC3014. el resultado de la detección es

escrita en un registro de estado y enviado a través del bus I2C hacia la

microcomputadora en la tarjeta B.

4.3.2.3.Entrada de señal por componentes.

En esta unidad, la entrada de señal compuesta esta

conformada por 2 entradas Y /Cb / Cr y R/G/B/H/VD, esta

también corresponde a la sincronía en la señal G.

La señal seleccionada, es sacada por la terminal 31. La

conmutación del IC 3001 es controlada por la señal

INPUT_SEL( Que entra por la terminal 23 del CN3003)

desde la microcomputadora.

Como se muestra en la figura 3 la señal seleccionada

usando el IC 3001 se comparte en dos rutas diferentes.

Una es directamente introducida al seleccionador de

video IC 3011 en la siguiente etapa. La otra es introducida

al IC3011 a través de un Filtro pasa bajos constituido por

el Q3015.

Cuando la señal de entrada es Y componente de color por

diferencia pasa por un filtro pasa bajos es seleccionada

usando IC3011. La conmutación del IC3011 es controlada

por medio de por la señal de control LPF( Introducida por

la terminal 20 del CN3003) proveniente de la

microcomputadora. La señal seleccionada es sacada por

la terminal 31 del IC 3011 y después es sacada por la

terminal 4 (G/Y) del conector CN3002 hacia la tarjeta B.

Las señales de sincronía (HD y VD) introducida por el

J3011 es metida al selector IC3007 y sacada desde el

CN3002(DSUB_H por la terminal 8 y DSUB_V en la

terminal 10) hacia la tarjeta B durante la entrada del la

señal RGB y selección.

Customer Services Latin América - 40 -

Page 42

Televisores de Plasma

4.3.3 Bloque de Audio.

En esta unidad, otras funciones como la terminal de salida audífonos

es completada en la tarjeta Q como si fuera el bloque de Audio. El

bloque de audio ejecuta también todas las señales de audio desde

que entra hasta que sale esta. La figura muestra el diagrama a

bloques del seguimiento de una señal de audio.

Customer Services Latin América - 41 -

Page 43

Televisores de Plasma

Diagrama a bloque de la señal de audio

Customer Services Latin América - 42 -

Page 44

Televisores de Plasma

Una de las señales de audio que viene de un equipo externo, y la

señal de audio del sintonizador es seleccionado por medio de dos

selectores. La señal seleccionada es compartida por dos rutas. Una de

estas es reforzada y sacada por la terminal de audio. La otra es

introducida al circuito de surround como las señales de las bocinas y

los audífonos. La señal de salida que viene del circuito de surround es

ajustada en volumen y calidad usando el procesador de audio.

Compartiéndolo en las rutas de las bocinas, sub_woofer y audífonos.

La señal que sale del procesador de Audio, es reforzada o amplificada

y después es sacada. Los bloques son descritas para cada función en

la parte de abajo.

4.3.3.1 Circuito de selección de entrada.

La señal entrada de video ½ es introducida por J3000 y la señal

sacada proveniente del sintonizador es introducida al interruptor de AV

IC3014 con el fin de seleccionar una de las señales. La señal

seleccionada (VID_L) es introducida la selector de Audio IC3006.

La señal de entrada componente de entrada 1 que se introduce por

J3004 y la señal de audio de entrada de componentes 2 introducida

por J3002 son introducidas el IC3006. El IC 3006 selecciona una de

las señales de audio componentes de entrada y la señal resultante se

saca por lC3014. La señal Seleccionada se comparte en dos rutas.

Una es sacada hacia las bocinas y los audífonos y la otra es sacada

hacia un canal de salida de audio. El Seleccionador de audio IC3006

es controlado a través del Bus I2C por medio de la microcomputadora

que se localiza en la tarjeta B.

4.3.3.2 Circuito de salida de Audio.

La señal que sale por las terminales 14 y 15 del conmutador de audio

IC3006, es reforzado usando el IC3015 es sacada por medio de la

terminal de salida de Audio (J3008). Los transistores Q3032 y Q3033

en la sección de salida del IC3015 son el circuito de silenciamiento de

las terminales de audio.

La base de los transistores silencia con un nivel alto (

aproximadamente 10V). La señal que viene de la terminal

de salida, es sacada sin la conversión del nivel de la señal

seleccionada.

La señal que se encuentra en la terminal de salida es

silenciada cuando la señal de control de la

microcomputadora(LINE_MUTE) es puesta en nivel alto

cuando el voltaje de alimentación (AN_+12V) cae o se

incrementa. LINE_ MUTE y AN_+12V son introducidas a

un circuito de silenciamiento formado por Q3028 y Q3029.

La señal de entrada que viene del D3075, es puesto en

alto para silenciar la señal de salida de audio, cuando la

señal de silenciamiento LINE_MUTE es puesta en alto y

cuando la alimentación AN_12V cae o se incrementa.

4.3.3.3. Circuito de TruSurround.

La señal de audio que es introducida, seleccionada y

sacada por la terminal 12 t 13 del IC3006, es sacada a

través del circuito de la sección de volumen del

procesador de TruSurround el IC2003. La señal de audio

introducida en el IC2003, es procesada en Surround en el

IC2003 cuando el modo de Surround es puesto en

TruSurround. Cuando un modo que no sea TruSurround

es puesto, la señal de entrada es solo pasada en el

IC2003.

El IC2003, el sonido se incrementa mas acústicamente

que en otro modos cuando una señal de entrada es

amplificada en modo de TruSurround y es sacado

directamente.

Por lo tanto el sonido es atenuado causando un circuito

de selección de sonido (Formado por Q2004 y Q2005).

En la etapa de formación del IC2003 de esto el volumen

del sonido en el modo TruSurround es el mismo que en

otros modos.

La selección del modo de Trusurround del IC2003 es

controlado usando la señal de salida del DAC(de la

Customer Services Latin América - 43 -

Page 45

Televisores de Plasma

terminal 24 del IC2000) y es introducida en la terminal 2. El modo del

TruSurround es seleccionado cuando la terminal 2 es puesta en alto

(9V). El circuito de selección del volumen de sonido es también

controlado usando el la señal de salida del DAC ( Terminal 24 del

IC2000) y se introduce al Q2004 y Q2005.

4.3.3.4. Procesador de Audio.

El IC2000 es un procesador de audio. El procesador de audio ajuste el

volumen, tone y balance. Esto también tiene muchos circuitos de

surround internos. En esta unidad, el proceso de Surround es

realizado en el IC 2000, cuando simula y cuando pone los modos de

salón (Hall). IC2000 es controlado por medio del bus I2C por medio de

la microcomputadora en la tarjeta B. Una señal en la terminal 24 es la

salida del DAC (colector abierto) señal de I2C. En esta unidad , esta

señal de salida es usada para controlar el procesador de TruSurround

IC2003 y la sección de volumen.

Las señales Izquierda y derecha que se sacan del IC2003 son

introducidas a los pines 6 y 7 del IC2000. La entrada de señales de

audio son procesadas en volumen tono y balance y surround usando

IC 2000 es son sacadas por las terminales 20 y 19. Las señales de

salida son introducidas al amplificador de salida de Audífonos y al

amplificador de Audio en la siguiente etapa. Las señales L+R

procesadas en volumen es sacada por la terminal 22 parta el

Sub_Woofer.

4.3.3.5 Amplificador de Audífonos.

Las señales Izquierda y Derecha sacadas del IC 2000 son introducidas

a través de un circuito de Silenciamiento al amplificador de audífonos

IC3010. La señal amplificada usando IC3010 es sacada por

CN3010(terminal 1 HP_L, y terminal 2 HP_R) hacia la tarjeta H1,

donde la señal de salida es introducida a través de un circuito de

Silenciamiento desde del conector de salida de los audífonos.

La señal de audífonos es silenciada en la tarjeta fuente de la señal y

secciones anteriores al amplificador de Audífonos.

En la tarjeta Q, la señal en la tarjeta fuente en el

amplificador de audífonos es silenciada. Q3037 y Q3038

son encendidos y silenciados usando la señal de salida

desde un circuito de control de silenciamiento. La

operación del circuito de control silenciamiento se

describirá después.

4.3.3.6 Amplificador de Audio.

Las señales Izquierda y derecha sacadas del IC2000 son

introducidas al amplificador principal de audio IC2001 y

IC2002. Las señales de los canales Izquierdo y derecho

son amplificadas usando cada amplificador. Las señales

son entonces sacadas a través de un filtro LC del CN3007

hacia las bocinas de los canales Izquierdos y Derechos.

Los amplificadores principales de Audio IC 2001 e

IC2002 son amplificadores digitales. La señal análoga

proviene de la terminal 11 y es una señal interna

modulada en PWM y es amplificada a una señal PWM de

aproximadamente 26 VP-P y aproximadamente sobre una

portadora de 120KHz. La señal amplificada es sacada por

la terminal 4. Las señales que salen del amplificador son

enviadas al filtro LC que es un filtro pasa bajos en la

siguiente etapa para eliminar la componente portadora y

es introducida hacia las bocinas para reproducir el

sonido.

Los amplificadores de poder tiene un circuito de

silenciamiento interno. El silenciamiento es cancelado

cuando en la terminal 12 existe un voltaje mayor a 4V. El

modo de silenciamiento es activado cuando en la terminal

12 se tienen de 1.8V a 2.5V. La señal de silenciamiento.

SP_MUTE es sacada desde el circuito de control de

silenciamiento y en la sección de detección de señal de

audífonos HP_SW de la tarjeta H1 es introducida a la

terminal 12. La terminal 12 del IC2001 e IC2002 son

puestas a nivel de tierra cuando la terminal SP_MUTE

que viene del circuito de control es puesta en

alto(Aproximadamente 10V). La señal de salida de las

Customer Services Latin América - 44 -

Page 46

Televisores de Plasma

bocinas es en este momento silenciada. La terminal 12 llega

aproximadamente a 2.5V cuando la señal de detección de audífonos

es puesta en alto (5V). Y después de esto las bocinas son silenciadas.

4.3.3.7 Salida de Sub_Woofer.

La señal izquierda y derecha que es sacada por la terminal 22 del

IC2000 es filtrada y reforzada usando un filtro pasa bajos formado por

IC3016 que es un amplificador operacional. La señal reforzada del

sob-woofer es sacada a través del circuito de silenciamiento Q3036 y

Q3039 proveniente de la terminal de salida de Sub-woofer en J3011.

Q3036 es controlado por medio de la señal de salida SP_MUTE

proveniente del circuito de silenciamiento. Esta es silenciada cuando la

señal SP_MUTE es puesta en alto. Q3039 es controlado por medio de

la señal de detección de entrada de audífonos HP_SW la que se pone

en un estado alto cuando los audífonos son insertados en su terminal

de entrada.

4.3.3.8 Circuito de control de silenciamiento.

El silenciamiento es controlado a través de señales como LINE_MUTE

y A_MUTE provenientes de un microcomputadora y de la línea de

alimentación AN+12V.

A_MUTE y la línea de alimentación AN+12V son introducidas al

circuito de silenciamiento conformado por Q3034 y Q3035 de esta

forma la señal de silenciamiento SP_MUTE es sacada de

D3064.SP_MUTE es puesta en alto (Aproximadamente 10V) cuando

la señal de silenciamiento A_MUTE que viene de la microcomputadora

es puesta en alto y cuando la línea de alimentación de audio AN+12V

cae o se incrementa.

Una terminal de salida de audio es silenciada por LINE_MUTE y

AN+12V( ver sección 2.3.2).

La señal de salida es silenciada cuando la terminal SP_MUTE es

puesta en nivel alto. Las salidas Las bocinas y Sub_woofer es

silenciada cuando la señal de detección de audífonos

HP_SW es puesto en alto o cuando SP_MUTE es puesta

en estado alto.

4.3.4 Circuito de control de Ventilador.

El circuito de control del ventilador esta formado por

IC3012 y Q3022. En este bloque el circuito de control del

ventilador realiza procesos tales como control de

velocidad, detección de paro del ventilador y detección del

voltaje de control del ventilador. El voltaje de control del

ventilador es gobernado por medio de una señal llamada

FAN_DRV proveniente de la tarjeta B con el fin de

controlar la velocidad del ventilador. El voltaje del

ventilador es atenuada y retroalimentada hacia el

microcontrolador(FAN_FB). La señal de detección de paro

de ventilador que viene del ventilador es Ored usando

IC3017 i es sacado hacia el microcontrolador hacia la

terminal (FAN_DET).

4.3.5 Control S.

Esta unidad tiene terminales de Entrada / Salida de

control S. En la figura se muestra el flujo de la señal S.

Como se muestra en la figura, la señal SIRCS que viene

del receptor del control remoto no esta habilitada cuando

la señal de control S es usada. Solo la señal de SIRCS

proveniente del la entrada de Control S es recibida en

este caso. La terminal de salida de control S saca la

señal que viene de la entrada Control s cuando el

conector S es insertado en la terminal de entrada Control

S. La salida del Control S saca la señal SIRCS1 que viene

del bloque del foto sensor del control remoto siempre y

cuando no este insertada la terminal S . La figura muestra

el flujo de la señal del control S.

Customer Services Latin América - 45 -

Page 47

Televisores de Plasma

Señales SIRCS y de control S

Customer Services Latin América - 46 -

Page 48

Televisores de Plasma

Diagrama a bloques de la tableta Q

Customer Services Latin América - 47 -

Page 49

Televisores de Plasma

5. Tarjeta de TU.

5.1 Bloque de proceso de video.

5.1.1 Diagrama a bloques del circuito de proceso de video.

La figura muestra el diagrama a bloques del proceso de video.

Customer Services Latin América - 48 -

Page 50

Televisores de Plasma

5.1.2 Circuito para el proceso de la Sincronía Horizontal.

Una señal compuesta de video con un voltaje de 2.0 Vpp sale de la

terminal 22 (DET OUT) del TU6001 cuando una señal al 100% blanca

es introducida. La señal de sincronismo horizontal es detectada

proveniente de esta señal usando el Q6004.

La señal de sincronismo H detectada es introducida la

microcomputadora del tuner como una forma de onda ECE-Phaseshifted de 0 a 5V. La microcomputadora del tuner cuéntale pulse en

intervalos de 2 milisegundos cuatro veces i confirma que se este

recibiendo una señal cuando la Cantidad de pulsos es de 104 a 255.

El modo de servicio puede ser cambiado cuando la microcomputadora

del tuner reconoce la recepción de una señal.

5.1.3 Circuito para el proceso de sincronía Vertical.

Una señal compuesta de video de 1.8 Vpp sale de la terminal 21 (DET

OUT2) del TU6001 todo esto cuando una señal 100% blanca es

introducida. La señal de sincronismo V es detectada en la señal

compuesta de video usando Q6001 y el Q6002. La señal de

sincronismo vertical detectada es introducida ala microcomputadora

del Tuner como una señal ECE-Phase-shifted en forma de diete de

sierra de 0 a 5V. La microcomputadora del Tuner detiene el enfoque

de una imagen usando esta forma de onda.

GR6001 reduce le fantasma usando el interruptor en

encendido de la microcomputadora del tuner y envía una

señal compuesta al reforzador GR6011 con un voltaje

1.8Vpp.

La señal compuesta es convertida a otra de 0.8Vpp

usando Q6011 y se envía al tarjeta Q. La descripción de

los pines del TU6001 y GR6001 es mostrada a

continuación.

5.1.4. Circuito de procesamiento de video.

Una señal compuesta de video de 1.8 Vpp sale de la terminal 21 (DET

OUT) del TU6001 y es introducida a través del un reforzador Q6005 al

GR6001 con un voltaje de 1.8Vpp cuando una señal 100% blanca es

introducida.

Customer Services Latin América - 49 -

Page 51

Televisores de Plasma

NO Nombre I/O Función

1

2

3

4

5

6

11

12

13

14

15

21

22

23

24

25

26

27

28

29

30

31

9v

30v

5v

SCL

SDA

AS

RF AGC

VIF

+B (9v)

AFT OUT

GND

DET OUT2

DET OUT

ST IND

SAP IND

MODE

F MONO

NC

MUTE I Terminal de Silenciamiento de Audio

NC

R OUT

L OUT

Alimentación del Tuner

I

I

I

Datos seriales para sintonía

I/O

I/O

Fixed 5V

I

Terminal RF AGC

I

Verificación VIF

-

Alimentación de IF /MPX

I

Salida análoga de AFT

O

Tierra ( GND)

O

Salida de ajuste de video 1.8±0.1V

O

Salida de Video 2.0± 0.2 V

Salida de indicador estereo

O

Salida del indicador SAP

O

Interruptor de modo para audio multiplexado H: 3.5V-9.0V, L: 0V –1.5V

I

Terminal para forzado de monoaural

I

H:8.5V-9.0V, M: 2.0V-7.0V L:0V-0.8V

-

ON: 4V-9V; OFF: 0V-0.8V

-

Salida de audio canal derecho

O

Salida de Audio Canal Izquierdo

O

PLL ON

(NPN

colector

abierto)

Customer Services Latin América - 50 -

Page 52

Televisores de Plasma

5.2 Circuito de proceso de audio

5.2.1 Diagrama a bloques del circuito de audio.

La siguiente figura muestra el circuito a bloques del procesamiento de

audio.

5.2.2 Circuito de procesamiento de Audio.

El circuito de procesamiento de audio amplifica la señal de audio

incluyendo la componente de DC que proviene del TU6001 usando

IC6008 (Amplificador operacional) se elimina la componente de CD

usando C6075 y C6080 y después se envía la señal de audio a la

tarjeta Q.

5.3. Bloque del Microcontrolador para control del Tuner.

Las funciones de la microcomputadora para control del Tuner se

pueden clasificar en 6 principales:

1. Interruptor para el modo de computadora externa (Tarjeta de

ajuste).

2. Control del TU6001 a través de bus bidireccional

I2C

3. Conmutación del modo dual de audio.

4. Control de silenciamiento de Audio

5. Modo forzado de recepción monoaural durante

recepción estereo.

6. AGC Control durante el ajuste automático.

La información requerida para cada uno de los diferentes

procesos referidos arriba, es leída por medio del Bus, de

un Convertidor A/D o I (Puerto de entrada) mostrados en

la lista siguiente y es procesada por medio de Software.

La asignación de terminales para el microprocesador del

tuner es mostrada en la siguiente tabla.

Customer Services Latin América - 51 -

Page 53

Televisores de Plasma

No Puerto Nombre I/O Función

1 PA1 O_CNCT

2 PA0 I_CNCT I Detección de falla en el convertidor de alimentación: L: Anormal; H: normal

3 PB7 I_MLOCK I Terminal de salida de detección de amarrado de AFC. L:Ordinaria H: Muse Lock (Señal de

MUSE provista).

4 PB6 O_SMUTE

5 PB5 O_YCMUTE

6 PB4 O_RECSW1

7 PB3 I_NSYNC I Terminal de entrada para detección de sincronía de trama BS.L:Señal de referencia BS, H:

Señales excepto 0(Sin señal y con señal Muse)

8 PB2 O_PCMRST

9 PB1 O_DECSW1

10 PB0 O:DECSW2

11 PC7 I_BINTN I Puesta para el modo de computadora externa (Tarjeta de ajuste) en bajo. L: Modo de

computadora externa, H:Ordinario

12 PC6 O_2SAP

13 PC5 O_BSPCNT

14 PC4 O_MASW

15 PC3 O_SUBSW

16 PC2 O_MUTE

17 PC1 O_AFCSW

18 PC0 O_SMUSE

19 EC/PD7 I_2HS I Entrada de sincronía Horizontal para sintonización de la sub-pantalla U/V.

20 RMC-PD6 I_2STRN I Terminal de entrada para detección transmisión estereofónica para la sub-pantalla. H:otros

L:Estereo

21 ACI/PD5 I_2BILN I Terminal de entrada para detección transmisión audio dual para la sub-pantalla. H: otros L: Audio

Dual.

22 HS0/PD4 I_HS I Terminal de entrada para la sincronía Horizontal para la sintonía de la pantalla Maestra U/V

23 SI/PD3 I_SI I Terminal de entrada del puerto serial tri-alambrado (SIO BUS)

24 SO/PD2 O_SO O Terminal de salida del puerto serial tri-alambrado (SIO BUS)

25 SCK/PD1 IO_SCK I/O Terminal de entrada de reloj del puerto serial tri-alambrado (SIO BUS)

26 VSS VSS

27 INT2/PD0 I_2VPN

28 XTAL O_XTAL O Conexión del oscilador cerámico

29 EXTAL I_EXTAL I Conexión del oscilador cerámico

Customer Services Latin América - 52 -

Page 54

Televisores de Plasma

30 RST I_RSTN I Entrada de reset

31 TO/PE7 O_SEP

32 PWM/PE6 Terminal de entrada del SW GR

33 PE5/AN3 I_DECIN I Terminal de entrada del decodificador, terminal de entrada para detección de conectado o

desconectado: L: conectado H: desconectado

34 PE4/AN2 I_ANTL I Terminal de entrada para la inversión de DC para medir el nivel de entena.

35 PE3/AN1 I_AFT I Terminal de entrada del voltaje de AFT para la sintonización U/V de la pantalla maestra

36 PE2/AN0 I_2AFT I Terminal de entrada del voltaje de AFT para la sintonización U/V de la sub-pantalla

37 PE1/INT1 I_VPN I Terminal de entrada de sincronía vertical para la sintonía de la pantalla maestra.

38 PE0/INT0 I_CPSL I Terminal de entrada del puerto l tri-alambrado seria para selección del chip (SIO BUS

39 XLC O_XLC

40 EXLC I_EXLC

41 R O_R

42 G O_G

43 B O_B

44 I I

No Puerto Nombre I/O Función

45 YS YS

46 YM YM

47 PF7/PWM7/

SDA1