SINCLAIR ZX81 User Manual [fr]

Robotisez votre ZX81

P. Gueulle - ETSF - MICRO-SYSTEMES (extraits)

La mise à l'étude d'extension matérielles pour le ZX81 exige une connaissance sinon totale, du moins satisfaisante de l'organisation interne de la machine.

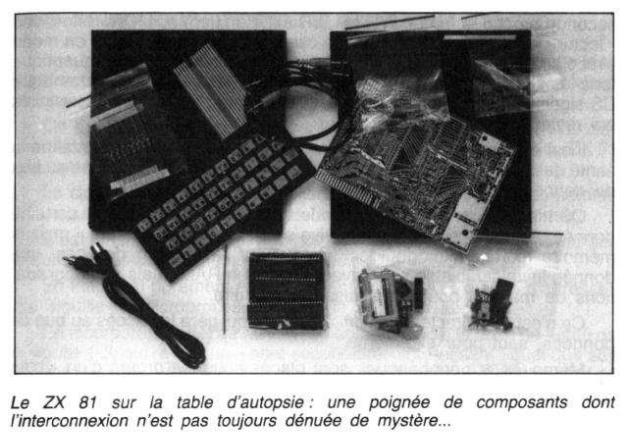

Une auréole de mystère a toujours entouré les produits Sinclair, sans doute dans le but de protéger autant que possible des techniques de pointe hautement vulnérables.C'est compter sans la persévérance des passionnés.

De patientes recherches, d'innombrables recoupements entre des expériences et des lectures de publications britanniques permettent maintenant aux membres de ce que certains ont baptisé le «clan Sinclair», de se faire une idée beaucoup plus nette de ce qui se passe sous le petit capot noir...

Organisation générale d'un système à microprocesseur

Le ZX 81 n'est qu'un cas particulier de système à microprocesseur, mais quel cas!

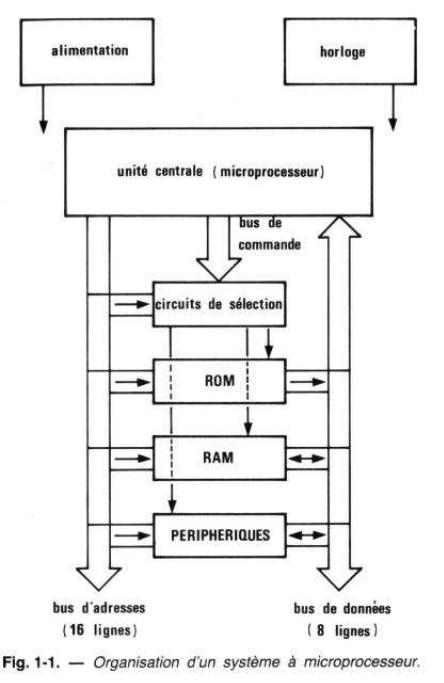

Une organisation commune se retrouve dans tous les systèmes microprogrammés, seules des variantes à vrai dire mineures permettant de les distinguer (fig. 1-1).

Si l'on excepte les organes «secondaires» que sont, par exemple, les circuits d'alimentation et d'horloge, on peut scinder n'importe quel système en trois grandes parties:

· l'unité centrale, c'est-à-dire le microprocesseur lui-même, chargée d'exécuter tous les traitements d'information proprement dits. Un jeu d'instructions, propre à chaque modèle de microprocesseur, fixe de façon limitative la panoplie d'opérations élémentaires disponibles. C'est cela, lelangage machine que l'on utilisera...

Outre les circuits logiques de traitement, dont le comportement est dicté par les instructions exécutées, le microprocesseur contient un certain nombre de registres capables de stocker temporairement des informations.

La plupart des instructions opèrent sur des données présentes dans des registres, et rangent le résultat également dans un registre.

Le microprocesseur Z 80 A, autour duquel est bâti le ZX 81, est l'une des unités centrales possédant le plus de registres, et le plus large jeu d'instructions : un sérieux gage de souplesse d'emploi!

·la mémoire se décompose elle-même en deux parties: mémoirela morteou ROM, qui contient le programme machine à exécuter ainsi que des données figées (par exemple la forme des caractères utilisés par le ZX 81, ou encore la valeur de pi). Cette mémoire estprogramméeune fois pour toutes en usine, et son contenu ne peut en aucun cas être altéré par l'utilisateur.

La mémoire viveou RAM sert de «bloc-notes» au microprocesseur, qui y rangera à son gré (ou plutôt au gré du programme!), les informations que les registres internes ne suffiraient pas à abriter.

Certains petits systèmes ne possèdent pas de RAM, et se contentent des registres. Le ZX 81 de base, lui, possède 1 K-octet de RAM, soit l'équivalent de 1024 registres.

La mémoire vive est essentiellementvolatile:tout son contenu s'efface dès la coupure de l'alimentation, mais en revanche, on peut aussi bien y lire qu'y écrire des informations.

·les périphériques sont tous les organes qui, connectés à l'unité centrale, servent à communiquer avec l'extérieur: écran vidéo, clavier, interface cassette, imprimante, cartes d'entrée-sortie, cartes sonores, poignées de jeu, etc. Ces «accessoires» jouent un rôle essentiel car, sans eux, rien ne permettrait d'agir sur le microprocesseur qui, lui-même, ne pourrait pas davantage commander quoi que ce soit!

Des liaisons doivent bien sûr exister entre tous ces éléments. Les informations sont constituées de huit états logiques(1 ou 0) correspondant à la présence ou à l'absence d'une tension de cinq volts.

Huit fils (plus une masse) devraient donc relier chaque circuit extérieur à l'unité centrale.

Il faut également que le microprocesseur, lorsqu'il échange des informations avec, disons, une mémoire, puisse indiquer à laquelle des «cases» de cette mémoire il s'intéresse : la ROM du ZX 81 comporte 8 192 «cases» ou «adresses», et sa RAM peut en compter 1024 ou beaucoup plus si des extensions lui sont ajoutées.

En fait, le Z 80 peut distinguer jusqu'à 65 536 adresses différentes (64 fois 1024 soit 64 K adresses).

Moyennant un certain codage (le code binaire), on peut se contenter de seize fils pour véhiculer une adresse reconnaissable sans ambiguïté.

Pour minimiser, autant que faire se peut, les liaisons déjà touffues nécessaires dans un système à microprocesseur, on fait appel au principe du BUS

Un BUS est un groupe de lignes desservant, en parallèle, un certain nombre d'organes.

Le Z 80 possède unbus de donnéesà huit lignes, et un bus d'adresses à seize lignes.

Comme il faut à tout prix éviter un mélange inextricable des données relatives à tel ou tel «abonné» du bus, on utilise le système dit à trois états:

Chaque «abonné» (mémoire, périphérique, ou même microprocesseur) est normalement dans un état dit «haute impédance». Cet état «d'attente» le déconnecte entièrement du bus sur lequel il ne peut ni lire ni écrire.

Des circuits supplémentairesde sélectionpeuvent ordonner à tel ou tel «abonné» de se connecter au bus, soit en tant qu'« émetteur», soit en tant que «récepteur» d'informations. En effet, le bus de données peut véhiculer des informations dans les deux sens : à partir de l'unité centrale ou vers elle.

Comme c'est le microprocesseur qui «décide» s'il veut envoyer ou recevoir des données (en fonction des instructions qu'il exécute), il possède deux broches nommées RD et WR. Ces broches, qui font partie du troisième et dernier bus du système, lebus de commande, sont normalement maintenues au «1 » logique (+5V).

RD passe à zéro lorsque l'unité centrale veutacquérirune information. En même temps, le bus d'adresses reçoit les «coordonnées» de l'information à aller chercher quelque part sur la «carte mémoire» de 64 K-octets.

Inversement, WR passe à zéro lorsque le bus d'adresses véhicule l'adresse à laquelle doit être acheminée une information venant du microprocesseur.

Les mémoires mortes, qui ne peuvent qu'être lues, possèdent seulement une entrée «de sélection» : normalement placées dans l'état «haute impédance», elles passent en mode «émission» dès que cette entrée (nommée CS) est mise à zéro.

Les mémoires vives et les périphériques peuvent fonctionner dans les deux sens lorsque CS est à un, l'état «haute impédance» est forcé. Lorsque CS passe à zéro, l'état de l'organe dépend de celui d'une seconde broche nommée WR: si WR est à un, le mode «émission» ou «lecture» est sélectionné. Dans le cas contraire, on se trouve en mode «réception» ou «écriture». Il est facile de retenir cela en remarquant que tous les signaux «surlignés» sontactifs à l'état zéro, et en sachant que CS signifie Chip Select, WR Write, et RD Read : quelques mots anglais qui reviendront souvent!

Il est évidemment vital (parfois au sens propre en ce qui concerne la santé des composants!) qu'un ordre parfait règne dans les accès au bus de données bidirectionnel.

Où irions-nous, Si l'unité centrale envoyait sur le bus une certaine donnée, pendant que la mémoire vive serait en mode «écriture» mais la mémoire morte en mode «lecture»? Dans le meilleur des cas, une donnée invraisemblable se trouverait écrite en RAM, mais des dégrada tions de matériel pourraient aussi se produire.

Ce n'est pas directement l'unité centrale qui gère les accès au bus de données, sauf pour elle-même.

Mémoires et périphériques sont placés sous les ordres d'un «chef d'orchestre» nommécircuit de sélection.

Ce circuit logique relativement simple (les spécialistes dirontcombinatoire puisqu'il ne comporte que des portes, à l'exclusion de toute bascule, registre, compteur...) combine entre eux les signaux WR et RD, et certaines lignes du bus d'adresses unidirectionnel.

On peut affirmer que, mis à part le choix des différentes mémoires et des divers périphériques, c'est le schéma du circuit de sélection qui détermine l'organisation matérielle du système complet, planou de mémoire.

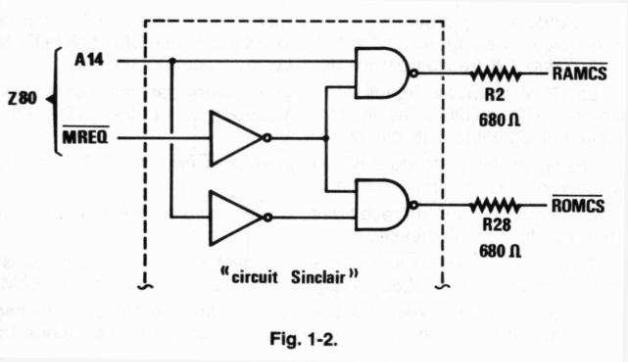

En plus de ces signaux, le Z 80 génère également une ligne MREQ, qui passe à zéro quand l'unité centrale cherche à dialoguer avec de la mémoire(Memory Request).

Parallèlement, il existe aussi un signal IORQ passant à zéro losque le dialogue doit s'établir avec un périphérique d'entrée-sortie (lnput Output Request).

En fait, de larges recouvrements peuvent s'opérer entre ces deux modes d'échanges de données.

Le cas du ZX 81 est un parfait exemple de ce que des concepteurs habiles peuvent obtenir par un choix avisé des circuits de sélection : le principal avantage de ces choix est bien sûr une extrême simplicité du schéma (quatre circuits intégrés, parfois cinq), et donc un prix de vente record, avec le succès que l'on sait...

Les sélections mémoire du ZX 81

Les circuits de sélection mémoire du ZX 81 sont inclus, comme bien d'autres fonctions de cette machine, dans le fameux et bien mystérieux «circuit Sinclair».

On peut cependant se faire une idée assez précise de certains des circuits qu'il contient, en examinant le schéma de cet «ancêtre» du ZX 81 que fut le ZX 80.

Le circuit de cette machine utilisait en effet uniquement des boîtiers TTL courants reliés entre eux par les pistes du circuit imprimé.

C'est ainsi, par exemple, que nous avons reconstitué le schéma des circuits de sélection mémoire, reproduit à la figure 1-2.

En tait, c'est purement et simplement la ligne A14 du bus d'adresses qui aiguille le microprocesseur vers la ROM ou la RAM.

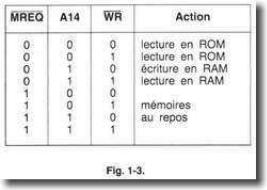

En incorporant l'effet de MREQ, on aboutit donc à la table de vérité de lafigure 1-3, qui révèle un «effet secondaire» intéressant : quel que soit l'état de la ligne WR, le passage à zéro simultané de MREQ et de A14 entraîne une lecture de la ROM. Or, cette combinaison se présente non seulement lors de l'exécution d'instructions PEEK sur le contenu de la ROM, mais aussi lors de tentatives de POKE, vouées à l'échec puisqu'on ne peut écrire en ROM, mais que rien n'empêche de programmer, ne fût-ce que par erreur.

Dans ces conditions, l'unité centrale enverrait une donnée sur le bus (l'argument de POKE), mais la ROM, en mode lecture, en enverrait une autre, très certainement différente! Non seulement une telle opération est absurde, mais elle risquerait d'endommager le Z 80 ou la ROM.

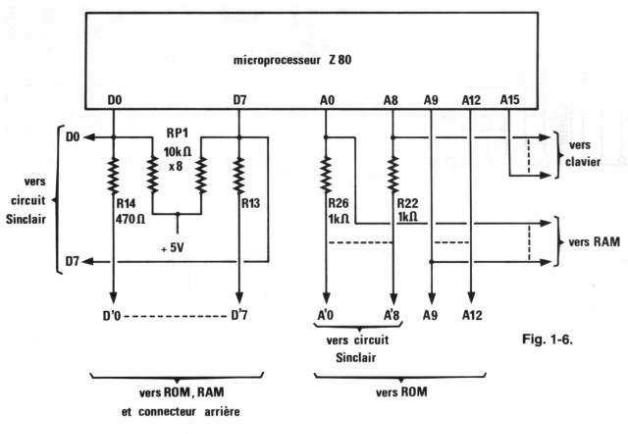

C'est certainement pour cette raison que les ingénieurs de chez Sinclair ont incorporé huit résistances en série dans le bus de données (R7 à R15, de 470 ohms).

Par contre, le circuit Sinclair accède directement aux lignes de données de l'unité centrale, avec laquelle il peut donc dialoguer en toute indépendance vis-à-vis des mémoires : ceci a son importance au sein du très complexe processus d'affichage de l'image vidéo.

Du côté du bus d'adresses, un artifice semblable est utilisé, comme en témoignent lesfigures 1-4 et 1-5 (brochages de la ROM et de la RAM), et la figure 1-6 (raccordement des bus au microprocesseur).

La ROM reçoit les lignes A0 à A8 à travers des résistances de 1 kilo-ohm (R22 à R26). Ces lignes «résistives» sont notées A0' à A8', et rejoignent également le circuit Sinclair.

Les lignes A9 à A12 du Z 80 rejoignent directement la ROM, mais ne desservent pas le circuit Sinclair. En revanche, la RAM reçoit directement de l'unité centrale les lignes A0 à A9 du bus d'adresses.

Tout cela signifie que le circuit Sinclair peut assigner une adresse à la ROM pendant que le Z 80 dialogue avec une adresse de la RAM.

Cette particularité est à la base du fonctionnement de l'affichage vidéo: en effet, la génération du signal TV comporte des tâches trop rapides pour le microprocesseur, et c'est le circuit Sinclair qui s'en charge, notamment en interrogeant le générateur de caractéressitué en haut de la ROM. Pendant ce temps, le Z 80 exécute des tâches plus lentes, en liaison avec la RAM...

Donc, la ROM reçoit les lignes A0 à A12, avec ou sans résistances:

chacune de ces lignes pouvant prendre deux états distincts (0 ou 1), c'est un total de 213 =8192 combinaisons que l'on peut mettre en évidence à ce niveau.

Ce nombre de combinaisons distinctes du bus d'adresses correspond «comme par hasard» à la capacité de la ROM, 8 K-octets, c'est-à-dire 8 192 cellules (8 x 1024).

Il est donc clair que, pour peu que le signal ROMCS soit mis à zéro, l'unité centrale pourra lire individuellement n'importe quelle adresse de la ROM.

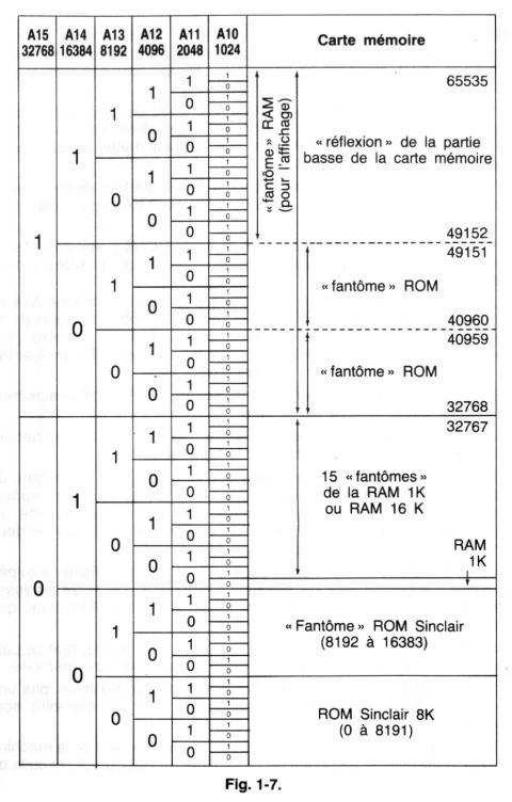

Seulement, ROMCS_ne tient compte que de l'état de la ligne A14 en plus de l'inévitable MREQ. Comme il existe deux grands segments de 16 K-octets de l'espace mémoire pour lesquels A14 est à zéro (voir figure 1-7), il est clair que la ROM ne pourra faire aucune différence entre, par exemple, l'adresse 8 191 et l'adresse 40 959.

Pour ces deux adresses, en effet, les lignes A0 à A12 ont exactement les mêmes états, et A14 est à zéro.

A l'intérieur d'un même segment de 16 K-octets, la ROM ne tiendra pas davantage compte de l'état de la ligne A13.

Finalement, donc, c'est quatre fois que l'on retrouvera le contenu de la ROM sur la carte mémoire de la figure 1-7: une première fois «au bon endroit» (de 0 à 8 191) lorsque A15 et A13 sont à zéro, une seconde fois juste à la suite entre 8 192 et 16 383 (A15 à zéro, mais A13 à un), et deux autres fois de façon symétrique avec A15 à un.

La RAM de base de 1 K-octet subit un traitement similaire: équipée des lignes d'adresses A0 à A9, elle peut distinguer 2 10 = 1024 adresses différentes, mais ignore superbement les lignes A10 à A13, ainsi que A15

Résultat de ce dédain, c'est trente-deux fois, pas moins, que ce petit segment de 1024 octets est «dédoublé» dans l'espace mémoire.

Le gaspillage est considérable : sur 64 K-octets disponibles, pas une adresse ne reste libre alors que seulement 9 K de mémoire sont implantés (8 K de ROM et 1 K de RAM)!

En fait, cette libéralité ne nuit en rien au fonctionnement de la machine de base, mais évite le recours à de complexes (donc coûteux) circuits de sélection.

Loading...

Loading...