Video IF with FPLL,

MAC State

Features

● Active multistandard video IF

with FPLL demodulator

● 12-MHz bandwidth

● MAC state

TDA 6050-5

Bipolar IC

P-DIP-20

Type Ordering Code Package

TDA 6050-5 Q67000-A5123 P-DIP-20

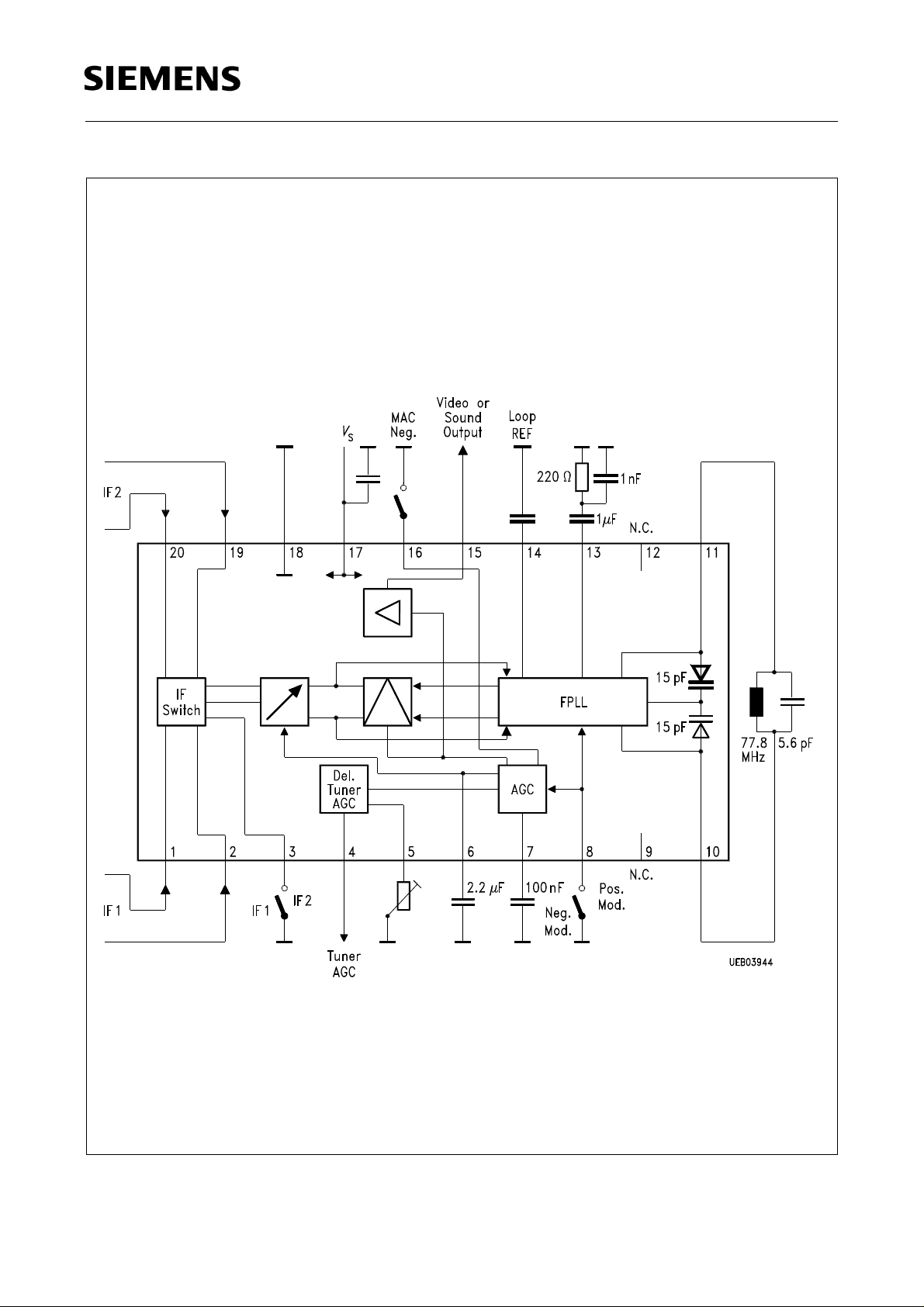

Circuit Description

The IF circuit consists of a four-stage capacitively coupled and symmetrically designed controlled

amplifier and a real synchronous demodulator with a FPLL-carrier regeneration. Two IF inputs can

be selected for applications with different SAWs. The main performance of the device is the very low

differential phase DP and gain DG combined with an excellent intermodulation ratio. The positive

video output is used to derive the IF and tuner control voltage. The AGC threshold is set by means

of a potentiometer. Dependent on the modulation polarity the video signal and the AGC are

switched over. MAC state can be selected by an additional signal.

Application

Multistandard TV/VTR and cable converters with mono or stereo applications.

Semiconductor Group 63 06.94

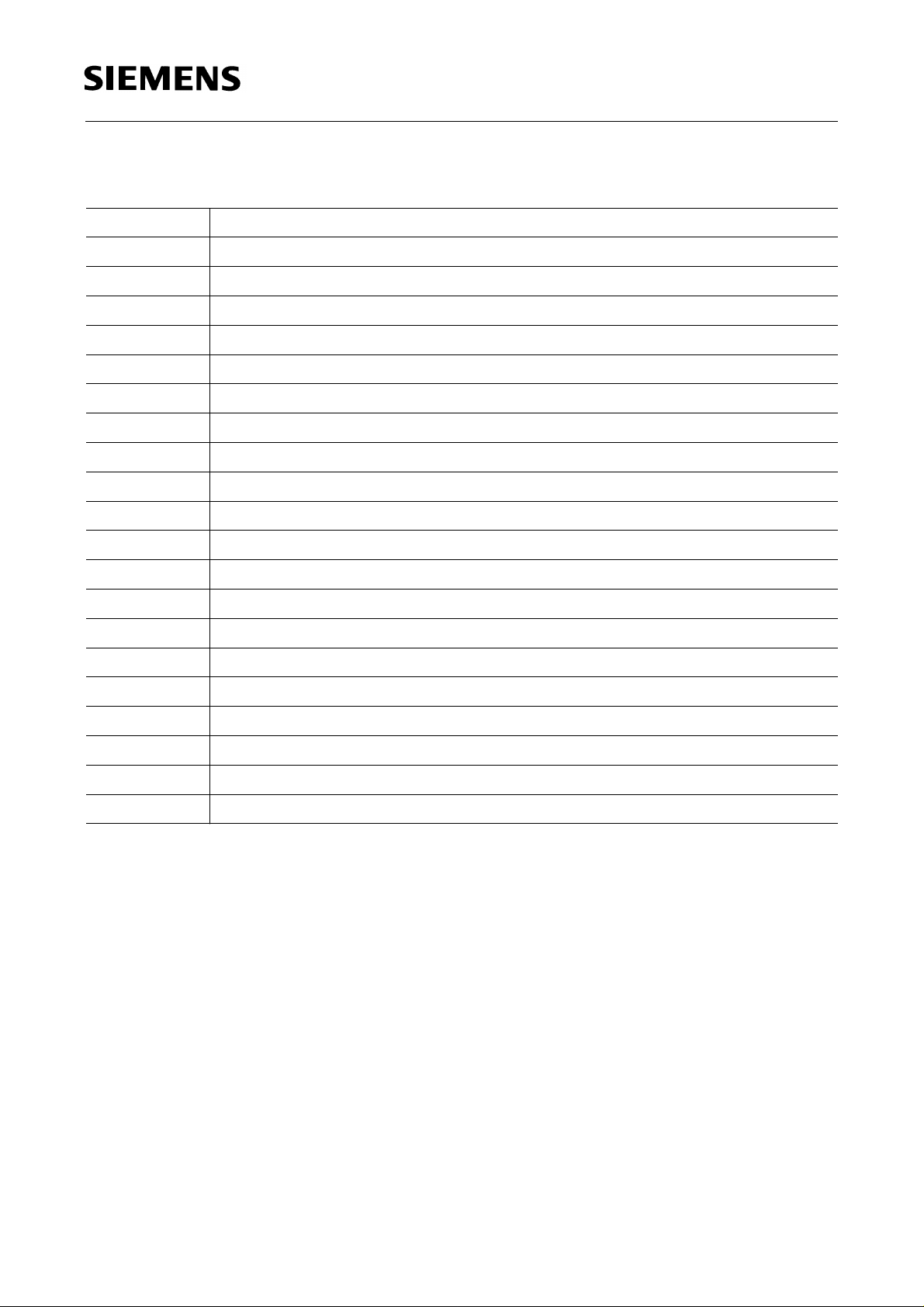

Pin Functions

Pin No. Function

1 IF input 1a

2 IF input 1b

3 IF switch

4 Tuner AGC output

5 Tuner AGC threshold

6 Main AGC-time constant

7 Mean value AGC-time constant

8 Positive/negative modulation switch

9 N.C.

10 FPLL-VCO (2 × video carrier)

TDA 6050-5

11 FPLL-VCO (2 × video carrier)

12 N.C.

13 FPLL-loop filter

14 FPLL-loop reference

15 Video output

16 MAC-standard switch

17 +

18 Ground

19 IF input 2a

20 IF input 2b

V

supply voltage

S

Semiconductor Group 64

TDA 6050-5

Block Diagram

Semiconductor Group 65

Loading...

Loading...