Sharp LH540225U-35, LH540225U-25, LH540225M-35, LH540225M-25, LH540225M-20 Datasheet

...

LH54021 5/ 25

512 × 18 / 1024 × 18 Synchronous FIFO

FEATURES

••

Fast Cy cle Times: 20/ 25/35 ns

•• Pin-Compatible Drop-In Replacements for

IDT72215B/ 25B FI FOs

•• Choice of IDT- Comp atible or

Enhanced

Oper at ing

Mode; Selected by an Input Control Signal

•• Device Comes Up into One of T wo Known Defau lt

States at Reset Depending on the Stat e of the

EMODE

Control I nput : Progr am ming is Allowed, but

is not Required

•• Internal Memor y Array Archit ectur e Based on CMOS

Dual-Port SRAM Tec hnology, 512 × 18 or 1024 × 18

•• ‘Synchronous’ Enable-Plus-Clock Control at Both

Input Port and Outp ut Port

•• Independent ly-Syn chr onized Oper ation of Input Port

and Out put Port

•• Control I nput s Samp led on Rising Clock Edge

•• Most Control Signals Asse rtive- LO W for

Noise Immunit y

•• May be Cascaded for Increased Depth, or

Para llele d for Incre ased W idth

•• Five Status Flags: Full, Almost -Fu ll, Half-Full,

Almost-Em pt y, and Empt y; ‘Almos t’ Flags ar e

Progr ammable

••

In Enhanced Oper at ing Mode, Al most -Full ,

Half-Ful l , and Almos t-Empt y Fl ags can be Mad e

Completel y Synchronous

••

In Enhanced Opera ting Mo de, Dupli cat e Enable s

for Interlocked Paralleled FIFO Operation, for

36-Bit Data Width, when Se lected and

Appropri at ely Con nect e d

••

In Enhanced Opera ting Mo de, Disabl in g

Three- Stat e Outpu ts May be Ma de to Suppress

Reading

••

Data Retransmit Function

•• TTL/CMOS- Co mpa tible I /O

•• Space-Saving 68-Pin PLCC Package, and 64-Pi n

TQFP Package

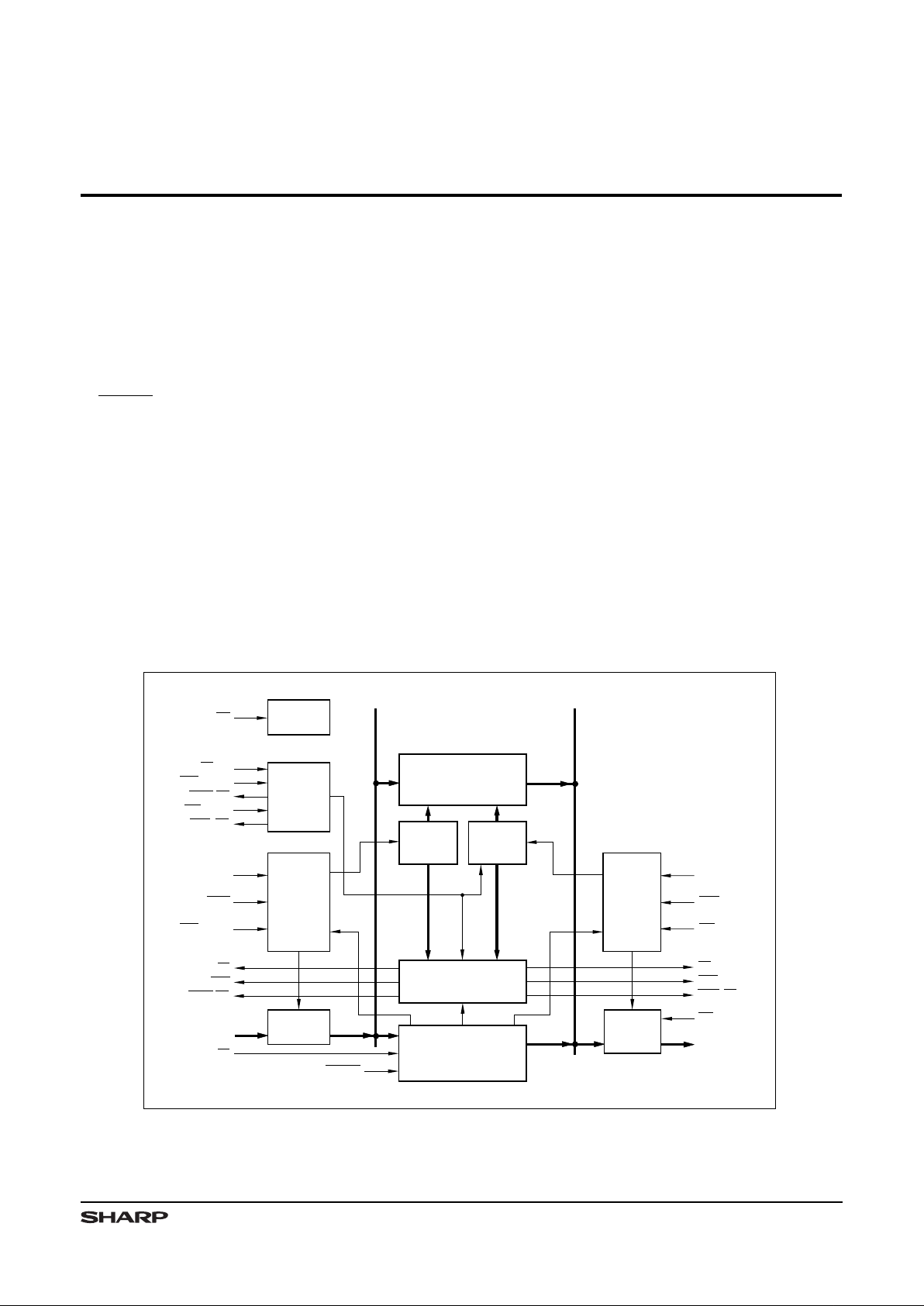

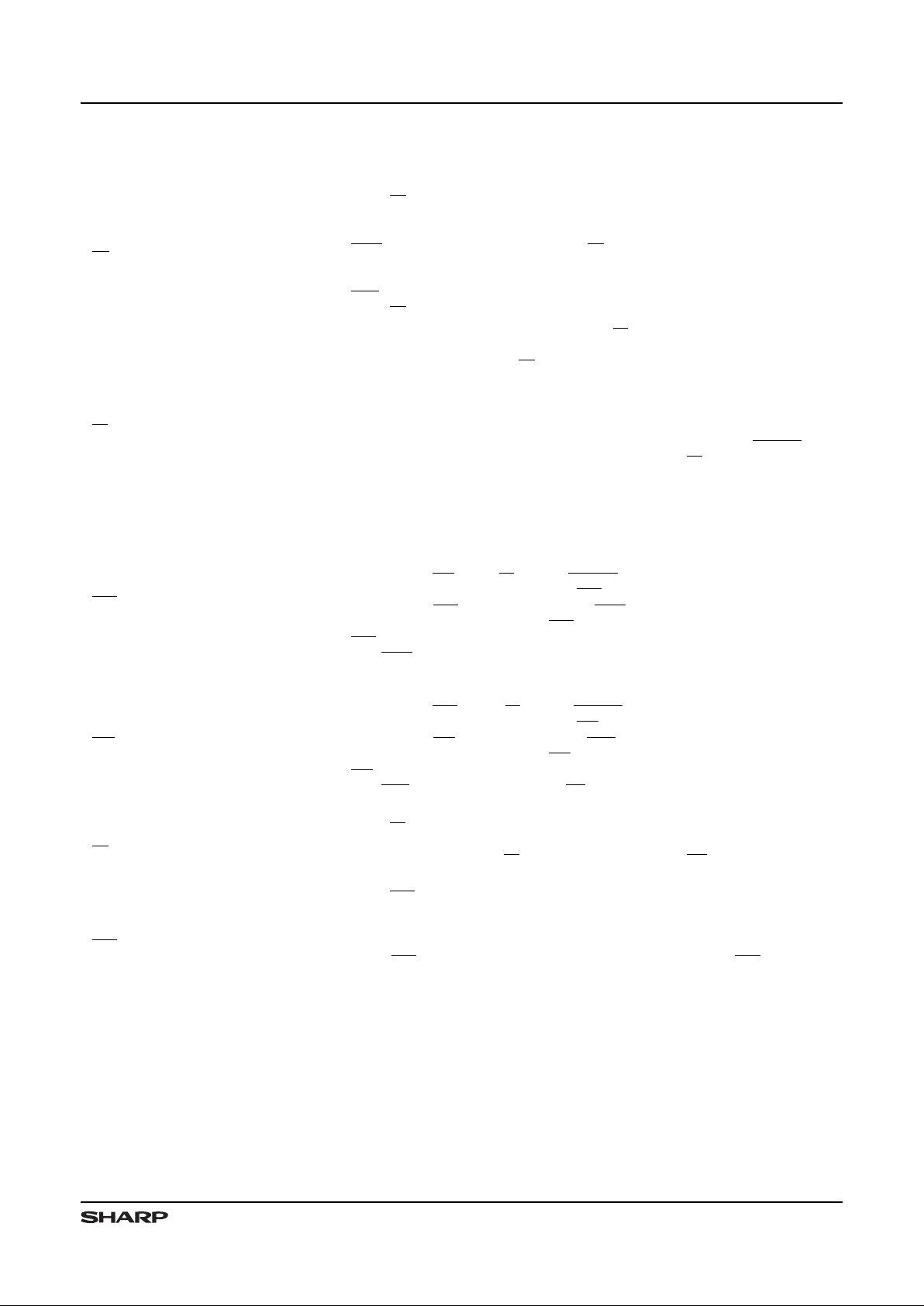

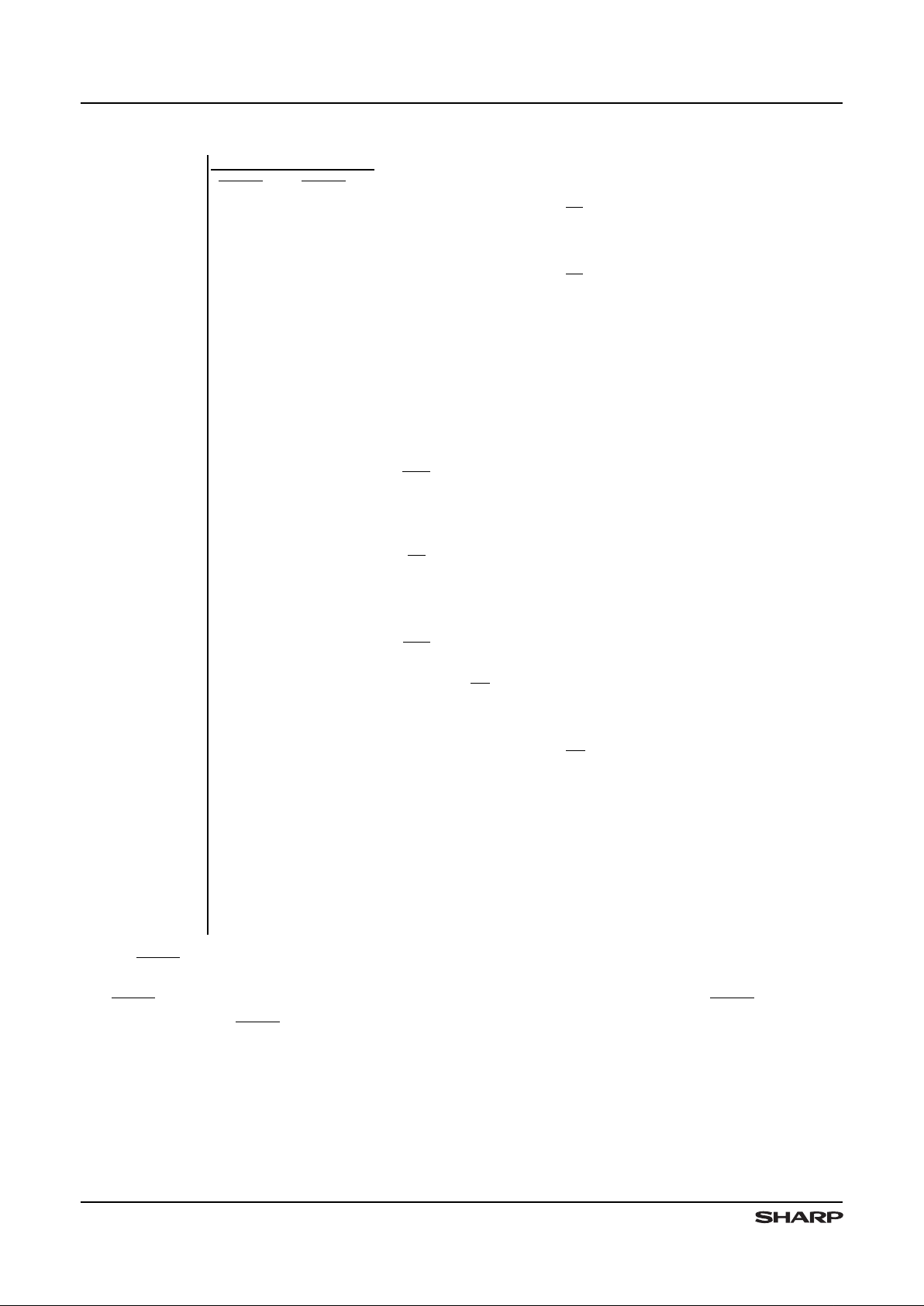

RESET

LOGIC

INPUT

PORT

RS

INPUT

PORT

CONTROL

LOGIC

READ

POINTER

WRITE

POINTER

DEDICATED AND

PROGRAMMABLE

STATUS FLAGS

FIFO

MEMORY ARRAY

512 x 18/1024 x 18

OUTPUT

PORT

CONTROL

LOGIC

FF

PAF

WXO/HF

RXO

/EF

2

PAE

D0 - D

17

WEN

WCK

Q

0

- Q

17

RCK

OUTPUT

PORT

REN

OE

PROGRAMMABLE

REGISTERS

EXPANSION

LOGIC

WXI/

WEN

2

FL/

RT

WXO/HF

RXI/

REN

2

RXO/

EF

2

LD

540215-1

WXI/

WEN

2

RXI/

REN

2

BOLD ITALIC = Enhanced Operating Mode.

EMODE

EF

Figure 1. LH540215/25 Bloc k Diagram

BOLD ITALIC = Enhanced Op erating Mode

1

FUNCTIONAL DESCRIPTION

NOTE: Throughou t this data sheet , a

BOLD IT ALIC

type

font is used for all references to

Enhanced Operati ng

Mode

features which do not function in IDT-Compatible

Operating Mode; and also for all references to the

re-

transmit

facility (which is not an IDT72215B/25B FIFO

feature), even though it may be used – subject to some

restrictions – in either of these two operating modes.

Thus, readers interested only in using the LH540215/25

FIFOs in IDT -Com pat ib le Oper at ing M ode ma y skip over

BOLD IT ALI C

sections, if they wish.

The LH540215/25 parts a re FIFO (Fi rst-In, First-Out)

memory devices, based on fully-static CMOS dual-port

SRAM t ec h no logy, capabl e of containing up to 512 or 1024

18-bit words respectively. They can replace tw o o r mo re

byte-wide FIFOs in many appli cations, for mi croprocesso rto-microprocessor or microprocesso r-to-bus communication. Their architecture supports synchronous operation, tied

to two independent free-running clocks at the input and

output ports respectively . However, these ‘clocks’ also may

be a period ic, asyn chronou s ‘dem and’ sign als. Al most al l

control-input signals and status-output signals are synchronized to these clocks, to simplify system design.

The input and output ports operate altogether inde pendently of each ot her, un les s the FIFO becomes either

totally full or else totally empt y. Da ta flow is initiated at a

port by the rising edge of its cor responding clock , and is

gated by the appropr iat e edge-sam pled enab le signals.

The following FIFO status flags monitor the extent to

which the internal memory has been filled: Full, AlmostFull, Half-Full, Almos t-Empty , and Empty. The Almost-Full

and Almost-Em pty flag offsets are progr ammable over the

entire FI FO depth; but, during a reset operation, each of

these is initialized to a default offset value of 63

10

(LH540215) or 12710 (LH540225) F IFO-memory words,

from the respective FIFO boundary. If this default offset

value is satisf actor y, no further program ming is r equir ed.

After a reset operatio n during wh ich the

EMODE

control

input was not asserted (was HIGH), these F IFOs operate in

the IDT-Compatible Operating Mode. In thi s mode, each

part is pin-compatible and functionally-compatible with the

IDT72215B/25B part of similar depth and speed grade; and

the

Control Regis ter

is not even accessible or visible to the

external-sys tem logic whic h is contr olling the FIFO, althou gh

it still performs the same co nt rol functi o ns .

However, assertion of the EMODE control input

during a rese t ope rati on l eaves Contr ol Re gis ter bi ts

00-05 set, and causes the FIFO to operate in the

Enhanced Operating Mode. In essence, asserting

EMODE chooses a dif ferent default stat e for the Control Register. The system optionally then may program the Control Register in a ny desired manner to

activa te or deac tivate any or a ll of th e Enhanced -Operat ing-Mode features which i t can control, inc luding

sel ect able-cl ock -ed ge flag synchroni zation, and read

inhi bi tion w hen t he data output s ar e disabled.

Whenev er EMODE is being asserted, interlocke dopera tion paral leling also is avai lable, by appropriate

inter connect i on of the FIFO’s expansi on in puts .

The retransmit facility i s available during standalone

operation, in either IDT-Compatible O perating Mode or

Enhanced Operating Mode. (See Tables 1 and 2.) It is

ino per ativ e if t he FL/RT input signal is grounded . It is not

an IDT72215B/25B feature.

The Retransmit control

sign al causes the interna l FIFO read-address pointer

to be set back to zero, without affecting the internal

FIFO write-address pointer. Thus, the Retransmit

contr ol signal al so provi des a mechani sm whereby a

bloc k of dat a delimi ted by the zero physica l address

and the current writ e-address-pointer address may

be re ad out r epeat edl y , an ar bi trar y num ber of times .

The only restrictions are that neit her the read-address pointer nor the write-address pointer may

‘wra p around’ dur ing this entire pro cess, and that the

retransmit facili ty is not available during depth-cascaded oper ation, ei ther in IDT -Com pat ible Oper atin g

Mode o r in Enhanced Opera ting Mode. (See T abl es 1

and 2.) A lso, the flags behave differen tly for a short

time after a retransmit operation. Otherwis e, the retransm it facility is ava ilable du ring standa lone operation, in either IDT-Compatible Operating Mode or

Enh anced Oper ating M ode.

Note that, when FL/RT is being used as RT, RT is

an asser tive -HI GH signal , rather tha n asser tive -LOW

as it is in most other FIFOs having a retransmit

facility.

Progr am ming the progr am mable-flag of fs et s,

the t iming synchronization of the various status flags, the

optional read-suppression funct ionality of OE, and

the b ehavi or of the po inter s whic h access the of fset val ue regi st ers and th e Control Regis ter

may b e individually controlled by asserting the signal LD, without any

res et operat io n. When LD is being asserted, and writing

is being enabled by asserting WEN, some por tion of the

input b us word D0 – D17 is used at the next rising edge of

WCLK to program one or more of the programmable

regis ters on suc cessive write cloc ks. Likewise, the values

programmed into these programmable registers may be

read out for verification by asserting LD and REN, with

the outputs Q0 – Q17 enabled. Reading out thes e programm able register s should not be initiated while they are

being writ ten into. T able 3 defines t he possi ble mode s of

operation for loading and reading out the contents of

prog ramm able registe rs .

BOLD ITALIC = Enhanced Op erating Mode

LH540215/25 512 x 18/1024 x 18 Synchronous FIFO

2

In the Enhanced Operat in g Mode, co ordi nat ed o peration of two 18-bit FIFOs as one 36- bit FIFO may be

ensured by ‘inter locked’ crosscoupl ing of the statusflag output s from each FI FO to the expansi on input s

of the other one; that is, FF to WXI/WEN2, and EF to

RX I/REN2, in both direct ions between tw o parallel ed

FIFOs. This ‘interlocked’ operation takes effect

automat ically, if two paral leled FIFOs are crossconnected in this manner, with t he EMO DE control input

being asserted (LOW). (See Tables 1 and 2, also

Figur es 27 and 30.) IDT -com pat ib le depth cascadi ng

no longer is available when operating in this ‘interlocked-paralleled’ mode; however, pipelined depth

cas cadi ng remai ns avai la ble .

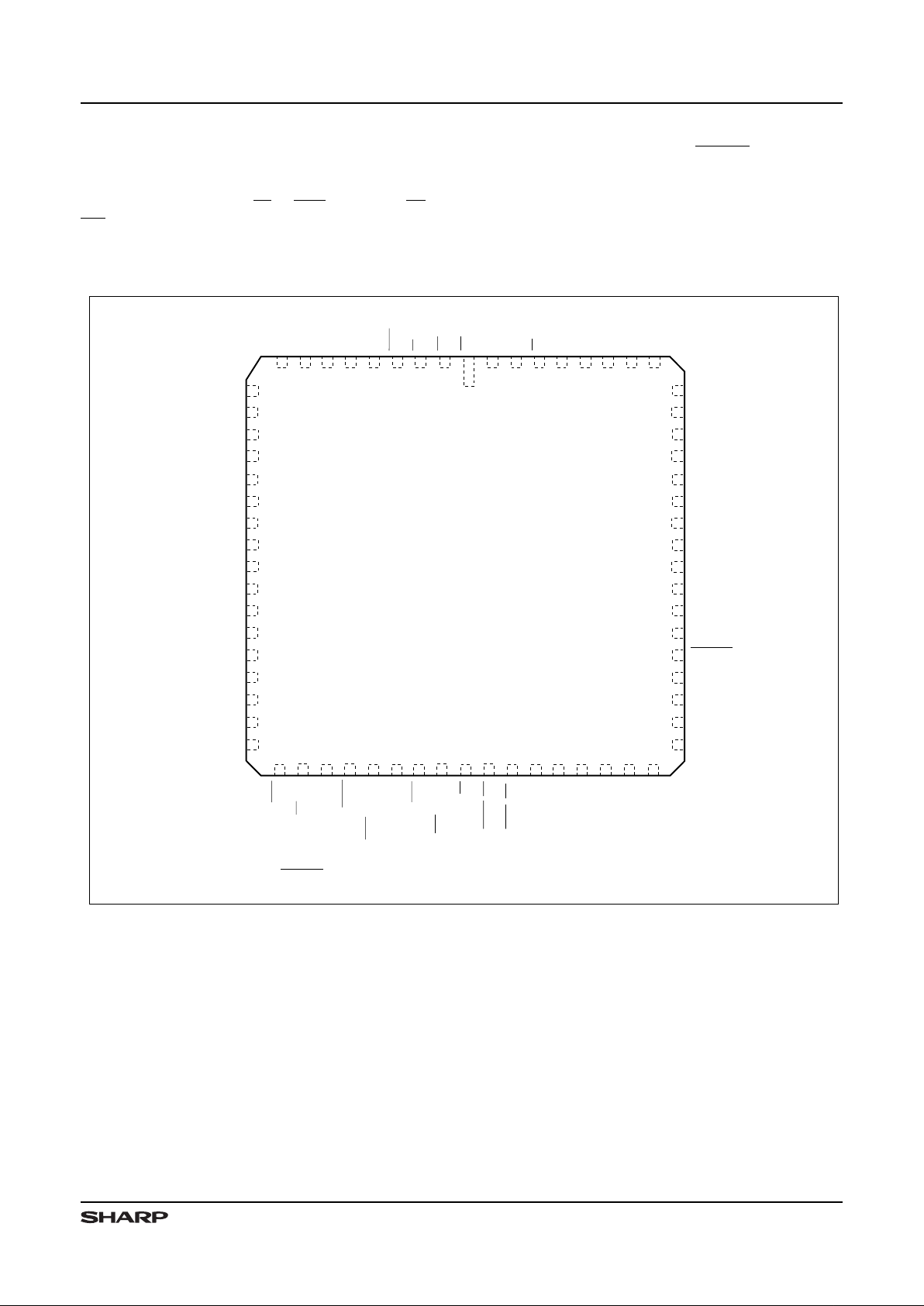

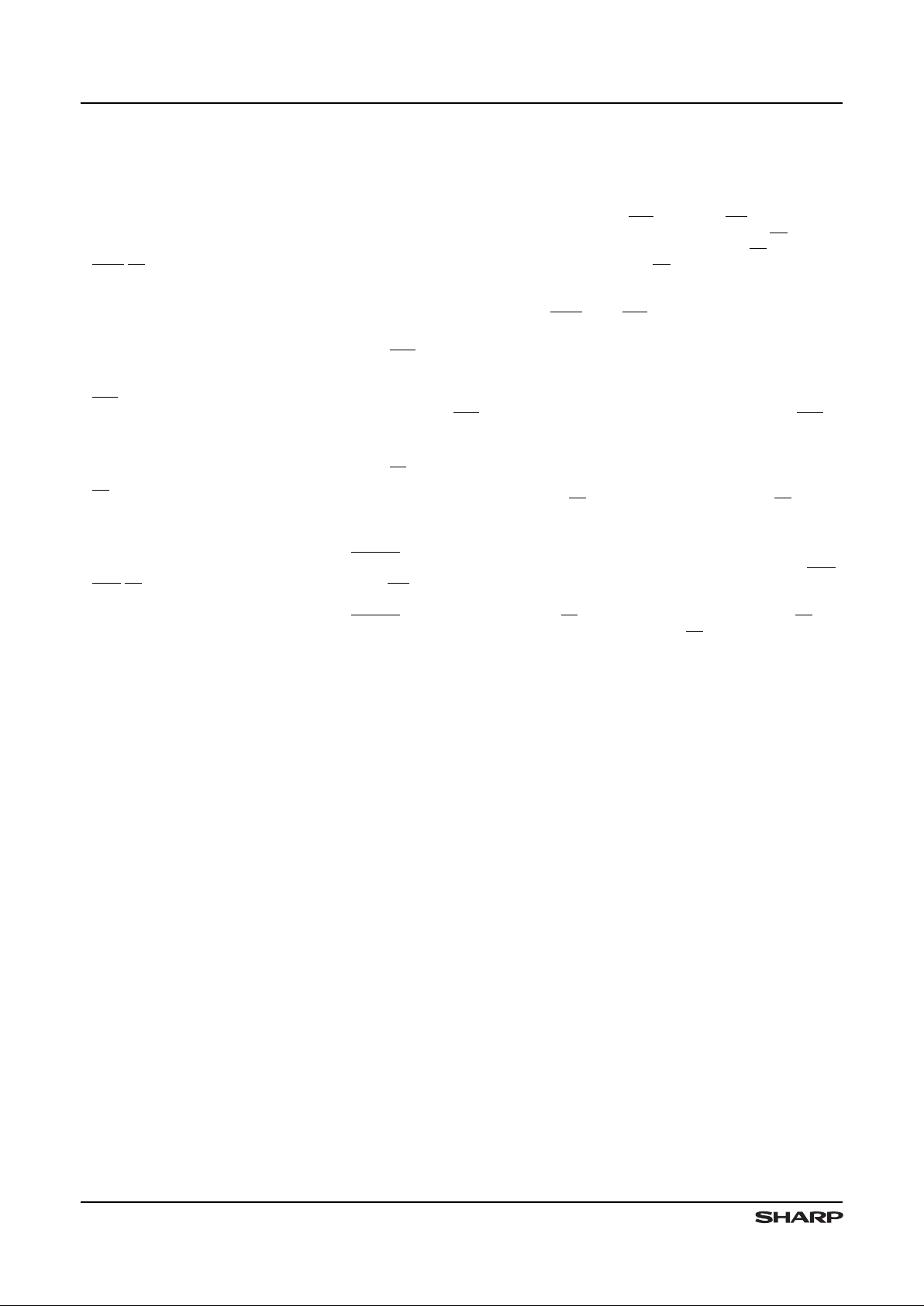

TOP VIEW

540215-2

3 2 1 6867666564636261987654

Q

17

Q

16

Q

15

LD

OE

V

CC

EF

V

CC

D15D16D

17

RCLK

REN

RS

16

17

18

19

20

23

24

21

22

26

15

11

12

13

14

10

25

D

2

D

0

D

13

D

14

D

11

D

12

D

9

D

10

D

8

V

CC

D

7

D

5

D

6

D

3

D

4

D

1

55

54

53

52

51

48

47

50

49

46

44

60

59

58

57

56

45

Q

11

V

CC

Q

10

Q

9

Q

8

Q

7

EMODE

*

Q

6

Q

5

Q

4

V

CC

Q

14

Q

13

Q

12

33 34 35 36 37 38 39 40 41 42 4327 28 29 30 31 32

Q2Q

3

WXO/HF

Q

0

Q

1

V

CC

V

CC

FL/

RT

WCLK

RXO/

EF

2

FF

RXI/

REN

2

PAF

WXI/

WEN

2

WEN

PAE

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

BOLD ITALIC = Enhanced Operating Mode.

*

This pin is VCC on IDT pinout; if EMODE pin is simply

biased to V

CC

, part will behave identical to IDT functionality.

68-PIN PLCC

Figure 2. Pin Connections for 68-Pin PLCC Package

BOLD ITALIC = Enhanced Op erating Mode

512 x 18/1024 x 18 Synchronous FIFO L H540215/25

3

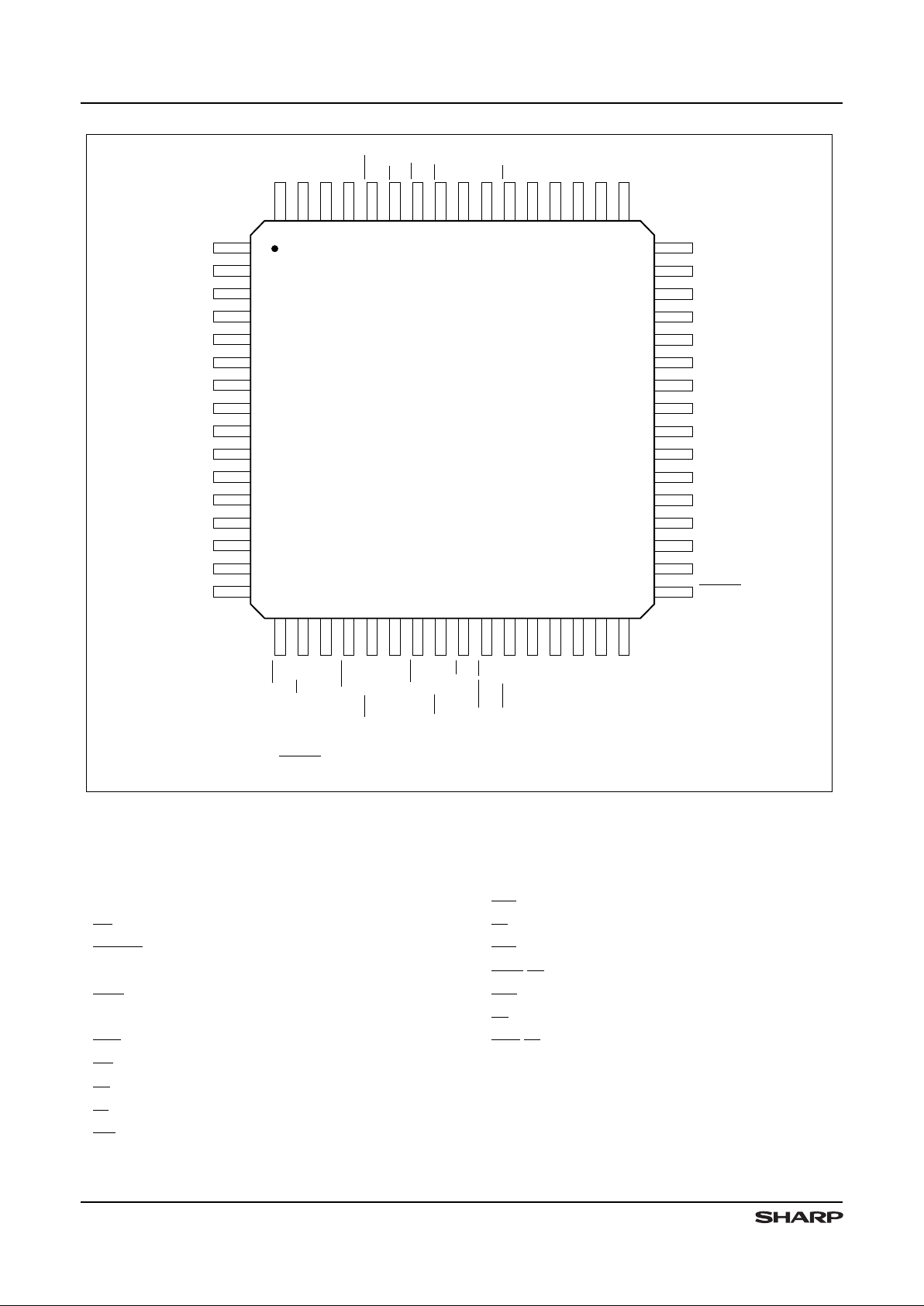

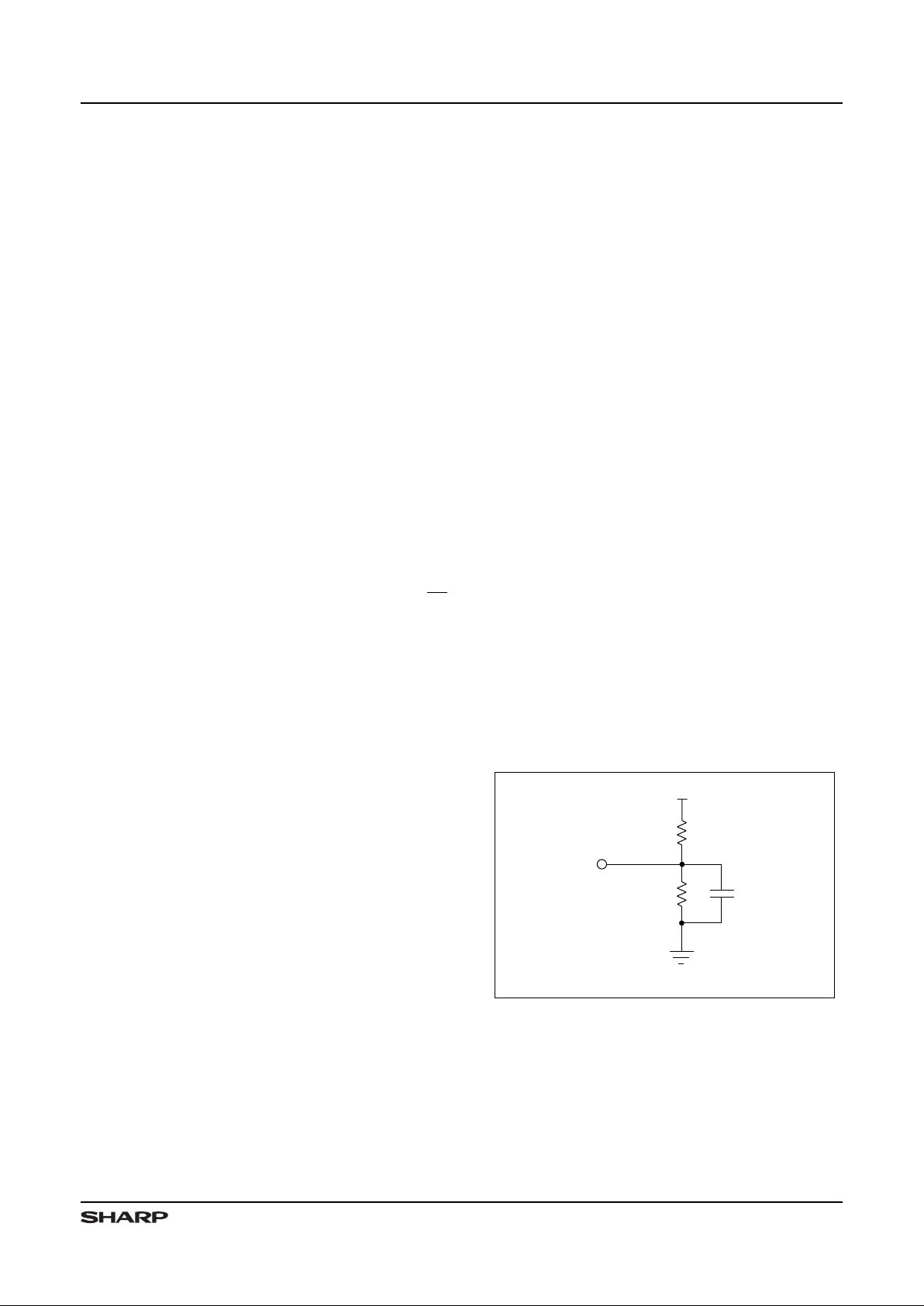

TOP VIEW

540215-34

58 57 56 55 54 53 52 51 50 4964 63 62 61 60 59

Q

17

Q

16

LD

OE

V

CC

EF

V

CC

D16D

17

REN

RS

7

8

9

10

11

14

15

12

13

6

2

3

4

5

1

16

D

2

D

0

D

13

D

15

D

11

D

12

D

9

D

10

D

8

D

7

D

5

D

6

D

3

D

4

D

1

RCLK

D

14

43

42

41

40

39

36

35

38

37

44

48

47

46

45

34

Q

14

Q

11

Q

12

Q

10

Q

9

Q

7

Q

8

Q

5

Q

6

Q

4

Q

13

33

Q

15

23 24 25 26 27 28 29 30 31 3217 18 19 20 21 22

Q

0

Q

1

PAF

FF

PAE

FL/

RT

WCLK

WXI/

WEN

2

WXO/HF

WEN

Q

2

V

CC

Q

3

64-PIN TQFP

V

CC

V

SS

V

SS

V

SS

V

SS

V

SS

EMODE

*

V

SS

RXO/

EF

2

RXI/

REN

2

V

SS

BOLD ITALIC = Enhanced Operating Mode.

*

This pin is VCC on IDT pinout; if EMODE pin is simply

biased to V

CC

, part will behave identical to IDT functionality.

Figur e 3. Pin Connect ion s for 64-Pi n TQFP Package

SUMMARY OF SIGNALS /PINS

PIN NAME

D0 – D

17

Data Inpu ts

RS Reset

EMODE Enhan ced Ope rati ng Mod e

WCLK Write Clock

WEN Write Enable

RCLK Read Cloc k

REN Read Enab le

OE Output Enable

LD Load

FL

/RT

First Load/

Retransmit

RXI

/REN

2

Read Expa nsio n Input/

Read Enable 2

PIN NAME

WXI

/WEN

2

Wri te Expa nsio n Input /

Write Enable 2

FF Full Flag

PAF Prog ramm abl e Almo st- Full Flag

WXO/HF Write Expansion Output/Half-Full Flag

PAE P rog ramm abl e Almo st- Empt y Fla g

EF Empty Flag

RXO/

EF

2

Read Expansion Output

/Empty Flag 2

Q0 – Q

17

Data Outputs

V

CC

Power

V

SS

Ground

BOLD ITALIC = Enhanced Op erating Mode

LH540215/25 512 x 18/1024 x 18 Synchronous FIFO

4

PIN LIST

SIGNAL NAME PLCC PIN NO. TQFP PIN NO.

RS 1 57

OE 2 58

LD 3 59

REN 4 60

RCLK 5 61

D

17

763

D16864

D1591

D1410 2

D

13

11 3

D

12

12 4

D

11

13 5

D

10

14 6

D

9

15 7

D

8

17 8

D

7

19 9

D

6

20 10

D

5

21 11

D

4

22 12

D

3

23 13

D

2

24 14

D

1

25 15

D

0

26 16

PAE 27 17

FT/

RT

28 18

WCLK 29 19

WEN 30 20

WXI/

WEN

2

31 21

PAF 33 23

RXI/

REN

2

34 24

FF 35 25

WXO/HF 36 26

RXO/

EF

2

37 27

Q

0

38 28

SIGNAL NAM E PLCC PIN NO. TQFP PIN NO.

Q

1

39 29

Q

2

41 31

Q

3

42 32

Q

4

44 34

Q

5

46 36

Q

6

47 37

EMODE

48 33

Q

7

49 38

Q

8

50 39

Q

9

52 41

Q

10

53 42

Q

11

55 44

Q

12

56 45

Q

13

58 47

Q

14

59 48

Q

15

61 50

Q

16

63 52

Q

17

64 53

EF 66 54

V

SS

662

VCC16 NC

V

SS

18 NC

V

CC

32 22

V

SS

40 30

V

CC

43 NC

V

SS

45 35

V

SS

51 40

V

CC

54 43

V

SS

57 46

V

CC

60 49

V

SS

62 51

V

CC

65 NC

V

SS

67 55

V

CC

68 56

BOLD ITALIC = Enhanced Op erating Mode

512 x 18/1024 x 18 Synchronous FIFO L H540215/25

5

PIN DESCRIPTIONS

PIN NAME

PIN

TYPE

1

DESCRIPTION

D0 – D

17

Data Inputs I Data inputs from an 18-bit bus.

RS Reset I

When

RS is taken LOW, the FIFO’s internal read and write pointers are set to

address the first physical location of the RAM array;

FF, PAF, and HF go HIGH;

and

PAE and EF go LOW . The pro gra mmab le- flag -of fs et regi ster s

and the

Control Register

are set to their default values. (But see the description of

EMODE

, below.) A reset operation is required before an initial read or write

operati on afte r power -up .

EMODE

Enhan ced

Opera tin g

Mode

I

When EMODE is tied LOW, the default setting for Control Register bits 00-05

after a reset operation changes to HIGH rather than LOW, thus enabling all

Control-Register-controllable Enhanced Operating Mode features, and

allowing access to the Control Register for reprogramming or readback.

(See Tables 1, 2, and 5.) If this behavior is desired,

EMODE may be

grounded; however, Control Register bits 00-05 still may be individually

program med to sel ecti vel y enabl e or disabl e certa in of the Enh ance d Mode

features, even though those features associated with interlocked-paralleled

operat ion alw ays are ena bled whenev er

EMODE is being asserted. (See

Table 2.) Alternatively,

EMODE may be tied to V

CC,

so that the FIFO is

functi onal ly IDT-co mpat ibl e, and the Con tro l Regis ter is not accessi ble or

visible, and all of its bits remain LOW.

Controlling EMODE dynamica lly

during system ope rati on is not recomme nded .

WCLK Write Clock I

Data is written into the FIFO on a LOW-to-HIGH transition of WCLK, whenever

WEN (Write Enable) is being asserted (LOW), and LD is HIGH. If LD is LOW, a

progra mmab le regi ster rathe r than the int erna l FIFO mem ory is writ ten into.

In the

Enhanced Operating Mode, WEN

2

is ANDed with WEN to produce an

effec tiv e inter nal wri te- enab le sign al.

2

WEN Write Enable I

When

WEN is LOW and LD is HIGH, an 18-bit data word is written into the FIFO

on every LOW-to-HIGH transition of WCLK. When

WEN is HIGH, the FIFO

internal memory continues to hold the previous data. (See Table 3.) Data will not

be written into the FIFO if

FF is LOW.

In the Enhanced Operating Mode, WEN

2

is ANDed wit h WEN to prod uce an effec tive intern al writ e-e nab le sign al.

2

RCLK Read Cloc k I

Data is read from the FIFO on a LOW-to-HIGH transition of RCLK whenever

REN

(Read Enable) is being asserted (LOW), and

LD is HIGH. If LD is LOW , a

progra mmab le regi ster rathe r than the int erna l FIFO mem ory is read from.

In the

Enhanced Operating Mode, REN

2

is ANDed with REN (and whenever

Contro l Regis ter bit 05 is HIGH, also wit h

OE) to prod uce an ef fect ive

internal read-enable signal.

2

REN Read Enab le I

When REN is LOW and LD is HIGH, an 18-bit data word is read from the FIFO on

every LOW-to-HIGH transition of RCLK. When

REN is HIGH, and/or also when

EF is LOW, the FIFO’s output register continues to hold the previous data word,

whether or not Q

0

– Q17 (the data outputs) are enabled. (See Table 3.)

In the

Enhanced Operating Mode, REN

2

is ANDed with REN (and whenever

Contro l Regis ter bit 05 is HIGH, also wit h

OE) to prod uce an ef fect ive

internal read-enable signal.

2

OE Output Enable I

When

OE is LOW, the FIFO’s data outputs drive the bus to which they are

connect ed. If

OE is HIGH, the FIFO’s outputs are in high-Z (high-impedance)

state.

In the Enhanced Operating Mode, OE not only continues to control the

outputs in this same manner, but also can function as an additional ANDing

input to the com bine d eff ect ive read -en able signal , alon g with

REN and

REN

2

, whenever Control Register bit 05 is HIGH. (See Table 5.)

2

1

I = Input, O = Output, Z = High-Impedance, V = Power Vo ltage Level

2

The ostensible differences in signal assertivenes s are reconciled before ANDing.

BOLD ITALIC = Enhanced Op erating Mode

LH540215/25 512 x 18/1024 x 18 Synchronous FIFO

6

PIN DESCRIPTIO NS (cont’d)

PIN NAME

PIN

TYPE

1

DESCRIPTION

LD Load I

When

LD is LOW, the data word on D0 – D17 (the data input s) is writ ten int o a

programmable-flag-offset register,

or into the Control Register (when in the

Enhanced Operating Mode),

on the LOW-to-HIGH transition of WCLK, whenever

WEN is LOW. (See Table 3.) Also, when LD is LOW, a word is read to Q0 – Q17 (the

data outputs) from the offset registers

and/or the Contro l Regis ter (wh en in the

Enhanced Operating Mode)

on the LOW-to-HIGH transition of RCLK, whenever

REN is LOW. (See again Table 3, and particularly the Notes following this table.)

When

LD is HIGH, normal FIFO write and read operations are enabled.

FL

/RT

First Load /

Retran smit

I

In the standalone or paralleled configuration,

FL/RT should be LOW during a reset

operation. (See Tables 1 and 2.)

However, thereafter, in the standalone or

paralleled configuration, if

FL is taken HIGH, it functions instead as RT

(Retransmit), and resets the FIFO’s internal read pointer to the first physical

locati on of the RAM array . Note that alt hou gh Retr ans mit is an ‘en han ced’

feature, it is always available for a FIFO during standalone operation, whether

the FIFO is in IDT-Compatible Operating Mode or in Enhanced Operating

Mode; it is not regula ted eit her by the Contro l Regis ter or by the

EMODE

control input.

In IDT-compatible cascaded configuration, FL has an entirely

different function; it is grounded for the first FIFO device (the ‘master’ device or ‘firstload’ device), and is set to HIGH for all other FIFO devices in the daisy chain. Thus,

the

Retransmit

feature is not available for FIFOs operating in an IDT-compatible

cascaded configuration.

WXI

/WEN

2

Write

Expansion

Input/

Write

Enable 2

I

This signal is dual-purpose; its functionality is determined during a reset operation,

accordi ng to its own stat e, and also accord ing to the stat es of the thre e other

control inputs

RXI

/REN

2

, FL

/RT

, and

EMODE

. (See Tables 1 and 2.) In the

standal one or paralle led con figu rat ion,

WXI/

WEN

2

is grounded. In the cascaded

configuration,

WXI/

WEN

2

is connecte d to WXO (Write Expansion Output) of the

previous device, and functions as

WXI.

In the Enhanced Operating Mode,

WXI/WEN2 functio ns as a second write- ena ble sig nal , WEN2, which is ANDed

with

WEN to prod uce an ef fect ive intern al writ e-e nabl e sign al.

2

RXI

/REN

2

Read

Expansi on

Input/

Read

Enable 2

I

This signal is dual-purpose; its functionality is determined during a reset operation,

accordi ng to its own stat e, and also accord ing to the stat es of the thre e other

control inputs

WXI

/WEN

2

, FL

/RT

, and

EMODE

. (See Tables 1 and 2.) In the

standal one or paralle led con figu rat ion,

RXI/

REN

2

is grounded. In the cascaded

configuration,

RXI/

REN

2

is connecte d to RXO (Read Expansion Output) of the

previous device, and functions as

RXI.

In the Enhanced Operating Mode,

RXI/REN2 functions as a second read-enable signal, REN2, which is AND ed

with

REN – and perhaps also with OE, if Cont rol -Reg ist er bit 05 is HIGH – to

produce an effective internal read-enable signal.

2

FF Full Flag O

When

FF is LOW, the FIFO is full; further advancement of its internal write-address

pointer, and further data writes through its Data Inputs into its internal memory

array, are inhibited. Whe n

FF is HIGH, the FIFO is not full. FF is synch ron ized to

WCLK.

PAF

Progra mmab le

Almost-Full Flag

O

When

PAF is LOW, the FIFO is ‘almost full,’ based on the almost-full-offset value

programmed into the FIFO’s Almost-Full Offset Register. The default value of this

offset at reset is one-eighth of the total number of words in the FIFO-memory array,

minus one, measured from ‘full.’ (See Table 4.) In the IDT-Compatible Operating

Mode,

PAF is asynchronous.

In the Enhance d Opera tin g Mode, P AF is

synchronized to WCLK after a reset operation, according to the state of

Control Register bit 04. (See Table 5.)

NOTES:

1. I = Input, O = Output, Z = High-Impedance, V = Power Voltage Level

2. The ostensib le differences in sign al assertiveness are reconciled before ANDing.

BOLD ITALIC = Enhanced Op erating Mode

512 x 18/1024 x 18 Synchronous FIFO L H540215/25

7

PIN NAME

PIN

TYPE

1

DESCRIPTION

WXO/HF

Write

Expansion

Output/

Half-Full Flag

O

This signal is dual-purpose; its functionality is determined during a reset operation

according to the states of the two control inputs

WXI/

WEN

2

and RXI/

REN

2

. (See

T a bles 1 and 2.) In the standal one or para llel ed conf igur ati on, when ever

HF is LOW

the device is more than half full. In IDT-Compatible Operating Mode,

HF is

asynchronous;

in the Enhanced Operating Mode, HF may be synchronized

either to WCLK or to RCLK after a reset operation, according to the state of

Control Register bits 02 and 03. (See Table 5.)

In the IDT-compatible cascaded

configuration, a pulse is sent from

WXO to the WXI input of the next FIFO in the

daisy-chain cascade, whenever the last location in the FIFO is written.

PAE

Programmable

Almost-Empty

Flag

O

When PAE is LOW, the FIFO is ‘almost empty,’ based on the almo st- empt y-o ff set

value programmed into the FIFO’s Almost-Empty Offset Register. The default value

of this offset at reset is one-eighth of the total number of words in the FIFO-memory

array, minus one, measured from ‘empty.’ (See Table 4.) In IDT-Compatible

Operati ng Mode ,

P AE is async hro nous .

In the Enhanced Operating Mode, PAE

is synchron ize d to RCLK afte r a reset oper ati on, acc ordi ng to the sta te of

Control Register bit 01. (See Table 5.)

EF Empty Flag O

When

EF is LOW, the FIFO is empty; further advancement of its internal readaddress pointer, and further readout of data words from its internal memory array to

its Data Outputs, are inhibited. When

EF is HIGH, the FIFO is not empty. EF is

synchronized to RCLK.

RXO

/EF

2

Read

Expansion

Output

O

This signal is dual-purpose; its functionality is determined by the state of the

EMODE

control input during a reset operation. (See Tables 1 and 2.) In the IDT-

Compatible Operating Mode, in a cascaded configuration, a pulse is sent from

RXO

to the

RXI input of the next FIFO in the daisy-chain cascade, whenever the last

location of the FIFO is read.

In the Enhanced Operating Mode, whenever

EMODE is being asserted (LOW), EF2 behaves as an exact duplicate of EF,

but delayed by one full cycle of RCLK with respect to

EF.

Q0 – Q

17

Data Outputs O/Z Data outputs to drive an 18-bit bus.

V

CC

Power V +5 V power-supply pins.

V

SS

Ground V 0 V ground pins.

NOTE:

1. I = Input, O = Output, Z = High-Impedance, V = Power Voltage Level

PIN DESCRIPTIONS (cont’d)

BOLD ITALIC = Enhanced Op erating Mode

LH540215/25 512 x 18/1024 x 18 Synchronous FIFO

8

ABSOLUTE MAXIMUM RATINGS

PARAMETER RATING

Supply Voltage to VSS Potentia l –0.5 V to 7 V

Signal Pin Voltage to V

SS

Potenti al –0.5 V to VCC + 0.5 V

DC Output Current

1

±75 mA

Temperature Range wit h Powe r Appli ed

2

–55°C to 125°C

Stora ge Temperatur e Rang e –65°C to 150°C

Power Dissipation (PLCC Package Limit) 2 W

NOTES:

1. O nly one out put may be shorted at a time, for a period not exceed ing 30 seconds.

2. Measured with clocks idle.

OPERATING RANGE

SYMBOL PARAMETER MIN. MAX. UNIT

T

A

T emper ature, Amb ient

070C

V

CC

Supply Voltage 4.5 5.5 V

V

SS

Supply Voltage 0 0 V

V

IL

Logic LOW Input Voltage –0.5 0.8 V

V

IH

Logic HIGH Input Voltage 2.0 VCC + 0.5 V

DC ELECTRICAL CHARACTERISTICS (Over Operating Range)

SYMBOL PARAMETER TEST CONDITIONS MIN. MAX. UNIT

I

LI

Input Leakage VCC = 5.5 V, VIN = 0 V to V

CC

–10 10 µA

I

LO

I/O Leakage OE ≥ VIH, 0 V ≤ V

OUT

≤ V

CC

–10 10

µA

V

OH

Output HIGH Vo ltag e IOH = –12.0 mA 2.4 V

V

OL

Output LOW V ol tage IOL = 16.0 mA 0.4 V

I

CC

Average Operating Supply Current

1

Measur ed at fCC = 50 MHz 190 mA

I

CC2

Average Standby Supply Current All inputs = V

IH

MIN. (cl ocks idle) 25 mA

I

CC3

Power-Down Supply Current All inputs = VCC – 0.2 V (clocks idle) 1 mA

NOTE:

1. Output load is disconnected.

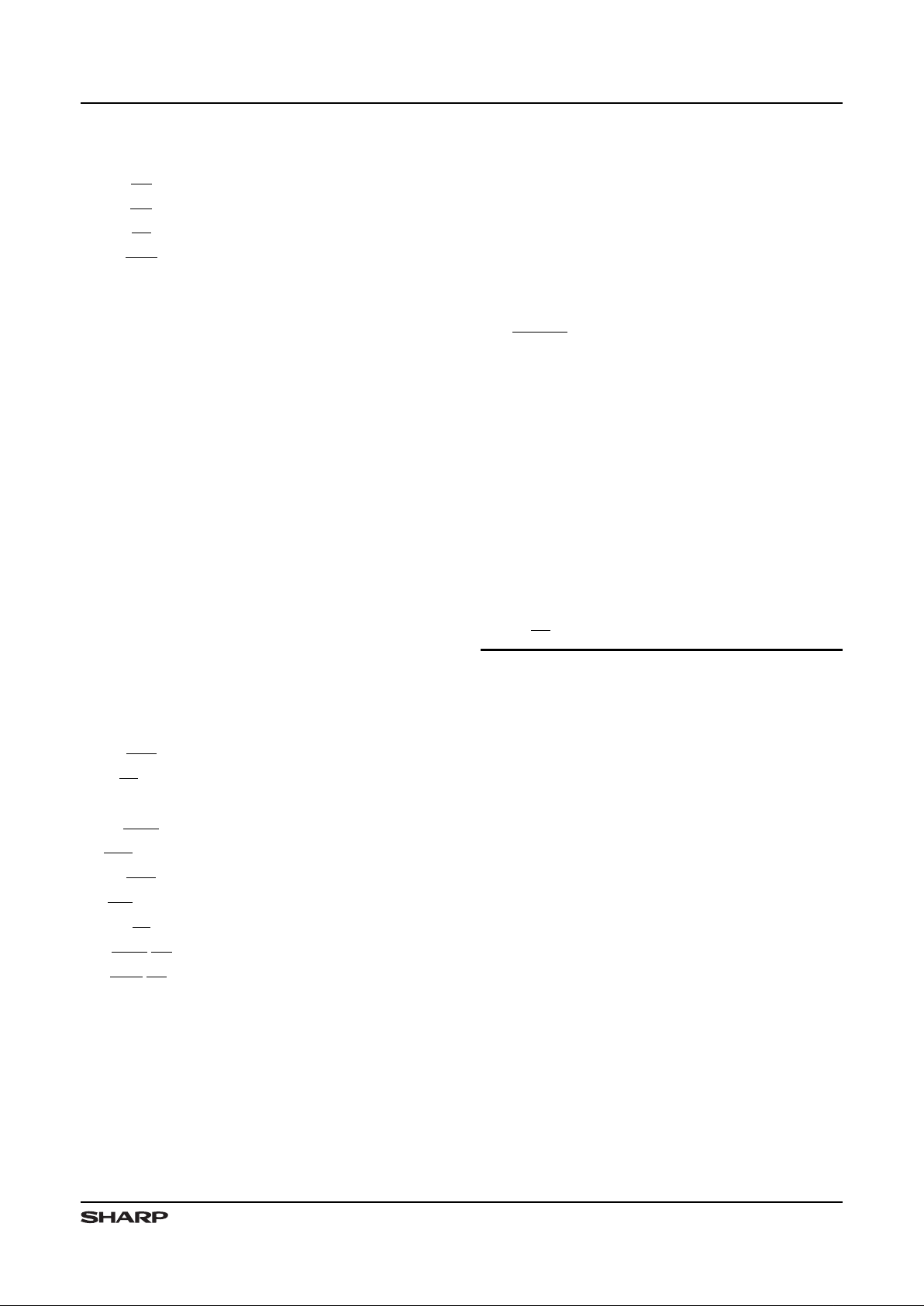

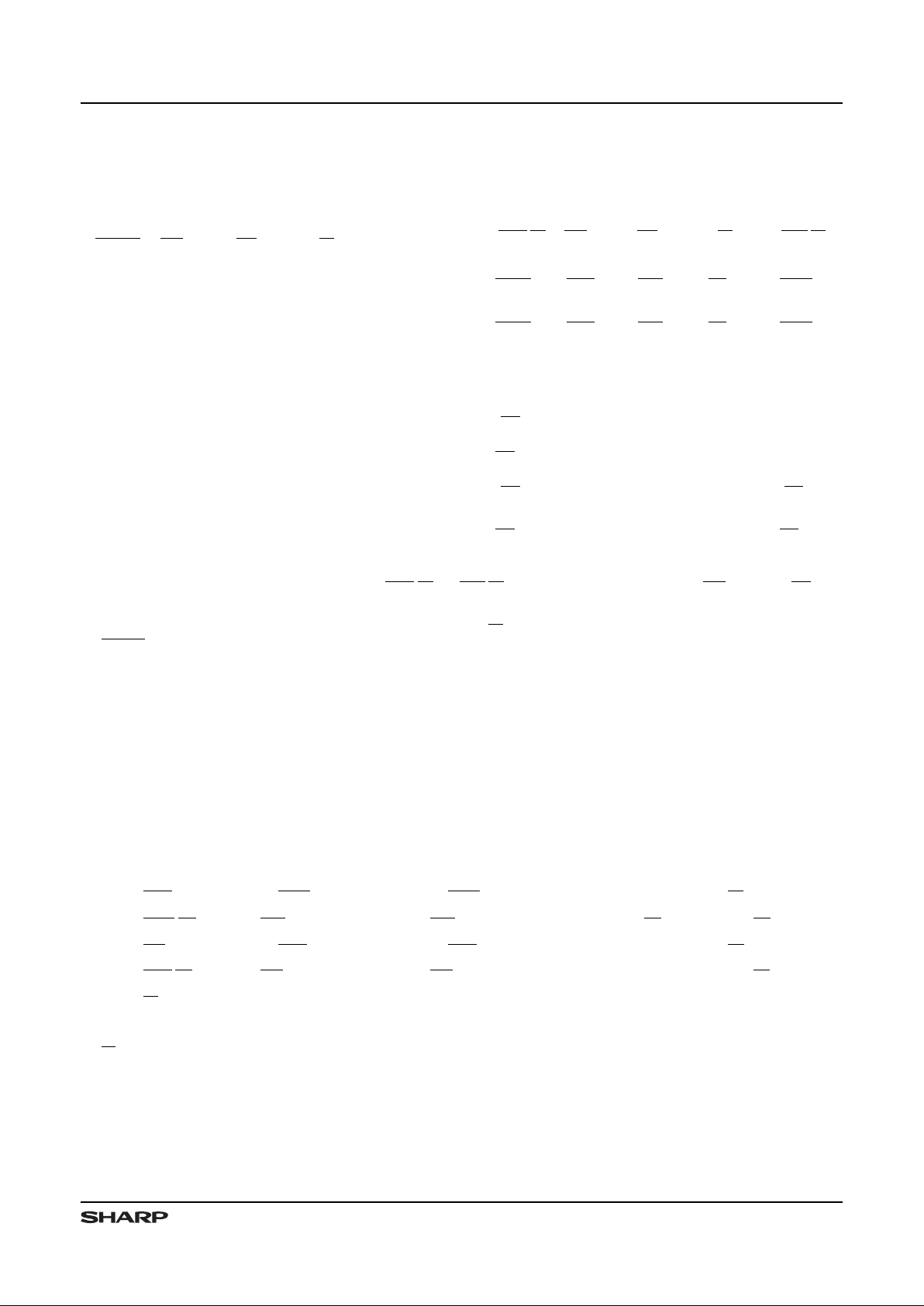

AC TE ST C O N DIT IO N S

PARAMETER RATING

Input Puls e Levels VSS to 3 V

Input Rise and Fall T ime s

(10% to 90%)

3 ns

Input T imi ng Refe renc e Level s 1.5 V

Output Tim ing Ref ere nce Leve ls 1.5 V

Output Load,

Tim ing Tests

(Figure 4)

R

1

(Top Resistor ) 1.1k Ω

R

2

(Bottom Resist or)

680 Ω

C

L

(Load Capacitance) 30 pF

CAPACITANCE

1, 2

PARAMETER RATING

CIN (Input Capacitance) VIN = 0 V 8 pF

C

OUT

(Output Capaci tanc e) V

OUT

= 0 V 8 pF

NOTES:

1. Sample tested onl y.

2. Capacitances are maximum values at 25°C, measured at

1.0 MHz, with V

IN

= 0 V.

540215-3

DEVICE

UNDER

TEST

+5 V

30 pF

1.1 k Ω

680 Ω

INCLUDES JIG AND SCOPE CAPACITANCES

*

*

Figure 4. Output Load Circuit

BOLD ITALIC = Enhanced Op erating Mode

512 x 18/1024 x 18 Synchronous FIFO L H540215/25

9

AC ELECTRICAL CHARACTERISTICS

SYMBOL PARAMETER

–20 –25 -35

MIN. MAX. MIN. MAX. MIN. MAX.

f

CC

Clock Cycle Frequency 50 40 28.6

t

A

Data A cces s T ime 2 12 3 15 3 20

t

CLK

Clock Cycle Time 20 25 35

t

CLKH

Clock HIGH Time 8 10 14

t

CLKL

Clock LOW Time 8 10 14

t

DS

Data Set up T ime 5 6 7

t

DH

Data Hol d Ti me 2 2 2

t

ENS

Enable Setup Time 5 6 7

t

ENH

Enable Hold Time 2 2 2

t

RS

Reset Pulse Width

1

20 25 35

t

RSS

Reset Setup Time

2

12 15 20

t

RSR

Reset Recovery Time

2

12 15 20

t

RSF

Reset to Flag and Output Time 30 35 40

t

OLZ

Output Enable to Output in Low-Z

2

000

t

OE

Output Enable to Output Valid 9 12 15

t

OHZ

Output Enable to Output in High-Z

2

19112115

t

WFF

Write Clock to Full Flag 12 15 20

t

REF

Read Clock to Empty Flag 12 15 20

t

PAF

Clock to Programmable Almost-Full Flag (IDT-Compatible Operating

Mode)

14 17 23

t

PAE

Clock to Programmable Almost-Empty Flag (IDT-Compatible

Operating Mode)

14 17 23

t

HF

Clock to Half-Fu ll Flag (IDT - Comp ati ble Oper ati ng Mode ) 14 17 23

t

PAFS

Clock to Programmable Almost-Full Flag

(Enhanced Operating Mode)

14 17 23

t

PAES

Clock to Programmable Almost-Empty Flag

(Enhanced Operating Mode)

14 17 23

t

HFS

Clock to Half-Full Flag (Enhanced Operating Mode) 14 17 23

t

XO

Clock to Expansion-Out 12 15 20

t

XI

Expan sion -In Pul se Width 7 9 13

t

XIS

Expan sion -In Set up T ime 7 9 14

t

SKEW1

Skew Time Between Read Clock and Write Clock for Full Flag

3

91116

t

SKEW2

Skew T ime Bet ween Write Clock and Read Clock for Emp ty Flag

4

91116

NOTES:

1. Pulse widths less than the stated minimum values may cause incorrect oper ation.

2. Values are guaranteed by design; not c urrently tested.

3. These times also apply to the Programmable-Almost-Full and Half-Full flags when they are synchronized to WCLK.

4. These times also apply to the Half-Full and Prog rammable-Almost-Empty flags when they are synchronized to RCLK.

BOLD ITALIC = Enhanced Op erating Mode

LH540215/25 512 x 18/1024 x 18 Synchronous FIFO

10

DESCRIPTION OF SIGNALS AN D

OPERATING SEQUENCES

T abl e 1. Gro upin g-Mode Det erm inatio n

During a Reset Oper ation

5

EMODE

WXI/

WEN

2

RXI/

REN

2

FL/

RT

MODE

WXO/HF

USAGE

WXI/

WEN

2

USAGE

RXI/

REN

2

USAGE

FL/

RT

USAGE

RXO

/EF

2

USAGE

H

1

HHH

Cascaded

Slave

2

WXO WXI RXI FL RXO

H

1

HHL

Cascaded

Master

2

WXO WXI RXI FL RXO

H

HLX

(Reser ved)

–––––

H

LHX

(Reser ved) –––––

H

LL H

3

(Not Allowed

During Reset )

(HF) (no ne) (none)

(RT)

(none)

H

LL L

3

Standalone HF (none) (none)

RT

(none)

LXX

H

3

(Not Allowed

During Reset)

(HF) (WEN2) (REN2) (RT) (EF2)

LXX

L

3

Interlocked

Paralleled

4

HF WEN

2

REN

2

RT EF

2

NOTES:

1. In IDT-compatible cascading, a reset operation forces

WXO/HF and RXO/

EF2

HIGH for the nth FIFO, thus forcing WXI/

WEN2

and RXI/

RE N

2

HIGH for the (n + 1)st FIFO.

2. The terms ‘master’ and ‘slave’ refer to IDT-compatible casca ding . In pipelined casca ding4, there is no such distinction.

3. Once grouping mode has been determined during a reset operation, FL/RT then may go HIGH to activate a retransmit operation.

4. EMODE must be asserted for access to the Control Register to be enabled. Also, FIFOs being used in a pipelined-cascading

configuration should be in Interlocked Paralleled mode.

5. Setup-time and recovery-time specifications apply during a reset operation.

6. H = HIGH; L = LOW; X = Don’t Care.

T abl e 2. Expansi on- Pin Usage According to

Groupi ng Mo de

I/O PIN

IDT-COMPATIBLE OPERA TING MODE

ENHAN CED

OPER ATING MODE

DEPTH-CASCA DED

MASTER

DEPTH-CASCADED

SLAVE

STANDALONE

INTERLOCKED

PARALLELED

I WXI /

WEN

2

From WXO ((n-1)st FIFO) From WXO ((n-1)st FIFO) Grounded

From FF (other FIFO)

O WXO/HF To WXI ((n+1)st FIFO) To WXI ((n+1)st FIFO) Becomes HF

Becomes HF

I

RXI/

REN

2

From RXO ((n-1)st FIFO) From RXO ((n-1)st FIFO) Grounded

From EF (other FIFO)

O RXO

/EF

2

To RXI ((n+1)st FIFO) To RXI ((n+1)st FIFO) Unused

Becomes EF

2

I FL/

RT

Grounded (Logic LOW) Logic HIGH

Becomes RT1Becomes RT

1

NOTE:

1.

FL/RT may be grounded if

the Retransmit fa cility

is not being used.

BOLD ITALIC = Enhanced Op erating Mode

512 x 18/1024 x 18 Synchronous FIFO L H540215/25

11

T abl e 3. Select ion of Re ad and Wri te Oper ati ons

LD WEN

3,4

REN

3, 4

WCLK RCLK ACTION

LXX– –

No operation.

LLL

∧∧

Illegal combination, which will cause errors.

LLH

∧

X Write to a programmable register.

1

LHH ∧ X

Hold present value of programmable-register write counter, and do not

write.

2

LH L X ∧Read from a programmable register.

1

LHHX

∧

Hold present value of programmable-register read counter, and do not

read.

2

HL X

∧

X Normal FIFO write operation.

HXLX

∧

Normal FIFO read operation.

H L X – X No write operation.

HHXXX

No write operation.

H X L X – No read operation.

H X H X X No read operation.

H L L – – No operation.

KEY:

H = Logic ‘HIGH’; L = Logic ‘LOW’; X = ‘Don’t-care’ (logic ‘HIGH,’ logic ‘LOW,’ or any transition);

∧ = A ‘LOW’-to-‘HIGH’ transition; – = Any condition EXCEPT a ‘LOW’-to-‘H IGH’ transition.

NOTES:

1. The selection of a programmable register to be written or read is controlled by two simple s tate machines. One state machine controls the selection for writing; the other state machine controls the selection for reading. These two state machines operate independently of each other.

Both state machines are reset to point to Word 0 by a reset operation.

In the Enhanced Operating Mode, if Control Register bit 00 is set,

both state machines are al s o reset to point to Word 0 by deassertion of LD after LD has been asserted (that is, by a rising edge of

LD), followed by a valid memory array write cycle for the writing-control state machine and/or by a valid memory array read cycle

for the reading-control state machine.

2. The order of the two programmable registers which are accessible in IDT-Compatible Operating Mode, as selected by either state machine, is

always:

Word 0: Almost-Empty Offset Register

Word 1: Almost-F ull O f fse t Regi ster

Word 0: Almost-Empty Offset Register

...

(repeats indefinitely)

...

The order of the three programmable registers which are accessible in Enhanced Operating Mode, as selected by either state

machine , is al ways:

Word 0: Almo s t-Empty Offset Reg ist er

Wo rd 1: Almost-Full Offset Register

Wo rd 2 : Control Register

Wo rd 0: Almost-Empty Offset Register

………

…

(repeats indefinitely)

………

…

Note that, in IDT-Compatible Operating Mode, Word 2 is not accessed; Word 0 and Word 1 alternate.

3. After normal FIFO operation has begun, writing new contents into either of the offset re gisters should onl y be done when the FIFO is empty .

4. WEN2, REN2, and OE may be ANDed terms in the enabling of read and write operations, accordi ng to the state of the EMODE control

input and of Control Register Bit 05.

BOLD ITALIC = Enhanced Op erating Mode

LH540215/25 512 x 18/1024 x 18 Synchronous FIFO

12

T abl e 4. Status Flags

NUMBER OF UNRE AD DATA WORDS PRE SENT WITHIN FIFO

1, 2

FULL

FLAG

MIDDLE FLAGS

EMPTY

FLAG

512 × 18 FIFO 1024 × 18 FIFO

FF PAF HF PAE EF

0 0 HHHLL

1 to q 1 to q H H H L H

(q + 1) to 256 (q + 1) to 512 HHHHH

257 to (512 – (p + 1)) 513 to (1024 – (p + 1)) H H L H H

(512 – p) to 511 (1024 – p) to 1023 H L L H H

512 1024 L L L H H

NOTES:

1. q = Programmable-Almost-Empty Offset value. (Default values: 512 × 18, q = 63; 1024 × 18, q = 127.)

2. p = Programmable-Almost-Full Offset value. (Default values: 512 × 18, p = 63; 1024 × 18, p = 127.)

3. Only 9 (51 2 × 18) or 10 (1024 × 18) of the 12 offset-value-register bits should be programmed. The unneeded most-signi ficant-end bits sh oul d

be LO W (zero).

4. The f lag outp ut is delayed by one full clock cyc le in Enhanced Operating Mode, when synchronous operation is specified fo r intermediate flags.

DESCRIPTION OF SIGNAL S AND OPERA T I NG SEQUENCES (con t’d)

BOLD ITALIC = Enhanced Op erating Mode

512 x 18/1024 x 18 Synchronous FIFO L H540215/25

13

Tabl e 5. Control-Regi st er Form at

COMMAND

REGISTER

BITS

CODE

VALUE AFTER RES E T FLAG

AFFECTED,

IF ANY

DESCRIPTION NOTES

EMODE = H EMODE = L

00

L

LH–

Deassertion of

LD does not

reset the pro gram mabl eregister write pointer and

read pointer.

IDT - comp ati ble add ress ing

of programmable registers.

H

Deassertion of

LD resets

the programmable-register

write pointer and read

pointer to address Word 0,

the Programmable-AlmostEmpty- Flag -Of fs et Regi ste r .

The change takes effect

after a valid write ope rati on

or a valid read operation,

respect ive ly , to the memo ry

array .

Non-a mbi guou s

addressing of

programmable registers.

01

L

LH

PAE

Set by

↑↑

RCLK, reset by

↑↑

WCLK.

Asynchronous flag

clocking.

H

Set and reset by

↑↑

RCLK.

Synch rono us fla g clock ing.

03, 02

LL

LL HH HF

Set by

↑↑

WCLK, reset by

↑↑

RCLK.

Asynchronous flag

clocking.

LH Set and reset by

↑↑

RCLK.

Synch rono us fla g clock ing

at output port.

HL,

Set and reset by

↑↑

WCLK.

Synch rono us fla g clock ing

at input port.

HH

04

L

L

H

PAF

Set by

↑↑

WCLK, reset by

↑↑

RCLK.

Asynchronous flag

clocking.

H

Set and reset by

↑↑

WCLK.

Synch rono us fla g clock ing.

05

L

LH–

OE has no effect on an

intern al read operat ion ,

apart from disabling the

outputs.

Allows the read-address

point er to adva nce eve n

when Q

0

– Q17 are not

driving the output bus.

H

Deassertion of

OE inhibits

a read operation; whenever

the data outputs Q

0

– Q

17

are in the high-Z state, the

read pointer does not

advance.

Inhibits the read-address

point er fro m advanc ing

when Q

0

– Q17 are not

driving the output bus;

thus, guards against data

loss.

06

L

LL

–

Reserved.

Future use to control depth

cascading and interlocked

paralleling.

H

11, 10,

09, 08, 07

LLLLL LLLLL LLLLL

–

Reserved. Reserved.

NOTES:

1.

When

EMODE

is HIGH, and

Control Register bits 00-05 are LOW,

the FIFO behaves in a manner functionally equiv alent to the

IDT72215B/25B FIFO of similar depth and speed grade. Under these conditions, the

Control Register

is not visible or accessible to the ex-

ter nal syst em whi ch inclu des t he FIFO.

2.

If

EMODE

is not asserted (is HIGH),

Control Register bits 00-05 remain LOW

after a reset operation.

Howeve r, if EMODE is asserted (is

LOW) during a reset operation, Control Register bits 00-05 are forced HIGH, and remain HIGH until cha nged. Control Register bits

06-11 are unaffected by EMODE .

BOLD ITALIC = Enhanced Op erating Mode

LH540215/25 512 x 18/1024 x 18 Synchronous FIFO

14

Data Inputs

DATA IN (D0 – D17)

Data, progra mmable-flag-offset values, and

Control-

Register

codes are input to the FIFO as 18-bit words on

D0 – D17. Unused bit positions in offset-v alue

and Con-

trol-Register

words should be zero-filled.

Control Inputs

RESET (RS)

The FIFO is reset whenever the asynchro nous Reset

(RS) input is taken to a LOW state. A reset operation is

required after power-up, be fore the first write operation

may occur. The state of the FIFO is fully defined after a

reset operation. If the default values which are entered

into the Progra mmable-Fl ag-Offset-Value Registers

and

the Control Register

by a reset operation are acceptable, then no device programming is required. A reset

operat ion init ializes the FIFO’s internal read-add ress and

write-a ddress point ers to the FIFO’s f irst physical memory

location. The five sta tus flags, FF, PA F, HF, PA E, and EF,

are updated to indicate that the FIFO is completely empty;

thus, the first three of these are reset to HIGH, and the

last two are re set to LOW . The f lag -of fse t values for PAF

and P A E each are init ialize d to one- eight h of th e de pth of

a single FIFO, minus one; 63 for a 512-word FIF O, and

127 for a 1024-word FIFO. If

EMODE

is not being as-

sert ed (i.e. , if

EMOD E

is HIGH), all

Contro l Register

bits

are initialized to LOW, to configur e the FIFO to opera te in

the IDT72215B/ 25B-Compati ble Opera ting Mode. Unt il a

write opera tion occu rs, the data output s D0 – D17 all are

LOW whenever OE is LOW.

ENHANCED OPERATING MODE (EMODE)

Whenever EMODE is asserted during a reset operation, Contr ol Register bits 00 – 05 re main HIGH

rather than LOW after the completion of the reset

operation. Thus, EMOD E has the effe ct of act iva tin g

all of the Enhanced- Opera ting- Mod e featur es durin g

a reset operation. Subsequently, they may be individual ly disabl ed or re-enabl ed by changing the set ting of Control-Regis ter bi ts. The behavior of these

Enhanced-Opera ting-Mode features is described in

Table 5. For permanent Enhanced-Operating-Mode

operation, EMODE must be grounded; dy nami c c ontrol of EM OD E during sys tem oper ation is not recom mended.

Asser ting EMODE during a reset operation also

causes WXI/WEN2 to be configured as WEN2, and

RX I/REN2 to be conf igured as RE N2, to support interlocked-paralleled operation of two FIFOs ‘side by

side. (See Figur e 27.) Additional ly , RXO/EF2 is conf igured as EF2, which dupl icate s the EF signal with one

extra RCK cycle delay, in order to provide proper

timing for ‘pipelined’ cascaded opera tion.

WRITE CLOCK (WCLK)

A rising ed ge (LO W-to-HIGH transition) of WCLK in iti ates a FIFO w rite cycle if LD is HIGH, or a programmable-re giste r write cycle if LD is LO W . The 18 da ta inputs,

and a ll input-side synchronous control inputs, mus t meet

setup and hold times with respect to the rising edge of

WCLK. The input-side sta tus flags are meaningful after

specified time interva ls, following a rising edge of WCLK.

Conceptua lly, the WCLK input r eceives a free-running ,

periodic ‘clock’ waveform, which is used to control other

signals which are edg e-sensit ive. Howeve r, th ere actually

is not any abso lute requirem ent t hat the W CLK wavef orm

must

be periodic. An ‘asynchronous’ mode of operation

is in fact possible, i f WEN is continuously asserted (that

is, is continuously held LOW), and WCLK receives aperiodic ‘cloc k’ pulses of suitable duration . There like wise is

no requirement that WCLK must have any particular

synchronization relation to the read clock RCLK. These

two clock inputs may in fact receive the same ‘clock’

signal; or t hey m ay r eceive totally-diffe rent signa ls, which

are not synchron ized to each other in any way.

WRITE ENABLE (WEN)

Whenever WE N is being asser t ed (is LO W) an d LD is

HIGH, and the FIF O is not ful l, an 18-bit data word is

loaded into the effective inpu t register for the memory

array at every WCLK rising edge (LOW-to-HIGH transition ). Data words are s tored into the two-port memory

array sequ entia lly , regard less of any ongoing re ad oper ation. Whenever W EN is not being asserted (is HI GH), the

input register retains whatever data word it contained

previousl y, and no new data word gets loaded into the

memo ry arr ay.

To preve nt overrunning the internal FIFO boundaries,

further write operati ons are inhi bited whenever t he Full

Flag (FF) is being asserted (is LOW). If a valid read

oper a tion then occurs, upon the completion of that read

cycle FF again goes HIGH after a time t

WFF

, and another

write operation is allowed to begin whenever WCLK

makes another LOW-to-HIGH transition. Effectively,

WEN is overridden by FF; thus, during normal FIFO

operation, WEN has no effect when the FIFO is full.

In the Enhanced Operating Mode, whenever

EMOD E is being asserted (is LOW), WXI/ W E N2 functions as WEN2, an additiona l duplicate (albei t assertive-HIGH) write-enable input, in order to provide

an‘interlocking’ mechanism for reliable synchronization of two paral leled FIFOs. To control writing ,

WEN2 is ANDed with WEN; this logic-AND function

(WEN

WEN2) then behaves l i ke W EN i n the forego-

ing descr iption.

DESCRIPT ION OF SIGNAL S AN D

OPERATING SEQUENCES (cont’d )

BOLD ITALIC = Enhanced Op erating Mode

512 x 18/1024 x 18 Synchronous FIFO L H540215/25

15

Loading...

Loading...