Sharp LH521028AU-20, LH521028AU-17, LH521028AU-35, LH521028AU-25 Datasheet

LH521028A

CMOS 64K × 18 Static RAM

FEATURES

•• Fast A ccess T imes: 15/17/ 20/25/ 35 ns

•• Wide Word (18-Bits) for:

– Improved Performance

– Reduced Component Count

– Nine-bit Byte for Parit y

•• T ransparent Address Latch

•• Reduced Loading on Address Bus

•• Low-Power Stand-by Mode when

Deselected

•• TTL Compatible I/O

•• 5 V

± 10% Supply

•• 2 V Data Retention

•• JEDEC Standard Pinout

•• Package: 52-Pin PLCC

FUNCTIONAL DESCRIPTION

The LH521028 is a high-speed 1,179,648-bit CMOS

SRAM organized as 64K × 18. A fast, efficient design is

obtained with a CMOS periphery and a matrix constructed with polysilicon load memory cells. The

LH521028 is available in a compact 52- Pin PLCC, which

along with the six pairs of supply terminals, provide for

reliable operation.

The control signals include Write Enable (W), Chip

Enable (E), High an d Low By te Select ( SL and SH), Out put

Enable (G) and Address Latch Enable (ALE). The wide

word provides for reduced component count, improved

density, r educed Addr ess bus loading and improved performance . The wide word also allows for byte-parit y with

no additional RAM required .

This RAM is fully static in opera tion. The Chip Enable

(E) control permits Read and Write operations when

active (LOW) or places the RAM in a low-power standby

mode wh en inactive (HI GH).The Byt e-select controls, S

H

and SL, are also used to enable or disable Read and Write

operations on the high and the low bytes. The Address

Latches are transpar ent wh en ALE is HIGH (for a pplications not requiring a latch), and are latch ed when ALE is

LOW. The Address Latches and the wi de word help to

eliminate the need for external Address bus buffers and/or

latches .

Write cycles occur when Chip Enable (E), SH and/or

SL, and Write Enable (W) are LOW. The Byte-select

signals can be used for Byt e-write oper ations by disabling

the other byte during the Write operation. Data is transferred from the DQ pins to the memor y location specified

by the 16 address lines. The proper use of the Output

Enable control (G) can pre vent bus con ten tion.

When E and either SH or SL are LO W and W is HIGH,

a static Read will occur at the mem or y location spec ifie d

by the addr ess line s. G must be brought LOW to enable

the outputs. Since the device is fully static in operation,

new Read cycles can be performed by simply changing

the address with ALE HIGH.

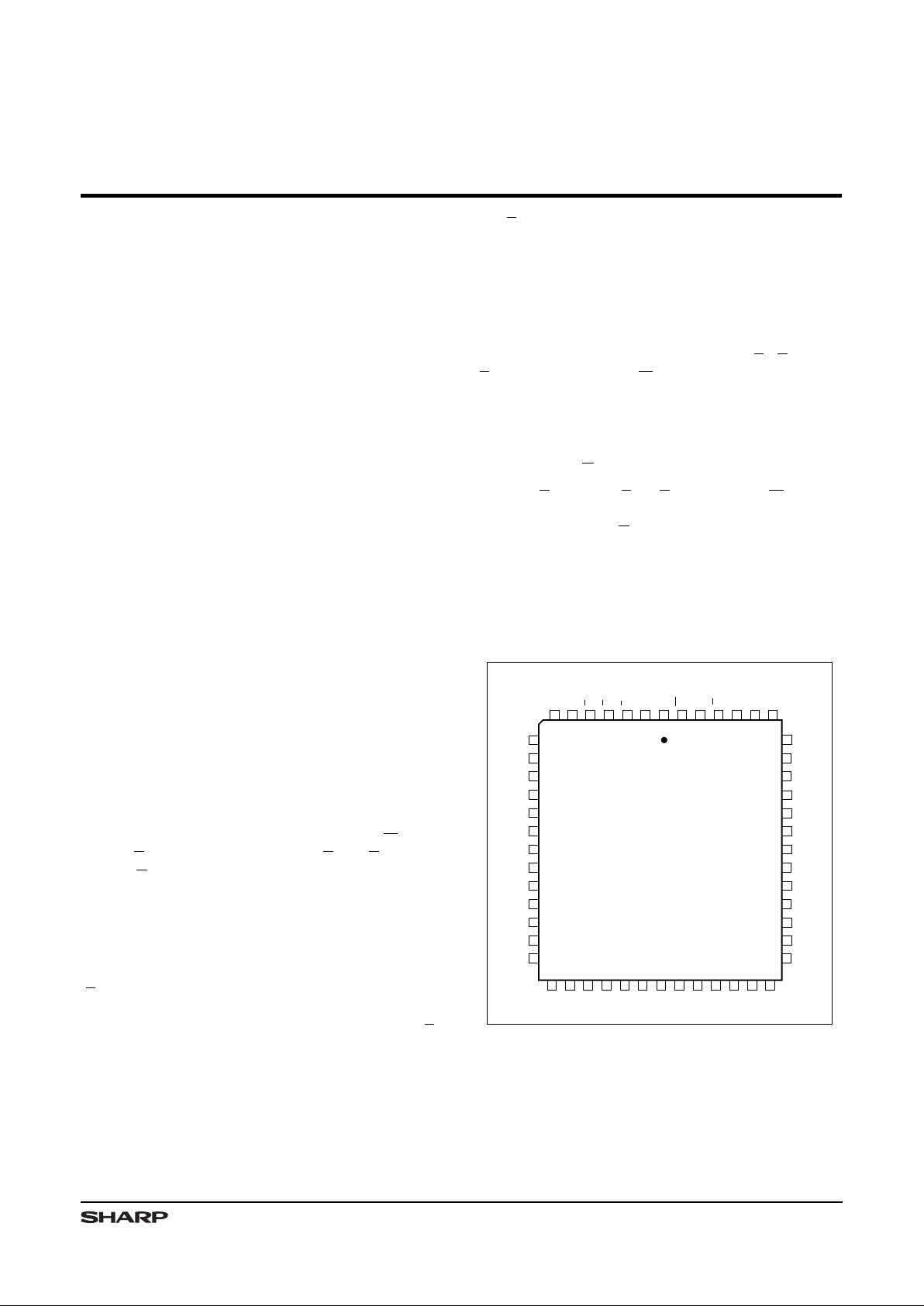

PIN CONNECTIONS

521028-1D

8

9

10

11

12

13

14

15

16

17

18

19

20

46

45

44

43

42

41

40

39

38

37

36

35

34

7 6 5 4 3 2 1 525150494847

21 22 23 24 25 26 27 28 29 30 31 32 33

DQ

8

DQ

7

DQ

6

V

CC

V

SS

DQ

5

DQ

4

DQ

3

DQ

2

V

SS

V

CC

DQ

1

DQ

0

DQ

9

DQ

10

V

CC

V

SS

DQ

11

DQ

12

DQ

13

DQ

14

V

SS

V

CC

DQ

15

DQ

16

DQ

17

A

1

A

0

E

S

H

S

L

V

CC

V

SS

W

ALE

G

A

15

A

14

A

13

A

3

A

5

A

6

A

7

V

SS

V

CC

A

8

A

10

A

11

A

12

A

4

A

9

A

2

52-PIN PLCC

TOP VIEW

Figure 1. Pin Connecti ons for PLCC Package

1

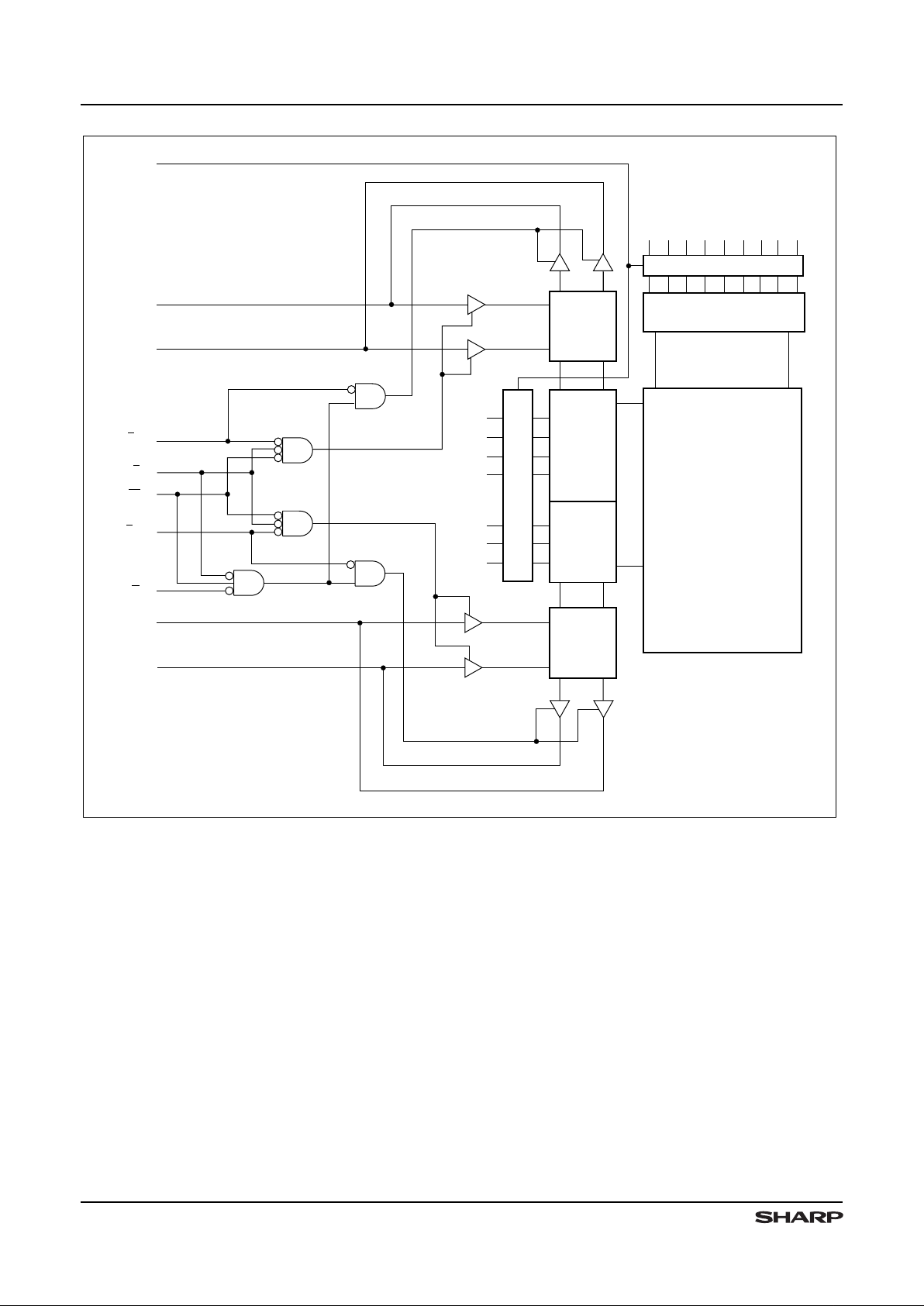

521028-12

. . .. . .

. . .

MEMORY ARRAY

(65,536 x 18)

TRANSPARENT LATCH

ROW DECODE

I/O

CIRCUIT

BLOCK

DECODE

COLUMN

DECODE

I/O

CIRCUIT

TRANSPARENT LATCH

A

15

A

14

A

13

A

12

A

11

A

10

A

9

A8A7A6A5A4A3A2A1A

0

DQ

0

DQ

8

S

L

E

W

S

H

G

DQ

9

ALE

DQ

17

. . .

. . .

. . .

Figure 2. L H521028 A Block Diagr am

LH521028A CMOS 64 K ×× 18 Static RAM

2

TRUTH TABLE

ADDRESS E S

H

SLALE G WDQ

0

-DQ

8

DQ9-DQ

17

MODE I

CC

Don’t Care

HXXHXX

High-Z High-Z Standby

I

SB

V alid

LLHHLH

Active High-Z Read

I

CC1

V alid

LHLHLH

High-Z Ac tive Read

I

CC1

V alid

LLLHLH

Activ e Active Read

I

CC1

V alid

LLLHHH

High-Z High-Z Re ad

I

CC1

Don’t Care

LLLLLH

Data Out Dat a O ut Read

I

CC1

V alid

LLHHXL

Data In Don ’t Care Write, low byte

I

CC1

V alid

LHLHXL

Don’t Car e Data In Write , high byte

I

CC1

V alid

LLLHXL

Data In Dat a In Write, both bytes

I

CC1

V alid

LHHHXL

Don’t Car e Do n ’t Care Write, inhibited

I

CC1

Don’t Care

LLLLXL

Data In Dat a In Write, both bytes

I

CC1

NOTE:

X = Don’t Care, L = LOW, H = HIGH

PIN DESCRIPTIONS

PIN SIGNAL PIN SIGNAL PIN SIGNAL PIN SIGNAL

1

V

SS

14

DQ

13

27

V

SS

40

DQ

4

2

V

CC

15

DQ

14

28

V

CC

41

DQ

5

3

S

L

16

V

SS

29

A

8

42

V

SS

4

S

H

17

VCC

30

A

9

43

V

CC

5

E

18

DQ

15

31

A

10

44

DQ

6

6

A

0

19

DQ

16

32

A

11

45

DQ

7

7

A

1

20

DQ

17

33

A

12

46

DQ

8

8

DQ

9

21

A

2

34

DQ

0

47

A

13

9

DQ

10

22

A

3

35

DQ

1

48

A

14

10

V

CC

23

A

4

36

V

CC

49

A

15

11

V

SS 24

A

5 37

V

SS 50

G

12

DQ

11

25

A

6

38

DQ

2

51

ALE

13

DQ

12

26

A

7

39

DQ

3

52

W

CMOS 64K ×× 18 Stati c RAM LH521028A

3

PIN DEFINITIONS

V

CC

Positive Supply Voltage Terminals

V

SS

Reference Terminals

A0 – A15Address Bus Input

The Ad dress bu s is decod ed to select one 18- bit word

out of the total 64K wo rds f or Read and Writ e operat ion s.

E Chip Enable Active LOW In put

Chip Enable is used to en able the device for Read and

Write operations. When HIGH, both Read and Write

operations are disabled and the device is in a reduced

power state. When LOW, a Read or Write operation is

enabled.

W Write Enable Active LOW Input

Write Enable is used to select either Read or Write

operations when the device is enabled. When Write

Enable is HIGH and the device is Enabled, a Read

operat ion is select ed. When W rite Enab le is LOW and the

device is enabled, a Write oper ation is selected. A Bytewrite oper ation is available by using th e Byte-select controls.

SH, S

L

Select High Active LOW Inputs

Select Low

The Select High and Select Low signals, in conjunction

with the Chip Enable and W r ite Ena ble signals, allow the

selection of the individual bytes for Read and Write operations. When High, the Select signal will deselect its

byte and prevent Read or Write operations . When the

Select signal is LOW and Chip Enable is LOW, a Read or

Write operation is performed at the location dete rmined

by the c ontent s of the Addr ess bus . When Chip Ena ble is

HIGH, th e Select signals are Don’t Care. S elect Low (SL)

is assigned to DQ0 – DQ8 and Select High (SH) is

assigned to DQ9 – DQ17.

ALE Address Latch Active High Input

Enable

The Addr ess La tch Enable signal is used to c ontrol t he

Tr ans parent lat ches on the Addr ess bus. T he Lat ch es a re

transparent when HIGH and are latched when LOW. If

not required, Address Latch Enable may be tied H IGH,

lea ving the Addr ess bu s in a transpar ent condit ion.

DQ0 – DQ17 Data Bus Input/Output

DQ0 – DQ8 comprise the Low byte, selected by SL,

and DQ9 – DQ17 comprise the High Data byte, selected

by SH. The Data Bus is in a high impedance input mode

during Write operations and standby. The Data bus is in

a low-impe dance output mode dur ing Read oper ations.

G Output Enable Active LOW Input

The Out put Enable signal is u sed t o cont rol the o u tpu t

buffers on the Data Input/Output bus. When G is HIGH,

all output buffers are forced to a high impedance condition. When G is LOW, the output buffers will become

active only during a R ead operation (E and SH / SL are

LO W, W is HIGH).

LH521028A CMOS 64 K ×× 18 Static RAM

4

ABSOLUTE MAXIMUM RATINGS

1

PARAMETER RATING

VCC to VSS Potential –0.5 V to 7 V

Input Voltage Range –0.5 V to VCC + 0.5 V

DC Output Current

2

± 40 mA

Storage T e mperature Range –65oC to 150oC

Power Dissipation (Package Limit ) 2 W

NOTES:

1. Stresses greater than those listed under ‘Absolute Maximum Ratings’ may cause permanent damage to the device. This is a st ress rating for

transient condi tions only. Functional operation of the device at these or any other conditions above those indicated in the ‘ O perating Range’

of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

2. Outputs should not be shorted for more than 30 seconds. No more than one output should be shorted at any time.

OPERATING RANGES

SYMBOL PARAMETER MIN TYP MAX UNIT

T

A

T em perat ure, Ambi ent

070

o

C

V

CC

Sup ply V oltag e

4.5 5.0 5.5 V

V

SS

Sup ply V oltag e

000V

V

IL

Logic ‘0 ’ Input V olta ge

1

–0.5 0.8 V

V

IH

Logic ‘1 ’ Input V olta ge

2.2 VCC + 0.5 V

NOTE:

1. Negative undershoot of up to 3.0 V is permitted once per cycle.

DC ELECTRICAL CHARACTERIS TICS

SYMBOL PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

I

CC1

Oper ating Curr ent

1

t

CYCLE

= minimum

300 mA

I

SB1

Standb y Current

E ≥ VCC – 0.2 V

VIN ≥ VCC – 0.2 V o r VIN ≤ 0.2 V

f = 0

4mA

I

SB2

Standb y Current

E ≥ V

IH

VIN = VIH or V

IL

50 mA

I

LI

Inpu t Lea kage Cur ren t VIN = 0 V to V

CC

–2 2

µA

I

LO

I/O Leakage Current VIN = 0 V to V

CC

–2 2

µA

V

OH

Out put Hig h V oltage IOH = –4.0 mA

2.4 V

V

OL

Output Low Voltag e IOL = 8.0 m A

0.4 V

NOTE:

1. I

CC

is dependent upon output loading and cycle rates. Specified values are with outputs open.

CMOS 64K ×× 18 Stati c RAM LH521028A

5

Loading...

Loading...