Page 1

LC-M3700

LC-M3710

LC-M3700

1st Edition

LC-M3710

SERVICE MANUAL

WIDE LCD MONIT OR

LC-M3700

MODELS

LC-M3710

In the interests of user-safety (Required by safety regulations in some countries) the set should be restored

to its original condition and only parts identical to those specified should be used.

CONTENTS

Page

» IMPORTANT SERVICE SAFETY PRECAUTION.........................................................................................2

» SPECIFICATIONS ........................................................................................................................................6

» OPERATION MANUAL .................................................................................................................................7

» DIMENSIONS .............................................................................................................................................12

» REMOVING OF MAJOR PARTS ................................................................................................................13

» ADJUSTING PROCEDURE OF EACH SECTION .....................................................................................17

» HOW TO UPGRADE THE INTERNAL PROGRAM....................................................................................30

» DESCRIPTION OF FUNCTION OF MAJOR ICs .......................................................................................34

» CHASSIS LAYOUT .....................................................................................................................................58

» BLOCK DIAGRAM......................................................................................................................................60

» OVERALL WIRING DIAGRAM ...................................................................................................................68

» DESCRIPTION OF SCHEMATIC DIAGRAM .............................................................................................72

» SCHEMATIC DIAGRAM .............................................................................................................................73

» PRINTED WIRING BOARD ASSEMBLIES..............................................................................................132

» REPLACEMENT PARTS LIST..................................................................................................................173

» PACKING OF THE SET ............................................................................................................................212

SHARP CORPORATION

This document has been published to be used for

after sales service only.

The contents are subject to change without notice.

Page 2

LC-M3700

3

2

2

LC-M3710

IMPORTANT SERVICE SAFETY PRECA UTION

Ë

Service work should be performed only by qualified service technicians who are thoroughly familiar with all safety checks and the servicing guidelines which follow:

WARNING

1. For continued safety, no modification of any circuit

should be attempted.

2. Disconnect AC power before servicing.

» Use an AC voltmeter ha ving with 5000 ohm per v olt,

or higher, sensitivity or measure the A C v oltage drop

across the resistor.

» Connect the resistor connection to all exposed metal

CAUTION: FOR CONTINUED PROTECTION

AGAINST A RISK OF FIRE REPLACE ONLY WITH

SAME TYPE FUSE.

F7501, F7502, F7503, F7504, F7551, F7552, F7553,

F7611, F7612, F7613, F7614, F7641, F7642, F7643

(T315mAL, 250V), F2701, F2702 (T4AH, 250V)

parts having a return to the chassis (antenna, metal

cabinet, screw heads, knobs and control shafts,

escutcheon, etc.) and measure the AC voltage drop

across the resistor.

All checks must be repeated with the AC cord plug

connection reversed. (If necessar y, a nonpolarized

adaptor plug must be used only for the purpose of

completing these checks.)

Any reading of 0.75 Vrms (this corresponds to 0.5

BEFORE RETURNING THE RECEIVER

(Fire & Shock Hazard)

mA. rms AC.) or more is excessive and indicates a

potential shock hazard which must be corrected

before returning the monitor to the owner.

Before returning the receiver to the user, perform

the following safety checks:

1. Inspect all lead dress to make certain that leads are

not pinched, and check that hardware is not lodged

between the chassis and other metal parts in the

receiver.

2. Inspect all protective devices such as non-metallic

control knobs, insulation materials, cabinet backs,

adjustment and compartment covers or shields,

isolation resistor-capacitor networks, mechanical

DVM

AC SCALE

1.5k ohm

10W

insulators, etc.

3. To be sure that no shock hazard exists, check for

leakage current in the following manner.

» Plug the AC cord directly into a 110~240 volt A C outlet.

» Using two clip leads, connect a 1.5k ohm, 10 watt

0.15 µF

TEST PROBE

resistor paralleled by a 0.15µF capacitor in series

with all exposed metal cabinet parts and a known

earth ground, such as electrical conduit or electrical

ground connected to an earth ground.

2345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212

TO EXPOSED

METAL PARTS

CONNECT TO

KNOWN EARTH

GROUND

SAFETY NOTICE

Many electrical and mechanical parts in WIDE LCD

MONITOR have special safety-related characteristics.

These characteristics are often not evident from visual

inspection, nor can protection afforded by them be

necessarily increased by using replacement components

rated for higher voltage , w attage , etc.

Replacement parts which have these special safety

characteristics are identified in this manual; electrical

and shaded areas in the

Schematic Diagrams.

For continued protection, replacement parts must be

identical to those used in the original circuit.

The use of a substitute replacement parts which do not

have the same safety characteristics as the factory

recommended replacement parts shown in this service

manual, may create shock, fire or other hazards.

components having such features are identified by “ å”

234567890123456789012345678901212345678901234567890123456789012123456789012345678901234567890121

234567890123456789012345678901212345678901234567890123456789012123456789012345678901234567890121

2

Replacement Parts List

and

Page 3

LC-M3700

2

2

LC-M3710

PRECAUTIONS A PRENDRE LORS DE LA REPARATION

Ë

Ne peut effectuer la réparation qu' un technicien spécialisé qui s'est parfaitement

accoutumé à toute vérification de sécurité et aux conseils suivants.

AVERTISSEMENT

de 0,15µF en série avec toutes les pièces métalliques

exposées du coffret et une terre connue comme une

1. N'entreprendre aucune modification de tout circuit.

C'est dangereux.

2. Débrancher le récepteur avant toute réparation.

PRECAUTION: POUR LA

PROTECTION CONTINUE CONTRE

LES RISQUES D'INCENDIE,

REMPLACER LE FUSIBLE

F7501, F7502, F7503, F7504, F7551,

A V

F7552, F7553, F7611, F7612, F7613,

F7614, F7641, F7642, F7643

(T315mAL, 250V), F2701, F2702

(T4AH, 250V)

conduite électrique ou une prise de terre branchée à

la terre.

• Utiliser un voltmètre CA d'une sensibilité d'au moins

5000Ω/V pour mesurer la chute de tension en travers

de la résistance.

• Toucher avec la sonde d'essai les pièces métalliques

exposées qui présentent une voie de retour au châssis

(antenne, coffret métallique, tête des vis, arbres de

commande et des boutons, écusson, etc.) et mesurer

la chute de tension CA en-travers de la résistance.

Toutes les vérifications doivent être refaites après avoir

inversé la fiche du cordon d'alimentation. (Si

nécessaire, une prise d'adpatation non polarisée peut

être utilisée dans le but de terminer ces vérifications.)

Tous les courants mesurés ne doivent pas dépasser

VERIFICATIONS CONTRE L'INCEN-DIE ET

LE CHOC ELECTRIQUE

Avant de rendre le récepteur à l'utilisateur, effectuer

0,5 mA.

Dans le cas contraire, il y a une possibilité de choc

électrique qui doit être supprimée avant de rendre le

récepteur au client.

les vérifications suivantes.

1. Inspecter tous les faisceaux de câbles pour s'assurer

que les fils ne soient pas pincés ou qu'un outil ne soit

pas placé entre le châssis et les autres pièces

métalliques du récepteur.

2. Inspecter tous les dispositifs de protection comme les

boutons de commande non-métalliques, les isolants,

le dos du coffret, les couvercles ou blindages de réglage

DVM

ECHELLE CA

1.5k ohm

10W

et de compartiment, les réseaux de résistancecapacité, les isolateurs mécaniques, etc.

3. S'assurer qu'il n'y ait pas de danger d'électrocution en

vérifiant la fuite de courant, de la facon suiv ante:

• Brancher le cordon d'alimentation directem-ent à une

0.15 µF

SONDE D'ESSAI

prise de courant de 110-240V. (Ne pas utiliser de

transformateur d'isolation pour cet essai).

• A l'aide de deux fils à pinces, brancher une résistance

de 1.5 kΩ 10 watts en parallèle a v ec un condensateur

234567890123456789012345678901212345678901234567890123456789012123456789012345678901234567890121

AUX PIECES

METALLIQUES

EXPOSEES

BRANCHER A UNE

TERRE CONNUE

AVIS POUR LA SECURITE

De nombreuses pièces, électriques et mécaniques,

dans les téléviseurs présentent des caractéristiques

spéciales relatives à la sécurité, qui ne sont souvent

pas évidentes à vue. Le degré de protection ne peut

pas être nécessairement augmentée en utilisant des

pièces de remplacement étalonnées pour haute tension,

puissance, etc.

Les pièces de remplacement qui présentent ces

caractéristiques sont identifiées dans ce manuel; les

pièces électriques qui présentent ces particularités sont

234567890123456789012345678901212345678901234567890123456789012123456789012345678901234567890121

identifiées par la marque " å " et hachurées dans la

liste des pièces de remplacement et les diagrammes

schématiques.

Pour assurer la protection, ces pièces doivent être

identiques à celles utilisées dans le circuit d'or igine.

L'utilisation de pièces qui n'ont pas les mêmes

caractéristiques que les pièces recommandées par

l'usine, indiquées dans ce manuel, peut provoquer des

électrocutions, incendies, radiations X ou autres

accidents.

3

Page 4

LC-M3700

2

2

LC-M3710

IMPORTANT SERVICE SAFETY PRECA UTION

Ë

Service work should be performed only by qualified service technicians who are thoroughly familiar with all safety checks and the servicing guidelines which follow:

WARNING

1. For continued safety, no modification of any circuit

should be attempted.

2. Disconnect AC power before servicing.

CAUTION: FOR CONTINUED PROTECTION

AGAINST A RISK OF FIRE REPLACE ONLY WITH

SAME TYPE FUSE.

F7501, F7502, F7503, F7504, F7551, F7552, F7553,

F7611, F7612, F7613, F7614, F7641, F7642, F7643

(T315mAL, 250V), F2701, F2702 (T4AH, 250V)

BEFORE RETURNING THE RECEIVER

(Fire & Shock Hazard)

Before returning the receiver to the user, perform

the following safety checks:

1. Inspect all lead dress to make certain that leads are

not pinched, and check that hardware is not lodged

between the chassis and other metal parts in the

receiver.

2. Inspect all protective devices such as non-metallic

control knobs, insulation materials, cabinet backs,

adjustment and compartment covers or shields,

isolation resistor-capacitor networks, mechanical

insulators, etc.

3. To be sure that no shock hazard exists, check for

leakage current in the following manner.

» Plug the AC cord directly into a 220~240 volt A C outlet.

» Using two clip leads, connect a 50k ohm, 10 watt

resistor paralleled by a 0.15µF capacitor in series

with all exposed metal cabinet parts and a known

earth ground, such as electrical conduit or electrical

ground connected to an earth ground.

» Use an AC voltmeter ha ving with 5000 ohm per v olt,

or higher, sensitivity or measure the A C v oltage drop

across the resistor.

» Connect the resistor connection to all exposed metal

parts having a return to the chassis (antenna, metal

cabinet, screw heads, knobs and control shafts,

escutcheon, etc.) and measure the AC voltage drop

across the resistor.

All checks must be repeated with the AC cord plug

connection reversed. (If necessar y, a nonpolarized

adaptor plug must be used only for the purpose of

completing these checks.)

Any reading of 35V peak (this corresponds to 0.7

mA. peak AC.) or more is excessive and indicates a

potential shock hazard which must be corrected

before returning the monitor to the owner.

DVM

AC SCALE

50k ohm

10W

0.15 µF

TEST PROBE

TO EXPOSED

METAL PARTS

CONNECT TO

KNOWN EARTH

GROUND

234567890123456789012345678901212345678901234567890123456789012123456789012345678901234567890121

SAFETY NOTICE

Many electrical and mechanical parts in WIDE LCD

MONITOR have special safety-related characteristics.

These characteristics are often not evident from visual

inspection, nor can protection afforded by them be

necessarily increased by using replacement components

rated for higher voltage , w attage , etc.

Replacement parts which have these special safety

characteristics are identified in this manual; electrical

and shaded areas in the

Schematic Diagrams.

For continued protection, replacement parts must be

identical to those used in the original circuit.

The use of a substitute replacement parts which do not

have the same safety characteristics as the factory

recommended replacement parts shown in this service

manual, may create shock, fire or other hazards.

components having such features are identified by “ å”

234567890123456789012345678901212345678901234567890123456789012123456789012345678901234567890121

Replacement Parts List

and

4

Page 5

LC-M3700

LC-M3710

Precautions for using lead-free solder

1 Employing lead-free solder

"PWBs" of this model employs lead-free solder. The LF symbol indicates lead-free solder, and is attached on the

PWBs and service manuals. The alphabetical character following LF shows the type of lead-free solder.

Example:

L Fa

Indicates lead-free solder of tin, silver and copper.

2 Using lead-free wire solder

When fixing the PWB soldered with the lead-free solder, apply lead-free wire solder. Repairing with conventional

lead wire solder may cause damage or accident due to cracks.

As the melting point of lead-free solder (Sn-Ag-Cu) is higher than the lead wire solder by 40°C, we recommend

you to use a dedicated soldering bit, if you are not familiar with how to obtain lead-free wire solder or soldering bit,

contact our service station or service branch in your area.

3 Soldering

As the melting point of lead-free solder (Sn-Ag-Cu) is about 220°C which is higher than the conventional lead

solder by 40°C, and as it has poor solder wettability, you may be apt to keep the soldering bit in contact with the

PWB for extended period of time. However, Since the land may be peeled off or the maximum heat-resistance

temperature of parts may be exceeded, remov e the bit from the PWB as soon as you confirm the steady soldering

condition.

Lead-free solder contains more tin, and the end of the soldering bit may be easily corroded. Mak e sure to turn on

and off the power of the bit as required.

If a different type of solder stays on the tip of the soldering bit, it is allo y ed with lead-free solder. Clean the bit after

every use of it.

When the tip of the soldering bit is blackened during use, file it with steel wool or fine sandpaper.

Be careful when replacing parts with polarity indication on the PWB silk.

Lead-free wire solder for servicing

Part No, ★ Description Code

ZHNDAi123250E J φ0.3mm 250g(1roll) BL

ZHNDAi126500E J φ0.6mm 500g(1roll) BK

ZHNDAi12801KE J φ1.0mm 1kg(1roll) BM

5

Page 6

LC-M3700

LC-M3710

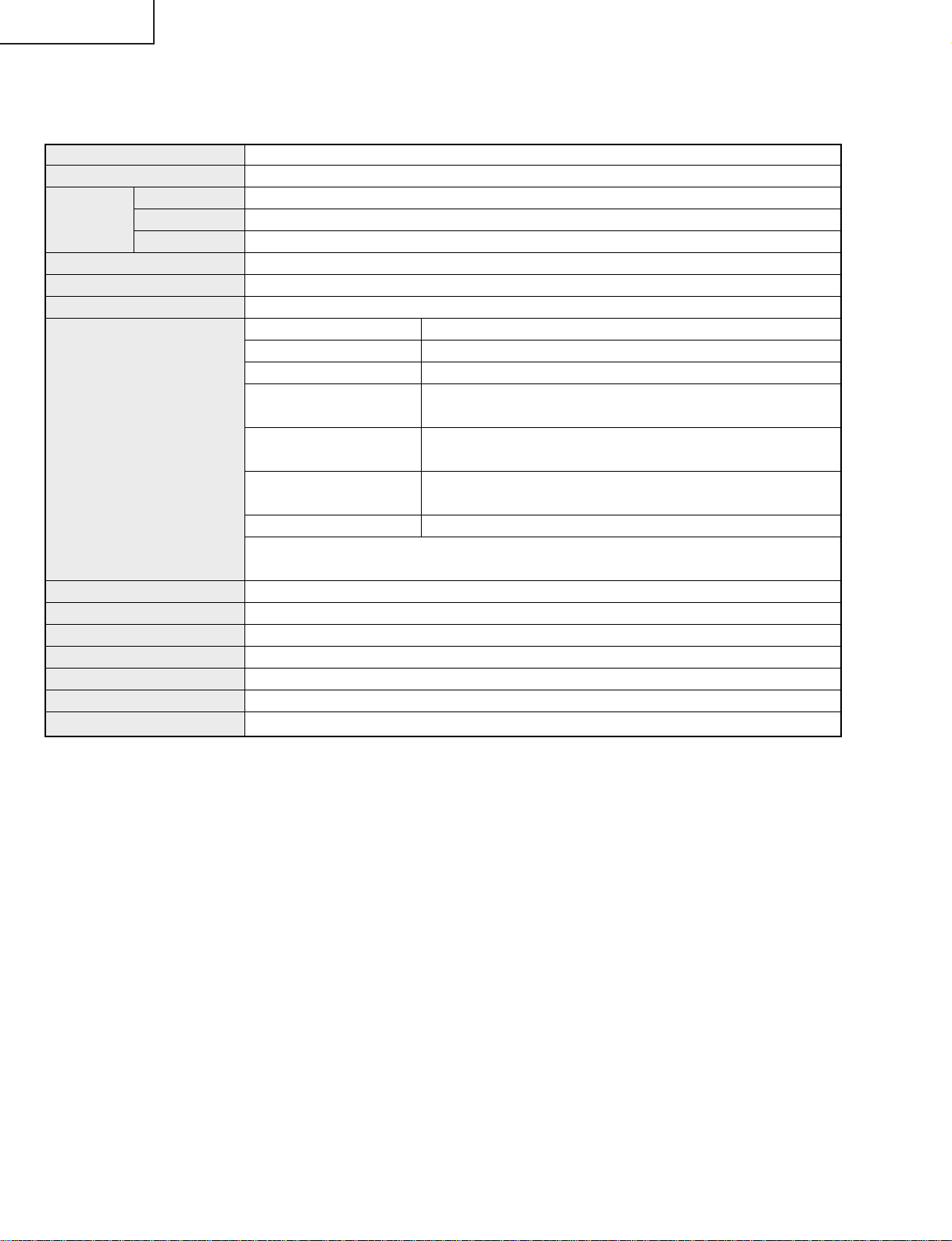

SPECIFICATIONS

Product

Model

Screen size

LCD Panel Drive

Number of dots

Colour system

Speaker

Audio amplifier

Terminals

Power requirement

Power consumption

Standby power consumption

Dimensions

Weight

Operating temperature 0°C – +40°C

Operating humidity 20% – +80%

Wide LCD Monitor

LC-M3700/LC-M3710

37” (819.6 mm (width) x 460.8 mm (height), 940.3 mm (diagonal))

TFT (thin film transistor) Active Matrix

3,147,264 dots (768 (height) x 1,366 (width) x 3)

NTSC (3.58/4.43MHz), PAL/PAL-60, SECAM

ø

5 cm, 1 piece

External speakers: 20 W (10 W + 10 W) Built-in monitor speaker: 0.8 W

INPUT1 VIDEO in (BNC), S-video in, AUDIO (L/R) in

INPUT2(INPUT/OUTPUT

VIDEO OUTPUT VIDEO out (BNC)

INPUT3 (Y/G, Cr/Pr/R, COMPONENT video in/PC (ANALOG) in (BNC),

Cb/Pb/B, HD, VD) AUDIO in (stereo jack, ø 3.5mm)

INPUT3/PC(ANALOG)

OUTPUT

PC(ANALOG)INPUT PC (ANALOG) INPUT in (Mini D-Sub 15 pin),

PC(DIGITAL)INPUT PC (DIGITAL) INPUT in (DVI-D)

RS-232C INPUT terminal (9 pins), RS-232C OUTPUT terminal (9 pins),

SPEAKER terminal (L/R), AC input terminal

AC110 - 240V, 50/60Hz

182 W

1.2 W

949 mm x 99.5 mm x 572 mm

19 kg (without stand)

VIDEO in/out (RCA), AUDIO (L/R) in/out

INPUT3/PC (ANALOG) OUTPUT (Mini D-Sub 15 pin)

AUDIO in (stereo jack, ø 3.5 mm)

Ë

As a part of policy of continuous improvement, SHARP reserves the right to make design and specification

changes for product improvement without prior notice. The performance specification figures indicated are

nominal values of production units. There may be some deviations from these values in individual units.

6

Page 7

Part Names – Display

MENU

ENTER

UP

RIGHT

LEFT

DOWN

INPUT

VOL

Liquid Crystal Display panel

Side control panel

(See below.)

Front view

Side control panel

Remote

control sensor

*

When using the

remote control, point

it towards here.

STANDBY/ON

button

STANDBY/ON

indicator

Panel side

MENU

ENTER

VOL +/–

UP

LEFT

RIGHT

DOWN

INPUT

Menu operation

buttons

Cursor

control

LC-3700 LC-3710

About LC-M3710:

»

The SHARP logo for the LC-M3710 model is

on the vertical base.

Removing the terminal cover

1. Hold down the two claws at the top of the terminal

cover, and pull the cover toward you so it opens a

little.

2. Slowly lift the cover so the three claws at the bottom

come loose from the claw holes in the console.

2

1

3

Rear view

Built-in monitor

speaker

SPEAKER (R)

External speaker terminal

(right)

POWER

Main power on/off

switch

SPEAKER (L)

External speaker terminal

(left)

AC Input

terminal

INPUT2 (INPUT/

OUTPUT)

VIDEO OUTPUT

RS-232C INPUT

RS-232C OUTPUT

INPUT1

PC (DIGITAL) INPUT

INPUT3/PC (ANALOG)

OUTPUT

INPUT3

PC (ANALOG)

INPUT

Removing the terminal cover

Lower claw

Upper claw

OPERATION MANUAL

LC-M3700

LC-M3710

7

Page 8

LC-M3700

Part Names – Remote Control Unit

INPUT

RETURN

MENU

STANDBY/ON

ENLARGE

WIDE

LCD MONITOR

ENTER

VOL

Signal transmitter

Remote control unit

STANDBY/ON

MENU

VOL +/–

ENLARGE

INPUT

RETURN

WIDE

Cursor control ('/"/\/|)

ENTER

INPUT1

INPUT1: Terminals are provided for two types of video input signal. Input Select

No matter which video signal is selected, the system uses the signal input to the audio terminals for

audio.

Related topic:

Input Select

*1 “Auto” (automatic colour system detection) is factory preset value. Color System

INPUT 1

AUDIO

VIDEOS-VIDEO

R - - L

1

S-video

INPUT1

audio

Video

Connecting Peripheral Equipment

Terminal type

BNC

S terminal

Compatible signals

NTSC (3.58/4.43), PAL, SECAM (*1)

NTSC (3.58/4.43), PAL, SECAM (*1)

Video

S-video

LC-M3710

8

Page 9

Connecting Peripheral Equipment (Continued)

INPUT2

INPUT 2 (INPUT/OUTPUT)

VIDEO

AUDIOR - - L

2

INPUT2

audio

Video

Terminal type

RCA

Compatible signals

NTSC (3.58/4.43), PAL, SECAM (*2)Video

INPUT2: Input or output can be selected for INPUT2. (*1) INPUT2 Select

This setting cannot be switched when INPUT2 is currently being displayed.

When this is set to

“Output”, video signals input fr

om the INPUT1 video input terminal are output. (*3)

An audio signal is output with this setting (i.e. the audio signal corresponding to the video currently

being displayed). (*4)

Related topic:

*1 “Input” is factory preset value.

*2 “Auto” (automatic colour system detection) is factory preset value. Color System

*3 Outputs video from INPUT1, regardless of the currently displayed signal.

*4 If the “INPUT2 Select” is set to “Output”, audio output is as follows

.

Example 1

Input Selection : INPUT1

“Input Select” : AV

Example 2

Input Selection : INPUT3

“Input Select” : RGB

INPUT2 video output: Video from INPUT1

INPUT2 audio output: Audio from INPUT1

INPUT2 video output: Video from INPUT1

INPUT2 audio output: Audio from INPUT3

INPUT3

INPUT 3

AUDIOPr/Cr/RPb/Cb/B VDHDY/G

3

Input Select: RGB

INPUT3 audio

Input Select:

COMPONENT

Horizontal

sync signal (H sync)

Vertical

sync signal (V sync)

The signal is input with the Y/Pb/Pr (Y/Cb/Cr) terminals. The HD and VD terminals are

not used. Video adjustment options on the menu are the AV type.

Compatible input range: 480i/576i, 480p/576p, 1080i (50Hz (*4) /60Hz), 720p (60Hz). (*1)

The monitor operates using Video (RGB) and Sync (HD/VD) signals, just like a PC

(analog). Supported sync signals are ordinary separate sync (HD/VD) and Sync On

Green. (*2) (*3)

Video adjustment options on the menu are the PC type.

Compatible input range: Conforms to PC (analog). Appendix 1

COMPONENT

RGB

Ë INPUT3: Either COMPONENT or RGB can be selected for the input video signal. Input Select

Related topic:

Input Select

*1 Auto-detects video signal frequency.

*2 Automatic sync signal type detection

*3 Sync signal presence is detected in the order: Separate Sync Sync On Green. If for some reason

Separate Sync is not input, the system will operate assuming that the signal is a Sync On Green

signal (i.e. that the sync signal is contained in the G signal of RGB), and this may result in an

unstable image, depending on the video signal.

*4 1080i (50Hz) corresponds to a SMPTE274M signal. (Horizontal frequency is 28.125kHz)

LC-M3700

LC-M3710

9

Page 10

LC-M3700

PC

Terminal type

D-Sub15-pin

DVI-D

Compatible signals

VGA, SVGA, XGA, SXGA and others Appendix 1

In addition to ordinary Separate Sync (HD/VD) signals, the system is also

compatible with Composite Sync (Csync) and Sync On Green. (*1) (*2)

VGA, SVGA, XGA, SXGA and others Appendix 1

Analog

Digital

Connecting Peripheral Equipment (Continued)

PC: Terminals for two kinds of PC video input signal are available. Input Select

No matter which video signal is selected, the system uses the signal input to the audio terminals for

audio.

Related topic:

*1 Auto-detects Sync signal type.

*2 Sync signal presence is detected in the order: Separate Sync Composite Sync Sync On

Green. If for some reason neither Separate Sync nor Composite Sync is input, the system will

operate assuming that the signal is a Sync On Green signal (i.e. that the sync signal is contained in

the G signal of RGB), and this may result in an unstable image, depending on the video signal.

PC(DIGITAL)INPUT

PC (digital) video

PC(ANALOG)INPUT

AUDIO

PC (analog) video

PC audio

VIDEO OUTPUT

Ë When INPUT2 is displayed, video from INPUT2 is output. Otherwise video from INPUT1 is output.

INPUT3/PC (ANALOG) OUTPUT

Ë When INPUT3 is displayed, video from INPUT3 is output. Otherwise PC (analog) video is output.

RS-232C INPUT/RS-232C OUTPUT

Ë The RS-232C INPUT and RS-232C OUTPUT are used to control this monitor with a PC.

To connect a single monitor to a PC, connect to the RS-232C INPUT terminal.

To connect multiple monitors in a daisy chain for control by PC, use the RS-232C OUTPUT terminal.

RS-232C INPUT

RS-232C OUTPUT

INPUT 3 / PC (ANALOG) OUTPUT

VIDEO

OUTPUT

Video

LC-M3710

10

Page 11

Appendix 3: Menu Option Reference Chart

Contrast

Black Level

Red

Green

Blue

Advanced

Reset

0 - 40

–30 - 0 - +30

–30 - 0 - +30

–30 - 0 - +30

–10 - 0 - +10

Yes, No

Picture

Lock Item

PIN

PIN Clear

Control Lock

Input Select

Input Signal *

1

Auto Sync.

Fine Sync.

Picture Flip

Language

INPUT2 Select

ID No. Setting

Enlarge

Panel Protection Cover

Wide Mode

DNR

Quick Shoot

Monitor Speaker Output

H-Pos.

V-Pos .

Clock

Phase

Reset

0 - 180

0 - 99

0 - 180

0 - 40

Yes, No

Yes, No

Yes, No

Off

22

33

Select the position from 1 to 4

Select the position from 1 to 9

Menu Display

Remote

Buttons

Power

RS-232C

Lock, Unlock

Lock, Unlock

Lock, Unlock

Lock, Unlock

Lock, Unlock

Setup

–15 - 0 - +15

–15 - 0 - +15

L 30 - 0 - R 30

Yes, No

–8 - 0 - +8

Off, Mode1, Mode2

Audio

Brightness

Power Management

Input 4 digit numbers

Yes, No

Power

control

Normal, Full, Cinema, Dot by Dot *

3

Off, High, Low

On, Off

On, Off

Option

Treble

Bass

Balance

Reset

Analog, Digital *

1

640 480, 720 400, 640 480, 848 480, 852 480,

1024 768, 1280 768, 1366 768, 640 480p *

2

Start Now

When Connected

Normal, Mirror, Upside Down, Rotate

Japanese, English, Deutsch, Français, Español

Input, Output

Input numbers from 000 to 255

C.M.S. (H)

C.M.S. (S)

C.M.S. (V)

C.M.S.

R

Y

G

C

B

M

Reset

–30 - 0 - +30

–30 - 0 - +30

–30 - 0 - +30

–30 - 0 - +30

–30 - 0 - +30

–30 - 0 - +30

Yes, No

Attached, Detached

Menu option reference chart: PC input mode

*1 May not be displayed for certain signal types.

*2 Items displayed may vary according to input signal types.

*3 Items displayed may vary according to input signal types.

» Depending on the conditions, certain menu items may be displayed in grey. These items cannot be selected.

NOTE:

×

×

××××

××××

×

C.M.S. (H)

C.M.S. (S)

C.M.S. (V)

Color Temp

Black

3D-Y/C

Monochrome

Film Mode

I/P Setting

Contrast

Black Level

Color

Tint

Sharpness

Advanced

Reset

High, Mid-High, Mid, Mid-Low, Low

Off, High, Low

Standard, Fast, Slow

On, Off

On, Off

Interlace, Progressive

C.M.S.

R

Y

G

C

B

M

Reset

0 - 40

–30 - 0 - +30

–30 - 0 - +30

–30 - 0 - +30

–10 - 0 - +10

–30 - 0 - +30

–30 - 0 - +30

–30 - 0 - +30

–30 - 0 - +30

–30 - 0 - +30

–30 - 0 - +30

Yes, No

Yes, No

Picture

Lock Item

PIN

PIN Clear

Wide Mode

Color System

DNR

Quick Shoot

Monitor Speaker Output

H-Pos.

V-Pos .

Reset

–10 - 0 - +10

–20 - 0 - +20

Yes, No

Off

22

33

Select the position from 1 to 4

Select the position from 1 to 9

Menu Display

Remote

Buttons

Power

RS-232C

Lock, Unlock

Lock, Unlock

Lock, Unlock

Lock, Unlock

Lock, Unlock

Setup

–15 - 0 - +15

–15 - 0 - +15

L 30 - 0 - R 30

Yes, No

Audio

Brightness

Power Management

Input 4 digit numbers

Yes, No

Power

control

Normal, Full 14:9, Zoom 14:9, Panorama, Cinema 14:9, Cinema 16:9, Full, Underscan

Auto, PAL, SECAM, NTSC3.58, NTSC4.43

Off, High, Low

On, Off

On, Off

Option

Treble

Bass

Balance

Reset

AV , Y/C

COMPONENT, RGB *

2

Normal, Mirror, Upside Down, Rotate

Japanese, English, Deutsch, Français, Español

Input, Output

Input numbers from 000 to 255

–8 - 0 - +8

Off, Mode1, Mode2

Attached, Detached

Control Lock

Input Select *

1

Position

Picture Flip

Language

INPUT2 Select *

3

ID No. Setting

Enlarge

Panel Protection Cover

Menu option reference chart: AV input mode

*1 This item cannot be chosen if input other than

“INPUT1” or “INPUT3” is selected.

*2 Available only for

“INPUT3”

*3 Not available when

“INPUT2” is selected.

» Depending on the conditions, certain menu items may be displayed in grey. These items cannot be selected.

NOTE:

×

×

LC-M3700

LC-M3710

11

Page 12

LC-M3700

LC-M3710

DIMENSIONS

Unit: mm

909

810

99.5

66.1

462.8

949

821.6

200

200

36

13

13

12.3

37

65

105265370

6.5

572

12

66.1

24

18.5

223

200

115

142

72.5

188.3

155

38.5

335.8

12

Page 13

REMOVING OF MAJOR PARTS

SC4101

SC4102

8

10

11

6

7

5

5

9

FPC holder (left)

PC I/F PWB shield

Wire Holder

Monitor PWB shield

FPC holder (right)

Terminal cover B

Terminal cover A

Cabinet B (bottom)

1. Remove the terminal cover.

2. Remove the four lock screws that fix the temporary stand and remove the simple stand.

3. Remove the two lock screws that fix the handle and remove the handle.

4. Remove the 29 lock screws that fix the cabinet B and remove the cabinet B.

5. Remove the seven lock screws that fix the cabinet B (bottom) and remove the cabinet B (bottom).

6. Remove the two lock screws that fix the terminal cover B and remove the terminal cover B.

7. Remove the two lock screws that fix the terminal cover A and remove the terminal cover A.

8. Remove the four lock screws that fix the PC I/F PWB shield and remove the PC I/F PWB shield.

9. Remove the four lock screws that fix the monitor PWB shield and remove the monitor PWB shield.

10. Remove the four lock screws that fix the FPC holder (left) and remove the FPC holder (left).

11. Remove the four lock screws that fix the FPC holder (right) and remove the FPC holder (right).

3

Handle

LC-M3700

LC-M3710

4

2

1

Temporary stand

Terminal cover

4

3

Handle

13

Page 14

LC-M3700

LC-M3710

12. Disconnect the connectors from each PWB.

13. Remove the two lock screws that fix the key PWB and remove the key PWB.

14. Remove the two lock screws that fix the R/C LED PWB and remove the R/C LED PWB.

15. Remove the two lock screws that fix the speaker-L PWB and remove the speaker-L PWB.

16. Remove the two lock screws that fix the AC inlet PWB and remove the AC inlet PWB.

17. Remove the two lock screws that fix the terminal-1 PWB and remove the terminal-1 PWB.

18. Remove the two lock screws that fix the terminal-2 PWB and remove the terminal-2 PWB.

19. Remove the two lock screws that fix the speaker-R PWB and remove the speaker-R PWB.

20. Remove four lock screws that fix the speaker angle and remove the speaker angle.

SC4601

CN1703

CN1704

CN1701

CN1705

CN3702

CN2702

P7803

P7501

P7506

P7502

P7505

P7503

P7507

P151

12

P7504

P7551

12

P7552

P7554

P7553

P202

P7557

P101

12

CN1702

P7704

CN1706

P2003

CN1707

CN3701

CN4701

12

CN2701

P7802

P7707

P2004

CN9

CN8

P1101

12

SC4602 SC4604

12

12

CN11

CN1

SC1103

CN2001

P7705

P2005

SC4603

P1501

P1504

SC2405

P7611

P7616

P7615

P7612

P2508

P2302

P7649

P2301

P7618

P7644

P7647

P7613

12

P7614

P7641

12

P7642

P7643

P202

P1801

12

P1507

SC1506

P1505

SC2406

20

Speaker angle

13

Key PWB

R/C LED PWB

14

Speaker-LPWB

AC inlet PWB

15

16

17

Terminal-1 PWB

14

Terminal-2 PWB

18

Speaker-R PWB

19

Page 15

LC-M3700

LC-M3710

21. Remove the inverter-3 PWB.

22. Remove the three lock screws that fix the inverter-4 PWB and remove the inverter-4 PWB.

23. Remove the four lock screws that fix the main PWB and remove the main PWB.

24. Remove the four lock screws that fix the monitor PWB and remove the monitor PWB and monitor PWB angle.

25. Remove the two lock screws that fix the PC I/F PWB and remove the PC I/F PWB.

26. Remove the four lock screws that fix the DC/DC PWB and remove the DC/DC PWB.

27. Remove the one lock screw that fixes the holder B assembly and remove the holder B assembly.

28. Remove the one lock screw that fixes the holder A assembly and remove the holder A assembly.

29. Remove the inverter-1 PWB.

30. Remove the one lock screw that fixes the inverter 2 PWB and remove the inverter-2 PWB.

Holder A assembly

28

29

Inverter-1 PWB

Holder B assembly

27

DC/DC PWB

26

PC I/F PWB

25

PC I/F PWB

angle

Monitor PWB

21

Inverter-3 PWB

24

Monitor PWB angle

30

Inverter-2 PWB

22

Inverter-4 PWB

Main PWB

Power PWB

23

31

15

Page 16

LC-M3700

LC-M3710

» Cautions in handling the liquid crystal panel

1. Handle the liquid crystal panel in a clean room (Humidity: 50% or more).

2. The operator should wear an earth band without fail.

3. Take care not to give an impact (dropping, vibrating, etc.) to the liquid crystal panel

4. Use an ionizer (within 30 cm).

32. Remove the five lock screws that fix the liquid crystal panel and remove the liquid crystal panel unit.

33. Remove the three lock screws that fix each sheet-fixing angle and remove each sheet-fixing angle.

34. Remove the reflection/shade sheet, prism sheet, diffusion sheet and diffusion plate.

35. Remove the three lock screws that fix each lamp holder (upper, lower) and remove each lamp holder (upper,

lower).

36. Remove the lamp assembly from the lamp clip.

Lamp holder (upper)

Sheet-fixing angle

33

32

35

34

33

Sheet-fixing angle

Lamp holder (lower)

Lamp unit

36

Diffusion plate

Diffusion plate

Prism sheet

Reflection/shade sheet

Back shield

35

Lamp holder (lower)

Lamp holder (upper)

16

Page 17

LC-M3700

LC-M3710

ADJUSTING PROCEDURE OF EACH SECTION

[How to enter the process adjustment mode]

Caution:Take great care not to allow the customer to know the method of entering the process

adjustment mode described below. If the setting in the process adjustment mode is changed

indiscriminately, an unrecoverable error may be caused.

<Main process>

1) Using the remote control or main body switch, put the unit in a standby state. (The power LED is "Red".)

2) Press the "MAIN POWER" button to turn off the power.

3) Press the "POWER" button on the display section to turn off the power.

4) While pressing the "INPUT" and "MENU" keys on the main body side together, press the "MAIN POWER"

switch on the main body to turn on the power.

If a display such as "1/16" and "N358" is shown in blue characters on one line at the top of the screen several

seconds later, the process adjustment mode has been entered. Pressing any of the cursor UP/DOWN/LEFT/

RIGHT keys will display the process adjustment items.

If you fail to enter the process adjustment mode (the same display as in the case of normal startup appears),

repeat the above-described steps again.

<Monitor process>

1) Using the remote control or main body switch, put the unit in a standby state. (The power LED is "Red".)

2) Press the "MAIN POWER" button to turn off the power.

3) Press the "POWER" button on the display section to turn off the power.

4) While pressing the "INPUT" and "UP" keys on the main body side together, press the "MAIN POWER" switch

on the main body to turn on the power.

It is also possible to enter the monitor process mode by setting "KOUTEI CHANGR" on the last line of the first

page of the main process mode to MONITOR with the VOL +/- key and pressing the ENTER key. To switch

from the monitor process mode to the main process mode, set "KOUTEI CHANGR" on the last line of the first

page of the monitor process mode to MAIN and press the ENTER key.

17

Page 18

LC-M3700

LC-M3710

[Key operation]

MENU: Used to move up by one line.

RETURN: Used to move down by one line.

VOL +/-: Used to change the setting on the selected line (+1/-1).

Cursor UP/DOWN: Used to scroll by page (Previous/Next).

Cursor RIGHT/LEFT: Used to change the setting on the selected line (+10/-10).

INPUT: Used to change the input (INPUT1→ INPUT2→ INPUT3→ PC).

ENTER: Used to execute the function.

[Reading of process adjustment values]

The adjustment values set at the factory before shipping are stored on the main PWB of this unit (not covering all

the items in the process menu). In repairing the unit, if the problem is solved only by replacing the PCI/F unit, you

can read the stored adjustment values and therefore all you do is to adjust some items only.

• How to read the stored ex-factory adjustment values (backup data)

Select (page7) EEPROM RECOVER, set it from "OFF" to "ON" with the "VOL" key, and then press the "ENTER"

key. If "error" is displayed, you have failed to read the data and therefore have to adjust all the items.

• Adjustments required after reading the stored ex-factory adjustment values (when the data is read successfully)

Ë+Badj3.3V reference voltage adjustment

Ë+Badj1.8V important component operating voltage adjustment (It is adjusted automatically by pressing the

"ENTER" key after 3.3V adjustment above.)

ËN358 WB adjusting white balance adjustment (Video)

ËPAL WB adjusting white balance adjustment (Video)

ËCOMP 15K WB adjusting white balance adjustment (Component 525i)

ËCOMP 33K WB adjusting white balance adjustment (Component hi-vision)

18

Page 19

[Actual adjustment]

P802P802P802

11

121212

Before entering the process adjustment mode, reset all the user settings.

(Execute Menu [Video Adjustment]-|[Reset].)

1. Analog adjustment

1) Voltage adjustment

Adjustment item Adjustment condition Adjusting method

LC-M3700

LC-M3710

1 3.3V adjustment page2

+BAdj3.3V

(NTSC color bar received)

2 1.8V adjustment page2

+BAdj1.8V

2) PAL signal adjustment

Adjustment item Adjustment condition Adjusting method

1 Signal input

Connect a voltmeter to TP4 of the PC I/F unit and

adjust the voltage to 3.30±0.01V.

TP4

TP4

If 3.3V adjustment is completed, pressing the ENTER

key on the remote control with the "+BADJ1.8V" line

selected will adjust the voltage automatically. If

"ERR" appears, adjust the voltage to 1.90V using pin

(1) of CN9 of the PC I/F unit.

Using a signal generator, feed PAL split field color

bars (containing 100% white and having color

saturation of 75%) to the video signal input terminal

of INPUT1 or INPUT2.

1 Setting

Set the color system is to PAL by selecting a PAL

source.

2

MAIN PAL Y

gain adjustment

Page3

PAL Y GAIN

Using pin (1) of P802, adjust the gain to

0.70±0.025Vp-p.

19

Page 20

LC-M3700

0.53Vp-p

0.53Vp-p

LC-M3710

2) PAL signal adjustment

Adjustment item Adjustment condition Adjusting method

3

MAIN PAL color

density adjustment

4

MAIN PAL Cr level adjustment

5

MAIN CONTRAST

adjustment

PAL CB GAIN

CONTRAST 15k

Using pin (3) of P802, make adjustment so that the

interval indicated in the figure below becomes

0.53±0.025Vp-p.

Using pin (5) of P802, make adjustment so that the

interval indicated in the figure below becomes

0.53±0.025Vp-p.

0.53Vp-p

Using the IC8805 output (TP8805), adjust the

contrast to 0.90±0.025Vp-p above the pedestal.

TP8805TP8805

3) SECAM signal adjustment

Adjustment item Adjustment condition Adjusting method

Signal input Using a signal generator, feed SECAM split field

color bars (containing 100% white and having color

saturation of 75%) to the video signal input terminal

of INPUT1 or INPUT2.

Setting Set the color system to SECAM.

1

SECAM Y gain

2 Page4

adjustment

SECAM color density

3 Page4

adjustment

SECAM Y GAIN

SECAM CB GAIN

Using pin (1) of P802, adjust the gain to

0.70±0.025Vp-p.

Using pin (3) of P802, make adjustment so that the

interval indicated in the figure below becomes

0.53±0.025Vp-p.

20

Page 21

0.53Vp-p

3) SECAM signal adjustment

Adjustment item Adjustment condition Adjusting method

LC-M3700

LC-M3710

4 MAIN SECAM Cr level SECAM CR GAIN

adjustment

Using pin (5) of P802, make adjustment so that the

interval indicated in the figure below becomes

0.53±0.025Vp-p.

0.53Vp-p

4) N358 signal adjustment

Adjustment item Adjustment condition Adjusting method

Signal input Using a signal generator, feed NTSC3.58 split field

color bars (containing 100% white and having color

saturation of 75%) to the video signal input terminal

of INPUT1 or INPUT2.

Setting Set the color system to N358.

1

MAIN N358 Y gain

2 page 5

adjustment

N358 Y GAIN

Using pin (1) of P802, adjust the gain to

0.70±0.025Vp-p.

MAIN N358 color

3 N358 CB GAIN

density adjustment

MAIN N358 Cr level

4 N358 CR GAIN

adjustment

MAIN N358 TINT

5 N358 TINT

adjustment

Using pin (3) of P802, make adjustment so that the

interval indicated in the figure below becomes

0.53±0.025Vp-p.

Using pin (5) of P802, make adjustment so that the

interval indicated in the figure below becomes

0.53±0.025Vp-p.

0.53Vp-p

Using the TB124_MAIN output (P802-3pin), make

adjustment so that the bottoms of waveforms are

aligned as shown in the figure below.

Should be aligned like this.

21

Page 22

LC-M3700

LC-M3710

5) Component 15kHz signal adjustment

Adjustment item Adjustment condition Adjusting method

Signal input

1 Setting

2 MAIN component 15K Page 6

CONTRAST adjustment COMP 15k (CONTRAST)

6) Component HDTV signal adjustment

Adjustment item Adjustment condition Adjusting method

Signal input

1 Setting

Using a signal generator, feed component 15K full

field color bars (containing 100% white and having

color saturation of 100%) to the component video

signal input terminal of INPUT3.

et to component 15kHz.

Using IC8805 (TP8805), adjust the contrast to

0.90±0.025Vp-p.

Using a signal generator, feed component 33K

(HDTV1080i) full field color bars (containing 100%

white and having color saturation of 100%) to the

component video signal input terminal of INPUT3.

Set to component 33kHz.

2 MAIN component HDTV Page 6

CONTRAST adjustment COMP HD CONTRAST

Using IC8805 (TP8805), adjust the 100% white to

0.90±0.025Vp-p above the pedestal.

22

Page 23

2. Analog adjustment

1) N358 white balance adjustment

Adjustment item Adjustment condition Adjusting method

Signal input Using a signal generator, feed NTSC signal window

patterns (in-window 20IRE) to the video input

terminal of INPUT1.

20IRE

LC-M3700

LC-M3710

1 Setting

2 R CUTOFF adjustment Page7

N358 R CUTOFF

Set the color system to N358.

1. On the R CUTOFF item, press the ENTER key to

display the special gamma.

2. Adjust the value so that the color in the window

becomes brightest.

3 G CUTOFF adjustment N358 G CUTOFF 1. On the G CUTOFF item, press the ENTER key to

display the special gamma.

2. Adjust the value so that the color in the window

becomes brightest.

4 B CUTOFF adjustment N358 B CUTOFF 1. On the B CUTOFF item, press the ENTER key to

display the special gamma.

2. Adjust the value so that the color in the window

becomes brightest.

5 Setting Set the window white level of the window pattern

from the signal generator to 80IRE.

80IRE

6 R DRIVE adjustment N358 R DRIVE 1. On the R DRIVE item, press the ENTER key to

display the special gamma.

2. Adjust the value so that the color in the window

becomes brightest.

7 G DRIVE adjustment N358 G DRIVE 1. On the G DRIVE item, press the ENTER key to

display the special gamma.

2. Adjust the value so that the color in the window

becomes brightest.

8 B DRIVE adjustment N358 B DRIVE 1. On the B DRIVE item, press the ENTER key to

display the special gamma.

2. Adjust the value so that the color in the window

becomes brightest.

9 Setting On the item, press the ENTER key again to make the

special gamma disappear.

After performing steps 1 to 3 and 6 to 8, repeat adjustment so that the color becomes brightest for both 20IRE and 80IRE.

23

Page 24

LC-M3700

LC-M3710

2) PAL white balance adjustment

Adjustment item Adjustment condition Adjusting method

Signal input Using a signal generator, feed NTSC signal window

patterns (in-window 20IRE) to the video input

terminal of INPUT1.

20IRE

1 Setting

2 R CUTOFF adjustment Page8

PAL R CUTOFF

Set the color system to PAL.

1. On the R CUTOFF item, press the ENTER key to

display the special gamma.

2. Adjust the value so that the color in the window

becomes brightest.

3 G CUTOFF adjustment PAL G CUTOFF 1. On the G CUTOFF item, press the ENTER key to

display the special gamma.

2. Adjust the value so that the color in the window

becomes brightest.

4 B CUTOFF adjustment PAL B CUTOFF 1. On the B CUTOFF item, press the ENTER key to

display the special gamma.

2. Adjust the value so that the color in the window

becomes brightest.

5 Setting Change the ion-window white level of the window

pattern from the signal generator to 80IRE.

80IRE

6 R DRIVE adjustment PAL R DRIVE 1. On the R DRIVE item, press the ENTER key to

display the special gamma.

2. Adjust the value so that the color in the window

becomes brightest.

7 G DRIVE adjustment PAL G DRIVE 1. On the G DRIVE item, press the ENTER key to

display the special gamma.

2. Adjust the value so that the color in the window

becomes brightest.

8 B DRIVE adjustment PAL B DRIVE 1. On the B DRIVE item, press the ENTER key to

display the special gamma.

2. Adjust the value so that the color in the window

becomes brightest.

9 Setting On the item, press the ENTER key again to make the

special gamma disappear.

After performing steps 1 to 3 and 6 to 8, repeat adjustment so that the color becomes brightest for both 20IRE and 80IRE.

24

Page 25

3) Component 15K white balance adjustment

Adjustment item Adjustment condition Adjusting method

Signal input Using a signal generator, feed component 15K signal

(525i) window patterns (in-window 20IRE) to the

video input terminal of INPUT3. Y input only is

sufficient.

20IRE

LC-M3700

LC-M3710

1 Setting

2 R CUTOFF adjustment Page9

COMP 15k R CUTOFF

Set the input to INPUT3 component.

1. On the R CUTOFF item, press the ENTER key to

display the special gamma.

2. Adjust the value so that the color in the window

becomes brightest.

3 G CUTOFF adjustment COMP 15k G CUTOFF 1. On the G CUTOFF item, press the ENTER key to

display the special gamma.

2. Adjust the value so that the color in the window

becomes brightest.

4 B CUTOFF adjustment COMP 15k B CUTOFF 1. On the B CUTOFF item, press the ENTER key to

display the special gamma.

2. Adjust the value so that the color in the window

becomes brightest.

5 Setting Change the in-window white level of the window

pattern from the signal generator to 80IRE.

80IRE

6 R DRIVE adjustment COMP 15k R DRIVE 1. On the R DRIVE item, press the ENTER key to

display the special gamma.

2. Adjust the value so that the color in the window

becomes brightest.

7 G DRIVE adjustment COMP 15k G DRIVE 1. On the G DRIVE item, press the ENTER key to

display the special gamma.

2. Adjust the value so that the color in the window

becomes brightest.

8 B DRIVE adjustment COMP 15k B DRIVE 1. On the B DRIVE item, press the ENTER key to

display the special gamma.

2. Adjust the value so that the color in the window

becomes brightest.

9 Setting On the item, press the ENTER key again to make the

special gamma disappear.

After performing steps 1 to 3 and 6 to 8, repeat adjustment so that the color becomes brightest for both 20IRE and 80IRE.

25

Page 26

LC-M3700

E

E

LC-M3710

4) Component 33K white balance adjustment

Adjustment item Adjustment condition Adjusting method

Signal input Using a signal generator, feed component 33K signal

(1080i) window patterns (in-window 20IRE) to the

video input terminal of INPUT3. Y input only is

sufficient.

20IR

1 Setting

2 R CUTOFF adjustment Page10

COMP HDTV R CUTOFF

Set the input to INPUT3 component.

1. On the R CUTOFF item, press the ENTER key to

display the special gamma.

2. Adjust the value so that the color in the window

becomes brightest.

3 G CUTOFF adjustment COMP HDTV G CUTOFF 1. On the G CUTOFF item, press the ENTER key to

display the special gamma.

2. Adjust the value so that the color in the window

becomes brightest.

4 B CUTOFF adjustment COMP HDTV B CUTOFF 1. On the B CUTOFF item, press the ENTER key to

display the special gamma.

2. Adjust the value so that the color in the window

becomes brightest.

5 Setting Change the in-window white level of the window

pattern from the signal generator to 80IRE.

80IR

6 R DRIVE adjustment COMP HDTV R DRIVE 1. On the R DRIVE item, press the ENTER key to

display the special gamma.

2. Adjust the value so that the color in the window

becomes brightest.

7 G DRIVE adjustment COMP HDTV G DRIVE 1. On the G DRIVE item, press the ENTER key to

display the special gamma.

2. Adjust the value so that the color in the window

becomes brightest.

8 B DRIVE adjustment COMP HDTV B DRIVE 1. On the B DRIVE item, press the ENTER key to

display the special gamma.

2. Adjust the value so that the color in the window

becomes brightest.

9 Setting On the item, press the ENTER key again to make the

special gamma disappear.

After performing steps 1 to 3 and 6 to 8, repeat adjustment so that the color becomes brightest for both 20IRE and 80IRE.

26

Page 27

3. Monitor section adjustment

Analog adjustment

1) Voltage adjustment

Adjustment item Adjustment condition Adjusting method

LC-M3700

LC-M3710

Using a signal generator, feed NTSC signal color

bars to the video input terminal of INPUT1.

1 Setting

2 VLS BIAS adjustment Monitor process

adjustment mode

Page2

3 GRAY LEVEL Monitor process

adjustment adjustment mode

Page2

4 COM BIAS adjustment Monitor process

adjustment mode

Page2

1. Set the input to INPUT1.

2. Enter the process adjustment mode, set the

KOUTEI CHANGR item on Page 1 to MONITOR

with the VOL key and press the ENTER key.

3. The monitor process adjustment mode is

established.

Connect a digital voltmeter to TL4103 (A-side) or

TL4103 (B-side) and adjust the VLS bias to

15.00V±0.05V.

Connect a digital voltmeter to TL4102 (A-side) or

TL4101 (B-side) and adjust the gray level to

14.50V±0.05V.

1. On the COM BIAS item, press the ENTER key to

display the adjustment pattern.

2. Set the value so that the flicker near the center of

the screen is minimized.

3. Press the ENTER key to make the pattern

disappear.

27

Page 28

LC-M3700

LC-M3710

2) Monitor white balance adjustment (15k)

~ All the video adjustments on the MAIN side should be completed before making this adjustment.

Adjustment item Adjustment condition Adjusting method

Signal input

Using a signal generator, feed composite signal

(NTSC) raster patterns (20IRE) to the video input

terminal of INPUT1.

20IRE

1 Setting

1. [Video Adjustment]-[Reset] execution

2. [Energy-Saving Setting]-Brightness [+8]

3. [Video Adjustment]-[Pro Setting]-[Color

Temperature]-Middle

4. [Video Adjustment]-[Pro Setting]-[Black Extension]OFF

2 Adjustment Page14 Using a color meter, adjust R GAMMA 15K (LO) and

B GAMMA 15K (LO) to x=0.287, y=0.285±0.0035

(Measure the central part of the screen.)

3 Setting Using a signal generator, feed composite signal

(NTSC) raster patterns (80IRE) to the video input

terminal of INPUT1.

80IRE

4 Adjustment Page14 Using a color meter, adjust R GAMMA 15K (HI) and

B GAMMA 15K (HI) to x=0.287, y=0.285±0.0015

(Measure the central part of the screen.)

5 Adjustment Page14 Change the WRITE GAMMA 15K item from OFF to

ON with the VOL key and press the ENTER key.

(Execution of writing of the adjusted values.)

28

Page 29

3) Monitor white balance adjustment (HDTV)

~ All the video adjustments on the MAIN side should be completed before making this adjustment.

Adjustment item Adjustment condition Adjusting method

LC-M3700

LC-M3710

Signal input

1 Setting

2 Adjustment Page14

3 Setting

Using a signal generator, feed component signal

(1080i) raster patterns (20IRE) to the video input

terminal of INPUT3. Y input only is sufficient.

20IRE

1. [Video Adjustment]-[Reset] execution

2. [Energy-Saving Setting]-Brightness [+8]

3. [Video Adjustment]-[Pro Setting]-[Color

Temperature]-Middle

4. [Video Adjustment]-[Pro Setting]-[Black

Extension]-OFF

Using a color meter, adjust R GAMMA (LO) and B

GAMMA (LO) to x=0.287, y=0.285±0.0035

(Measure the central part of the screen.)

Using a signal generator, feed component signal

(1080i) raster patterns (80IRE) to the video input

terminal of INPUT3.

4 Adjustment Page14

5 Adjustment Page14

4. Factory settings

Adjustment item Adjustment condition Adjusting method

1 Settings

2 Factory settings Page1

80IRE

Using a color meter, adjust R GAMMA (HI) and B

GAMMA (HI) to x=0.287, y=0.285±0.0015

(Measure the central part of the screen.)

Change the WRITE GAMMA HDTV item from

OFF to ON with the VOL key and press the

ENTER key.

(Execution of writing of the adjusted values.)

Enter the process adjustment mode.

Set the INDUSTRY INIT item to ON with the VOL

+/- key and press the ENTER key.

2. When the process mode is exited and the input

is set to INPUT1, factory setting has been

completed.

3. Turn OFF the main power.

Items initialized through factory setting

• EUser adjustment value

• EPassword

• EAccumulated operating time (main side only)

• EID number

29

Page 30

LC-M3700

LC-M3710

HOW TO UPGRADE THE INTERNAL PROGRAM

The program used in this unit is divided into the following two programs, which are rewritten by different methods.

• Main program

• Monitor program

[How to enter the process adjustment mode]

Caution:Take great care not to allow the customer to know the method of entering the process

adjustment mode described below. If the setting in the process adjustment mode is changed

indiscriminately, an unrecoverable error may be caused.

<Main process>

1) Plug the power cord in the wall outlet.

2) Press the "MAIN POWER" button to turn off the power.

3) While pressing the "INPUT" and "MENU" buttons together, press the "MAIN POWER" button to turn on the

power.

(Keep pressing the "INPUT" and "MENU" buttons until a display appears.)

If "1/16" is displayed in blue characters on the screen several seconds later, the process adjustment mode has

been entered. Pressing any of the cursor UP/DOWN/LEFT/RIGHT keys will display the 1st page of the process

adjustment mode.

If you fail to enter the process adjustment mode (the same display as in the case of normal startup appears),

repeat the above-described steps again.

[Necessary devices]

• Personal computer

Personal computer equipped with Windows 95/98/me/2000/xp

Personal computer with a COM port (RS-232C). An USB-RS232C converter may be used depending on the

setting, but consider the compatibility.

• RS-232C scroll cable

"Interlink cable" can be used.

[Preparations]

1) Software for rewriting is provided as an executable file having a name such as "MAIN_2002_10_10A.exe"

(tentative name). Create a directory with an appropriate name on the hard disc of the PC to be used for

rewriting and copy the software to it.

2) When this file is double-clicked on Windows, decompressing the compressed file is started. Carefully check

if the contents of the decompressed file correspond to the documentation attached to the program.

3) Using the RS-232C cable, connect the personal computer with the main body.

4) Enter the process adjustment mode according to "How to enter the process adjustment mode" described

above.

30

Page 31

LC-M3700

LC-M3710

[How to rewrite the main program]

1) After entering the process adjustment mode, proceed to page 16 using the ÅgDOWNÅh key on the remote

control or main body ("16/16" is displayed on the upper-left corner).

2) Select "CENTER PROG UPDATE" with the "MENU" or "RETURN" key on the remote control.

3) Change "CENTER PROG UPDATE" from "OFF" to "ON" with the "VOL (+)/(-)" on the remote control.

4) Press the "ENTER" key on the remote control. The characters displayed on the screen disappear and the

screen becomes black.

5) Double-clock the decompressed batch file (specified by the attached documentation) in the directory on the

PC.

6) A black window (MS-DOS window) opens on the screen and writing is started automatically.

After a short time, "OK, Received successfully" is displayed on the screen.

Rewriting of the main program has been completed. Unplug the power cord to turn off the power and then turn

it on again.

7) For confirmation, enter the process adjustment mode again and check that the version information shown on

the lines "CENTER Version", "OSD version" and "CVIC Version" on the 1st page corresponds to the new

version shown on the attached documentation.

31

Page 32

LC-M3700

LC-M3710

[How to rewrite the monitor program]

1) After entering the process adjustment mode, start up the terminal software obtained separately.

(Freeware products available on the Internet can be used.)

2) Make setting as shown below.

Baud rate: 9600

Data: 8 bits

Parity: NONE

Stop: 1 bit

Flow control: NONE

3) If the above setting is made correctly, pressing the ÅgENTERÅh key on the PC will make ÅgERRÅh appear on

the terminal software.

4) In this state, type the following. ( means the ENTER key.)

The characters displayed on the screen disappear and the screen becomes black.

IPL_0002

~ Immediately after the above entry, an unusual display may be appear on the terminal software, which means no

abnormal condition.

32

Page 33

LC-M3700

LC-M3710

5) Change the baud rate to 115200.

6) Press the ÅgENTERÅh key to make appear the following display

ERR

SEND "MONITOR PROG UPDATE PROGRAM" from PC to MR

7) Using the file transmission function (function to transmit specified file contents) of the terminal software, select

the decompressed file (specified by the attached documentation) in the directory on the PC and execute

transmission.

8) When the following display appears on the terminal software, rewriting of the monitor program has been

completed. (Its contents may vary depending on the terminal software or program.)

Unplug the power cord to turn off the power and then turn it on again.

9) For confirmation, enter the process adjustment mode again and check that the version information shown on

the line "Monitor Version" on the 1st page corresponds to the new version shown on the attached documentation.

33

Page 34

LC-M3700

LC-M3710

DESCRIPTION OF FUNCTION OF MAJOR ICs

• IC4701 (IXA332WJ)

This IC is a QS driver for EVEN.

It QS (Quick Shoot)-drives the input signal sent from the DVI receiver according to the temperature parameter

setting from the monitor microcomputer.

• EIC4901 (IXA332WJ)

This IC is a QS driver for ODD.

It QS (Quick Shoot)-drives the input signal sent from the DVI receiver according to the temperature parameter

setting from the monitor microcomputer. In addition, after QS-driving the H and V synchronization signal and

DE signal sent from the DVI receiver, it outputs the H and V synchronization signal and DE signal.

• EIC4501 (IXA457WJ)

This IC is a liquid crystal controller.

It allocate the video data of the 24-bit RGB signal, H and V synchronization signal and DE signal sent from the

QS driver (ODD and EVEN) to the left-side ODD and EVEN and the right-side ODD and EVEN of the liquid

crystal panel and outputs the control signal for driving the liquid crystal panel. It also generates the control

signal for dimmer control.

• EIC4303 (IXA345WJ)

This IC is a CPLD.

Because the QS driver and liquid crystal controller are general-purpose FPGAs, it is used to make setting for

each FPGA. After resetting, it reads the program data from IC4301 (flash) and makes setting for each IC

through serial transmission.

• EIC4105 (IXA350WJ)

This IC is a gray scale reference power for TFT liquid crystal. It incorporates ten circuits of gray scale output

buffer amp, a CMOS buffer amp and a reference voltage supply.

• EIC2004 (IXA3491CE)

This IC is a monitor microcomputer. It performs OSD control of the monitor section, detection of the panel

temperature through the thermistor, setting of the temperature parameter for the OS driver, setting of the timing

for the liquid crystal controller, setting of the dimmer control data, power control of the monitor section, monitoring

of each power line, remote control decoding and OPC control.

34

Page 35

LC-M3700

Ë

VHiTFP501++-1Q (ASSY:IC1104)

Panel Bus HDCP DIGITAL RECEIVER

»Block Diagram

»Pin Function

Pin No. Pin Name I/O Pin Function

79 AGND — Analog ground—Ground reference and current return for analog circuitry.

79 AGND — Analog ground—Ground reference and current return for analog circuitry.

82,85,88,91 AVDD — Analog VDD—Power supply for analog circuitry. Nominally 3.3V.

67 CAP O

Bypass capacitorÅ\4.7 _F tantalum and 0.01 _F ceramic capacitors connected to ground.

41,40 CTL[2:1] O General purpose control signals—Used for user defined control. In normal mode

CTL1 is not powered down via PDO.

94 DDC_SA 1 Display data channel_serial address—I2C Slave address bit A0 for display data

channel (DDC). Refer to I2C Interface section for more details.

92 DDC_SCL I/O Display data channel_serial clock—I2C Clock for the DDC. External pullup

resistors = 10 k_ and 3.3V to lerant.

93 DDC_SDA I/O Display data channel_serial data—I2C Data for the DDC. External pullup

resistors = 10 k_ and 3.3V to lerant.

46 DE O Output data enable—Used to indicate time of active video display versus

nonactive display or blanking interval. During blanking, only HSYNC, VSYNC

and CTL1_2 are transmitted. During times of active display, or nonblanking,

only pixel data, QE[23:0] and QO[23:0], is transmitted.

High: active display interval

Low: blanking interval

1 DFO I Output clock data format—Controls the output clock (ODCK) format for either

TFT or DSTN panel support. For TFT support ODCK clock runs continuously.

For DSTN support ODCK only clocks when DE is high; otherwise, ODCK is held

low when DE is low.

High: DSTN support/ODCK held low when DE = low.

Low: TFT support/ODCK runs continuously.

5, 39, 68 DGND — Digital ground—Ground reference and current return for digital core.

6, 38 DVDD Digital VDD—Power supply for digital core. Nominally 3.3V.

48 HSYNC O Horizontal sync output

100 OCK_INV I ODCK Polarity _ Selects ODCK edge on which pixel data (QE[23:0] and QO

[23:0]) and control signals(HSYNC, VSYNC, DE, CTL1_2 ) are latched.

Normal mode:

High: latches output data on rising ODCK edge.

Low: latches output data on falling ODCK edge.

44 ODCK O Output data clock—Pixel clock. All pixel outputs QE[23:0] and QO[23:0]

(if in 2-pixel/clock mode) along with DE, HSYNC, VSYNC and CTL[2:1] are

synchronized to this clock.

19, 28,45, 58,76 OGND —

Output driver ground—Ground reference and current return for digital output drivers.

18, 29,43, 57,78 OVDD — Output driver VDD—Power supply for output drivers. Nominally 3.3V.

2 PD I Power down—An active low signal that controls the TFP501 power-down state.

During power down all output buffers are switched to a high-impedance state

and brought low through a weak pulldown. All analog circuits are powered down

and all inputs are disabled, except for PD.

If PD is left unconnected, an internal pullup defaults the TFP501 to normal operation.

High: normal operation

Low: power down

9 PDO I Output drive power down—An active low signal that controls the power-down

state of the output drivers.

During output drive power down, the output drivers (except SCDT and CTL1) are

driven to a high-impedance state. A weak pulldown slowly pulls these outputs to

a low level. When PDO is left unconnected an internal pullup defaults the

TFP501 to normal operation.

High: normal operation/output drivers on.

Low: output drive power down.

98 PGND — PLL ground _ Ground reference and current return for internal PLL.

4 PIXS I Pixel select—Selects between one or two pixel per clock output modes. During

2-pixel/clock mode, both even pixels, QE[23:0], and odd pixels, QO[23:0], are

output in tandem on a given clock cycle. During 1 pixel/clock, even and odd

pixels are output sequentially, one at a time, with the even pixel first, on the

even pixel bus, QE[23:0]. (The first pixel per line is pixel-0, the even pixel. The

second pixel per line is pixel-1, the odd pixel.)

High: 2 pixel/clock

Low: 1 pixel/clock

95 PROM_SCL I/O EEPROM_serial clock—I2C clock for EEPROM interface data. External pullup

resistors = 10 k_ and 3.3V to lerant.

96 PROM_SDA I/O EEPROM_serial data—I2C data for EEPROM interface data. External pullup

resistors = 10 k_ and 3.3V to lerant.

97, 99 PVDD (1, 2) PLL VDD—Power supply for internal PLL. Nominally 3.3V.

LC-M3710

35-2

35

35-1

Page 36

LC-M3700

10_17 QE[0:7] O Even blue pixel output

—Output for even and odd blue pixels when in 1-pixel/

clock mode. Output for even only blue pixel when in 2-pixel/clock mode. Output

data is synchronized to the output data clock, ODCK.

LSB: QE0/pin 10

MSB: QE7/pin 17

20_27 QE[8:15] O Even green pixel output

—Output for even and odd green pixels when in 1-pixel/

clock mode. Output for even only green pixel when in 2-pixel/clock mode.

Output data is synchronized to the output data clock, ODCK.

LSB: QE8/pin 20

MSB: QE15/pin 27

30_37 QE[16:23] O Even red pixel output

—Output for even and odd red pixels when in 1-pixel/clock

mode. Output for even only red pixel when in 2-pixel/clock mode. Output data is

synchronized to the output data clock, ODCK.

LSB: QE16/pin 30

MSB: QE23/pin 37

49_56 QO[0:7] O Odd blue pixel output

—Output for odd only blue pixel when in 2-pixel/clock

mode. Not used, and held low, when in 1-pixel/clock mode. Output data is

synchronized to the output data clock, ODCK.

LSB: QO0/pin 49

MSB: QO7/pin 56

59_66 QO[8:15] O Odd green pixel output

—Output for odd only green pixel when in 2-pixel/clock

mode. Not used, and held low, when in 1-pixel/clock mode. Output data is

synchronized to the output data clock, ODCK.

LSB: QO8/pin 59

MSB: QO15/pin 66

69_75,77 QO[16:23] O Odd red pixel output

—Output for odd only red pixel when in 2-pixel/clock mode.

Not used, and held low, when in 1-pixel/clock mode. Output data is

synchronized to the output data clock, ODCK.

LSB: QO16/pin 69

MSB: QO23/pin 77

42 RSVD O Reserved—Must be tied high for normal operation.

80 Rx2+ I Channel-2 positive receiver input Positive side of channel-2 T.M.D.S. low

voltage signal differential input pair.

Channel-2 receives red pixel data in active display and CTL2 control signal

during blanking.

81 Rx2_ I Channel-2 negative receiver input

—Negative side of channel-2 T.M.D.S. low

voltage signal differential input pair.

83 Rx1+ I Channel-1 positive receiver input

—Positive side of channel-1 T.M.D.S. low

voltage signal differential input pair. Channel_1 receives green pixel data in

active display and CTL1 control signal during blanking.

84 Rx1_ I Channel-1 negative receiver input

—Negative side of channel-1 T.M.D.S. low

voltage signal differential input pair.

86 Rx0+ I Channel-0 positive receiver input

—Positive side of channel-0 T.M.D.S. low

voltage signal differential input pair. Channel-0 receives blue pixel data in active

display and HSYNC, VSYNC control signals during blanking.

87 Rx0_ I Channel-0 negative receiver input

—Negative side of channel-0 T.M.D.S. low

voltage signal differential input pair.

89 Rx0+ I Clock positive receiver input

—Positive side of reference clock T.M.D.S. low

voltage signal differential input pair.

90 RxC_ I Clock negative receiver input

—Negative side of reference clock T.M.D.S. low

voltage signal differential input pair.

8 SCDT O Sync detect _ Output to signal when the link is active or inactive. The link is

considered to be active when DE is actively switching. The TFP501 monitors the

state DE to determine link activity. SCDT can be tied externally to PDO to

power down the output drivers when the link is inactive.

High: active link

Low: inactive link

3 ST I Output drive strength select

—Selects output drive strength for high or low

current drive. (see dc specifications for IOH and IOL vs ST state.)

High: high drive strength

Low: low drive strength

7 STAG I Staggered pixel select _ An active low signal used in 2 pixel/clock pixel mode

(PIXS = high). Time staggers the even and odd pixel outputs to reduce ground

bounce. Normal operation outputs the odd and even pixels simultaneously.

High: normal simultaneous even/odd pixel output.

Low: time staggered even/odd pixel output.

47 VSYNC O Vertical sync output

Pin No. Pin Name I/O Pin Function

Ë

VHiCXA2171Q-1Q (ASSY:IC8801)

Video/Sync Selector

»Block Diagram

LC-M3710

36-2

36

36-1

Page 37

LC-M3700

»Pin Function

Pin No. Pin Name I/O Pin Function

1 IN3_1 I IN3 system signal input terminals.

2 IN3_2 I Please input through a capacitor.

3 IN3_3 I Bias of the terminal voltage is carried out to 2.9V.

An input Y level should give me 0.7Vp-p and a composit input level as 0.7Vp-p

with a color bar 100%.

In Sync on Y and Sync on Green, please input a Sync level by 0.3 Vp-p.

IN3_1 : Cr/Cb/R signal input

IN3_2 : Cb/Pb/B signal input

IN3_3 : Y/YHD/G signal input

4 IN3_H I IN3_H : They are an self-support H synchronization or the input terminal of CS.

5 IN3_V I IN3_V : It is the input terminal of an self-support V synchronized signal.

Please input through the capacitor for a clamp. A bottom level is clamped by 1V.

Corresponds to positive/negative two-poles nature.

Please input an input on the level shown below.

0.4Vp-p < IN3_H < 4Vp-p

0.4Vp-p < IN3_V <4Vp-p

6 GND3 — GND of a synchronized signal system.

7 IN4_1 I IN4 system signal input terminals.

8 IN4_2 I Please input through a capacitor.

9 IN4_3 I Bias of the terminal voltage is carried out to 2.9V.

An input Y level should give me 0.7Vp-p and a composit input level as 0.7Vp-p

with a color bar 100%.

In Sync on Y and Sync on Green, please input a Sync level by 0.3 Vp-p.

IN4_1 : Cr/Cb/R signal input

IN4_2 : Cb/Pb/B signal input

IN4_3 : Y/YHD/G signal input

10 IN4_H I IN4_H : They are an self-support H synchronization or the input terminal of CS.