Page 1

LC-37HV6U

SERVICE MANUAL

SY3M1LC37HV6U

LCD COLOR TELEVISION

MODEL

In the interests of user-safety (Required by safety regulations in some countries) the set should be restored to its original condition and only parts identical to those specified should be used.

LC-37HV6U

CONTENTS

Page

» IMPORTANT SERVICE SAFETY PRECA UTION .....2

» SPECIFICATIONS................................................ 5

» OPERATION MANUAL ........................................ 6

» DIMENSIONS ....................................................13

» REMOVING OF MAJOR PARTS........................15

»

ADJUSTMENT PROCEDURES (AVC System) ..

» UPGRADING INSTALLED PROGRAMS ...........34

» ADJUSTMENT PROCEDURES (Display) .........37

» TROUBLE SHOOTING TABLE ..........................43

» MAJOR IC INFORMATIONS (AVC System) ...... 54

» MAJOR IC INFORMATIONS (Display)............... 76

» CHASSIS LAYOUT/

OVERALL WIRING DIAGRAM........................... 84

22

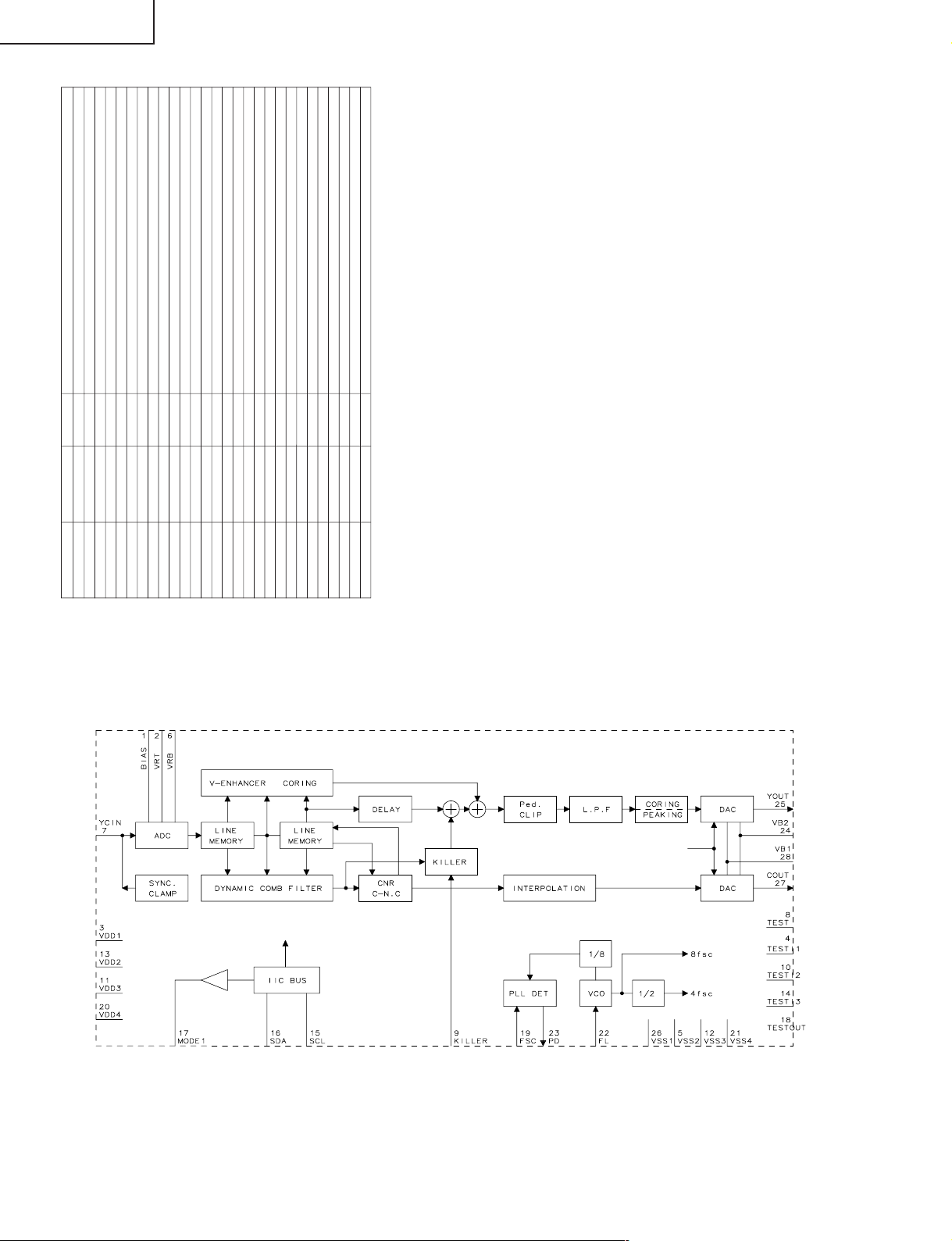

» SYSTEM BLOCK DIAGRAM (AVC System) ......92

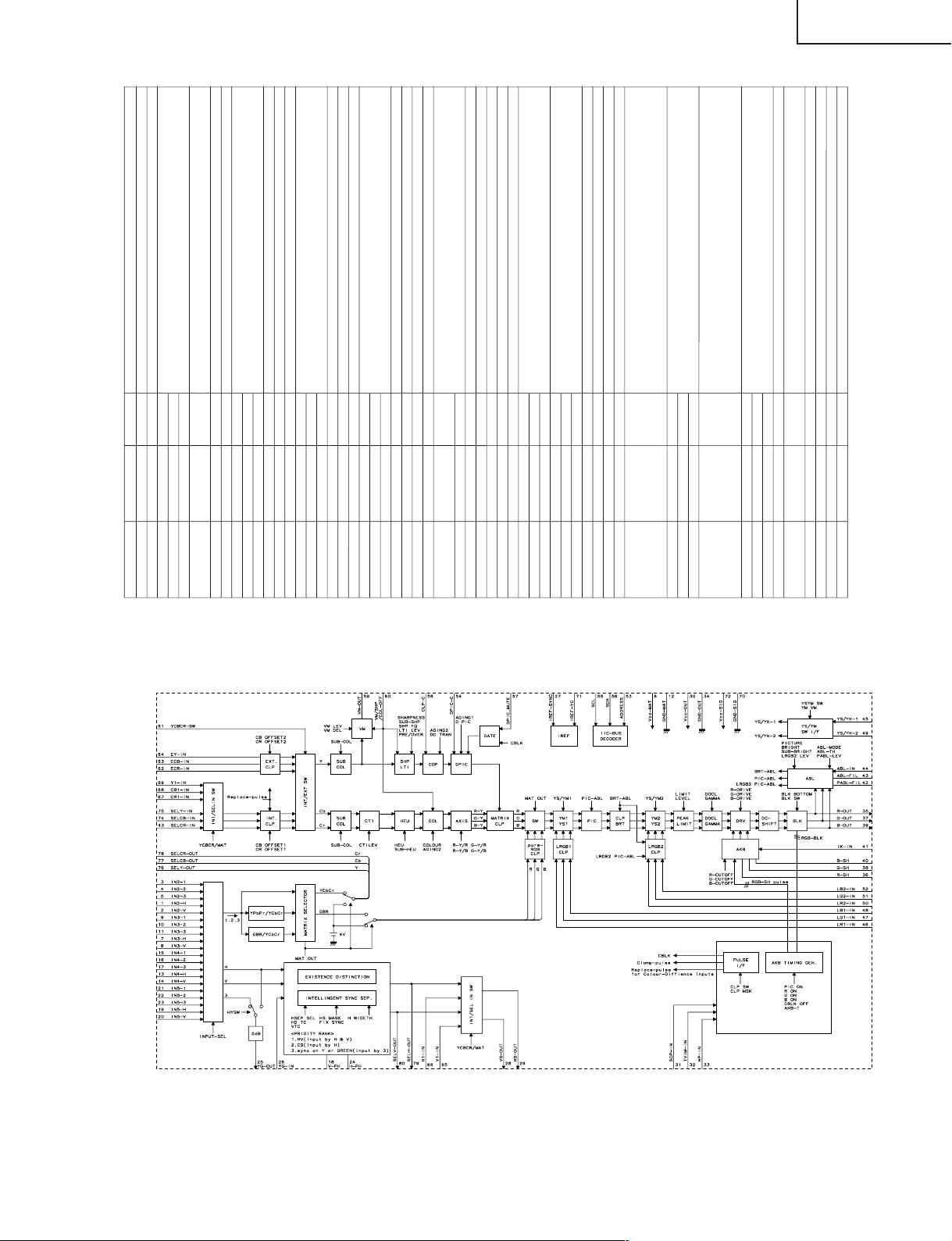

» SIGNAL FLOW BLOCK DIAGRAM

(AVC System)..................................................... 94

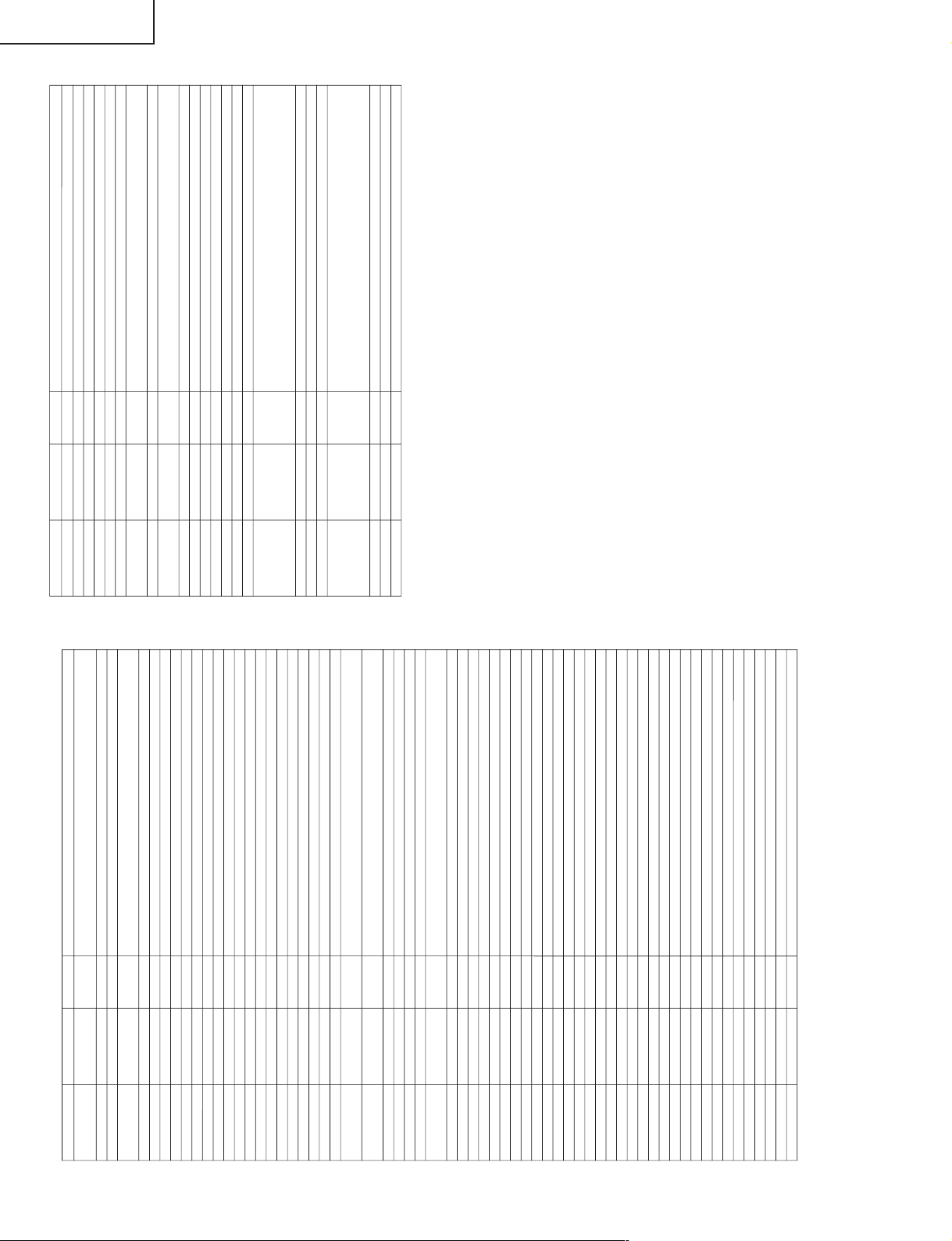

» POWER SYSTEM BLOCK DIAGRAM

(AVC System)..................................................... 96

» PC I/F BLOCK DIAGRAM (AVC System) ..........98

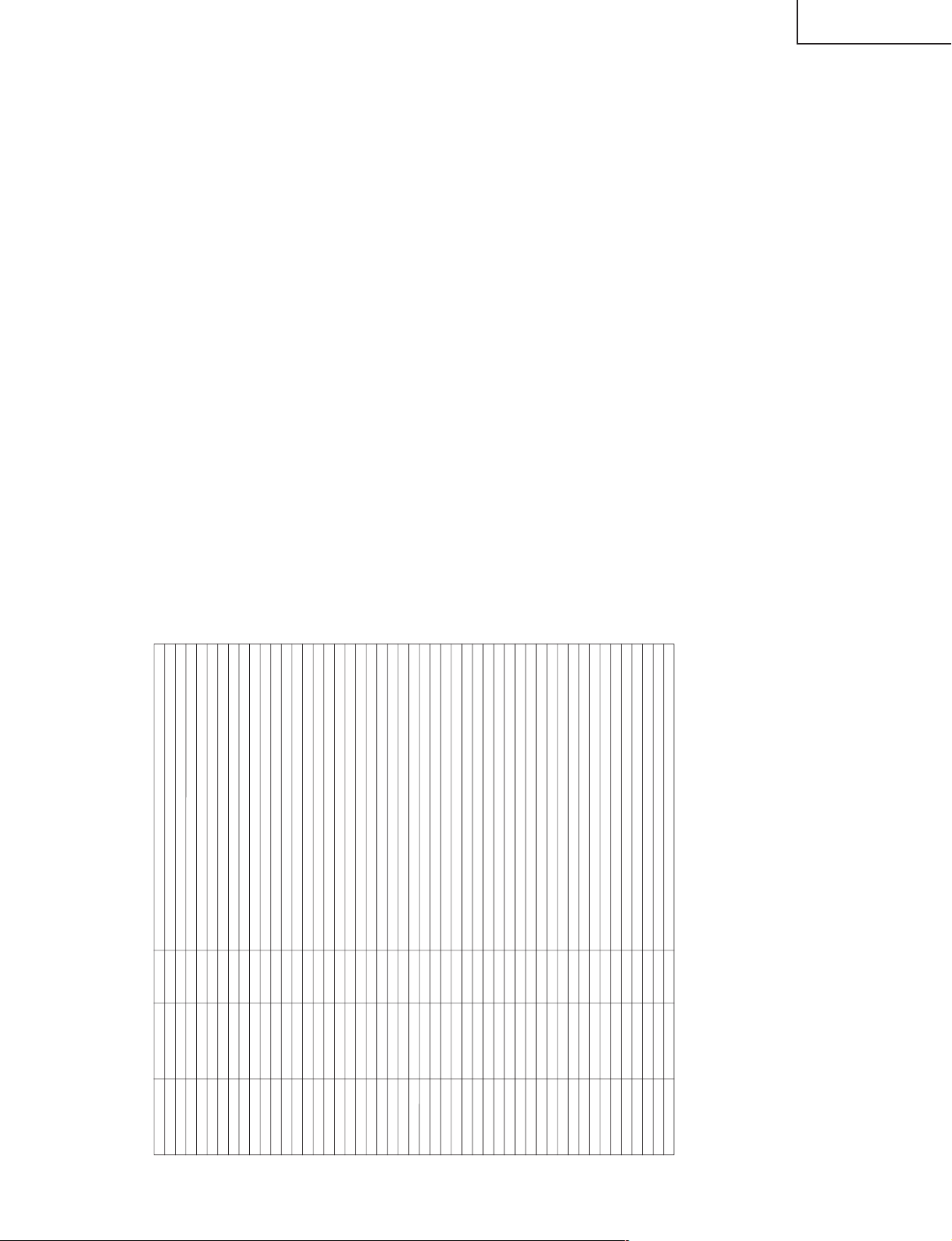

» SIGNAL BLOCK DIAGRAM (Display)..............100

» DESCRIPTION OF SCHEMATIC DIAGRAM ... 102

» SCHEMATIC DIAGRAM................................... 103

» PRINTED WIRING BOARD ASSEMBLIES...... 178

» PARTS LIST ..................................................... 219

» PACKING OF THE SET ...................................263

Page

SHARP CORPORATION

This document has been published to be used for

after sales service only.

The contents are subject to change without notice.

Page 2

LC-37HV6U

1

1

IMPORTANT SERVICE SAFETY PRECAUTION

Ë

Service work should be performed only by qualified service technicians who are thoroughly familiar with all safety checks and the servicing guidelines which follow:

WARNING

ground connected to an earth ground.

» Use an AC voltmeter ha ving with 5000 ohm per volt,

1. For continued safety, no modification of any circuit

should be attempted.

2. Disconnect AC power before servicing.

or higher, sensitivity or measure the A C v oltage drop

across the resistor.

» Connect the resistor connection to all exposed metal

parts having a return to the chassis (antenna, metal

A V

CAUTION: FOR CONTINUED

PROTECTION AGAINST A RISK OF

FIRE REPLACE ONLY WITH SAME

TYPE FUSE.

A VC SIDE: F701 (2A, 250V)

LCD SIDE: F7501, F7502, F7503,

F7504, F7551, F7552, F7553, F7611,

F7612, F7613, F7614, F7641, F7642,

F7643 (800mA, 250V), F2701, F2702

(4A, 250V)

cabinet, screw heads, knobs and control shafts,

escutcheon, etc.) and measure the AC voltage drop

across the resistor.

All checks must be repeated with the AC cord plug

connection reversed. (If necessar y, a nonpolarized

adaptor plug must be used only for the purpose of

completing these checks.)

Any reading of 0.75 Vrms (this corresponds to 0.5

mA rms AC.) or more is excessive and indicates a

potential shock hazard which must be corrected

before returning the monitor to the owner.

BEFORE RETURNING THE RECEIVER

(Fire & Shock Hazard)

Before returning the receiver to the user, perform

the following safety checks:

1. Inspect all lead dress to make certain that leads are

not pinched, and check that hardware is not lodged

between the chassis and other metal parts in the

receiver.

2. Inspect all protective devices such as non-metallic

control knobs, insulation materials, cabinet backs,

adjustment and compartment covers or shields,

isolation resistor-capacitor networks, mechanical

insulators, etc.

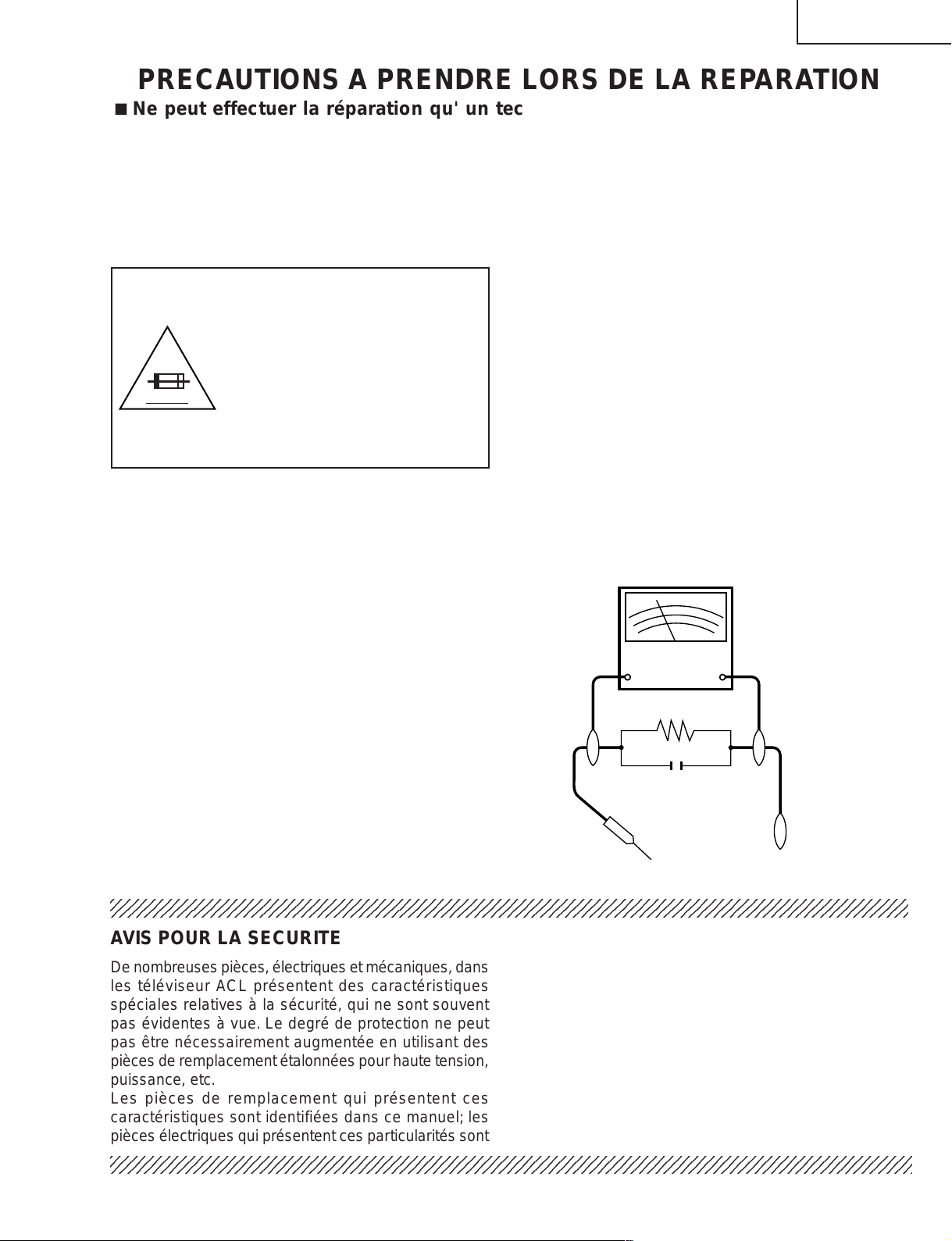

3. To be sure that no shock hazard exists, check for

leakage current in the following manner.

» Plug the AC cord directly into a 110~240 volt A C outlet.

» Using two clip leads, connect a 1.5k ohm, 10 watt

resistor paralleled by a 0.15µF capacitor in series

with all exposed metal cabinet parts and a known

earth ground, such as electrical conduit or electrical

23456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012

TO EXPOSED

METAL PARTS

DVM

AC SCALE

1.5k ohm

10W

0.15 µF

TEST PROBE

CONNECT TO

KNOWN EARTH

GROUND

SAFETY NOTICE

Many electrical and mechanical parts in LCD color

television have special safety-related characteristics.

These characteristics are often not evident from visual

inspection, nor can protection afforded by them be

necessarily increased by using replacement components

rated for higher voltage , wattage, etc.

Replacement parts which have these special safety

characteristics are identified in this manual; electrical

and shaded areas in the

Schematic Diagrams.

For continued protection, replacement parts must be

identical to those used in the original circuit.

The use of a substitute replacement parts which do not

have the same safety characteristics as the factory

recommended replacement parts shown in this service

manual, may create shock, fire or other hazards.

components having such features are identified by " å"

23456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012

Replacement Parts List

2

and

Page 3

LC-37HV6U

2

2

PRECAUTIONS A PRENDRE LORS DE LA REPARATION

Ë

Ne peut effectuer la réparation qu' un technicien spécialisé qui s'est parfaitement

accoutumé à toute vérification de sécurité et aux conseils suivants.

AVERTISSEMENT

de 0,15µF en série avec toutes les pièces métalliques

exposées du coffret et une terre connue comme une

1. N'entreprendre aucune modification de tout circuit.

C'est dangereux.

2. Débrancher le récepteur avant toute réparation.

PRECAUTION: POUR LA

PROTECTION CONTINUE CONTRE

LES RISQUES D'INCENDIE,

REMPLACER LE FUSIBLE

CÔTÉ A VC:F701 (2A, 250V)

CÔTÉ LCD:F7501, F7502, F7503,

A V

F7504, F7551, F7552, F7553, F7611,

F7612, F7613, F7614, F7641, F7642,

F7643 (800mA, 250V), F2701, F2702

(4A, 250V)

conduite électrique ou une prise de terre branchée à

la terre.

• Utiliser un voltmètre CA d'une sensibilité d'au moins

5000Ω/V pour mesurer la chute de tension en travers

de la résistance.

• Toucher avec la sonde d'essai les pièces métalliques

exposées qui présentent une voie de retour au châssis

(antenne, coffret métallique, tête des vis, arbres de

commande et des boutons, écusson, etc.) et mesurer

la chute de tension CA en-travers de la résistance.

Toutes les vérifications doivent être refaites après avoir

inversé la fiche du cordon d'alimentation. (Si nécessaire,

une prise d'adpatation non polarisée peut être utilisée

dans le but de terminer ces vérifications.)

Tous les courants mesurés ne doivent pas dépasser

VERIFICATIONS CONTRE L'INCEN-DIE ET

LE CHOC ELECTRIQUE

Avant de rendre le récepteur à l'utilisateur, effectuer

0,5 mA.

Dans le cas contraire, il y a une possibilité de choc

électrique qui doit être supprimée avant de rendre le

récepteur au client.

les vérifications suivantes.

1. Inspecter tous les faisceaux de câbles pour s'assurer

que les fils ne soient pas pincés ou qu'un outil ne soit

pas placé entre le châssis et les autres pièces

métalliques du récepteur.

2. Inspecter tous les dispositifs de protection comme les

boutons de commande non-métalliques, les isolants,

le dos du coffret, les couvercles ou blindages de réglage

DVM

ECHELLE CA

1.5k ohm

10W

et de compartiment, les réseaux de résistancecapacité, les isolateurs mécaniques, etc.

3. S'assurer qu'il n'y ait pas de danger d'électrocution en

vérifiant la fuite de courant, de la facon suivante:

• Brancher le cordon d'alimentation directem-ent à une

0.15 µF

SONDE D'ESSAI

prise de courant de 110-240V. (Ne pas utiliser de

transformateur d'isolation pour cet essai).

• A l'aide de deux fils à pinces, brancher une résistance

de 1.5 kΩ 10 watts en parallèle av ec un condensateur

234567890123456789012345678901212345678901234567890123456789012123456789012345678901234567890121

AUX PIECES

METALLIQUES

EXPOSEES

BRANCHER A UNE

TERRE CONNUE

AVIS POUR LA SECURITE

De nombreuses pièces, électriques et mécaniques, dans

les téléviseur ACL présentent des caractéristiques

spéciales relatives à la sécurité, qui ne sont souvent

pas évidentes à vue. Le degré de protection ne peut

pas être nécessairement augmentée en utilisant des

pièces de remplacement étalonnées pour haute tension,

puissance, etc.

Les pièces de remplacement qui présentent ces

caractéristiques sont identifiées dans ce manuel; les

pièces électriques qui présentent ces particularités sont

234567890123456789012345678901212345678901234567890123456789012123456789012345678901234567890121

identifiées par la marque " å " et hachurées dans la

liste des pièces de remplacement et les diagrammes

schématiques.

Pour assurer la protection, ces pièces doivent être

identiques à celles utilisées dans le circuit d'origine.

L'utilisation de pièces qui n'ont pas les mêmes

caractéristiques que les pièces recommandées par

l'usine, indiquées dans ce manuel, peut provoquer des

électrocutions, incendies, radiations X ou autres

accidents.

3

Page 4

LC-37HV6U

Precautions for using lead-free solder

1 Employing lead-free solder

"PWBs" of this model employs lead-free solder. The LF symbol indicates lead-free solder, and is attached on the

PWBs and service manuals. The alphabetical character following LF shows the type of lead-free solder.

Example:

L Fa

Indicates lead-free solder of tin, silver and copper.

2 Using lead-free wire solder

When fixing the PWB soldered with the lead-free solder, apply lead-free wire solder. Repairing with conventional

lead wire solder may cause damage or accident due to cracks.

As the melting point of lead-free solder (Sn-Ag-Cu) is higher than the lead wire solder by 40°C, we recommend

you to use a dedicated soldering bit, if you are not familiar with how to obtain lead-free wire solder or soldering bit,

contact our service station or service branch in your area.

3 Soldering

As the melting point of lead-free solder (Sn-Ag-Cu) is about 220°C which is higher than the conventional lead

solder by 40°C, and as it has poor solder wettability, you may be apt to keep the soldering bit in contact with the

PWB for extended period of time. However, Since the land may be peeled off or the maximum heat-resistance

temperature of parts may be exceeded, remov e the bit from the PWB as soon as you confirm the steady soldering

condition.

Lead-free solder contains more tin, and the end of the soldering bit may be easily corroded. Mak e sure to turn on

and off the power of the bit as required.

If a different type of solder stays on the tip of the soldering bit, it is allo y ed with lead-free solder. Clean the bit after

every use of it.

When the tip of the soldering bit is blackened during use, file it with steel wool or fine sandpaper.

Be careful when replacing parts with polarity indication on the PWB silk.

Lead-free wire solder for servicing

Part No, ★ Description Code

ZHNDAi123250E J φ0.3mm 250g(1roll) BL

ZHNDAi126500E J φ0.6mm 500g(1roll) BK

ZHNDAi12801KE J φ1.0mm 1kg(1roll) BM

4

Page 5

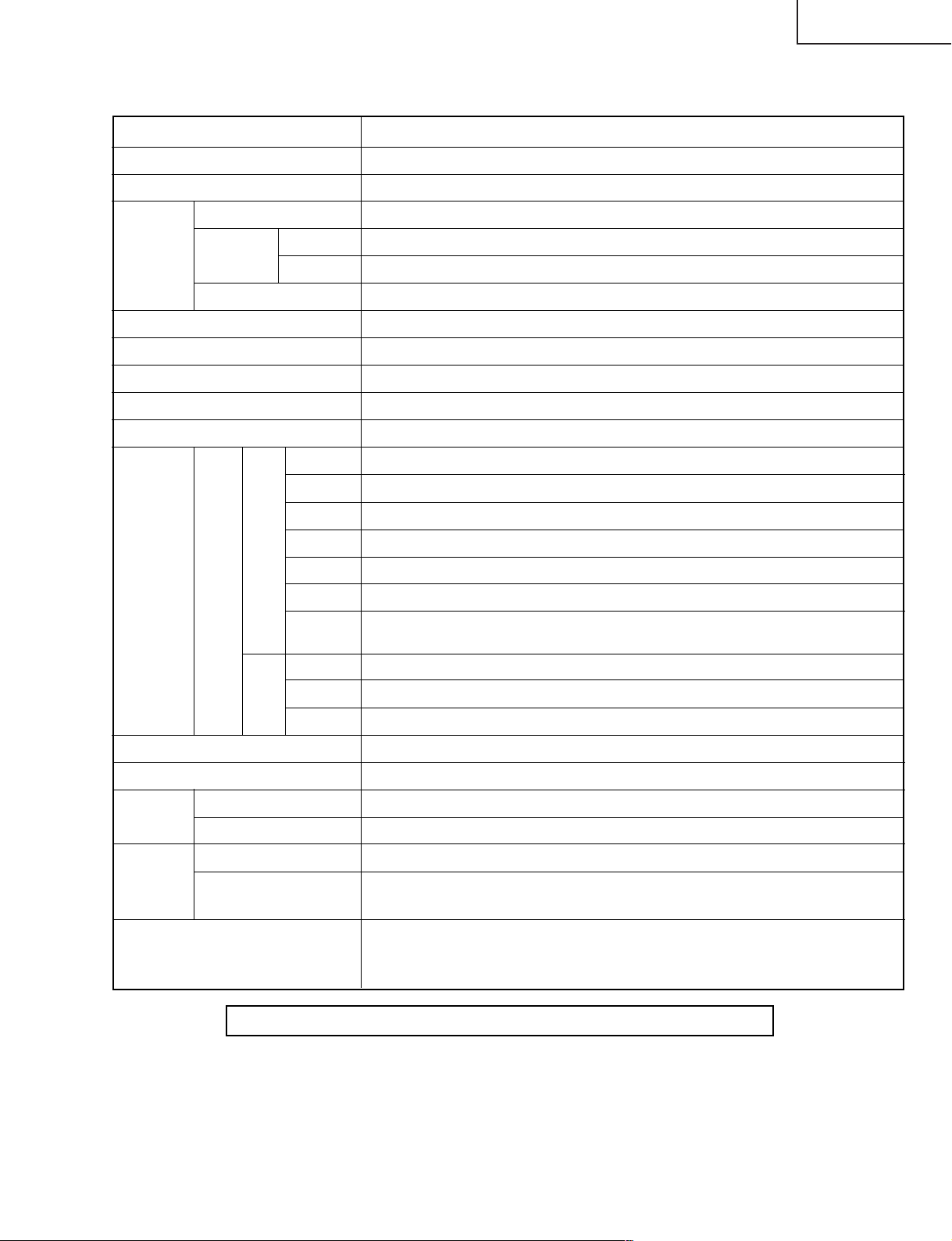

SPECIFICATIONS

Item 37" LIQUID CRYSTAL TELEVISION, Model: LC-37HV6U

LCD panel 37" Advanced Super View & BLACK TFT LCD

Number of dots 3,147,264 dots (1366 × 768 × 3dots)

TV

Function

Brightness 430 cd/m

TV-standard (CCIR)

Receiving

Channel

Audio multiplex BTSC System

VHF/UHF

CATV 1-125ch

American TV Standard NTSC System

VHF 2-13ch, UHF 14-69ch

2

LC-37HV6U

Backlight

Viewing angles H : 170° V : 170°

Audio amplifier 10W × 2

Speakers Ø 8cm 2pcs, Ø 2.5cm 2pcs

Terminals S-VIDEO in, AV in, COMPONENT in

OSD language

Power Requirement

Power

Consumption

Rear INPUT 1

AVC

System

Front

AVC System

Display

INPUT 2

INPUT 3

ANTENNA 75 Ω Unbalance, F Type for VHF/UHF/CATV in

Monitor Out Audio (Variable, Fixed), S-VIDEO out, AV out

DC OUTPUT DC 6.5V 7W MAX

EXT.

SPEAKER

INPUT 4 S-VIDEO, AV in

PC

Headphones

60,000 hours (at Manual Standard position)

S-VIDEO in, AV in

S-VIDEO in, AV in, COMPONENT in, DVI-HDTV in

4Ω 10W (L/R)

15 Pin mini D-Sub, Audio in (Ø 3.5mm jack)

Ø 3.5mm jack

English/French/Spanish

AC 110-240 V, 50/60 Hz

42W (0.4W Standby with AC 120 V)

142W (0.3W Standby with AC 120 V)

Weight

Accessories Operation manual (×1), Remote control unit (×1), System cable (×1), AC cord

AVC System

Display

12.1lbs./5.5 kg (without stand), 12.3 lbs./5.6 kg (with stand)

37.3lbs./16.9kg (Display only), 36.6lbs./16.6kg (with Display and speaker),

55.1lbs./25kg (with Display, speaker and stand)

(×2), "AA" size battery (×2), AVC sytem stand unit (×1), Cable clamp (Large

×1, Small ×1), RF cable (×1), Registration card (×1)

Specifications are subject to change without prior notice.

5

Page 6

LC-37HV6U

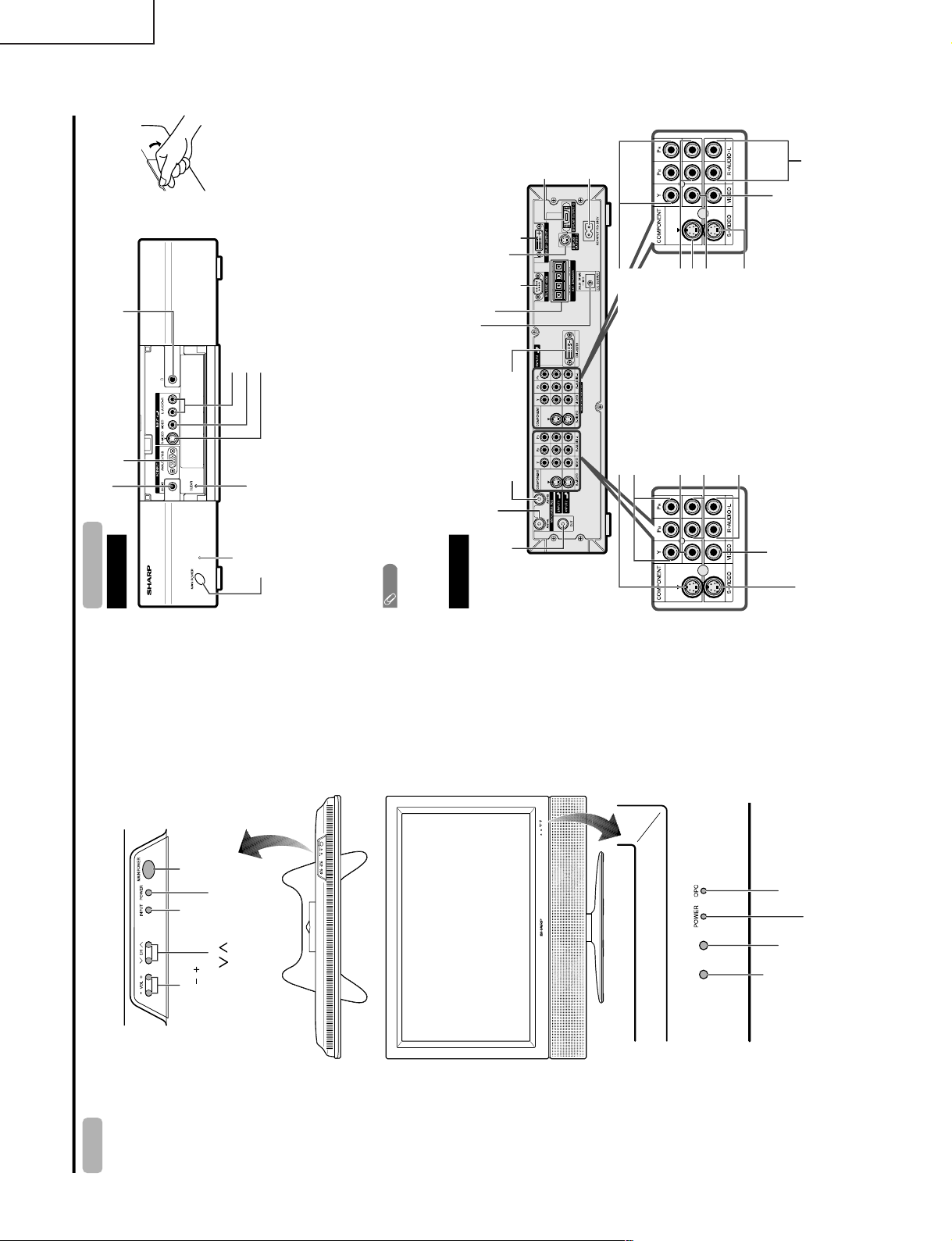

Part names

OPC indicator*

POWER indicator

MAIN POWER

button

OPC sensor

Display

POWER button

INPUT

button

VOLUME buttons

(VOL

/

)

CHANNEL buttons

(CH

/

)

Remote control sensor

*OPC: Optical Picture Con trol

Front view

CLEAR*

MAIN POWER button

INPUT 4 terminal (S-VI DE O)

INPUT 4 terminal (VIDE O)

PC INPUT terminal (AUDIO)

INPUT 4 terminals (AUD IO L/R )

PC INPUT terminal (ANALOG RGB)

AVC System

Rear view

INPUT 1 COMPONENT

video terminals (Y, P

B

, P

R

)

INPUT 3 COMPONENT

video terminals (Y, P

B

, P

R

)

MONITOR OUTPUT termin al

(S-VIDEO)

DISPLAY OUTPUT 1 terminal

DISPLAY

OUTPUT 2

terminal

AC I

NPUT

terminal

RS

-232C

terminal

MONITOR OUTPUT terminals (AUDIO L/R)

Antenna (A)

input terminal

Antenna (B)

input terminal

Antenna (A) output

terminal

DVI-HDTV

INPUT

terminal

INPUT 3 terminal (S-VI DE O)

INPUT 3 terminal (VIDE O)

INPUT 3 terminals (AUD IO L/R )

INPUT 1 terminal (S-VI DE O)

INPUT 1 terminal

(VIDEO)

INPUT 1 terminals

(AUDIO L/R)

INPUT 2 terminal (S-VI DE O)

INPUT 2 terminal (VIDE O)

INPUT 2 terminals

(AUDIO L/R)

How to open the door.

STANDBY/ON indicator

* If the AVC System is switched on but it does not appear to be operating correctly, it may need resetting. In this

case, press CLEAR, shown in the diagram, lightly with the end of a ballpoint pen or other pointed object.

This will reset the System as shown below.

• AV MO DE reset s to USE R

• TV channel returns to initial channel setting (Air:2ch, Cable:1 or 2ch)

• Twin pi ct ure resets to no rmal

• Audio setting initializes

• Dolby virtual resets to Off

• Image position initializes

NOTE

• Pressing CLEAR will not work if the System is in standby mode (indicator lights red).

• Pressing CLEAR will not delete channel preset or secret number. See page 61 for clearing the secret number when you

know it.

See page

for initializing to the factory preset values when you forget your secret number.

Headphone

(When connecting headphones, the sound from the

speakers is muted.)

DC OUTPUT terminal

(Terminal for expanded functionality in

the near future.)

MONITOR OUTPUT

terminal (VIDEO)

DISPLAY OUTPUT 3 terminal

EXTERN

AL SPEAKER terminals

OPERATION MANUAL

6

Page 7

LC-37HV6U

Part names

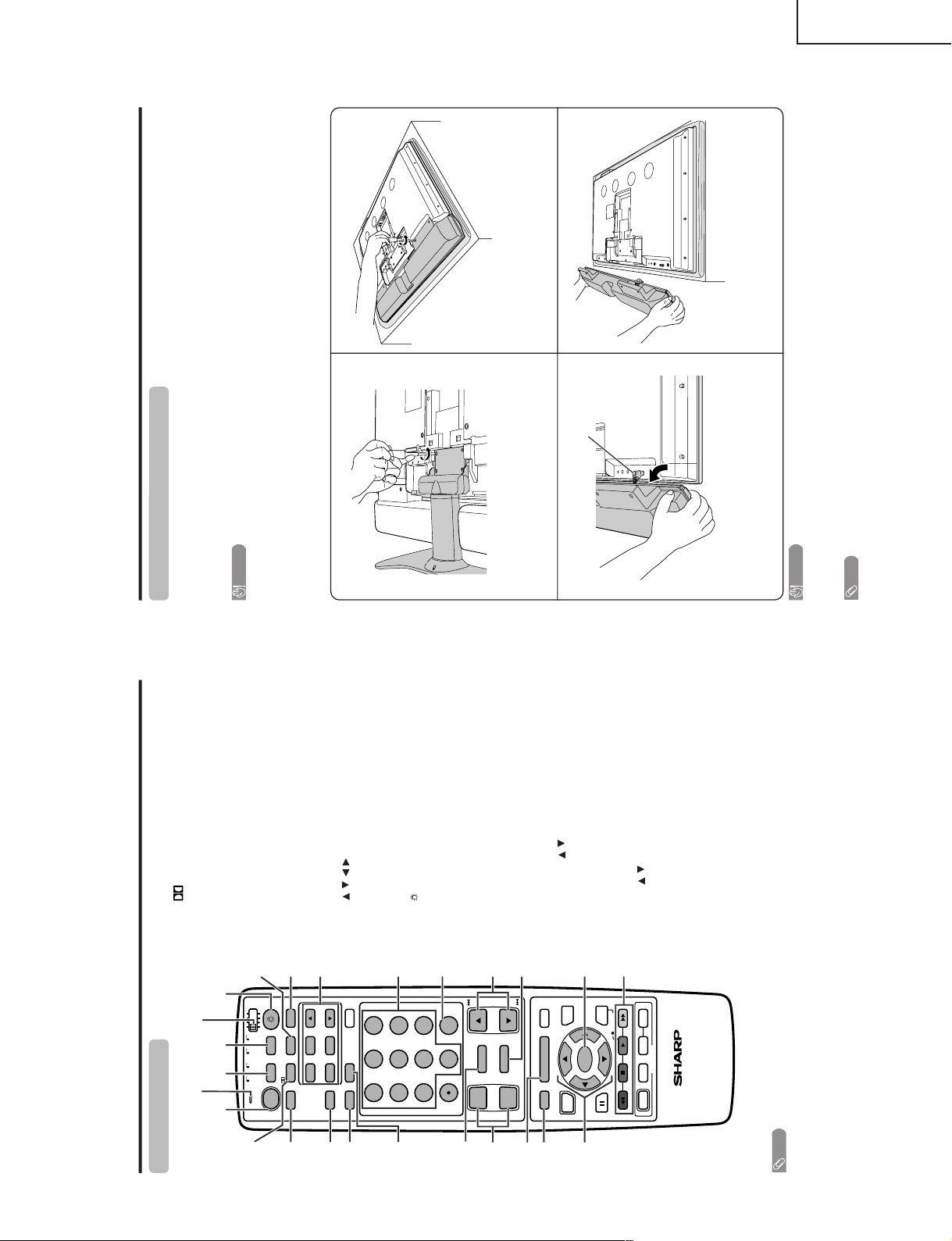

Remote control unit

NOTE

• When using the remote control unit, po in t it at th e Li qu id

Crystal Television.

• See pages for operating buttons not listed on this page.

TV

ANT-A/B

INPUT

Virtual

TWIN

MODE

AV

POWER

MTS CC

PICTURE

SELECT

SUB TWIN CH

+

—

FREEZE

MODE

VOL CH

MUTE

MENU TV/SAT/DVD

FAVORITE CH

RECEIVER

DTV/DVD TOP

SOURCE DTV/SAT

DTV/SAT

VCR REC

ABCD

RETURN

MENU

POWER

SET/

ENTER

MENU

GUIDE

INPUT VOL— VOL+

INFO

VIEW

SLEEP

LEARN

EDIT/

ENT

FLASHBACK

DISPLAY

INPUT

TV VCRCBL

/SAT

/DTV

DVD

/LD

123

456

789

100

0

POWER

16

17

18

19

20

21

22

24 25

23

3

2

1

4

5

6

7

8

9

10

11

12 13

14

15

1TVPOWER: Switch the Liquid Crystal Television power

on or off.

2

Virtual*: Select the Dolby virtual settings.

3 AV MODE: Select an audio or video setting.(AV mode:

DYNAMIC (Fixed), DYNAMIC,STANDARD, MOVIE,

GAME, USER. PC mode: STANDARD, USER.)

4 VIEW MODE: Select the screen si ze.

5DISPLAY: Display the channel information.

6SLEEP: Set the sleep timer.

7 FLASHBACK: Re tur n to th e prev ious chan ne l or inpu t

external mode.

8 VOL

+

/

–

: Set the volume.

9 MENU: Display the menu screen.

10 MENU RETURN: Return to the previous menu screen.

11

/

/

/

: Select a desired item on the screen.

12 ANT-A/B: Select between ANT-A and B to watch

broadcasts via the two tuners.

13 INPUT: Select a Liquid Crystal Television input source.

(TV, INPUT 1, INPUT 2, INPUT 3, INPUT 4, PC)

14

: When pressed all buttons on the remote contr ol unit

will light. The li ghting will tu rn off if no op erations are

performed within about 5 seconds. This button is used

for performing operations in dark places.

15 MTS: Sel ec t th e MT S/ SA P.

16 CC: Display captions during closed-caption source.

17 TWIN CH buttons

TWIN PICTURE: Set the twin picture mode.

Press again to return to no r ma l sc reen .

FREEZE: Set th

e still image. Press agai n to return to

normal screen.

SELECT: Select the active screen.

SUB INPU

T:

Select

an input source of sub screen.

TWIN CH

/

: Sel

ect the channel of sub screen.

18

0

– 9: Se

t the channel.

19 100 ENT: Select the three digit mode. Execute a

command of the channel.

20 CH

/

: Select the channel.

21 MUTE: Mute the sound.

22 SET/ENTER:

Execute a c

ommand.

23 FAVORITE CH

A, B, C, D: Select four preset favo ri te ch anne ls in fo ur

different categories.

When view

ing via ANT-A: up to 16 channe ls can be

assigned in A, B, C and D.

When viewing via ANT-B: up to 16 channels can be

assigned i

n A, B, C and D.

With AN

T-A and B combined, you ca n preset up to 32

favorite channels in advance.

While watching, you ca n to ggle the se le ct ed ch anne ls

by press

ing A, B, C and D.

24 LED for transmission confirmation

25 Mode switch

* VIRTUAL DOLBY SURROUND

Manufactured under license from Dolby

Laboratories."Dolby","Pro Logic" and the double-

D symbol are trademarks of Dolby Laboratories.

Preparation

Removing the stand and speaker

This unit has detachable type speaker.

You can detach the system speaker when using external amplifier/speaker.

Before detaching (or attaching) speaker, unplug the AC cord from the AC outlet and the system cable from the

Display.

CAUTION

• When using the TV with the supplied stand attached, do not remove the speaker. Doing so may disturb

the balance leading to product damage or personal injury.

Before attaching/detaching speaker

• Before performing work make sure to turn off the System.

• Before performing work spread cushioning over the base area to lay the Display on. This will prevent it from

being damaged.

CAUTION

• The speaker terminals on the Display are only for the attached speaker. Do not connect any third party plug or speaker

to the terminal.

• Insert the speaker plug completely into the terminal.

NOTE

• To attach the spe ak er, perform the ab ov e st ep s in rever se order.

2

34

Unfasten the screws used to secure the speaker in

place.

Take hold of the speaker and slowly slide it

sideways.

(The speaker plugs are still inser ted, so make

sure not to pull the speaker too far.)

Remove the speaker plugs from the terminal on the

Display.

(Do not remove the plugs by pulling the cord.)

Now the speaker can be detached from the Display .

Speaker plug

1

Unfasten the screws used to sec ure the sta nd

in place, and then detach the stand from the

Display.

(Hold the stand so it will not drop the stand from

the edge of the base area.)

7

Page 8

LC-37HV6U

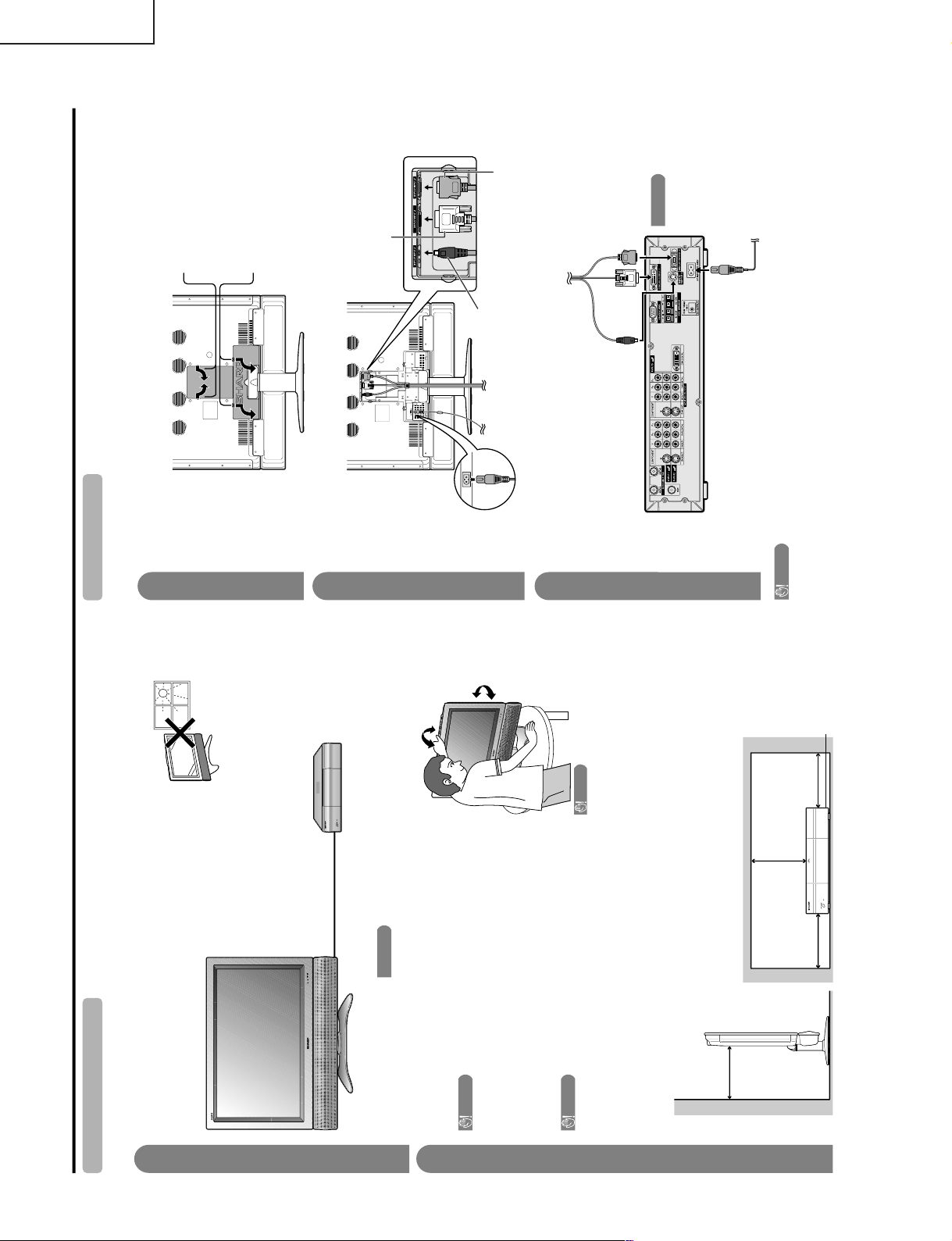

Setting the System in place

Handling the Display

CAUTION

• The Display is very heavy. Move it with two or more people.

• Do not remove the stand from the Display unless using an

optional bracket to mount it.

• Keep enough space above and behind the Display.

Handling the AVC System

CAUTION

• Do not put a VCR or other device on the AVC System.

• Keep enough space above and on the sides of the AVC System.

• Do not block the ventilation openings on the top and left side,

and the exhaust fan on the right side.

• Do not spr

ead a thick cloth beneath the AVC System, or cover it

with one, as this can cause overheating and result in

malfunction.

Where to place the System

"System" means the Display and AVC System. First select the location where to place the System.

Selecting the location of the System

• Select a place with no direct sunlight and good ventilation.

• The Display and the AVC System are connected by the system cable.

Keep enough space

System cable

AVC System

Display

There is an

exhaust fan on

the right side.

1

2

4 inches

(10 cm)

or more

2 inches

(5 cm) or more

2 inches

(5 cm) or

more

Preparation

If you want to keep a longer distance between the Display and A

VC

System, please pur

chase the optional system cable AN-07SC1

(about 23 feet/7 meters).

IMPORTANT

• You cannot use external speakers when you are using the optional system

cable (AN-07SC1).

2 inches

(5 cm) or

more

CAUTION

Adjust the scre en wi th both

hands. Put one ha nd on the

Display and tilt th e screen

while steadying th e stan d

with your other hand .

You can adjust the sc reen

vertically up to 4 de grees

forward or 6 degree s back-

ward, or rotate 10 de grees

horizontally.

System cable

AVC System (rear view)

AC cord

Display (rear view)

Setting the System

After putting the Display and the AVC System in place, connect the system cables and AC cords. Use the

cable clamps for bundling the cables.

Connecting the system cable and the AC cord to the Display

1

2

3

Removing the terminal cover

Connecting the system cable and the AC cord to the AVC System

CAUTION

• TO PREVENT RISK OF ELECTR IC SHOC K, DO NOT TOUCH UN-INSULATED PARTS OF ANY CABLES WITH THE

AC CORD CONNECTED.

Press down the two

upper hooks to remove

the cover toward you.

Press the two hooks

toward the center of the

Display and remove the

cover toward you.

AC cord

(GLAY)

Connect the plug firmly until the

hooks on both sides clic k.

(WHITE)

Connect the plug into th e te rminal

and secure it by tightening the

thumb screws.

(BLACK)

(BLACK) (WHITE) (GLAY)

You cannot use external

speakers when you are using

the optional system cable

(AN-07SC1).

IMPORTANT

System cable

8

Page 9

LC-37HV6U

Preparation

4

5

Attaching the clamps and bundling the cables with the clamp

Closing the terminal cover

Cable clamp (Large)

Insert the cable

clamp in the hole

on the Display leg

as shown.

Cable clamp (Small)

Peel off the seal

on the back and

attach as shown.

Display (rear view)

Cables come

out from the

small opening.

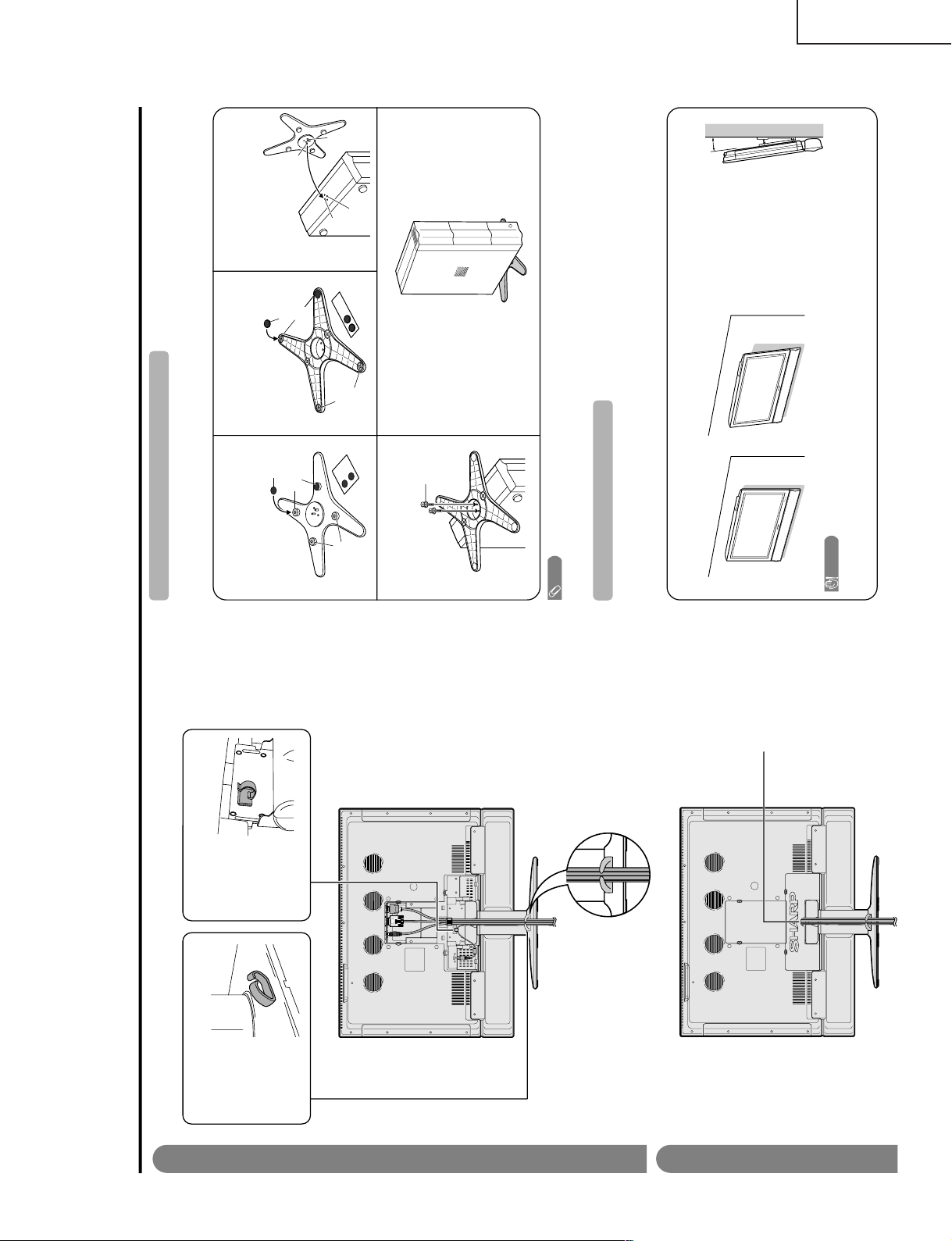

Setting the Display on the wall

CAUTION

• Installing the Liqu id Crystal T elevisio n requires spec ial skill that should only be performed by qualifie d service personnel.

Customers should no t attemp t to do th e work th emse lves. SH ARP be ars no respons ibil ity for im proper mo unti ng or

mounting that results in acc id en t or inj ury.

Using an optional brac

ket to mount the Display

• You can ask a qualified service personnel about using an optional AN-37AG1 bracket to mount the Display

to the wall.

• Carefully read the instructions that come with the bracket before beginning work.

Vertical mounting Angular mounting

Hanging on the wall

AN-37AG1 wall mount bracket. (See the bracket instructions for details.)

Setting the AVC System with the stand

1

How to install the A

VC System vertically using the stand unit.

• Use the supplied stand unit for installing the AVC System vertically in an upright position.

Stick each spacer to the

stand as shown.

Peel each spacer

away from the

paper and attach

to the four bulging

areas on the stand.

2

Attach each cushion to

the stand as shown.

3

Fit the stand to the AVC

System.

Peel each cushion

away from the

paper and attach

to the four areas at

the bottom.

Insert the stand in to the AVC

System, making sure that the

thick and thin bulge s of the

stand align with the big and

small holes on the AVC

System.

Stand

spacer

Bulge

Stand cushion

Thin bulge

Thick

bulge

Big hole

Small

hole

4

Attach the stand using the

stand screws as shown.

Stand screw

The AVC System installed

vertically with the stand.

NOTE

• When mounting the AVC System vertically, always use th e supp lied stan d. Be ca reful no t to bl ock vent ho les wh en

st

anding up directly on the floor or a flat surface as this can result in equipment failure.

Attaching point

Attaching point

Bulge

5°

About setting the Disp lay ang le

• You can set the Display on the

wa

ll up to 5 degrees forward

when the speaker is attached and

up to 20 degrees forward when

the speaker is not attached. Do

not set the angle outs id e th os e

ranges.

9

Page 10

LC-37HV6U

Using external equipment

Digital TV tuner

AVC System

(rear view)

AVC System

(front view)

AV Receiver

(Built-in Tuner Amp)VCR

DVD player

Game console/

Camcorder

PC

You can connect many types of external equipment to your System, like a DVD player, VCR, Digital TV tuner, PC,

game console and camcorder. To view external source images , select the input source from INPUT on the

remote control unit or on the Display.

CAUTION

• To protect all equipment, always turn off the AVC System before connecting to a DVD player, VCR, Digital TV tuner,

PC, game console, camc orde r or oth er ext ernal equipment.

NOTE

• Please refer to the relevant operation manual (DVD player, PC, etc.) carefully before making connections.

S-VIDEO

S-VIDEO

S-VIDEO

AV

S-VIDEO

AV

AV

AV

Y/P

B

/P

R

Y/P

B

/P

R

PC-AUDIO

ANALOG RGB

AV

S-VIDEO

DVI

Rear view

Useful adjustment settings

Connecting external speakers

When using external speakers

• Change the speaker setting to exter nal speakers.

Make sure to connect the speaker terminal and

cable polarity (

+

, –) properly

•

The speaker terminals have plus (

+

) and minus (

–

)

polarity.

• Plus is red and minus is black.

• The cables are also divided into plus and mi nu s.

• When connecting the left/right speakers, be sure to

connect the plus/minus terminals with the correct cables.

NOT

E

• Unplug the AC cord from the AC outlet be fore instal ling

the speakers.

CAUTION

• Make sure external speakers have 4 ohm and 10 watt

specifications.

• Connect the plus/minus terminals with the correct cables.

Incorrect connection ma y ca us e a sh ort.

How to connect the

speaker cable

Push down

the tab.

Insert the

end of the

cable.

1

2

3

Lift the tab

back up.

10

Page 11

Basic adjustment settings

AV input mode menu items

List of AV menu items to help you with

operations

OPC

Backlight

Contrast

Black Level

Color

Tint

Sharpness

Advanced

C.M.S.

Color Temp

Black

3D-Y/C

Monochrome

Film Mode

I/P Setting

Picture

No Signal Off

No Operation Off

EZ Setup

CH Set

up

Speaker

Input Signal

Parental CTRL

Position

Picture Flip

Language

Treble

Bass

Balance

Dolby Virtual

Audio Only

Input Select

DNR

Audio Out

Quick Shoot

Audio

Power control

Setup

Option

PC input mode menu items

List of PC menu items to help you with

operations

OPC

Backlight

Contrast

Black Level

Red

Green

Blue

C.M.S.

Picture

Power Management

Input Signal

Speaker

Auto Sync.

Fine Sync.

Picture Flip

Language

Audio

Power control

Setup

Treble

Bass

Balance

Dolby Virtual

Option

Audio Only

Audio Out

Quick Shoot

Appendix

PC compatibility chart

Apple and Macintosh are registered tradem arks

of Apple Computer, Inc.

DDC is a registered trademark of V ideo Electronics

Standards Association.

Power Management is a registered trademark of

Sun Microsystems, Inc.

VGA and XGA are registered trademarks of

International Business Mac hin es Co. , Inc.

PC/MAC Resolution

Horizontal Frequency

Vertical Frequency

VESA Standard

PC

31.5 kHz

37.9 kHz

31.5 kHz

37.9 kHz

31.5 kHz

37.9 kHz

37.5 kHz

43.3 kHz

31.5 kHz

35.1 kHz

37.9 kHz

48.1 kHz

46.9 kHz

53.7 kHz

48.4 kHz

56.5 kHz

60.0 kHz

68.7 kHz

45.0 kHz

48.1 kHz

64.0 kHz

34.9 kHz

49.7 kHz

60.2 kHz

640 x 400

720 x 400

VGA

640 x 480

WVGA 848 x 480

SVGA

800 x 600

1024 x 768XGA

1280 x 720

WXGA

1280 x 768

SXGA

1280 x 1024

VGA

640 x 480

MAC13"

XGA

1024 x 768

MAC19"

SVGA

832 x 624

MAC16"

60 Hz

85 Hz

60 Hz

85 Hz

60 Hz

72 Hz

75 Hz

85 Hz

60 Hz

56 Hz

60 Hz

72 Hz

75 Hz

85 Hz

60 Hz

70 Hz

75 Hz

85 Hz

60 Hz

60 Hz

60 Hz

67 Hz

75 Hz

75 Hz

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

LC-37HV6U

11

Page 12

LC-37HV6U

Command table

• About the command except being indicated here, it is outside the guarantee range of operation.

CONTROL ITEM COMMAND

PARAMETER

CONTROL CONTENTS

POWER SETTING It shifts to standby.

It input-switches by the toggle. (It is the same as an input change key)

It input-switches to TV. (A channel remains as it is. (Last memory))

It input-switches to INPUT1~INPUT4.

It input-switches to PC.

An input change is also included.

Although it can choose now, it is toggle operation in inside.

Although it can choose now, it is toggle operation in inside.

(Toggle)

Input terminal number (1–4)

AUTO

AV-Y/C

COMPONENT

AUTO

AV-Y/C

COMPONENT

DVI

(Toggle)

STANDARD

DYNAMIC

MOVIE

DYNAMIC (Fixed)

GAME

USER

Volume (0–60)

AV mode. ( ± 10)

PC mode. (± 90)

AV mode. (± 30)

PC mode. (± 60)

Only PC mode. (± 90)

Only PC mode. (± 20)

(Toggle) [AV]

Toggle operation.

An input change is included if it is not TV display.

In Air, 2–69ch is effective.

In Cable, 1–125ch is effective.

If it is not TV display, it will input-switch to TV.

If it is not TV display, it will input-switch to TV.

Change toggle operation of tuner A/B.

Toggle operation of a closed caption.

(Toggle)

Side Bar [AV]

S.Stretch [AV]

Zoom [AV]

Stretch [AV]

Normal [PC]

Stretch [PC]

Dot by Dot [PC]

Zoom [PC]

(Toggle)

Off

SRS

FOCUS

FOCUS

+

SRS

One screen

Twin screens

The channel number of TV

The channel number of TV + 1

The channel number of TV —1

(Toggle)

(Toggle)

OFF

CC1

CC2

T1

T2

(1~125)

AUTO

POWR

ITGD

ITVD

IAVD

IPCD

INP1

INP3

INPUT SELECTION A TOGGLE

INPUT SELECTION B

AV MODE SELECTION

VOLUME

POSITION

VIEWMODE

SRS

TWIN PICTURE

CHANNEL

ANT-A/B

CC

DIRECT

CH UP

CH DOWN

CHANNEL

H-POSITIONH-POSITION

V-POSITION

CLOCK

PHASE

INPUT 1

INPUT 3

AVMD

VOLM

HPOS

VPO

S

CLCK

PHSE

SRSS

TWI

N

DCCH

CHUP

CHDW

ANTS

CLCP

WI

DE

0

x

0

*

x

0

0

1

2

3

1

2

0

*

*

*

*

*

0

0

*

x

x

x

0

1

2

3

4

5

1

1

2

3

4

0

1

2

3

4

5

6

7

8

*

*

1

2

3

4

5

6

*

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

*

*

*

*

*

*

*

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

*

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

*

*

*

*

*

*

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

TV

INPUT1-4

PC

NOTE

• If an underbar (_) appears in the parame te r co lu mn , en te r a sp ac e.

• If an asterisk (*) appears, enter a value in the range indicated in brackets under CONTROL CONTENTS.

• As long as that from which the parameter ( × ) in the table is a numerical value, it may write anything.

Return code (0DH)

Response code format

Normal response

Problem response (communication error or incorrect command)

Return code (0DH)

OK

ERR

RS-232C port specifications

Return codeCommand 4-digits Parameter 4-

digits

PC Control of the System

• When a program is set, the Display can be controlled from the PC using the RS-232C terminal.

The input signal (PC/AV) can be selected, the volume can be adjusted and various other adjust ments and

settings can be made, enabling automatic programmed playing.

•

Attach an RS-232C cable cross- type (commercially available) to the supplied Din/D-Sub RS- 232C for the

connections.

NOTE

• This operation system should be used by a person who is accustomed to using computers.

Communication conditions

Set the RS-232C communications settings on the PC to match the display’s communications conditions.

The Display’s communications settings are as follows:

Baud rate:

Parity bit:

Data length:

Stop bit:

Flow control:

9,600 bps

8 bits

None

1 bit

None

Appendix

Comman

d format

Communication procedure

Send the control commands from the PC via the RS-232C connector.

The display operates according to the received command and sends a response message to the PC.

Do not send multiple commands at the same time. Wait until the PC receives the OK response before sending

the next command.

Eight ASCII codes + CR

Comm

and 4-digits:Comma nd. Th e text of four charac ters .

Parameter 4-digits :Par am eter 0 – 9, x, bl an k, ?

Parameter

Input the parameter va lu es , al ig ni ng lef t, and fil l wi th bla nk (s ) fo r th e remai nd er. (Be sure that 4 values are in pu t for the

parame

ter.)

When the i

nput parameter is not within an adjustable range, "ERR" returns. (Refer to "Response code format".)

No problem to input any numerical value for "x" on the table.

When "?" is input for some commands, the present setting value responds.

C1 C2 C3 C4 P1 P2 P3 P4

0055

100

–

30

0009

0

????

?

12

Page 13

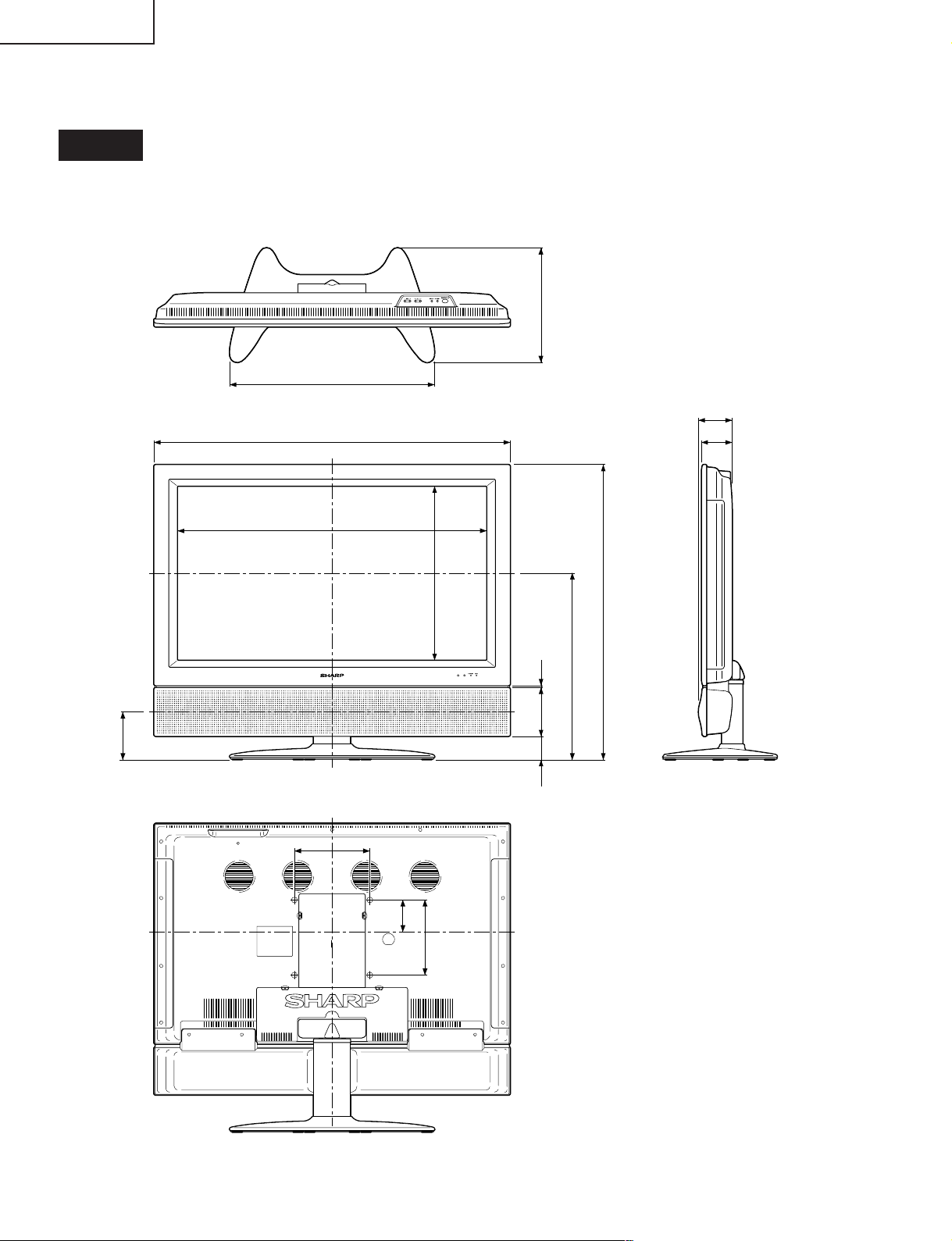

DIMENSIONS

LC-37HV6U

AVC System

1423/64(365)

59

/64(430)

16

(95)

64

/

47

3

927/32(250)713/64(183)

75/64(180)

Unit: inch/(mm)

(5)

16

/

3

13

Page 14

LC-37HV6U

Display

Unit: inch/(mm)

12 (305)

29

21

/

64

(545)

35

3

/

64

(90)

7

3

/

21

37

/

64

(948)

11

32

/

32

(821.6)

(82)

32

5(127)

(495.5)

2

/

1

19

(784)

64

/

55

30

(462.8)

32

/

7

18

(5)

16

/

3

(130)

64

/

7

16

/

7

(62) 5

2

7

7

/

8

(200)

32

/

11

(85)

3

(200)

8

/

7

7

14

Page 15

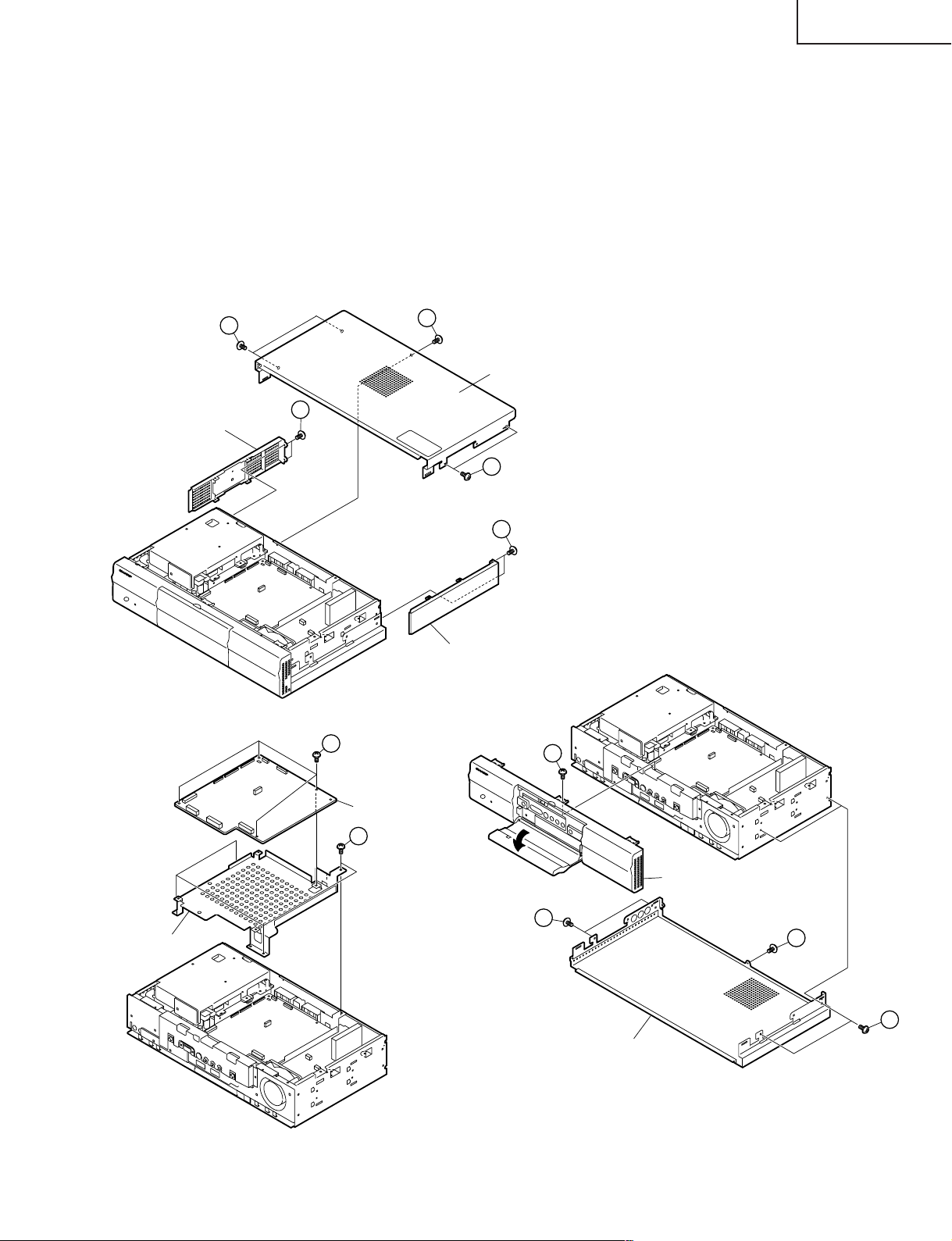

REMOVING OF MAJOR PARTS

Ë Ë

Ë AVC System

Ë Ë

1. Remove the five top cabinet retaining screws and slide the top cabinet backward to remove it.

2. Remove the four side cover retaining screws on both the right and left sides and slide the side covers

backward to remove them.

3. Remove the one front panel retaining screws and remove the front panel.

4. Remove the five bottom cabinet retaining screws and slide the bottom panel backward to remove it.

5. Remove the four screws securing the main PWB angle and remove the angle upward.

6. Remove the four screws securing the main PWB to the angle and remove the main PWB.

LC-37HV6U

1

Side Cover (L)

1

Top Cabinet

2

1

2

Side Cover (R)

6

3

Main PWB Angle

Main PWB

5

Front Panel

4

4

4

Bottom Panel

15

Page 16

LC-37HV6U

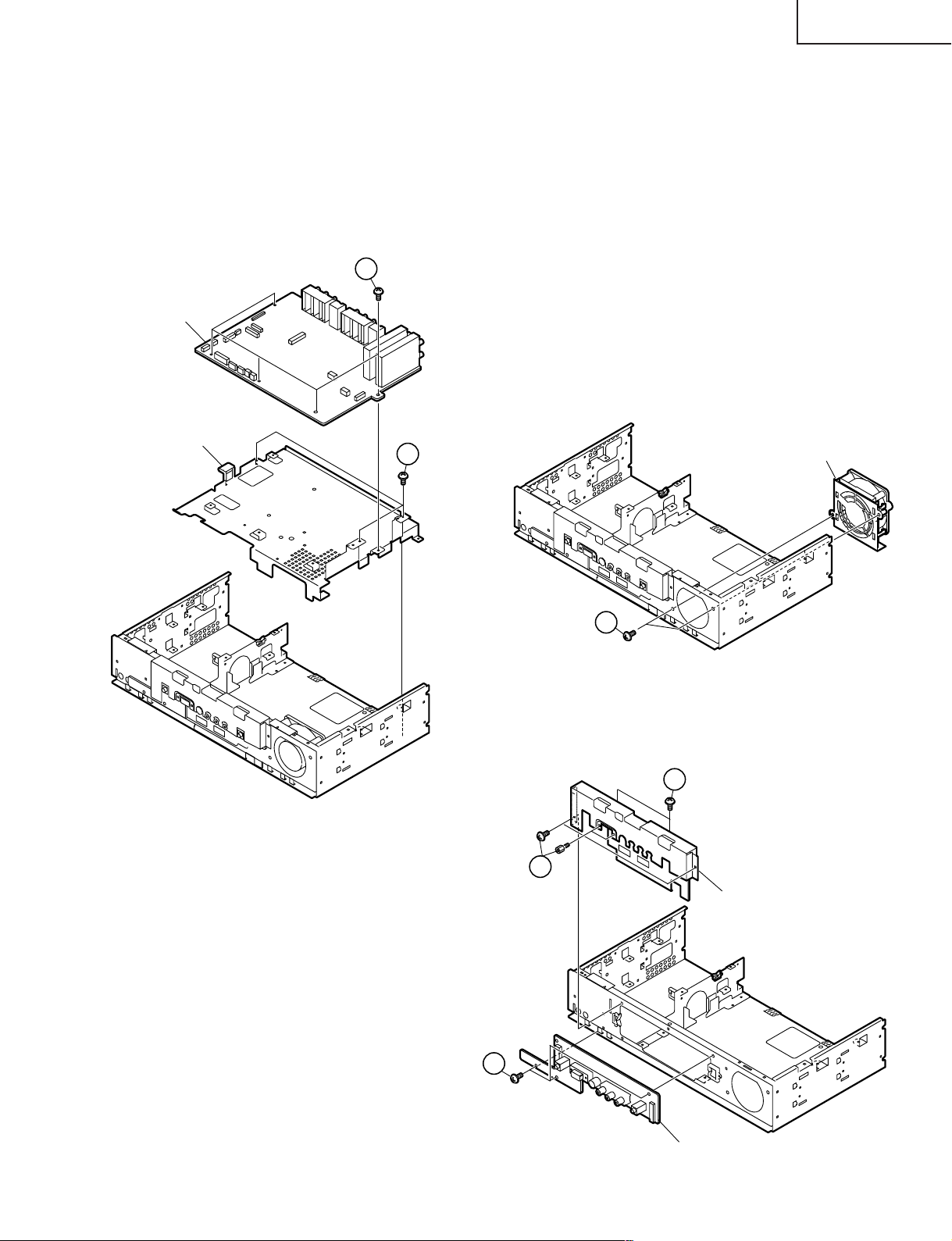

7. Remove the system/control terminal retaining:

7-1. Remove the four hex head screws securing the terminals of the system and control cables (white).

7-2. Remove the four screws securing the terminal of the system cable (gray).

7-3. Remove the four rear chassis retaining screws.

8. Remove the PC I/F and Audio I/F units:

8-1. Remove the five PC I/F top shield retaining screws and remove the shield.

8-2. Remove the six PC I/F unit retaining screws and remove the unit.

8-3. Remove the two PC I/F bottom angle retaining screws and remove the angle.

8-4. Remove the two Audio I/F unit retaining screws and remove the Audio I/F unit.

9. Remove the rear chassis.

9-1. Remove the three tuner nuts.

9-2. Remove the 13 rear cabinet retaining screws and remove the rear cabinet.

10. Remove the three power unit retaining screws and remove the power unit.

8-1

8-2

PC I/F Top Shield

PC I/F unit

Audio I/F unit

8-4

8-3

PC I/F Bottom Angle

7-1

7-3

7-2

Rear Cabinet

10

9-2

9-2

9-2

Power Unit

9-2

9-1

9-2

16

Page 17

11. Remove the AV unit:

Cooling Fan

12-1

11-1. Remove the five AV unit retaining screws and remove the AV unit.

11-2. Remove the three AV unit angle retaining screws and remove the angle.

12. Remove the fan:

12-1. Remove the two cooling fan retaining screws and remove the cooling fan.

13. Remove unit from the front chassis:

13-1. Remove the two hex head screws and four screws securing the front shield to the front chassis and

remove the front shield.

13-2. Remove the four screws securing the front unit and remove the unit.

11-1

AV Unit

AV Unit Angle

11-2

LC-37HV6U

13-1

13-1

Front Shield

13-2

Front Unit

17

Page 18

LC-37HV6U

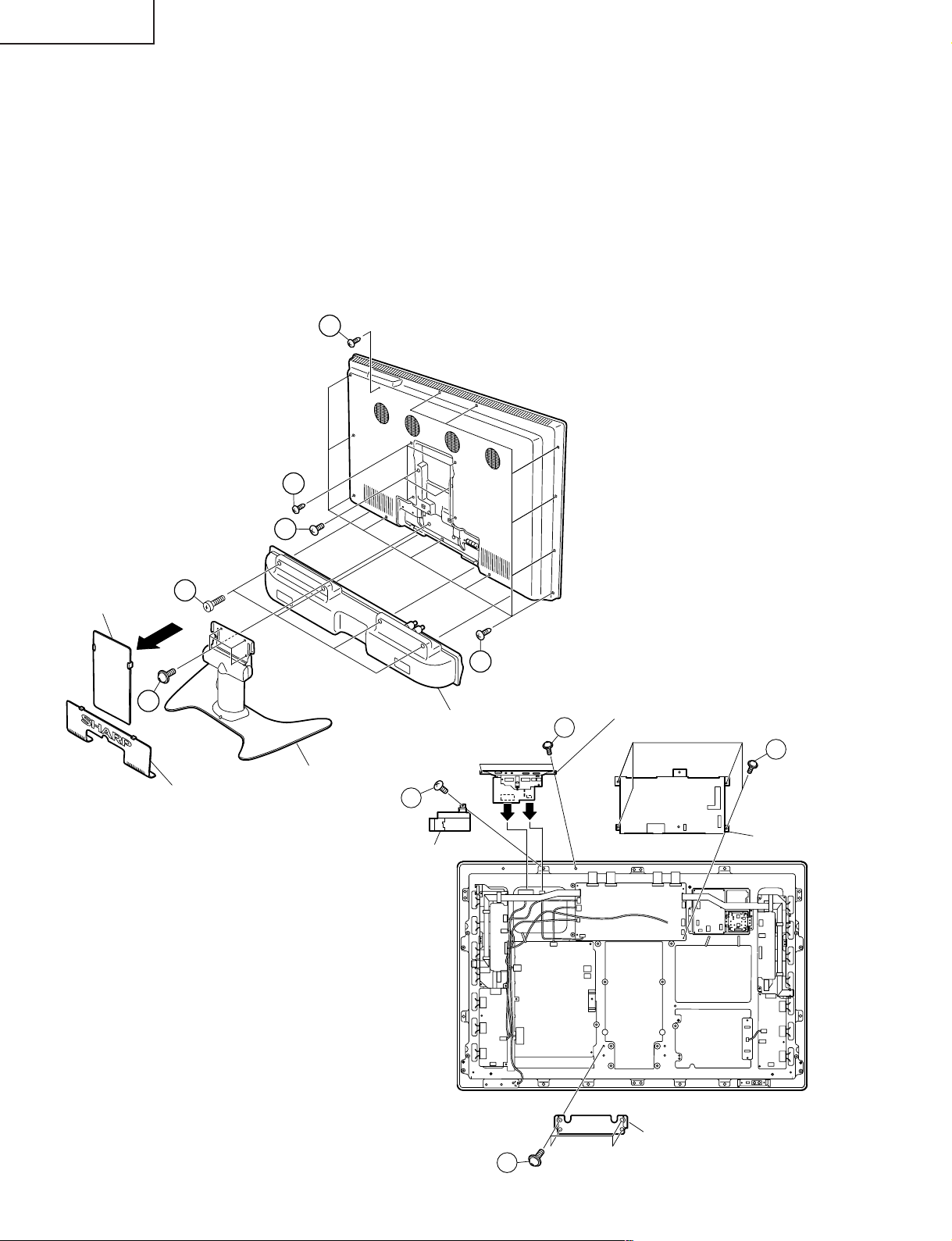

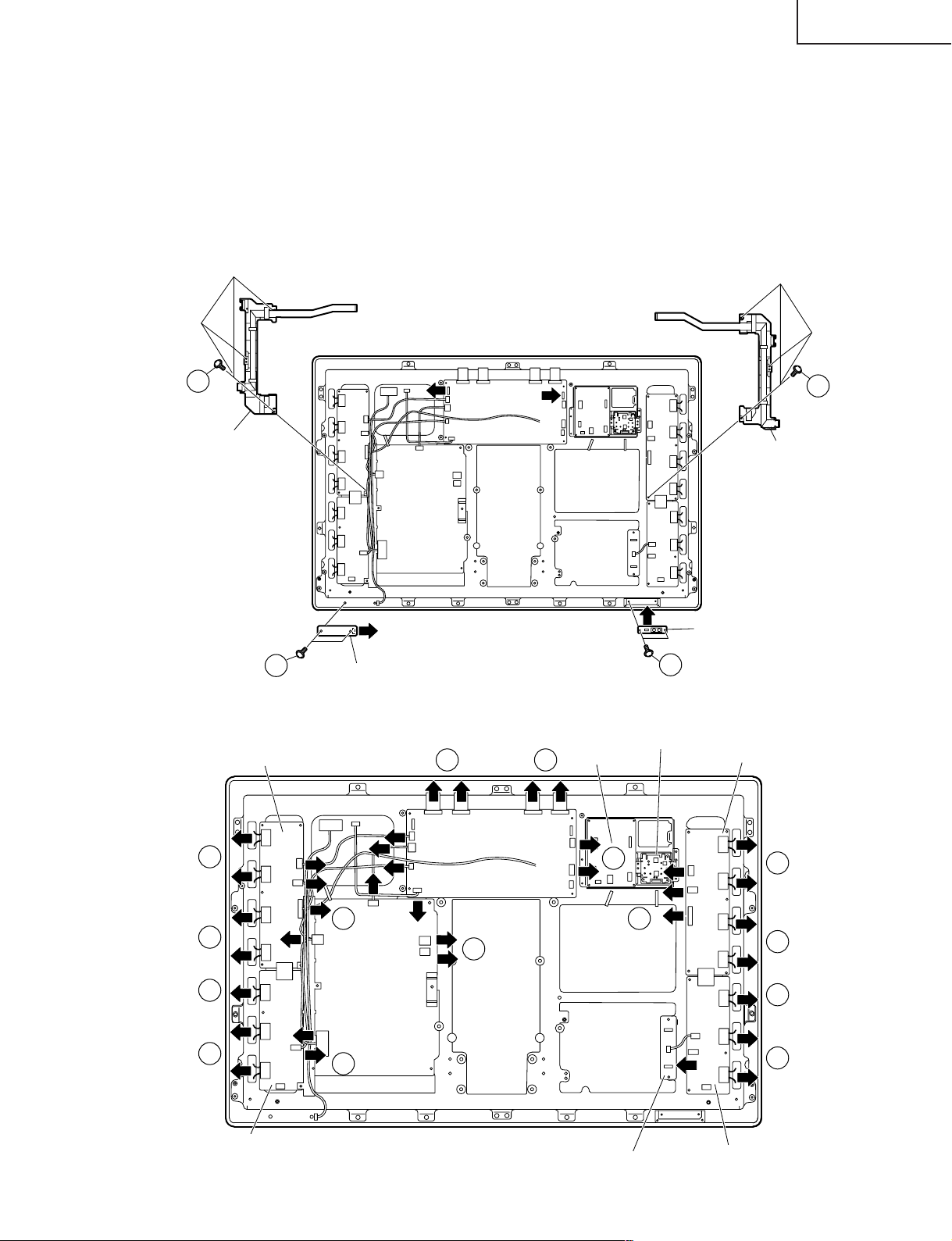

Ë Ë

Ë Display

Ë Ë

1. Remove the top and bottom terminal covers.

2. Remove the four lock screws from the speaker. Disconnect the speaker terminals and detach the speaker.

3. Remove the four lock screws from the stand, and detach the stand.

4. Remove the 18 lock screws from the cabinets A and B, and remove the cabinet B.

5. Remove the two lock screws from the operation PWB assembly, and detach the operation PWB assembly.

6. Remo v e the lock screw from the operation PWB insulating sheet, and detach the operation PWB insulating sheet.

7. Remove the seven lock screws from the main PWB shield, and detach the main PWB shield.

8. Remove the four lock screws from the stand fixture, and detach the stand fixture.

4

Terminal Cover (Top)

3

Terminal Cover (Bottom)

4

4

2

1

4

Speaker

Stand

6

Operation PWB Insulating Sheet

P152

5

P151

Operation PWB Assembly

7

Main PWB Shield

18

Stand Fixture

8

Page 19

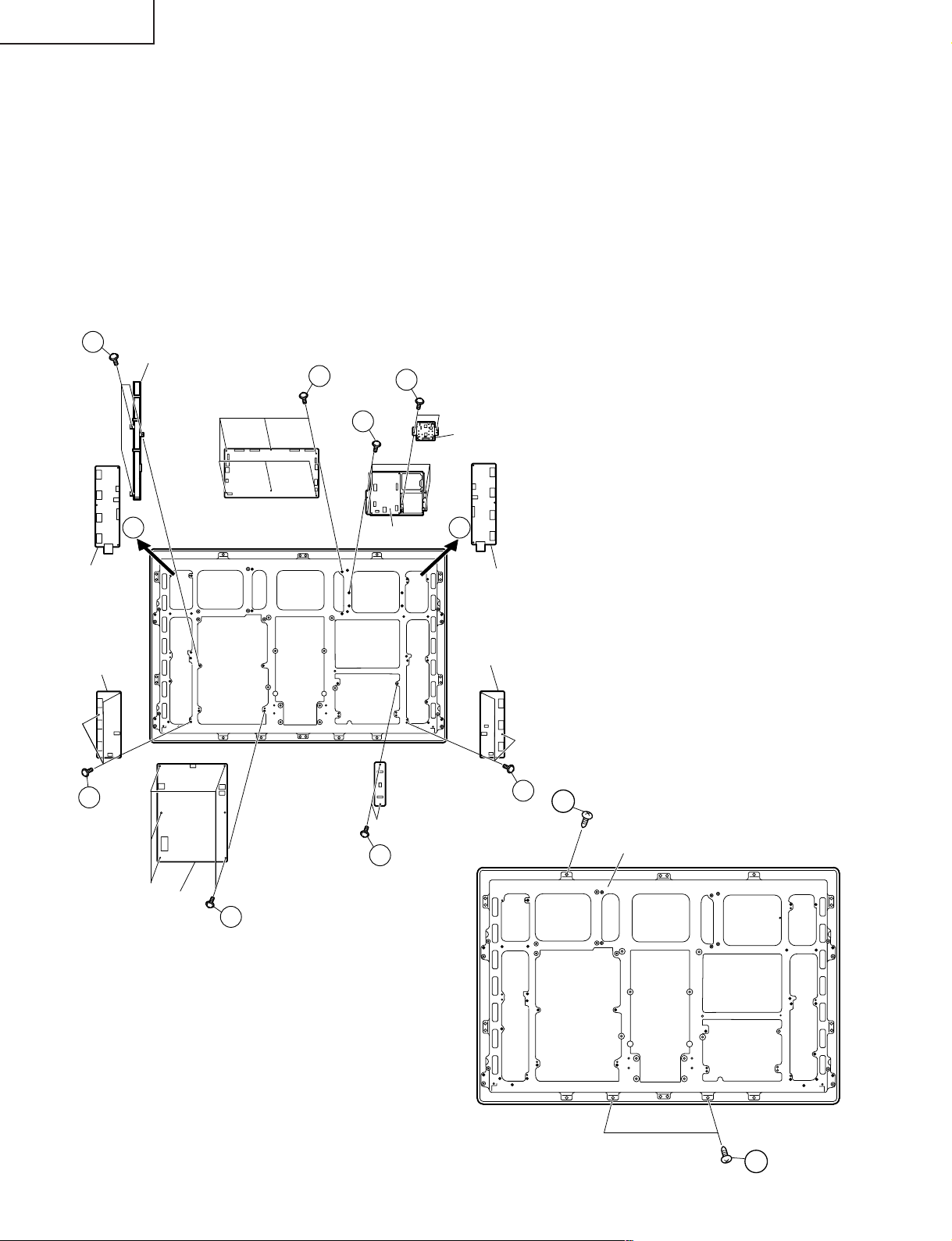

LC-37HV6U

FFC Holder (Left)

FFC Holder (Right)

Cable Holder

Cable Holder

Speaker Jack PWB

R/C, LED PWB

P101

CN4101

CN4102

9

11

10

9

9. Open the six FFC holders. Remo ve the three lock screws from each of the right and left FFC holders. Disconnect

all the FFC connectors and detach the right and left FFC holders.

10.Remove the two lock screws from the speaker jack PWB, disconnect the connector, and detach the speaker jack

PWB.

11.Remove the two lock screws from the R/C, LED PWB, and detach the R/C, LED PWB.

12.Disconnect the connectors from each PWB. (13 from the monitor PWB, 5 from the power PWB, 6 from the audio

PWB, 7 from the inv erter-1 PWB, 5 from the inverter-2 PWB, 7 from the inv erter-3 PWB, 6 from the inv erter-4 PWB,

2 from the 1-Bit amplifier unit, and 1 from the thermistor PWB)

1-Bit Amplifier Unit

Inverter-1 PWB

12

P7505

P7506

P7507

12

12

CN3701

12

CN3782

CN3702

Power PWB

CN4701

CN4702

12 12

SC4601 SC4604

SC4603

CN4101

CN7004

CN2004

CN2002

Monitor PWB

12

Audio PWB

SC4602

CN7705

CN2003

12

12

12

P7554

CN2702

12

Inverter-2 PWB

Thermistor PWB

19

Inverter-3 PWB

P7616

P7619

P7618

P7647

P7644

Inverter-4 PWB

12

12

12

12

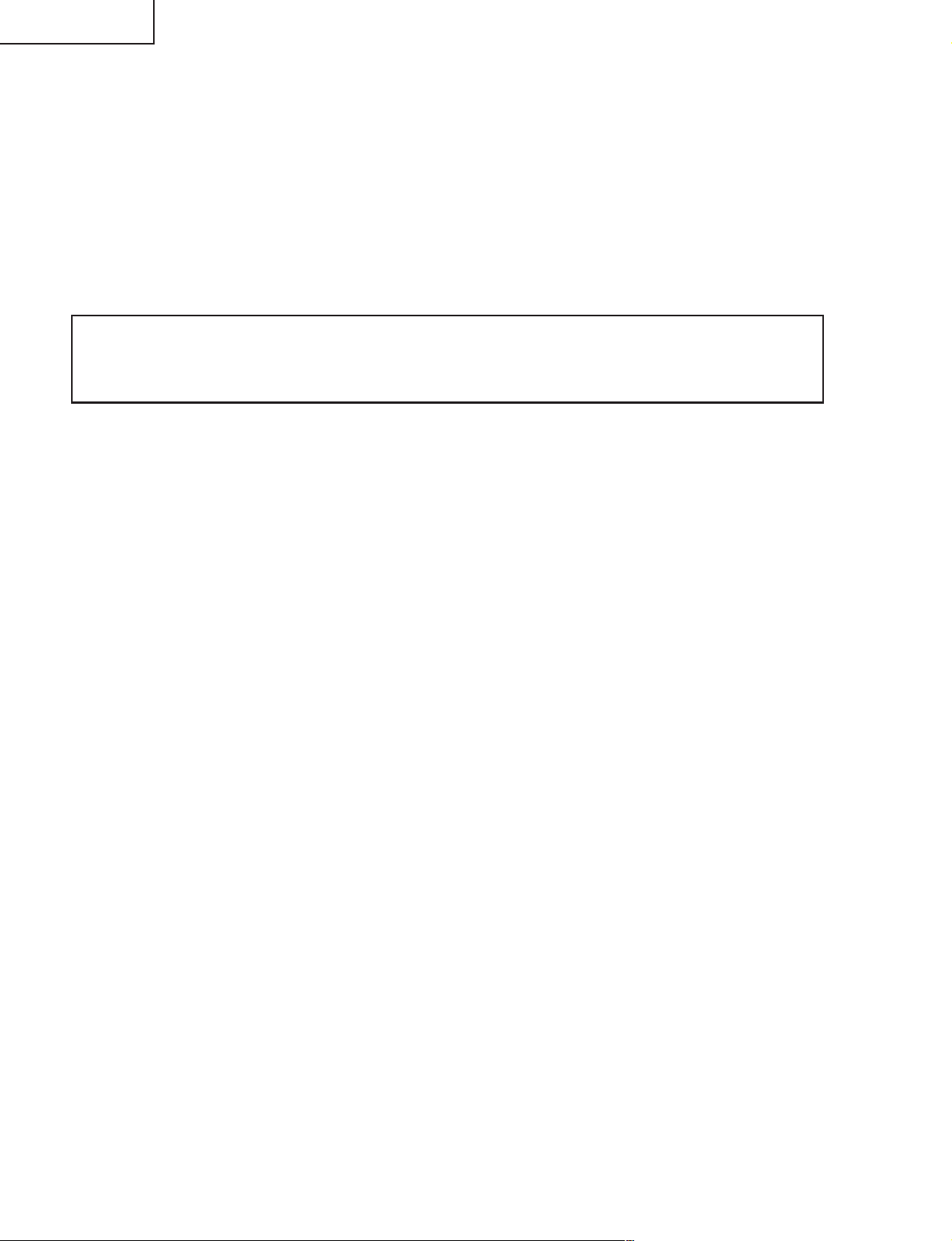

Page 20

LC-37HV6U

13. Remove the eight lock screws from the Monitor PWB, and detach the main PWB.

14. Remove the six lock screws from the power PWB, and detach the power PWB.

15. Remove the four lock screws from the audio PWB, and detach the audio PWB.

16. Remove the three lock screws from the holder, and detach the holder.

17. Detach the inverter-1 PWB.

18. Remove the three lock screws from the inverter-2 PWB, and detach the inverter-2 PWB.

19. Detach the inverter-3 PWB.

20. Remove the three lock screws from the inverter-4 PWB, and detach the inverter-4 PWB.

21. Remove the two lock screws from the thermistor PWB, and detach the thermistor PWB.

22. Remove the two lock screws from the 1-Bit amplifier unit, and detach the 1-Bit amplifier unit.

23. Remove the three lock screws from the chassis, and detach the chassis.

16

Inverter-1 PWB

Inverter-2 PWB

18

Holder

13

17 19

Monitor PWB

22

15

Audio PWB

Thermistor PWB

1-Bit Amplifier Unit

Inverter-3 PWB

Inverter-4 PWB

20

23

Power PWB

21

Chassis

14

23

20

Page 21

LC-37HV6U

• Precautions in handling the liquid crystal panel

1. Handle the liquid crystal panel in a clean room (Humidity: 50% or more).

2. Be sure to wear an earth wristband.

3. Be careful not to drop and shock the liquid crystal panel.

4. Use an ionizer (within 30 cm).

24.Remove the six lock screws from the LCD panel, and detach the LCD panel unit.

25.Remove the three lock screws from each of the sheet fixtures, and detach the sheet fixtures.

26.Detach the reflection/deflection sheet, prism sheet, diffusion sheet and diffusion panel.

27.Remove the three lock scre ws from each of the top and bottom lamp holders , and detach the top and bottom lamp

holders.

28.Detach the lamp assembly from the lamp clip.

23

23

Sheet fixture

24

Lamp Holder (Top)

Panel bracket

26

25

LCD Panel Unit (Front)

Lamp Holder (Bottom)

Lamp Unit

Diffusion Panel

27

Panel

bracket

Reflection Panel

LCD Panel Unit

24

Sheet fixture

24

24

Sheet fixture

21

26

Lamp Holder (Bottom)

Lamp Holder (Top)

Diffusion Sheet

Prism Sheet

Reflection/Deflection Sheet

Page 22

LC-37HV6U

ADJUSTMENT PROCEDURES (AVC SYSTEM)

Preparation for adjustment

1. The product has been adjusted and optimized in the factory. If the product needs to be readjusted for some

reason, e.g., after parts replacement, follow the instructions shown below.

2. Control parameter values set in the in-process adjustment mode has been stored in the corresponding registers.

When the product is readjusted, the contents of the registers are changed. Bef ore readjustment, f actory settings

should be noted in case the contents of registers require to be restored.

3. Use a stabilized AC power supply.

4. To rewrite a program, you should note the items ("OSD MENU" and "Adjustment Values") you want to change

and initialize EEPROM, and then rewrite the changes into EEPROM.

How to enter the in-process adjustment mode

CAUTION: Exercise great care to hide the procedure in entering the in-process adjustment mode from the

customer. Inadvertent setting changes in this mode may cause a fatal error resulting in a program being

unrecoverable.

1. Entering the in-process adjustment mode:

Connect the system cable between the display and AVC system.

Turn off the "MAIN POWER" button of the display once.

Turn on the main power while holding down the "INPUT" button and the "VOL (-)" button of the Display

simultaneously.

The system will be activated.

~If you see multiple lines of blue characters on the display, you are in the in-process adjustment mode. If not

(the normal activation screen opens), retry.

2. Accessing the inspection process mode:

After activation of the system, make adjustments according to the instructions indicated on the process

adjustment OSD menu screen.

Move to the General Process Adjustment (AVC System Section Process).

3. Restoring factory settings: (At the time of "INDUSTRY INIT" execution, please wait for about 30 seconds until

/// disappears.)

When the "INDUSTRY INIT" button is selected after activation of the system, factory channel setting remains

unchanged.

After the system exits from the in-process adjustment mode.

Changes made by the user will default to factory settings. Note that channel setting is also initialized.

4. Exiting from the in-process adjustment mode:

Unplug the power cable while the system is in the in-process adjustment mode to exit from the mode.

Take care not to press the "POWER" button on the remote controller or the AVC system after using factory

settings to run the system.

5. OSD menu screen and menu items during manual adjustment:

~The layout and men u items of the OSD menu screen ma y somewhat v ary depending on the program versions.

~Just rewriting a program does not cause settings to be "initial values". (Preparation for adjustment)

1. Button operation in the in-process adjustment mode

Cursor Up Move to the next page

Cursor Down Back to the previous page

Volume (+) Increase the setting by 1

Volume (-) Decrease the setting by 1

SET/ENTER Execute the function

Cursor Left Increase the setting by 10

Cursor Right Decrease the setting by 10

Channel (Up) Move the cursor up

Channel (Down) Move the cursor down

INPUT Change input (Tuner-A ->Tuner-B -> Input 1 -> Input 2 ->Input 3 -> Input 4 -> PC ->)

22

Page 23

2. In-process adjustment screen layout

Page Source of input Color system HDCP Model name

1/13 INPUT2 N358 HDCP: OFF MONITOR: LC-37HV6U

KEY WRITE ON

INDUSTRY INIT OFF

CENTER Version 1.01 (U 2003/09/12 A )

OSD Version 1.00 (J 2003/06/20 A )

CVIC Version W2002/11/27 11:33 X2002/11/27 13:53

V2002/04/19 11:26 S2002/11/27 13:49

MONITOR Version 7A.7A7A

ModelSelect MAIN 2

ModelSelect AV 4

LC-37HV6U

ModelSelect MONITOR xx

STANDBY TYPE 0

HOTEL MODE OFF

6. Loading the backup data and setting HDCP when the PC I/F unit is replaced

Nearly all data including factory settings, user settings, and channel setting is stored in the PC I/F unit.

The product comes with EEPROM (IC1506) on the Main Unit in case the PC I/F unit is replaced; original data

backed up on the EEPROM can be loaded to the new PC I/F unit.

∫ How to load the backup data

Select EEPROM RECOVER in the OSD menu (page 7) and turn the "Volume" key ON; then press "SET/

ENTER".

∫ How to set HDCP

After completion of adjustments, select KEY WRITE "ON" in the OSD menu (page 1/13) f or manual adjustment

and turn the "Volume" key ON; then press "SET/ENTER".

∫ How to read the factory settings (backup data)

Select EEPROM RECOVER (page 7), set it from "OFF" to "ON" with the "Volume" key, and then press the

"SET/ENTER" key.

∫ Adjustments required after reading the factory settings

1) Page 2

Ë +Badj3.3V Adjustment of reference voltage

Ë +Badj1.8V Adjustment of important component operating voltage (It is adjusted automatically by pressing

the "SET/ENTER" key after performing 3.3V adjustment.)

2) Page 8 to Page 10

Ë N358 WB adjustment White balance adjustment (TV, VCR, etc.)

Ë COMP 15K WB adjustment White balance adjustment (Component 480i)

Ë COMP HDTV WB adjustment White balance adjustment (Component 1080i)

23

Page 24

LC-37HV6U

1) Analog adjustment

(1) V oltage adjustment

Item Adjusting conditions/points Adjusting procedure

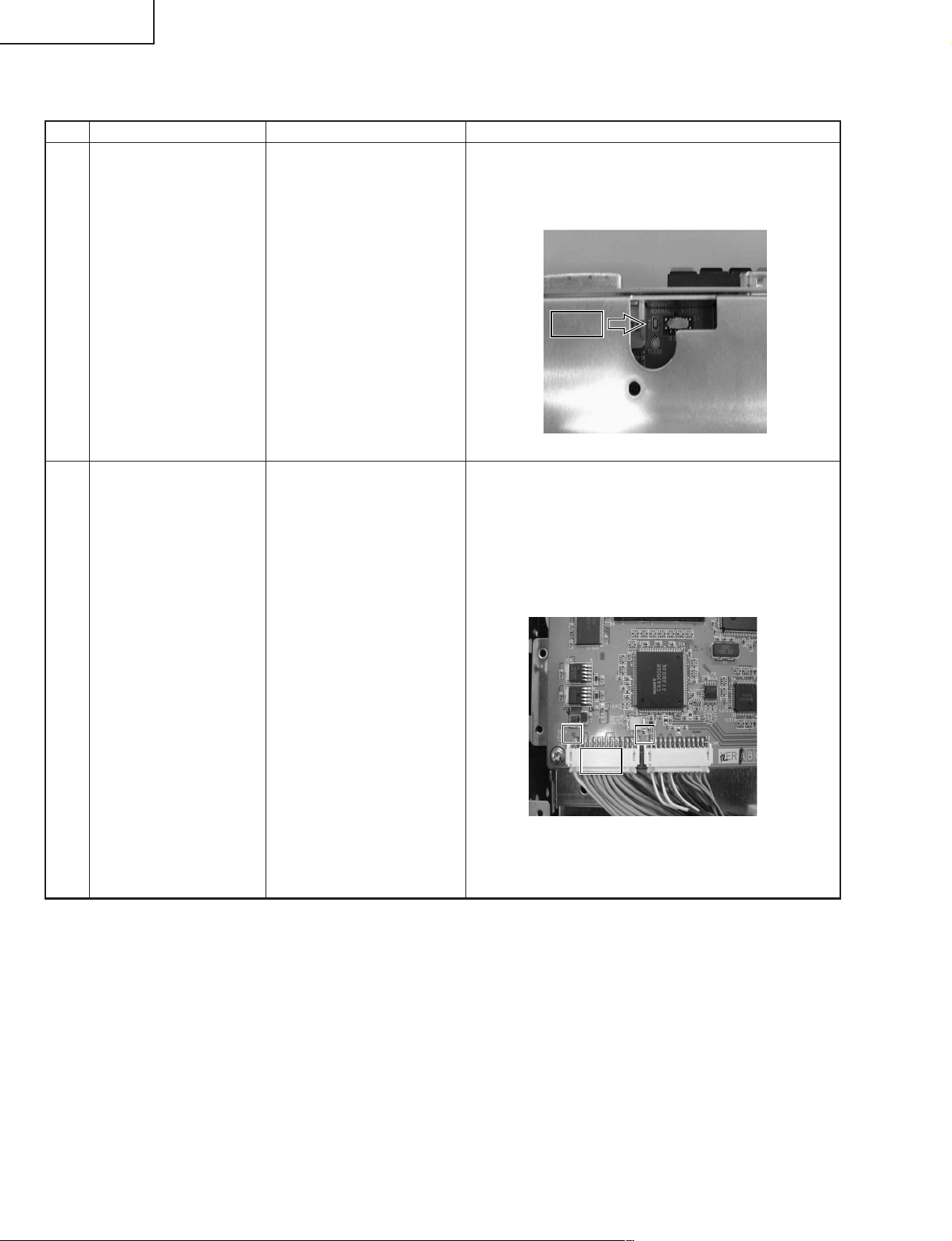

1 3.3 V Adjustment Page: 2 • Connect a DC voltmeter to TP4 on the PC I/F unit.

Location: TP4

Move the cursor to

and (–)

keys to adjust the voltage to 3.30 ± 0.01 V.

TP4TP4

"Ë

+Badj.3.3V" and use

"VOL" (

+)

2 1.8 V Adjustment Page: 2 • After adjustment to 3.3 V, move the cursor to the

Location: Pin (6) of CN9 "Ë+Ba dj.1.8V" l i ne and pre ss the "ENTER" key on

the remote controller. Adjustment will be made

automatically.

If "ERR" appears, adjust the voltage at pin (6) of

CN9 on the PC I/F unit to 1.90 ± 0.01 V.

11

CN9CN9

1313

24

Page 25

(2) Tuner adjustment

TP1102TP1102

TP1101

TP1101

Item Adjusting conditions/points Adjusting procedure

1 Signal setting Signal: • Use a signal generator to provide the tuner with a

NTSC RF Signal RF signal of 193.25 MHz on the split field color bar.

(Split field color bar)

Input terminals:

•

The color saturation of the color bar must be 75%.

A 100% white area must be included.

ANT-A, ANT-B • Make sure the 100% white area (synchronized)

US channel 10 received shows 2.00 Vp-p when the color bar opens in

video mode. If not, adjust the signal generator.

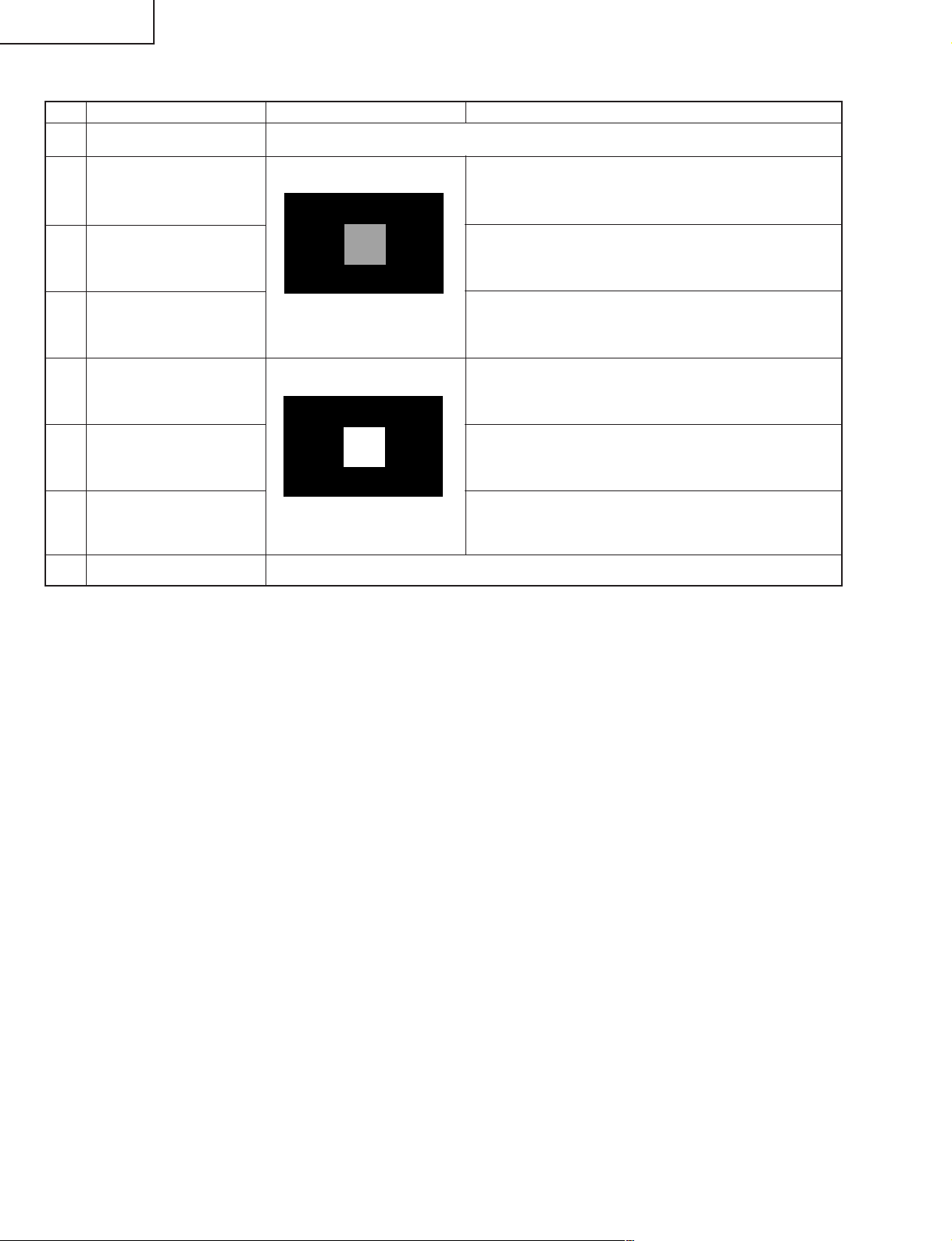

2 Tuner level Adjustment Page: 4 1.Provide the above RF signal to ANT-A and adjust

Locations: TP1101, TP1102

"TUNERA DAC ADJ" so that the tuner output is

1.0 ± 0.02 Vp-p at TP1101 when US channel 10 is

received.

LC-37HV6U

1.0Vp-p

2.Provide the above RF signal to ANT-B and adjust

"TUNER B DAC ADJ" so that the tuner output is

1.0 ± 0.02 Vp-p at TP1102 when US channel 10 is

received.

1.0Vp-p

25

Page 26

LC-37HV6U

0.7Vp-p

0.525Vp-p

(3) NTSC signal adjustment

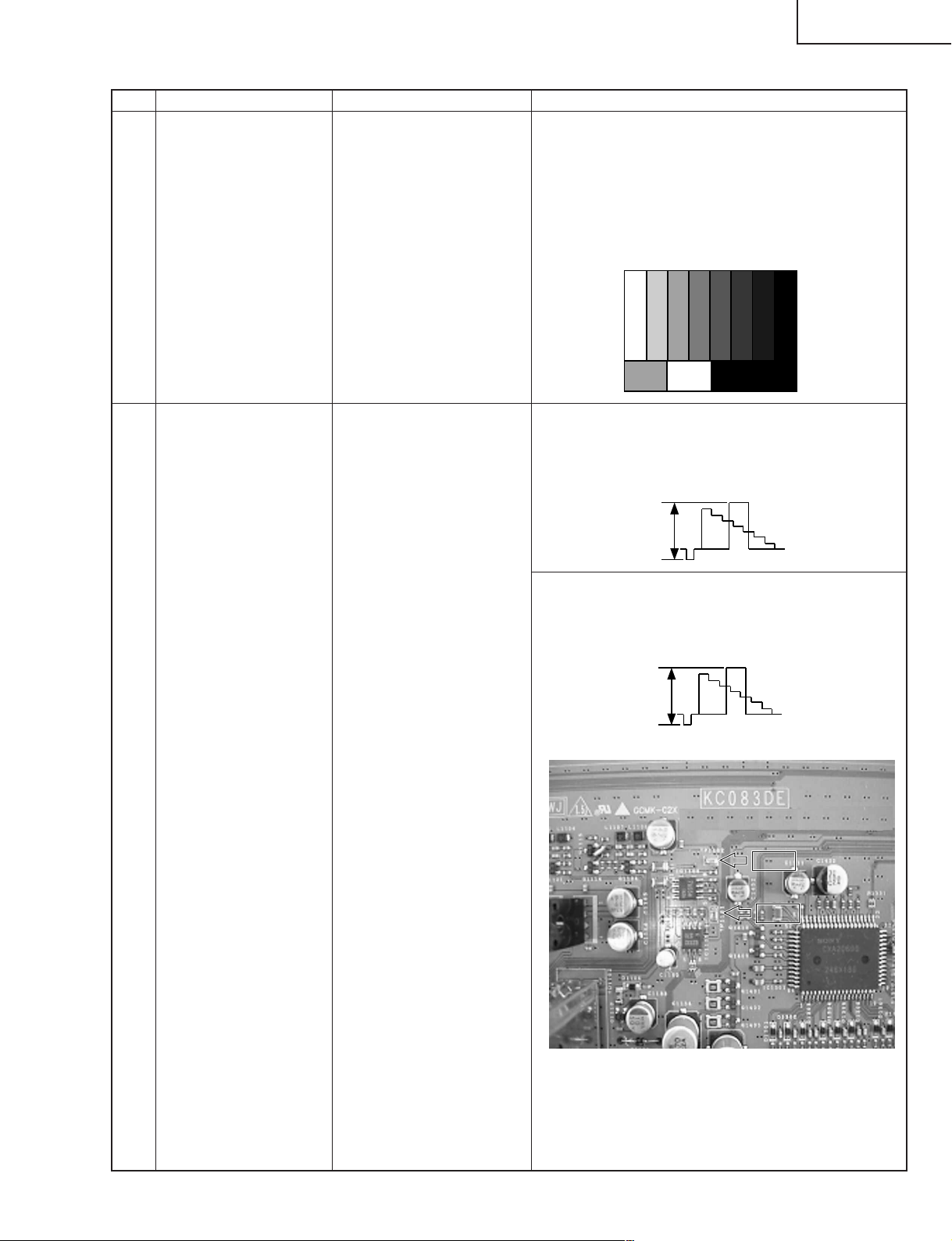

Item Adjusting conditions/points Adjusting procedure

1 Signal setting Signal: • Use a signal generator to provide the split field color

NTSC bar to the video image input pin of video input 1.

Split field color bar

•

The color saturation of the color bar must be 75%. A

100% white area must be included.

• Make sure the 100% white area (synchronized)

shows 2.00 Vp-p when the color bar opens in

video mode. If not, adjust the signal generator.

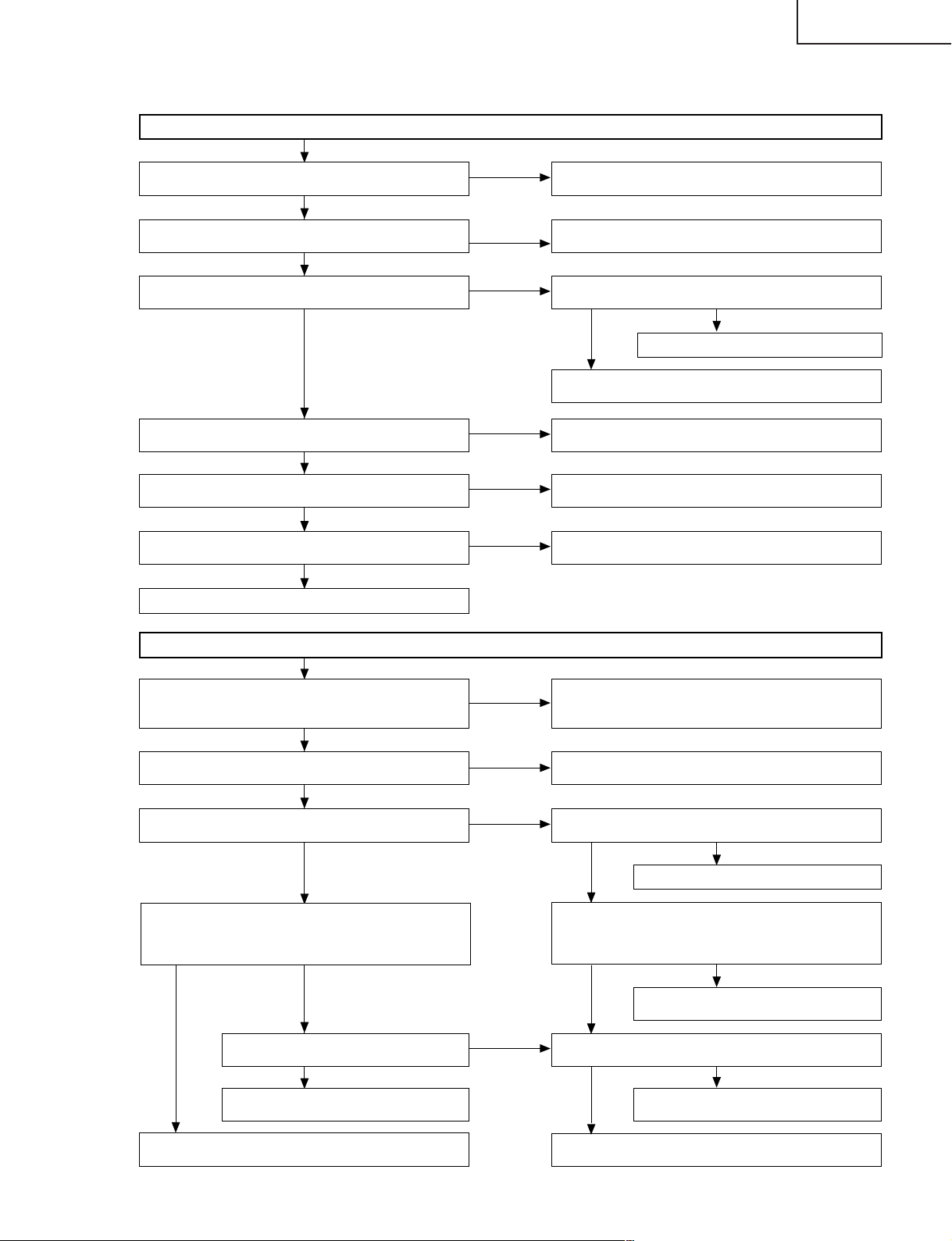

2 MAIN N358 Y Page: 3 Adjust "MAIN N358 Y GAIN" so that the 100%

GAIN Adjustment Signal pin: INPUT1, video white area shows 0.7 ± 0.01 Vp-p at pin (1) of P801.

Location: Pin (1) of P801

P801P801

11

1312

3 MAIN N358 CB Page: 3 Adjust "MAIN N358 CB GAIN" so that the width

GAIN Adjustment Location: Pin (3) of P801 shown below is 0.525 ± 0.01 Vp-p at pin (3) of P801.

26

Page 27

LC-37HV6U

Smoothed

1.0Vp-p

Smoothed

Item Adjusting conditions/points Adjusting procedure

4 MAIN N358 TINT Page: 3 Adjust "MAIN N358 TINT" so that the bottom edges

Adjustment Location: Pin (3) of P801 of the waveform at pin (3) of P801 are in line with

each other as shown below.

5 MAIN N358 CR GAIN Page: 3 Adjust "MAIN N358 CR GAIN" so that the width

Adjustment Location: Pin (5) of P801 shown below is 0.525 ± 0.01 Vp-p at pin (5) of P801.

0.525Vp-p

6 MAIN Page: 3 Adjust "MAIN CONTRAST 15K" so that the

CONTRAST 15K Location: Pin (7) of P801 difference between black and while peaks is

Adjustment 0.95 ± 0.02 V at pin (7) of P801.

7 Two-screen setting Press the TWIN PICT- Make the adjustment-purpose special two-screen

URE key. setting.

(The same images should appear on the main and

sub screens.)

8 SUB N358 Y Page: 4 Adjust "SUB N358 Y CONTRAST" so that the

CONTRAST Adjustment Location: Pin (9) of P801 difference between the black and white peaks is

1.0 ± 0.02 Vp-p at pin (9) of P801.

9 SUB N358 COLOR Page: 4 Adjust "SUB N358 COLOR GAIN" so that the black

GAIN Adjustment Location: Pin (11) of P801 peak is 0.7 ± 0.01 Vp-p at pin (11) of P801.

0.7Vp-p

10 SUB N358 TINT Page: 4 Adjust "SUB N358 TINT" so that the bottom edges

Adjustment Location: Pin (11) of P801 of the waveform at pin (11) of P801 are in line with

each other as shown below.

27

Page 28

LC-37HV6U

0.7Vp-p

0.70Vp-p

0.7Vp-p

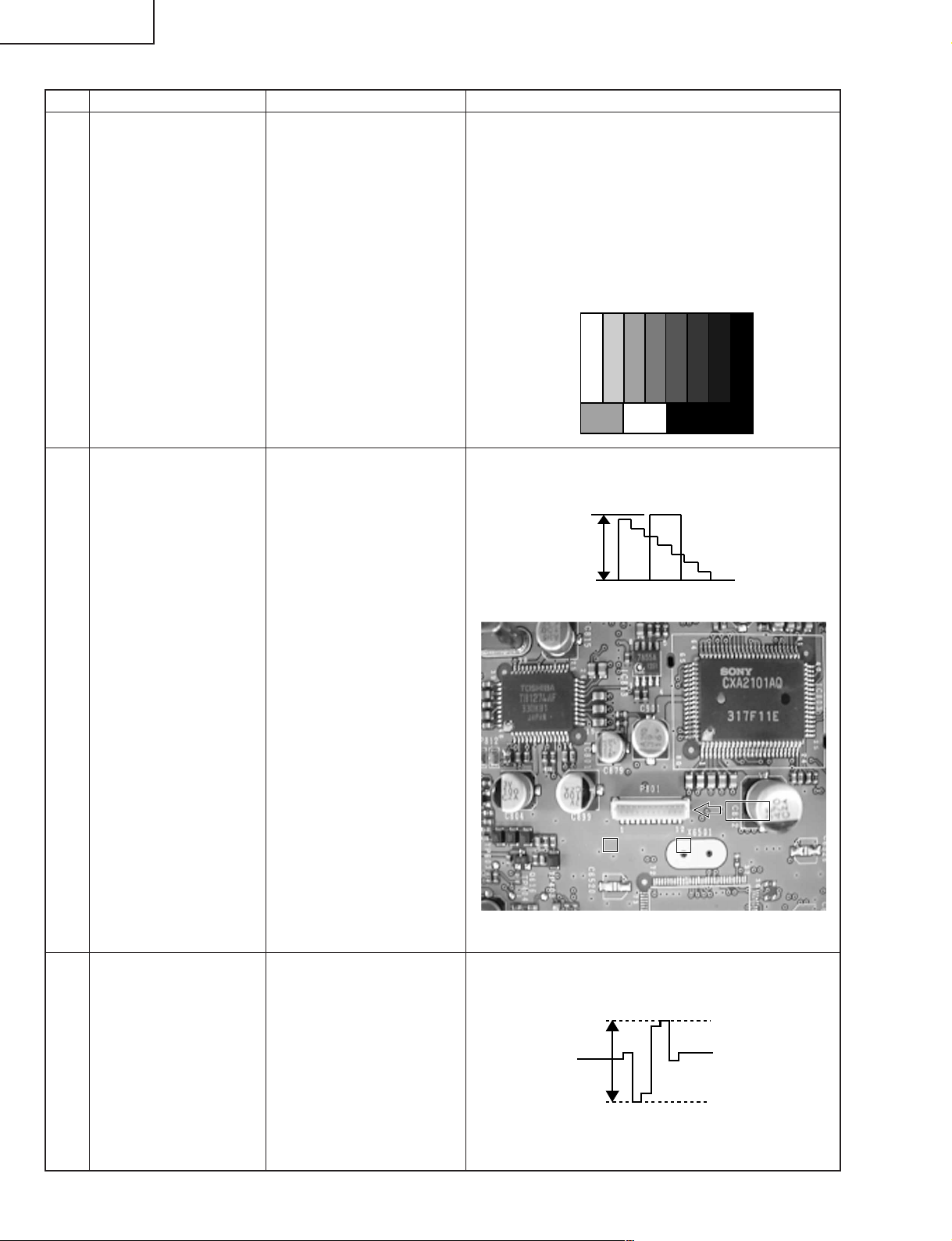

(4) Component 15 kHz signal adjustment

Item Adjusting conditions/points Adjusting procedure

1 Signal setting Signal: Provide the 100% color bar source of component 15k

Component 15k to the component input pin of video input 1.

100% color bar

Signal pin:

INPUT1 COMPONENT

2 COMP 15K GAIN Page: 5 Adjust "COMP 15K GAIN" so that

Location: Pin (1) of P801 0.70 ± 0.01 Vp-p is achieved at pin (1) of P801.

3 COMP 15K CB GAIN Page: 5 Adjust "COMP 15K CB GAIN" so that the width

Location: Pin (3) of P801 shown below is 0.70 ± 0.01 Vp-p at pin (3) of P801.

4 COMP 15K CR GAIN Page: 5 Adjust "COMP 15K CR GAIN" so that the width

Location: Pin (5) of P801 shown below is 0.70 ± 0.01 Vp-p at pin (5) of P801.

(5) Component HDTV signal adjustment

Item Adjusting conditions/points Adjusting procedure

1 Signal setting Signal: Provide the component HDTV source of the 100%

Component HDTV color bar to the component pin of video input 1.

100% color bar

Signal pin:

INPUT1 COMPONENT

2 COMP HDTV Page: 6 Adjust "COMP HDTV CONTRAST" so that the

CONTRAST Adjustment Location: Pin (9) of P801 difference between the black and while peaks is 0.95

± 0.02 Vp-p at pin (9) of P801.

28

Page 29

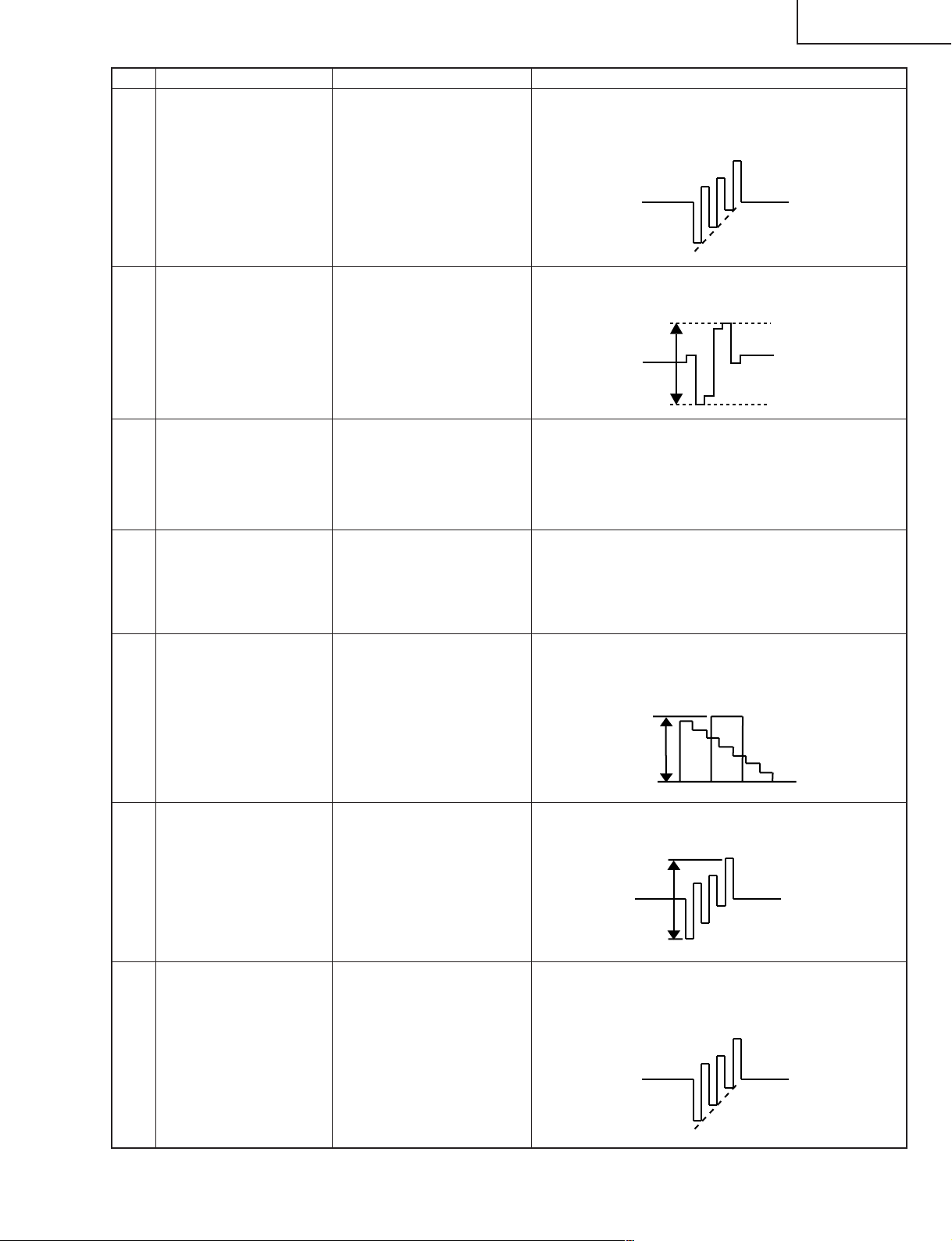

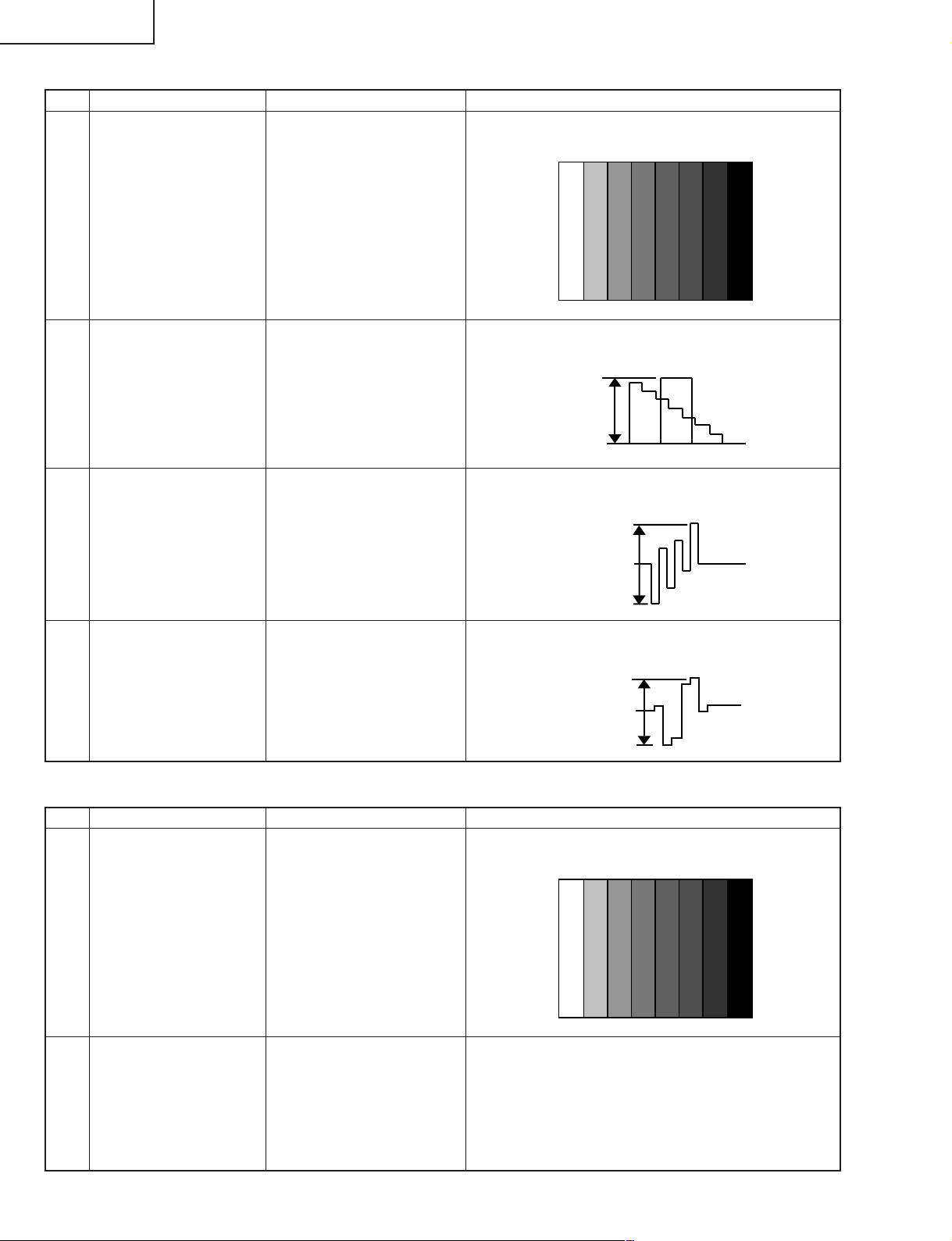

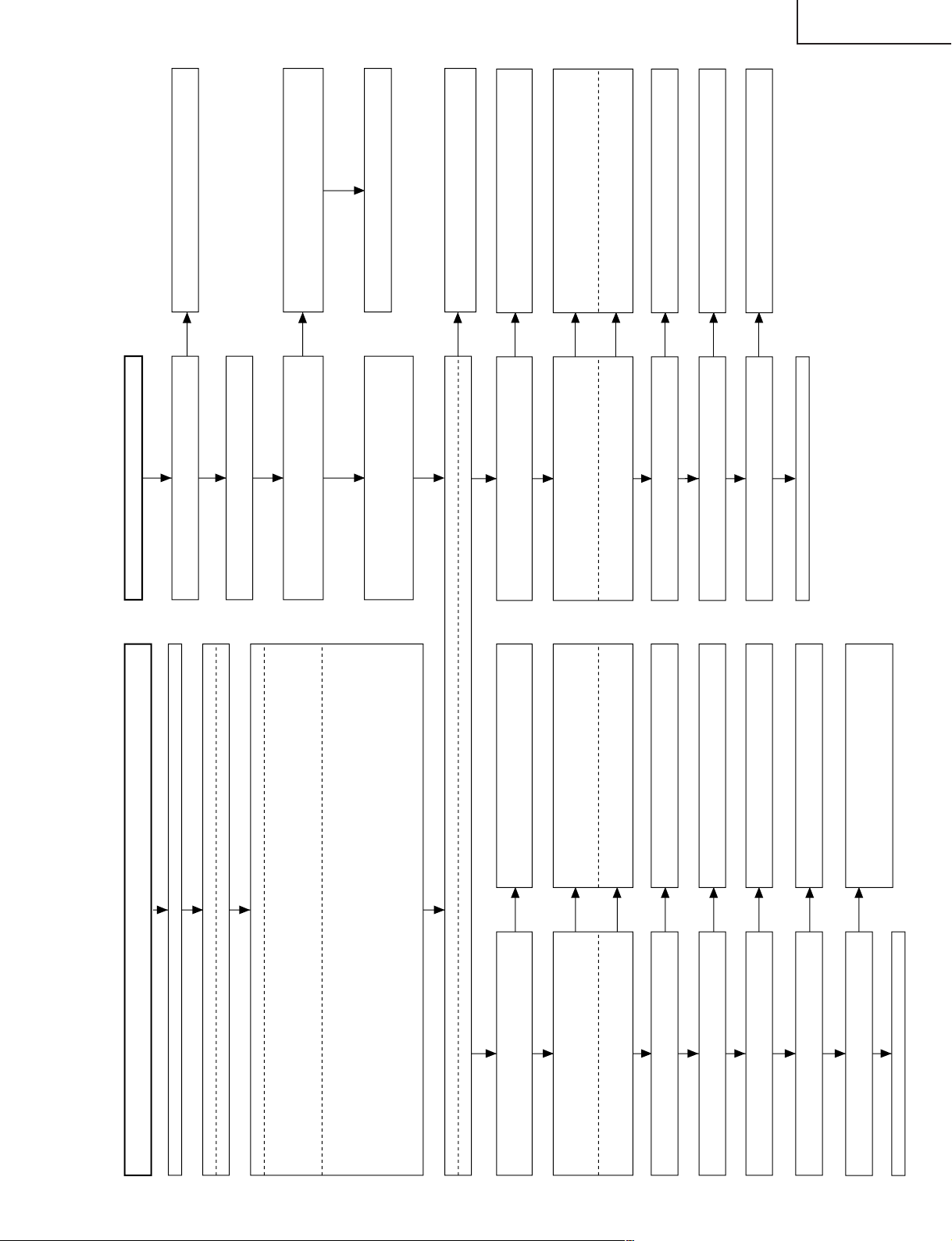

2) Digital white balance adjustment

(1) NTSC signal adjustment

Item Adjusting conditions Adjusting procedure

1 Setting

2

N358 R cutoff

N358 G cutoff

3

N358 B cutoff

4

N358 R drive

5

N358 G drive

6

N358 B drive

7

8 Convergence

LC-37HV6U

1. Provide the adjusting N358 signal (adjustment conditions) to the video image input pin of

video input 1. Page: 8

20% white window pattern

~

It is recommended that a

pattern without chroma and

burst be used.

80% white window pattern

~

It is recommended that a

pattern without chroma and

burst be used.

Repeat the above adjustments until convergence is reached (Adjust cutoff, drive, cutoff, drive and so on.)

1. Press "1" on the remote controller in the process

adjustment mode.

2. Adjust "N358 R CUTOFF" so that the luminance level of

the window pattern is maximized.

1. Press "2" on the remote controller in the process

adjustment mode.

2. Adjust N358 G CUTOFF so that the luminance level of

the window pattern is maximized.

1. Press "3" on the remote controller in the process

adjustment mode.

2. Adjust "N358 B CUTOFF" so that the luminance level of

the window pattern is maximized.

1. Press "4" on the remote controller in the process

adjustment mode.

2. Adjust "N358 R DRIVE" so that the luminance level of

the window pattern is maximized.

1. Press "5" on the remote controller in the process

adjustment mode.

2. Adjust "N358 G DRIVE" so that the luminance level of

the window pattern is maximized.

1. Press "6" on the remote controller in the process

adjustment mode.

2. Adjust "N358 B DRIVE" so that the luminance level of

the window pattern is maximized.

(2) COMPONENT 15 kHz signal adjustment

Item Adjusting conditions Adjusting procedure

1 Setting

2

COMP 15 kHz

R cutoff

COMP15 kHz

3

1. Provide the adjusting 525i component signal (adjustment conditions) to the component

video input pin of video 1. Page: 9

20% white window pattern

G cutoff

COMP 15 kHz

4

~

Simply press Y.

80% white window pattern

5

B cutoff

COMP

15 kHz

R drive

COMP15 kHz

6

G drive

COMP 15 kHz

7

~

B drive

Simply press Y.

1. Press "1" on the remote controller in the process

adjustment mode.

2. Adjust "COMP 15K R CUTOFF" so that the luminance

level of the window pattern is maximized.

1. Press "2" on the remote controller in the process

adjustment mode.

2. Adjust "COMP 15K G CUTOFF" so that the luminance

level of the window pattern is maximized.

1. Press "3" on the remote controller in the process

adjustment mode.

2. Adjust "COMP 15K B CUTOFF" so that the luminance

level of the window pattern is maximized.

1. Press "4" on the remote controller in the process

adjustment mode.

2. Adjust "COMP 15K R DRIVE" so that the luminance

level of the window pattern is maximized.

1. Press "5" on the remote controller in the process

adjustment mode.

2. Adjust "COMP 15K G DRIVE" so that the luminance

level of the window pattern is maximized.

1. Press "6" on the remote controller in the process

adjustment mode.

2. Adjust "COMP 15K B DRIVE" so that the luminance

level of the window pattern is maximized.

8 Convergence

Repeat the above adjustments until convergence is reached (Adjust cutoff, drive, cutoff, drive and so on.)

29

Page 30

LC-37HV6U

(3) COMPONENT HDTV signal adjustment

Item Adjusting conditions Adjusting procedure

1 Setting

2

COMP HDTV

R cutoff

HDTVG cutoff

COMP

3

COMP HDTV

4

B cutoff

COMP HDTV

5

R drive

HDTV

COMP

6

G drive

HDTV

COMP

7

B drive

1. Provide the adjusting 1080i component signal (adjustment conditions) to the component

vide input pin of video 1. Page: 10

20% white window pattern

~

Simply press Y.

80% white window pattern

~

Simply press Y.

1. Press "1" on the remote controller in the process

adjustment mode.

2. Adjust "COMP HDTV R CUTOFF" so that the

luminance level of the window pattern is maximized.

1. Press "2" on the remote controller in the process

adjustment mode.

2. Adjust "COMP 15K G CUTOFF" so that the luminance

level of the window pattern is maximized.

1. Press "3" on the remote controller in the process

adjustment mode.

2. Adjust "COMP HDTV B CUTOFF" so that the luminance

level of the window pattern is maximized.

1. Press "4" on the remote controller in the process

adjustment mode.

2. Adjust "COMP HDTV R DRIVE" so that the luminance

level of the window pattern is maximized.

1. Press "5" on the remote controller in the process

adjustment mode.

2. Adjust "COMP HDTV G DRIVE" so that the luminance

level of the window pattern is maximized.

1. Press "6" on the remote controller in the process

adjustment mode.

2. Adjust "COMP HDTV B DRIVE" so that the luminance

level of the window pattern is maximized.

8 Convergence

Repeat the above adjustments until convergence is reached (Adjust cutoff, drive, cutoff, drive and so on.)

30

Page 31

LC-37HV6U

4. Factory setting

Item Adjusting conditions Adjusting procedure

INDUSTRY INIT

1

Page: 1

Notes:

1) Perform factory setting as the latest task. Do not turn on the power after factory setting.

2) Turn the AVC’s AC power off to turn off the system.

Never turn off the power during factory setting.

3) After completion of factory setting, the system will exit from the process adjustment mode automatically. If not so,

HDCP has been set to off. Check HDCP setting.

4) Factory setting results in initializations of all user settings including channel setting.

(Items set in process adjustment mode are not initialized).

Items initialized by factory setting include the following:

• User settings (menu)

• Channel data (including broadcast frequencies)

• Password

• Operation time

• Auto installation flag

• Optimal manufacturer settings

• VCHIP block setting

1. Move the cursor to the "INDUSTRY INIT" line, use the

VOL key to turn the system on and press the ENTER

key.

Factory setting is complete when the process adjustment

menu disappears and the system enters the TUNER

input mode.

~Make sure HDCP is on. If it is off, the system cannot

exit from the process adjustment mode.

2. Turn off the AVC AC power.

31

Page 32

LC-37HV6U

Ë Ë

Ë Adjustment Model Menu List (AVC System)

Ë Ë

Do not change items, the adjustment procedure of which is not described in this manual. Inadvertent changes of

such items may result in unexpected or unrecoverable errors.

PAGE LINE NAME FUNCTION

1 1 KEY WRITE

2 INDUSTRY INIT Resetting the internally stored data to the factory settings

3 CENTER Version Main microprocessor version information (program)

4 OSD Version Main microprocessor version information (data)

5 CVIC Version Main microprocessor version information (program)

6 MONITOR Version Monitor microprocessor version information

7 ModelSelect MAIN

8 ModelSelect AV

9 ModelSelect MONITOR

10 STANDBY TYPE

11 HOTEL MODE

2 1 Ë+BAdj3.3V 3.3V adjustment

3 1 ËN358 MAIN Adjust

4 1 ËN358 SUB Adjust

5 1 ËCOMP 15K Adjust

6 1 ËCOMP HDTV Adjust

7 1 TUNER TEST1(CH15)

8 1 ËN358 White Balance

9 1 ËCOMP15K White Balance

2 Ë+BAdj1.8V(Enter:Auto)

3 ËREFERENCE Adjust

4 Select Adj Signal

5 Center Acutime Cumulative operating time on AVC center side

6 RESET Reset

7 BackLight Acutime Cumulative operating time of monitor

8 RESET Reset

2 N358 MAIN+SUB Adjust

3 MAIN N358 Y GAIN Adjustment in one-screen mode or adjustment of main side (left) in two-screen mode

4 MAIN N358 CB GAIN Adjustment in one-screen mode or adjustment of main side (left) in two-screen mode

5 MAIN N358 CR GAIN Adjustment in one-screen mode or adjustment of main side (left) in two-screen mode

6 MAIN N358 TINT Adjustment in one-screen mode or adjustment of main side (left) in two-screen mode

7 MAIN CONTRAST 15K Adjustment in one-screen mode or adjustment of main side (left) in two-screen mode

8 MAIN CUBBRIGHT 15K

2 SUB N358 CONTRAST Adjustment of sub side (left side) in two-screen mode

3 SUB N358 COLOR GAIN Adjustment of sub side (left side) in two-screen mode

4 SUB N358 TINT Adjustment of sub side (left side) in two-screen mode

5 TUNERA DAC ADJ Level adjustment of Tuner-A

6 TUNERB DAC ADJ Level adjustment of Tuner-B

2 COMP 15K GAIN Adjustment of component (480i)

3 COMP 15K CB GAIN Adjustment of component (480i)

4 COMP 15K CR GAIN Adjustment of component (480i)

2 COMP HDTV CONTRAST Adjustment of component (1080i)

3 COMP HDTV SUBBRIGHT Adjustment of component (1080i)

2 TUNER TEST2(CH10)

3 PEAK ACL SW

4 DC TRAN

5 DYNAMIC GAMMA

6 SIGNAL INFO

7 CENTER PROG UPDATE Version upgrade of software

8 EEPROM SAVE Adjustment value data save

9 EEPROM RECOVER Adjustment value data recovery

2 PAL White Balance

3 PC White Balance

4 N358 R CUTOFF White balance adjustment of NTSC

5 N358 G CUTOFF White balance adjustment of NTSC

6 N358 B CUTOFF White balance adjustment of NTSC

7 N358 R DRIVE White balance adjustment of NTSC

8 N358 G DRIVE White balance adjustment of NTSC

9 N358 B DRIVE White balance adjustment of NTSC

2 COMP15K R CUTOFF Digital white balance adjustment of component (480i)

3 COMP15K G CUTOFF Digital white balance adjustment of component (480i)

4 COMP15K B CUTOFF Digital white balance adjustment of component (480i)

5 COMP15K R DRIVE Digital white balance adjustment of component (480i)

6 COMP15K G DRIVE Digital white balance adjustment of component (480i)

7 COMP15K B DRIVE Digital white balance adjustment of component (480i)

8 COMP15K PASS SW

1.8V adjustment (Note that the value measured at the terminal area of the PC/IF PWB unit is 1.9V.)

32

Page 33

PAGE LINE NAME FUNCTION

10 1 ËCOMP33K White Balance

2 COMPHDTV R CUTOFF Digital white balance adjustment of component (1080i)

3 COMPHDTV G CUTOFF Digital white balance adjustment of component (1080i)

4 COMPHDTV B CUTOFF Digital white balance adjustment of component (1080i)

5 COMPHDTV R DRIVE Digital white balance adjustment of component (1080i)

6 COMPHDTV G DRIVE Digital white balance adjustment of component (1080i)

7 COMPHDTV B DRIVE Digital white balance adjustment of component (1080i)

11 Omitted

12 1

13 1 DEBUG PRINT SW

MONITOR GAMMA OFFSET R

2

MONITOR GAMMA OFFSET G

3

MONITOR GAMMA OFFSET B

4 MONITOR GAMMA R

5 MONITOR GAMMA G

6 MONITOR GAMMA B

7 MONITOR GAMMA WRITE

2 PIC ADJ MAKER SELECT

3 PIC ADJ KOUTEI SELECT

4 1274 V_CD_MODE

5 ACL HARD SW

6 DEBUG_SELECT_SW

7

DEBUG COMPANY SELECT

8

DEBUG PANELTYPE SELECT

LC-37HV6U

33

Page 34

LC-37HV6U

UPGRADING INSTALLED PROGRAMS

Programs installed in the product are mainly divided into the following two categories:

∫ Main programs (for AVC System)

∫ Monitor program (for Display)

CAUTON: Exercise great care to hide the procedure in entering the in-process adjustment mode from the

customer. Inadvertent setting changes in this mode may cause a fatal error resulting in a program being

unrecoverable.

[Tools required]

∫ PC

A Windows 95/98/me/2000/XP PC that has a COM port (RS-232C).

A USB-R232C converter will be acceptable provided that it is appropriately set and has PC compatibility.

∫ RS-232C cross cable

Interlink cable is also acceptable.

[Preparations]

Rewriting a program needs the product to enter the adjustment process mode.

1) The re writing software is supplied in the form of an ex e file named e.g., "MAIN_2002_10_10A.e x e" (provisional).

Create a directory on a HD and copy the software into the directory.

2)Double-click the file. The file will be self-extracted. Check the extracted file against the documentation

accompanying with the software.

3) Connect the AVC System and the Display unit with each other and make them ready for oper ation (mak e sure

the power LEDs of the AVC System and Display unit turn red).

4) Use an RS-232C cable to connect the PC to the AVC System.

5) Exercise great care to hide the procedure in entering the adjustment process mode from the customer.

Press the "MAIN POWER" button while holding down the "VOL (–)" key and the "INPUT" key on the Display

unit simultaneously.

If blue characters appear on the display, the system has entered the in-process adjustment mode successfully.

If not (the normal activation screen opens), retry.

[Rewriting the main program]

1) In the in-process adjustment mode , press the "CH(ù)" k e y on the remote controller. You will move to page ("7"

will appear on the upper left corner of the screen).

2) Make sure CENTER PROG UPDATE on page 7 is highlighted.

(It checks that "CENTER PROG UPDATE" on page 7 is chosen.)

3) Use the "VOL(–)/(+)" keys to change OFF to ON.

4)Press the "ENTER" key on the remote controller. Characters on the screen will disappear and the screen

blacks out.

5) Double-click the batch file specified in the document accompanying with the software.

6) A black window (MS-DOS window) will open and rewriting starts automatically.

Rewiring of the main program is now complete. Unplug the AC cord from the AVC System and turn off the

system and then on again.

7) Enter the adjustment process mode and make sure the version information on the CENTER Version, OSD

Version and CVIC Version lines on page 1/13 has been updated.

34

Page 35

LC-37HV6U

Continued

35

Page 36

LC-37HV6U

[How to rewrite the monitor program]

1) After entering the process adjustment mode, start up the terminal software obtained separately.

(Freeware products available on the Internet can be used.)

2) Make setting as shown below.

Baud rate: 9600

Data: 8 bits

Parity: NONE

Stop: 1 bit

Flow control: NONE

3) If the above setting is made correctly, pressing the "ENTER" key on the PC will make "ERR" appear on the

terminal software.

4) In this state, type the following. (

The characters displayed on the screen disappear and the screen becomes black.

IPL_0002

~ Immediately after the above entry, an unusual display may be appear on the terminal software, which means no

abnormal condition.

5) Change the baud rate to 115200.

6) Press the "ENTER" key to make appear the following display

ERR

SEND "MONITOR PROG UPDATE PROGRAM" from PC to MR

7) Using the file transmission function (function to transmit specified file contents) of the terminal software, select

the decompressed file (specified by the attached documentation) in the directory on the PC and execute

transmission.

8) When the following display appears on the terminal software, rewriting of the monitor program has been

completed. (Its contents may vary depending on the terminal software or program.)

Unplug the power cord to turn off the power and then turn it on again.

9) For confirmation, enter the process adjustment mode again and check that the version information shown on

the line "Monitor Version" on the 1st page corresponds to the new version shown on the attached documentation.

means the ENTER key.)

36

Page 37

LC-37HV6U

ADJUSTMENT PROCEDURES (Displa y)

The adjustment values are set to the optimum conditions at the factory before shipping. If a value should become

improper or an adjustment is required due to part replacement, make an adjustment according to the following

procedure.