SHARP ERA450TU, ER-A450T Service Manual

SERVICE MANUAL

ELECTRONIC

CASH REGISTER

MODEL ER-A450T

SRV Key : LKGIM7113RCZZ

PRINTER: PR-45M

("U" and "A" version)

CAUTION

EXTREME CAUTION MUST BE TAKEN WHEN SERVICING THIS MACHINE. WHEN THE

MODE SWITCH IS IN THE OFF POSITI ON, VOLTAGE I S STI LL SUPPLIED TO THE ENTIRE

MACHINE.

WHEN WORKING ON THIS MACHINE MAKE SURE THAT THE POWER CORD IS

REMOVED FROM THE WALL OUTLET.

CONTENTS

CHAPTER 1. SPECIFICATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

CHAPTER 2. OPTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

CHAPTER 3. SERVICE RESET AND MASTER RESET . . . . . . . . . . . . . . . . 3-1

CHAPTER 4. HARDWARE DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

CHAPTER 5. TEST FUNCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

CHAPTER 6. DOWN LOAD FUNCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

CHAPTER 7. SERVICE PRECAUTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

CHAPTER 8. CIRCUIT DIAGRAM & PWB LAYOUT . . . . . . . . . . . . . . . . . . . 8-1

PARTS GUIDE

Parts marked with " " are important for maintaining the safety of the set. Be sure to replace these parts with specified

ones for maintaining the safety and performance of the set.

This document has been published to be used

SHARP CORPORATION

for after sales service only.

The contents are subject to change without notice.

CHAPTER 1. SPECIFICATIONS

1. Appearance/Rat ing

1) Rating

Power source 120V 10% AC , 60Hz

Power consumption Standby: 14 W

Operating temperature 32 - 104 °F (0°C - 40°C)

Operating humidity 10% - 90% (RH)

Physical dimensions,

including the drawer

Weight 27.6 lbs ( 13.5 kg )

Operating: 37 W (max.)

16.5(W) x 16.8(D) x 11.5(H) in.

(420(W) x 427(D) x 292(H)mm)

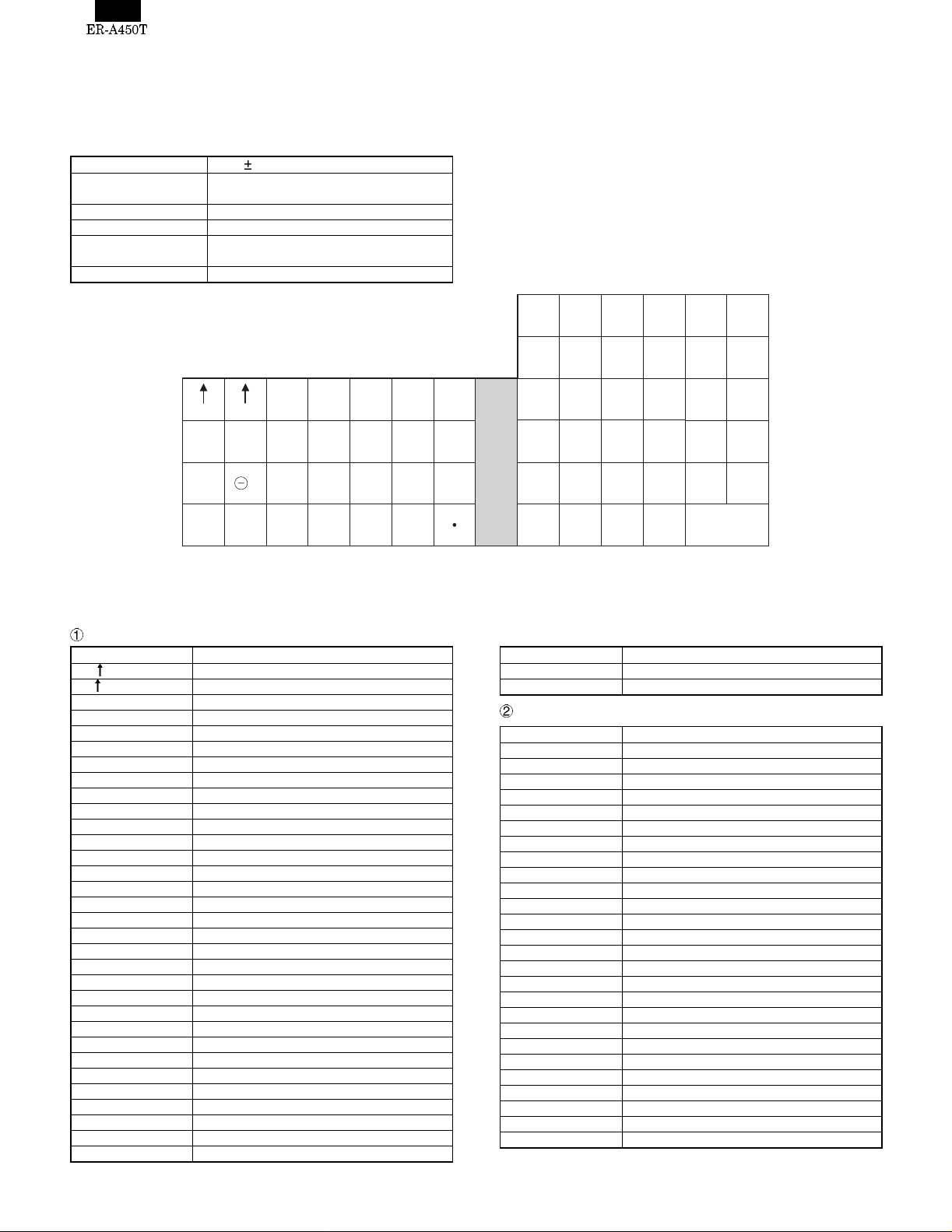

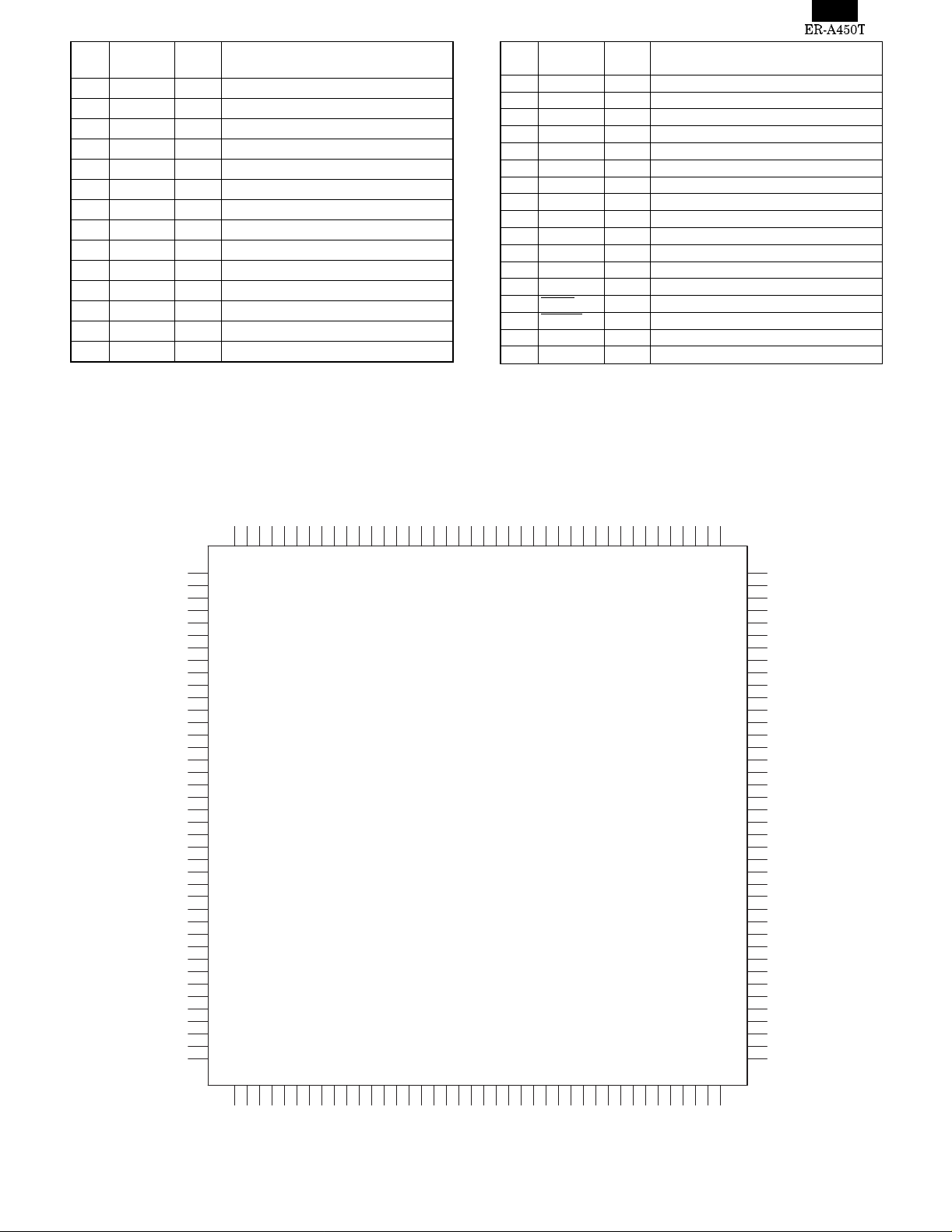

2. Keyboard

1) Standard keyboard layout

CASH

RECEIPT JOURNAL

RFNDRCPT SLIP

1

RA

PO %1

2) Key top name

Standard Key Top

KEY TOP DESCRIPTION

RECEIPT Receipt paper feed key

JOURNAL Journal paper feed key

0 to 9,00 Numeric keys

• Decimal point key

@/FOR Multiplication / Split-pricing key

CL Clear key

1 to 20 Department keys

PLU/SUB PLU / Subdepartment key

TAX1 SHIFT Tax 1 shift key

TAX2 SHIFT Tax 2 shift key

UPC UPC key

SLIP Slip print key

%1 Percent 1 key

CASH # Cashier code entry key

RCPT Receipt print key

(-) 1 Discount 1 key

NC New charge account balance key

PBLU Previous balance lookup key

FINAL Final key

AMT Amount key

AUTO Automatic sequencing key

RA Received on account key

PO Paid out key

RFND Refund key

VOID Void key

SCALE Scale ke y

OPEN TARE Open tare key

CH Charge key

CHK Check key

MDSE SBTL Merchandise subtotal key

SBTL Subtotal key

CA/AT Cash/amount tendered key

VOID

FINAL

PLU/

SUB

5

CL

7

8

00

9

5

6

2

3

14

3

2

1

#

@/FOR

PBLU

NC

4

1

0

AMT

15

10

14

9

13

8

12

7

11

6

SCALE

20

19

18

17

16

OPEN

TARE

TAX1

SHIFT

TAX2

SHIFT

CHK

MDSE

SBTL

AUTOUPC

FS

SHIFT

FS

TEND

CH

SBTL

CA/AT

Fig. 2-1

KEY TOP DESCRIPTION

FS SHIFT Food stamp shift key

FS TEND Food stamp tendered

Optional Key Top

KEY TOP DESCRIPTION

21 to 50 Department keys

TAX3 SHIFT Tax 3 shift key

TAX4 SHIFT Tax 4 shift key

(-)2 - 4 Discount 2 - 4 keys

000 Triple zero key

# Non-add code key

NS No sale key

TAX Tax key

DEPT # Department No. entry key

REPEAT Repeat key

INQ UPC inquiry key

AUTO2 - 10 Automatic sequencing 2 - 10 keys

RA2 Received on account 2 key

PO2 Paid out 2 key

CH2 - 5 Charge 2 - 5 keys

CA2 Cash total 2 key

CONV1 - 4 Currency conversion 1 - 4 keys

CHK2 Check 2 key

RFND SALE Refund sales key

B-DAY Birthday date entry key

NON DELETE Non delete key

PRICE CHANGE Price change key

P1 - 3 UPC price level 1 - 3 keys

SRVC Service key

DEP Deposit key

DEP RFND Deposit refund key

1 – 1

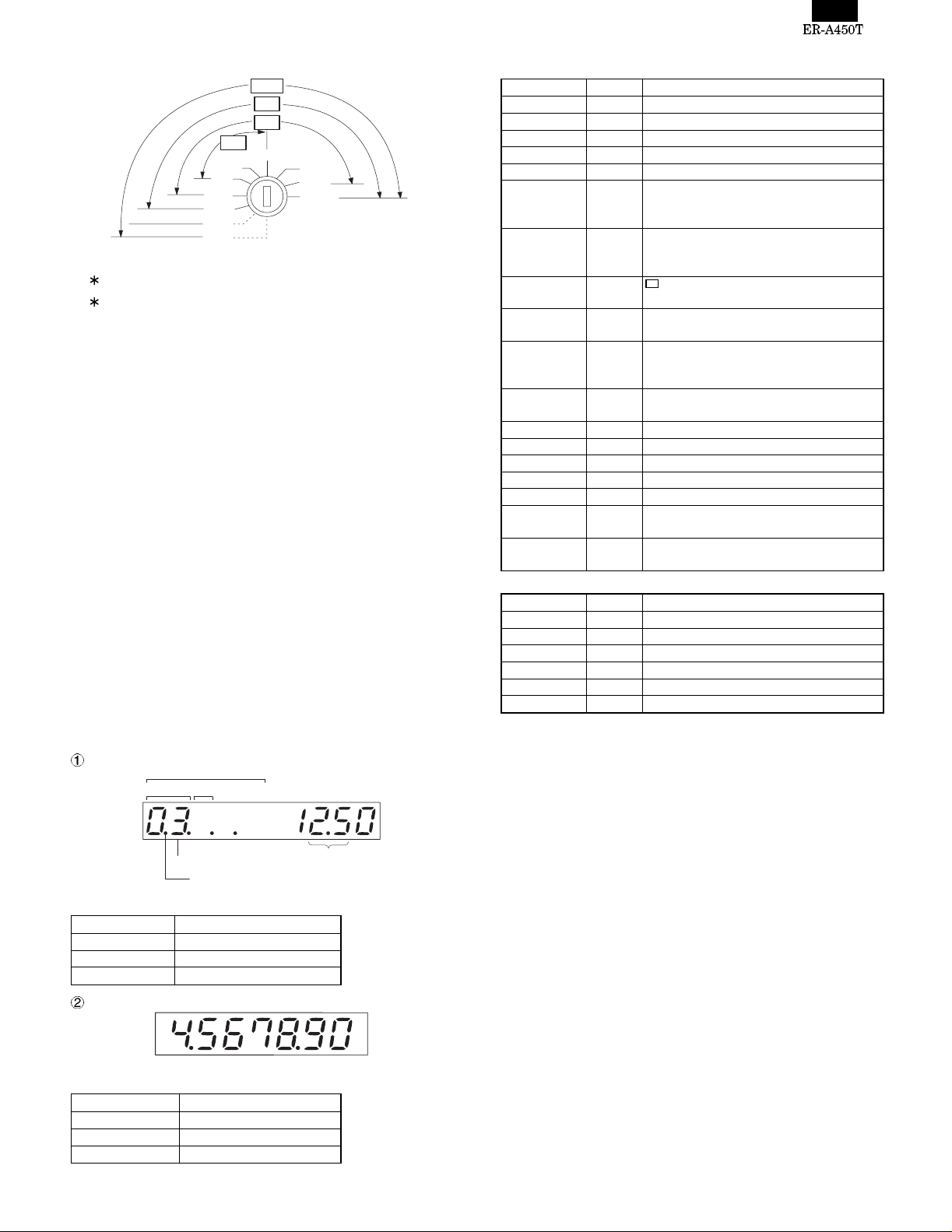

3. Mode switch

SRV

MA

SM

OP

REG

OP,X/Z

OFF

PGM1

PGM2

(SRV)

(SRV')

Fig. 3-1

The key can be removed in the REG or OFF position.

In the SRV’ mode, key inputs are prohibited and no display is present.

[Functions]

MGR

X1/Z1

X2/Z2

• Function for each key position

• SRV’: System reset

• SRV: Service mode (Service programming)

• PGM2: Allows programming of an item that is not changed fre-

quently, in addition to the PGM1 mode programming.

• PGM1: Allows programming of items frequently changed (e.g.

department, PLU pricing, and discount rate setting).

• OP X/Z: Allows X or Z operation by clerks or cashiers.

• REG: Allows registrations.

• MGR: Allows the operations, by authorized person such as a

manager (e.g. correction after transaction finished or

cancellation of entry limits), which are not permitted to

ordinary cashiers.

• X1/Z1: Allows reading and resetting of daily sales total.

• X2/Z2: Allows reading or resetting sales totals for a specified

period.

• OFF: Switching off the display to prevent key board entries.

4. Display

Display contents

<Segment>

Position Description

Amount 1-8

Minus sign 4-10 - : Floating

Error 10 E

PGM Mode 10 P

VOID Mode 10 u

RFND SALE

Mode

CASH,

CHECK,

CHARGE

SUB TOTAL

/ short tender

Change 10 C : Light up whenever the change due

Foreign

Currency

SUB TOTAL

Food Stamp

Change

Department 9-10 Not zero-suppressed

PLU 5-10 Not zero-suppressed

Repeat 8 Endless count, starting from 2.

Receipt OFF 9 _

Cashier No. 2-3 - xx - : cashier code (xx = code 1-99)

VP

compulsory

Slip

compulsory

<Decimal point>

Decimal point 4-1 Based on setuper multiplication.

TAB 4-1 SRV JOB#901

Sentinel 10 PGM JOB#2321

Price Level-3 9 For UPC code entry

Price Level-2 8 For UPC code entry

Scale entry 7 Item unit price

1-10 rrrrrrrrrr :

Light up only at the starting of RFND

SALE

10 f : Light up when a registration is finalized

by depressing CASH, CHECK,

CHARGE key

10

amount appears in the display.

10 c

10-8 xxF : FS amount

10 U : Light up when the validation printing is

compulsory

10 P : Light up when the slip printing is

compulsory (REG/MGR/VOID mode)

Position Description

1) Layout

Operator display

No. of positions 10

Color of display Yellow Green

Character size 14.2 (H) ✕ 8.0 (W) mm

Customer display (Pop-up display)

No. of positions 7

Color of display Yellow Green

Character size 14.2 (H) ✕ 8.0 (W) mm

PLU/SUB

DEPT REPEAT

P3 P2 $

RCPT

OFF

CID sentinel indicator

Fig. 4-1

7 segment display (LED)

$

Fig. 4-2

7 segment display (LED)

Cashier code

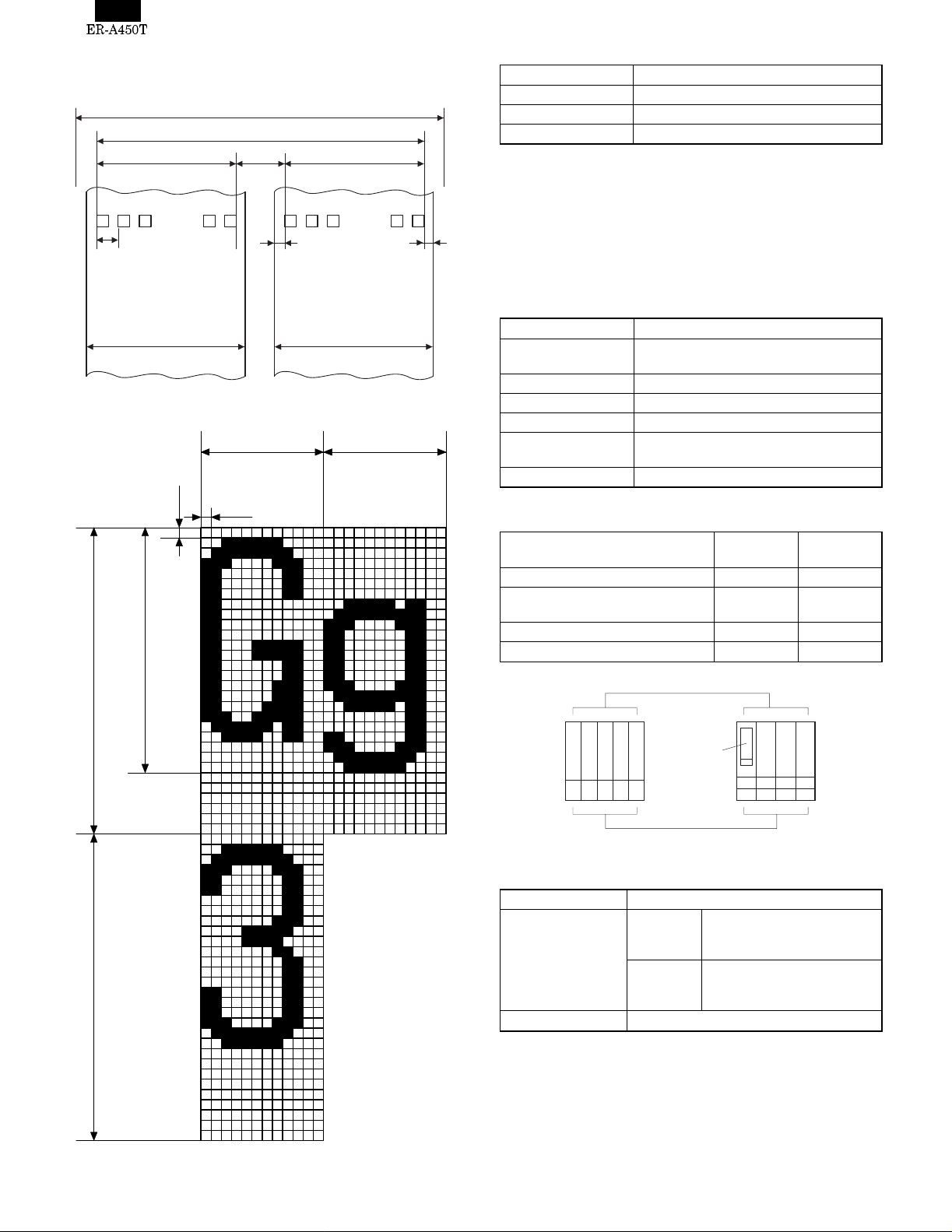

5. Specifications

1) Printer (PR-45M)

•

No. of station: 2: Receipt and Journal

• Validation: No

• Printing system: Line thermal

• No. of dot: Receipt: 288 dots

Journal: 288 dots

• Dot pitch: Horizontal: 0.125 mm

Vertical: 0.125 mm

• Font: 10 dots (W) × 24 dots (H)

• Printing capacity: Receipt: Max. 24 characters

Journal: Max. 24 characters

• Character size: 1.25 mm (W) × 3.0 mm (H):

• Print pitch: Column distance: 1.5 mm

• Print speed: Approximate 50 mm/s (13.3 lines/sec)

• Paper feed speed

(Manual feed): Approximate 40 mm/s

• Reliability: Mechanism MCBF 5 million lines

• Paper end sensor: Yes (Receipt and Journal)

At 10 × 24 dots

Row distance: 3.75 mm

Head life 5 × 10

7

pulses

1 – 2

• Cutter: Manual

• Paper near end sensor: No

• Printing area:

Number of thermal head heater elements 864 dots

(688dots)

36

(288dots)

14

(112dots)

36

(288dots)

2) Paper

Item Description

Name Heat-quality paper

Roll dimension 44.5 ±0.5 mm in width

Thickness 0.06 mm to 0.08 mm

3) Cutter

• Method: Manual

0.125

• Print for mat:

3.75 (30dots)

44.5±0.5

0.125

3.0 (24dots)

4

44.5±0.5

(Units : mm)

1.5 (12dots) 1.5 (12dots)

0.125

4.5

6. Drawer

1) Specification

(1) Drawer box and drawer

Model name SK-423

Size 420 (W) x 427(L: included lock key) x

Color GRAY 368

Material Metal

Bell Release lever Standard equipment; Located at the

Drawer open sensor Standard equipment

2) Money case

Separation from the drawer Allowed Allowed

Separation of the coin

compartments from the money case

Bill separator - YES

Number of compartments 5B/5C 4B/8C

112(H: included rubber leg)

bottom

For

"U" version

Disallowed Disallowed

Bill compartments

"A" version

For

Bill separator

Coin compartments

3) Lock

Location of the lock Front

Method of locking

and unlocking

3.75 (30dots)

Key No. SK1-1

UNIT: mm

Locking: Insert the drawer lock key into

the lock and turn it 90

degrees counterclockwise.

Unlocking: Insert the drawer lock key into

the lock and turn it 90

degrees clockwise.

1 – 3

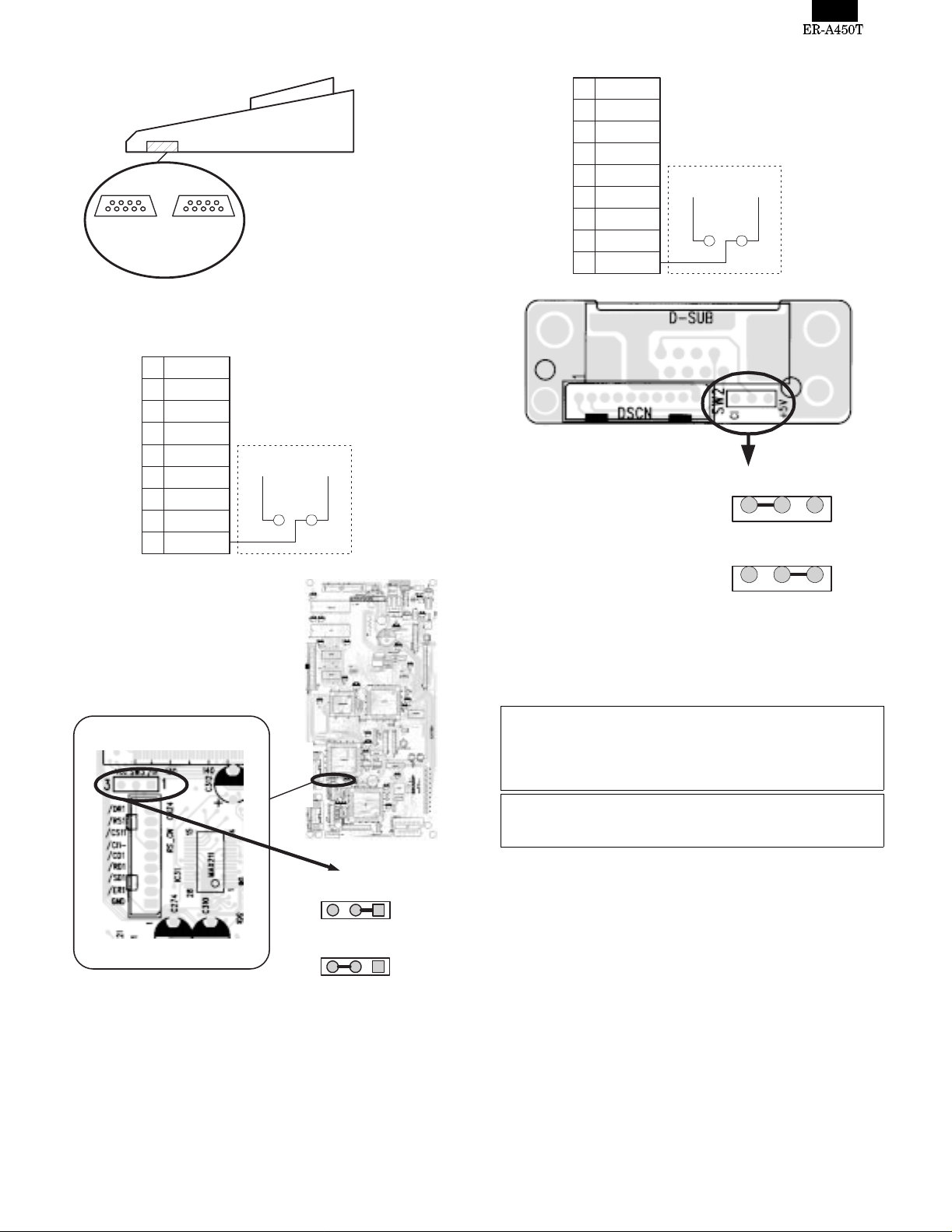

7. RS232 Interface

Channel No.:

Port 1(CH8)

1) Port 2 (CH1)

1

2

3

4

5

6

7

8

9

Channel No.:

Port 2(CH1)

/CD

RD

SD

/ER

GND

/DR

/RS

/CS

on the Main PWB

VCC

/CI

SW3

2) Port 1 (CH8)

1

2

3

4

5

6

7

8

9

/CD

RD

SD

/ER

GND

/DR

/RS

/CS

on the RS connector PWB

+5V

/CI

SW2

Pin No.9 : /CI signal (Default)

SW2

CI

Pin No.9 : +5V signal

+5V

Pin No.9 : /CI signal (Default)

SW3

VCC

31

Pin No.9 : Vcc(+5V) signal

VCC

31

SW3

/CI

/CI

SW2

CI

The No.9 pin signal of the Port 1 (CH8) can be selected between the

/CI signal and the +5V signal by changing the connection of the SW2

(initial value: /CI signal)

NOTE:

Optional bar code reader: When connecting an ER-A6HS1, connect

it to the Port 1 (or 2) and switch the No.9 pin signal to the +5V

signal.

When connecting other RS232 devices to either the Port 1 (or 2),

make sure the No.9 pin signal is proper before connecting the device.

If you want to connect an RS232 device to the ECR with the No.9

pin of the port 1 (or 2) set to +5V, make sure the AC cable of the

ECR is disconnected from the wall outlet to protect the device.

+5V

1 – 4

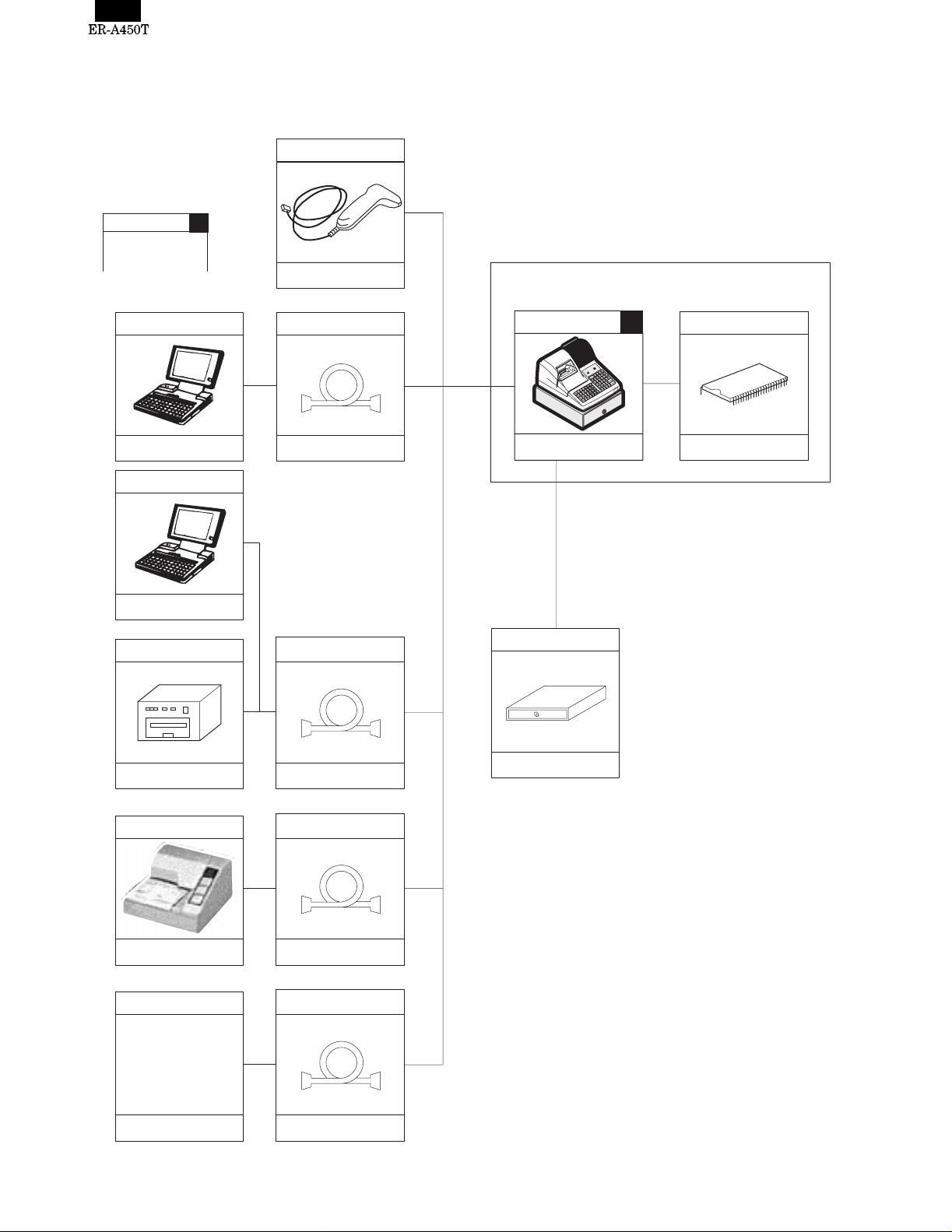

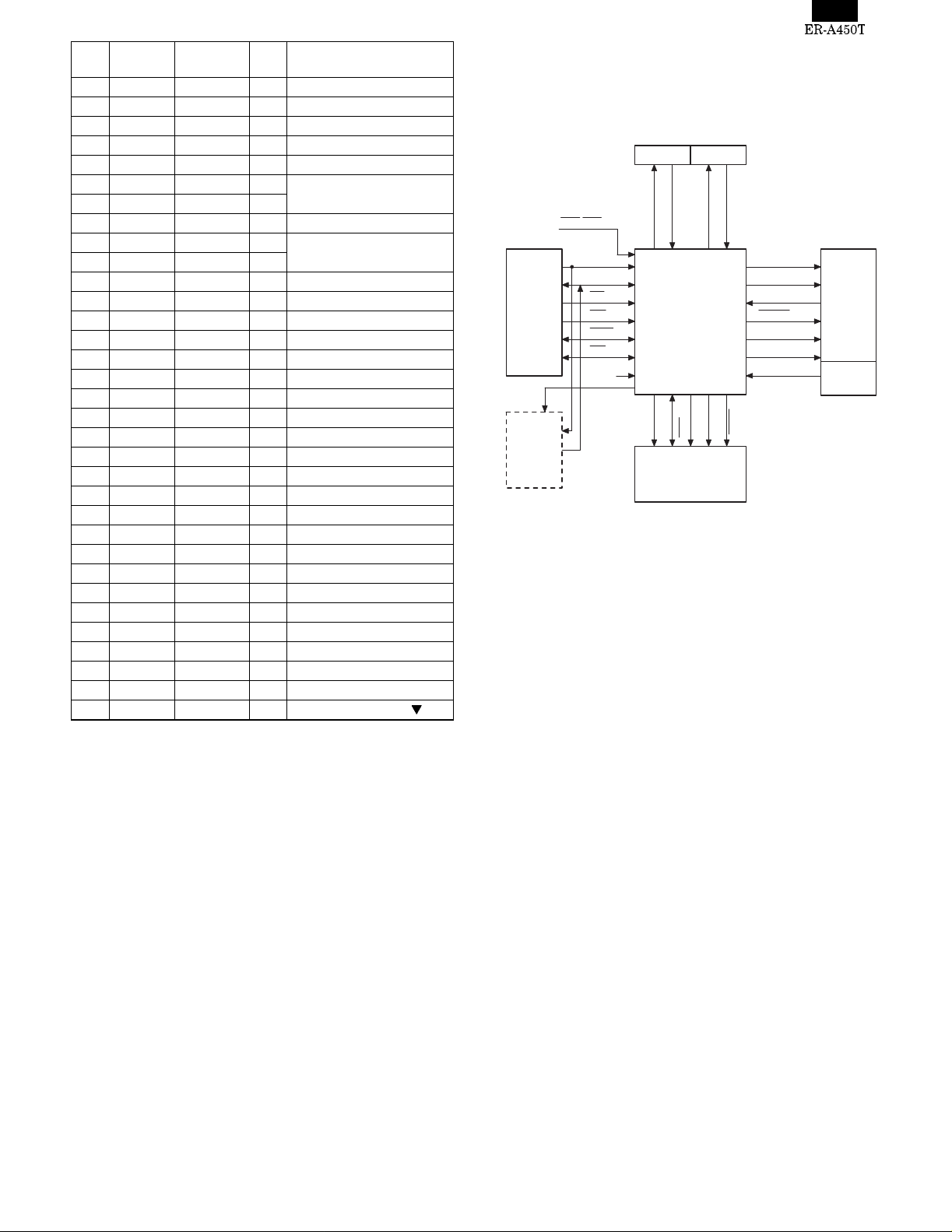

CHAPTER 2. OPTIONS

1. System configuration

LOCAL PURCHASE

(NOTE1)

This symbol sho ws

NEW MODEL

BARCODE READER

ER-A6HS1 or

LOCAL PURCHASE

COMPUTER

PC UTILITY

ER-02FD EXE

or

ER-01/02FD

LOCAL PURCHASE

CABLE

LOCAL PURCHASE

CABLE3.5 inch FDD

RS-232

2port

ER-A450T

MASTER MACHINE

ER-04DW

REMOTE DRAWER

ER-03RA

OPTION RAM

LOCAL PURCHASE

LOCAL PURCHASE

LOCAL PURCHASE

CABLESLIP PRINTER

LOCAL PURCHASE

CABLEPRINT DATA

Note : Only 2 peripherals max may be connected at any one time.

Fig. 1-1

2 – 1

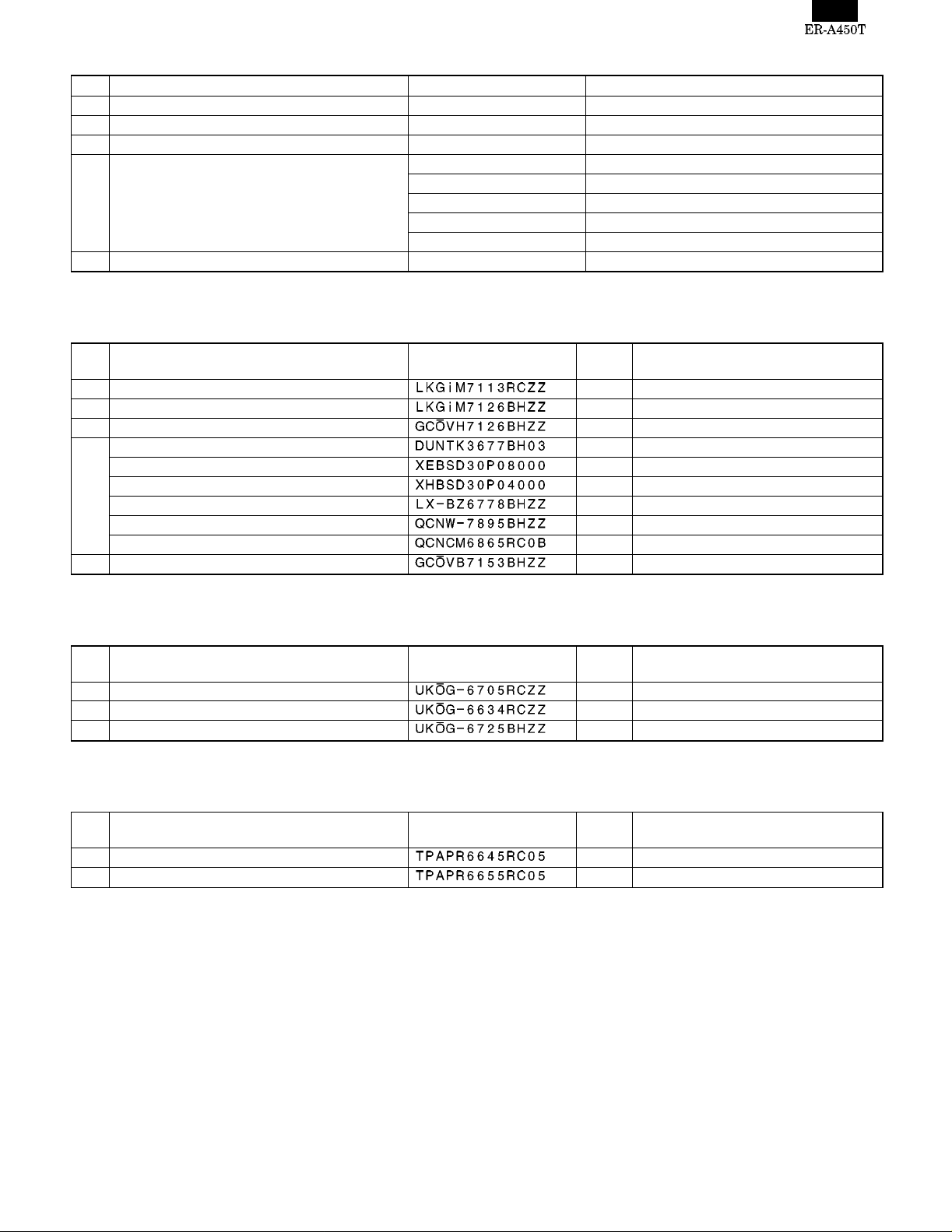

2. Options (SHARP only)

No. NAME MODEL DESCRIPTION

1 EXPANSION RAM CHIP ER-03RA 512K bytes RAM CHIP

2 REMOTE DRAWER ER-04DW

3 PRESETS LOADER ER-01FD/02FD FD unit

4 KEY TOP KIT ER-11KT7 1 × 1 KEY TOP UNIT

ER-12KT7 1 × 2 KEY TOP UNIT

ER-22KT7 2 × 2 KEY TOP UNIT

ER-11DK7G 1 × 1 DUMMY KEY KIT

ER-51DK7G 5 × 1 DUMMY KEY KIT

5 BARCODE READER ER-A6HS1

3. Service options

No. NAME PARTS CODE

1 SERVICE KEY

2 MODE KEY GRIP COVER

3 DRIP-PROOF KEYBOARD COVER

4 JOURNAL NEAR END SENSOR UNIT

Screw (Sensor unit – Top cabinet)

Screw (Sensor unit – Earth wire – Top cabinet)

Screw (Earth wire – Top cabinet)

Earth wire

Connector (2pin)

5 TEXT PRESET KEYBOARD COVER

4. Service tools

No. NAME PARTS CODE

1 RS-232 LOOP BACK CONNECTOR

2 KEY TOP REMOVER

32 × 2 KEY TOP INSTALLING JIG

5. Supplies

PRICE

RANK

AF

AL OP key only

BE Include the switch cover

BB Q’ty: 1

AA Q’ty: 1

AA Q’ty: 1

AA Q’ty: 1

AF Q’ty: 1

AA Q’ty: 1

BH

PRICE

RANK

BU

AX

BP

DESCRIPTION

DESCRIPTION

No. NAME PARTS CODE

1 Thermal roll paper

2 Thermal roll paper

2 – 2

PRICE

RANK

AY 5 roll/pack

BA 5 roll/pack (High preservation type)

DESCRIPTION

CHAPTER 3. SERVICE RESET AND MASTER RESET

1. SERVICE reset (Program Loop Reset)

Used to return the machine back to its operational state after a lockup has occurred.

Procedure

• Method 1

1) Unplug the AC cord from the wall outlet.

2) Set the mode switch to (SRV′) position.

3) Plug in the AC cord to the wall outlet.

4) Turn to (SRV) position from (SRV′) position.

• Method 2

1) Set the mode switch to PGM2 position.

2) Turn off the AC switch.

3) While holding down JOURNAL FEED key and RECEIPT FEED

key, Turn on the AC switch.

Note: When disassembling and reassembling always power up us-

ing method 1 only. Method 2 will not reset the CKDC8.

Note: SRV programming job#926-B must be set to "4" to allow PGM

program loop reset.

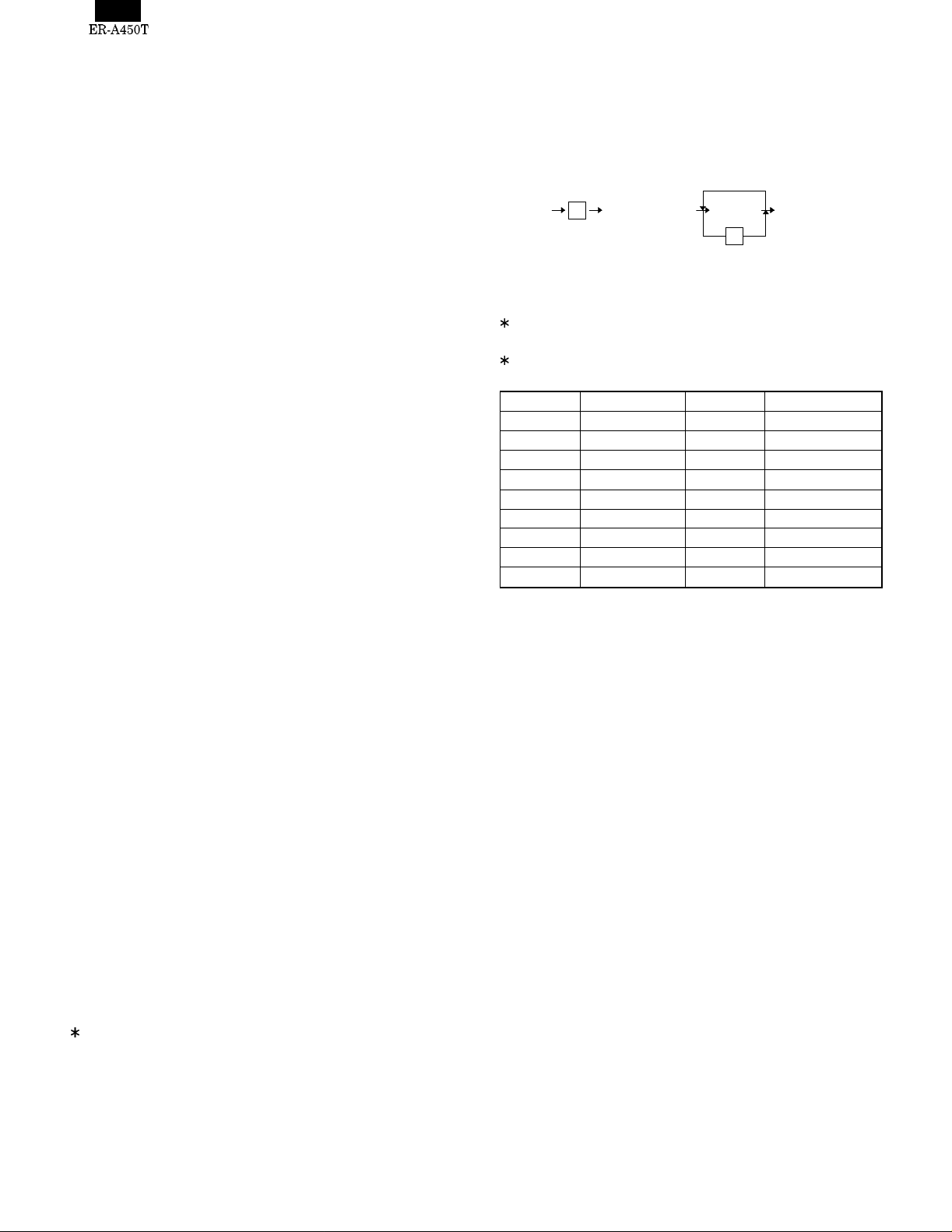

2. Master reset (Al l me mory clear)

There are two possible methods to perform a master reset.

• MRS-1

Used to clear all memory contents and return machine back to its

initial settings and return keyboard back to default keyboard layout.

[key setup procedure]

0

Disable

*2

Free key setup

complete.

*1

MRS-2

executed

NOTES:

1: When the 0 key is pressed, the key of the key number on display

is disabled.

2: Push the key on the position to be assigned. With this, the key of

the key number on display is assigned to that key position.

Key number Key name Key number Key name

1 Numeric key "0" 10 Numeric key "9"

2 Numeric key "1" 11 Numeric key "00"

3 Numeric key "2" 12 Numeric key "000"

4 Numeric key "3" 13 Decimal point key

5 Numeric key "4" 14 CL key

6 Numeric key "5" 15 @/FOR

7 Numeric key "6" 16 SBTL key

8 Numeric key "7" 17 CA/AT key

9 Numeric key "8"

Key position set Free key

0

Procedure

1) Unplug the AC cord from the wall outlet.

2) Set the MODE switch to the (SRV′) position.

3) Plug in the AC cord to the wall outlet.

4) While holding down JOURNAL FEED key, t urn to (SRV) position

from (SRV′) position.

• MRS-2

Used to clear all memory and keyboard contents.

This reset returns all programming back to defaults. The keyboard

must be entered by hand.

This reset is used if an application needs different keyboard layout

other than that supplied by a normal MRS-1.

Procedure

1) Unplug the AC cord from the wall outlet.

2) Set the MODE switch to the (SRV′) position.

3) Plug in the AC cord to the wall outlet.

4) While holding down JOURNAL FEED key and RECEIPT FEED

key, turn to (SRV) position from (SRV′) position.

5) Key position assignment:

After the execution of MRS-2, only the RECEIPT FEED and

JOURNAL FEED keys can remain effective on key assignment.

Any key can be assigned on any key position on the main keyboard.

3 – 1

CHAPTER 4. HARDWARE DESCRIPTION

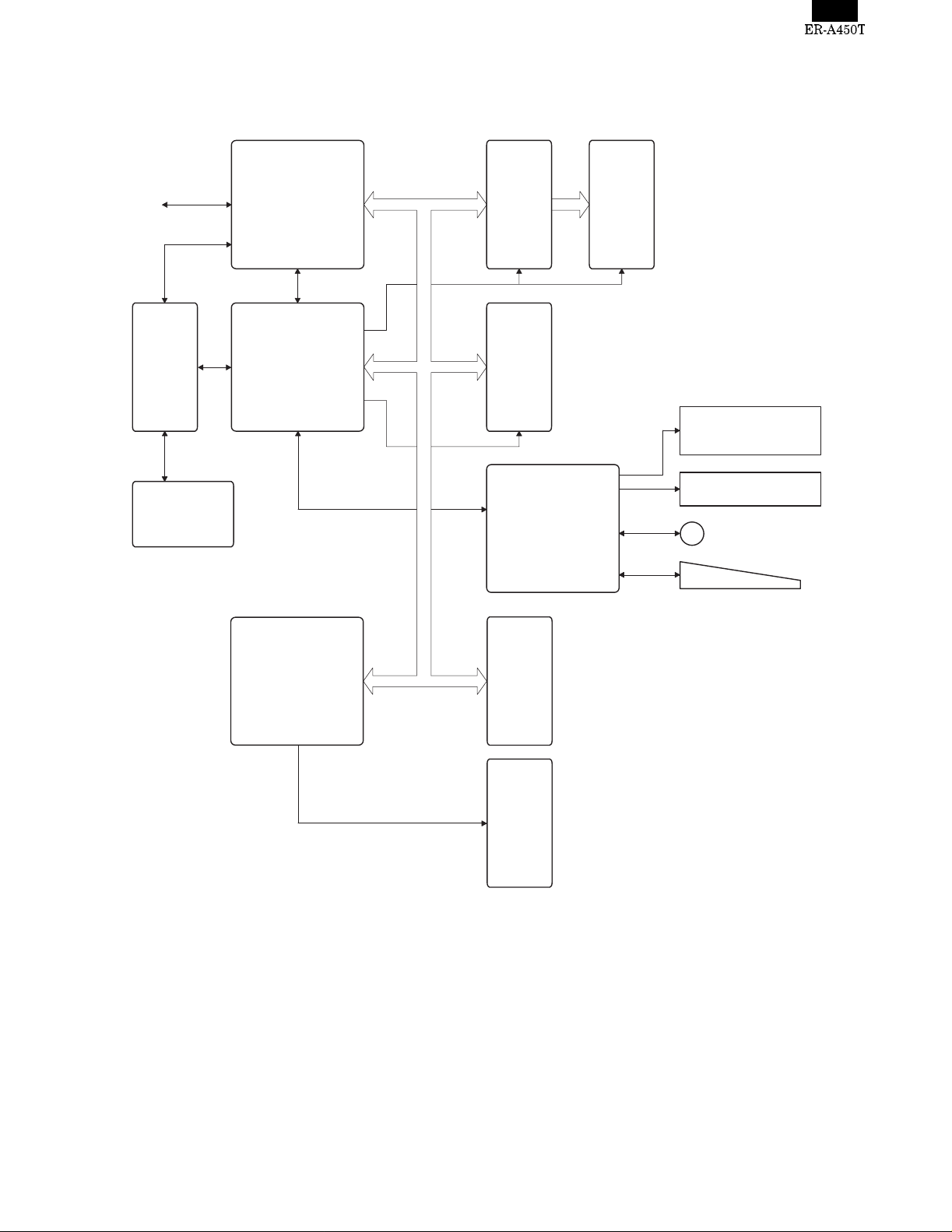

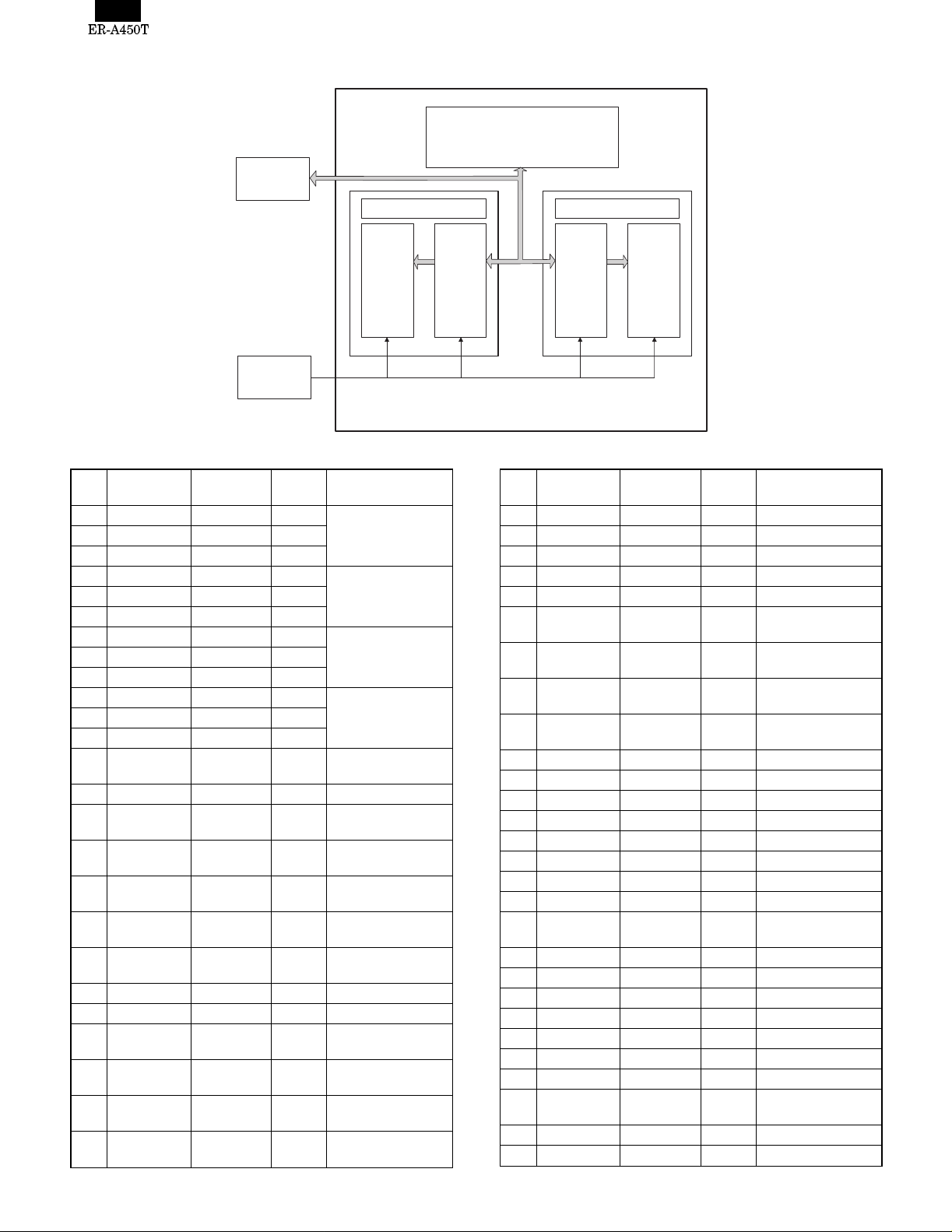

1. Hard ware block diagram

DRAWER

TPRC1

PRINTER

PR-45M

CPU

GATE ARRAY

MPCA7

STANDARD

RAM1

256KB

STANDARD

ROM

512KB

CKDC8

OPTIONAL

RAM2

512KB

ER-03RA:512KB

OPERATER DISPLAY

1 LINE

7SEG 10DIG

CUSTOMER DISPLAY

1 LINE

7SEG 7DIG

SWITCH

KEY BOARD

OPC2

RS232

I/F

1 ports

RS232

I/F

CH1

Fig. 1-1

4 – 1

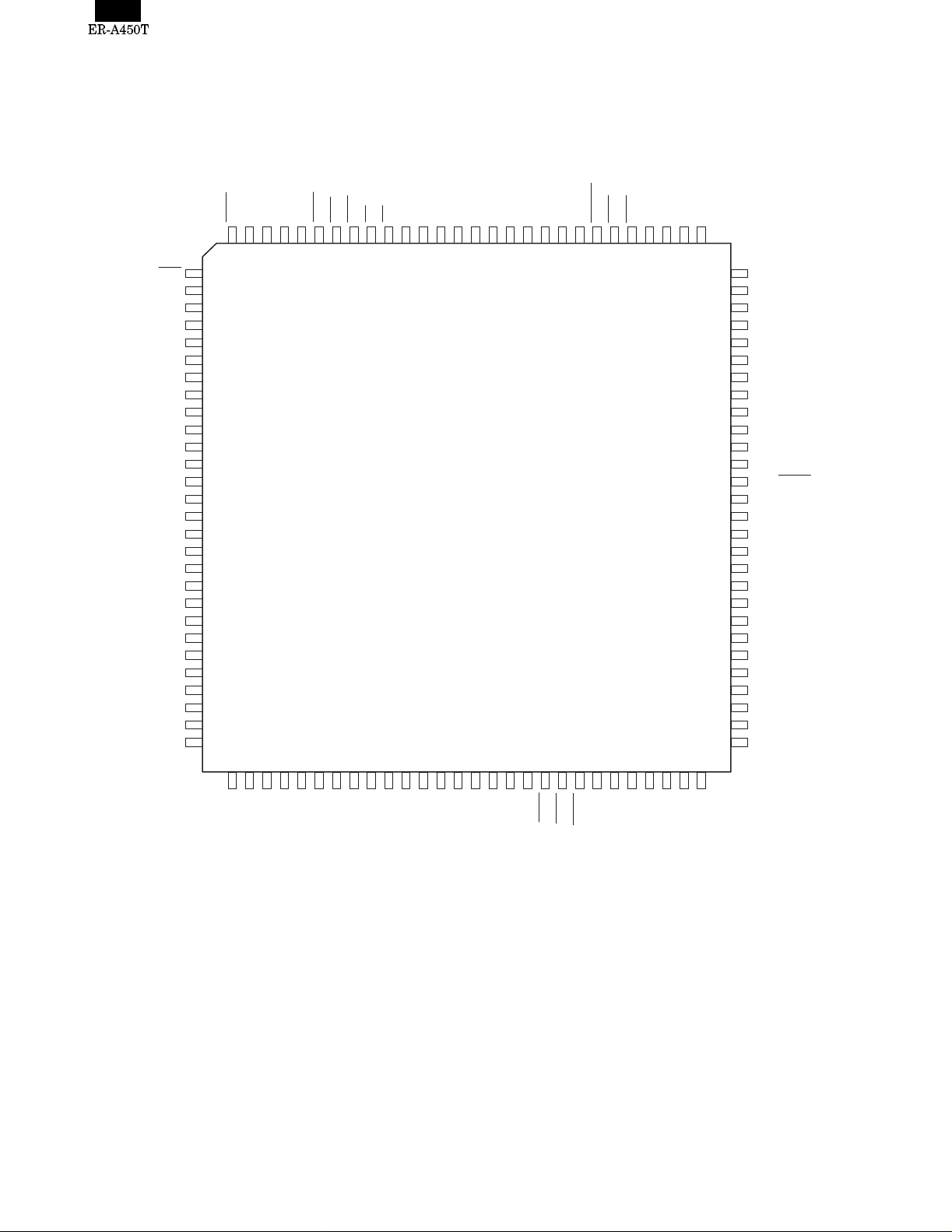

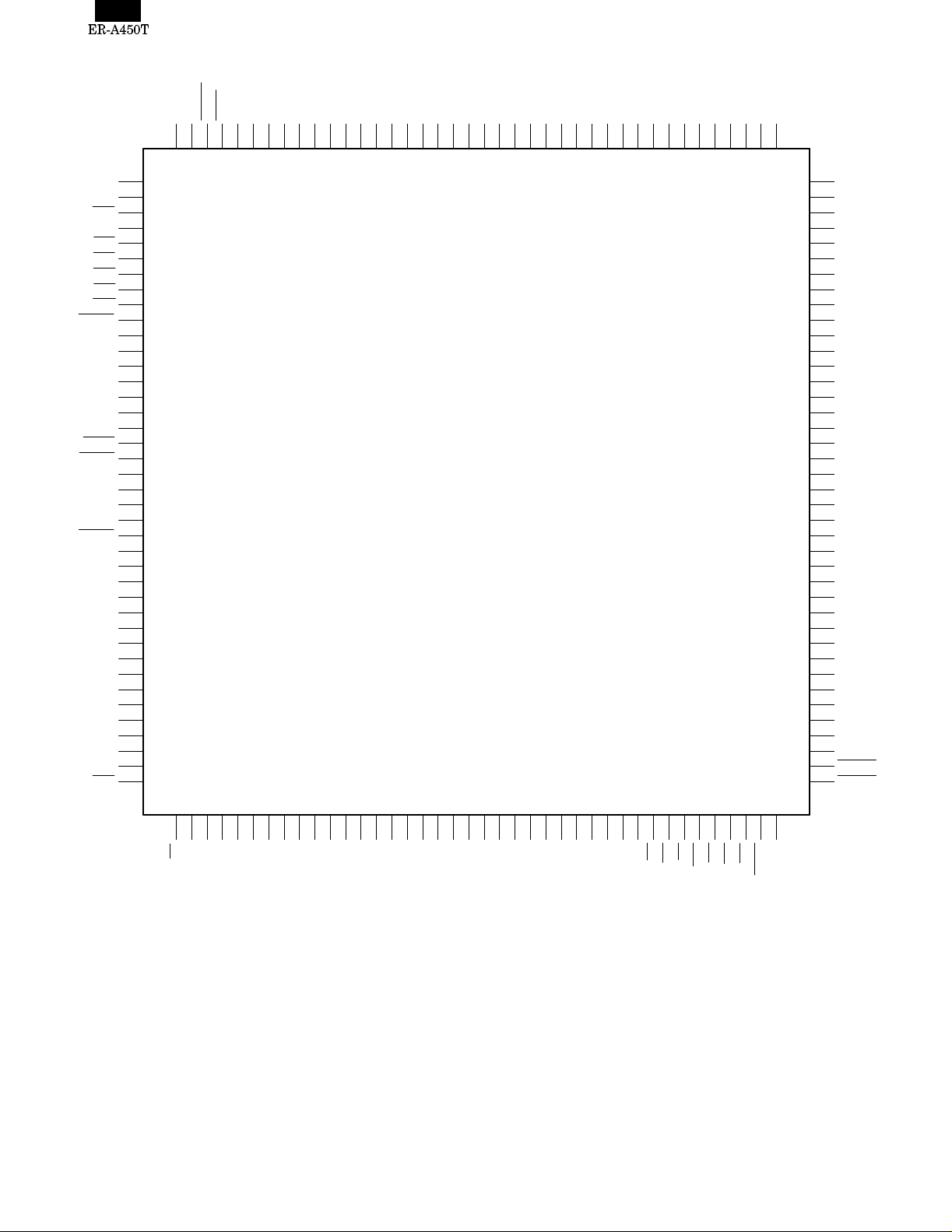

2. Description of main LSI’s

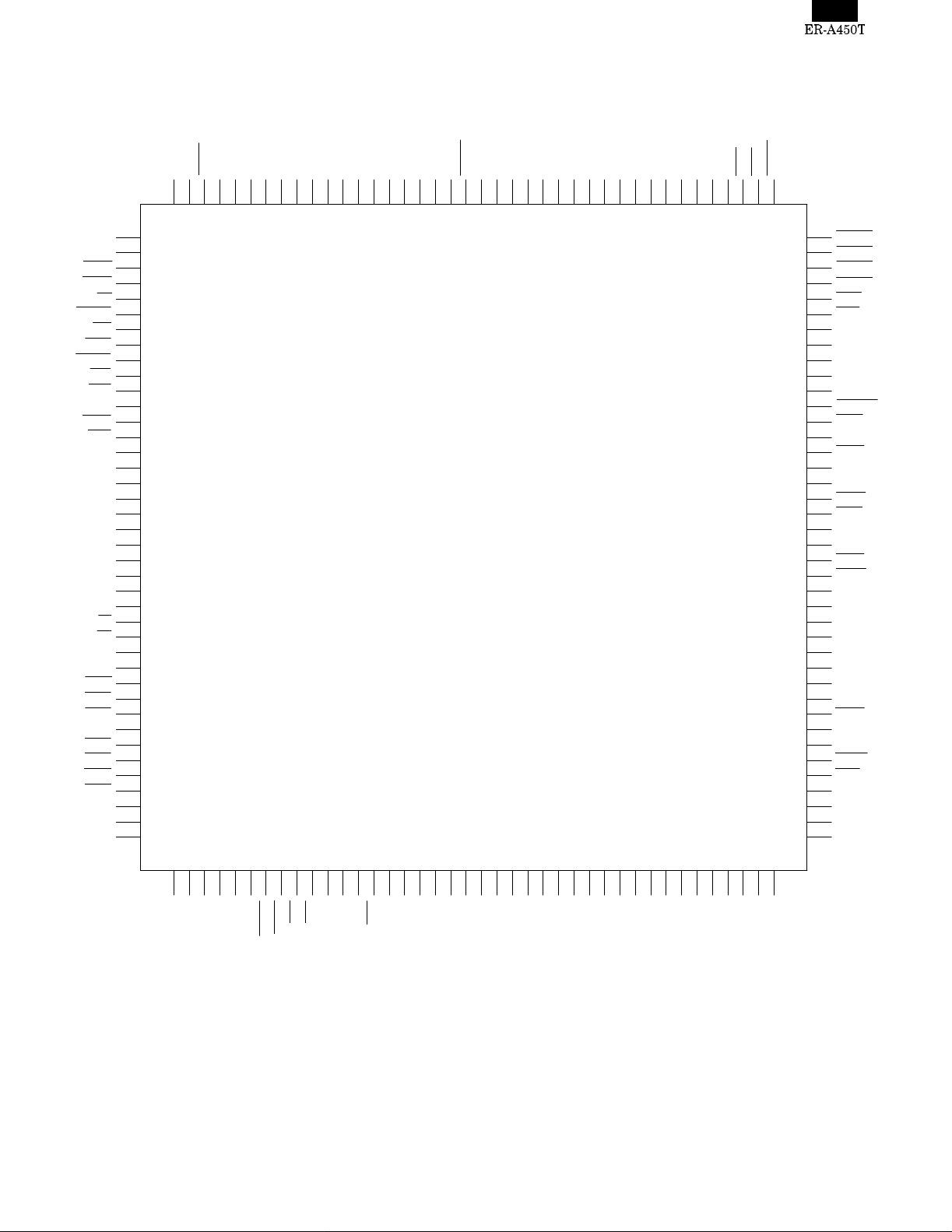

2-1. CPU (HD6415108-10)

1) Pin configuration

MD2

MD1

STBY

MD0

VCC

LWR

RFSH

HWR

RD

AS

X

E

VSS

XTAL

VSS

EXTAL

TXD2

TXD1

RXD2

RXD1

SCK2

UASKC

IRQ1

IRQ0

VCC

AN3

AVCC

AN2

RES

NMI

VSS

P10

P11

P12

P13

P14

P15

P16

P17

D0

D1

D2

D3

D4

D5

D6

D7

VSS

A0

A1

A2

A3

A4

A5

A6

A7

112

111

110

109

108

107

106

105

104

103

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

293031323334353637383940414243444546474849505152535455

102

999897969594939291908988878685

101

100

56

84

83

82

81

80

78

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

AN1

AN0

AVSS

VSS

P67

P66

P65

P64

P63

P62

P61

P60

P57/STOP

P56

P55

P54

P53

P52

P51

P50

VSS

P47

P46

P45

P44

P43

P42

P41

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

VSS

A20

HD6415108-10 pin configuration

Fig. 2-1

4 – 2

A21

A22

A23

VSS

WAIT

BACK

P33

BREQ

P34

P35

P36

P37

VCC

P40

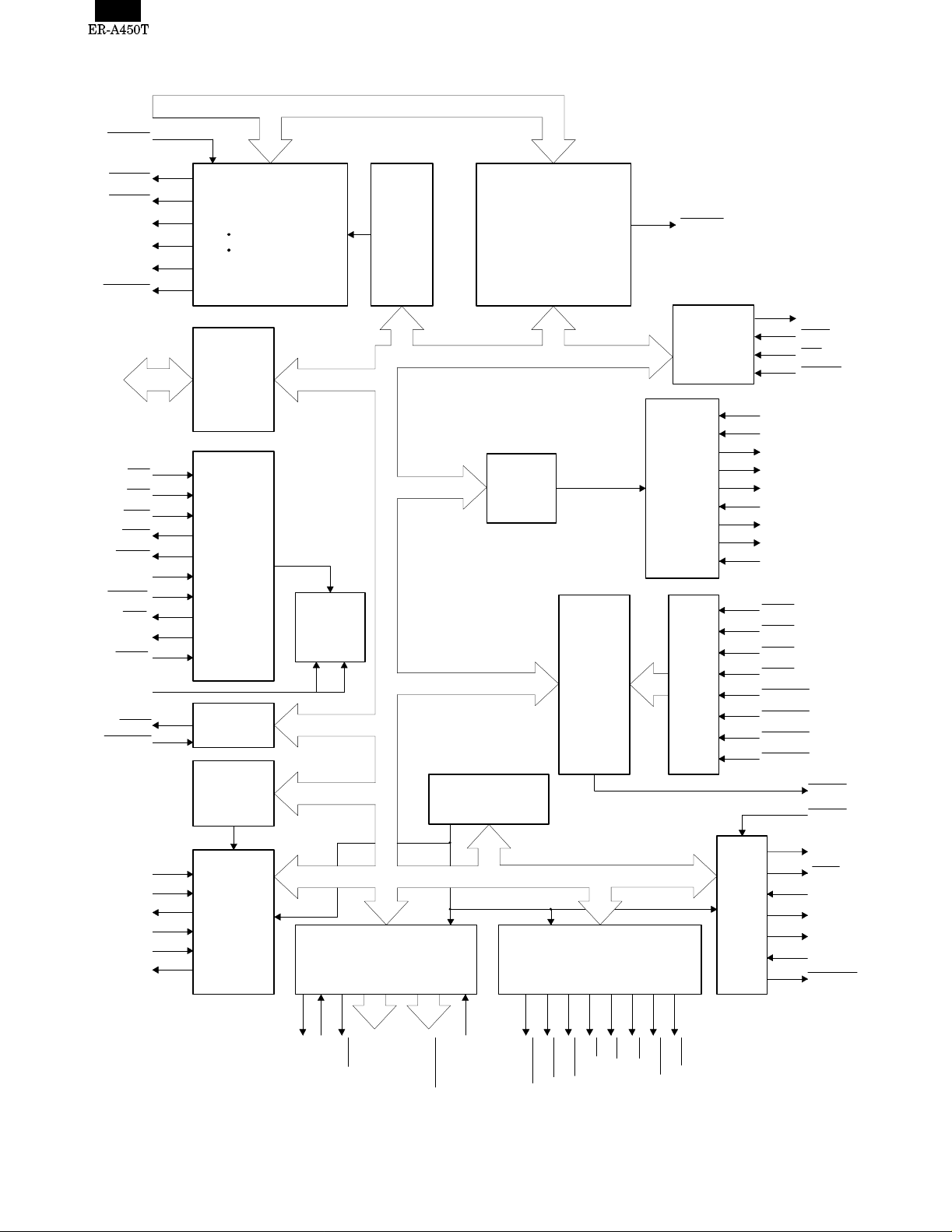

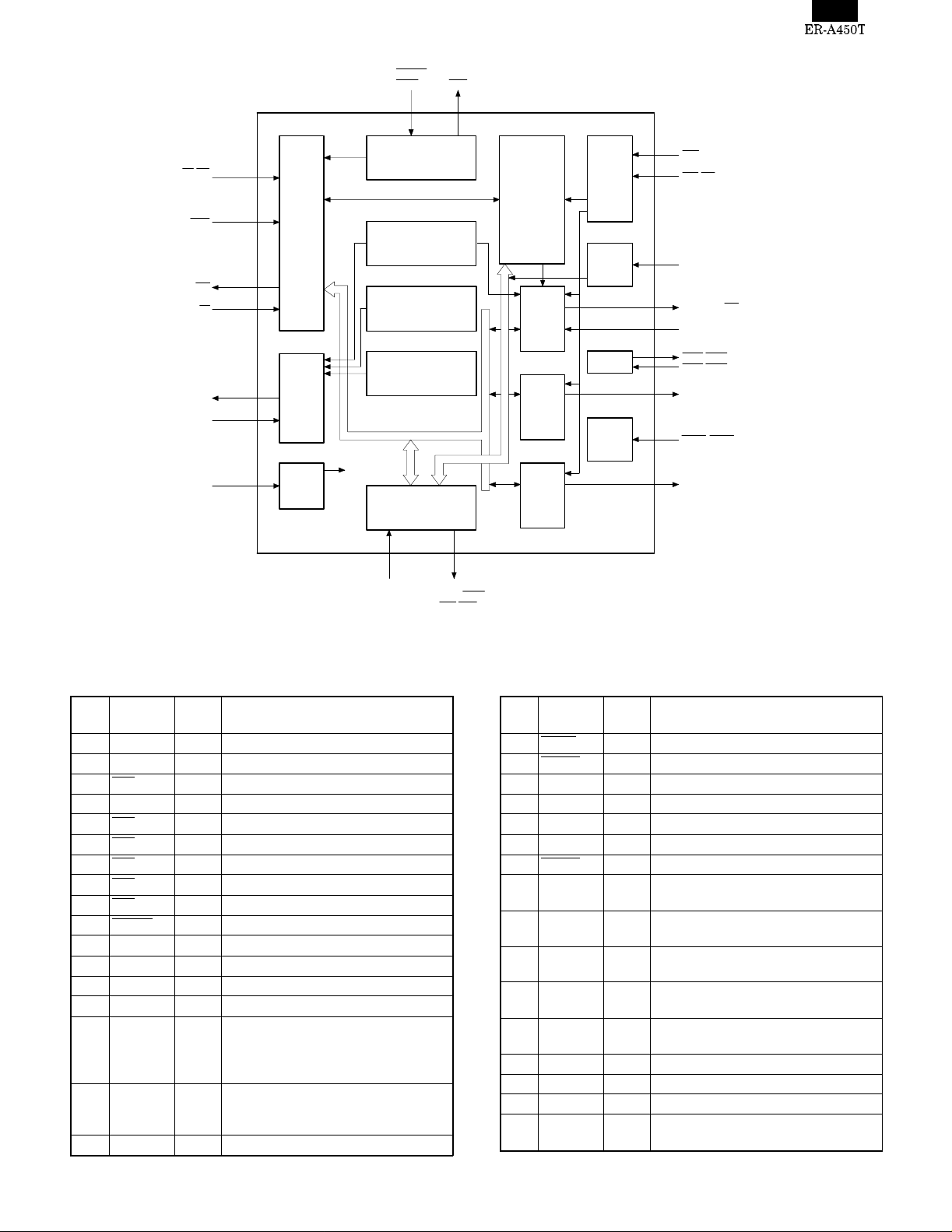

2) Block diagram

EXTAL

XTAL

X

E

MD2

MD1

MD0

RES

STBY

NMI

AS

RD

HWR

LWR

RFSH

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AVCC

AVSS

D7D6D5D4D3

Data bus Port 1

Clock

oscillator

Watch

dog timer

H8/500 CPU DTC

Interruption controller

Refresh controller

Wait state

controller

A/D convertor

D2

P17

D1

D0

16bit free running

timer x 2ch

Serial

communication

interface x 2ch

P16

P15

8bit timer

P14

P13

P12

P11

Data bus (Lower)

P10

P27/A23

P26/A22

P25/A21

P24/A20

Port 2

P23/A19

P22/A18

P21/A17

P20/A16

A15

A14

A13

A12

A11

Data bus (Upper)

Address bus

A10

A9

A8

A7

A6

Address bus

A5

A4

A3

A2

A1

A0

P37

P36

P35

P34

Port 3Port 4

P33

BREQ

BACK

WAIT

P47

FTI2

P45

FTI1

P43

P42

P41/TMCI

P40

Port 5Port 6Port 7Port 8

TXD2

RXD2

TXD1

RXD1

SCK2

IRQ2

IRQ1

IRQ0

P73

AN2

AN1

Fig. 2-2

4 – 3

AN0

P67

P66

RS/P65

RR/P64

CS/P62

CD/P63

DR/P61

ER/P60

STOP/P57

P56

FMRS

P54

P53

P52

P51

P50

3) Pin description

PIN

SYMBOL

No.

/RES /RESET

1

NMi NMi

2

3 VSS VSS GND

4 P10 ERC OUT EVENT READ CANCEL (to CKDC)

5 P11 LDRQ OUT LOAD REQUEST (to CKDC)

6 P12 /SHEN IN SHIFT ENABLE (from CKDC)

7 P13 /FRES OUT FISCAL MEMORY RESET (Nu)

8 P14 BUSY IN FISCAL MEMORY BUSY (Nu)

9 P15 /RDY IN FISCAL MEMORY READY (Nu)

10 P16 PDS IN POP-UP DISPLAY SENSOR (Nu)

11 P17 IN GND

12 D0 D0 I/O DATA BUS 0

13 D1 D1 I/O DATA BUS 1

14 D2 D2 I/O DATA BUS 2

15 D3 D3 I/O DATA BUS 3

16 D4 D4 I/O DATA BUS 4

17 D5 D5 I/O DATA BUS 5

18 D6 D6 I/O DATA BUS 6

19 D7 D7 I/O DATA BUS 7

20 VSS VSS GND

21 A0 A0 OUT ADDRESS BUS 0

22 A1 A1 OUT ADDRESS BUS 1

23 A2 A2 OUT ADDRESS BUS 2

24 A3 A3 OUT ADDRESS BUS 3

25 A4 A4 OUT ADDRESS BUS 4

26 A5 A5 OUT ADDRESS BUS 5

27 A6 A6 OUT ADDRESS BUS 6

28 A7 A7 OUT ADDRESS BUS 7

29 A8 A8 OUT ADDRESS BUS 8

30 A9 A9 OUT ADDRESS BUS 9

31 A10 A10 OUT ADDRESS BUS 10

32 A11 A11 OUT ADDRESS BUS 11

33 A12 A12 OUT ADDRESS BUS 12

34 A13 A13 OUT ADDRESS BUS 13

35 A14 A14 OUT ADDRESS BUS 14

36 A15 A15 OUT ADDRESS BUS 15

37 VSS VSS GND

38 A16 A16 OUT ADDRESS BUS 16

39 A17 A17 OUT ADDRESS BUS 17

40 A18 A18 OUT ADDRESS BUS 18

41 A19 A19 OUT ADDRESS BUS 19

42 A20 A20 OUT ADDRESS BUS 20

43 A21 A21 OUT ADDRESS BUS 21

44 A22 A22 OUT ADDRESS BUS 22

45 A23 A23 OUT ADDRESS BUS 23

46 VSS VSS GND

47 /WAIT /WAIT IN Wait signal from MPCA

48 /BACK /BACK OUT Bus control request acknowledge

49 /BREQ /BREQ IN Bus control request

50 P33 DOPS IN Drawer open sensor signal

51 P34 /DR0 OUT Drawer open drive signal

52 P35 /DR1 OUT Option drawer 1 drive signal

53 P36 NU IN (Nu) GND

54 P37 NU IN (Nu) GND

55 VCC VCC +5V

56 P40 /IFV IN (Nu) pull-up

P41 /PTMG

57

58 P42 /TOF IN (Nu) pull-up

59 P43 /BOF IN (Nu) pull-up

SIGNAL

NAME

IN/

OUT

RESET INPUT from CKDC WUTH

IN

BUFFER

NON-MASKABLE INTERRUPT

IN

INPUT FOR SSP INTERRUPT INPUT

Printer (PR-45) timing signal from

IN

MPCA

FUNCTION

PIN

SYMBOL

No.

P44 /PRST

60

61 P45 /NEJ IN Near END signal journal

62 P46 NU IN (NU) GND

63 P47 /NER IN Near END signal receipt

64 VSS VSS GND

65 P50 TRG1 OUT Nu (GND)

66 P51 /PSTOP OUT Nu (GND)

67 P52 /CKDCR2 OUT Nu (GND)

68 P53 OPDS IN Nu (GND)

69 P54 FVPON OUT Nu (GND)

70 P55 FMRS IN Nu (GND)

71 P56 /SLIPLMP OUT Nu (GND)

72 P57 /STOP OUT Nu (GND)

P60 /ERS

73

74 P61 /DRS IN DR signal for RS232 (Data set Ready)

75 P62 /CSS IN CS signal for RS232 (Clear to Send)

76 P63 /CDS IN CD signal for RS232 (Carrier Detect)

P64 /RR

77

P65 /RSS

78

79 P66 (/RI), /CI IN CI signal for RS232 (Calling Indicator)

80 P67 HP IN Nu (GND)

81 VSS VSS GND

82 AVSS AVSS IN GND

83 AN0 Vrf IN Vrf

84 AN1 VHTEST IN VH Test input

85 AN2 VPTEST IN +24V test input

86 AN3 TM IN Thermal head thermistor level test

87 AVCC AVCC IN +5V

88 VCC VCC +5V

89 P80 /iRQ0 IN Interrupt signal 0 from MPCA

P81 /iRQ1

90

91 P82 /iRQ2 IN Interrupt signal (Nu) pull-up

92 P83 SCK2 OUT CKDC & FMC i/F sync shift clock

93 P84 RXD IN RS232C RECEIVE DATA

94 P85 TXD OUT RS232C SEND DATA

P86 RXD2

95

P87 TXD2

96

97 VSS VSS GND

98 EXTAL EXTAL IN X-TAL (19.66MHz)

99 XTAL XTAL IN X-TAL (19.66MHz)

100 VSS VSS GND

101 φφ OUT System clock (9.83MHz)

102 E OUT E clock (NU)

103 /AS /AS OUT Address strobe

104 /RD /RD OUT Read

105 /HWR /WR OUT Write

106 /LWR OUT Nu

107 /RFSH /RFSH OUT Refresh cycle (NU)

108 VCC VCC +5V

109 MD0 MD0 IN +5V (MODE 3)

110 MD1 MD1 IN +5V (MODE 3)

111 MD2 MD2 IN GND (MODE 3)

112 /STBY /STBY IN +5V (Nu)

SIGNAL

NAME

(/RSRQ)

IN/

OUT

Printer (PR-45) Reset signal from

IN

MPCA

ER signal for RS232 (Equipment

OUT

Ready)

RR signal for RS232 (Ready to

OUT

Receive) (Nu)

RS signal for RS232 (Request to

OUT

Send)

Interrupt signal from OPTION PWB

IN

CKDC, Fiscal memory unit I/F shift

IN

input data

CKDC, Fiscal memory unit I/F shift

OUT

output data

FUNCTION

4 – 4

2-2. G.A (MPCA7)

1) Pin configuration

160 NU

1RF

2JF

3PCUT

4FCUT

5VF

6STAMP

SLF

PHAI

7

8SLRS

9SLMTD

10RES

11TRG

12TRG

13POFF

14INT1

15HTS1

16SCK1

17STH1

18NU

19NU

20VCC

21GND

22NU

23VRESC

24SLTMG

25SLRST

26AS

27RD

28WR

29

30SDT7

31SDT6

32SDT5

33GND

34SDT4

35SDT3

36SDT2

37SDT1

38D0

39D1

40D2

41D342GND

159 DOTEN

158 TWAIT

157 NU

43

44

156 NU

155 NU

154 NU

153 NU

45D646D747SSPRQ

48

152 STH2

151 SCK2

150 HTS2

149 SLMTR

148 SLMTS

147 SLMTD

146 RJMTR

145 RAS3

144 NU

143 GND

142 VCC

141 ASKRX

139 NU

138 NU

137 RJMTD

135 DT5

134 DT6

133 DT7

132 GND

131 DT1

130 DT2

129 DT3

127 RJTMG

126 RJRST

125 RAS1

124 RAS2

123 ROS2

122 ROS1

140 NU

136 RJMTS

128 DT4

121 OPTCS

120 EXINT0

119 EXINT1

118 EXINT2

117 EXINT3

116 WRO

115 RDO

114 RA15

113 RA16

112 GND

111 RA17

110 RA18

109 EXWAIT

108 WAIT

107 NU

106 MCR1

105 NU

104

103 RCKX

102 IRRX

101 GND

100 VCC

DAX1

99

UATX

98 UARX

97

UASCK

96

IRTX

95 RCO

94 NU

93 NU

92 NU

91 NU

90 MA15

89 TEST

88 MD0

87 MD1

86 IPLON

85 INT4

84 PRST

83 PTMG

82 TRGI

81 A23

49

50

51RXDI

52TXDI

53SCKI

54IRQ0

55A0

56A1

57A2

58A3

59A4

60A5

62VCC

63A6

64A7

61GND

65A8

66A9

69A12

67A10

68A11

70A13

71A14

72A15

74A17

75A18

76A19

77A20

78A21

79A22

73A16

80NU

D4

D5

INT2

RESET

INT3

GATE ARRAY (LZ9AH39)

MPCA7

Fig. 2-3

4 – 5

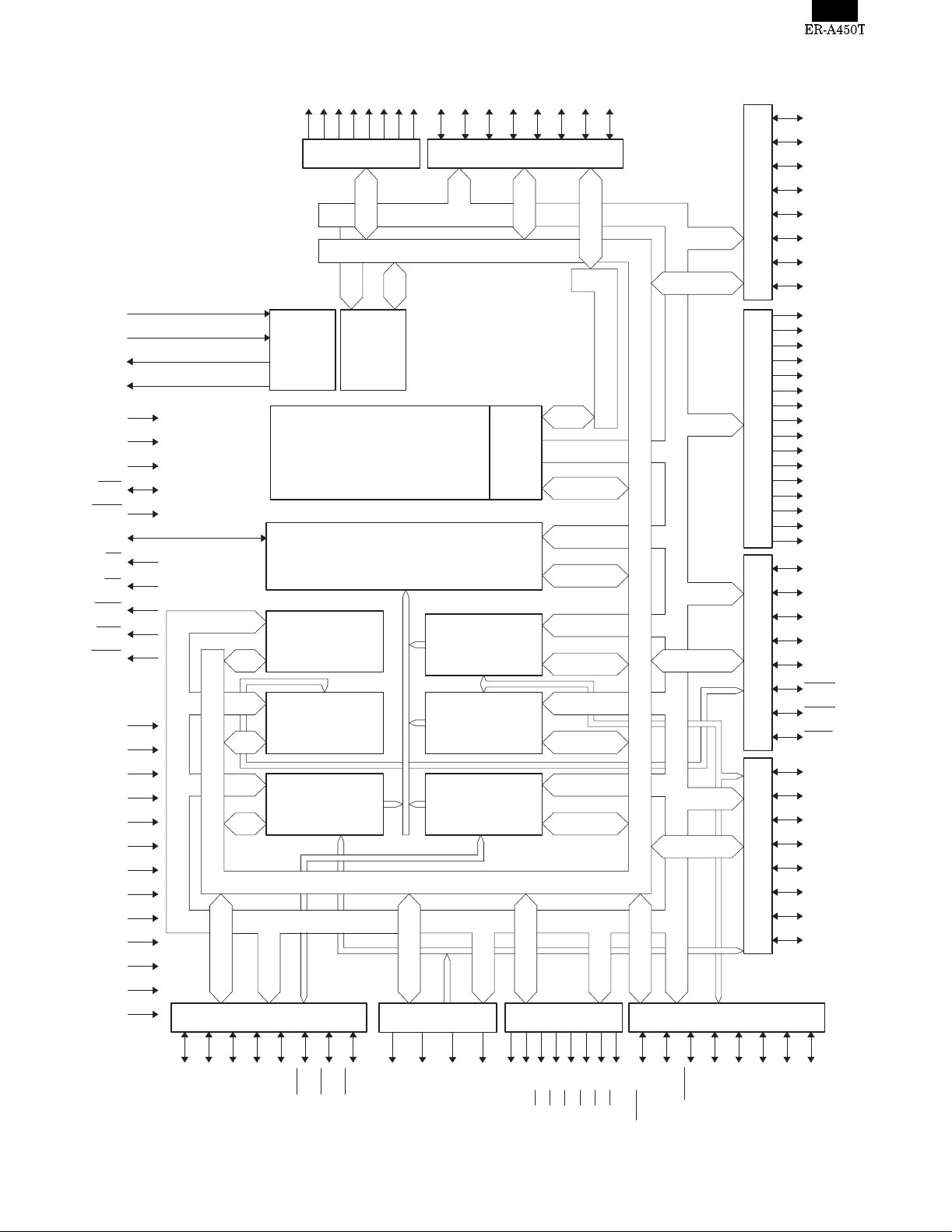

2) Block diagram

A23~A0

IRLON

ROS1

ROS2

RAS1

RAS2

RAS3

OPTCS

D0~D7

AS

RD

WR

RDO

WRO

Φ

RESET

RES

VRESC

POFF

MD0

MD1

WAIT

EXWAIT

Address decode

External CS

Internal CS

Buffer

Read/write

control

WAIT

control

Φ

Divider

RASEL

Image

control

SSP comparison register

BAR.

CHS

serial select

INTO

control

SSPRQ

I/R Control

Multiplexer

IRTX

IRRX

RCI

ASKRX

TXDI

SCKI

RXDI

HTS1

SCK1

STH1

HTS2

SCK2

STH2

INT4

INT1

INT2

INT3

EXINT0

EXINT1

EXINT2

EXINT3

CAPS

select

RJRST

SLRST

*PRST

RJTMG

SLTMG

PTMG

* Output selection with CAPS.

PRST/PTMG.

Print gate

Print pulse control

TRG

TRG

DOTEN

Print mode PMD

IRQ0

TEST

MTD

MTD

Motor

drive

Printer control port

DT1~9

SDT1~7

TRGI

PCUT

STAMP

FCUT

JF

RF

VF

SLF

SLRS

RJMTR

SLMTD

SLMTS

SLMTR

SLMTD

Fig. 2-4

4 – 6

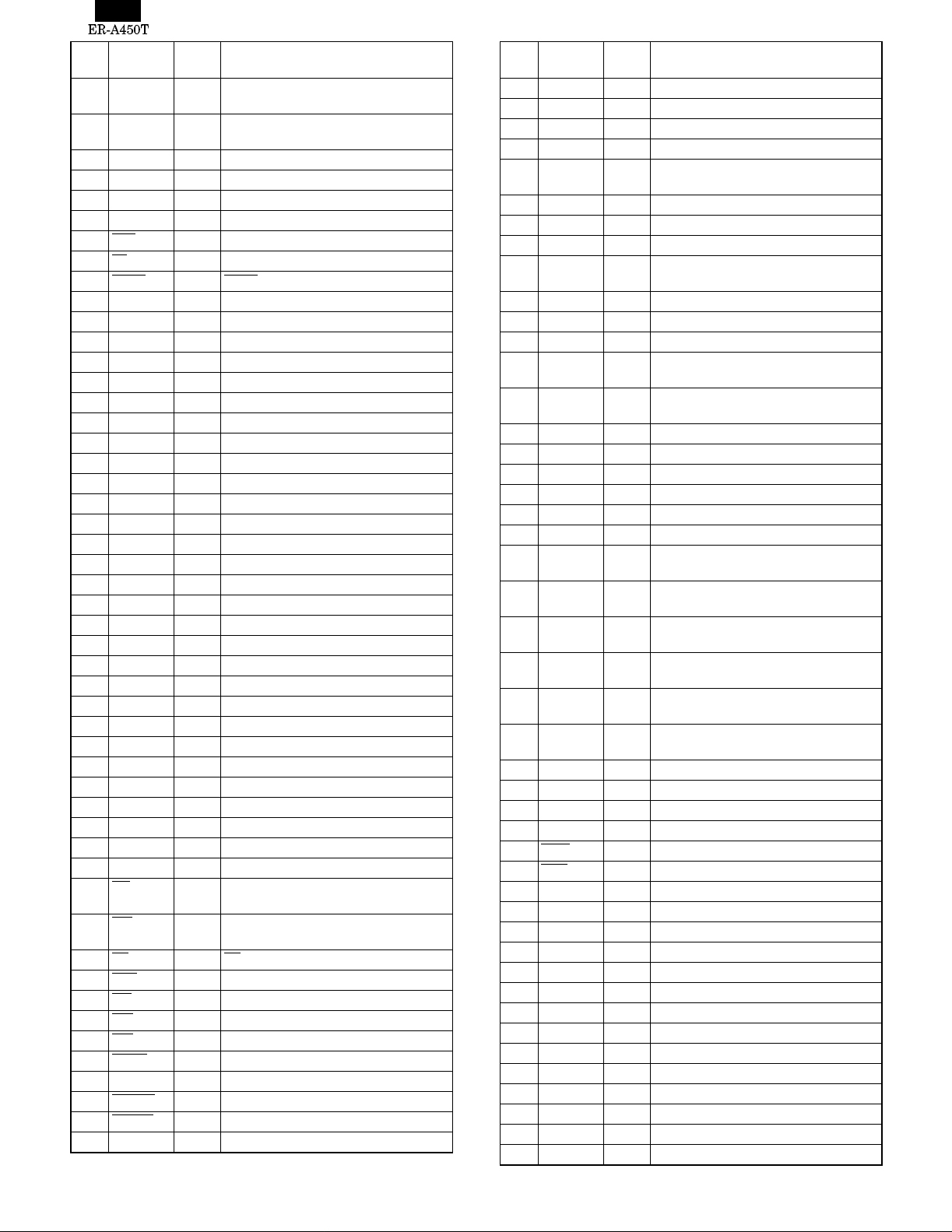

3) Pin description

Pin

Signal

No.

name

1

RF

2

JF

3

PCUT

4

FCUT

5

VF

6

STAMP

7

SLFS

8

SLRS

9

SLMTD

10

RES

11

TRG

12

TRG

13

POFF

14

INT1

15

HTS1

16

SCK1

17

STH1

18

RAS VZ

19 — — Nu

20

VCC

21

GND

22

INTMCR

23

VRESC

24

SLTMG

25

SLRST

26

AS

27

RD

28

WR

29

φ

30

SDT7

31

SDT6

32

SDT5

33

GND

34

SDT4

35

SDT3

36

SDT2

37

SDT1

38

D0

39

D1

40

D2

41

D3

42

GND

43

D4

44

D5

45

D6

46

D7

47

SPRQ

48

RESET

49

SHEN

50

INT3

In/

Out

Out Receipt side paper feed solenoid (NU)

Out Journal side paper feed solenoid (NU)

Out Printer partial cut signal (NU)

Out Printer auto cut signal (NU)

Out Multi line validation paper feed (NU)

Out Printer stamp signal (NU)

Out Slip printer paper feed singnal (NU)

Out Slip printer release signal (NU)

Out Slip printer motor drive signal (NU)

Out Peripheral output reset

Out Dot head trigger signal (NU)

Out Dot head trigger signal (NU)

In Power off signal input

In (NU)

Out 8 bit serial port output (for CKDC8)

Out Serial port shift clock output (for CKDC8)

In 8 bit serial port input (for CKDC8)

— Chip select (NU)

—+5V

—GND

— Interrupt (NU)

Out

In Slip printer timing signal (NU)

In Slip printer reset signal (NU)

In Address strobe

In Read strobe

In Write strobe

In (φ) System clock (9.83 MHz)

Out

Out

Out

—GND

Out

Out

Out

Out

I/O Data bus 0

I/O Data bus 1

I/O Data bus 2

I/O Data bus 3

—GND

I/O Data bus 4

I/O Data bus 5

I/O Data bus 6

I/O Data bus 7

Out SSP interrupt request to CPU

In MPCA reset

In Shift enable from CKDC8

In Interrupt signal (Nu)

Function

Turns active when reset and power

down is met

Slip printer printhead drive signal (dot7)

(NU)

Slip printer printhead drive signal (dot6)

(NU)

Slip printer printhead drive signal (dot5)

(NU)

Slip printer printhead drive signal (dot4)

(NU)

Slip printer printhead drive signal (dot3)

(NU)

Slip printer printhead drive signal (dot2)

(NU)

Slip printer printhead drive signal (dot1)

(NU)

Pin

No.

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

Signal

name

RXD2

TXD2

SCK2

IRQ0

A0

A1

A2

A3

A4

A5

GND

VCC

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

LCDC

A23

TRGI

PTMG

PRST

RDY

IPLON

MD1

MD0

TEST

MA15

MA18

MA19

RCVRDY1

RCVRDY2

RC0

IRTX

UASCK

UARX

UATX

VCC

GND

IRRX

RCI

DAX1

DAX2

MCR1

In/

Out

Out 8 bit serial port output to CPU

In 8 bit serial port input from CPU

In Serial port shift clock input from CPU.

Out Interrupt request to CPU

In Address bus 0

In Address bus 1

In Address bus 2

In Address bus 3

In Address bus 4

In Address bus 5

—GND

—+5V

In Address bus 6

In Address bus 7

In Address bus 8

In Address bus 9

In Address bus 10

In Address bus 11

In Address bus 12

In Address bus 13

In Address bus 14

In Address bus 15

In Address bus 16

In Address bus 17

In Address bus 18

In Address bus 19

In Address bus 20

In Address bus 21

In Address bus 22

— LCD CS (NU)

In Address bus 23

In Dot pulse control/drive signal (NU: GND)

Out Printer timing signal to CPU

Out Printer reset signal to CPU

In Ready from FMC unit

In To option connector (NU) +5V

In Mode select input (GND)

In Mode select input (GND)

In +5V

— Image address 15

—Nu

—Nu

—Nu: +5V

—Nu: +5V

Remote control encord signal for CPU

—

(NU)

— I/R output for LED (NU)

— I/R serial data shift clock (NU)

— I/R serial data for CPU (NU)

— I/R serial data from CPU (NU) +5V

—+5V

—GND

— I/R input from I/R unit (NU) +5V

— I/R input from I/R unit (NU) +5V

— System clock (NU)

—Nu

—Nu

Function

4 – 7

Pin

No.

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

Signal

name

MCR2

WAIT

EXWAIT

RA18

RA17

GND

RA16

RA15

RDO

WRO

EXINT3

EXINT2

EXINT1

EXINT0

OPTCS

ROS1

ROS2

RAS2

RAS1

RJRST

RJTMG

DT4

DT3

DT2

DT1

GND

DT7

DT6

DT5

MTD

MTD

DOT9

DOT8

SYNC

ASKRX

VCC

GND

In/

Out

—Nu

Out Wait request signal

External wait control input signal (NU)

In

+5V

Out Nu

Out Nu

— GND

Out Nu

Out Nu

Out Expansion RD signal

Out Expansion WR signal

In RS232C /CD interrupt

In Option PWB (PULL UP)

In RS232C /CI interrupt

In Option PWB (PULL UP)

Chip select base signal for expansion

Out

option

Out ROM 1 chip select signal

Out ROM 2 chip select signal (NU)

Out RAM 2 chip select signal

Out RAM 1 chip select signal

In Printer reset signal

In FOR TPRC (NU) +5V

Out Printer dot signal 4 (NU)

Out Printer dot signal 3 (NU)

Out Printer dot signal 2 (NU)

Out Printer dot signal 1 (NU)

— GND

Out Printer dot signal 7 (NU)

Out Printer dot signal 6 (NU)

Out Printer dot signal 5 (NU)

Out Printer motor

Out Printer motor drive signal (NU)

Out Printer dot signal 9 (NU)

Out Printer dot signal 8 (NU)

— Nu (+5V)

— I/R input from I/R unit (NU) Pull-up

— +5V

— GND

144 — — Nu

145

146

147

148

149

150

151

152

RAS3

RJMTR

SLMTD

SLMTS

SLMTR

HTS2

SCK2

STH2

Out Nu

Printer motor lock detection signal (NU)

In

GND

Out Nu

Out Nu

In GND

Out Serial output to FMC unit

Out Serial clock to FMC unit

In Serial input to FMC unit

153 — — Nu

154 — — Nu

155 — — Nu

156 — — Nu

157 — — Nu

158

159

160

LCDWT

DOTEN

RASP

IN TPRC wait signal

Out Dot drive enable signal (Nu)

—Nu

Function

drive signal (NU)

Option

2-3. CKDC8

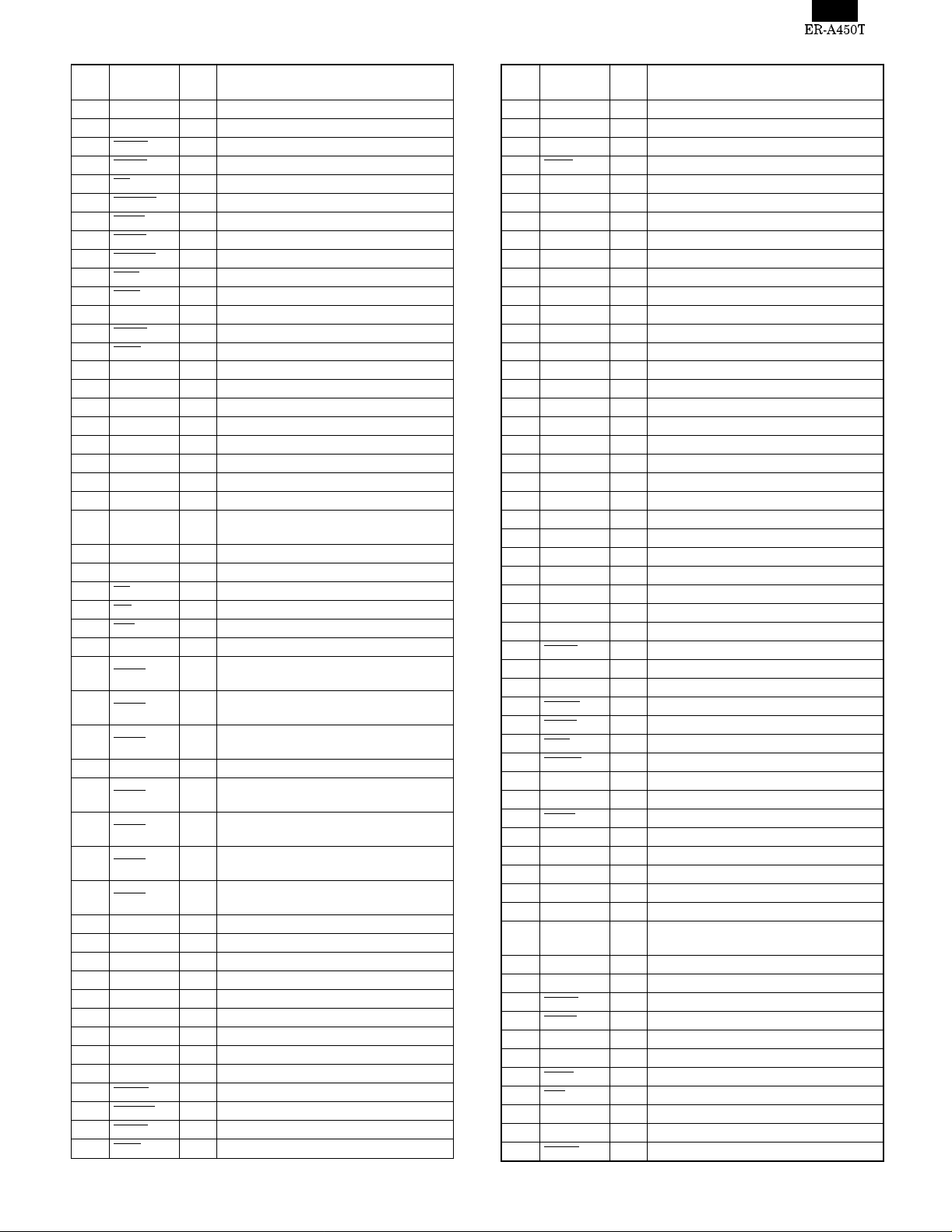

1) Pin configulation

NUNUG10G9G8G7G6G5G4G3G2G1BUZ

DP

SA

SB

SC

SD

SE

SF

SG

GND

VDD

KR4

KR10

KR11

NU

HTS

STH

646362616059585756555453525150

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

171819202122232425262728293031

ST0

/SCK

ST1

ST2

CKDC8

ST3

ST4

ST5

VDD

NU

GND

2) Pin assignment (CKDC8)

Pin

SYMBOL

No.

1 DP DP OUT DISPL AY SEGM ENT Dp

2 A SA OUT DISPLAY SEGMENT a

3 B SB OUT DISPLAY SEGMENT b

4 C SC OUT DISPLAY SEGMENT c

5 D SD OUT DISPLAY SEGMENT d

6 E SE OUT DISPLAY SEGMENT e

7 F SF OUT DISPLAY SEGMENT f

8 G SG OUT DISPLAY SEGMENT g

9 VSS0 GND GND

10 VDD0 VDD VDD

11 KR4 KR4 IN KEY RETURN 4

12 KR10 KR10 IN

13 KR11 KR11 IN KEY RETURN (MODE sw)

14 KR8 NU IN GND

15 HTS HTS IN

16 STH STH OUT

17 /SCK / SCK IN SHIFT CLOCK

18 ST0 ST0 OUT KEY STROBE 0

19 ST1 ST1 OUT KEY STROBE 1

20 ST2 ST2 OUT KEY STROBE 2

21 ST3 ST3 OUT KEY STROBE 3

22 ST4 ST4 OUT KEY STROBE 4

23 ST5 ST5 OUT KEY STROBE 5

24 VDD1 VDD VDD

25 AXSS GND GND

26 KR9 NU GND

27 KR0 KR0 IN KEY RETURN 0

28 KR1 KR1 IN KEY RETURN 1

29 KR2 KR2 IN KEY RETURN 2

30 KR3 KR3 IN KEY RETURN 3

31 KR5 KR5 IN KEY RETURN 5

SIGNAL

NAME

IN/

OUT

/POFFNUST8

49

ST7

48

ST6

47

/RESETS

46

/SHEN

45

ERC

44

LDRQ

43

GND

42

41

40

GND

39

38

37

/RES0

36

VDD

35

GND

34

KR7

33

32

KR0

KR1

KR2

KR3

KR5

KR6

FUNCTION

KEY RETURN (feed clerk

MRS sw)

4 – 8

Pin

No.

SYMBOL

SIGNAL

NAME

IN/

OUT

FUNCTION

32 KR6 KR6 IN KEY RETURN 6

33 KR7 KR7 IN KEY RETURN 7

34 AVRF GND

35 AVDD VDD

36 /RESET /RES0 IN

37 XT2

38 XT1

32.768 KHz

39 IC GND

40 X2

41 X1

4.19 MHz

42 VSS1 GND

43 LDRQ LDRQ IN LORD REQUEST

44 ERC ERC IN EVENT READ CANCEL

45 SHEN / SHEN OUT SHIFT ENABLE

46 /RES1 /RESETS OUT SYSTEM TO RESET

47 ST6 ST6 OUT KEY STROBE 6

48 ST7 ST7 OUT KEY STROBE 7

49 ST8 ST8 OUT KEY STROBE 8

50 ST9 NU OUT KEY STROBE 9

51 /POFF /POFF IN POWER OFF

52 BUZ BUZ OUT BUZZER

53 T0 G1 OUT DISPLAY DIGIT 1

54 T1 G2 OUT DISPLAY DIGIT 2

55 T2 G3 OUT DISPLAY DIGIT 3

56 T3 G4 OUT DISPLAY DIGIT 4

57 T4 G5 OUT DISPLAY DIGIT 5

58 T5 G6 OUT DISPLAY DIGIT 6

59 T6 G7 OUT DISPLAY DIGIT 7

60 T7 G8 OUT DISPLAY DIGIT 8

61 T8 G9 OUT DISPLAY DIGIT 9

62 T9 G10 OUT DISPLAY DIGIT 10

63 T10 NU OUT DISPLAY DIGIT 11

64 ID NU OUT DISPLAY SEGMENT

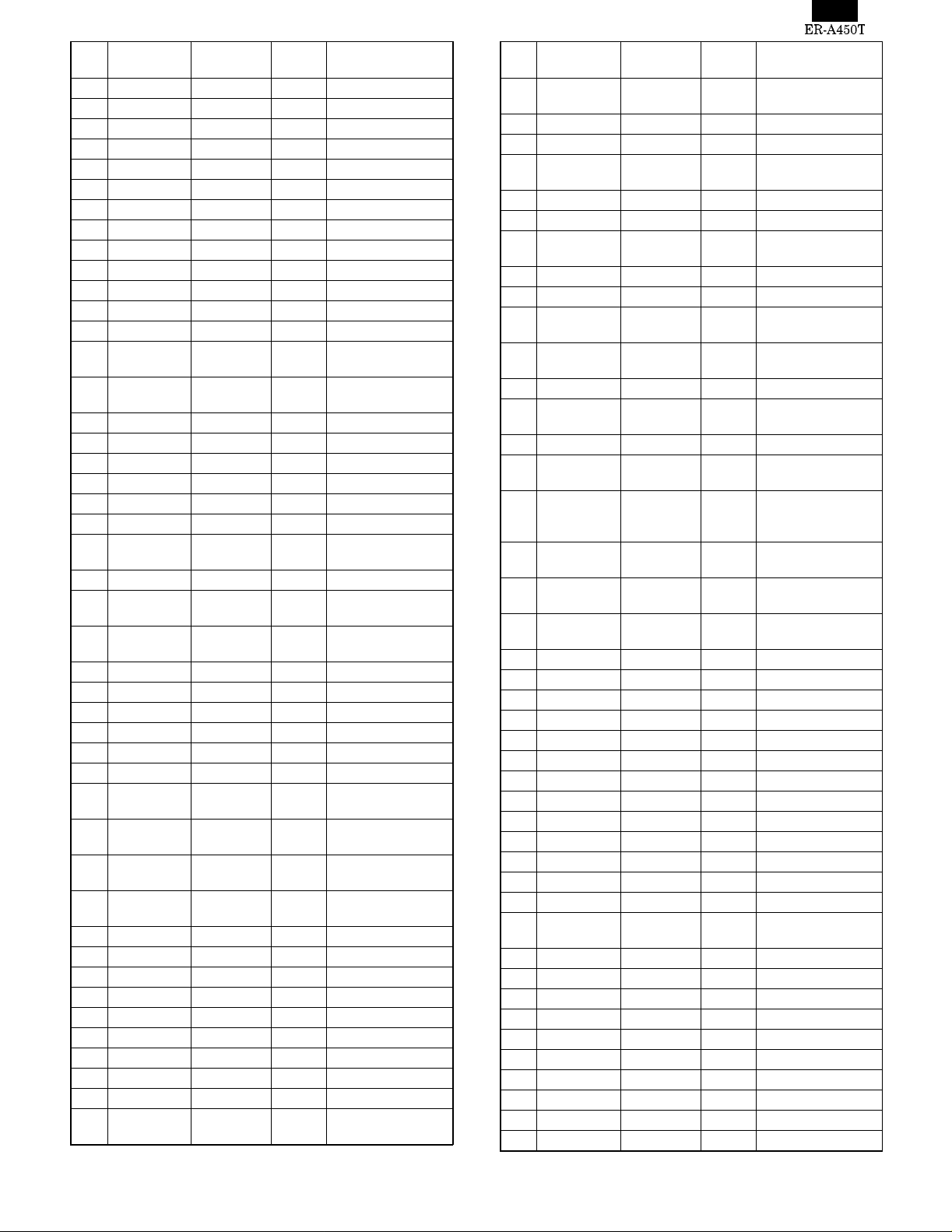

2-4. TPRC1 (F258024PC)

1) General

TPRC1 is the LSI circuit of the peripheral circuits of the microcomputer required for thermal printer control.

Auto cutter Pulse motor

POF,RES

CPU

(H8/500)

CG ROM

A0~23

D0~7

RD

WR

WAIT

INT

PHAI

The CPU is designed for use with H8/500. The bus I/F, however, is

not restricted to the design concept.

The printer is designed mainly for use with PR-58. However, the

thermalhead composition (the dot number and the block number) is

rather flexible.

1. Auto cutter (Option)

2. Pulse motor

3. Thermalhead

4. Switch

CTAO,CTBO

PFP,PCRES

TPRC1

BD0~2

BRD

BA0~15

PB RAM

(SRAM)

Fig. 2-6

XRS,XJS

RVPON,JVPON

RTRM,PTJM

BWR

BRAS

(BRAS)

SO

CLOCK

SI

LATCH

ST1~4

HCD

PHUP,PSP,

PST,POP

Thermal

head

Switch

sensor

4 – 9

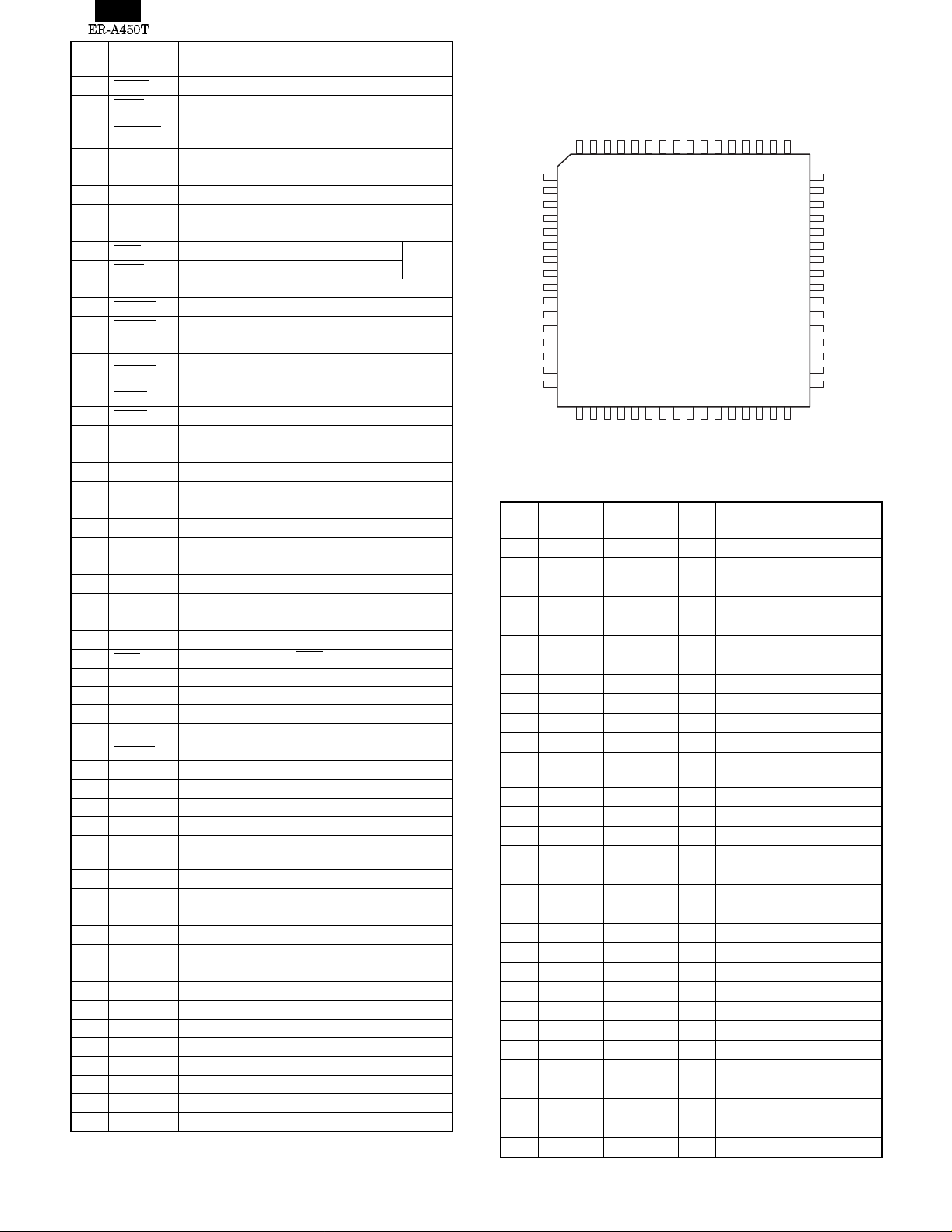

2) Pin configuration

GND

GND

GND

ST6

GND

GND

GND

SO

VCC

VCC

VCC

VCC

TEST1

D3

GND

GND

GND

INTI

GND

150

GND

149 BD3

148 BD4

147

146 BD5

145 BD6

54A11

55A12

56A13

144 BD7

143 BA0

57A14

58A15

VCC

VCC

VCC

141

142

140

139 PHAI

59A1660616263A17

137 BA2

138 BA1

136 BA3

135 BA4

134 BA5

64A18

65A19

66A20

67A21

GND

133 BA6

132

68A22

69A237071

GND

GND

131

130

129 BA7

128 BA8

127 BA9

126 BA10

72RD

73WR

74AS75POF

GND

GND

125 BA11

123 P.P

122

121

124 BA12

76INT

77

78

79BREQ

120

119

118 BA13

117 BA14

116

115

114

113 CGS

112

111

110

109 JAS

108

107 JCS

106 JDS

105 RAS

104 RBS

103

102

101

100

80

PTJM

PTRM

BA15

BRD

BWR

GND

GND

GND

JBS

VCC

VCC

VCC

VCC

VCC

99

GND

98

97 RCS

96 RDS

95

CTAO

94

CTBO

93

VHCOM

92 JVPON

91

GND

GND

90

89

GND

88 RVPON

87

PFP

86

PCRES

85 PHUP

84 JPE

83

ROE

82

EBACK

81

EBREQ

NU

GND

158 RESET

160

159

157 BRAS

156 BRAS

155 BD0

44A4

45A5

46A6

154 BD1

47A7

1

2

3ST1

4

5ST2

6ST3

7ST4

8ST5

9

10LATCH

11

12

13

14SI

15

16CLOCK

17INHDEC

18CSEN

19TEST2

20

21

22

23

24

25D0

26D1

27D2

28

29D4

30

31

32

33D5

34D6

35D7

36A0

37A1

38A2

39NU

40

43A3

41

42BACK

GND

GND

153 BD2

152

151

48A8

49A950515253A10

WI

GND

GND

GND

VCC

VCC

VCC

GND

GND

WO

NU

INH

Fig. 2-7

4 – 10

3) Block diagram

INHBEC

CSEN

CGS

RD,WR

A0~23

D0~7

WO

INT

INTI

PHAI

Φ)

(

DECODEK UNIT

SYSTEM

PDCTLU

HEAD CONTROL

TIMER UNIT

HOST BUS I/F UNIT

WI

INTERRUPT

CIRCUIT

CLOCK

GEN.

MOTOR CONTROL

TIMER UNIT

CUTTER CONTROL

TIMER UNIT

PB I/F UNIT

BD0~7

BA0~15

BRAS,BRAS

BRD,BWR

HEAD

I/F

MOTOR

CONTROL

CUTTER

CONTROL

I/F

PORT

MISC.

TEST

CIRCUIT

RES

POF,INH

POP,PHUP,PFP,PCRES

PTRM,PTJM

CLOCK,SO,ST1~5,HCO

SI

EBAK,EPEQ

EBRK,EACK

RVPON,JVPON,

RAS,RBS,RCS,RDS,

JAS,JBD,JCS,JDS

TEST1,TEST2

CTAO,CTBO

TPRC1 BLOCK DIAGRAM

Fig. 2-8

4) Pin description

Pin

Signal

No.

name

1 GND — GND

2 GND — GND

3

ST1 O Head drive strobe signal 1

4 GND — GND

5

ST2 O Head drive strobe signal 2

6

ST3 O Head drive strobe signal 3

7

ST4 O Head drive strobe signal 4

8

ST5 O NU

ST6 O NU

9

10

LATCH O Head latch signal

11 GND — GND

12 GND — GND

13 GND — GND

14 SI I Data return line, thermalhead -- TPRC1

15 SO O Send data from TPRC1 to thermalhead

16 CLOCK O Thermalhead CLOCK signal

17 INHDEC I GND

In/Out Function

Data from PB-RAM or zero data are

outputted at the falling of CLOCK signal.

16

SO is outputted at the edge of I Ä O,

and is taken at the edge of o Ä I.

Pin

Signal

No.

name

18

CSEN I GND

TEST2 I +5V internal counter timer test pin

19

In/Out Function

20 Vcc — +5V

21 Vcc — +5V

22 Vcc — +5V

23 Vcc — +5V

24

TEST1 I +5V internal counter timer test pin

25 D0 I/O Data bus 0: Internal register, print buffer

data IO

26 D1 I/O Data bus 1: Internal register, print buffer

data IO

27 D2 I/O Data bus 2: Internal register, print buffer

data IO

28 D3 I/O DAta bus 3: Internal register, print buffer

data IO

29 D4 I/O Data bus 4: Internal register, print buffer

data IO

30 GND — GND

31 GND — GND

32 GND — GND

33 D5 I/O Data bus 5: Internal register, print buffer

data IO

4 – 11

Pin

No.

Signal

name

In/Out Function

34 D6 I/O Data bus 6: Internal register, print buffer

data IO

35 D7 I/O Data bus 7: Internal register, print buffer

data IO

36 A0 I Address bus 0

37 A1 I Address bus 1

38 A2 I Address bus 2

39 TPRCRQ2 — Request signal

40

INTI I +5V

41

WI I +5V

42

BACK I BACK

43 A3 I Address bus 3

44 A4 I Address bus 4

45 A5 I Address bus 5

46 A6 I Address bus 6

47 A7 I Address bus 7

48 A8 I Address bus 8

49 A9 I Address bus 9

50 GND — GND

51 GND — GND

52 GND — GND

53 A10 I Address bus 10

54 A11 I Address bus 11

55 A12 I Address bus 12

56 A13 I Address bus 13

57 A14 I Address bus 14

58 A15 I Address bus 15

59 A16 I Address bus 16

60 Vcc — +5V

61 Vcc — +5V

62 Vcc — +5V

63 A17 I Address bus 17

64 A18 I Address bus 18

65 A19 I Address bus 19

66 A20 I Address bus 20

67 A21 I Address bus 21

68 A22 I Address bus 22

69 A23 I Address bus 23

70 GND — GND

71 GND — GND

72

RD I Read strobe signal: Gate enable of data

bus D0 - D7 tri-state buffer

73

WR I Write strobe signal: Write enable into

the internal register and the print buffer.

74

AS I AS

75

POF I Power off signal

INT O Interrupt signal

76

77

WO O Wait request signal to the CPU

78

INH I Head drive inhibit

BREQ O Bus request to CPU

79

80 — — NU

81

EBREQ I Bus request from option

EBACK O Bus acknowledge to option

82

83 RPE I Receipt paper empty

Pin

No.

Signal

name

In/Out Function

84 JPE I Journal paper empty

85 PHUP I Printer head up

86 PCRES I Auto cutter unit reset signal input (Nu)

87 PFP I Auto cutter unit FP signal input (Nu)

88 RVPON O Receipt side paper feed pulse motor

common power control signal (Nu)

89 GND — GND

90 GND — GND

91 GND — GND

JVPON O Journal side paper feed pulse motor

92

common power control signal (Nu)

93 VHCOM O Head drive common power control

94 CTBO O Cutter motor control signal (Nu)

95 CTAO O Cutter motor control signal (Nu)

96 RDS O Receipt side paper feed pulse motor

drive signal, phase D

97 RCS O Receipt side paper feed pulse motor

drive signal, phase C

98 GND — +5V

99 Vcc — +5V

100 Vcc — +5V

101 Vcc — +5V

102 Vcc — +5V

103 Vcc — +5V

104 RBS O Receipt side paper feed pulse motor

drive signal, phase B

105 RAS O Receipt side paper feed pulse motor

drive signal, phase A

106 JDS O Journal side paper feed pulse motor

drive signal, phase D

107 JCS O Journal side paper feed pulse motor

drive signal, phase C

108 JBS O Journal side paper feed pulse motor

drive signal, phase B

109 JAS O Journal side paper feed pulse motor

drive signal, phase A

110 GND — GND

111 GND — GND

112 GND — GND

113 CGS O NU

114

BWR O PB-RAM write strobe signal

115

BRD O PB-RAM read strobe signal

116 BA15 O NU

117 BA14 O Address 14 for PB-RAM

118 BA13 O Address 13 for PB-RAM

119 PTRM I Receipt motor connector sensor signal

120 PTJM I Journal motor connector sensor signal

121 GND — GND

122 GND — GND

123 POPI O GND

124 BA12 O Address bus 12 for PB-RAM

125 BA11 O Address bus 11 for PB-RAM

126 BA10 O Address bus 10 for PB-RAM

127 BA9 O Address bus 9 for PB-RAM

128 BA8 O Address bus 8 for PB-RAM

129 BA7 O Address bus 7 for PB-RAM

4 – 12

Pin

No.

Signal

name

In/Out Function

130 GND — GND

131 GND — GND

132 GND — GND

133 BA6 O Address bus 6 for PB-RAM

134 BA5 O Address bus 5 for PB-RAM

135 BA4 O Address bus 4 for PB-RAM

136 BA3 O Address bus 3 for PB-RAM

137 BA2 O Address bus 2 for PB-RAM

138 BA1 O Address bus 1 for PB-RAM

139 PHAI I TPRC1 clock input pin (9.83 MHz)

140 Vcc — +5V

141 Vcc — +5V

142 Vcc — +5V

143 BA0 O Address bus 0 for PB-RAM

2-5. OPC2

1) Pin configuration

Pin

No.

Signal

name

In/Out Function

144 BD7 I/O Data bus 7 for PB-RAM

145 BD6 I/O Data bus 6 for PB-RAM

146 BD5 I/O Data bus 5 for PB-RAM

147 GND — GND

148 BD4 I/O Data bus 4 for PB-RAM

149 BD3 I/O Data bus 3 for PB-RAM

150 GND — GND

151 GND — GND

152 GND — GND

153 BD2 I/O Data bus 2 for PB-RAM

154 BD1 I/O Data bus 1 for PB-RAM

155 BD0 I/O Data bus 0 for PB-RAM

156 BRAS O PB-RAM chip select: Active HIGH (Nu)

157

BRAS O PB-RAM chip select: Active LOW

RESET I TPRC1 reset signal

158

159 GND — GND

160 NU — GND

SL00

SL01

SL02

SL10

SL11

SL12

SL20

SL21

SL22

SL30

SL31

SL32

/CD0

BRK0

TRNEMP0

RCVRDY0

TRNRDY0

/CTS0

RCVDT0

VCC

GND

/CI0

/RTS0

/CS0

/CD1

BRK1

TRNEMP1

RCVRDY1

TRNRDY1

/CTS1

RCVDT1

/CI1

/RTS1

/CS1

/CD2

TRNEMP2

RCVRDY2

TRNRDY2

CTS2Z

RCVDT2

MCLK

RSLCT1

RSLCT0

/RIN

/WIN

SYCBKD

TRNEMPD

RCVRDYD

TRNRDYD

/DSRD

/CTSD

RCVDTD

/RTSD

/DTRD

TRNDTD

/CSD

GND

VCC

SYCBKC

TRNEMPC

RCVRDYC

TRNRDYC

/DSRC

/CTSC

RCVDTC

/RTSC

/DTRC

TRNDTC

/CSC

GND

SYCBKB

TRNEMPB

RCVRDYB

TRNRDYB

/DSRB

/CTSB

RCVDTB

/RTSB

124

77

123

122

79A080

/DTRB

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

TRNDTB

/CSB

GND

SYCBKA

TRNEMPA

RCVRDYA

TRNRDYA

/DSRA

/CTSA

RCVDTA

/RTSA

/DTRA

TRNDTA

/CSA

UTST

DBTST

RCVCLK

TRNCLK

RES

GND

VCC

/W

/R

DB7

DB6

DB5

DB4

GND

DB3

DB2

DB1

DB0

/RES

/WR

/RD

/OPTCS

A5

A4

A3

A2

RST

160

159

158

157

156

155

154

153

152

151

150

149

148

147

146

145

144

143

142

141

140

139

138

137

136

135

134

133

132

131

130

129

128

127

126

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52D053D154D255D356

57D458D559D660D761

62

63X164X265

66

67

69

70PX71

72

125

73

74

75

76

/CI2

/CS2

/CD3

BRK3

TRNEMP3

/CI3

/CS3

/CTS3

RCVDT3

TRNRDY3

RCVRDY3

GND

GND

VCC

TRCK

XOUT

AB068AB1

US1CH

/POF

/TRV

/RSRQ

TXE

/TRRQ

RXDATA0

A1

/TRQ178/TRQ2

4 – 13

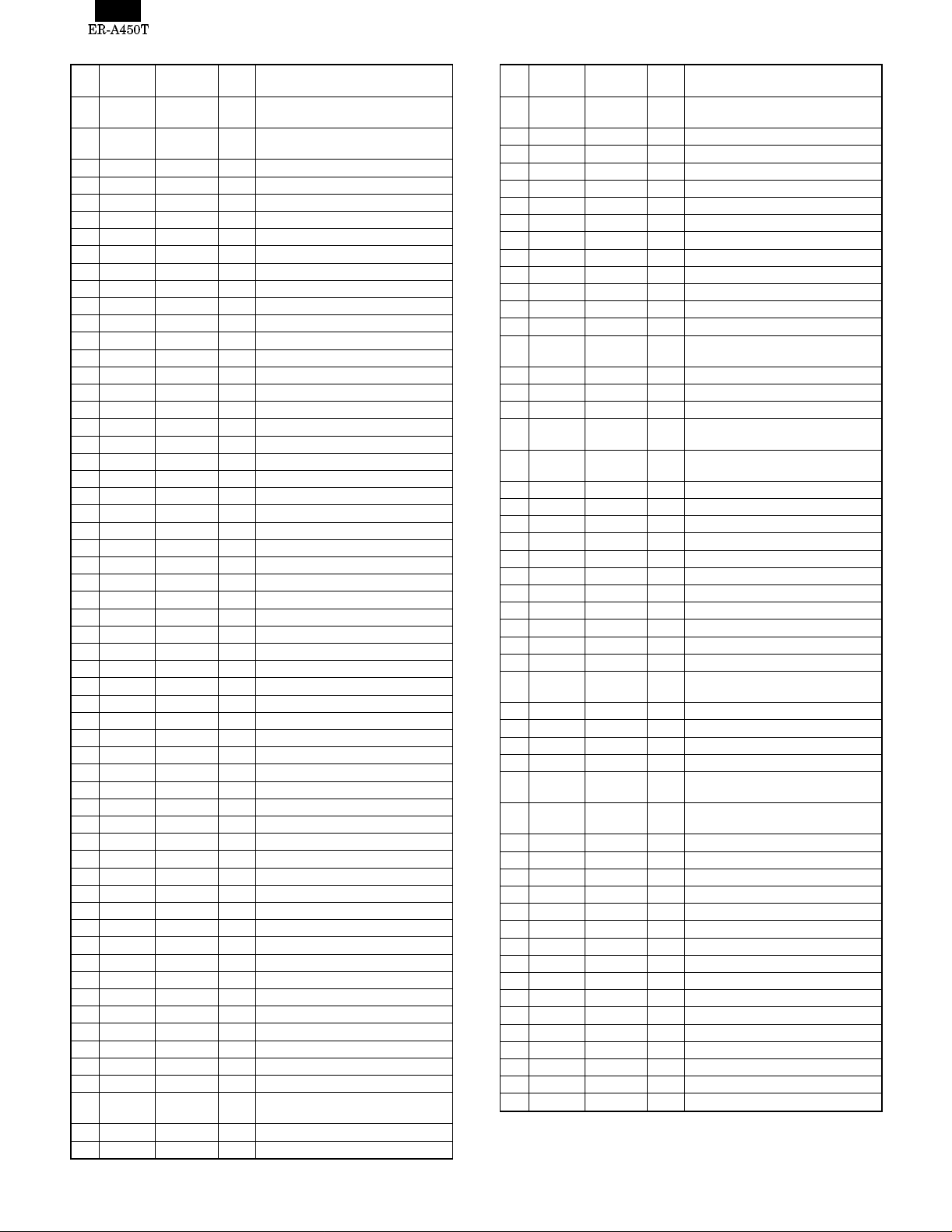

2) Block diagram

OPC2

OPC1

DATA BUS

OPC1~USART

BAUD RATE GENERATOR BAUD RATE GENERATOR

USART

A

USART

Common input

3) Pin description

Pin

NO.

10 SL30 GND ISU RS-232/UNIT3

11 SL31 GND ISU

12 SL32 GND ISU

13 /CD0 /DCD1 IS

14 BRK0 BRK1 IS RS-232 break signal

15 TRNEMP0 TRENMP1 IS

16 RCVRDY0 RCVRDY1 IS

17 TRNRDY0 TRNRDY1 IS

18 /CTS0 /CTS1 IS

19 RCVDT0 RCVDT1 IS

20 VCC VCC +5V

21 GND GND GND

22 /CI0 /CI1 IS

23 /RTS0 /RTS1 O

24 /CS0 /CS1 O

25 /CD1 /DCD2 IS

Name ER-A770 I/O Description

1 SL00 VCC ISU RS-232/UNIT0

2 SL01 GND ISU

channel select

3 SL02 GND ISU

4 SL10 GND ISU RS-232/UNIT1

5 SL11 GND ISU

channel select

6 SL12 GND ISU

7 SL20 GND ISU RS-232/UNIT2

8 SL21 GND ISU

channel select

9 SL22 GND ISU

channel select

RS-232 control

signal /CD input

RS-232 transmission

buffer empty signal

RS-232 data reception

enable signal

RS-232 transmission

enable signal

RS-232 clear to

send signal

RS-232 reception

data signal

RS-232 control

signal /CI input

RS-232 request to

send signal

RS-232 chip select

signal

RS-232 control

signal /CD input

USART

B

Pin

NO.

USART

C

Name ER-A770 I/O Description

USART

D

26 BRK1 BRK2 IS GND

27 TRNEMP1 TRENMP2 IS GND

28 RCVRDY1 RCVRDY2 IS GND

29 TRNRDY1 TRNRDY2 IS GND

30 /CTS1 /CTS2 IS +5V

31 RCVDT1 RCVDT2 IS

32 /CI1 /CI2 IS

33 /RTS1 /RTS2 O

34 /CS1 /CS2 O

RS-232 reception

data signal

RS-232 control

signal /CI input

RS-232 request to

send signal

RS-232 chip select

signal

35 /CD2 VCC IS +5V

36 TRNEMP2 TRENMP3 IS GND

37 RCVRDY2 RCVRDY3 IS GND

38 TRNRDY2 TRNRDY3 IS GND

39 CTS2Z /CTS3 IS +5V

40 RCVDT2 RCVDT3 IS GND

41 /CI2 VCC IS +5V

42 /CS2 /CS3 O NU

43 /CD3 /SINT IS

RS-232: /CD,

IN-LINE : /P1

44 BRK3 GND IS GND

45 TRNEMP3 GND IS GND

46 RCVRDY3 GND IS GND

47 TRNRDY3 GND IS GND

48 /CTS3 GND IS GND

49 RCVDT3 GND IS GND

50 /CI3 GND IS GND

51 /CS3 /SRCS O

RS-232/INLINE chip

select signal

52 D0 D0 IO Data bus (CPU)

53 D1 D1 IO Data bus (CPU)

4 – 14

Pin

NO.

Name ER-A770 I/O Description

54 D2 D2 IO Data bus (CPU)

55 D3 D3 IO Data bus (CPU)

56 GND GND GND

57 D4 D4 IO Data bus (CPU)

58 D5 D5 IO Data bus (CPU)

59 D6 D6 IO Data bus (CPU)

60 D7 D7 IO Data bus (CPU)

61 GND GND GND

62 VCC VCC +5V

63 X1 NC O OSI14 NC

64 X2 # I OSI14 System clock

65 XOUT CLK_USART O Clock (USART)

66 TRCK NC O NC

67 AB0 AH0 O

68 AB1 AH1 O

Address bus for

USART

Address bus for

USART

69 US1CH GND IS GND

70 PX NC O NC

71 /POF /POFF IS POFF signal

72 /RSRQ /IRQ1 3S RS232 INTRRUPT

73 /TRV GND IS GND

74 RXDATA0 NC O NC

75 TXE /SRESET O

INLINE SOFT

RESET

76 /TRRQ /TRQ2 3S INLINE INTRRUPT

77 /TRQ1 /TRQ1 ON6

78 /TRQ2 NC ON6

TIMER INTRRUPT

(RS232)

TIMER INTRRUPT

(INLINE)

79 A0 A0 I Address bus for CPU

80 A1 A1 I Address bus for CPU

81 A2 A2 I Address bus for CPU

82 A3 A3 I Address bus for CPU

83 A4 A4 I Address bus for CPU

84 A5 A5 I Address bus for CPU

85 /OPTCS /OPTCS I

86 /RD /RDO I

87 /WR /WRO I

88 /RES /RES IS

Option chip select

(from MPCA)

Read signal

(from CPU)

Write signal

(from CPU)

Reset signal

(from CPU)

89 DB0 DB0 IO DATA BUS (USART)

90 DB1 DB1 IO DATA BUS (USART)

91 DB2 DB2 IO DATA BUS (USART)

92 DB3 DB3 IO DATA BUS (USART)

93 GND GND GND

94 DB4 DB4 IO DATA BUS (USART)

95 DB5 DB5 IO DATA BUS (USART)

96 DB6 DB6 IO DATA BUS (USART)

97 DB7 DB7 IO DATA BUS (USART)

98 /R /RDH O

Read signal

(to USART)

Pin

NO.

99 /W /WRH O

Name ER-A770 I/O Description

Write signal

(to USART)

100 VCC VCC +5V

101 GND GND GND

102 RES RES USART O

Reset signal

(to USART)

103 TRNCLK GND I GND

104 RCVCLK GND I GND

105 DBTST /SRCS ID

RS-232/INLINE

USART chip select

106 UTST VCC ID +5V

107 /CSA /CS1 IS USART_A chip select

108 TRNDTA TXD1 O

109 /DTRA /DTR1 O

RS-232 transmission

data signal

RS-232 data

terminal ready signal

110 /RTSA NC O NC

111 RCVDTA RCVDT1 IS

RS-232 reception

data signal

112 /CTSA GND IS GND

113 /DSRA /DSR1 IS

RS-232 data set

ready signal

RS-232 data

114 TRNRDYA TRNRDY1 O

transmission enable

signal

115 RCVRDYA RCVRDY1 O

116 TRNEMPA TRNEMP1 O

117 SYCBKA BRK1 IO

RS-232 data reception

enable signal

RS-232 transmission

buffer empty signal

Break code

detection signal

118 GND GND GND

119 /CSB /CS2 IS USART_B chip select

120 TRNDTB TXD2 O NC

121 /DTRB /DTR2 O NC

122 /RTSB NC O NC

123 RCVDTB RCVDT2 IS GND

124 /CTSB GND IS GND

125 /DSRB /DSR2 IS GND

126 TRNRDYB TRNRDY2 O NC

127 RCVRDYB RCVRDY2 O NC

128 TRNEMPB TRNEMP2 O NC

129 SYCBKB BRK2 IO NC

130 GND GND GND

131 /CSC /CS3 IS

USART_C chip

select

132 TRNDTC TXD3 O NC

133 /DTRC /DTR3 O NC

134 /RTSC /RTS3 O NC

135 RCVDTC RCVDT3 IS GND

136 /CTSC GND IS GND

137 /DSRC /DSR3 IS GND

138 TRNRDYC TRNRDY3 O NC

139 RCVRDYC RCVRDY3 O NC

140 TRNEMPC TRNEMP3 O NC

141 SYCBKC NC IO NC

4 – 15

Loading...

Loading...