Page 1

CIRCUIT DIAGRAM

CODE : 00ZAR650//C1/

DIGITAL COPIER

MODEL

CONTENTS

[ 1 ] DESCRIPTION OF CIRCUIT . . . . . . . . . . . . . . . . . . . . . . . . . . 1 - 1

AR-650

[ 2 ] LOGIC CIRCUIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 - 1

Parts marked with “ “ are important for maintaining the safety of the set.

Be sure to replace these parts with specified ones for maintaining the safety and performance of the set.

This document has been published to be used for

SHARP CORPORATION

after sales service only.

The contents are subject to change without notice.

Page 2

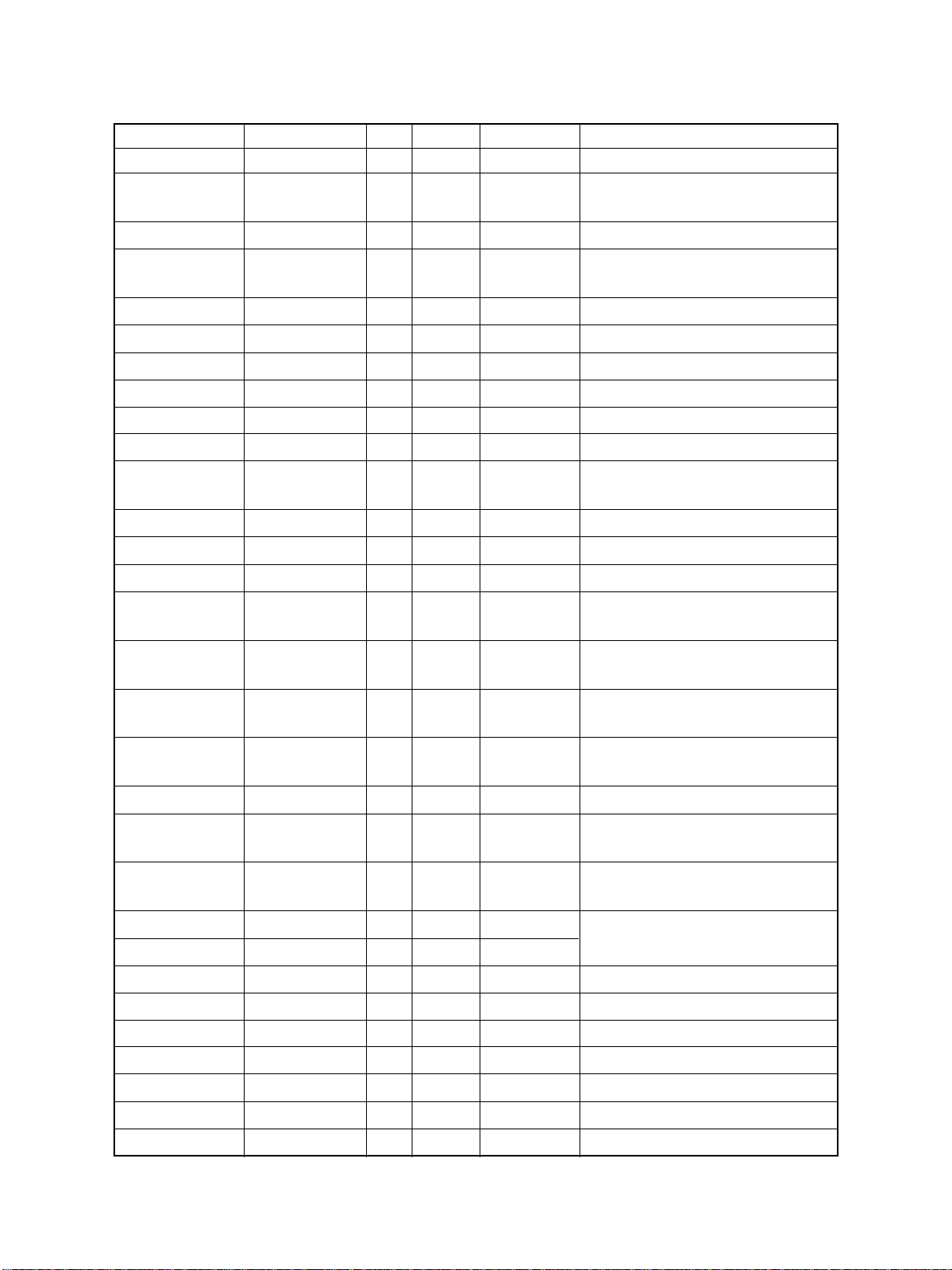

CONTENTS

1. DESCRIPTION OF CIRCUIT ............................................................................. 1–1

1.1 CPU Functions ........................................................................................................................... 1–2

1.1.1 Main CPU (TMP95C063F)................................................................................................... 1–2

1.1.2 PFC-CPU (TMP91C640N)................................................................................................... 1–9

1.1.3 Gate Array (LCA301) ........................................................................................................... 1–13

1.1.4 Scanner CPU (TMP95C063F) ............................................................................................. 1–20

1.1.5 Laser CPU (TMP95C063F).................................................................................................. 1–25

1.1.6 System CPU (NR4650)........................................................................................................ 1–30

2. LOGIC CIRCUIT ................................................................................................ 2–1

2.1 System Board (PWA-SYS) 1/29~29/29...................................................................................... 2–1

2.2 Mother Board (PWA-MTB) 1/2~2/2 ............................................................................................ 2–30

2.3 Logic Board (PWA-LGC) 1/23~23/23......................................................................................... 2–32

2.4 ADU Board (PWA-ADU) 1/2~2/2................................................................................................ 2–55

2.5 MOT Board (PWA-MOT) 1/1 ...................................................................................................... 2–57

2.6 SLG Board (PWA-SLG) 1/10~10/10 .......................................................................................... 2–58

2.7 CCD Board (PWA-CCD) 1/5~5/5 ............................................................................................... 2–68

2.8 PLG Board (PWA-PLG) 1/21~21/21 .......................................................................................... 2–73

2.9 SDV Board (PWA-SDV) 1/3~3/3................................................................................................. 2–94

2.10 LDR Board (PWA-LDR) 1/3~3/3 .............................................................................................. 2–97

2.11 ADF Circuit...............................................................................................................................

2–101

2 - 1 CONTENTS

Page 3

GENERAL PRECAUTIONS REGARDING THE INSTALLA TION

AND SERVICE

The installation and service should be done by a qualified service technician.

1. Transportation/Installation

• When transporting/installing the copier, move it by the casters while lifting the stoppers.

The copier is quite heavy and weighs approximately 250 kg (551 lb), therefore pay full attention

when handling it.

• Be sure to use a dedicated outlet with AC 115V or 120V/20A (220V, 230V, 240V/10A) or more for

its power source.

• The copier must be grounded for safety.

Never ground it to a gas pipe or a water pipe.

• Select a suitable place for installation.

Avoid excessive heat, high humidity, dust, vibration and direct sunlight.

• Also provide proper ventilation as the copier emits a slight amount of ozone.

• To insure adequate working space for the copying operation, keep a minimum clearance of

80 cm (32”) on the left, 80 cm (32”) on the right and 10 cm (4”) in the rear.

2. Service of Machines

• Basically, be sure to turn the main switch off and unplug the power cord during service.

• Be sure not to touch high-temperature sections such as the exposure lamp, the fuser unit, the

damp heater and their periphery.

• Be sure not to touch high-voltage sections such as the chargers, the transfer belt and the highvoltage transformer.

• Be sure not to touch rotating/operating sections such as gears, belts, pulleys, fan, etc.

• When servicing the machines with the main switch turned on, be sure not to touch live sections

and rotating/operating sections. Avoid exposure to laser radiation.

• Use suitable measuring instruments and tools.

• Avoid exposure to laser radiation during servicing.

− Avoid direct exposure to beam.

− Do not insert tools, parts, etc. that are reflective into the path of the laser beam.

− Remove all watches, rings, bracelets, etc. that are reflective.

3. Main Service Parts for Safety

• The breaker, door switch, fuse, thermostat, thermofuse, thermistor, etc. are particularly important for safety. Be sure to handle/install them properly.

4. Cautionary Labels

• During servicing, be sure to check the rating plate and the cautionary labels such as “Unplug the

power cord during service”, “Hot area”, “Laser warning label” etc. to see if there is any dirt on

their surface and whether they are properly stuck to the copier.

Page 4

5. Disposition of Consumable Parts/Packing Materials

• Regarding the recovery and disposal of the copier, supplies, consumable parts and packing

materials, it is recommended to follow the relevant local regulations or rules.

6. When parts are disassembled, reassembly is basically the reverse of disassembly unless

otherwise noted in this manual or other related documents. Be careful not to reassemble

small parts such as screws, washers, pins, E-rings, toothed washers in the wrong places.

7. Basically, the machine should not be operated with any parts removed or disassembled.

8. Precautions Against Static Electricity

• The PC board must be stored in an anti-electrostatic bag and handled carefully using a wrist-

band, because the ICs on it may become damaged due to static electricity.

Caution: Before using the wrist band, pull out the power cord plug of the copier and make

sure that there is no uninsulated charged objects in the vicinity.

Caution : Dispose of used RAM-IC’s (including lithium batter y)

according to the manufacturer’s instructions.

Vorsicht : Entsorgung des gebrauchten RAM-IC’s (inklusive

der Lithium Batterie) nach Angaben des Herstellers.

Page 5

1. DESCRIPTION OF CIRCUIT

BT

HDD

SCSI

(Optional Board)

LAN-Card

(for Debug)

P

W

A

-D

S

P

-3

0

0

L

C

D

7

8

9

4

5

6

1

2

3

0

C

L

R

/S

T

P

8

VRAM

NVRAM

LCD

Controller

RTC

PWA-F-MTB-300

PCI-Bus(33MHz)

32

IS

A

-B

u

s

ASIC

PCI-Bus

SRAM

32

CODEC

CLK

ASIC

Image Data

DRAM

Boot

ROM

OSC

SDRAMSDRAM

Serial-I/F

ADF

F

in

is

h

e

r

PFP

LCF

ADU

IPC

Serial-I/F

M-CPU

Gate

Array

PFC

PWA-F-LGC-300

SRAM

ROM

NVRAM

Serial-I/F

Serial-I/F

A

D

R

/D

A

T

-B

u

s

I/O

-

B

u

s

64bit-RISC

O

S

C

Flash

ROM.1

Flash

ROM.1

PWA-F-SLG-300

S-CPU

SRAM

EPROM

A

D

R

/D

A

T

-

B

u

s

Serial-I/F

Image Data

ASIC

Image Data

PWA-F-CCD-300

CCD

AmpAmp

A/DA/D

ASIC

PWA-F-PLG-300

PWA-F-SYS-300

D/A

L-CPU

D/A

EPROM

SRAM

A

D

R

/D

A

T

-B

u

s

Galvano

DRV

Galvano

DRV

ASIC

Galvanic

Mirror 1

Galvanic

Mirror 2

Galvanic

Mirror 3

Galvanic

Mirror 4

Laser Unit

Laser

Beam

Sensor

Amp

AmpA/D

PWA-F-LDR-300

PWM DRV LD

PWA-F-LDR-300

PWM DRV LD

PWA-F-LDR-300

PWM DRV LD

PWA-F-LDR-300

PWM DRV LD

Image Data

1 - 1 CIRCUIT DESCRIPTION

Page 6

1.1 CPU Functions

1.1.1 Main CPU (TMP95C063F)

(1) Outline and Features

The main CPU is a high-speed, advanced-function 16-bit microcontroller. This 144-pin mini flat package microcontroller has been developed for control of various mid-scale to large-scale equipment.

The main features of the main CPU are as follows:

q Original high-speed 16-bit CPU (900H_CPU)

• Upwardly compatible with TLCS-90/900 and instruction mnemonics

• 16 Mbyte linear address space

• General-use register and register bank system

• 16-bit multiplication and division operations, bit transfer/operation instructions

• High-speed DMA: 4-channel (640 ns/2 bytes at 25 MHz)

w Minimum instruction execution time: 160 ns (at 25 MHz oscillation)

e Built-in RAM: Not available

Built-in ROM: Not available

r External memory expansion

• Expandable to 16 Mbytes (both for program/data)

• External data bus width select terminal (AM8/16)

• Coexistence of external data bus 8/16 bit widths possible

... Dynamic data bus sizing

t Built-in DRAM controller: 2 ch

• 2CAS/2WE selectable

y 8-bit timer: 8 ch

u 16-bit timer: 2 ch

i Pattern generator: 4-bit x 2 ch

o General-use serial interface: 2 ch

• Baud rate generated by external clock

!0 10-bit A/D converter: 8 ch

!1 8-bit D/A converter: 2 ch

!2 Watchdog timer

!3 Chip select/wait controller: 4 blocks

!4 Interrupt functions

• CPU x 2: Software interrupt instructions, undefined instruction violation

• Internal interrupts: x 22

• External interrupts: x 11

!5 91 I/O port terminals

!6 Standby function

Three halt modes (RUN, IDLE, STOP)

Seven interrupt masking levels can be set.

(2) Main CPU functions

The main CPU has respective interfaces with system CPU, PFC, engine gatearray, finisher interface

IC (IPC), laser CPU for each, and performs the entire control of the copier engine.

The control program is stored in external ROM (27C4002-100F1).

Adjustment values for the engine are stored in battery backed up externel RAM (NVM).

CIRCUIT DESCRIPTION 1 - 2

Page 7

(3) Pin assignments

AVCC

AVSS

VREFL

VREFH

PC7/AN7

PC5/AN5

PC6/AN6

PC4/AN4

PC3/AN3

PC2/AN2

P07/AN0

PC1/AN1

DVCC

PD0/INT0

PD1

PD2

PD3

PD4

PE0

PE1

PE2

PE3

PE4

PE5

PE6

PE7

DVSSA0A1A2A3A4A5A6A7

A8

DAREFH

DAREFL

DAOUT0

DAOUT1

DVSS

PB0/INT4/T18

PB1/INT5/T19

PB2/TO8

PB3/TO9

PB4/INT6/TIA

PB5/INT7/TIB

PB6/TOA

PB7/TOB

PA0/TXD0

PA1/RXD0

PA2/CTS0

PA3/SCLK0

DVCC

PA4/TXD1

PA5/RXD1

PA6/CTS1

PA7/SCLK1

NMI

P90/TI0

P91/TO1

P92/TI2

P93/TO3

P94/TI4

P95/TO5

P96/TI6

P97/TO7

T80/BS

P81/SCOUT

P82/WAIT

AM8/16

CLK

144

1

5

10

15

140 135 130 125 120 115 110

TMP95C063F

MFP144

TOP VIEW

20

25

30

35

36

70656055504540

105

100

95

90

85

80

75

109

108

DVCC

A9

A10

A11

A12

A13

A14

A15

A16/P20

A17/P21

A18/P22

A19/P23

A20/P24

A21/P25

A22/P26

A23/P27

DVSS

D15/P17

D14/P16

D13/P15

D12/P14

D11/P13

D10/P12

D9/P11

D8/P10

DVCC

D7

D6

D5

D4

D3

D2

D1

D0

DVSS

RD

73

37

X1

X2

EA

DVSS

RESET

WDTOUT

P84/INT0

P85/INT1

P83/NMI2

DVCC

P86/INT2

P87/INT3

P70/PG00

P71/PG01

P72/PG02

P73/PG03

P74/PG10

P75/PG11

P76/PG12

P77/PG13

DVSS

P64/CS3/RAS3

P65/CAS3/WE3

P67/UCAS3/UW3/WE3

P63/UCAS1/UW1/WE1

P66/LCAS3/LW3/REFOUT3

P62/LCAS1/LW1/REFOUT1

P55/R/W

P57/CS2

P56/CS0

P60/CS1/RAS1

P61/CAS1/WE1

P54/BUSAK

72

WR

P52/HWR

P53/BUSRQ

Pin assignment diagram (top view)

1 - 3 CIRCUIT DESCRIPTION

Page 8

I/O Map of Main CPU

Port Name At reset R IN/OUT Signal Name FUNCTION

P97/T07

P96/T16

CMOS-IN PULL-UP

CMOS-IN PULL-UP

X

X

IN

IN

FCOV-1

TRNSW-0

Front cover, H: Open, L:Close

Reverse switch H: When paper is

past, L: No paper, (TRN-SW:S18)

P95/T05

P94/T14

P93/T03

P92/T12

P91/T01

P90/T10

P87/INT3

P86/INT2

P85/INT1

P84/INT0

P83/NMI2

P82/WAIT

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

X

—

X

X

X

—

↑

↑

↑

X

—

—

IN

OUT

IN

IN

IN

OUT

IN

IN

IN

IN

Not used

OUT

TRNES-0

POUT-0

TFUSW-1

EINT1-1

EXTSW-1

MVDEN-1

TXINT-1

CMINT-1

PFREQ-1

EINT2-1

CTDRM-0

Reverse exit switch, H: When paper is

past, L: No paper, (TRNE-SW:S17)

External I/F output (image quality

control)

A toner full: H, Normal: L, (T-FULLSW:SW15)

External I/F input 2 (image quality

control)

Fuser exit switch, L: When paper is

past, H: No paper, (EXIT-SW:S15)

Paper transport signal to POPS on PLG board

MAIN⇔PC communications interrupt

MAIN⇔System-CPU(S) reception interrupt

PFC→MAIN reception request interrupt

External I/F input 3 (image quality

control)

Image density sensor (IQM) REM

signal, L:ON, H:OFF

P81/SCOUT

P80/BS

P77/PG13

P76/PG12

P75/PG11

P74/PG10

P73/PG03

P72/PG02

P71/PG01

P70/PG00

P67/UCAS3/UW3/

WE3

P66/LCAS3/LW3/

REFOUT

P65/CAS3/WE3

P64/CS3/RAS3

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

TTL-OUT H

TTL-OUT H

TTL-OUT H

TTL-OUT H

↑

X

—

—

—

—

—

—

—

—

—

—

—

—

IN

IN

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

Not used

Not used

OUT

OUT

LSBSY-1

DEVSW-0A

TRMD-0

TRMC-0

TRMB-0

TRMA-0

RGTD-0

RGTC-0

RGTB-0

RGTA-0

CS3-0

L-CPU operation status signal

Developer unit, L: Installed, H: Uninstalled

Transfer belt motor driving signal

(Low active),(TRB-MOT:M25)

Alingning motor driving signal

(Low active), (RGT-MOT:M17)

Chip select for SRAM

CIRCUIT DESCRIPTION 1 - 4

Page 9

Port Name At reset R IN/OUT Signal Name FUNCTION

P63/UCAS1/UW1/

TTL-OUT H

—

Not used

WE1

P62/LCAS1/LW1/

REFOUT1

P61/CAS1/WE1

P60/CS1/RAS1

P57/CS2

P56/CS0

P55/RW

P54/BUSAK

P53/BUSRQ

P52/HWR

WR

RD

P27/A23

P26/A22

P25/A21

P24/A20

P23/A19

P22/A18

TTL-OUT H

TTL-OUT H

TTL-OUT H

TTLOUT L

TTL-OUT H

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

TTL-OUT H

TTL-OUT H

TTL-OUT H

TTL-OUT H

TTL-OUT H

TTL-OUT H

—

—

—

—

—

—

—

—

X

—

—

—

—

—

—

—

—

Not used

Not used

OUT

OUT

OUT

OUT

OUT

OUT

IN

OUT

OUT

OUT

Not used

OUT

OUT

OUT

OUT

CS1-0

CS2-0

CS0-0

RW-0

STKCL-0

REVCL-0

EINT3-1

WR-0

RD-0

ERSLP-0

A21

A20

WD-E

A18

Finisher IPC chip select

Main ROM chip select

Gate array chip select

Optional interface switching control signal

Stack clutch, L:ON, H:OFF, (STK-CLT:CL3)

Reverse clutch, L:ON, H:OFF, (REV-CLT:CL2)

External I/F input 4 (image quality

control)

External memory write signal

External memory read signal

Discharge LED lamp, L:ON, H:OFF, (ERS)

Address bus

Address bus

WD-E signal, Enable:H, Disable:L

Address bus

P21/A17

P20/A16

P17/D15

P16/D14

P15/D13

P14/D12

P13/D11

P12/D10

P11/D9

P10/D8

D7

D6

D5

D4

D3

D2

D1

TTL-OUT H

TTL-OUT H

TTL 3STATE

TTL 3STATE

TTL 3STATE

TTL 3STATE

TTL 3STATE

TTL 3STATE

TTL 3STATE

TTL 3STATE

TTL 3STATE

TTL 3STATE

TTL 3STATE

TTL 3STATE

TTL 3STATE

TTL 3STATE

TTL 3STATE

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

OUT

OUT

IN/OUT

IN/OUT

IN/OUT

IN/OUT

IN/OUT

IN/OUT

IN/OUT

IN/OUT

IN/OUT

IN/OUT

IN/OUT

IN/OUT

IN/OUT

IN/OUT

IN/OUT

A17

A16

D15

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

Address bus

Address bus

Data bus

Data bus

Data bus

Data bus

Data bus

Data bus

Data bus

Data bus

Data bus

Data bus

Data bus

Data bus

Data bus

Data bus

Data bus

1 - 5 CIRCUIT DESCRIPTION

Page 10

Port Name At reset R IN/OUT Signal Name FUNCTION

—

—

IN/OUT

OUT

D0

A15

Data bus

Address bus

D0

A15

TTL 3STATE

TTL OUT

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

PA7/SCLK1

PA6/CTS1

PA5/RXD1

TTL OUT

TTL OUT

TTL OUT

TTL OUT

TTL OUT

TTL OUT

TTL OUT

TTL OUT

TTL OUT

TTL OUT

TTL OUT

TTL OUT

TTL OUT

TTL OUT

TTL OUT

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

↑

↑

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

Not used

IN

IN

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

LCTS-0

LRXD-1

Address bus

Address bus

Address bus

Address bus

Address bus

Address bus

Address bus

Address bus

Address bus

Address bus

Address bus

Address bus

Address bus

Address bus

Address bus

L-CPU CTS signal

L-CPU⇒M-CPU serial I/F receive data

PA4/TXD1

PA3/SCLK0

PA2/CTS0

PA1/RXD0

PA0/TXD0

PB7/TOB

PB6/TOA

PB5/TIB/INT7

PB4/TIA/INT6

PB3/TO9

PB2/TO8

PB1/TI9/INT5

PB0/TI8/INT4

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

—

—

—

↑

—

—

—

—

—

—

—

↑

—

OUT

OUT

OUT

IN

OUT

OUT

OUT

IN

Not used

OUT

OUT

IN

IN

LTXD-0

MREQP-0

MACKP-0

PFRXD-1

PFTXD-0

RSTSW-0

DRCLK-1

STINT-1

DRMON-0

DRMBK-0

PDWN-1

EINT0-1

M-CPU⇒L-CPU serial I/F send data

M-CPU⇒PFC transmission request signal

M-CPU⇒PFC reception enable signal

PFC⇒M-CPU serial I/F receive data

M-CPU⇒PFC serial I/F send data

Main switch OFF at L, (S42)

Drum motor reference clock, (DRM-

MOT:M12)

SYSTEM⇔MAIN transmission interrupt (STINT)

DRM-MOT ON Signal,L:ON, H:OFF

(DC brushless motor), (M12)

DRM-MOT BRK signal,L:Brake,

H:OFF (DC brushless motor), (M12)

When 5V drops to 0V: H, Otherwise:

L, Rising edge detection

External I/F input 1 (image quality

control)

CIRCUIT DESCRIPTION 1 - 6

Page 11

Port Name At reset R IN/OUT Signal Name FUNCTION

PC7/AN7

PC6/AN6

CMOS-IN

CMOS-IN

—

—

IN

IN

FUSSW-1

STHU-1A

Fuser unit, L: Uninstalled, H: Installed

Upper heatroller thermistor (END),

(THMSH/U)

PC5/AN5

PC4/AN4

PC3/AN3

PC2/AN2

PC1/AN1

PC0/AN0

PD0/INT8

PD4

PD3

PD2

PD1

PE7

PE6

PE5

CMOS-IN

CMOS-IN

CMOS-IN

CMOS-IN

CMOS-IN

CMOS-IN

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

—

—

—

—

—

—

↑

—

—

—

↑

—

—

—

IN

IN

IN

IN

IN

Not used

IN

OUT

OUT

OUT

IN

OUT

OUT

OUT

THML-1A

THMU-1A

CTDS-1

DRTMP-1

ATS-1

GND

RXINT-1

HVTM-0

HVTT-0

HVDDC-0

PFACK-1

HVDAC-0

LRTS-0

HVTBB-0

Lower heatroller thermistor (THMSH/L)

Upper heatroller thermistor (Center),

(THMSH/U)

Image density sensor Analog input, (IQM)

Drum thermistor analog input, (THMSD)

Auto toner sensor analog input, (ATS)

MAIN⇔PC communications interrupt

Main charger, L:ON, H:OFF, (HVT-TM)

Transfer belt bias, L:ON, H:OFF, (HVT-

TM)

Developer bias (DC),L:ON, H:OFF,(HVT-DB)

PFC→M-CPU transmission enable signal

Developer bias (AC),L:ON, H:OFF,(HVT-DB)

M-CPU→L-CPU transmission request

signal (enable:L)

Transfer belt brush bias , L:ON,

H:OFF, (HVT-TM)

PE4

PE3

PE2

PE1

PE0

DAREFH

DAREFL

DAOUT0

DAOUT1

NMI

EA

CLR

CLK

WDOUT

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN

CMOS-IN

CMOS-IN

TTL-OUT

TTL-OUT

X

—

—

—

—

—

—

—

—

—

—

—

—

—

IN

OUT

OUT

OUT

OUT

—

—

Not used

Not used

IN

IN

IN

OUT

OUT

IPCSW-1

DRMCW-0

LRST-0

FNOF2-0

FANOF-0

5V

GND

5V

GND

RST-0

WDT-0

Finisher PC board, L:connected,

H:disconnected

Drum motor rotation direction, H:CCW, L:CW,

(DC brushless motor), (DRM-MOT:M12)

L-CPU reset signal, L: Reset, H: Normal

Fan speed signal-2, L: Low speed,

H: High speed

Fan speed signal-1, L: Low speed,

H: High speed

Reference voltage of D/A convertor

Non Maskable Interrupt

External Access

Reset at L

Clock

Microcontroller out of control: L, Normal: H

1 - 7 CIRCUIT DESCRIPTION

Page 12

Port Name At reset R IN/OUT Signal Name FUNCTION

GND

AM8/16

RESET

VREFH

—

—

—

—

—

IN

Bus width, Mixed 8- and 16-bit buses at L

Reset signal

Reference voltage input for A/D converter

VREFL

AVCC

AVSS

X1/X2

DVCC

DVSS

R : Programmable pull-up resistor

↑ : Pulled up

X : Not pulled up

— : No pull-up functions

—

—

—

—

—

—

IN

—

Reference voltage input for A/D converter

A/D converter power supply

A/D converter power supply

Oscillator terminal

5V power supply

GND terminal

CIRCUIT DESCRIPTION 1 - 8

Page 13

1.1.2 PFC-CPU (TMP91C640N)

(1) Features

This 8-bit CMOS microcontroller integrates an 8-bit CPU, ROM, RAM, A/D converter, multifunction

timer/event counter, and general-use serial interface in a single chip. External memory can be expanded to 48 Kbytes for proglam, and data memory to 1 Mbytes.

• Internal ROM: 16 Kbytes

• Internal RAM: 512 bytes

• External program memory: 48 Kbytes

• External data memory: 1 Mbytes

• Precision 8-bit A/D converter (6 ch)

• General-use serial interface (1 ch)

• Stepping motor control (2 ch)

• 54 I/O port terminals

(2) PFC-CPU functions

PFC controls the paper feed system.

All operations for transporting the paper feeding from each cassette up to the aligning rollers in the

machine are controlled by PFC.

1 - 9 CIRCUIT DESCRIPTION

Page 14

(3) Pin assignment of PFC-CPU

VREF

AGND

(AN0)P50

(AN1)P51

(AN2)P52

(AN3)P53

(AN4)P54

(AN5)P55

(TO3/M00)P60

(M01)P61

(M02)P62

(M03)P63

(TO/M10)P70

(M11)P71

(M12)P72

(M13)P73

(INT0)P80

(INT1/T14)P81

(INT2/T15)P82

(TO3/TO4)P83

NMI

RESET

CLK

(D0)P00

(D1)P01

(D2)P02

(D3)P03

(D4)P04

(D5)P05

(D6)P06

(D7)P07

(GND)Vss

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

64

Vss

63

P37(WAIT)

62

P36(WR)

61

P35(RD)

60

P34(CTS)

59

P33(TXD)

58

P32(TXD/RTS/SCLK)

57

P31(RXD)

56

P30(RXD)

55

EX

54

P43(A19)

53

P42(A18)

52

P41(A17)

51

P40(A16)

50

P27(A15)

49

P26(A14)

48

P25(A13)

47

P24(A12)

46

P23(A11)

45

P22(A10)

44

P21(A9)

43

P20(A8)

42

P17(A7)

41

P16(A6)

40

P15(A5)

39

P14(A4)

38

P13(A3)

37

P12(A2)

36

P11(A1)

35

P10(A0)

34

X1

X2

33

TMP91C640N pin assignment (shrink DIP)

CIRCUIT DESCRIPTION 1 - 10

Page 15

I/O Map of PFC-CPU

Port Name At reset IN/OUT Signal Name FUNCTION

P37/WAIT

P36/WR

Not used

Not used

P35/RD

P34/CTS

P33/TXD

P32/TXD/RTS/

SCLK

P31/RXD

P30/RXD

P55/AN5

P54/AN4

P53/AN3

P52/AN2

P51/AN1

P50/AN0

P83/TO3/TO4

P82/INT2/TI5

OUT

IN

OUT

OUT

IN

IN

IN

IN

IN

Not used

Not used

Not used

OUT

Not used

PFREQ-1

MACKP-1

PFRXD-0

PFACK-1

PFTXD-0

PSTPC-1

24VCK-1

ADCNT-1

5VSW-1

PSTPD-0

Send request (TO G/A)

ACK signal (FROM G/A)

Serial transmission data (TO G/A)

ACK signal (TO G/A)

Serial receive data (FROM G/A)

Paper stop switch (P-STP-SW:S13)

When paper is past: H, No paper: L

Front door check (analog voltage)

Front door open at 2.5 V or less

ADU connection status

When installed: L

Paper feed status signal

P81/INT1/TI4

P80/INT0

P73/M13

P72/M12

P71/M11

P70/M10/TO2

P63/M03

P62/M02

P61/M01

P60/M00/TO1

P07/D7

P06/D6

P05/D5

P04/D4

P03/D3

P02/D2

P01/D1

P00/D0

IN

IN

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

MREQP-1

RSTRT-1

SIDMD-0

SIDMC-0

SIDMB-0

SIDMA-0

ENDMD-0

ENDMC-0

ENDMB-0

ENDMA-0

DRV7-1

DRV6-1

DRV5-1

DRV4-1

DRV3-1

DRV2-1

DRV1-1

DRV0-1

Send request (from G/A): External interrupt

Copier aligning roller restart signal

ADU Side guide motor control signal

(SID-MOT:M9)

ADU End guide motor control signal

(END-MOT:M8)

Driver control signal

1 - 11 CIRCUIT DESCRIPTION

Page 16

Port Name At reset IN/OUT Signal Name FUNCTION

P43/A19

P42/A18

OUT

OUT

CLKD-0

CLKC-0

For driver control data (DRV0 to 7)

Registration control signal

P41/A17

P40/A16

P27/A15

P26/A14

P25/A13

P24/A12

P23/A11

P22/A10

P21/A9

P20/A8

P17/A7

P16/A6

P15/A5

P14/A4

P13/A3

P12/A2

P11/A1

P10/A0

OUT

OUT

Not used

Not used

OUT

OUT

OUT

OUT

OUT

OUT

IN

IN

IN

IN

IN

IN

IN

IN

CLKB-0

CLKA-0

SCSWF-0

SCSWE-0

SCSWD-0

SCSWC-0

SCSWB-0

SCSWA-0

RETS7-1

RETS6-1

RETS5-1

RETS4-1

RETS3-1

RETS2-1

RETS1-1

RETS0-1

Registration data output: rising edge

Registration output data for holding: falling edge

Enable signal for bus buffer

Switch, sensor input (bus buffer)

NMI

EA

RST

CK

X1

X2

VREF

AGND

IN

IN

IN

Not used

IN

IN

—

—

5V

GND

PFRST-0

Non mastkable Interrupt

External access

Reset signal

Oscillator input

Oscillator output

Reference voltage input for A/D converter

Ground input for A/D converter

CIRCUIT DESCRIPTION 1 - 12

Page 17

1.1.3 Gate Array (LCA301)

(1) Gate array functions

The gate array is controlled b y the main CPU and the gate arra y’s internal logic circuit. The gate arr a y

has the following functions:

• Pulse motor control (drum, transfer belt)

• Interface with NV-RAM (A key circuit is provided to prevent against clearing data inadv ertently ev en

if the microcontroller is out of control).

• General-use I/O port

(2) Gate array pin assignment diagram

156 105

157

208

104

53

152

1 - 13 CIRCUIT DESCRIPTION

Page 18

I/O Map of Gate Array

Port Name At reset IN/OUT Signal Name FUNCTION

PA0

CMOS-IN

IN

CNT-1

Line jumper wire L: Line for factory

adjustment), H: Field (for delivery)

PA1

PA2

PA3

PA4

PA5

PA6

PA7

PB0

PB1

PB2

PB3

PB4

PB5

PB6

PB7

PC0

PC1

PC2

CMOS-IN

CMOS-IN

CMOS-IN

CMOS-IN

CMOS-IN

CMOS-IN

CMOS-IN

CMOS-IN

CMOS-IN

CMOS-IN

CMOS-IN

CMOS-IN

CMOS-IN

CMOS-IN

CMOS-IN

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

IN

IN

IN

IN

IN

IN

IN

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

PCCNT-0A

PCDSR-0

CPMSW-0

CPSW2-0

Not used

Not used

Not used

RMS0-1

RMS1-1

RMS2-1

RMS3-1

RMS4-1

RMS5-1

RMS6-1

RMS7-1

Not used

Not used

Not used

PC connection line

DSR signal for PC

RMS

PC3

PC4

PC5

PC6

PC7

A0

A1

A2

A3

A4

A5

A6

A7

A12

A13

A14

D0

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

TTL-IN PULL-UP

TTL-IN PULL-UP

TTL-IN PULL-UP

TTL-IN PULL-UP

TTL-IN PULL-UP

TTL-IN PULL-UP

TTL-IN PULL-UP

TTL-IN PULL-UP

TTL-IN PULL-UP

TTL-IN PULL-UP

TTL-IN PULL-UP

TTL-IN CMOS-OUT PULL-UP

IN/OUT

OUT

OUT

OUT

OUT

OUT

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

Not used

Not used

Not used

Not used

Not used

A0

A1

A2

A3

A4

A5

A6

A7

A12

A13

A14

D0

Address bus

Data bus

CIRCUIT DESCRIPTION 1 - 14

Page 19

Port Name At reset IN/OUT Signal Name FUNCTION

D1

D2

TTL-IN CMOS-OUT PULL-UP

TTL-IN CMOS-OUT PULL-UP

IN/OUT

IN/OUT

D1

D2

Data bus

D3

D4

D5

D6

D7

RD

WR

CS

CTS

RXD

CBSY

CMD

SACK

SERR

RXDINT

TXDINT

CMDINT

STSINT

TTL-IN CMOS-OUT PULL-UP

TTL-IN CMOS-OUT PULL-UP

TTL-IN CMOS-OUT PULL-UP

TTL-IN CMOS-OUT PULL-UP

TTL-IN CMOS-OUT PULL-UP

IN/OUT

IN/OUT

IN/OUT

IN/OUT

IN/OUT

TTL-IN PULL-UP

TTL-IN PULL-UP

TTL-IN PULL-UP

TTL-IN

TTL-IN

TTL-IN

TTL-IN

TTL-IN

TTL-IN

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

IN

IN

IN

IN

IN

IN

IN

IN

IN

OUT

OUT

OUT

OUT

D3

D4

D5

D6

D7

RD-0

WR-0

CS0-0

PCCTS-0

PCRXD-0

CBSY-0

CMD-0

SACK-0

SERR-0

RXINT-1

TXINT-1

CMINT-1

STINT-1

Read signal

Write signal

Chip select signal

CTS signal for PC

PC serial receive data (from PC)

System I/F command BSY signal

System I/F receive data signal

System I/F status ACK signal

System I/F status error signal

MAIN⇔PC reception interrupt (RXINT)

MAIN⇔PC transmission interrupt (TXINT)

System I/F reception interrupt

System I/F transmission interrupt

RTS

TXD

SBSY

STS

CACK

CERR

SCLK

RESET

CNTRST

TESTSW

TSTEN

PD0

PD1

PD2

PD3

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

CMOS-IN

CMOS-IN SCHMITT

CMOS-IN

CMOS-IN

INPUT with PULL-DOWN

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

OUT

OUT

OUT

OUT

OUT

OUT

IN

IN

IN

IN

IN

OUT

Not used

OUT

OUT

PCRTS-0

PCTXD-0

SBSY-0

STS-0

CACK-0

CERR-0

Not used

GARST-0

Not used

Not used

Not used

STKSL-0

CLMTA-0

CLMTB-0

For external PC

PC serial data send data (to PC)

System I/F status BSY signal

System I/F send data signal

System I/F command ACK signal

System I/F command error signal

Reset signal

H

GND

GND

Gate solenoid, L:ON, H:OFF, (GATE-

SOL:SOL4)

Main charger cleaning motor (CLN-MOT:M11)

PD2 PD3

H H Brake

HLCW

L H CCW

L L OFF

1 - 15 CIRCUIT DESCRIPTION

Page 20

Port Name At reset IN/OUT Signal Name FUNCTION

PD4

PD5

CMOS-OUT H

CMOS-OUT H

OUT

Not used

FURMT-0

Fur brush motor, L: ON, H: OFF, (FUR-MOT:M10)

PD6

PD7

PE0

PE1

PE2

PE3

PE4

PE5

PE6

PE7

OSC1

OSC2

DICH1

LDCH1

CLKCH1

DICH2

LDCH2

CLKCH2

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

IN

OUT

CMOS-OUT L

CMOS-OUT L

CMOS-OUT L

CMOS-OUT L

CMOS-OUT L

CMOS-OUT L

OUT

Not used

Not used

Not used

Not used

Not used

Not used

Not used

Not used

Not used

IN

OUT

OUT

OUT

OUT

Not used

Not used

Not used

CTRON-0

X1

X2

DADA T-1

DALTH-1

SCK-1

ON at counter:L, OFF at counter: H, (T)

Oscillator input

Oscillator output

D/A serial data

D/A serial data strobe, L: Latch, H: Hold

D/A serial clock

PF0

PF1

PF2

PF3

PF4

PF5

PF6

PF7

PG0

PG1

PG2

CMOS-OUT IN

CMOS-OUT IN

CMOS-OUT IN

CMOS-OUT IN

CMOS-OUT IN

CMOS-OUT IN

CMOS-OUT IN

CMOS-OUT IN

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

IN

IN

IN

IN

IN

IN

IN

Not used

OUT

OUT

OUT

EXCSW-1A

MCLSW-0

CLNSW-0

BRMRK-1A

ATSSW-1

CTRCN-1A

EXPON-0

USSR-1

SBSSR-0

HTRMT-1

Reverse door switch, H:CLOSE,

L:OPEN, (EXC-SW:S19)

Main charger cleaning switch ON:L,

OFF:H, (CLN-M-SW:S16)

Cleaner connection signal,

L: Connection, H: No connection

Brush motor lock detection signal,

L: Normal, H: Lock

Auto toner sensor connection signal,

L: Connection, H: No connection

Total counter connection signal,

L: Connection, H: No connection

Exposure lamp ON signal, H: ON, L: OFF

SSR for heater lamp, L:ON. H:OFF, (SSR-U)

SSR for sub heater lamp, L:ON. H:OFF, (SSR-S)

Heat roller motor, L:ON, H:OFF,(HTR-

MOT:M18)

CIRCUIT DESCRIPTION 1 - 16

Page 21

Port Name At reset IN/OUT Signal Name FUNCTION

PG3

CMOS-OUT H

OUT

HTRML-0

Heat roller motor, L:Low speed ON,

H:OFF,(HTR-MOT:M18)

PG4

PG5

PG6

PG7

PH0

PH1

PH2

PH3

PH4

PH5

PH6

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

SCRP-0

RVSF-0

DCTOF-0

HTRFA-0

EXTFA-0

DEVFA-0

CHFAN-0

DCTIF-0

TNRMT-0

DEVON-0

DVMBK-0

Scraper solenoid, L:ON,

H:OFF,(SCRP-SOL:SOL3)

Reverse fan motor, L:ON, H:OFF,

(REV-FAN-MOT:M27)

Duct out fan motor, L:ON, H:OFF,

(DUCT-OUT-FAN-MOT:M23)

Heater fan motor, L:ON, H:OFF, (HTRFAN-MOT:M20)

Exit fan motor, L:ON, H:OFF,

(EXIT-FAN-MOT:M19)

Main charger fan motor, L:ON, H:OFF,

(DEV-FAN-MOT:M21)

Main charger fan motor, L:ON, H:OFF,

(DEV-FAN-MOT:M21)

Duct in fan motor, L:ON, H:OFF,

(DUCT-IN-FAN-MOT:M22)

Toner motor, L:ON, H:OFF,

(TNR-MOT:M14)

Developer motor, L:ON, H:OFF,

(DEV-MOT:M16)

Developer motor, L:BRAKE,

H:NORMAL, (DEV-MOT:M16)

PH7

P10

P11

P12

P13

P14

P15

P16

P17

DCCLK1

DCCLK2

DCCLK3

DCCLK4

CMOS-OUT H

CMOS-IN

CMOS-N

CMOS-IN

CMOS-N

CMOS-IN

CMOS-IN

CMOS-IN

CMOS-IN

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

OUT

DRMSW-0

Drum motor drive current select, L:Acceleration,

H:Constant, (DRM-MOT:M12)

IN

IN

TEMP-0A

HOPSW-1

Toner Empty:L, Normal:H(TNR-EMP-SW:S14)

Toner supply cover switch, H:open,

L:close (TNR-HOP-SW:S11)

IN

KCTRC-1A

Key counter connecting signal

L;connect, H:disconnect

IN

HTRDY-1

At HTR-ready :L, other:H

Not used

Not used

Not used

Not used

OUT

OUT

OUT

OUT

ADDCK-1

HTRCK-1

DEVCK-1

PFMCK-1

1 - 17 CIRCUIT DESCRIPTION

ADU-MOT reference clock, (M24)

HTR-MOT reference clock, (M18)

DEV-MOT reference clock, (M16)

PFP-MOT reference clock (M31)

Page 22

Port Name At reset IN/OUT Signal Name FUNCTION

SM_A

CMOS-OUT H

OUT

DRMTA-0

Drum motor control signal

(Active low), (M12)

SM_B

SM_NA

SM_NB

SMCLK

PJ0

PJ1

PJ2

PJ3

PJ4

PJ5

PJ6

PJ7

MWR

SMINT

CS0

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

CMOS-IN

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

OUT

OUT

OUT

IN

OUT

OUT

OUT

OUT

OUT

Not used

Not used

Not used

OUT

Not used

Not used

DRMTB-0

DRMTC-0

DRMTD-0

DRCLK-1

TCMTB-0

TCMTA-0

AUGMT-0

RSTRT-1

PCDTR-0

WRRAM-0

Drum motor reference clock (fromM-CPU)

Transfer belt cam motor (TRB-CAM-MOT:M26)

PJ0 PJ1

H H Brake

LHCW

H L CCW

L L STOP

Toner transport motor, L:ON, H:OFF,

(AUG2-MOT:M15)

RESTART (⇒PFC)

For external PC

RAM write signal

CS1

CS2

CS3

CS4

CS5

PK0

PK1

PK2

PK3

PK4

PK5

PK6

PK7

MULTD0

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

CMOS-OUT H

CMOS-IN

CMOS-IN

CMOS-IN

CMOS-IN

CMOS-IN

CMOS-IN

CMOS-IN

CMOS-IN

CMOS-IN

OUT

Not used

Not used

Not used

Not used

IN

IN

IN

IN

IN

Not used

Not used

Not used

Not used

CSRAM-0

TRCS1-0

TRCS-0

AGMRK-1A

PSTPC-1

PSTPD-0

RAM chip select signal (8KB)

Transfer belt separation switch

(TR-SEP-SW:S44)

Transfer belt touch switch(TR-TCH-SW:S43)

Toner transport motor Lock signal

L:NORMAL, H:LOCK, (AUG2-MOT:M15)

Paper stop s witch, L: No paper , H:

When paper is past, (PSTP-SW:S13)

Paper feed status signal

CIRCUIT DESCRIPTION 1 - 18

Page 23

Port Name At reset IN/OUT Signal Name FUNCTION

MULTD1

MULTA

MULTY

CMOS-IN

CMOS-IN

CMOS-OUT H

IN

IN

OUT

REVCL-0

STKCL-0

REVCL-0A

Reverse clutch signal, (REV-CLT:CL2)

Stack clutch control signal, (STK-

CLT:CL3)

Reverse clutch signal, L;ON, H:OFF,

(REV-CLT:CL2)

1 - 19 CIRCUIT DESCRIPTION

Page 24

1.1.4 Scanner CPU (TMP95C063F)

(1) Outline and Features

The same TMP95C063F as the main CPU is used for the scanner CPU. For details, refer to the item

for the main CPU.

(2) Scanner CPU functions

The scanner CPU has respective interface with the system CPU and the ADF, and controls scanner

operations.

It is also in charge of setting the various ASIC (SIPS, SH) parameters for image processing (preprocessing).

(3) Pin assignments of scanner CPU: See the item for the main CPU.

Scanner CPU I/O map

S/N PIN Port Name R IN/OUT Signal Name FUNCTION

117

A0

—

OUT

CPUA0

Address bus

1

—

10

11

12

13

14

15

16

17

18

19

116

115

114

113

112

111

110

109

107

106

105

104

103

102

101

35

144

143

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

AM8/16

AVCC

AVSS

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

IN

—

—

CPUA1

CPUA2

CPUA3

CPUA4

CPUA5

CPUA6

CPUA7

CPUA8

CPUA9

CPUA10

CPUA11

CPUA12

CPUA13

CPUA14

CPUA15

SG

+5V

SG

Address bus

Address bus

Address bus

Address bus

Address bus

Address bus

Address bus

Address bus

Address bus

Address bus

Address bus

Address bus

Address bus

Address bus

Address bus

Bus width selection

A/D converter power supply

A/D converter ground

(mixed 8- and 16-bit buses)

(fixed to 5V)

(fixed to ground)

2

3

4

5

6

7

8

9

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

36

75

76

77

78

79

80

81

82

CLK

D0

D1

D2

D3

D4

D5

D6

D7

—

—

—

—

—

—

—

—

—

—

IN/OUT

IN/OUT

IN/OUT

IN/OUT

IN/OUT

IN/OUT

IN/OUT

IN/OUT

(OPEN)

CPUD0

CPUD1

CPUD2

CPUD3

CPUD4

CPUD5

CPUD6

CPUD7

20

21

22

23

24

25

26

27

28

CIRCUIT DESCRIPTION 1 - 20

Not used

Data bus

Data bus

Data bus

Data bus

Data bus

Data bus

Data bus

Data bus

—

—

—

—

—

—

—

—

—

Page 25

S/N PIN Port Name R IN/OUT Signal Name FUNCTION

29

84

D8

—

IN/OUT

CPUD8

Data bus

—

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

85

86

87

88

89

90

91

3

4

1

2

18

48

84

108

D9

D10

D11

D12

D13

D14

D15

DAOUT0

DAOUT1

DAREFH

DAREFL

DVCC

DVCC

DVCC

DVCC

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

IN/OUT

IN/OUT

IN/OUT

IN/OUT

IN/OUT

IN/OUT

IN/OUT

OUT

—

IN

IN

—

—

—

—

CPUD9

CPUD10

CPUD11

CPUD12

CPUD13

CPUD14

CPUD15

SCNLIM

(OPEN)

+5V

SG

+5V

+5V

+5V

+5V

Data bus

Data bus

Data bus

Data bus

Data bus

Data bus

Data bus

Scanner motor driving

current setting (Vref)

Not used

Reference voltage terminal

(upper limit) for D/A converter

Reference voltage terminal

(lower limit) for D/A converter

5V power supply

5V power supply

5V power supply

5V power supply

—

—

—

—

—

—

—

Increasing this setting

increases the current

—

—

—

—

—

—

—

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

132

5

37

57

74

92

118

40

23

100

99

98

97

96

95

94

93

71

DVCC

DVSS

DVSS

DVSS

DVSS

DVSS

DVSS

EA

NMI

A16

P21/A17

P22/A18

P23/A19

P24/A20

P25/A21

P26/A22

P27/A23

P52

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

IN

IN

OUT

—

—

OUT

—

—

—

—

OUT

+5V

SG

SG

SG

SG

SG

SG

SG

+5V

A16

(OPEN)

(OPEN)

WDTEN

(OPEN)

(OPEN)

(OPEN)

(OPEN)

JIGER

5V power supply

GND terminal

GND terminal

GND terminal

GND terminal

GND terminal

GND terminal

(external access)

Not used

Address bus

Not used

Not used

Watchdog enable

Not used

Not used

Not used

Not used

Enable jig

—

—

—

—

—

—

—

(internal ROM)

Fixed: H

—

—

—

Enable:H, Disable:N

—

—

—

—

At completion of SLG

operation: L

63

70

P53

—

OUT

JIGOK

Jig OK

1 - 21 CIRCUIT DESCRIPTION

At error detection: L

Page 26

S/N PIN Port Name R IN/OUT Signal Name FUNCTION

64

69

P54

—

—

(OPEN)

Not used

—

65

66

67

68

69

70

71

72

73

74

75

76

77

68

67

66

65

64

63

62

61

60

59

58

49

50

RW

CS0

CS2

CS1

P61

P62

P63

CS3

P65

P66

P67

PG00

PG01

—

—

—

—

—

—

—

—

—

—

—

—

—

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

CPURW

CPUCS0

CPUCS2

CPUCS1

VSYNC

FAN3SP

FAN3ON

CPUCS3

PHSCHG

FAN2SP

FAN2ON

DCM-A

DCM-B

Write/Read to special register

SRAM chip select

PROM chip select

SH (CCD) chip select

Image vertical synchronization

SLG Fan speed selection

(SLG-FAN-MOT:M4)

SLG Fan ON/OFF signal

(SLG-FAN-MOT:M4)

SIPS chip select

SH mode switching

OPT Fan speed selection

(OPT-FAN-MOT:M3-2)

OPT Fan ON/OFF

(OPT-FAN-MOT (M3-2)

DCM motor phase A

(DCM-MOT:M2)

DCM motor phase B

(DCM-MOT:M2)

L active

L active

L active

L active

—

High speed: H,

Low speed: L

ON:L,

OFF:H

L active

High speed: H,

Low speed: L

ON:L,

OFF:H

L active

L active

78

79

80

81

82

83

84

85

86

87

88

89

90

91

51

52

53

54

55

56

32

33

34

43

44

45

46

47

PG02

PG03

P74

P75

P76

P77

P80

P81

P82

P83

P84/INT0

P85/INT1

P86/INT2

P87/INT3

—

—

—

—

—

—

OUT

DCM-C

DCM motor phase C

L active

(DCM-MOT:M2)

OUT

DCM-D

DCM motor phase D

L active

(DCM-MOT:M2)

X

IN

X

IN

X

IN

—

—

X

IN

X

IN

X

IN

X

IN

APS1

APS2

APS3

(OPEN)

(OPEN)

APS4

APS5

APS6

SRTS

APS sensor

APS sensor

APS sensor

Not used

Not used

APS sensor

APS sensor

APS sensor

SYS⇒SLG transmission

—

—

—

—

—

L active

interrupt

—

X

IN

(OPEN)

DFRAK

Not used

ADF⇒SLG reception

L active

—

enable signal

—

(OPEN)

Not used

—

92

24

P90

CIRCUIT DESCRIPTION 1 - 22

—

OUT

SCNDIR

Scanner motor rotation

direction, (SCN-MOT:M1)

Page 27

S/N PIN Port Name R IN/OUT Signal Name FUNCTION

93

25

TO1

—

OUT

SCNCLK

Scanner motor CLK

(SCN-MOT:M1)

94

95

96

97

98

99

100

101

102

103

104

105

106

107

26

27

28

29

30

31

14

15

16

17

19

20

21

22

P92

P93/TO3

P94

P95

P96

P97/TO7

TXD0

RXD0

CTS0

PA3

TXD1

RXD1

CTS1

PA7

—

—

—

—

—

—

—

X

—

—

—

X

—

—

OUT

OUT

OUT

OUT

OUT

OUT

OUT

IN

OUT

—

OUT

IN

OUT

OUT

FAN1ON

FAN1SP

FAN4ON

EXPEN

EXPON

EXPPWM

STXD

SRXD

SCTS

(OPEN)

DFTXD

DFRXD

DFAK

DFRQ

OPT Fan ON/OFF

(OPT-FAN-MOT:M3-1)

OPT Fan speed selection

(OPT-FAN-MOT:M3-1)

Not used

Exposure lamp output enable

Exposure lamp ON

Exposure intensity adjustment

SLG⇒SYS serial I/F send data

SYS⇒SLG serial I/F

receive data

SLG⇒SYS transmission

interrupt

Not used

SLG⇒ADF serial I/F send data

ADF⇒SLG serial I/F receive data

SLG⇒ADF reception

enable signal

SLG⇒ADF transmission

request signal

ON: L,

OFF: H

High speed: H,

Low speed: L

Enable: L

Lamp ON: L

PWM

Serial

Serial

L active

—

Serial

Serial

L active

L active

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

6

PB0/TI8/INT4

7

INT5

8

PB2/TO8

9

PB3/TO9

PB4/TIA/INT6

10

11

PB5/TIB/INT7

12

PB6/TOA

13

PB7/TOB

133

PC0/AN0

134

PC1/AN1

135

PC2/AN2

136

PC3

137

PC4

138

PC5

139

PC6

—

—

—

—

X

X

—

—

—

—

—

—

—

—

↑

IN

—

—

OUT

(OPEN)

PWDNCK

(OPEN)

(OPEN)

DFRRQ

Not used

Power down check

Not used

Not used

ADF⇒SLG reception

Power off: L

L active

—

—

—

request signal

IN

SCHOM

Scanner motor home SW

Home position: H

(HOME-SW:S2)

↑

IN

IN

—

—

—

IN

IN

—

IN

SCNT

DFCNT

SG

SG

SG

EWSCNT

PGCNT

(OPEN)

DSWCNT

System board connection

ADF connection

Not used

Not used

Not used

EWS connection

Pattern Generator connection

Not used

DIP SW board/adjustment

Connection: L

Connection: L

—

—

—

Connection: L

Connection: L

—

Connection: L

jig connection

1 - 23 CIRCUIT DESCRIPTION

Page 28

S/N PIN Port Name R IN/OUT Signal Name FUNCTION

123

140

PC7

—

IN

24VCHK

24V power supply check

Power drop: L

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

131

130

129

128

127

126

125

124

123

122

121

120

119

73

41

141

142

42

72

PD0

PD1

PD2

PD3

PD4

PE0

PE1

PE2

PE3

PE4

PE5

PE6

PE7

RD

RESET

VREFH

VREFL

WDTOUT

WR

—

—

—

—

—

—

—

—

—

—

OUT

OUT

OUT

OUT

OUT

X

IN

X

IN

X

IN

X

IN

X

IN

X

IN

X

IN

X

IN

OUT

↑

IN

IN

SCNMD0

SCNMD1

SCNMD2

SCNMD3

SCNHLD

DIPSW8

DIPSW7

DIPSW6

DIPSW5

DIPSW4

DIPSW3

DIPSW2

DIPSW1

CPURD

CPURST

+5V

Scanner motor step angle

setting (SCN-MOT:M1)

Scanner motor hold

Scanner unit standalone

mode

Reading

Reset

Reference voltage input for

For adjustment

Enable: L

Reset: L

—

A/D converter (H)

IN

SG

Reference voltage input for

—

A/D converter (L)

OUT

WDTOUT

Watchdog timer output

Microcontroller malfunc-

tion (out of control): L

OUT

CPUWR

Write

Enable: L

143

38

144

39

X1

X2

—

—

IN/OUT

IN/OUT

X1

X2

R : Programmable pull-up resistor

↑ : Internal pull-up enabled

X : Internal pull-up disabled

— : No internal pull-up function

CIRCUIT DESCRIPTION 1 - 24

Oscillator terminal

Oscillator terminal

—

—

Page 29

1.1.5 Laser CPU (TMP95C063F)

(1) Outline and features

The same TMP95C063F as the main CPU is used f or the Laser CPU. For details, ref er to the item for

the main CPU.

(2) Laser CPU functions

The laser CPU has an interface with the main CPU , and controls the inside of the laser unit (rotation

of the polygonal motor, galvanic mirror control, laser power control, etc.)

It is also in charge of setting the various ASIC (POPS) parameters for image processing (post-processing).

(3) Pin assignments of laser CPU: See the item for the main CPU.

Laser CPU I/O map

Port Name At reset R IN/OUT Signal Name FUNCTION

P97/TO7

CMOS-IN PULL-UP

—

OUT

(FANSP-1)

Fan speed selection, L: High speed,

H: Low speed, (LSU-FAN-MOT: M6)

P96/TI6

P95/TO5

P94/TI4

P93/TO3

P92/TI2

P91/TO1

P90/TI0

P87/INT3

P86/INT2

P85/INT1

P84/INT0

P83/NMI2

P82/WAIT

P81/SCOUT

P80/BS

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

—

—

—

—

—

—

—

—

—

—

IN

IN

IN

IN

IN

IN

FAN-0

(WUL-0)

(WLL-0)

OFFST-0

BMSW2-1

BMSW1-1

BMSW0-1

BUSY-0

PVDEN-0

CNTRD-1

COMINT-0

COMND-1

(CLKEN-1)

BUSEN-1

Fan, L: ON, H: OFF

Beam sensor window upper limit

Beam sensor window lower limit

Beam sensor detection mode, L: Detection

Beam sensor select

Beam sensor busy (A/D conversion in

progress), Interrupt at rise at end of conversion

Interrupt at rise at end of page, L: Print area

Reading from POPS possible, H: Read

Interrupt from monitor IC, L: Buffer empty

Command/data select output to monitor IC

Crystal oscillator enable,

L: Disable, H: Enable

Bus release with POPS at EWS

connection, H: Enable

OUT

↑

↑

OUT

OUT

OUT

OUT

↑

X

X

OUT

OUT

OUT

P77/PG13

P76/PG12

P75/PG11

P74/PG10

P73/PG03

P72/PG02

P71/PG01

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

—

—

—

—

—

—

↑

OUT

OUT

OUT

OUT

OUT

OUT

ERR-1

IN

LVDEN-0

LE-0

LDOFF-0

DDISD-1

DDISC-1

DDISB-1

1 - 25 CIRCUIT DESCRIPTION

HYSNC error/PWM calibration BUSY,

H: Error

L-CPU secondary scanning direction

sync signal

Laser enable, L: Enable

Forced laser OFF during manual feed, L: OFF

Laser driver D forced stop

Laser driver C forced stop

Laser driver B forced stop

Page 30

Port Name At reset R IN/OUT Signal Name FUNCTION

P70/PG00

P67/UCAS3/UW3/

WE3

CMOS-IN PULL-UP

TTL-OUT H

—

—

OUT

OUT

DDISA-1

CNTST-0

Laser driver A forced stop

HSYNC count of adjustment sensor,

L: Count

P66/LCAS3/LW3/

REFOUT

P65/CAS3/WE3

P64/CS3/RAS3

P63/UCAS1/UW1/

WE1

P62/LCAS1/LW1/

REFOUT

P61/CAS1/WE1

P60/CS1/RAS1

P57/CS2

P56/CS0

P55/RW

P54/BUSAK

P53/BUSRQ

P52/HWR

WR

RD

TTL-OUT H

TTL-OUT H

TTL-OUT H

TTL-OUT H

TTL-OUT H

TTL-OUT H

TTL-OUT H

TTL-OUT L

TTL-OUT H

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

—

—

—

—

—

—

—

—

—

—

—

——

—

—

—

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

Not used

Not used

Not used

OUT

OUT

CSNVM-0

GDALAT-0

CSGDAC-0

(DAWR-0)

(DASC1-0)

(DASC0-0)

CSPOPS-0

CSPROM-0

CSSRAM-0

GLVMT-1

WR-0

RD-0

Serial EEPROM chip select, L: Select

Galvanic mirror DAC latch, L: Latch

Galvanic mirror DAC chip select, L: Select

Beam sensor DAC latch (at compara-

tor)

Beam sensor DAC select

(at comparator)

POPS chip select, L: Select

PROM chip select, L: Select

SRAM chip select, L: Select

Galvanic mirror driver mute, H: Mute

External memory write signal

External memory read signal

P27/A23

P26/A22

P25/A21

P24/A20

P23/A19

P22/A18

P21/A17

P20/A16

P17/D15

P16/D14

P15/D13

P14/D12

P13/D11

P12/D10

P11/D9

TTL-OUT H

TTL-OUT H

TTL-OUT H

TTL-OUT H

TTL-OUT H

TTL-OUT H

TTL-OUT H

TTL-OUT H

TTL 3STATE

TTL 3STATE

TTL 3STATE

TTL 3STATE

TTL 3STATE

TTL 3STATE

TTL 3STATE

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

IN/OUT

IN/OUT

IN/OUT

IN/OUT

IN/OUT

IN/OUT

IN/OUT

LDOND-0

LDONC-0

LDONB-0

LDONA-0

LDRDY-0

SCRST-1

VDIS-1

A16

D15

D14

D13

D12

D11

D10

D9

Laser D forced ON, L: ON, H: OFF

Laser C forced ON, L: ON, H: OFF

Laser B forced ON, L: ON, H: OFF

Laser A forced ON, L: ON, H: OFF

Illuminating on drum inhibit signal, L:

Ready, H: Copy

PWM calibration, H: Calibration

IVDEN-0 inhibit during control between

pages, H: Beam control in progress

Address bus

Data bus

Data bus

Data bus

Data bus

Data bus

Data bus

Data bus

CIRCUIT DESCRIPTION 1 - 26

Page 31

Port Name At reset R IN/OUT Signal Name FUNCTION

P10/D8

D7

TTL 3STATE

TTL 3STATE

—

—

IN/OUT

IN/OUT

D8

D7

Data bus

Data bus

D6

D5

D4

D3

D2

D1

D0

A15

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

TTL 3STATE

TTL 3STATE

TTL 3STATE

TTL 3STATE

TTL 3STATE

TTL 3STATE

TTL 3STATE

TTL OUT

TTL OUT

TTL OUT

TTL OUT

TTL OUT

TTL OUT

TTL OUT

TTL OUT

TTL OUT

TTL OUT

TTL OUT

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

IN/OUT

IN/OUT

IN/OUT

IN/OUT

IN/OUT

IN/OUT

IN/OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

D6

D5

D4

D3

D2

D1

D0

A15

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

Data bus

Data bus

Data bus

Data bus

Data bus

Data bus

Data bus

Address bus

Address bus

Address bus

Address bus

Address bus

Address bus

Address bus

Address bus

Address bus

Address bus

Address bus

A4

A3

A2

A1

A0

PA7/SCLK1

PA6/CTS1

PA5/RXD1

PA4/TXD1

PA3/SCLK0

PA2/CTS0

PA1/RXD0

PA0/TXD0

PB7/TOB

PB6/TOA

PB5/TIB/INT7

TTL OUT

TTL OUT

TTL OUT

TTL OUT

TTL OUT

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

—

—

—

—

——

—

—

↑

—

—

↑

↑

—

—

—

X

OUT

OUT

OUT

OUT

OUT

OUT

OUT

IN

OUT

OUT

IN

IN

OUT

OUT

OUT

IN

A4

A3

A2

A1

A0

SCLK-1

LDDALD-0

RXD-1

TXD-1

RTS-0

CTS-0

RXD-0

TXD-0

LSBSY-0

WDEN-0

PMOK-0

Address bus

Address bus

Address bus

Address bus

Address bus

Serial clock for laser power DAC/EEPROM

Serial latch for laser power DAC, L: Latch

Serial data for EEPROM read

Serial data for laser power DAC/

EEPROM write

L-CPU⇒M-CPU send request signal

M-CPU⇒L-CPU serial receive data

M-CPU⇒L-CPU serial receive data

L-CPU⇒M-CPU serial send data

Laser write system bus busy, L: Ready

Watchdog enable, L: Enable

Polygonal mirror motor PLLOK, L:OK, (POL-MOT:M5)

1 - 27 CIRCUIT DESCRIPTION

Page 32

Port Name At reset R IN/OUT Signal Name FUNCTION

PB4/TIA/INT6

PB3/TO9

CMOS-IN PULL-UP

CMOS-IN PULL-UP

—

—

OUT

OUT

PMON-0

(PMBRK-0)

Polygonal mirror motor ON, L:ON

Polygonal mirror motor brake, L:ON

PB2/TO8

PB1/TI9/INT5

PB0/T18/INT4

PC7/AN7

PC6/AN6

PC5/AN5

PC4/AN4

PC3/AN3

PC2/AN2

PC1/AN1

PC0/AN0

PD4

PD3

PD2

PD1

PD0

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN

CMOS-IN

CMOS-IN

CMOS-IN

CMOS-IN

CMOS-IN

CMOS-IN

CMOS-IN

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

—

—

—

—

—

—

—

—

—

IN

PMCLK-1

PDWN-1

Polygonal mirror motor reference clock

When 5V drops to 0V: H,

OUT

X

Otherwise: L, Rising edge detection

↑

IN

MVDEN-0

M-CPU secondary scanning direction

sync signal, L: Enable

BMAD7-1

IN

BMAD6-1

IN

BMAD5-1

IN

BMAD4-1

IN

BMAD3-1

IN

BMAD2-1

IN

BMAD1-1

IN

BMAD0-1

IN

X

IN

EWSCN-0

Beam sensor AD value (12 bits)

Bus release at EWS connection,

L: POPS⇔L-CPU release

↑

↑

↑

↑

IN

IN

IN

IN

BMAD11-1

BMAD10-1

BMAD9-1

BMAD8-1

Beam sensor AD value (12 bits)

PE7

PE6

PE5

PE4

PE3

PE2

PE1

PE0

DAREFH

DAREFL

DAOUT0

DAOUT1

NMI

CLK

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN PULL-UP

CMOS-IN

TTL-OUT

—

—

—

—

—

—

—

—

—

—

—

—

—

—

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

—

—

—

—

IN

OUT

BMDA7-1

BMDA6-1

BMDA5-1

BMDA4-1

BMDA3-1

BMDA2-1

BMDA1-1

BMDA0-1

5V

GND

5V

(SNSCK-1)

Beam sensor comparison value (at

comparator)

Beam position sensor (secondary scanning

direction) comparison value

Beam sensor HYSNC detection

threshold value

Dual-use DA output data

Clock to SNS

CIRCUIT DESCRIPTION 1 - 28

Page 33

Port Name At reset R IN/OUT Signal Name FUNCTION

WDOUT

EA

TTL-OUT

—

—

OUT

WDTOUT-0

GND

At microcontroller out of control: L, normal: H

AM8/16

RESET

VREFH

VREFL

AVCC

AVSS

X1/X2

DVCC

DVSS

—

—

—

—

—

—

—

—

—

IN

IN

IN

GND

CPURST-0

5V

GND

5V

GND

R : Programmable pull-up resistor. Signals in parentheses are unused.

↑ : Pulled up

X : Not pulled up

— : No pull-up functions

Mixed 8- and 16-bit buses at L

Reset signal

A/D converter reference input signal

A/D converter reference input signal

A/D converter power supply

A/D converter power supply

Oscillator terminal

5V power supply

Ground terminal

1 - 29 CIRCUIT DESCRIPTION

Page 34

1.1.6 System CPU (NR4650)

(1) Features

The NR4650 64-bit microprocessor uses MIPS’s RISC architecture and features the following advanced functions.

It is also completely compatible in terms of software architecture with Integrated De vice Technology’s

IDT79RV4650.

❍ 64-bit microprocessor with built-in advanced functions

• 64-bit integer operations

• 64-bit register

• 100 MHz, 133 MHz clock speeds

❍ High performance

• 133 MIPS (at 133 MHz clock speed)

• Integer multiplier having 66.7M Mul-Add/sec performance (at 133 MHz clock speed)

• Single-precision floating point processor of 44 MFLOP/sec (at 133 MHz clock speed)

• >300,000 dhrystone/sec (at 133 MHz clock speed) (175 dhrystone MIPS)

• Cache memory of 8 Kbytes each for instructions and data

• Integer DSP function supported

• High-speed interrupt decoding

• Cache lock function

❍ Lower power consumption

• 3.3V power voltage

• Power management function using standby mode

❍ Large internal cache memory

• Cache memory of 8 Kbytes each for instructions and data

• 2-way set-associative system

• Write back and write through supported

❍ Highly compatible with the NR3000 and NR4600 family

• Completely upwardly compatible with NR3000 and NR4600 family application software

❍ Low cost

• 32-bit bus interface mode can be set

• Low cost achieved by elimination of TLB function and double-precision floating point processor

❍ Short development provided by system support

• Extensive support for real-time operation

• Easier development of software by high compatibility with MPS III instruction sets

❍ Wide range of installable applications

• Game equipment

• Multimedia equipment

• Networking equipment

• Printers

❍ 5V interface support (only on NR4650G)

• 5V signals can be input.

CIRCUIT DESCRIPTION 1 - 30

Page 35

(2) System CPU functions

The system CPU is used in combination with a system control LSI with dedicated PCI bridge. This

CPU has interfaces with the HDD, main CPU and scanner CPU, and performs control of ASIC in the

SYS board, image data processing (compression, decompression, etc.), connection processing with

external network lines (LAN, DSS, etc.), and control of the control panel.

The PCI bus is released to the outside via the MTB board, and is constructed to be connectable to a

LAN printer board and SCSI board.

The control program is stored in external ROM (F-ROM).

The download function can be used to read new programs from a personal computer (PC).

Adjustment values for the clock and the system are stored together with setting values in battery

backed up internal RAM.

(3) Pin assignment of system CPU

0.5 mm pitch 208-pin QFP type (all models)

157

156

105

104

TOP View

208 Pin QFP

208

53

1 52

1 - 31 CIRCUIT DESCRIPTION

Page 36

(4) Names of Terminals and Functions