SGS Thomson Microelectronics M48Z35-70MH1, M48Z35, M48Z35Y-70PC1, M48Z35Y-70MH1, M48Z35Y Datasheet

...

1/18August 1999

M48Z35

M48Z35Y

256 Kbit (32Kb x 8) ZEROP OWER® SRAM

■ INTEGRATED ULTRA LOW POWER SRAM,

POWER-FAIL CONTROL CIRCUIT and

BATTERY

■ READ CYCLE TIME EQUALS WRITE CYCLE

TIME

■ AUTOMATIC POWER-FAIL CHIP DESELECT

and WRITE PROTECTION

■ WRITE PROTECT VOLTAGES

(V

PFD

= Power-fail Deselect Voltage):

– M48Z35: 4.50V ≤ V

PFD

≤ 4.75V

– M48Z35Y: 4.20V ≤ V

PFD

≤ 4.50V

■ SELF-CONTAINED BATTERY in th e CAPHAT

DIP PACKAGE

■ PACKAGING INCLUDES a 28-LEAD SOIC and

SNAPHAT

®

TOP (to be Ordered Separately)

■ SOIC PACKAGE PROVIDES D IREC T

CONNECTION for a SNAPHAT TOP which

CONTAINS the BATTERY and CRYSTAL

■ PIN and FUNCTION COMPATIBLE with

JEDEC STANDARD 32K x8 SRAMs

DESCRIPTION

The M48Z35/35Y ZEROPOWER

®

RAM is a 32

Kbit x8 non-volatile static RAM that integrates

power-fail deselect circuitry and battery control

logic on a single die. The monolithi c chip is available in two special packages to provide a highly integrated battery backed-up memory solution.

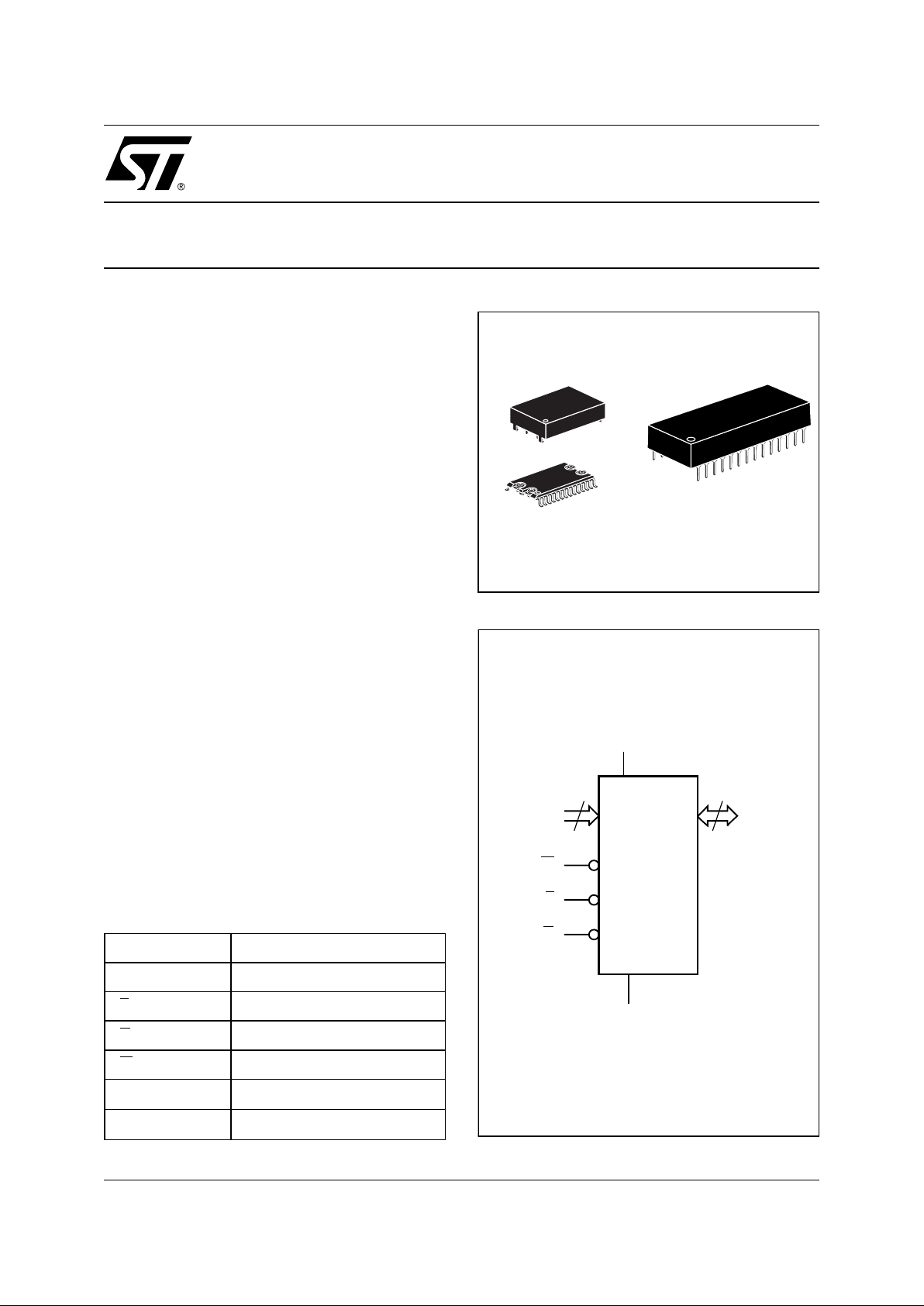

Figure 1. Logic Diagram

AI01616D

15

A0-A14

W

DQ0-DQ7

V

CC

M48Z35

M48Z35Y

G

V

SS

8

E

Table 1. Signal Names

A0-A14 Address Inputs

DQ0-DQ7 Data Inputs / Outputs

E

Chip Enable

G

Output Enable

W

Write Enable

V

CC

Supply Voltage

V

SS

Ground

28

1

28

1

SOH28 (MH)

SNAPHAT (SH)

Battery

PCDIP28 (PC)

Battery CAPHAT

M48Z35, M48Z35Y

2/18

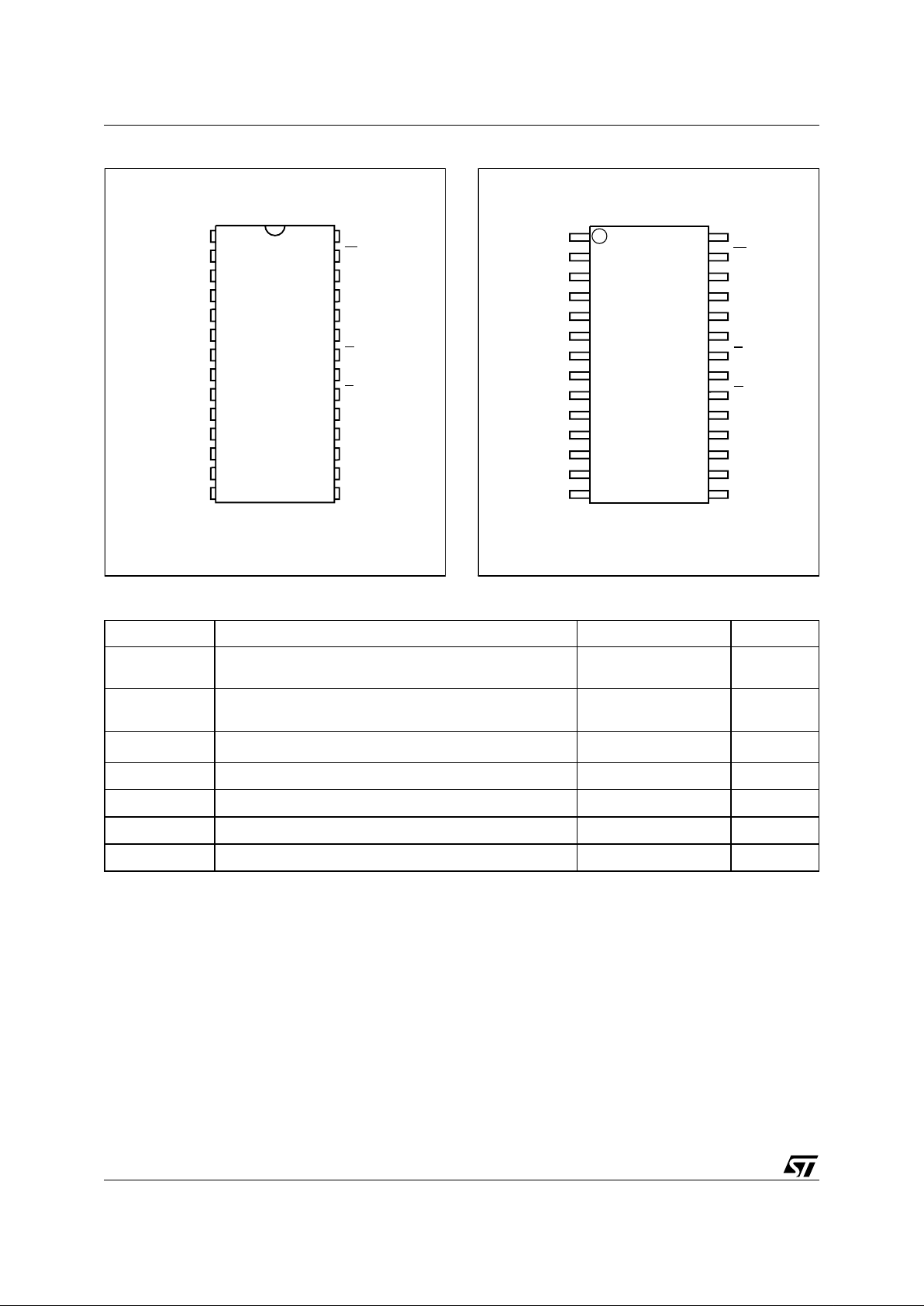

Figure 2A. DIP Pin Connections

A1

A0

DQ0

A7

A4

A3

A2

A6

A5

A13

A10

A8

A9

DQ7

W

A11

G

E

DQ5DQ1

DQ2

DQ3V

SS

DQ4

DQ6

A12

A14 V

CC

AI01617D

M48Z35

M48Z35Y

8

1

2

3

4

5

6

7

9

10

11

12

13

14

16

15

28

27

26

25

24

23

22

21

20

19

18

17

Table 2. Absolute Maximum Ratings

(1)

Note: 1. Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress

rating only and functional operation of the device at these or a ny other conditions above those indicat ed in the operational section

of this spec ification is not im plied. Exposure t o the abso lute max imum rat ing cond itions for extende d period s of tim e may affe ct

reliability.

2. Soldering temperature not to exceed 260°C for 10 seconds (total thermal budget not to exceed 150°C for longer than 30 seconds).

CAUTION: Negative undershoo ts bel ow –0.3V are not al l owed on any pin whi l e i n the Battery Back-up mode.

CAUTION: Do NOT wave solder SOIC to avoid damaging SNAPHA T sockets.

Symbol Parameter Value Unit

T

A

Ambient Operating Temperature Grade 1

Grade 6

0 to 70

–40 to 85

°C

T

STG

Storage Temperature (VCC Off) SNAPHAT

SOIC

–40 to 85

–55 to 125

°C

T

SLD

(2)

Lead Solder Temperature for 10 seconds 260 °C

V

IO

Input or Output Voltages –0.3 to 7 V

V

CC

Supply Voltage –0.3 to 7 V

I

O

Output Current 20 mA

P

D

Power Dissipation 1 W

Figure 2B. SOIC Pin Connections

AI02303C

8

2

3

4

5

6

7

9

10

11

12

13

14

22

21

20

19

18

17

16

15

28

27

26

25

24

23

1

A1

A0

DQ0

A7

A4

A3

A2

A6

A5

A13

A10

A8

A9

DQ7

W

A11

G

E

DQ5DQ1

DQ2

DQ3V

SS

DQ4

DQ6

A12

A14 V

CC

M48Z35Y

3/18

M48Z35, M48Z35Y

The M48Z35/35Y is a non-volatile pin and function

equivalent to any JEDEC standard 32K x8 SRAM.

It also easily fits into many ROM, EPROM, and

EEPROM sockets, providing the non-volatility of

PROMs without any requirement for special write

timing or limitations on the n umber of writes that

can be performed. The 28 pin 600mil DIP

CAPHAT™ houses the M48Z35/35Y silicon with a

long life lithium button cell in a single package.

The 28 pin 330mil SOIC provides sockets with

gold plated contacts at both ends for direct con-

nection to a separate SNAPHAT housing cont aining the battery. The unique design allows the

SNAPHAT battery p acka ge t o b e m ount ed o n t op

of the SOIC package after the c ompletion of the

surface mount process. Insertion of the SNAPHAT

housing after reflow prevents potential battery

damage due to the high temperatures required for

device surface-mounting. The SNAPH AT housing

is keyed to prevent reverse insertion.

Table 3. Operating Modes

(1)

Note: 1. X = VIH or VIL; VSO = Battery Back-up Swit ch ov er Volta ge.

2. See T able 7 for deta ils .

Mode

V

CC

E G W DQ0-DQ7 Power

Deselect

4.75V to 5.5V

or

4.5V to 5.5V

V

IH

X X High Z Standby

Write

V

IL

X

V

IL

D

IN

Active

Read

V

IL

V

IL

V

IH

D

OUT

Active

Read

V

IL

V

IH

V

IH

High Z Active

Deselect

V

SO

to V

PFD

(min)

(2)

X X X High Z CMOS Standby

Deselect

≤

V

SO

X X X High Z Battery Back-up Mode

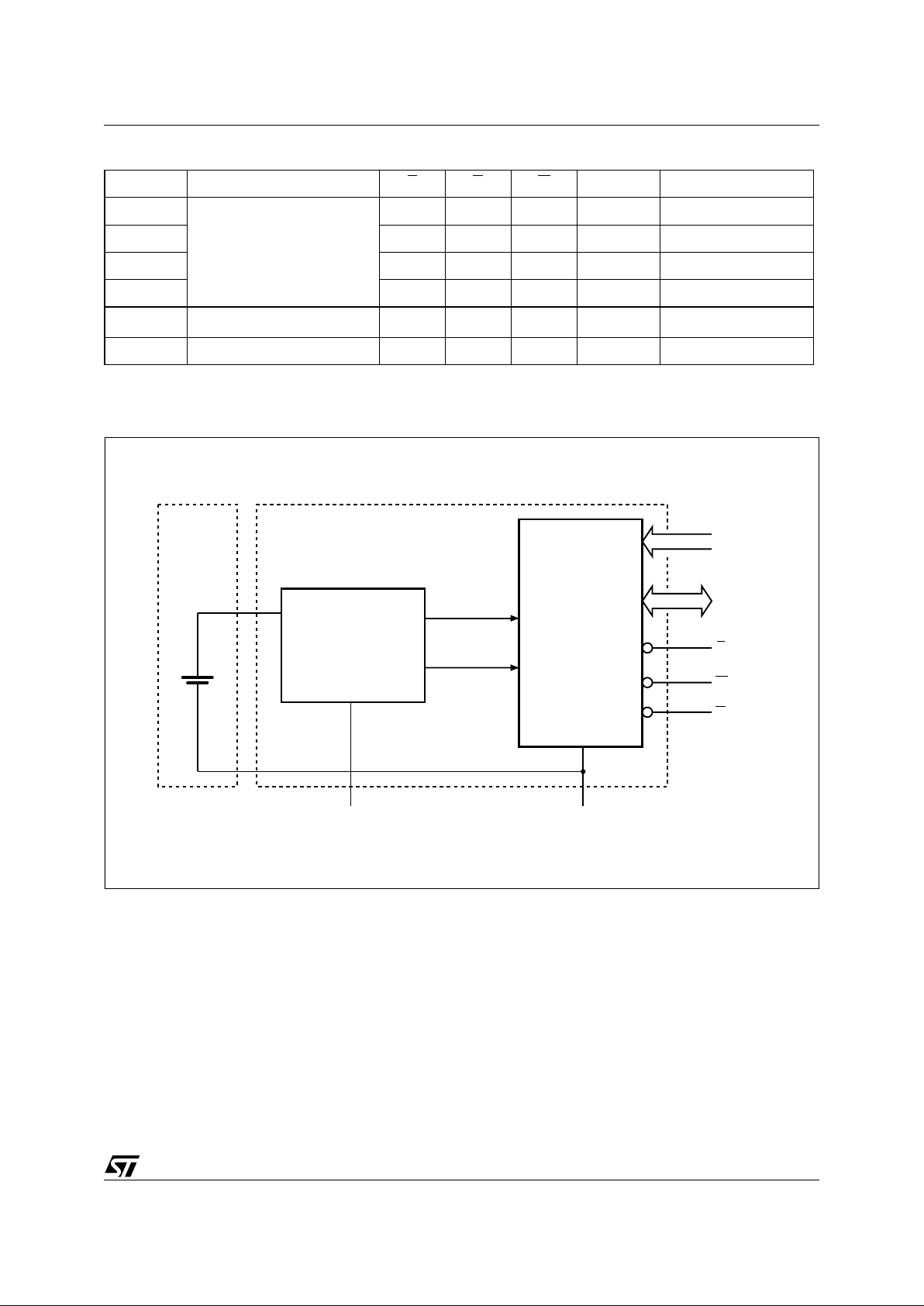

Figure 3. Block Diagram

AI01619B

LITHIUM

CELL

V

PFD

V

CC

V

SS

VOLTAGE SENSE

AND

SWITCHING

CIRCUITRY

32K x 8

SRAM ARRAY

A0-A14

DQ0-DQ7

E

W

G

POWER

M48Z35, M48Z35Y

4/18

The SOIC and battery packages are shipped separately in plastic anti-static tubes or in Tape & Reel

form.

For the 28 lead SOIC, the battery package (i.e.

SNAPHAT) part number is "M4Z28-BR00SH1".

The M48Z35/35Y also has its own Power-fail Detect circuit. The control circuitry constantly monitors the single 5V supply for an out of tolerance

condition. When V

CC

is out of tolerance, the circuit

write protects the S RAM, p roviding a high degree

of data security in the midst of unpredictable s ystem operation brought on by low V

CC

. As VCC falls

below approximately 3V, the control circuitry connects the battery which maintains data until valid

power returns.

READ MODE

The M48Z35/35Y is in the Read Mode whenever

W

(Write Enable) is high, E (Chip Enable) is low.

The device architecture allows ripple-through access of data from eight of 264,144 locations in the

static storage array. Thus, the unique address

specified by the 15 Address Inputs defines which

one of the 32,768 bytes of data is to be accessed.

Valid data will be available at the Data I/O pins

within Address Access time (t

AVQV

) after the last

address input signal is stable, providing that the E

and G access times are also satisfied. If the E and

G

access times are not met, valid data will be

available after the latter of the Chip Enable Access

time (t

ELQV

) or Output Enable Access time

(t

GLQV

).

The state of the eight three-s tate Da ta I/O si gnals

is controlled by E

and G. If the outputs are activat-

ed before t

AVQV

, the data lines will be driven to an

indeterminate state until t

AVQV

. If the Ad dres s In-

puts are changed while E

and G remain active,

output dat a will rem ain v alid for Outp ut Dat a Hold

time (t

AXQX

) but will go indeterminate until the next

Addr e ss Access.

WRITE MODE

The M48Z35/35Y is in the Write Mode whenever

W

and E are low. The start of a write is referenced

from the latter occurring f alling edge of W

or E. A

write is terminated by the earlier rising edge of W

or E. The addresses must be held valid throughout

the cycle. E

or W must return high for a minimum

of t

EHAX

from Chip Enable or t

WHAX

from Write Enable prior to the initiation of another read or write

cycle. Data -in must be vali d t

DVWH

prior to the end

of write and remain valid for t

WHDX

afterward. G

should be kept high during write cycles to avoid

bus contention; although, if the output bus has

been activated by a low on E

and G, a low on W

will disab le the ou t pu t s t

WLQZ

after W falls.

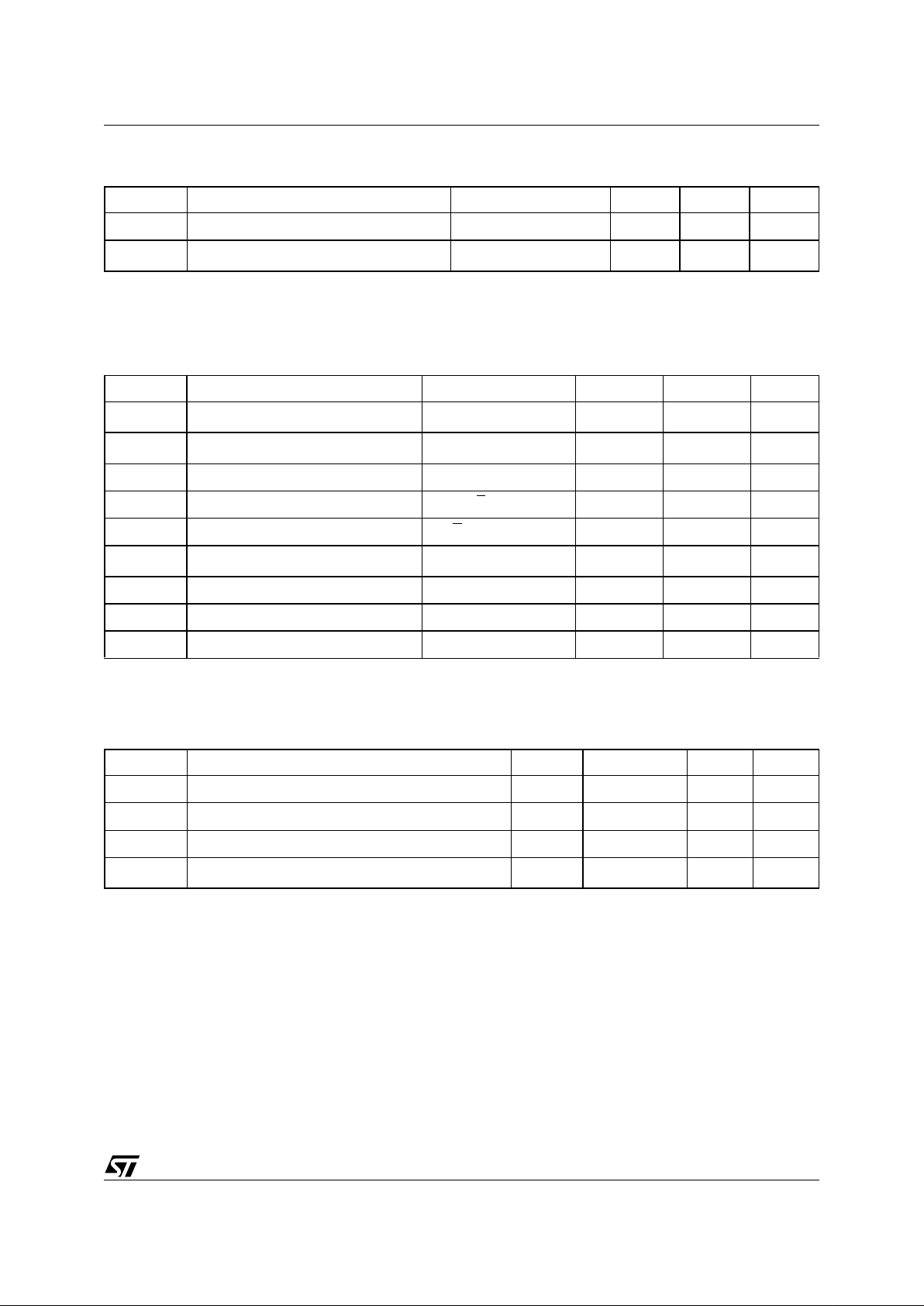

Table 4. AC Measurement Conditions

Note that Output Hi-Z is defined as the point where data is no longer

driven.

Input Rise and Fall Times

≤

5ns

Input Pulse Voltages 0 to 3V

Input and Output Timing Ref. Voltages 1.5V

Figure 4. AC Testing Load Circuit

AI03211

CL = 100pF or

5pF

CL includes JIG capacitance

645Ω

DEVICE

UNDER

TEST

1.75V

5/18

M48Z35, M48Z35Y

Table 5. Capacitance

(1, 2)

(T

A

= 25 °C)

Note: 1. Effective capacitan ce measured wi th power su pply at 5V.

2. Sampled only, not 100% tested.

3. Outputs deselect ed.

Table 6. DC Characteristics

(T

A

= 0 to 70 °C or –40 to 85 °C; VCC = 4.75V to 5.5V or 4.5V to 5.5V)

Note: 1. Outputs deselected .

2. Negativ e s p i k e s of –1V allo wed for up t o 10 ns once pe r cycle .

Table 7. Power Down/Up Trip Points DC Characteristics

(1)

(TA = 0 to 70 °C or –40 to 85 °C)

Note: 1. All voltages referenced to VSS.

2. At 25 ° C.

Symbol Parameter Test Condition Min Max Unit

C

IN

Input Capacitance

V

IN

= 0V

10 pF

C

IO

(3)

Input / Output Capacitance

V

OUT

= 0V

10 pF

Symbol Parameter Test Condition Min Max Unit

I

LI

(1)

Input Leakage Current

0V ≤ V

IN

≤ V

CC

±1 µA

I

LO

(1)

Output Leakage Current

0V ≤ V

OUT

≤ V

CC

±5 µA

I

CC

Supply Current Outputs open 50 mA

I

CC1

Supply Current (Standby) TTL

E

= V

IH

3mA

I

CC2

Supply Current (Standby) CMOS

E

= VCC – 0.2V

3mA

V

IL

(2)

Input Low Voltage –0.3 0.8 V

V

IH

Input High Voltage 2.2

V

CC

+ 0.3

V

V

OL

Output Low Voltage

I

OL

= 2.1mA

0.4 V

V

OH

Output High Voltage

I

OH

= –1mA

2.4 V

Symbol Parameter Min Typ Max Unit

V

PFD

Power-fail Deselect Voltage (M48Z35) 4.5 4.6 4.75 V

V

PFD

Power-fail Deselect Voltage (M48Z35Y) 4.2 4.35 4.5 V

V

SO

Battery Back-up Switchover Voltage (M48Z35/35Y) 3.0 V

t

DR

(2)

Expected Data Retention Time 10 YEARS

M48Z35, M48Z35Y

6/18

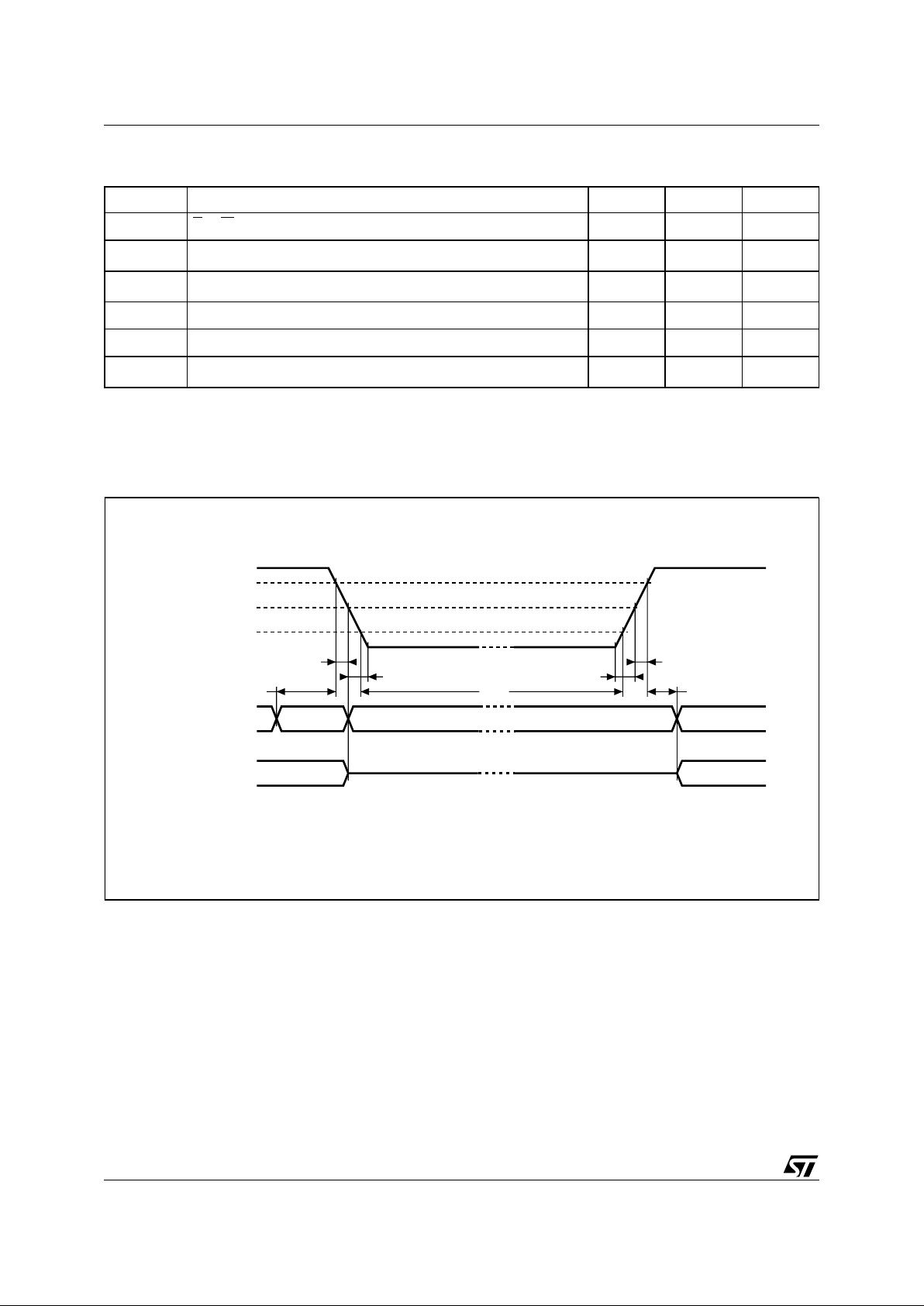

Table 8. Power Down/Up AC Characteristics

(T

A

= 0 to 70 °C or –40 to 85 °C)

Note: 1. V

PFD

(max) to V

PFD

(min) fall time of less than tF may result in deselection/write protection not occurring until 200µs after VCC pass-

es V

PFD

(min).

2. V

PFD

(min) to VSS fall time of less than tFB may cause corruption of RA M data.

3. t

REC

(min) = 20ms for industri al tempera ture grade (6) device.

Symbol Parameter Min Max Unit

t

PD

E or W at VIH before Power Down

0 µs

t

F

(1)

V

PFD

(max) to V

PFD

(min) VCC Fall Time

300 µs

t

FB

(2)

V

PFD

(min) to VSS VCC Fall Time

10 µs

t

R

V

PFD

(min) to V

PFD

(max) VCC Rise Time

10 µs

t

RB

VSS to V

PFD

(min) VCC Rise Time

1µs

t

REC

(3)

V

PFD

(max) to Inputs Recognized

40 200 ms

Figure 5. Power Down/Up Mode AC Waveforms

AI01168C

V

CC

INPUTS

(PER CONTROL INPUT)

OUTPUTS

DON'T CARE

HIGH-Z

tF

tFB

tR

tPD

tRB

tDR

VALID VALID

(PER CONTROL INPUT)

RECOGNIZEDRECOGNIZED

V

PFD

(max)

V

PFD

(min)

VSO

tREC

Loading...

Loading...