64 Kbit (8Kb x 8) ZEROPOWER® SRAM

INTEGRATED ULTRA LOW POWER SRAM,

POWER-FAIL CONTROL CIRCUIT and

BATTERY

UNLIMITED WRITE CYCLES

READ CYCLE TIME EQUALS WRITE CYCLE

TIME

AUTOMATIC P OWER-F AIL CHIP DES ELECT and

WRITE PROTECTION

WRITE PROTECT VOLT AGES

= Power-fail Deselect Voltage):

(V

PFD

– M48Z08: 4.50V ≤ V

– M48Z18: 4.20V ≤ V

SELF-CONTAINED BATTERY in the CAPHAT

DIP PACKAGE

PACKAGING INCLUDES a 28 LEAD SOIC

and SNAPHAT

®

TOP (to be Ordered

Separately)

SOIC PACKAGE PROVIDES DIRECT

CONNECTION for a SNAPHAT TOP which

CONTAINS the BATTERY

PIN and FUNCTION COMPATIBLE with the

DS1225 and JEDEC STANDARD 8K x 8

SRAMs

PFD

PFD

4.75V

≤

4.50V

≤

SNAPHAT (SH)

Battery

28

28

1

SOH28 (MH)

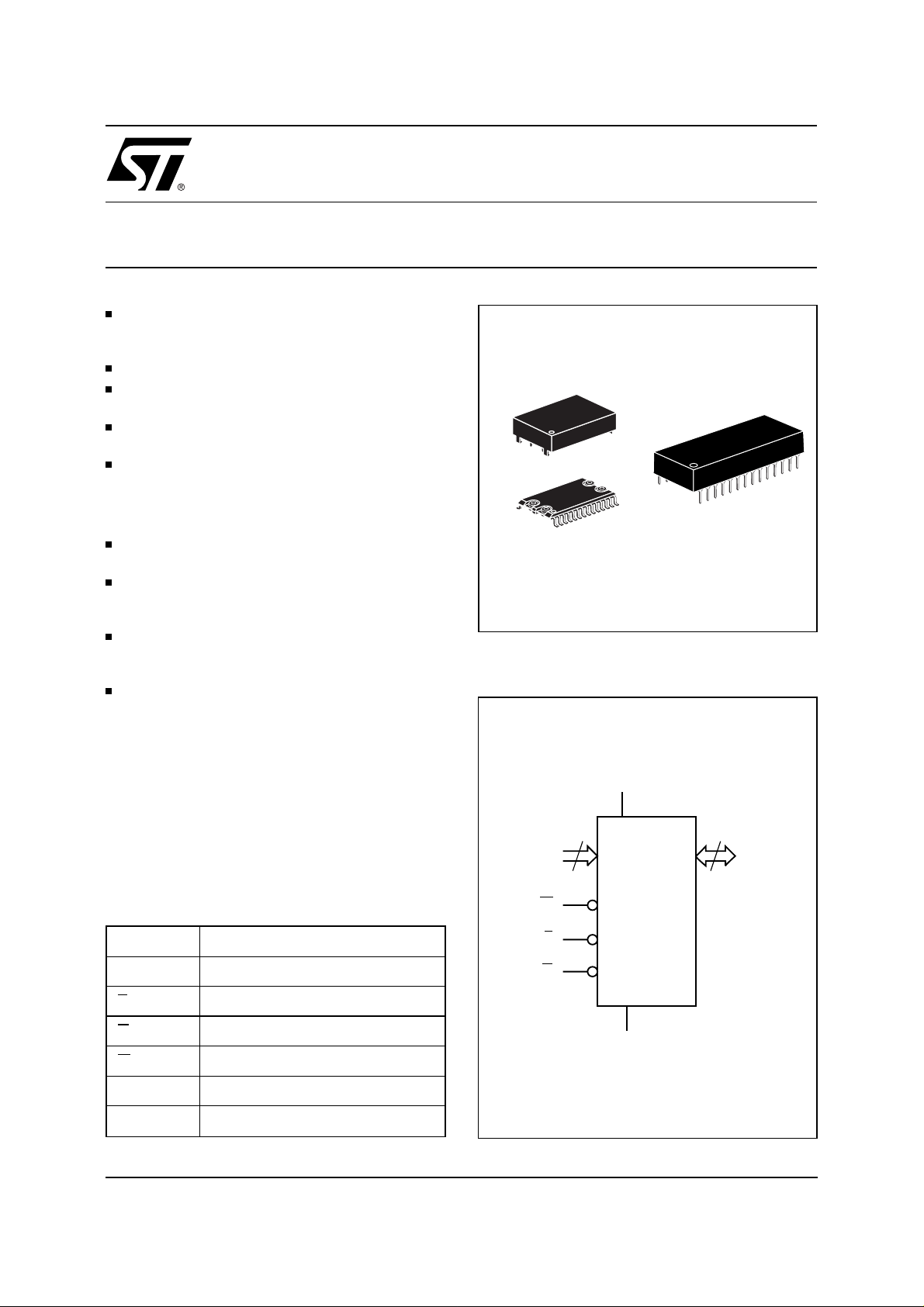

Figure 1. Logic Diagram

M48Z08

M48Z18

1

PCDIP28 (PC)

Battery CAPHAT

DESCRIPTION

The M48Z08/18 ZEROPOWER

®

RAM is an 8K x

V

CC

8 non-volatile static RAM which is pin and functional compatible with the DS1225. The monolithic

chip is available in two special packages to provide

a highly integrated battery backed-up memory so-

A0-A12

13

8

DQ0-DQ7

lution.

T ab le 1. Signal Names

A0-A12 Address Inputs

DQ0-DQ7 Data Inputs / Outputs

E Chip Enable

G Output Enable

W Write Enable

V

CC

V

SS

March 1999 1/18

Supply Voltage

Ground

W

E

G

M48Z08

M48Z18

V

SS

AI01022

M48Z08, M48Z18

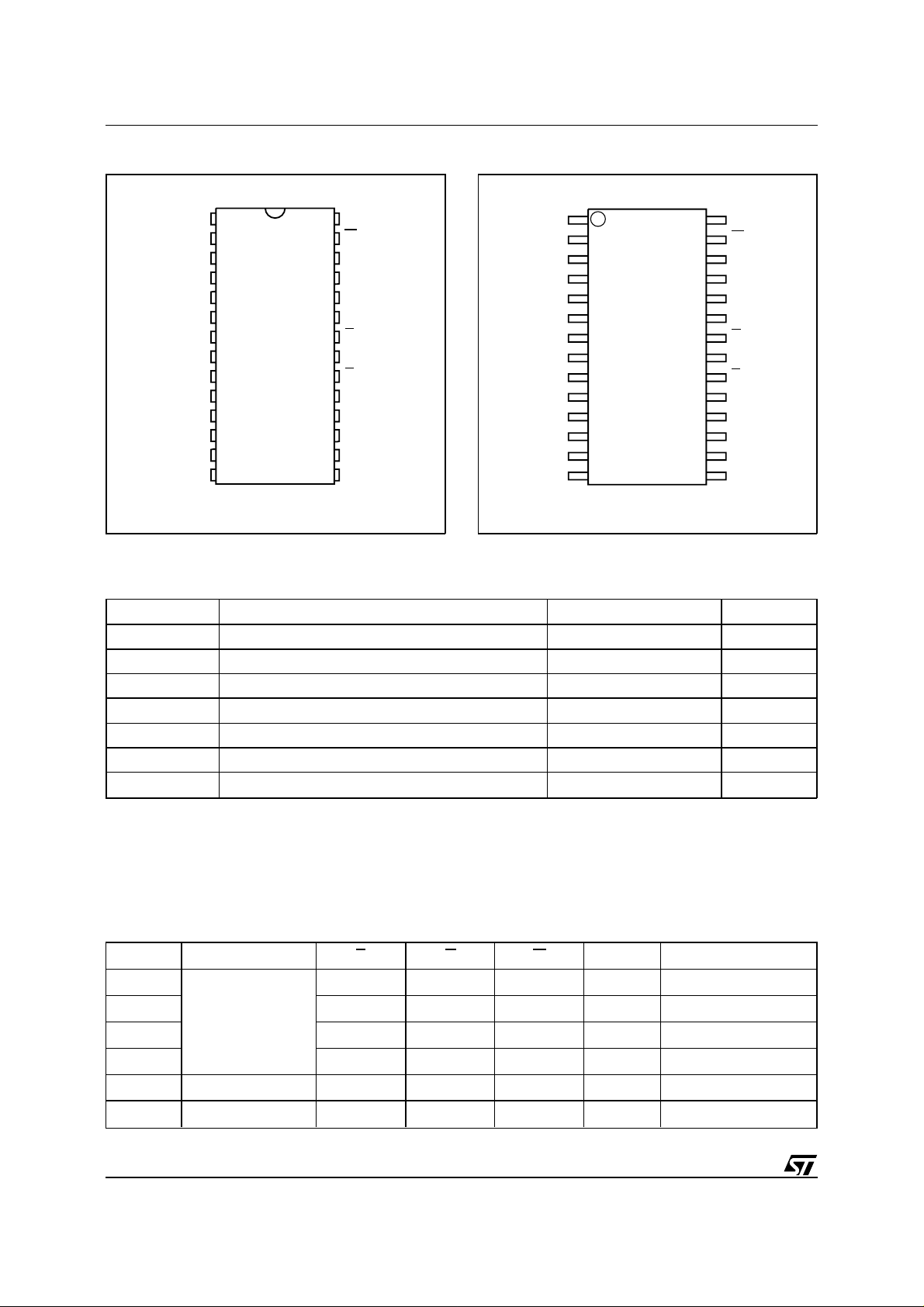

Figure 2A. DIP Pin Connections

28

27

26

25

24

23

22

21

20

19

18

17

16

15

AI01183

CC

W

NC

A8

A9

A11

G

A10

E

DQ7

DQ6

DQ5DQ1

DQ4

DQ3V

Warning:

NC V

1

A12

2

3

A7

4

A6

5

A5

6

A4

7

A3

A2

A1

A0

DQ0

8

9

10

11

M48Z08

M48Z18

12

13

DQ2

14

SS

NC = Not Connected.

T ab le 2. Absolute Maximum Ratings

(1)

Figure 2B. SOIC Pin Connections

Warning:

A7

A6

A5

A4

A3

A2

A1

A0

1

2

3

4

5

6

7

8

9

10

11

M48Z18

NC V

A12

DQ0

12

DQ2

SS

13

14

NC = Not Connected.

28

27

26

25

24

23

22

21

20

19

18

17

16

15

AI01023B

CC

W

NC

A8

A9

A11

G

A10

E

DQ7

DQ6

DQ5DQ1

DQ4

DQ3V

Symbol Parameter Value Unit

T

A

T

STG

(2)

T

SLD

V

IO

V

CC

I

O

P

D

Notes:

1. Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a

stress rating only and functional operation of the device at these or any other conditions above those indi cat ed in the operati onal

section of this specification is not implied. Exposure to the absolute maximum rating conditions for extended periods of time may

affect reliability.

2. Soldering temperature not to exceed 260°C for 10 seconds (total thermal budget not to exceed 150°C for longer than 30 seconds).

CAUTION: Negat i ve undershoots below –0.3 volts are not allowed on any pin while in the Battery Back-up mode.

CAUTION: Do NOT wave solder SOIC to avoid damaging SNAPHAT sockets.

Table 3. Operating Modes

Mode V

Deselect

Write V

Read V

Read V

Deselect V

Deselect ≤ V

Note:

1. X = V

Ambient Operating Temperature –40 to 85 °C

Storage T emper ature (VCC Off) –40 to 85 °C

Lead Solder Temperature for 10 seconds 260 °C

Input or Output Voltages –0.3 to 7 V

Supply Voltage –0.3 to 7 V

Output Current 20 mA

Power Dissipation 1 W

(1)

CC

4.75V to 5.5V

or

4.5V to 5.5V

to V

SO

or VIL; VSO = Battery Back-up Switchover Voltage.

IH

(min) X X X High Z CMOS Standby

PFD

SO

E G W DQ0-DQ7 Power

V

IH

IL

IL

IL

X X High Z Standby

XVILD

V

IL

V

IH

V

IH

V

IH

IN

D

OUT

High Z Active

X X X High Z Battery Back-up Mode

Active

Active

2/18

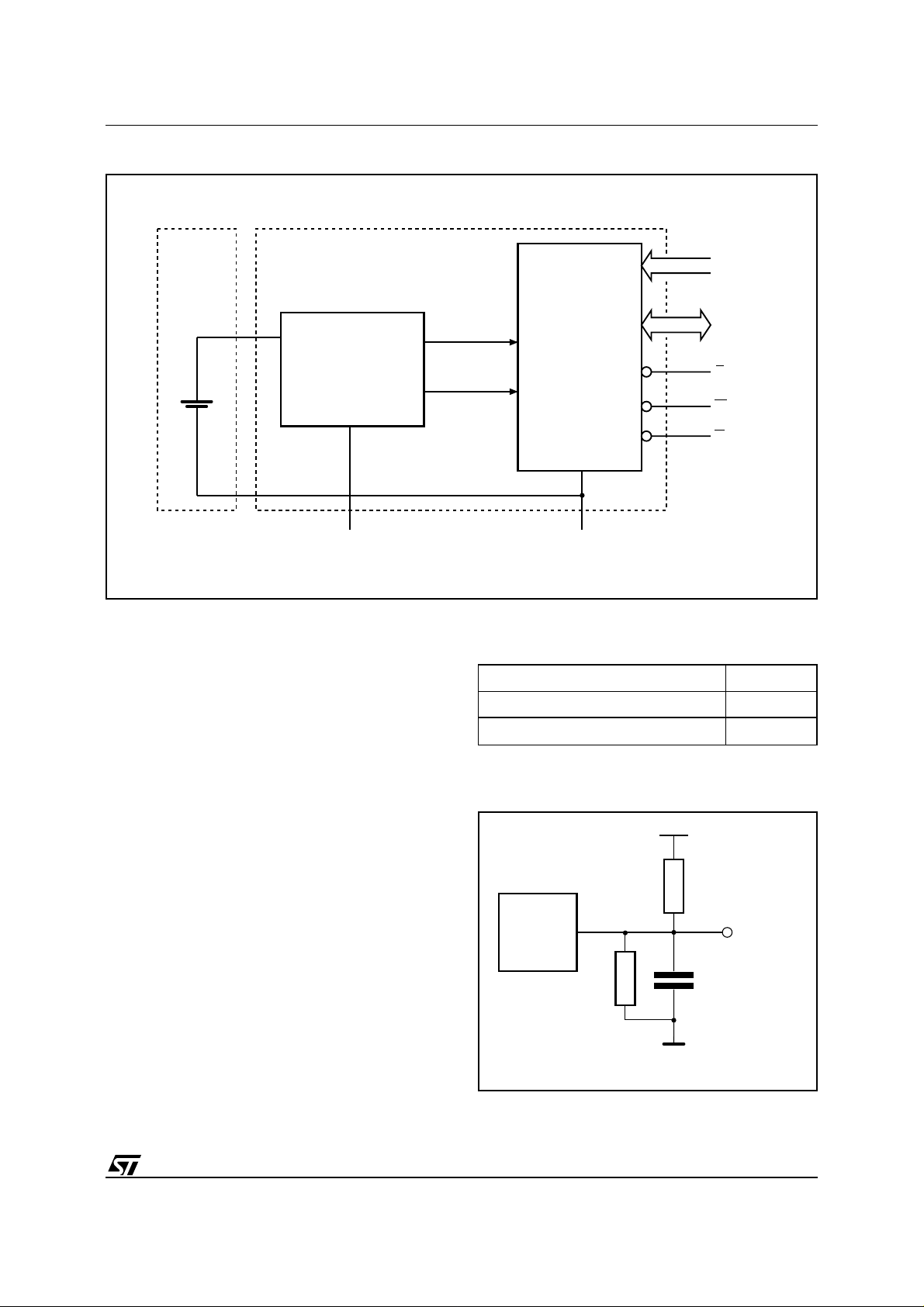

Figure 3. Block Diagram

M48Z08, M48Z18

A0-A12

LITHIUM

CELL

VOLTAGE SENSE

AND

SWITCHING

CIRCUITRY

V

CC

DESCRIPTION

(cont’d)

The M48Z08/18 is a non-volatile pin and function

equivalent to any JEDEC standard 8K x 8 SRAM.

It also easily fits into many ROM, EPROM, and

EEPROM sockets, providing the non-volatility of

PROMs without any requirement for special write

timing or limitations on the number of writes t hat

can be performed.

The 28 pin 600mil DIP CAPHAT houses the

M48Z08/18 silicon with a long life lithium button cell

in a single package.

The 28 pin 330mil SOIC provides s ockets with gold

plated contacts at both ends for direct connection

to a separate SNAPHAT housing containing the

battery. The unique design allows the SNAPHAT

battery package to be mounted on top of the SOIC

package after the completion of the surface mount

process. Insertion of the SNAPHAT housing after

reflow prevents potential battery damage due to the

high temperatures required for device surfacemounting. The SNAPHAT housing is keyed to prevent reverse insertion.

The SOIC and battery packages are shipped separately in plastic anti-static tubes or in Tape & Reel

form.

POWER

V

PFD

8K x 8

SRAM ARRAY

V

SS

Table 4. AC Measurement Conditions

Input Rise and Fall Times ≤ 5ns

Input Pulse Voltages 0 to 3V

Input and Output Timing Ref. Voltages 1.5V

Note that Output Hi-Z is defined as the point where data is no

longer driven.

Figure 4. AC Testing Load Circuit

5V

1.8kΩ

DEVICE

UNDER

TEST

1kΩ

CL includes JIG capacitance

CL = 100pF or 30pF

DQ0-DQ7

E

W

G

AI01394

OUT

AI01398

3/18

M48Z08, M48Z18

(1, 2)

T ab le 5. Capacitance

= 25 °C)

(T

A

Symbol Parameter T est Condition Min Max Unit

C

IN

(3)

C

IO

Notes:

1. Effective capacitance measured with power supply at 5V .

2. Sampled only, not 100% tested.

3. Outputs deselected

T ab le 6. DC Characteristics

= 0 to 70°C; VCC = 4.75V to 5.5V or 4.5V to 5.5V)

(T

A

Input Capacitance VIN = 0V 10 pF

Input / Output Capacitance V

= 0V 10 pF

OUT

Symbol Parameter Test Condition Min Max Unit

(1)

I

LI

(1)

I

LO

Supply Current Outputs open 80 mA

I

CC

I

CC1

I

CC2

(2)

V

IL

V

IH

V

OL

V

OH

Notes:

1. Outputs deselects.

2. Negative spikes of –1V allowed for up to 10ns once per cycle.

Input Leakage Current 0V ≤ VIN ≤ V

Output Leakage Current 0V ≤ V

Supply Current (Standby) TTL E = V

Supply Current (Standby) CMOS E = VCC – 0.2V 3 mA

OUT

≤ V

IH

CC

CC

Input Low Voltage –0.3 0.8 V

Input High Voltage 2.2 VCC + 0.3 V

Output Low Voltage IOL = 2.1mA 0.4 V

Output High Voltage IOH = –1mA 2.4 V

±1 µA

±5 µA

3mA

T able 7. Power Down/Up Trip Points DC Characteristics

= 0 to 70°C)

(T

A

(1)

Symbol Parameter Min Typ Max Unit

V

PFD

V

PFD

V

SO

t

DR

Note:

1. All voltages referenced to V

DESCRIPTION

Power-fail Deselect Voltage (M48Z08) 4.5 4.6 4.75 V

Power-fail Deselect Voltage (M48Z18) 4.2 4.3 4.5 V

Battery Back-up Switchover Voltage 3.0 V

Expected Data Retention Time 11 YEARS

.

SS

(cont’d)

When V

is out of tolerance, the circuit write

CC

protects the SRAM, providing a high degree of data

For the 28 lead SOIC, the battery package (i.e.

SNAPHAT) part number is "M4Z28-BR00SH1".

The M48Z08/18 also has its own Power-fail Detect

circuit. The control circuitry constantly monitors the

single 5V supply for an out of tolerance condition.

4/18

security in the midst of unpredictable system op-

eration brought on by low V

. As VCC falls below

CC

approximately 3V , the control circuitry connects the

battery which maintains data until valid power re-

turns.

M48Z08, M48Z18

T able 8. Power Down/Up Mode AC Characteristics

= 0 to 70°C)

(T

A

Symbol Parameter Min Max Unit

Notes

t

PD

(1)

t

F

t

FB

t

R

t

RB

t

REC

:1.V

2. V

(2)

V

E or W at VIH before Power Down 0 µs

V

(max) to V

PFD

V

(min) to VSO VCC Fall Time 10 µs

PFD

V

(min) to V

PFD

VSO to V

PFD

(min) VCC Fall Time 300 µs

PFD

(max) VCC Rise Time 0 µs

PFD

(min) VCC Rise Time 1 µs

E or W at VIH after Power Up 1 ms

(max) to V

PFD

passes V

CC

(min) to VSO fall time of less than tFB may cause corruption of RAM data.

PFD

(min) fall time of less than tF may result in deselection/writ e protection not occ urri ng until 200 µs after

PFD

(min).

PFD

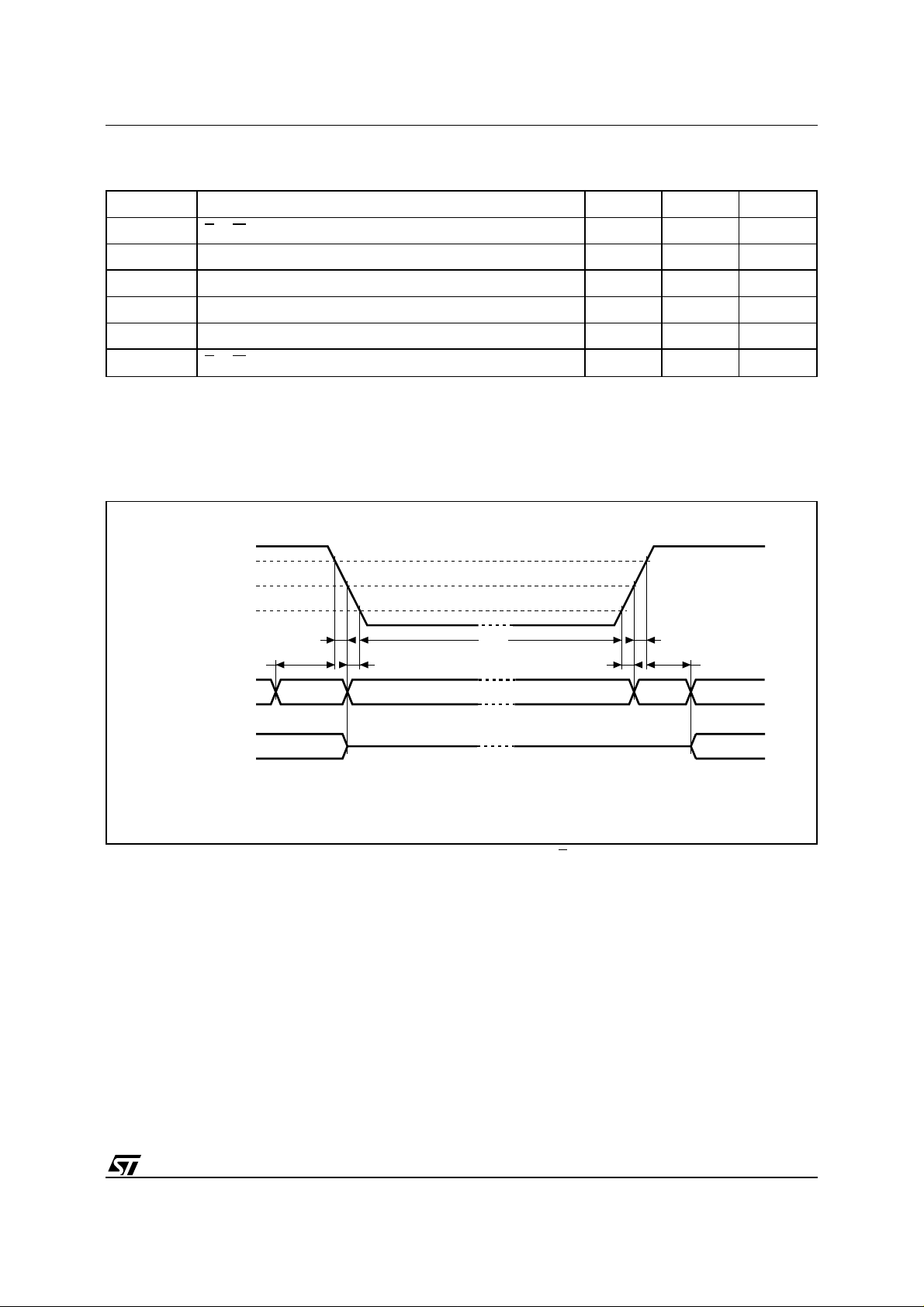

Figure 5. Power Down/Up Mode AC Waveforms

V

CC

V

(max)

PFD

V

(min)

PFD

VSO

tF

tDR

tFB

INPUTS

OUTPUTS

Note:

Inputs may or may not be recognized at this time. Caution should be taken to keep

may perform inadvertent writ e cyc l es after V

reset is being applied to the processor, a reset condition may not occur until after the system clock is running.

VALID VALID

(PER CONTROL INPUT)

rises above V

CC

(min) but before normal system operations begin. Even though a power on

PFD

DON'T CARE

HIGH-Z

E high as VCC rises past V

tR

NOTE

(PER CONTROL INPUT)

PFD

tRECtPD tRB

RECOGNIZEDRECOGNIZED

AI00606

(min ). Some system s

5/18

M48Z08, M48Z18

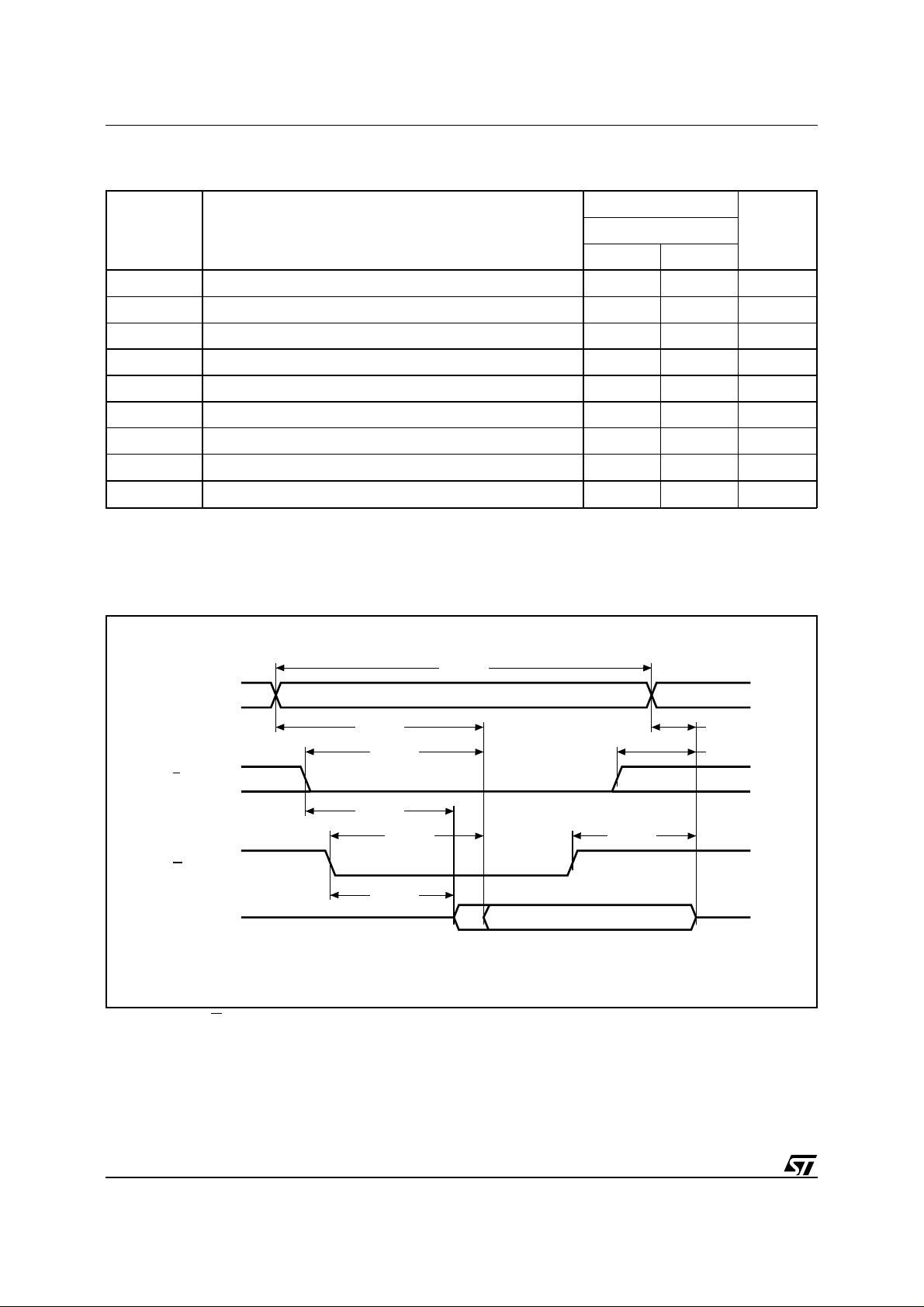

T ab le 9. Read Mode AC Characteristics

= 0 to 70°C; VCC = 4.75V to 5.5V or 4.5V to 5.5V)

(T

A

Symbol Parameter

Notes:

t

t

AVQV

t

ELQV

t

GLQV

t

ELQX

t

GLQX

t

EHQZ

t

GHQZ

t

AXQX

AVAV

1. C

2. C

(1)

(1)

(1)

(2)

(2)

(2)

(2)

(1)

Read Cycle Time 100 ns

Address Valid to Output Valid 100 ns

Chip Enable Low to Output Valid 100 ns

Output Enable Low to Output Valid 50 ns

Chip Enable Low to Output Transition 10 ns

Output Enable Low to Output Transition 5 ns

Chip Enable High to Output Hi-Z 50 ns

Output Enable High to Output Hi-Z 40 ns

Address Transition to Output Transition 5 ns

= 100pF (see Figure 4).

L

= 30pF (see Figure 4).

L

Figure 6. Read Mode AC Waveforms

M48Z08 / M48Z18

-100

Min Max

Unit

Note:

Write Enable (

A0-A12

E

G

DQ0-DQ7

W) = High.

tAVAV

VALID

tAVQV tAXQX

tELQV

tELQX

tGLQX

tGLQV

tGHQZ

VALID

tEHQZ

AI01385

6/18

Loading...

Loading...