SGS Thomson Microelectronics M28W640ECT, M28W640ECB Datasheet

FEATURES SUMMARY

■ SUPPLY VOLTAGE

= 2.7V to 3.6V Core Power Supply

–V

DD

–V

–V

■ ACCESS TIME: 70, 85, 90,100ns

■ PROGRAMMING TIME:

= 1.65V to 3.6V for Input/Output

DDQ

= 12V for fast Program (optional)

PP

– 10µ s typical

– Double Word Programming Option

– Quadruple Word Programming Option

■ COMMON FLASH INTERFACE

■ MEMORY BLOCKS

– Parameter Blocks (Top or Bott o m location)

– Main Blocks

■ BLOCK LOCKING

– All blocks locked at Power Up

– Any combination of blocks can be locked

for Block Lock-Down

–WP

■ SECURITY

– 128 bit user Programmable OTP cells

– 64 bit unique device identifier

■ AUTOMATIC STAND-BY MODE

■ PROGRAM and ERASE SUSPEND

■ 100,000 PROGRAM/ERASE CYCLES per

BLOCK

■ ELECTRONIC SIGNATURE

– Manufacturer Code: 20h

– Top Device Code, M28W640ECT: 8848h

– Bottom Device Code, M28W640ECB: 8849h

M28W640ECT

M28W640ECB

64 Mbit (4Mb x16, Boot Block)

3V Supp l y Fl ash Mem ory

PRELIMINARY DATA

Figure 1. Packages

FBGA

TFBGA48 (ZB)

6.39 x 10.5mm

TSOP48 (N)

12 x 20mm

April 2003

This is preliminary information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

1/55

M28W640ECT, M28W640ECB

TABLE OF CONTENTS

SUMMARY DESCRIPTION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Figure 2. Logic Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Table 1. Signal Names . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

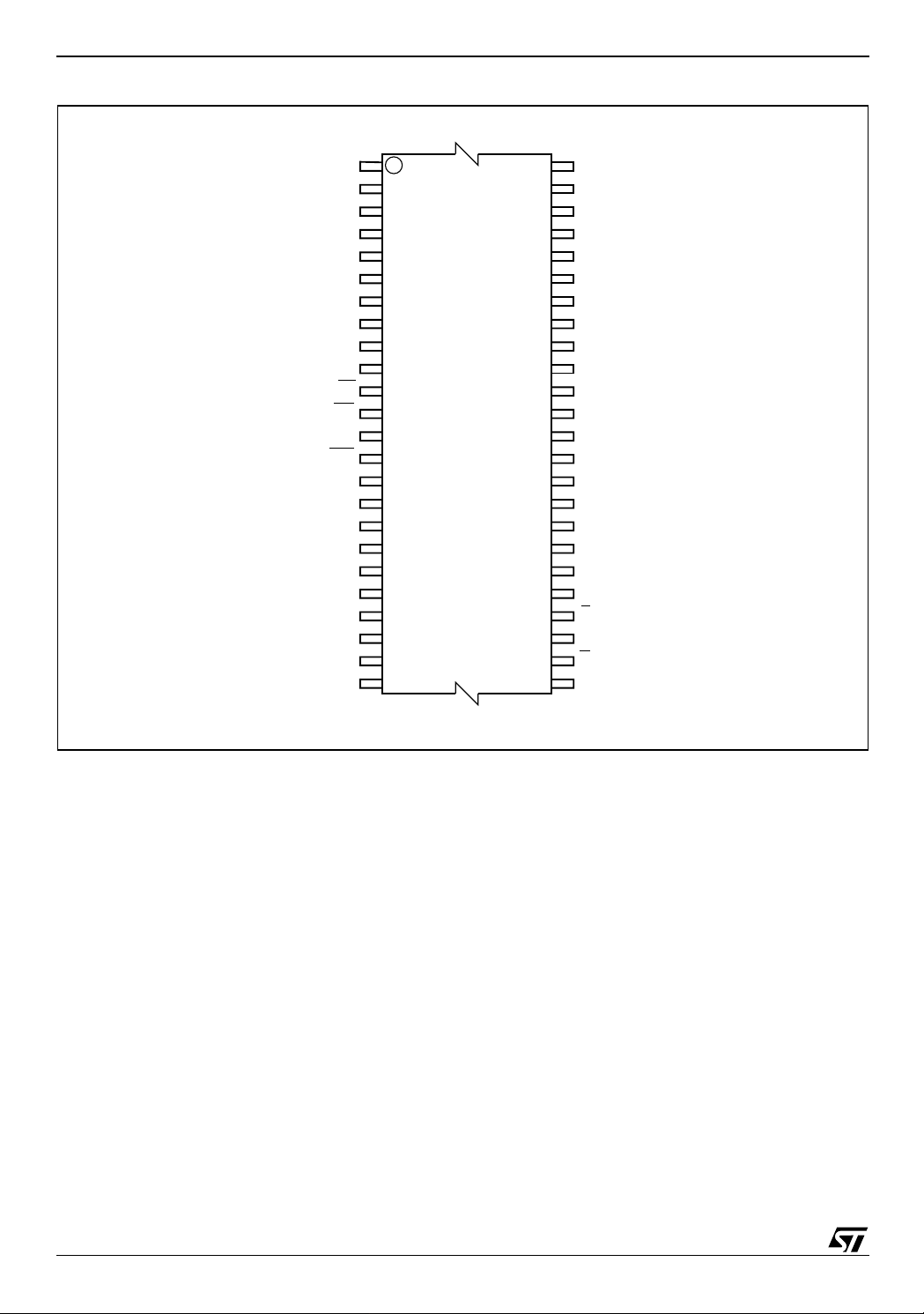

Figure 3. TSOP Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

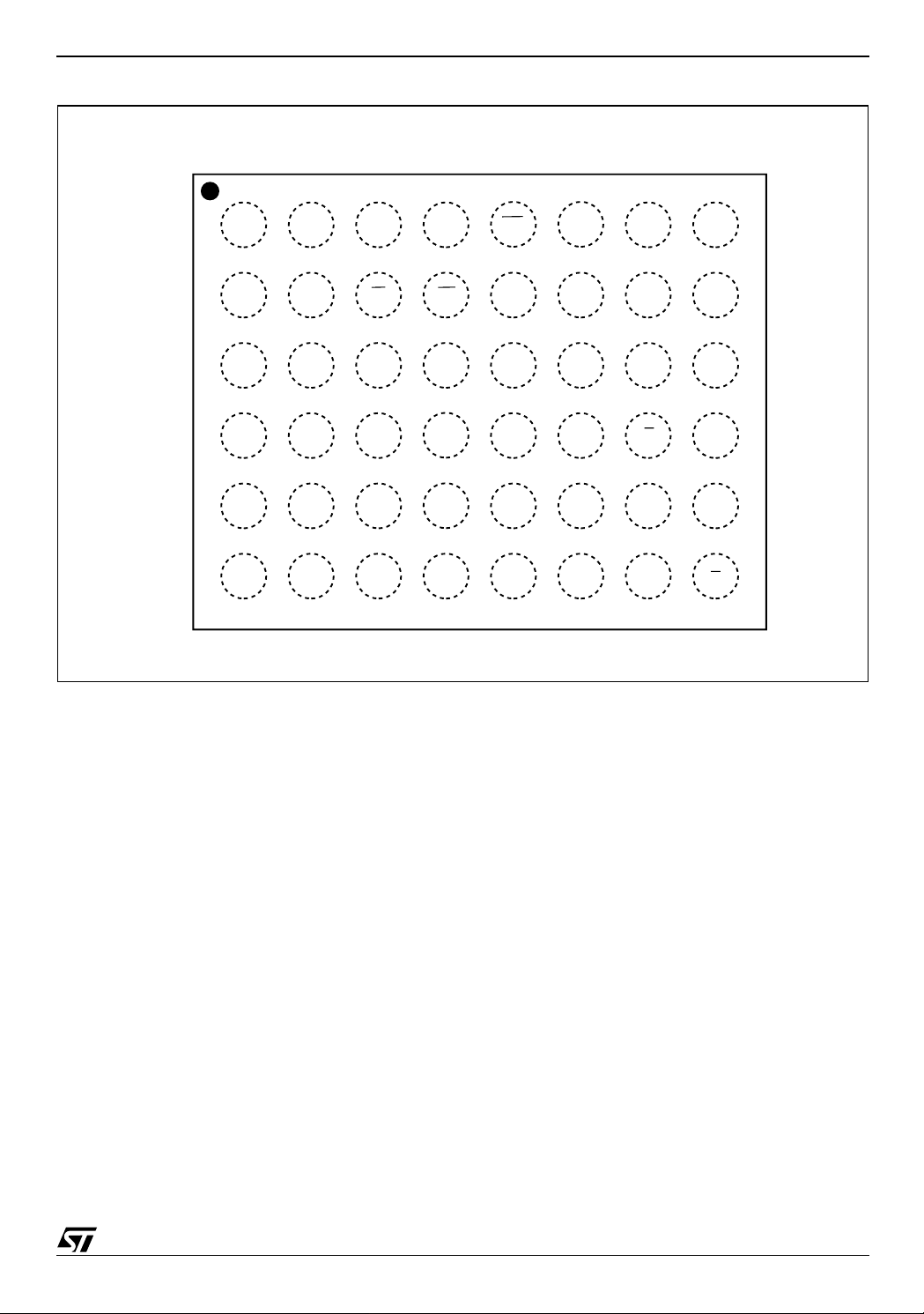

Figure 4. TFBGA Connections (Top view through package). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

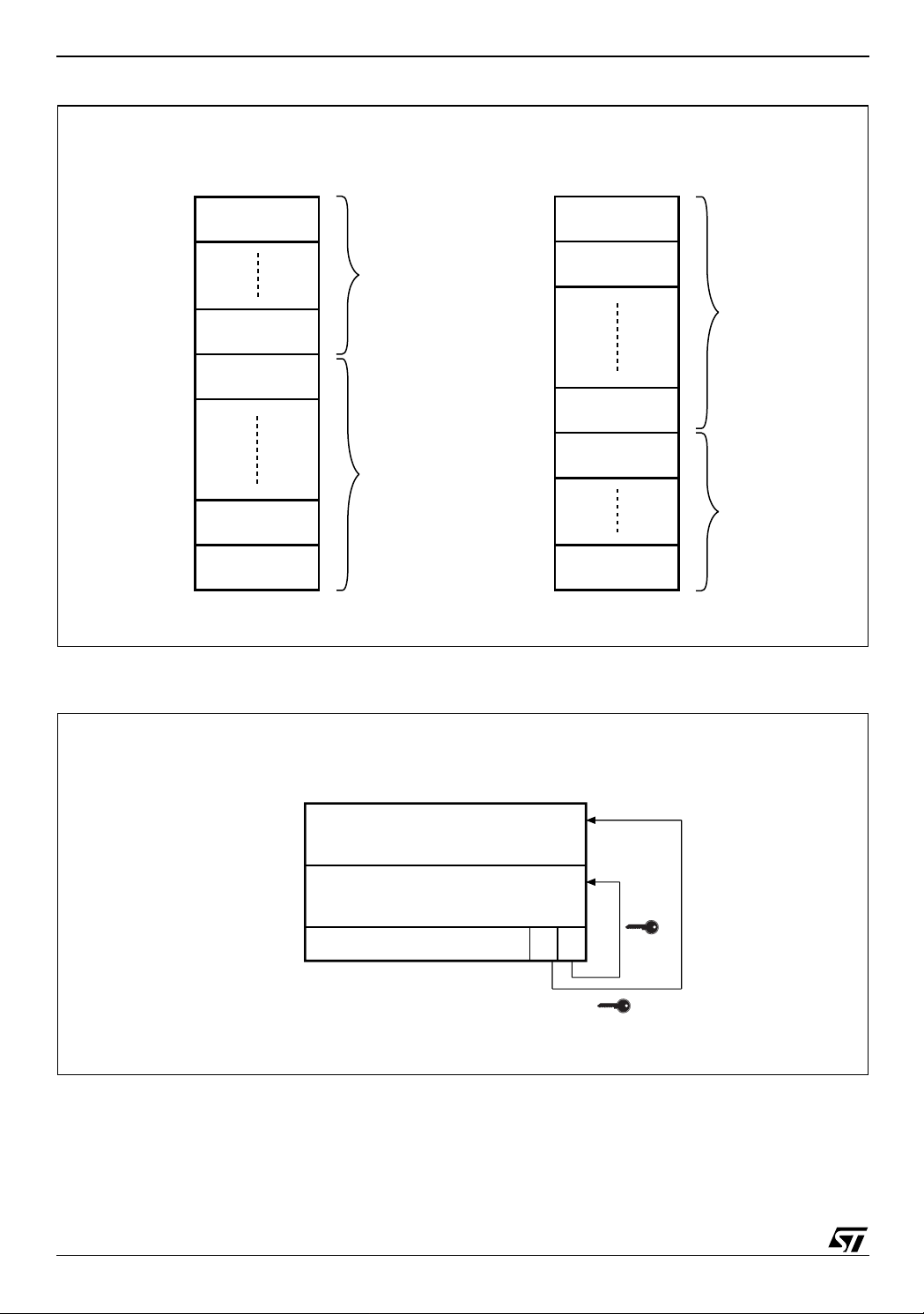

Figure 5. Block Addresses. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

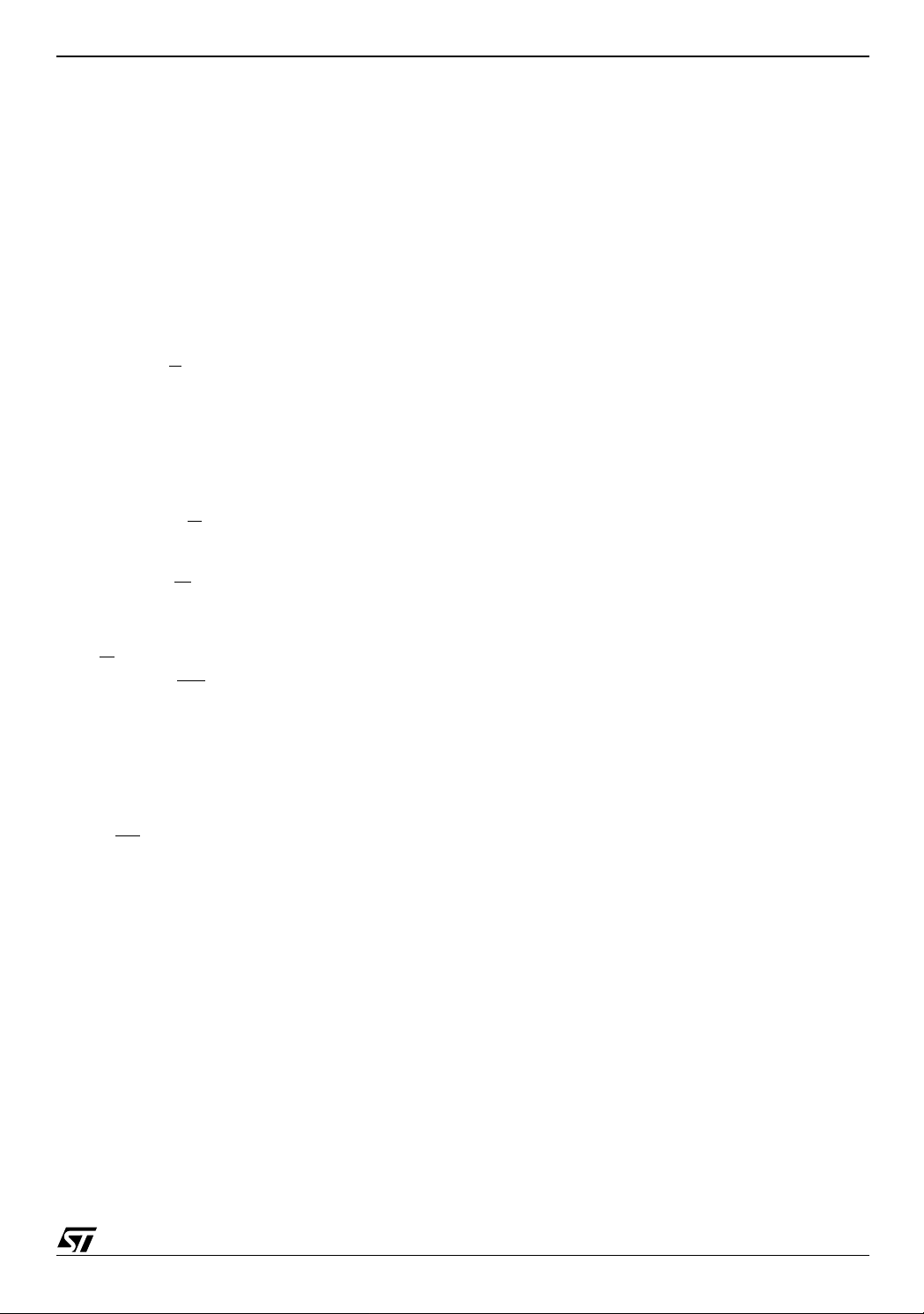

Figure 6. Protection Register Memory Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

SIGNAL DESCRIPTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Address Inputs (A0-A21). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Data Input/Output (DQ0-DQ15). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Chip Enable (E). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Output Enable (G). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Write Enable (W). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Write Protect (WP). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Reset (RP). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

V

Supply Voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

DD

V

Supply Voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

DDQ

V

Program Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

PP

V

Ground. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

SS

BUS OPERATIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Read.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 0

Write.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Output Disable. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 0

Standby. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Automatic Standby. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Read Electronic Signature Comma nd . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Table 2. Bus Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

COMMAND INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Read Memory Array Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

Read Status Register Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

Read Electronic Signature Comma nd . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Table 3. Command Codes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Read CFI Query Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Block Erase Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Program Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Double Word Program Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Clear Status Register Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Program/Erase Suspend Comm and . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Program/Erase Resume Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Protection Register Program Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

2/55

M28W640ECT, M28W640ECB

Block Lock-Down Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Table 4. Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Table 5. Read Electronic Signature. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Table 6. Read Block Lock Signature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

Table 7. Read Protection Register and Lock Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Table 8. Program, Erase Times and Program/Er ase Endu rance Cycles . . . . . . . . . . . . . . . . . . . . 16

BLOCK LOCKING. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Locked State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Unlocked State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Lock-Down State. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Reading a Block’s Lock Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Locking Operations During Erase Suspend . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Table 9. Block Lock Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Table 10. Protection Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

STATUS REGISTER. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Program/Erase Controller Status (Bit 7) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

Erase Suspend Status (Bit 6) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Erase Status (Bit 5). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Program Status (Bit 4). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

V

Status (Bit 3). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

PP

Program Suspend Status (Bit 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Block Protection Status (Bit 1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Reserved (Bit 0). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Table 11. Status Register Bits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

MAXIMUM RATING. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Table 12. Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

DC and AC PARAMETERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 2

Table 13. Operating and AC Measurement Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Figure 7. AC Measurement I/O Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

Figure 8. AC Measurement Load Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Table 14. Capacitance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Table 15. DC Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Figure 9. Read AC Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Table 16. Read AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Figure 10. Write AC Waveforms, Write Enable Controlled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Table 17. Write AC Characteristics, Write Enable Controlled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Figure 11. Write AC Waveforms, Chip Enable Controlled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Table 18. Write AC Characteristics, Chip Enable Controlled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Figure 12. Power-Up and Reset AC Waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Table 19. Power-Up and Reset AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

3/55

M28W640ECT, M28W640ECB

PACKAGE MECHANICAL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Figure 13. TSOP48 - 48 lead Plastic Thin Small Outline, 12 x 20mm, Package Outline . . . . . . . . 30

Table 20. TSOP48 - 48 lead Plastic Thin Small Outline, 12 x 20mm, Package Mechanical Data . 30

Figure 14. TFBGA48 6.39x10.5m m - 8x6 ball array, 0.75mm pitch, Bottom View Package Out line31

Table 21. TFBGA48 6.39x10.5mm - 8x6 ball array, 0.75mm pitch, Package Mechanical Data . . . 31

Figure 15. TFBGA48 Daisy Chain - Package Connections (Top view through package) . . . . . . . . 32

Figure 16. TFBGA48 Daisy Chain - PCB Connections proposal (Top view through package). . . . 32

PART NUMBERING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Table 22. Ordering Information Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

Table 23. Daisy Chain Ordering Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

APPENDIX A. BLOCK ADDRESS TABLES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Table 24. Top Boot Block Addresses, M28W640ECT. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Table 25. Bottom Boot Block Addresses, M28W640ECB. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

APPENDIX B. COMMON FLASH INTERFACE (CFI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Table 26. Query Structure Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

Table 27. CFI Query Identification String . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

Table 28. CFI Query System Interface Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Table 29. Device Geometry Definition. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

Table 30. Primary Algorithm-Specific Extended Query Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Table 31. Security Code Area . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

APPENDIX C. FLOWCHARTS AND PSEUDO CODES. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Figure 17. Program Flowchart and Pseudo Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Figure 18. Double Word Program Flowchart and Pseudo Code . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Figure 19. Quadruple Word Program Flowchart and Pseudo Code . . . . . . . . . . . . . . . . . . . . . . . . 46

Figure 20. Program Suspend & Resume Flowchart and Pseudo Code . . . . . . . . . . . . . . . . . . . . . 47

Figure 21. Erase Flowchart and Pseudo Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Figure 22. Erase Suspend & Resume Flowchart and Pseudo Code. . . . . . . . . . . . . . . . . . . . . . . . 49

Figure 23. Locking Operations Flowchart and Pseudo Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

APPENDIX D. COMMAND INTERFACE AND PROGRAM/ERASE CONTROLLER STATE . . . . . . . 52

Table 32. Write State Machine Current/Next, sheet 1 of 2.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Table 33. Write State Machine Current/Next, sheet 2 of 2.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

REVISION HISTORY. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Table 34. Document Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .54

4/55

SUMMARY DESCRIPTION

The M28W640EC is a 64 Mbit (4 Mbit x 16) nonvolatile Flash memory that can b e erased electrically at block level and programmed in-s ystem on

a Word-by-Word basis using a 2.7V to 3.6V V

supply for the circuitry and a 1.65V to 3.6V V

DD

DDQ

supply for the Input/Output pins. An optional 12V

V

power supply is provided to speed up custom-

PP

er programming.

The device features an asymmetrical blocked ar-

chitecture. The M28W640EC ha s an array of 135

blocks: 8 Parameter Blocks of 4 KWord and 127

Main Blocks of 32 KWord. M28W640ECT has the

Parameter Blocks at the top of the memory address space while the M28W640ECB locates the

Parameter Blocks starting from the bottom. The

memory maps are shown in Figure 5, Block Addresses.

The M28W640EC features an instant, individual

block locking scheme that allo ws any block to be

locked or unlocked with no latency, enabling instant code and data protection. All blocks have

three levels of protection. They can be locked and

locked-down individually preventing any accidental programming or erasure. There is an additional

hardware protection against program and erase.

When V

PP

≤ V

all blocks are protected against

PPLK

program or erase. All blocks are locked at Power

Up.

Each block can be erased separately. Erase can

be suspended in order to perform either read or

program in any other block and then resumed.

Program can be s uspended to read data in any

other block and then resumed. Each block can be

programmed and erased over 100,000 cycles.

The device includes a 192 b it Protection Register

to increase th e pr o tection of a system design. The

Protection Register is divided into a 64 bit segment

and a 128 bit segment. The 64 bi t segment contains a unique device number written by ST, while

the second one is one-time-programmable by the

user. The user programmable segment can be

permanently protected. Figure 6, shows the Protection Register Memory Map.

Program and Erase command s are written to the

Command Interface of the memory. An on-chip

Program/Erase Controller takes care of the timings necessary for program and erase operations.

The end of a program or erase operation can be

detected and any error conditions identified. The

command set required to control the memory is

consistent with JEDEC standards.

M28W640ECT, M28W640ECB

The memory is of fered in TSOP48 (12 X 20mm)

and TFBGA48 (6.39 x 10.5mm, 0.75mm pitch)

packages and is supplied with all the bits erased

(set to ’1’).

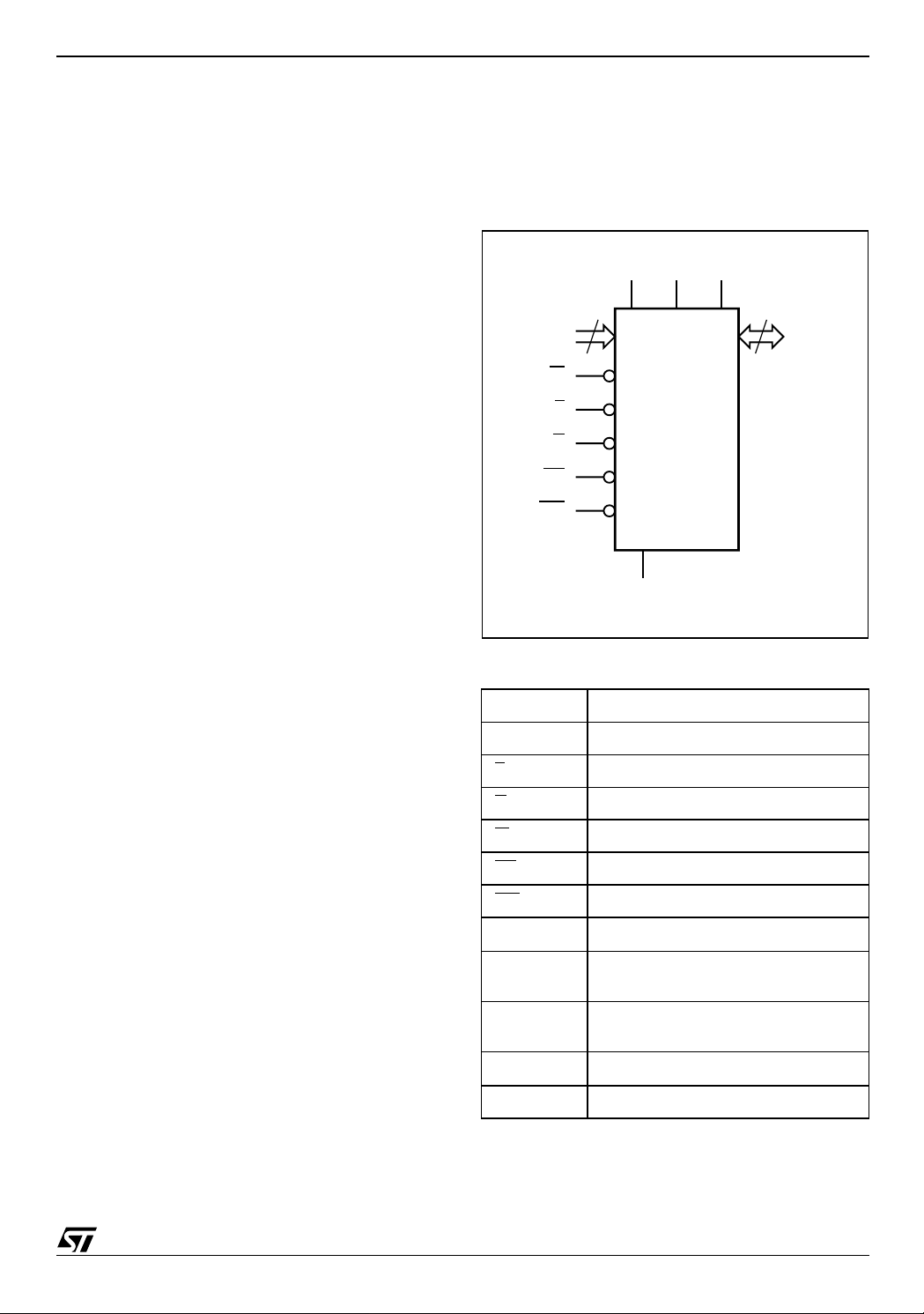

Figure 2. Logic Diagram

V

V

DD

DDQVPP

22

A0-A21

W

E

G

RP

WP

M28W640ECT

M28W640ECB

V

SS

Table 1. Signal Names

A0-A21 Address Inputs

DQ0-DQ15 Data Input/Output

E

G

W

RP

WP

V

DD

V

DDQ

V

PP

V

SS

NC Not Connected Internally

Chip Enable

Output Enable

Write Enable

Reset

Write Protect

Core Power Supply

Power Supply for

Input/Output

Optional Supply Voltage for

Fast Program & Erase

Ground

16

DQ0-DQ15

AI04378b

5/55

M28W640ECT, M28W640ECB

Figure 3. TSOP Connections

A15

A14

A13

A12

A11

1

48

A16

V

DDQ

V

SS

DQ15

DQ7

A10 DQ14

37

36

DQ6

DQ13

DQ5

DQ12

DQ4

V

DD

DQ11

DQ3

DQ10

DQ2

DQ9

DQ1

DQ8

DQ0

G

V

SS

E

A0

A21

A20

RP

V

PP

WP

A19

A18

A17

A9

A8

W

A7

A6

A5

A4

A3

A2

A1

12

M28W640ECT

M28W640ECB

13

24 25

AI04379b

6/55

Figure 4. TFBGA Connections (Top view through package)

M28W640ECT, M28W640ECB

87654321

A

B

C

D

E

F

DDQ

SS

DQ7V

A8A11A13

DQ13

PP

RP A18

A21

DQ11

DQ12

DQ4

WP A19

A20

DQ2

DD

A7V

A5A17WA10A14

DQ0DQ9DQ3DQ6DQ15V

DQ1DQ10V

A4

A2

A1A3A6A9A12A15

A0EDQ8DQ5DQ14A16

V

SS

G

AI04380

7/55

M28W640ECT, M28W640ECB

Figure 5. Block Addresses

M28W640ECT

Top Boot Block Addresses

3FFFFF

3FF000

3F8FFF

3F8000

3F7FFF

3F0000

00FFFF

008000

007FFF

000000

Note: A l so see Appe ndi x A, Tables 24 and 25 for a full l isting of the Bl ock Address es.

4 KWords

Total of 8

4 KWord Blocks

4 KWords

32 KWords

Total of 127

32 KWord Blocks

32 KWords

32 KWords

Bottom Boot Block Addresses

3FFFFF

3F8000

3F7FFF

3F0000

00FFFF

008000

007FFF

007000

000FFF

000000

M28W640ECB

32 KWords

32 KWords

Total of 127

32 KWord Blocks

32 KWords

4 KWords

Total of 8

4 KWord Blocks

4 KWords

AI04386b

Figure 6. Prot ect i on Register Me m o ry Map

PROTECTION REGISTER

8Ch

User Programmable OTP

85h

84h

81h

80h

Unique device number

Protection Register Lock 1 0

AI05520b

8/55

SIGNAL DESCRIPTIONS

See Figure 2 Logic Diagram and Table 1,Signal

Names, for a brief overview of the signals connected to this device.

Address Inputs (A0-A21). The Address Inputs select the cells i n the memory array to a ccess during Bus Read operations. During Bus Write operations they control the commands sent to the Command Interface of the internal state machine.

Data Input/Output (DQ0-DQ15). The Data I/O outputs the data stored at the selected address during a Bus Read operation or inputs a command or the data to be programmed durin g a Write Bus operation.

Chip Enable (E

). The Chip Enable input acti-

vates the memory control logic, input buffers, decoders and sense amplifiers. When Chip Enable is

and Reset is at VIH the device is in active

at V

IL

mode. When Chi p E nable i s at V

the memory is

IH

deselected, the outputs are high impedan ce and

the power consumption is reduced to the stand-by

level.

Output Enable (G

). The Output Enable controls

data outputs during the Bus Read operation of the

memory.

Write Enable (W

). The Write Enable controls the

Bus Write operation of the memory’s Command

Interface. The data and address inputs are latched

on the rising edge of Chip Enable, E, or Write Enable, W

Write Protect (WP

, whichever occurs first.

). Write Protect is an input

that gives an additional hardware protection for

each block. When Write Protect is at V

, the Loc k-

IL

Down is enabled and the prote ction status of t he

block cannot be changed. When Write Protect is at

, the Lock-Down is disabled and the block can

V

IH

be locked or unlocked. (refer to Table 7, Read Protection Register and Protection Register Lock).

Reset (RP

ware reset of the memory. W hen Reset is at V

). The Reset input provides a hard-

IL

the memory is in reset mode: the outputs are high

impedance and the current consumption is minimized. After Reset all blocks are in the Locked

M28W640ECT, M28W640ECB

state. When Reset is at V

operation. Exiting reset mode the device enters

read array mode, but a negative transition of Chip

Enable or a change of the addres s is required t o

ensure valid data outputs.

Supply Voltage. VDD provides the power

V

DD

supply to the internal core of the memory device.

It is the main power supply for all operations

(Read, Program and Erase).

Su pp ly V olt ag e . V

V

DDQ

power supply to the I/O pins a nd ena bles all Ou tputs to be powered independently from V

can be tied to VDD or can use a separate supply.

Program Supply Voltage. VPP is both a

V

PP

control input and a power supply pin. The two

functions are selected by the voltage range applied to the pin. The Supply Voltage V

Program Supply Voltage V

any order.

If V

is kept in a low voltage range (0V to 3.6V)

PP

V

is seen as a control input. In this case a volt-

PP

age lower than V

PPLK

against program or erase, whi le V

ables these functions (see Table 15, DC Characteristics for the relevant values). V

sampled at the beginning of a program or erase; a

change in its value after the operation has started

does not have any effect on Program or Erase,

however for Double or Q uadruple Word Program

the results are uncertain.

If V

is in the range 11.4V to 12.6V it acts as a

PP

power supply pin. In this condition V

stable until the Program/Erase algorit hm is completed (see Table 17 and 18).

Ground. VSS is the reference for all voltage

V

SS

measurements.

Note: Each device in a system should have

V

DD, VDDQ

pacitor close to the pin. See Figure 8, AC Mea-

,

and VPP decoupled wi th a 0.1 µF ca-

surement Load Circu it. The PCB trace widths

should be sufficient to carry the required V

program and erase currents.

, the device is in normal

IH

provides the

DDQ

can be applied in

PP

gives an absolute protection

PP

DD

and the

DD

> V

is only

PP

must be

PP

. V

PP1

DDQ

en-

PP

9/55

M28W640ECT, M28W640ECB

BUS OPERATIONS

There are six standard bus operations that control

the device. These are Bus Read, Bus Wri te, Output Disable, Standby, Automatic Standby and Reset. See Table 2, Bus Operations, for a summary.

Typically glitches of less than 5ns on Chip Enable

or Write Enable are ignored by the memory and do

not affect bus operations.

Read. Read Bus operations are used to output the contents of the Memory Array, the Electronic Signature, the Status Register and the Common Flash Interface. Both Chip Enable and Output Enable must be at V eration. The Chip Enable in put should be us ed to enable the device. Out put E nable shoul d be used to gate data onto the output. The data read depends on the previous command written to the memory (see Command Interface section). See Figure 9, Read Mode AC Wa veforms, and Table 16, Read AC Characteristics, for details of when the output becomes valid.

Read mode is the default state of the device when

exiting Reset or after power-up.

Write. Bus Write operations write Commands to the memory or latch Input Data to be programmed. A write operation is initiated when Chip Enable and Write Enable are at V V

. Commands, Input Data and Addresses are

IH

latched on the rising edge of Write Enable or Chip

Enable, whichever occurs first.

in order to perform a read op-

IL

with Output Enable at

IL

See Figures 10 and 11, Write AC Waveforms, and

Tables 17 and 18, Write AC Characteristics, for

details of the timing requirements.

Output Disa bl e . The data outputs are high impedance when the Output Enable is at V

.

IH

Standby. Stan dby disables most of the inte rnal circuitry allowing a substantial reduction of the current consumption. The memory is in stand-by when Chip Enable is at V

and the device is in

IH

read mode. The power consumption is reduced to

the stand-by level and the o utputs are set to high

impedance, independently from the Output Enable

or Write Enable inputs. If Chip Enable switches to

V

during a program or erase operation, t he de-

IH

vice enters Standby mode when finished. Automatic Standby. Automatic Standby pro-

vides a low power consumption state during Read

mode. Following a read operation, the device enters Automatic Standby after 150ns of bus inactivity even if Chip Enable is Low, V

current is reduced to I

. The data I nputs/Out-

DD1

, and the supply

IL

puts will still output data if a bus Read operation is

in progress.

Reset. During Reset mode when Output Enable is Low, V

, the memory is deselected and the out-

IL

puts are high impedance. The memory is in Reset

mode when Reset is at V

. The power consump-

IL

tion is reduced to the Standby level, independently

from the Chip Enable, Output Enable or Write Enable inputs. If Reset is pulled to V

during a Pro-

SS

gram or Erase, this operation is aborted and the

memory content is no longer valid.

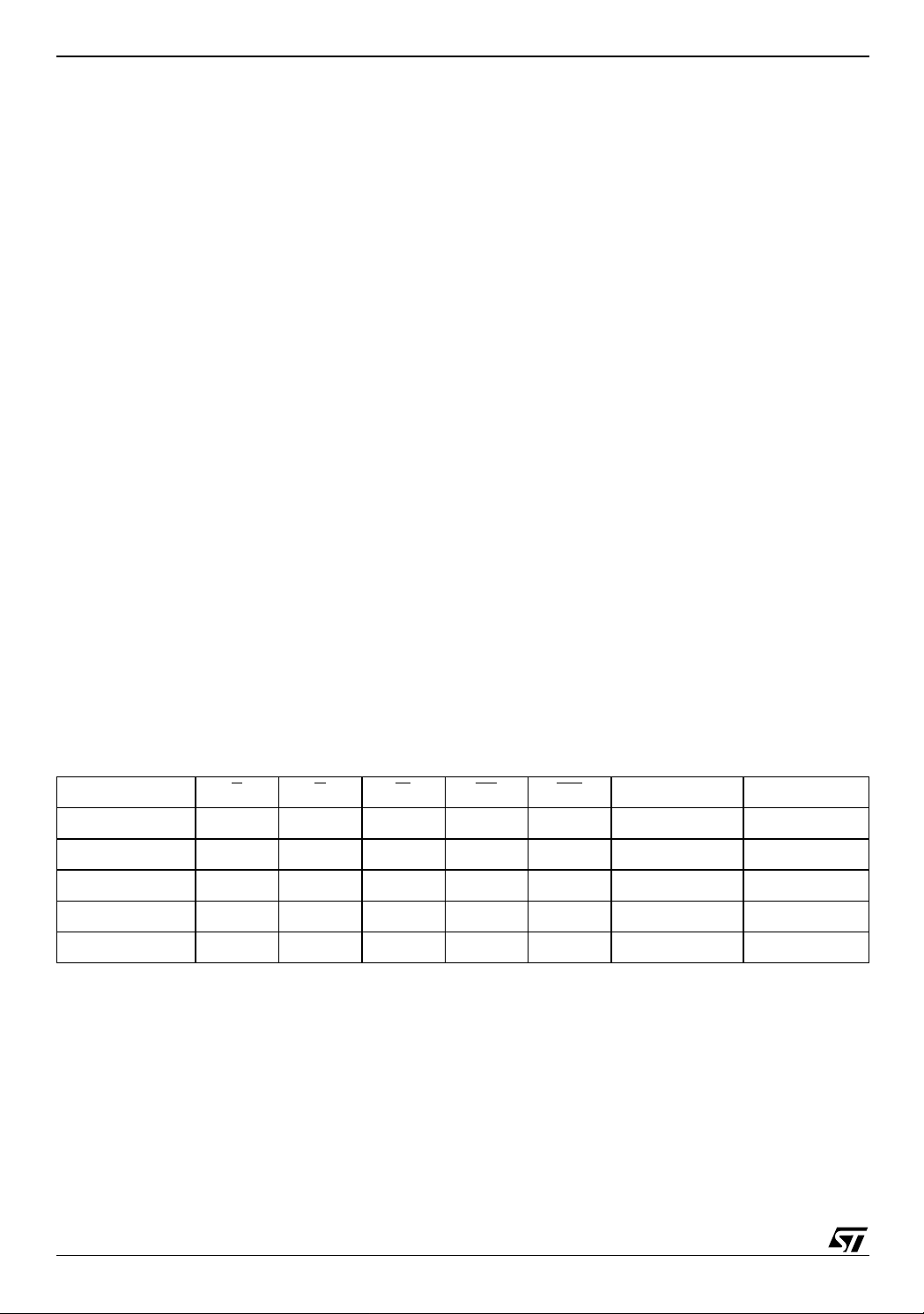

Table 2. Bus Operations

Operation E G W RP WP

Bus Read

Bus Write

Output Disable

Standby

Reset X X X

Note: X = VIL or VIH, V

10/55

V

V

V

V

= 12V ± 5%.

PPH

IL

IL

IL

IH

V

IL

V

IH

V

IH

XX

V

IH

V

IL

V

IH

V

IH

V

IH

V

IH

V

IH

V

IL

V

PP

X Don’t Care Data Output

V

X

X Don’t Care Hi-Z

X Don’t Care Hi-Z

X Don’t Care Hi-Z

DD

or V

PPH

DQ0-DQ15

Data Input

COMMAND INTERFACE

All Bus Write operations t o the me mory are in terpreted by the Command Interface. Commands

consist of one or more sequential Bus Write operations. An internal Program/Erase Controller handles all timings and verifies the correct execution

of the Program and Erase commands. The Program/Erase Controller provides a S tatus Register

whose output may be read at any time during, to

monitor the progress of the operation, or the P rogram/Erase states. See Table 3, Command

Codes, for a summary o f the c ommands and see

Appendix 22, Table 32, Write State Machine Current/Next, for a summa ry of the Command Interface.

The Command Interface is reset to Read mode

when power is first applied, when exiting from Reset or whenever V

is lower than V

DD

LKO

. Command sequences must be followed exactly. Any

invalid combination of commands will reset the device to Read mode. Refer to Table 4, Commands,

in conjunction with the text descriptions below.

Read Memory Array Command

The Read command returns the memory to its

Read mode. One Bus Write cycle is required to issue the Read Memory Array command and return

the memory to Read mode. Subsequ ent read operations will read the addressed locat ion and output the data. When a device Reset occurs, the

memory defaults to Read mode.

Read Status Register Command

The Status Register indicates when a program or

erase operation is complete and the success or

failure of the operation itself. Issue a Read Status

Register command to rea d the Status Register’s

contents. Subsequent Bus Read op erations read

the Status Register at any address, u ntil another

command is issued. See Table 11, Status Register

Bits, for details on the definitions of the bits.

The Read Status Register command m ay be issued at any time, even during a Program/Erase

operation. Any Read attempt during a Program/

Erase operation will automatically output the content of the Status Register.

Read Electronic Signature Command

The Read Electronic Signature command reads

the Manufacturer and Device Codes and the Block

Locking Status, or the Protection Register.

The Read Electronic Signature command consists

of one write cycle, a subsequent read will output

the Manufacturer Code, the Device Code, the

Block Lock and Lock-Down Status, or the Protection and Lock Register. See Tables 5, 6 and 7 for

the valid address.

M28W640ECT, M28W640ECB

Table 3. Command Codes

Hex Code Command

01h Block Lock confirm

10h Program

20h Erase

2Fh Block Lock-Down confirm

30h

40h Program

50h Clear Status Register

56h

60h

70h Read Status Register

90h Read Electronic Signature

98h Read CFI Query

B0h Program/Erase Suspend

C0h Protection Register Program

D0h

FFh Read Memory Array

Read CFI Query Command

The Read Query Command is used to read dat a

from the Common Flash Interface (CFI) Me mory

Area, allowing programming equi pment or applications to automatically match their interface to

the characteristics of the device. One Bus Write

cycle is required to issue the Read Query Command. Once the command is issued subsequent

Bus Read operations read from the Common

Flash Interface Memory Area. See Appendix B,

Common Flash Inte rface, Tables 26, 27, 28, 29,

30 and 31 for details on the information contained

in the Common Flash Interface memory area.

Block Erase Command

The Block Erase com mand can be used to erase

a block. It sets all the bits within the selected block

to ’1’. All previous d ata in th e block is lost. If th e

block is protected then the Erase operation will

abort, the data in the block will not be changed and

the Status Register will output the error.

Two Bus Write cycles are required to issue the

command.

■ The first bus cycle sets up the Erase command.

Double Word Program

Quadruple Word Program

Block Lock, Block Unlock, Block Lock-

Down

Program/Erase Resume, Block Unlock

confirm

11/55

M28W640ECT, M28W640ECB

■ The second latches the block address in the

internal state machine and starts the Program/

Erase Controller.

If the second bus cycle is not Write Erase Confirm

(D0h), Status Register bits b4 and b5 a re s et and

the command aborts.

Erase aborts if Reset turns to V

. As data integrity

IL

cannot be guaranteed when the Erase operation is

aborted, the block must be erased again.

During Erase operations the memory will accept

the Read Status Re gister com mand and the P rogram/Erase Suspend command, all other commands will be ignored. Typical Erase times are

given in Table 8, Program, Erase Times and P rogram/Erase Endurance Cycles.

See Appendix C, Figure 21 , Erase Flowchart and

Pseudo Code, for a suggested flowchart for using

the Erase command.

Program Command

The memory array can be programmed word-byword. Two bus write cycles are required to issue

the Program Command.

■ The first bus cycle sets up the Program

command.

■ The second latches the Address and the Data to

be written and starts the Program/Erase

Controller.

During Program operations the memory will accept the Read Status Register command and the

Program/Erase Suspend command. Typical Program times are g iven in Tab le 8, P rogram, E rase

Times and Program/Erase Endurance Cycles.

Programming aborts if Reset goe s to V

. As data

IL

integrity cannot be guaranteed when the program

operation is aborted, the block containing the

memory location must be erased and reprogrammed.

See Appendix C, Figure 17, Program Flowchart

and Pseudo Code, for the f lowchart for using the

Program command.

Double Word Program Command

This feature is offered to improve the programming

throughput, writing a page of two adjacent words

in parallel.The two words m ust differ only for the

address A0. Programm ing should not be at t emp ted when V

is not at V

PP

PPH

.

Three bus write cycles are necessary to issue the

Double Word Program command.

■ The first bus cycle sets up the Double Word

Program Command.

■ The second bus cycle latches the Address and

the Data of the first word to be written.

■ The third bus cycle latches the Address and the

Data of the second word to be written and starts

the Program/Erase Controller.

Read operations output the Status Register content after the programming has s tarted. Programming aborts if Reset goes to V

. As data integrity

IL

cannot be guaranteed when the program operation is aborted, the block containing the memory

location must be erased and reprogrammed.

See Appendix C, Figure 18, Double Word Program Flowchart and Pseudo Code, for the flowchart for using the Double Word Program

command.

Quadruple Word Program Command

This feature is offered to improve the programming

throughput, writing a page of four adjacent words

in parallel.The four words must differ only for the

addresses A0 and A1. Programming should not be

attempted when V

is not at V

PP

PPH

.

Five bus write cycles are necessary to issue the

Quadruple Word Program command.

■ The first bus cycle sets up the Quadruple Word

Program Command.

■ The second bus cycle latches the Address and

the Data of the first word to be written.

■ The third bus cycle latches the Address and the

Data of the second word to be written.

■ The fourth bus cycle latches the Address and

the Data of the third word to be written.

■ The fifth bus cycl e latches the Addres s and th e

Data of the fourth word to be written and starts

the Program/Erase Controller.

Read operations output the Status Register content after the programming has s tarted. Programming aborts if Reset goes to V

. As data integrity

IL

cannot be guaranteed when the program operation is aborted, the block containing the memory

location must be erased and reprogrammed.

See Appendix C, Figure 19, Quadruple Word Program Flowchart and Pseudo Code, for the flowchart for using the Quadruple Word Program

command.

Clear Status Register Command

The Clear Status Register comm and c an b e us ed

to reset bits 1, 3, 4 and 5 in the Status Register to

‘0’. One bus write cycle is required to issue the

Clear Status Register command.

The bits in the Status Register do not automatically return to ‘0’ when a new Program or Erase command is issued. The error bits in the Status

Register should be cleared before attempting a

new Program or Erase command.

Program/Erase Suspend Command

The Program/Erase Suspend command is used to

pause a Program or Erase operation. One bus

write cycle is required to issue the Program/Erase

command and pau se the Prog ram/Erase controller.

12/55

M28W640ECT, M28W640ECB

During Program/Erase Suspend the Command Interface will accept the Program/Erase Resume,

Read Array, Read Status Register, Read Electronic Signature and Read CFI Query commands. Additionally, if the suspend operation was Erase then

the Program, Double Word Program, Quadruple

Word Program, Block Lock, Block Lock -Down or

Protection Program commands will also be accepted. The block being erased may be protected

by issuing the Block Protect, Block Lock or Protection Program commands. When the Program/

Erase Resume com mand is issued the operation

will complete. Only the blocks not being erased

may be read or programmed correctly.

During a Program/Erase Suspend, the device can

be placed in a pseudo-standby mode by taking

Chip Ena ble to V

Reset turns to V

. Program/Erase is aborted if

IH

.

IL

See Appendix C, Figure 20 , Program Suspend &

Resume Flowchart and Pseudo Code, and Figure

22, Erase Suspend & Resume Flowchart and

Pseudo Code for flowcharts for using the Program/

Erase Suspend command.

Program/Erase Resume Command

The Program/Erase Resume command can be

used to restart the Program/Erase Controller after

a Program/Erase Suspend o peration has paused

it. One Bus Write cycle is required to issue the

command. Once the command is issued subsequent Bus Read operations read the Status Register.

See Appendix C, Figure 20 , Program Suspend &

Resume Flowchart and Pseudo Code, and Figure

22, Erase Suspend & Resume Flowchart and

Pseudo Code for flowcharts for using the Program/

Erase Resume command.

Protectio n Register Program Command

The Protection Register Program command is

used to Program the 128 bit user O ne-Time-Programmable (OTP) segment of the Protection Register. The segment is programmed 16 bits at a

time. When shipped all bits in the segment are set

to ‘1’. The user can only program the bits to ‘0’.

Two write cycles are required to issue the Protec-

tion Register Program command.

■ The first bus cycle sets up the Protection

Register Program command.

■ The second latches the Address and the Data to

be written to the Protection Register and starts

the Program/Erase Controller.

Read operations output the Status Register content after the programming has started.

The segment can be protected by programming bit

1 of the Protection Lock Register (see F igure 6,

Protection Register Memory Map). Attempting to

program a previously prot ected Protection Regis-

ter will result in a Status Register error. The protection of the Protection Register is not reversible.

The Protection Register Program cannot be suspended.

Block Lock Command

The Block Lock command is used to lock a block

and prevent Program or Erase operations from

changing the data in it. All blocks are locked at

power-up or reset.

Two Bus Write cycles are required to issue the

Block Lock command.

■ The first bus cycle sets up the Block Lock

command.

■ The second Bus Write cycle latc hes the block

address.

The lock status can be monitored for each block

using the Read Electronic Signature command.

Table. 10 shows the protection status after issuing

a Block Lock command.

The Block Lock bits are vo latile, once set they remain set until a hardware reset or power-down/

power-up. They are cleared by a Blocks Unlock

command. Refer to the section, Block Locking, for

a detailed explanation.

Block Unlock Command

The Blocks Unlock command i s used to unlock a

block, allowing the block to be programmed or

erased. Two Bus Write cycles are requ ired to issue the Blocks Unlock command.

■ The first bus cycle sets up the Block Unlock

command.

■ The second Bus Write cycle latc hes the block

address.

The lock status can be monitored for each block

using the Read Electronic Signature command.

Table. 10 shows the protection status after issuing

a Block Unlock command. Refer to the section,

Block Locking, for a detailed explanation.

Block Lock-Down Command

A locked block cannot be Programmed or Erased,

or have its protection status changed when WP

low, V

. When WP is high, V

IL

the Lock-Down

IH,

is

function is disabled and the locked blocks can be

individually unlocked by the Block Unlock command.

Two Bus Write cycles are required to issue the

Block Lock-Down command.

■ The first bus cycle sets up the Block Lock

command.

■ The second Bus Write cycle latc hes the block

address.

The lock status can be monitored for each block

using the Read Electronic Signature command.

Locked-Down blocks revert to the locked (and not

13/55

M28W640ECT, M28W640ECB

locked-down) state when the device is reset on

power-down. Table. 10 sho ws the protection sta-

Refer to the section, Block Locking, for a detailed

explanation.

tus after issuing a Block Lock-Down command.

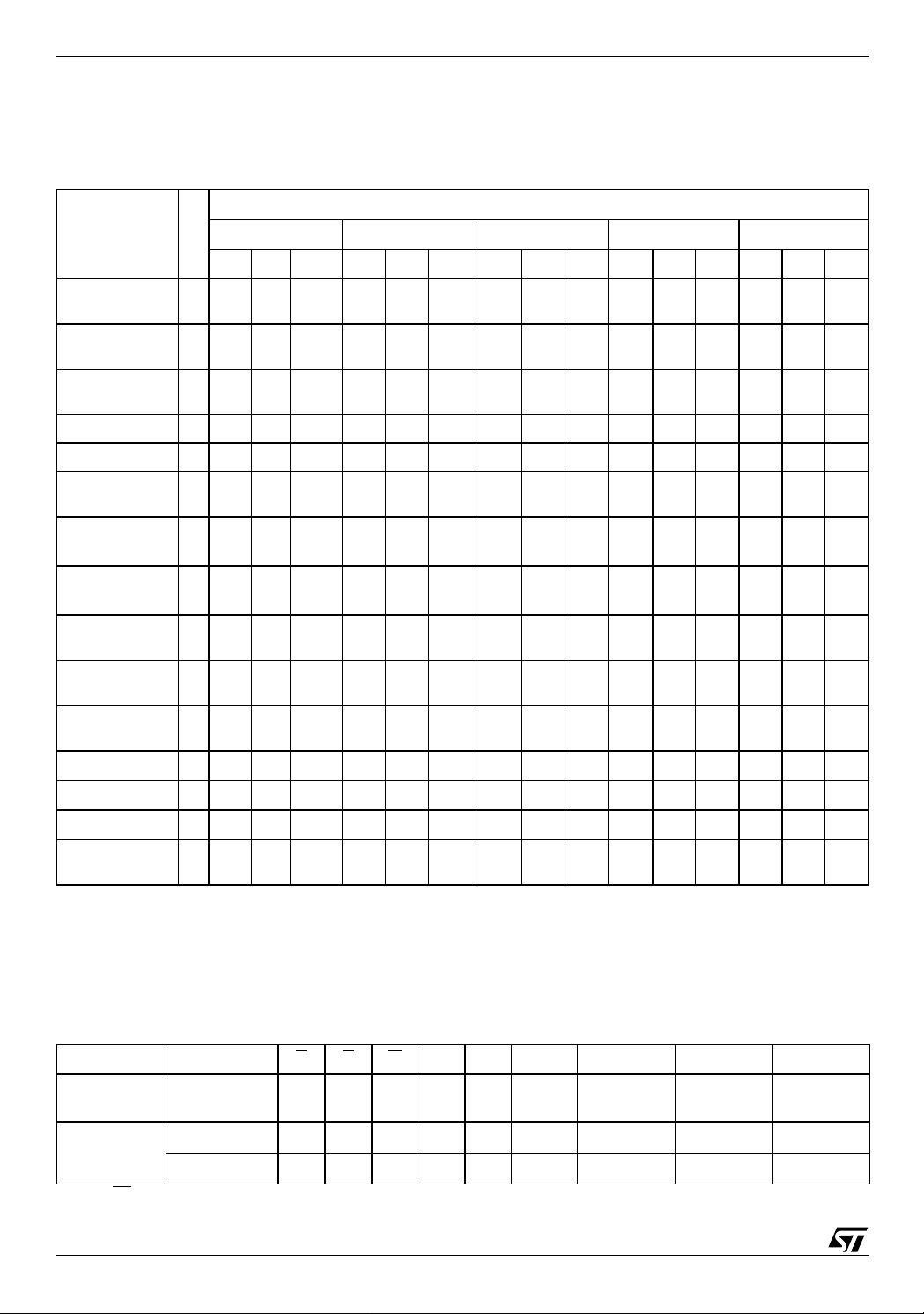

Table 4. Commands

Bus Write Operations

Commands

Read Memory

Array

Read Status

Register

Read Electronic

Signature

Read CFI Query 1+ Write X 98h Read QA QD

Erase 2 Write X 20h Write BA D0h

Program 2 Write X

Double Word

Program

Quadruple Word

Program

Clear Status

Register

Program/Erase

Suspend

Program/Erase

Resume

Block Loc k 2 Write X 60h Write

Block Unlock 2 Write X 60h Write

Block Loc k-Down 2 Write X 60h Write

Protection

Register Program

Note: 1. X = Don’t C are, RA=Rea d Addre ss, RD =Read D ata, SRD =Stat us Regis ter Da ta, ID =Identif ier (Ma nufact ure and Devic e Code),

(3)

(4)

QA=Query Address, QD=Query Data, BA=Block Address, PA=Program Address, PD=Program Data, PRA=Protection Register Address, PRD=Protection Register Data.

2. The s i gnature addresses are li st ed in Tables 5, 6 and 7.

3. Program Addres ses 1 and 2 must be consecuti ve Addresses differing only for A0.

4. Program Addres ses 1,2,3 and 4 m ust be consec utive Addr esses differi ng only for A 0 and A1.

5. To be c haracteriz ed.

1+ Write X FFh

1+ Write X 70h Read X SRD

1+ Write X 90h Read

1st Cycle 2nd Cycle 3rd Cycle 4th Cycle 5th Cycle

Cycles

Op. Add Data Op. Add Data Op. Add Data Op. Add Data Op. Add Data

RA RD

Read

(2)

IDh

SA

40h or

Write P A PD

10h

3 Write X 30h Write PA1 PD1 Write PA2 PD2

5 Write X

1 Write X 50h

1Write X B0h

1Write X D0h

(5)

Write PA1 PD1 Write PA2 PD2 Write PA3 PD3 Write PA4 PD4

56h

01h

BA

BA D0h

BA 2Fh

2 Write X C0h Write

PRA

PRD

Table 5. Read Electronic Signature

Code Device E G W A0 A1 A2-A7 A8-A21 DQ0-DQ7 DQ8-DQ15

Manufacture

Code

M28W640ECT

Device Code

M28W640ECB

Note: RP = VIH.

14/55

VILV

V

IL

V

VILV

IL

V

VILV

IL

V

IH

IHVIH

IHVIH

V

IL

V

V

0 Don’t Care 20h 00h

IL

0 Don’t Care 48h 88h

IL

0 Don’t Care 49h 88h

IL

M28W640ECT, M28W640ECB

Table 6. Read Block Lock Signature

Block Status E G W A0 A1 A2-A7 A8-A11 A12-A21 DQ0 DQ1 DQ2-DQ15

Locked Block

Unlocked Block

Locked-Down

Block

Note: 1. A Locked-Down Blo ck can be lock ed "DQ0 = 1" or unlocked "DQ0 = 0" ; s ee B l ock Locking section.

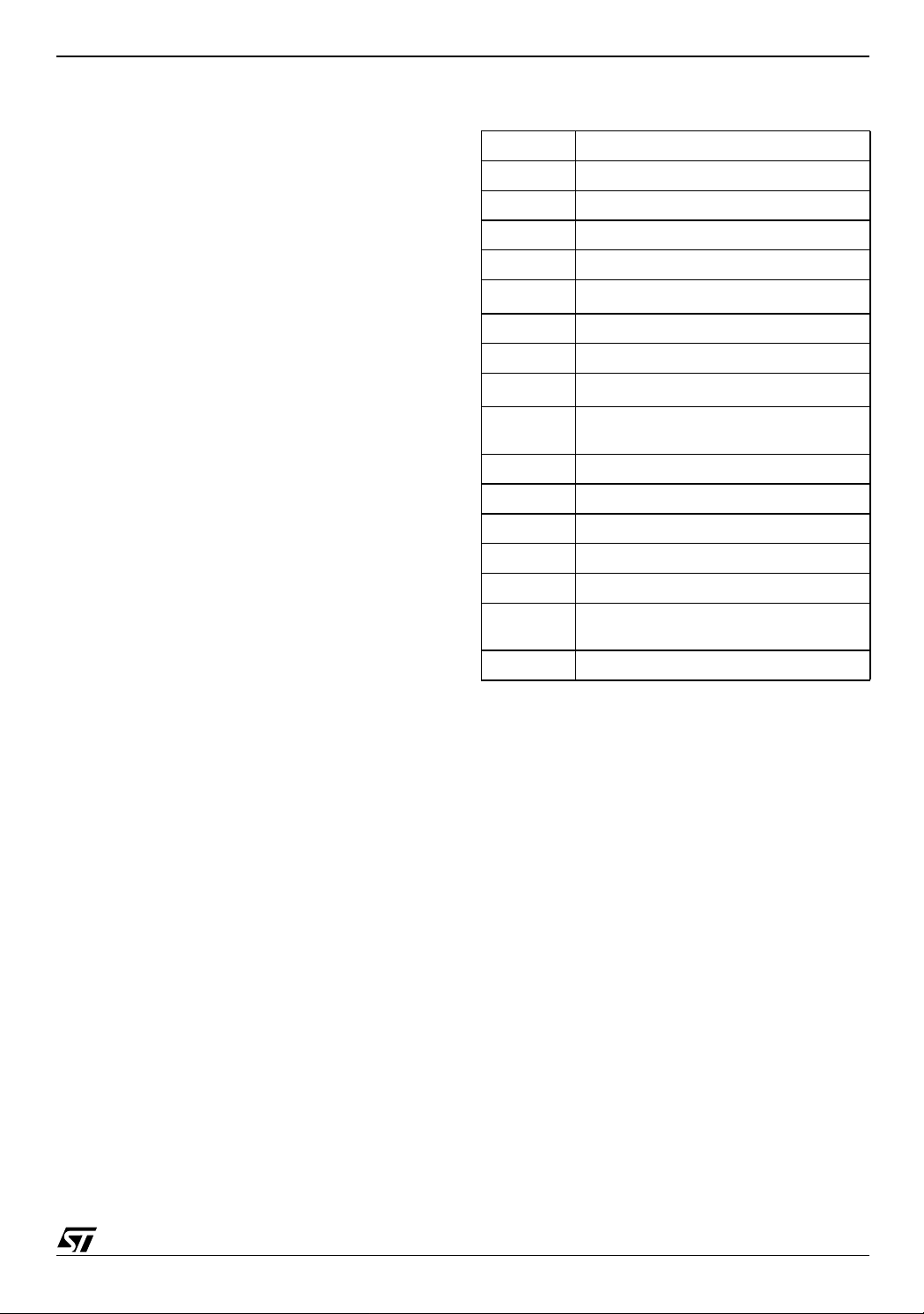

Table 7. Read Protection Register and Lock Register

Word E

Lock

Unique ID 0

Unique ID 1

Unique ID 2

Unique ID 3

OTP 0

OTP 1

OTP 2

OTP 3

OTP 4

OTP 5

OTP 6

OTP 7

V

ILVILVIHVILVIH

V

ILVILVIHVILVIH

V

ILVILVIHVILVIH

0 Don’t Care Block Address 1 0 00h

0 Don’t Care Block Address 0 0 00h

0 Don’t Care Block Address

X

(1)

1 00h

G W A0-A7 A8-A21 DQ0 DQ1 DQ2 DQ3-DQ7 DQ8-DQ15

V

ILVILVIH

V

ILVILVIH

V

ILVILVIH

V

ILVILVIH

V

ILVILVIH

V

ILVILVIH

V

ILVILVIH

V

ILVILVIH

V

ILVILVIH

V

ILVILVIH

V

ILVILVIH

V

ILVILVIH

V

ILVILVIH

80h Don’t Care 0

81h Don’t Care ID data ID data ID data ID data ID data

82h Don’t Care ID data ID data ID data ID data ID data

83h Don’t Care ID data ID data ID data ID data ID data

84h Don’t Care ID data ID data ID data ID data ID data

85h Don’t Care OTP data OTP data OTP data OTP data OTP data

86h Don’t Care OTP data OTP data OTP data OTP data OTP data

87h Don’t Care OTP data OTP data OTP data OTP data OTP data

88h Don’t Care OTP data OTP data OTP data OTP data OTP data

89h Don’t Care OTP data OTP data OTP data OTP data OTP data

8Ah Don’t Care OTP data OTP data OTP data OTP data OTP data

8Bh Don’t Care OTP data OTP data OTP data OTP data OTP data

8Ch Don’t Care OTP data OTP data OTP data OTP data OTP data

OTP Prot.

data

0 00h 00h

15/55

M28W640ECT, M28W640ECB

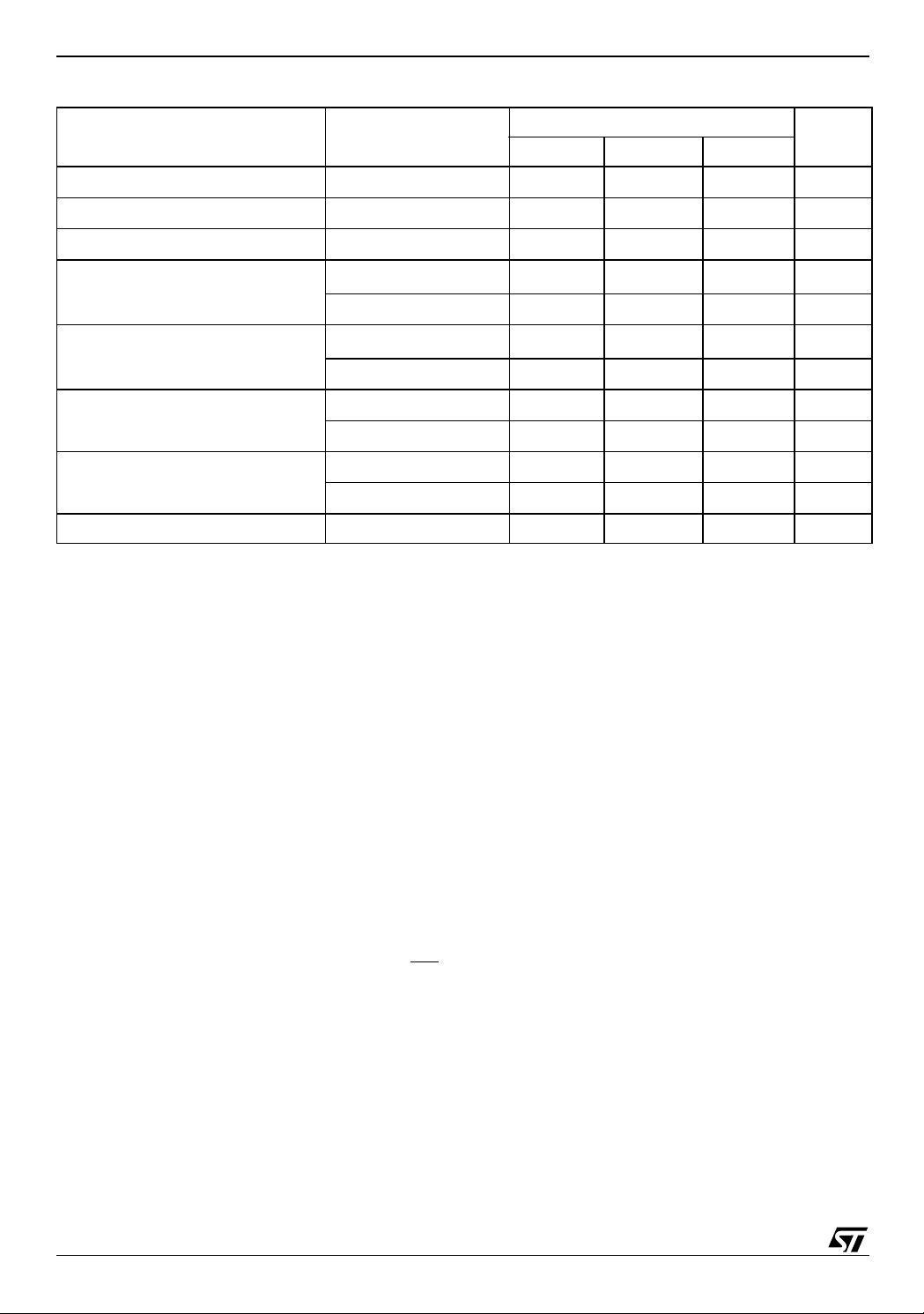

Table 8. Program , Erase Times and Program/Erase Endurance Cycl es

Parameter Test Conditions

V

Word Program

Double Word Program

Quadruple Word Program

Main Block Program

Parameter Block Program

Main Block Erase

Parameter Block Erase

Program/Erase Cycles (per Block) 100,000 cycles

Note: 1. Typical time to program a Main or Parameter Block using the Double Word Program and the Quadruple Word Program commands

respectively.

= V

PP

V

= 12V ±5%

PP

V

= 12V ±5%

PP

V

= 12V ±5%

PP

= V

V

PP

= 12V ±5%

V

PP

= V

V

PP

= 12V ±5%

V

PP

= V

V

PP

V

= 12V ±5%

PP

V

= V

PP

DD

DD

DD

DD

DD

Min Typ Max

M28W640EC

10 200 µs

10 200 µs

10 200 µs

0.16/0.08

0.02/0.01

(1)

0.32 5 s

(1)

0.04 4 s

110s

110s

0.4 10 s

0.4 10 s

5s

4s

Unit

BLOCK LOCKING

The M28W640EC features an instant, individual

block locking scheme that allo ws any block to be

locked or unlocked with no latency. This locking

scheme has three levels of protection.

■ Lock/Unlock - this first level allows software-

only control of block locking.

■ Lock-Down - this second level requires

hardware interaction before locking can be

changed.

■ V

PP

≤ V

- the third level offers a complete

PPLK

hardware protection against program and erase

on all blocks.

The protection status of each block can be set to

Locked, Unlocked, and Lock-Down. Table 10, defines all of the possible protection states (WP

DQ1, DQ0), and Appendi x C, Figure 23, shows a

flowchart for the locking operations.

Reading a Block’s Lock Status

The lock status of every block can be read in the

Read Electronic Signature mode of the device. To

enter this mode write 90h t o the device. Subsequent reads at the addres s specified in Table 6,

will output the pr otection sta tus of that bloc k. The

lock status is represented by DQ0 and DQ 1. DQ0

indicates the Block Lock/Unlock status and i s set

by the Lock comm and and cleared by the Unlock

command. It is also automatically set when entering Lock-Down. DQ1 indicates the Lock-Down status and is set by the Lock-Down command. It

cannot be cleared by software, only by a hardware

reset or power-down.

The following sections explain the operation of the

locking system.

Locked State

The default status of all blocks on power-up or after a hardware reset is L ocked (states (0,0,1) or

(1,0,1)). Locked blocks are fully protected from

any program or erase. Any program or erase operations attempted on a locked block will return an

error in the Status Register. The Status of a

Locked block can be changed to Unlocked or

Lock-Down using the appropriate software com-

,

mands. An Unlocked block can be Locked by issuing the Lock command.

Unlocked State

Unlocked blocks (states (0,0,0), (1,0,0) (1,1,0)),

can be programmed or erased. All unlocked

blocks return to the Locked state after a hardware

reset or when the device is powered-down. The

status of an unlocked block can be changed to

Locked or Locked-Down using the appropriate

software commands. A locked block can be unlocked by issuing the Unlock command.

16/55

M28W640ECT, M28W640ECB

Lock-Down State

Blocks that are Locked-Down (state (0,1,x))are

protected from program and erase operations (as

for Locked blocks) but th eir protect ion status cannot be changed using software comma nds alone.

A Locked or Unlocked block can be Locked-Down

by issuing the Lock-Down command. LockedDown blocks revert to the Locked state when the

device is reset or powered-down.

The Lock-Down function is depen dent on the WP

input pin. When WP=0 (VIL), the blocks in the

Lock-Down state (0,1,x) are protected from program, erase and protection status changes. When

=1 (VIH) the Lock-Down function is disabled

WP

(1,1,1) and Locked-Down blocks can be ind ividually unlocked to the (1,1,0) state by issuing the

software command, where they can be erased and

programmed. These blocks can then be relocked

(1,1,1) and unlocked (1,1,0) as desired while WP

remains high. When WP is low , blocks that were

previously Locked-Down return to the Lock-Down

state (0,1,x) regardless of any changes made

while WP

was high. Device reset or power-down

resets all blocks , including those in Lock-Down, to

the Locked state.

Locking Operations During Erase Suspend

Changes to block lock status can be performed

during an erase suspend by using the standard

locking command sequences to unlock, lock or

lock-down a block. This is useful in the case when

another block needs to be updated while an erase

operation is in progress.

To change block locking during an erase operation, first write the Erase Suspend command, then

check the status register until it indicates that the

erase operation has been suspended. Next write

the desired Lock com mand sequence to a block

and the lock status will be changed. After completing any desired lock, read, or program operations,

resume the erase operation with the Erase Resume command.

If a block is locked or locked-down during an erase

suspend of the same block, the locking status bits

will be changed immediately, b ut when the erase

is resumed, the erase operation will complete.

Locking operations cannot be performed du ring a

program suspend. Refer to Appendix D, Command Interface and Program/Erase Controller

State, for detailed information on which commands are valid during erase suspend.

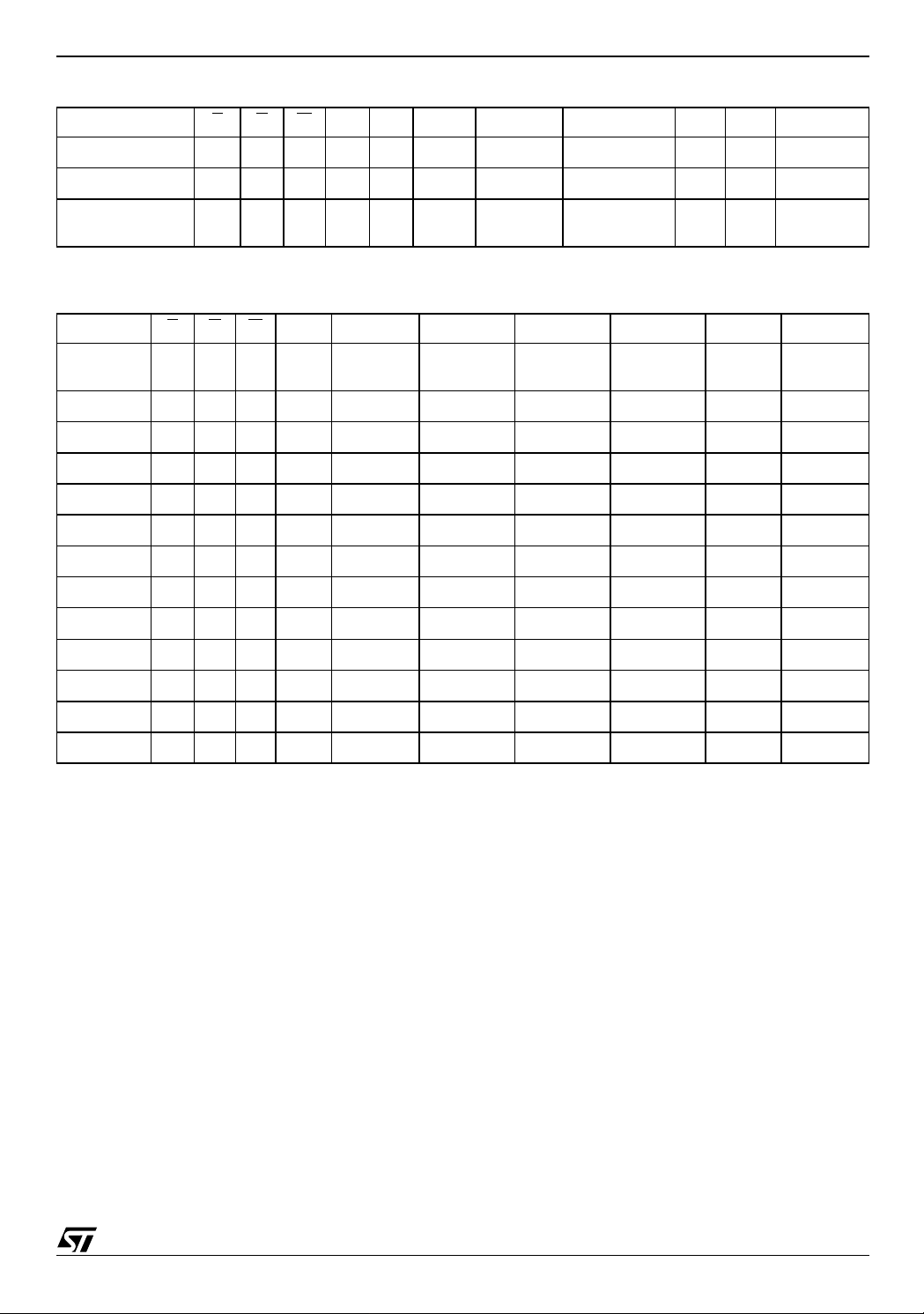

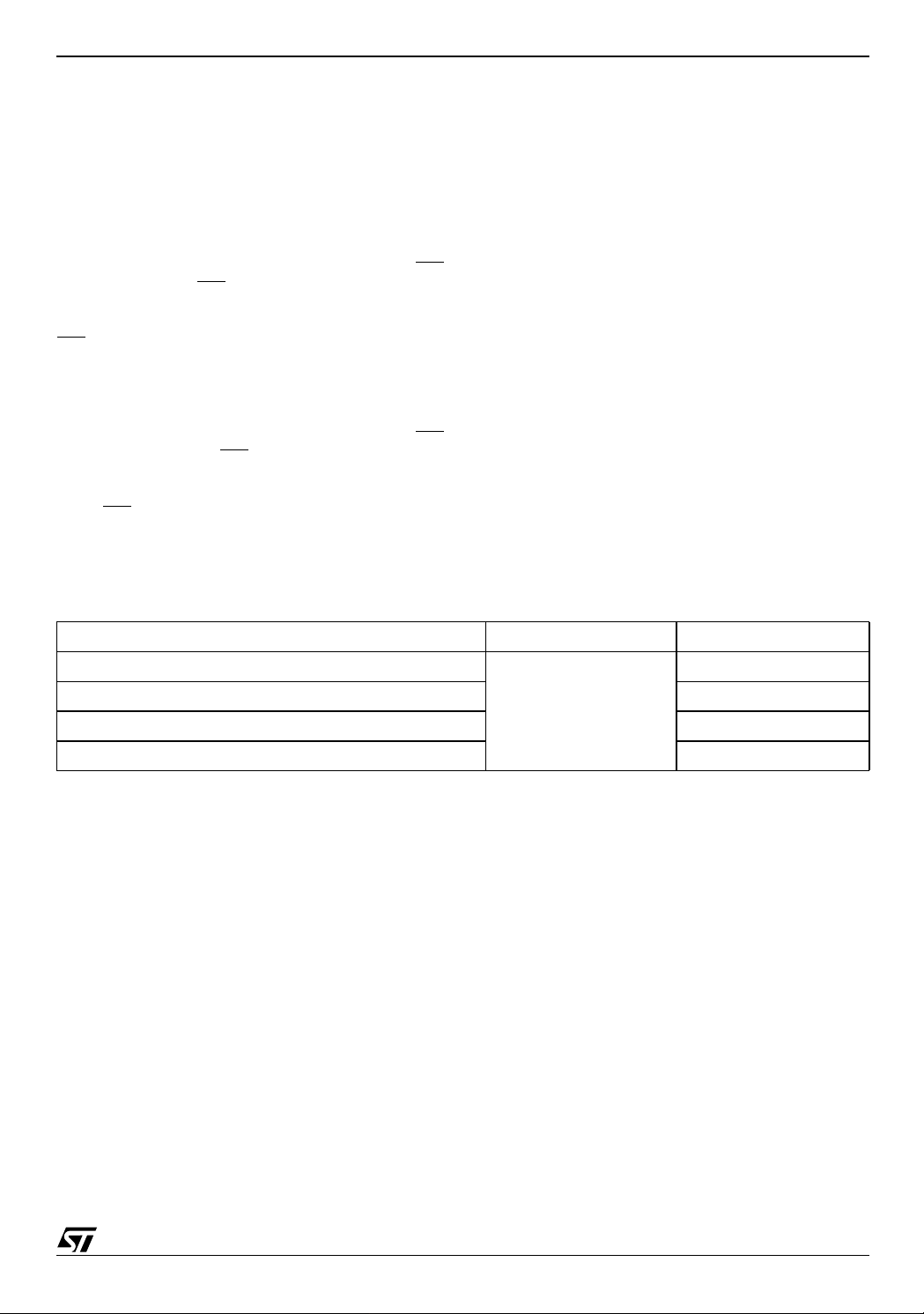

Table 9. Block Lock Status

Item Address Data

Block Lock Configuration

Block is Unlocked DQ0=0

Block is Locked DQ0=1

Block is Locked-Down DQ1=1

LOCK

xx002

17/55

Loading...

Loading...