CMOS LSI

Ordering number : EN5427A

22897HA (OT)/63196HA (OT) No. 5427-1/22

LC72133M, 72133V

SANYO Electric Co.,Ltd. Semiconductor Bussiness Headquarters

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110 JAPAN

PLL Frequency Synthesizer for

Electronic Tuning

Overview

The LC72133M and LC72133V are a phase-locked loop

frequency synthesizer LSI circuits for use in radio tuners.

It supports low-voltage (2.7 to 3.6 V) operation and can

implement high-performance AM/FM tuners easily.

Functions

• High speed programmable dividers

— FMIN: 10 to 120 MHz..........pulse swallower

(built-in divide-by-two prescaler), V

DD

≥ 2.7 V

10 to 130 MHz..........pulse swallower

(built-in divide-by-two prescaler), VDD≥ 3.0 V

— AMIN: 2 to 40 MHz..............pulse swallower

0.5 to 10 MHz...........direct division

• IF counter

— IFIN: 0.4 to 12 MHz...........AM/FM IF counter

• Reference frequencies

— Twelve selectable frequencies

(4.5 or 7.2 MHz crystal)

1, 3, 5, 9, 10, 3.125, 6.25, 12.5, 15, 25, 50 and 100 kHz

• Phase comparator

— Dead zone control

— Unlock detection circuit

— Deadlock clear circuit

• Built-in MOS transistor for forming an active low-pass

filter

• I/O ports

— Dedicated output ports: 4

— Input or output ports: 2

— Support clock time base output

• Serial data I/O

— Support CCB format communication with the

system controller.

• Operating ranges

— Supply voltage........................2.7 to 3.6 V

— Operating temperature............–20 to +70°C

• Package

MFP20

SSOP20

Package Dimensions

unit: mm

3036B-MFP20

unit: mm

3179A-SSOP20

SANYO: MFP20

[LC72133M]

SANYO: SSOP20

[LC72133V]

• CCB is a trademark of SANYO ELECTRIC CO., LTD.

• CCB is SANYO’s original bus format and all the bus

addresses are controlled by SANYO.

Pin Assignment

Block Diagram

No. 5427-2/22

LC72133M, 72133V

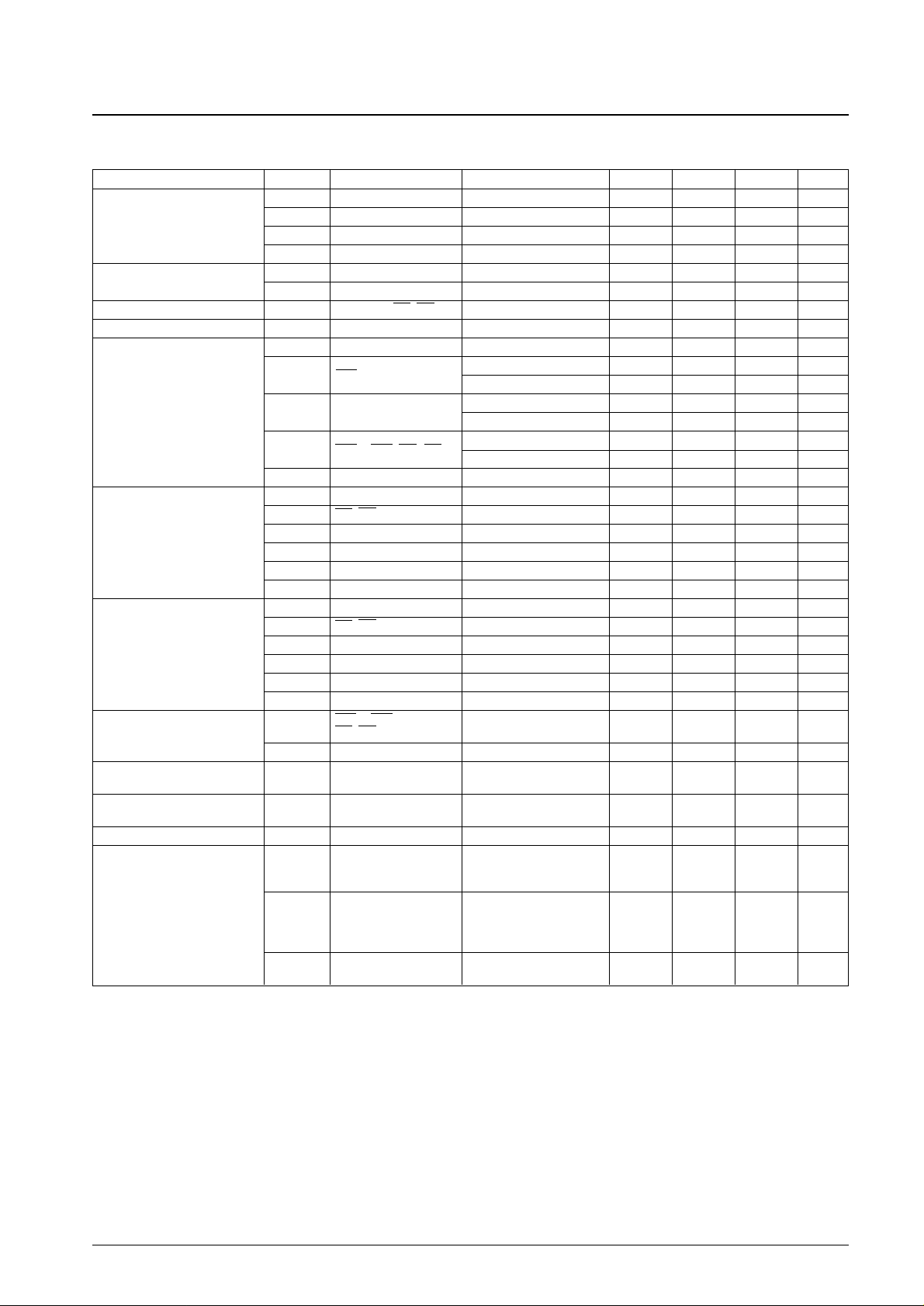

Specifications

Absolute Maximum Ratings at Ta = 25°C, VSS= 0 V

Allowable Operating Ranges at Ta = –20 to +70°C, VSS= 0 V

Note: * Recommended crystal oscillator CI values:

CI ≤ 120Ω (For a 4.5 MHz crystal)

CI ≤ 70Ω (For a 7.2 MHz crystal)

<Sample Oscillator Circuit>

Crystal oscillator: HC-49/U (manufactured by Kinseki, Ltd.), CL = 12 pF

C1 = C2 = 15 pF

The circuit constants for the crystal oscillator circuit depend on the crystal used, the printed circuit board pattern, and other items. Therefore we

recommend consulting with the manufacturer of the crystal for evaluation and reliability.

No. 5427-3/22

LC72133M, 72133V

Parameter Symbol Pins Ratings Unit

Supply voltage V

DD

max V

DD

–0.3 to +5.5 V

V

IN

1 max CE, CL, DI, AIN –0.3 to +5.5 V

Maximum input voltage V

IN

2 max XIN, FMIN, AMIN, IFIN –0.3 to VDD+ 0.3 V

V

IN

3 max IO1, IO2 –0.3 to +15 V

V

O

1 max DO –0.3 to +5.5 V

Maximum output voltage V

O

2 max XOUT, PD –0.3 to VDD+ 0.3 V

V

O

3 max BO1 to BO4, IO1, IO2, AOUT –0.3 to +15 V

I

O

1 max BO1 0 to 3.0 mA

Maximum output current I

O

2 max AOUT, DO 0 to 6.0 mA

I

O

3 max BO2 to BO4, IO1, IO2 0 to 6.0 mA

Allowable power dissipation Pd max

Ta ≤ 70°C: LC72133M 180 mW

Ta ≤ 70°C: LC72133V 160 mW

Operating temperature Topr –20 to +70 °C

Storage temperature Tstg –40 to +125 °C

Parameter Symbol Pins Conditions min typ max Unit

Supply voltage V

DD

V

DD

2.7 3.6 V

Input high-level voltage

V

IH

1 CE, CL, DI 0.7 V

DD

5.5 V

V

IH

2 IO1, IO2 0.7 V

DD

13 V

Input low-level voltage V

IL

CE, CL, DI, IO1, IO2 0 0.3 V

DD

V

V

O

1 DO 0 5.5 V

Output voltage

V

O

2

BO1 to BO4, IO1, IO2,

0 13 V

AOUT

f

IN

1 XIN VIN1 1 8 MHz

f

IN

2-1 FMIN VIN2-1 10 90 MHz

f

IN

2-2 FMIN VIN2-2 10 120 MHz

Input frequency f

IN

2-3 FMIN VIN2-1, VDD≥ 3.0 V 10 130 MHz

f

IN

3 AMIN VIN3, SNS = 1 2 40 MHz

f

IN

4 AMIN VIN4, SNS = 0 0.5 10 MHz

f

IN

5 IFIN VIN5 0.4 12 MHz

V

IN

1 XIN fIN1 400 900 mVrms

V

IN

2-1 FMIN fIN2-1, fIN2-3 70 900 mVrms

V

IN

2-2 FMIN fIN2-2 100 900 mVrms

Input amplitude V

IN

3 AMIN fIN3, SNS = 1 70 900 mVrms

V

IN

4 AMIN fIN4, SNS = 0 70 900 mVrms

V

IN

5-1 IFIN fIN5, IFS = 1 70 900 mVrms

V

IN

5-2 IFIN fIN6, IFS = 0 100 900 mVrms

Supported crystals Xtal XIN, XOUT * 4.0 8.0 MHz

Electrical Characteristics for the Allowable Operating Ranges at Ta = –20 to +70°C, VSS= 0 V

No. 5427-4/22

LC72133M, 72133V

Parameter Symbol Pins Conditions min typ max Unit

Rf1 XIN 1.0 MΩ

Built-in feedback resistance

Rf2 FMIN 500 kΩ

Rf3 AMIN 500 kΩ

Rf4 IFIN 250 kΩ

Built-in pull-down resistor

Rpd1 FMIN 200 kΩ

Rpd2 AMIN 200 kΩ

Hysteresis V

HIS

CE, CL, DI, IO1, IO2 0.1 V

DD

V

Output high level voltage V

OH

1 PD IO= –1 mA VDD– 1.0 V

V

OL

1 PD IO= 1 mA 1.0 V

V

OL

2 BO1

IO= 0.5 mA 0.6 V

I

O

= 1 mA 1.2 V

Output low level voltage V

OL

3 DO

IO= 1 mA 0.25 V

I

O

= 3 mA 0.75 V

V

OL

4 BO2 to BO4, IO1, IO2

IO= 1 mA 0.25 V

I

O

= 5 mA 1.25 V

V

OL

5 AOUT IO= 1 mA, AIN = 1.3 V 0.5 V

I

IH

1 CE, CL, DI VI= 5.5 V 5.0 µA

I

IH

2 IO1, IO2 VI= 13 V 5.0 µA

Input high level current

I

IH

3 XIN VI= V

DD

1.3 8 µA

I

IH

4 FMIN, AMIN VI= V

DD

2.7 15 µA

I

IH

5 IFIN VI= V

DD

5.4 30 µA

I

IH

6 AIN VI= 5.5 V 200 nA

I

IL

1 CE, CL, DI VI= 0 V 5.0 µA

I

IL

2 IO1, IO2 VI= 0 V 5.0 µA

Input low level current

I

IL

3 XIN VI= 0 V 1.3 8 µA

I

IL

4 FMIN, AMIN VI= 0 V 2.7 15 µA

I

IL

5 IFIN VI= 0 V 5.4 30 µA

I

IL

6 AIN VI= 0 V 200 nA

I

OFF

1

BO1 to BO4, AOUT,

VO= 13 V 5.0 µA

Output off leakage current

IO1, IO2

I

OFF

2 DO VO= 5.5 V 5.0 µA

High level three-state

I

OFFH

PD VO= V

DD

0.01 200 nA

off leakage current

Low level three-state

I

OFFL

PD VO= 0 V 0.01 200 nA

off leakage current

Input capacitance C

IN

FMIN 6 pF

Xtal = 7.2 MHz,

IDD1 V

DD

fIN2 = 130 MHz, 2 5 mA

V

IN

2 = 70 mVrms

PLL block stopped

Current drain

I

DD

2 V

DD

(PLL INHIBIT),

0.3 mA

Xtal oscillator operating

(Xtal = 7.2 MHz)

IDD3 V

DD

PLL block stopped

30 µA

Xtal oscillator stopped

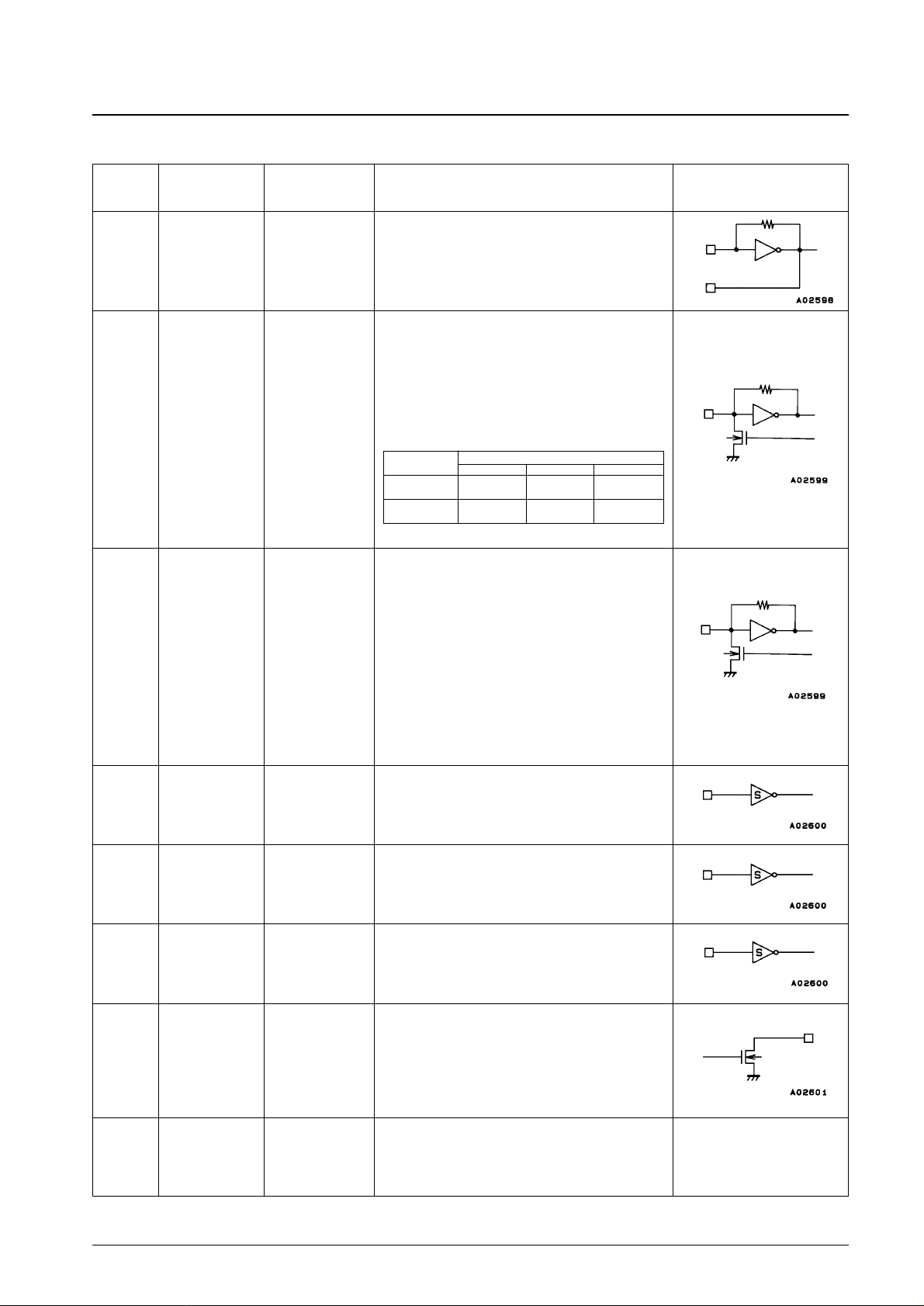

Pin Functions

No. 5427-5/22

LC72133M, 72133V

Symbol Pin No. Type Functions Circuit configuration

XIN

XOUT

FMIN

AMIN

CE

CL

DI

DO

V

DD

1

20

14

13

2

4

3

5

15

Xtal OSC

Local oscillator

signal input

Local oscillator

signal input

Chip enable

Clock

Data input

Data output

Power supply

• Crystal resonator connection

(4.5/7.2 MHz)

• FMIN is selected when the serial data input DVS bit is

set to 1.

• The input frequency range is from 10 to 130 MHz.

• The input signal passes through the internal divide-bytwo prescaler and is input to the swallow counter.

• The divisor can be in the range 272 to 65535. However,

since the signal has passed through the divide-by-two

prescaler, the actual divisor is twice the set value.

• AMIN is selected when the serial data input DVS bit is

set to 0.

• When the serial data input SNS bit is set to 1:

— The input frequency range is 2 to 40 MHz.

— The signal is directly input to the swallow counter.

— The divisor can be in the range 272 to 65535, and

the divisor used will be the value set.

• When the serial data input SNS bit is set to 0:

— The input frequency range is 0.5 to 10 MHz.

— The signal is directly input to a 12-bit programmable

divider.

— The divisor can be in the range 4 to 4095, and the

divisor used will be the value set.

Set this pin high when inputting (DI) or outputting (DO)

serial data.

• Used as the synchronization clock when inputting (DI) or

outputting (DO) serial data.

• Inputs serial data transferred from the controller to the

LC72133.

• Outputs serial data transferred from the LC72133 to the

controller.

The content of the output data is determined by the

serial data DOC0 to DOC2.

• The LC72133 power supply pin (V

DD

= 2.7 to 3.6 V)

• The power on reset circuit operates when power is first

applied.

Continued on next page.

Operating FMIN input frequency

conditions

10 to 90 MHz 10 to 120 MHz 10 to 130 MHz

Operating power-

2.7 to 3.6 V 2.7 to 3.6 V 3.0 to 3.6 V

supply voltage

Operating input 70 to 900 100 to 900 70 to 900

levels mVrms mVrms mVrms

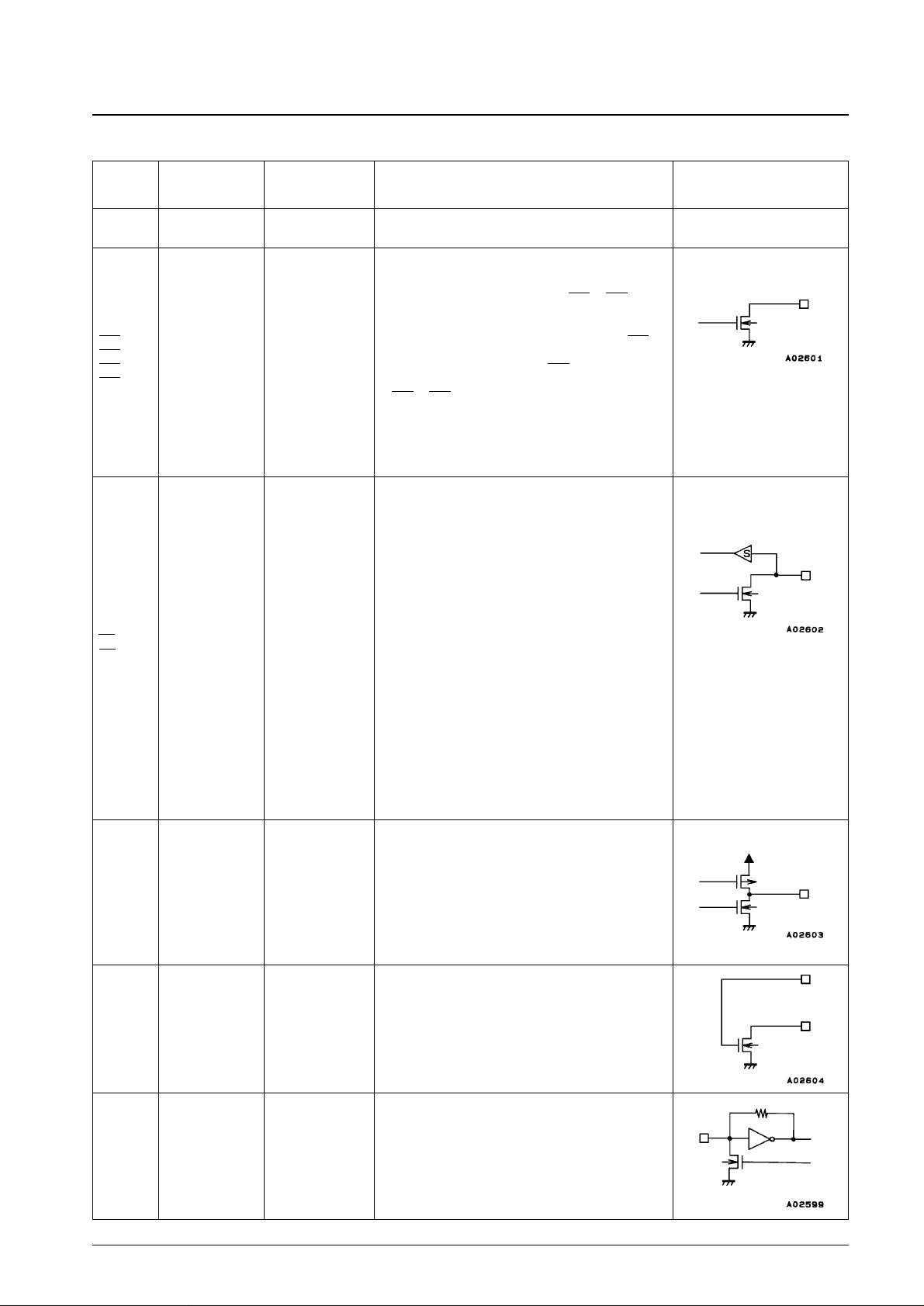

Continued from preceding page.

No. 5427-6/22

LC72133M, 72133V

Symbol Pin No. Type Functions Circuit configuration

V

SS

BO1

BO2

BO3

BO4

IO1

IO2

PD

AIN

AOUT

IFIN

19

6

7

8

9

10

12

16

17

18

11

Ground

Output port

I/O port

Charge pump

output

LPF amplifier

transistor

IF counter

• The LC72133 ground —

• Dedicated output pins

• The output states are determined by BO1 to BO4 bits in

the serial data.

Data: 0 = open, 1 = low

• A time base signal (8 Hz) can be output from the BO1

pin. (When the serial data TBC bit is set to 1.)

• Care is required when using the BO1 pin, since it has a

higher on impedance than the other output ports (pins

BO2 to BO4).

• The data = 0 (open) state is selected after the power-on

reset.

• I/O dual-use pins

• The direction (input or output) is determined by bits IOC1

and IOC2 in the serial data.

Data: 0 = input port, 1 = output port

• When specified for use as input ports:

The state of the input pin is transmitted to the controller

over the DO pin.

Input state: low = 0 data value

high = 1 data value

• When specified for use as output ports:

The output states are determined by the IO1 and IO2

bits in the serial data.

Data: 0 = open, 1 = low

• These pins function as input pins following a power on

reset.

• PLL charge pump output

When the frequency generated by dividing the local

oscillator frequency by N is higher than the reference

frequency, a high level is output from the PD pin.

Similarly, when that frequency is lower, a low level is

output. The PD pin goes to the high impedance state

when the frequencies match.

• The n-channel MOS transistor used for the PLL active

low-pass filter.

• Accepts an input in the frequency range 0.4 to 12 MHz.

• The input signal is directly transmitted to the IF counter.

• The result is output starting the MSB of the IF counter

using the DO pin.

• Four measurement periods are supported: 4, 8, 32, and

64 ms.

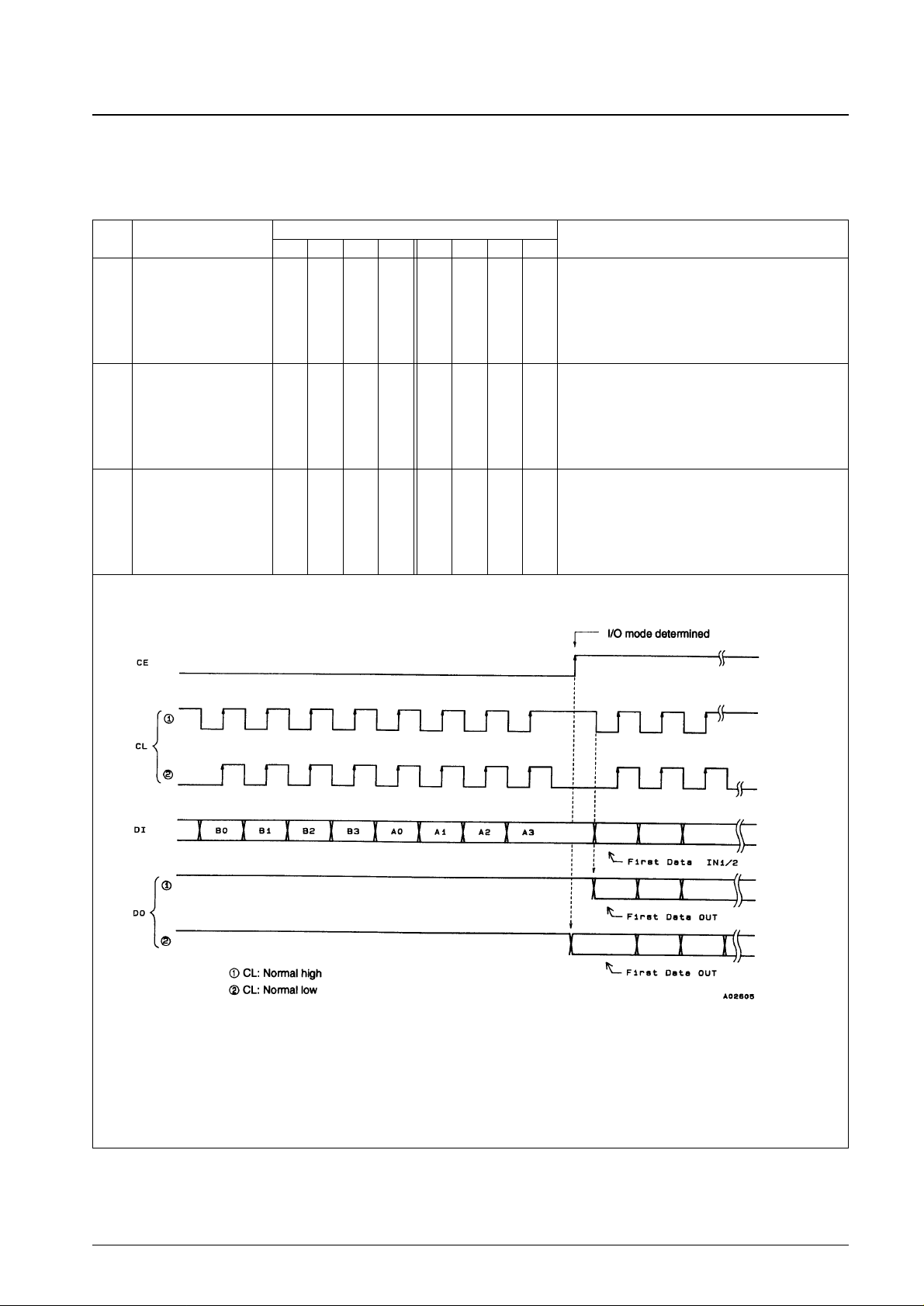

Serial Data I/O Methods

The LC72133 inputs and outputs data using the Sanyo CCB (computer control bus) audio LSI serial bus format. This

LSI adopts an 8-bit address format CCB.

No. 5427-7/22

LC72133M, 72133V

I/O mode

Address

Function

B0 B1 B2 B3 A0 A1 A2 A3

1

2

3

IN1 (82)

IN2 (92)

OUT (A2)

0 0 0 1 0 1 0 0

1 0 0 1 0 1 0 0

0 1 0 1 0 1 0 0

• Control data input mode (serial data input)

• 24 data bits are input.

• See the “DI Control Data (serial data input) Structure”

item for details on the meaning of the input data.

• Control data input mode (serial data input)

• 24 data bits are input.

• See the “DI Control Data (serial data input) Structure”

item for details on the meaning of the input data.

Data output mode (serial data output)

• The number of bits output is equal to the number of clock

cycles.

• See the “DO Output Data (Serial Data Output) Structure”

item for details on the meaning of the output data.

Loading...

Loading...