Ordering number : ENN*6830

LC680100A

32-Bit RISC Microcontroller

Preliminary

Overview

The LC680100A is a 32 bit microcontroller developed exclusively by Sanyo, based on a 32 bit RISC CPU and

incorporating on a single chip a high speed multiplier, 2kB of cache RAM, 2kB data RAM, DRAM control unit, external

memory control unit and peripheral

It is an ideal control device for digital cameras, color printers and hand held data terminals.

Features

(1) CPU core :32 bit RISC (Speed: 15MHz, Instruction cycle time: 67ns)

(2) High Speed Multiplier :16bit x 16bit (in 1 instruction cycle)

(3) Instruction cache RAM :2kB (512x32bit)

(4) Data RAM :2kB (512x32bit)

(5) DRAM Control Unit

(6) External memory bus control unit

(7) I/O port :One 16 bit I/O port, one 8 bit I/O port

(8) UART :Two full duplex asynchronous channels (one channel has 16bit FIFO)

(9) Serial I/O :One three-wire synchronous clock, 8 bit

(10) Timer :4 channels (TM0 = 16bit + 16bit)

(TM1, TM2, TM 3 = 8bit + 8bit)

(11) PWM Output :Three 8 bit resolution outputs (Common with TM1, TM2, TM3)

(12) Interrupt controller :13 source events (5 internal, 8 external), 5 vectored

(13) OSC circuit :Two types: main and RC. VCO/PLL is built-in, frequency multiplication possible.

(14) Standby :Standby (HOLD) and sleep (HALT) modes available

(15) VDD :3.3V typ.

Package and Pins

SQFP100, 10 0 pins

Development tools

A C compiler, assembler and emulator are available to be run on a PC.

CMOS IC

Ver.1.2

D0798

N3000 RM (IM) IT No.6830-1/16

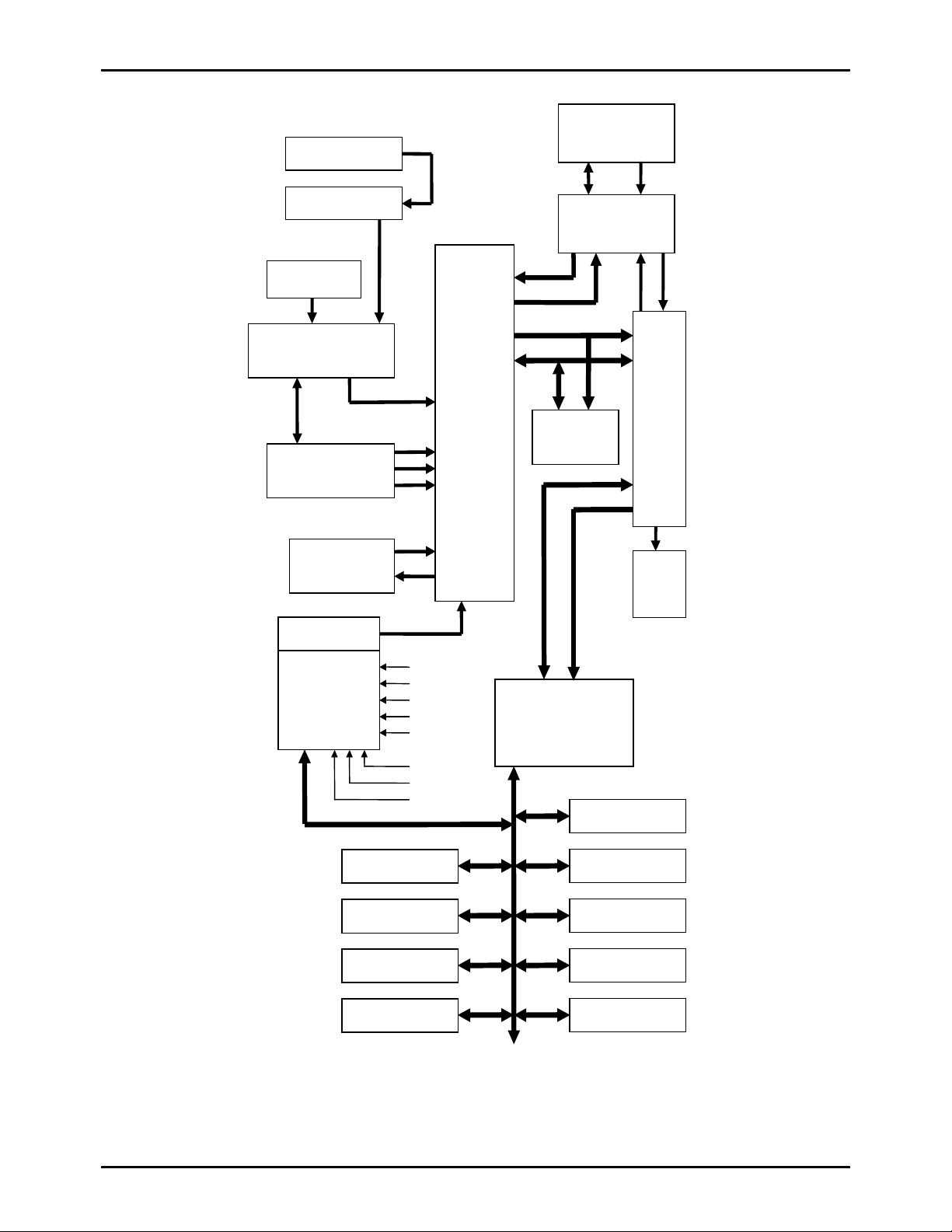

System Bl ock Diagram

LC680100A

Main OSC

Multiplie r Circu it

RC OSC

System Clock, Standby

Control

Mode Control

Reset Control

Coprocessor

(Multiplier)

32bit

RISC

CORE

Instruction Cache

(2k bytes)

Instruction Cache

Control

Data RAM

(2k bytes)

Bus

Control

DRAM

Control

Interrupt Control

Interrupt en ab le

control

TM0H

TM0L

TM1H

TM2H

TM3H

SIO0

UART0

UART1

Timer 0

Timer 1

Timer 2

Timer 3

Figure 1 LC680100A System Block Diagram

Special Function R eg ister

SFR Bus Control

SIO0

UART0

UART1

Port 0

Port 1

No.6830-2/16

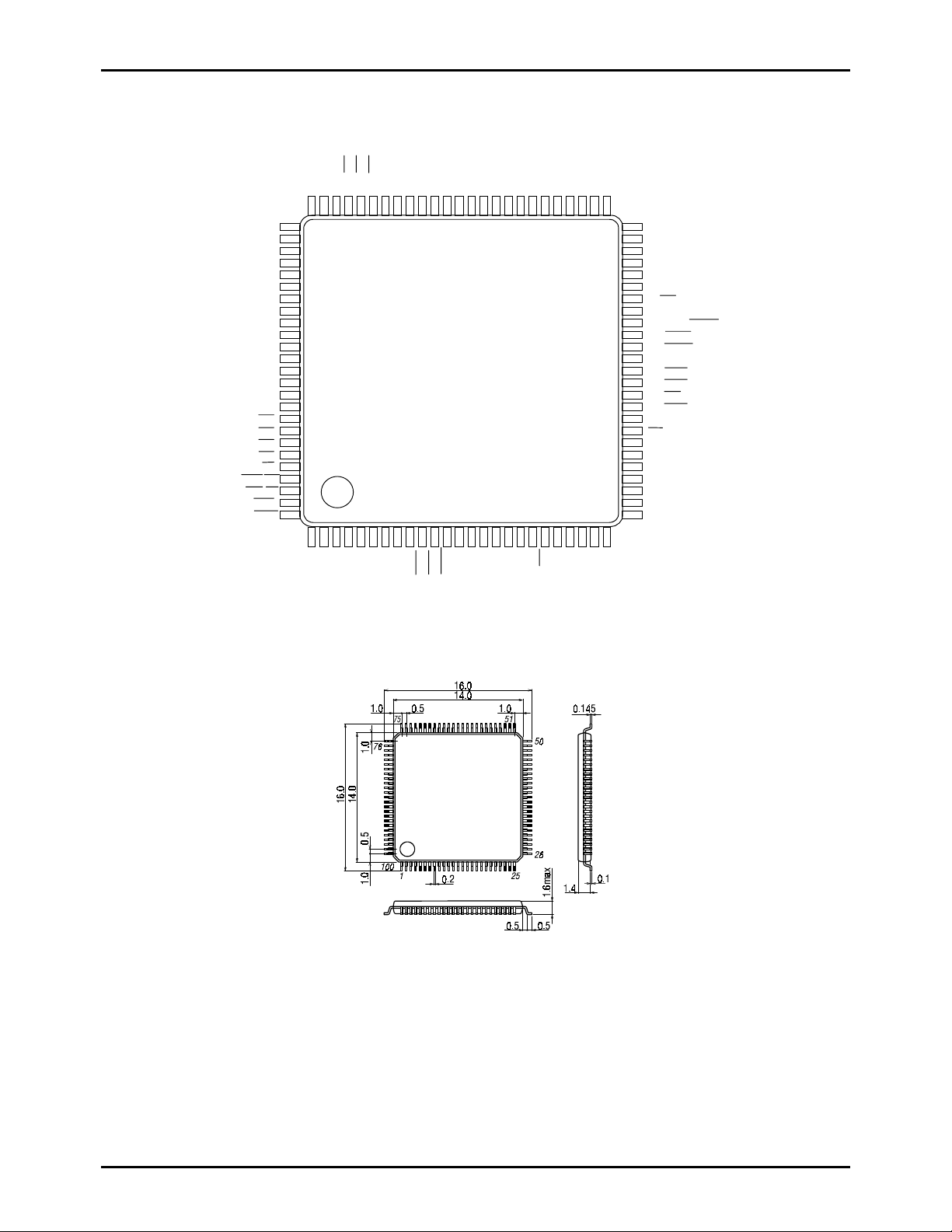

Terminal Assignment Diagram

(SQFP100, 0. 5 mm pit c h)

VSS

D0

D1

LC680100A

VDD

A27/CS3

A22

A23

A25/CS5

A17

A18

A19

A20

A21

A24

A26/CS4

A13

A11

A12

A14

A15

A16

A7

A8

A9

A10

VDD

D10

D11

D12

D13

D14

D15

VSS

CS0

CS1

CS2

CS6

WRU/UBS

WRL/WR

WAIT

BREQ

Package Dimension

(unit : mm)

3181B

D2

76

D3

77

D4

78

D5

79

D6

80

D7

81

82

D8

83

D9

84

85

86

87

88

89

90

91

92

93

94

95

RD

96

97

98

99

100

1 2 3 4 5 6 7 8 910111213141516171819202122232425

VDD

CK1

LC680100A

VSS

VDD

CK2

CMP

VSS

CKOT

CKIN

HOLDI

RESET

PHIOT

MODE

TEST

57 56 55 54 53 52 5160 59 5867 66 65 64 63 6270 69 68 6175 74 73 72 71

VDD

P02/SDO

P03/SDI

P00/TXD0

P04/SCK

P01/RXD0

VSS

P05/PWM0

P06/PWM1

P07/T0IN/INT0

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

P08/INT1

A6

A5

A4

A3

A2

A1

A0/LBS

VSS

P17/MCLK/HOLDO

P16/IRQOT

P15/RFREQ

P14/DMXS

P13/CASL

P12/CASU

P11/RAS

P10/BGNT

VDD

NMI

P0F

P0E

P0D/RXD1

P0C/TXD1

P0B/PWM2

P0A/INT3

P09/INT2

SANYO : SQFP-100

No.6830-3/16

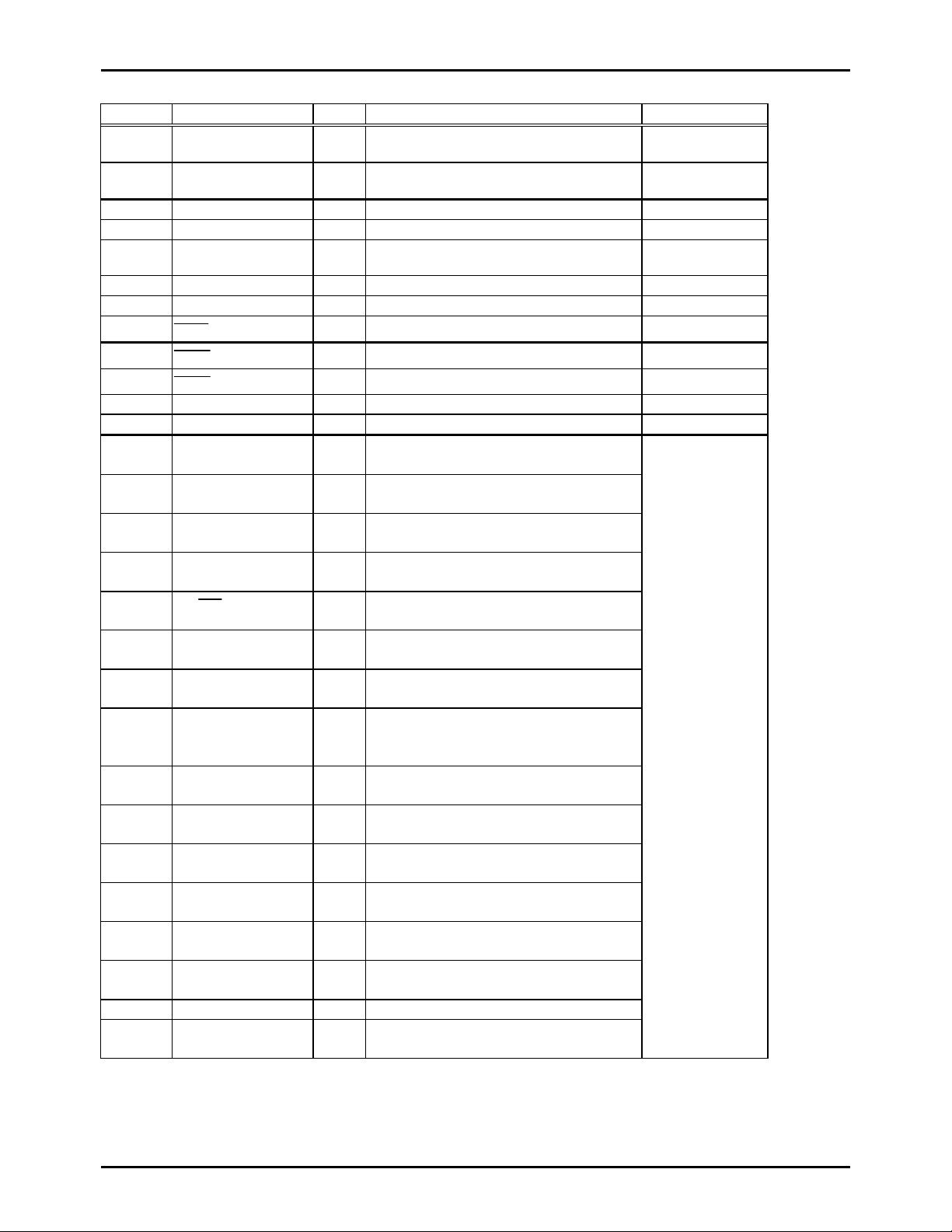

LC680100A

Terminal Functions

Pin Number Pin Name I/O Function Description Pin Format

1,6,15,34,55

,82

4,9,24,43,73

,91

2 CK1 I Input to main oscillator Schmitt Input

3 CK2 O Output from main oscillat or CMOS output

5 CMP I/O Phase comparator filter pin (multiplier circuit). Schmitt Input•Tristate

7 CKOT O CK1 or half frequency clock output from multiplier CMOS output

8 CKIN I External clock input Schmitt Input

10

11

12

13 MODE I Bus mode setting at reset Schmitt Input

14 TEST I Test input (Normally connected to VSS) Schmitt Input

16 P00/TXD0 I/O PORT0 bit0 I/O.

17 P01/RXD0 I/O PORT0 bit1 I/O.

18 P02/SDO I/O PORT0 bit2 I/O.

19 P03/SDI I/O PORT0 bit3 I/O.

20

21 P05/PWM0 I/O PORT0 bit5 I/O.

22 P06/PWM1 I/O PORT0 bit6 I/O.

23 P07/T0IN/INT0 I/O PORT0 bit7 I/O.

25 P08/INT1 I/O PORT0 bit8 I/O.

26 P09/INT2 I/O PORT0 bit9 I/O.

27 P0A/INT3 I/O PORT0 bit10 I/O.

28 P0B/PWM2 I/O PORT0 bit11 I/O.

29 P0C/TXD1 I/O PORT0 bit12 I/O.

30 P0D/RXD1 I/O PORT0 bit13 I/O.

31 P0E I/O PORT0 bit14 I/O.

32

VDD - Power supply +ve -

VSS - Power supply -ve -

PHIOT

HOLDI

RESET

SCK

P04/

P0F I/O PORT0 bit15 I/O.

Note: PU = pull-up

output

O System clock output CMOS output

I HOLD request input Schmitt Input

I Reset terminal Schmitt Input

•Used as input:

Also UA R T0 send

Also UART0 receive

Also SIO0 data out

Also SIO0 data in

I/O PORT0 bit4 I/O.

Also SIO0 clock

Also PWM0 output

Also PWM1 output

Timer0 event input

INT0 input

INT1 input

INT2 input

INT3 input

PWM2 output

UART1 send

UART1 receive

Schmitt Input;

presence of PU

resistor software

selectable.

•Used as Output:

CMOS/N-ch OD

mode so ftware

selectable.

No.6830-4/16

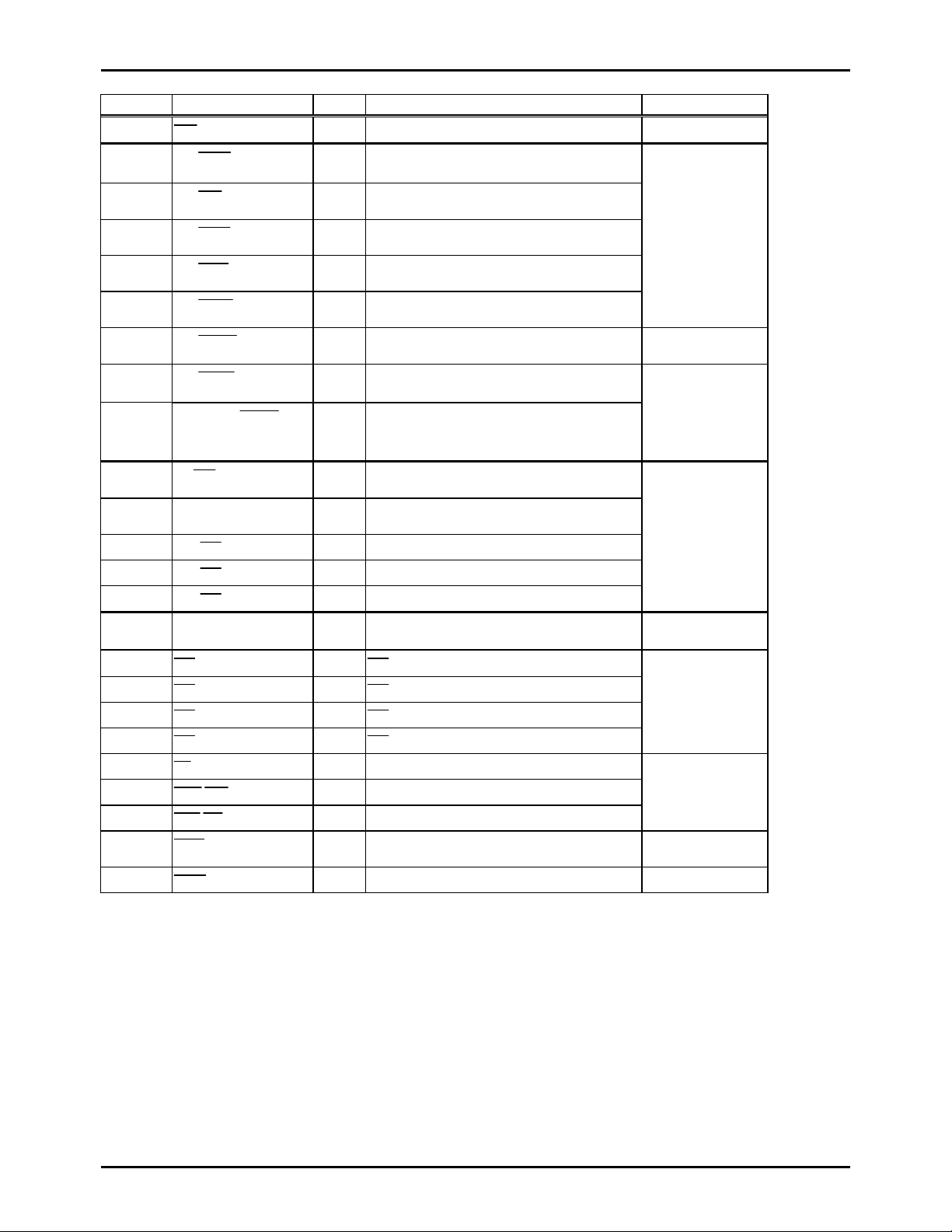

LC680100A

Pin Number Pin Name I/O Function Description Pin Format

33

35

36

37

38

39

40

41

42

44

45 to 54,

56 to 69

70

71

72

74 to 81,

83 to 90

92

93

94

95

96

97

98

99

100

NMI

BGNT

P10/

P11/

P12/

P13/

P14/

P15/

P16/

P17/MCLK/

A0/

RAS

CASU

CASL

DMXS

RFREQ

IRQOT

LBS

HOLD0

A1to A24 I/O Bus Address bit1 to 24.

CS5

A25/

A26/

A27/

CS4

CS3

D0 to D15 I/O Bus data bit0 to 15 Schmitt Input•Tristate

CS0

CS1

CS2

CS6

RD

WRU/UBS

WRL/WR

WAIT

BREQ

I NMI interrupt Schmitt Input

I/O PORT1 bit0 input.

Also bus grant output.

Schmitt Input•Tristate

output

I/O PORT1 bit1 input. Also

DRAM control R AS signal out.

I/O PORT1 bit2 input. Also

DRAM control C ASU signal out.

I/O PORT1 bit3 input. Also

DRAM control C ASL signal out.

I/O PORT1 bit4 input. Also

DRAM contr ol DM XS signal out.

I/O PORT1 bit5 input. Also

DRAM control RFREQ I/O.

I/O PORT1 bit6 input.

Also IRQOT output.

Schmitt Input•PU

Output

Schmitt Input•Tristate

output

I/O PORT1 bit7 input.

MCLK output,

HOLD sta te output

I/O Bus Address bit0 or

Lower byte strobe signal.

I/O

Bus Address bit25 or CS5.

I/O

Bus Address bit26 or CS4

I/O

Bus Address bit27 or CS3.

Schmitt Input•Tristate

output

output

I/O

CS0

I/O

CS1

I/O

CS2

I/O

CS6

I/O Bus read signal.

I/O Upper byte write signal or Upper byte strobe.

Schmitt Input•Tristate

output

Schmitt Input•Tristate

output

I/O Upper byte write signal or Write.

I/O Bus cycle wait Schmitt Input•PU

output

I Bus request. Schmitt Input

No.6830-5/16

Loading...

Loading...