SANYO LC665316A, LC665312A, LC665308A, LC665306A, LC665304A Datasheet

CMOS LSI

No. 5485

LC665304A, 665306A, 665308A, 665312A, 665316A

F

with 4, 6, 8, 12, and 16 KB of On-Chip ROM

Preliminary

Overview

The LC665304A, LC665306A, LC665308A, LC665312A,

and LC665316A are 4-bit CMOS microcontrollers that

integrate on a single chip all the functions required in a

system controller, including ROM, RAM, I/O ports, a

serial interface, 16-value comparator inputs, timers,

interrupt functions, and an optional sub-oscillator circuit.

These microcontrollers are available in a 48-pin package.

Features and Functions

• On-chip ROM capacitiy of 4, 6, 8, 12, and 16 kilobytes,

and an on-chip RAM capacity of 512 × 4 bits.

• Fully supports the LC66000 Series common instruction

set (128 instructions).

• I/O ports: 42 pins

• A sub-oscillator circuit can be used (option)

This circuit allows power dissipation to be reduced by

operating at lower speeds.

• 8-bit serial interface: two circuits (can be connected in

cascade to form a 16-bit interface)

• Instruction cycle time: 0.95 to 10 µs (at 3 to 5.5 V)

• Powerful timer functions and prescalers

— Time limit timer, event counter, pulse width

measurement, and square wave output using a 12-bit

timer.

— Time limit timer, event counter, PWM output, and

square wave output using an 8-bit timer.

— Time base function using a 12-bit prescaler.

• Powerful interrupt system with 8 interrupt factors and 8

interrupt vector locations.

— External interrupts: 3 factors/3 vector locations

— Internal interrupts: 5 factors/5 vector locations

• Flexible I/O functions

16-value comparator inputs, 20-mA drive outputs,

inverter circuits, pull-up and open-drain circuits

selectable as options.

• Optional runaway detection function (watchdog timer)

• 8-bit I/O functions

• Power saving functions using halt and hold modes.

• Packages: DIP48S, QIP48E (QFP48E)

our-Bit Single-Chip Microcontrollers

• Evaluation LSIs: LC66599 (evaluation chip) +

EVA800/850-TB662YXX2

LC66E5316(on-chip EPROM microcontroller)

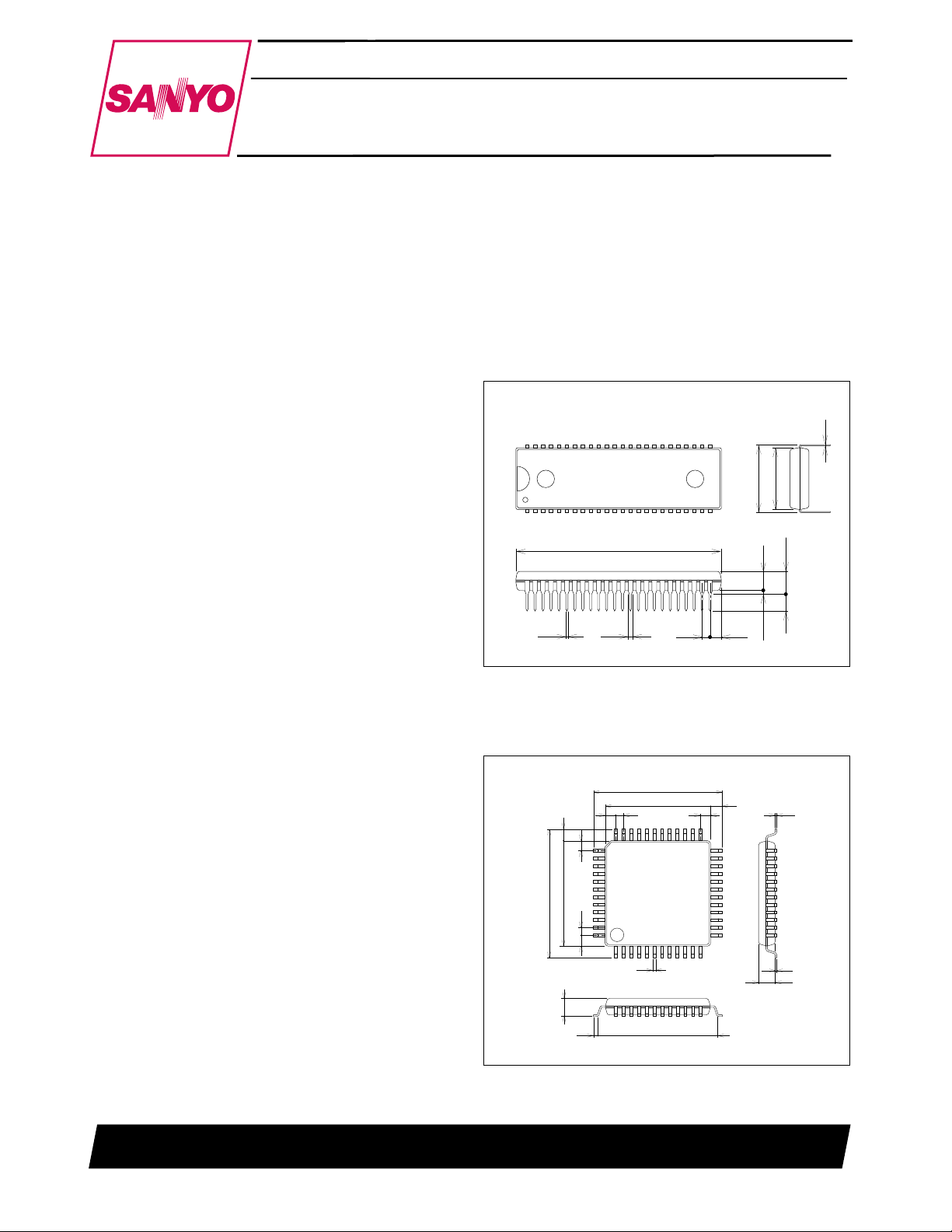

Package Dimensions

unit: mm

3149-DIP48S

[LC665304A/665306A/665308A/665312A/665316A]

2548

15.24

13.8

1

46.0

0.48

1.05 1.78

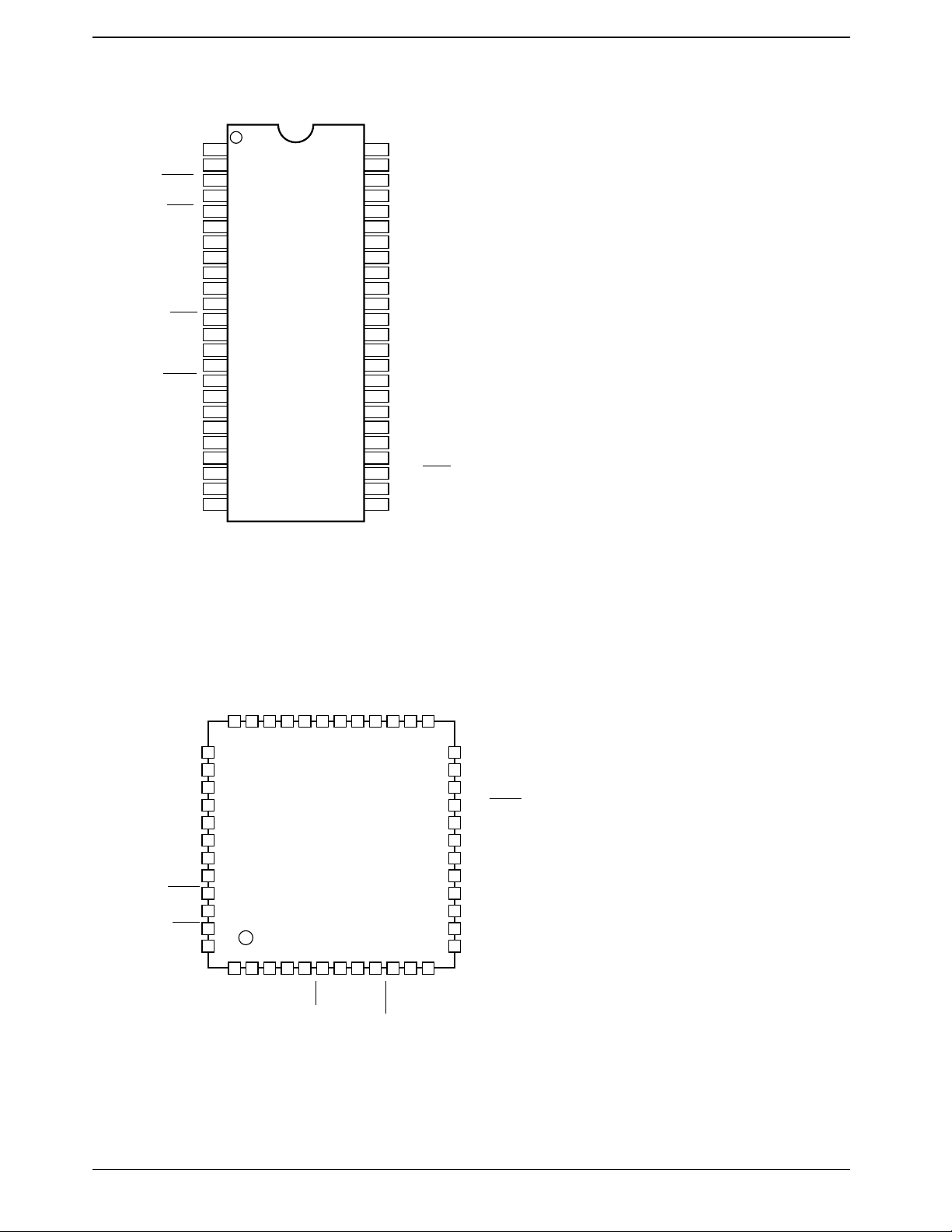

unit: mm

3156-QFP48E

[LC665304A/665306A/665308A/665312A/665316A]

17.2

14.0

1.0

1.5

36

1.614.0

37

1.5

17.2

1.0

1.5

48

112

0.35

3.0max

0.8

15.6

24

2.53

1.6

1.5

25

24

13

SANYO: QFP48E

5.1max

4.25

3.8

0.51min

SANYO: DIP48S

0.15

0.1

2.70

(STAND OFF)

0.25

SANYO Electric Co.,Ltd. Semiconductor Bussiness Headquarters

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110 JAPAN

22897HA (OT) No. 5485-1/26

Series Organization

LC665304A, 665306A, 665308A, 665312A, 665316A

Type No.

LC66304A/306A/308A 42 4 K/6 K/8 KB 512 W DIP42S QFP48E

LC66404A/406A/408A 42 4 K/6 K/8 KB 512 W DIP42S QFP48E

LC66506B/508B/512B/516B 64 6 K/8 K/12 K/16 KB 512 W DIP64S QFP64A

LC66354A/356A/358A 42 4 K/6 K/8 KB 512 W DIP42S QFP48E

LC66354S/356S/358S 42 4 K/6 K/8 KB 512 W QFP44M

LC66556A/558A/562A/566A 64 6 K/8 K/12 K/16 KB 512 W DIP64S QFP64E

LC66354B/356B/358B 42 4 K/6 K/8 KB 512 W DIP42S QFP48E

LC66556B/558B/562B/566B 64 6 K/8 K/12 K/16 KB 512 W DIP64S QFP64E

LC66354C/356C/358C 42 4 K/6 K/8 KB 512 W DIP42S QFP48E 2.5 to 5.5 V/0.92 µs

LC662104A/06A/08A 30 4 K/6 K/8 KB 384 W DIP30SD MFP30S

LC662304A/06A/08A/12A/16A 42

LC662508A/12A/16A 64 8 K/12 K/16 KB 512 W DIP64S QFP64E

LC665304A/06A/08A/12A/16A 48

LC66E308 42 EPROM 8 KB 512 W

LC66P308 42 OTPROM 8 KB 512 W DIP42S QFP48E

LC66E408 42 EPROM 8 KB 512 W

LC66P408 42 OTPROM 8 KB 512 W DIP42S QFP48E

LC66E516 64 EPROM 16 KB 512 W

LC66P516 64 OTPROM 16 KB 512 W DIP64S QFP64E

LC66E2108* 30 EPROM 8 KB 384 W

LC66E2316 42 EPROM 16 KB 512 W

LC66E2516 64 EPROM 16 KB 512 W

LC66E5316 52/48 EPROM 16 KB 512 W

LC66P2108* 30 OTPROM 8 KB 384 W DIP30SD MFP30S

LC66P2316* 42 OTPROM 16 KB 512 W DIP42S QFP48E

LC66P2516 64 OTPROM 16 KB 512 W DIP64S QFP64E

LC66P5316 48 OTPROM 16 KB 512 W DIP48S QFP48E

Note: * Under development

No. of

pins capacity

ROM capacity

4 K/6 K/8 K/12 K/16 KB

4 K/6 K/8 K/12 K/16 KB

RAM

512 W DIP42S QFP48E

512 W DIP48S QFP48E

DIC42S QFC48

with window with window

DIC42S QFC48

with window with window

DIC64S QFC64

with window with window

DIC42S QFC48

with window with window

DIC64S QFC64

with window with window

DIC52S QFC48

with window with window

Package Features

Normal versions

4.0 to 6.0 V/0.92 µs

Low-voltage versions

2.2 to 5.5 V/3.92 µs

Low-voltage high-speed versions

3.0 to 5.5 V/0.92 µs

On-chip DTMF generator versions

3.0 to 5.5 V/0.95 µs

Dual oscillator support

3.0 to 5.5 V/0.95 µs

Window and OTP evaluation versions

4.5 to 5.5 V/0.92 µs

Window evaluation versions

4.5 to 5.5 V/0.92 µs

OTP

4.0 to 5.5 V/0.95 µs

No. 5485-2/26

Pin Assignments

LC665304A, 665306A, 665308A, 665312A, 665316A

DIP48S

P20/SI0

P21/SO0

P22/SCK0

P23/INT0

P30/INT1

P31/POUT0

P32/POUT1

V

SS

OSC1

OSC2

V

DD

RES

PE0/XT1

PE1/XT2

TEST

P33/HOLD

P40/INV0I

P41/INV0O

P42/INV1I

P43/INV1O

P50

P51

P52

P53/INT2

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

1

2

3

4

5

6

7

8

9

LC665304A

5306A

5308A

5312A

5316A

QFP48E

P13

48

P12

47

P11

46

P10

45

P03

44

P02

43

P01

42

P00

41

PD3/AN4/INV4O

40

PD2/AN3/INV4I

39

PD1/AN2/INV3O

38

PD0/AN1/INV3I

37

PC3/INV2O

36

PC2/INV2I

35

PC1

34

PC0

33

P83

32

P82

31

P81/DS1

30

P80/DS0

29

P63/PIN1

28

P62/SCK1

27

P61/SO1

26

P60/SI1

25

P01

P00

PD3/AN4/INV4O

PD2/AN3/INV4I

PD1/AN2/INV3O

PD0/AN1/INV3I

PC3/INV2O

PC2/INV2I

PC1

PC0

P83

P82

36

35

34

33

32

31

30

29

28

27

26

25

37P02

38P03 23 P80/DS0

39P10 22 P63/PIN1

40P11 21 P62/SCK1

41P12 20 P61/SO1

42P13 19 P60/SI1

43P20/S10 18 P53/INT2

44P21/SO0 17 P52

45P22/SCK0 16 P51

46P23/INT0 15 P50

47P30/INT1 14 P43/INV1O

48P31/POUT0 13 P42/INV1I

1

2

P32/POUT1

V

3

SS

LC665304A

4

OSC1

OSC2

5306A

5308A

5312A

5316A

5

6

7

8

9

DD

RES

V

TEST

PE0/XT1

PE1/XT2

10

11

12

P40/INV0I

P33/HOLD

24 P81/DS1

P41/INV0O

Top view

We recommend the use of reflow soldering techniques to solder-mount QFP packages.

Please consult with your Sanyo representative for details on process conditions if the package itself is to be directly

immersed in a dip-soldering bath (dip-soldering techniques).

No. 5485-3/26

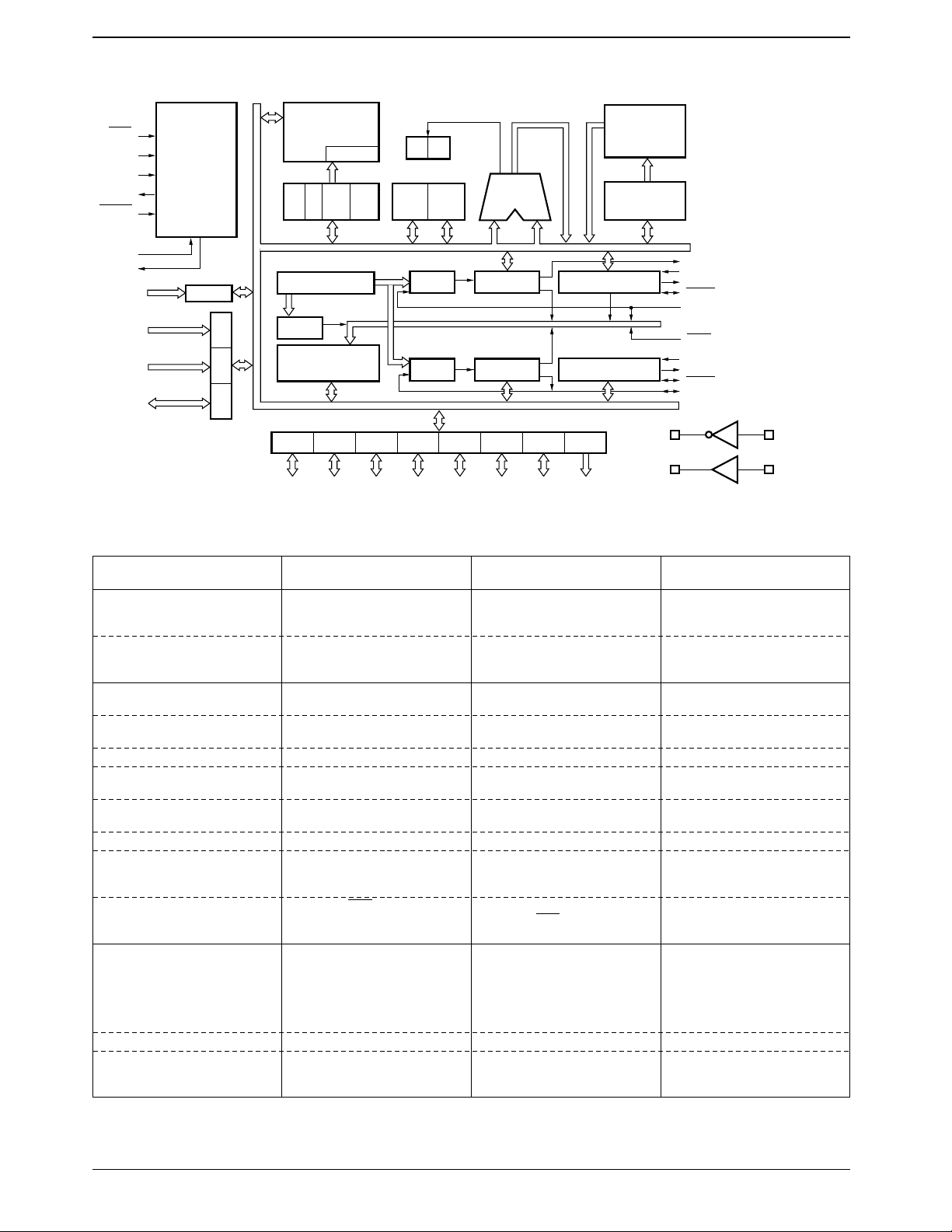

System Block Diagram

LC665304A, 665306A, 665308A, 665312A, 665316A

RES

TEST

OSC1

OSC2

HOLD

XT1

XT2

AN1 to 4

SYSTEM

CONTROL

ADC

RAM STACK

(512W)

FLAG

E

D

D

D

SP E A

M

R

P

P

P

X

L

H

PRESCALER

CZ

D

P

Y

MPX TIMER0 SERIAL I/O 0

ALU

ROM

4K/6K/8K/12K/16KB

PC

POUT0

SI0

SO0

SCK0

INT0

PE

PD

PC

MPX

INTERRUPT

CONTROL

MPX

TIMER1

P0 P1 P2 P3 P4 P5 P6

SERIAL I/O 1

P8

INT1, INT2

SI1

SO1

SCK1

PIN1, POUT1

INV

xO INVxI

(x=0 to 4)

DS1 DS0

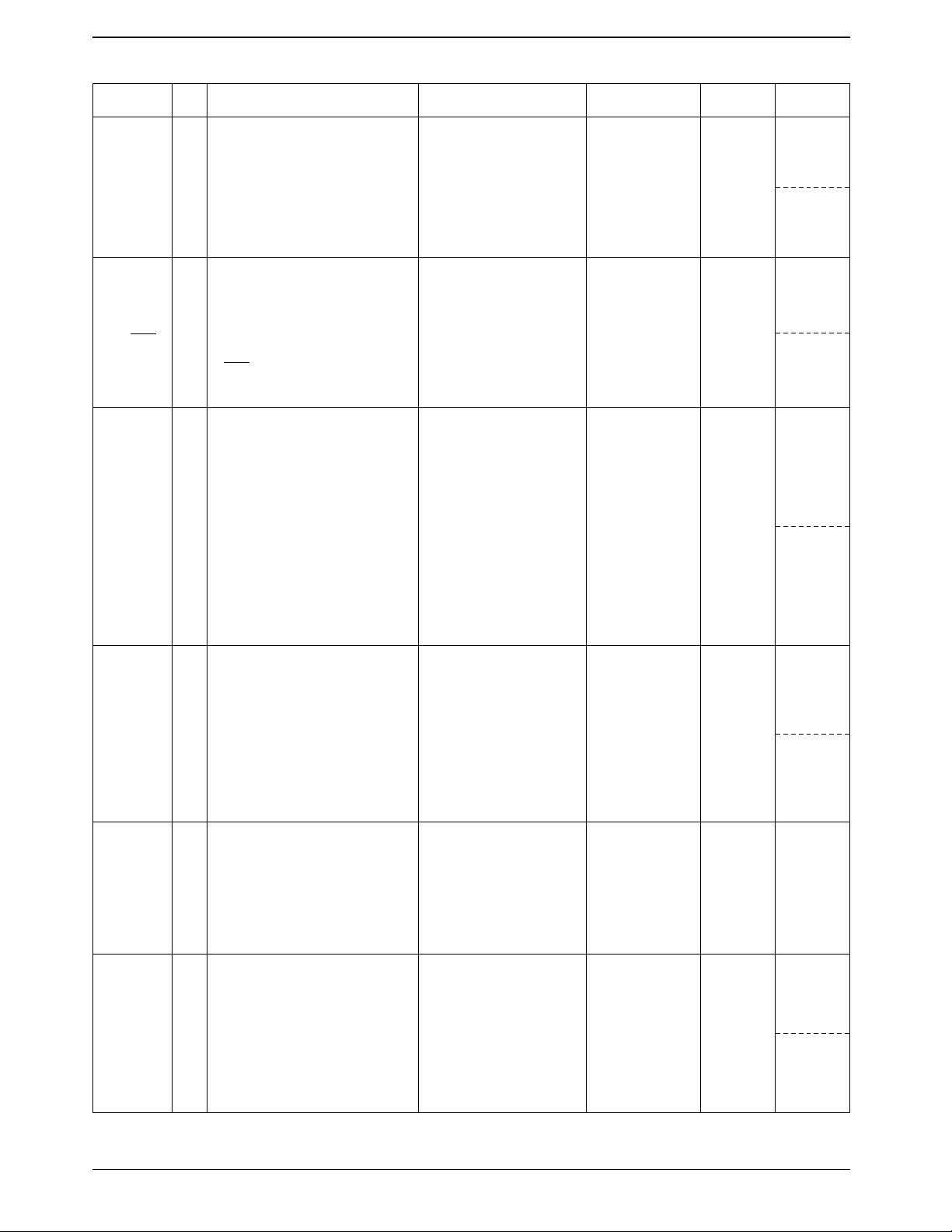

Differences between the LC6653XX Series and the LC663XX Series

Item

System differences

• Hardware wait time (number of

cycles) when hold mode is cleared

• Value of timer 0 after a reset

(Including the value after hold mode Set to FF0. Set to FFC. Set to FFC.

is cleared)

• Inverter array

• Buffer array (data shaper circuit)

• Sub-oscillator None None Yes (option)

• Three-value inputs/comparator

inputs

• Three-state output from P31

and P32

• Using P0 to clear halt mode In 4-bit groups In 4-bit groups Can be specified for each bit.

• External extended interrupts (Tools are handled with external None for INT3, INT4, and INT5. None for INT3, INT4, and INT5.

• Other P53 functions (Tools are handled with external Shared with INT2

Differences in main characteristics

• Operating power-supply voltage

and operating speed (cycle time)

• Pull-up resistors P0, P1, P4, and P5: about 3 to 10 kΩ P0, P1, P4, and P5: about 3 to 10 kΩ P0, P1, P4, and P5: about 100 kΩ

• Port voltage handling • P0, P1, PD, PE: Normal voltage • P0, P1, PD, PE: Normal voltage

(Including the LC66599 evaluation chip)

65536 cycles 16384 cycles 16384 cycles

About 64 ms at 4 MHz (Tcyc = 1 µs) About 16 ms at 4 MHz (Tcyc = 1 µs) About 16 ms at 4 MHz (Tcyc = 1 µs)

None (Tools are handled with

external devices.)

None (Tools are handled with

external devices.)

Yes Yes Only a 16-value comparator

None None Yes

None for INT3, INT4, and INT5.

devices.)

Shared with INT2

devices.)

• LC66304A/306A/308A • 3.0 to 5.5 V/0.92 to 10 µs (When the main oscillator is

• LC66E308/P308 2.2 to 5.5 V/3.92 to 10 µs • 3.0 to 5.5 V/25 to 127 µs

• P2 to P6 and PC: 15-V handling • P2 to P6 and PC: 15-V handling

LC6630X Series

4.0 to 6.0 V/0.92 t 10 µs • LC6635XA operating)

4.5 to 5.5 V/0.92 to 10 µs 3.0 to 5.5 V/1.96 to 10 µs (When the sub-oscillator is

handling handling

LC6635XB Series LC6653XX Series

None Yes

None Yes

Shared with INT2

(The logic is inverted.)

• 3.0 to 5.5 V/0.95 to 10 µs

operating)

All ports: normal voltage handling

(7-V handling provided)

For other differences and details, see the data sheets for the individual products.

No. 5485-4/26

Pin Function Overview

LC665304A, 665306A, 665308A, 665312A, 665316A

Pin I/O Overview Output driver type Options

P00

P01

P02

P03

P10

P11

P12

P13

P20/SI0

P21/SO0

P22/SCK0

P23/INT0

P30/INT1

P31/POUT0

P32/POUT1

I/O ports P00 to P03

• Input or output in 4-bit or 1-bit units

• P00 to P03 support the halt mode

I/O

control function (This function can be

specified in bit units.)

I/O ports P10 to P13

I/O

Input or output in 4-bit or 1-bit units

I/O ports P20 to P23

• Input or output in 4-bit or 1-bit units

• P20 is also used as the serial input SI0

pin.

• P21 is also used as the serial output

SO0 pin.

I/O

• P22 is also used as the serial clock

SCK0 pin.

• P23 is also used as the INT0 interrupt

request pin, and also as the timer 0

event counting and pulse width

measurement input.

I/O ports P30 to P32

• Input or output in 3-bit or 1-bit units

• P30 is also used as the INT1 interrupt

request.

• P31 is also used for the square wave

I/O

output from timer 0.

• P32 is also used for the square wave

and PWM output from timer 1.

• P31 and P32 also support 3-state

outputs.

• Pch: Pull-up MOS type

• Nch: Intermediate sink current

type

• Pch: Pull-up MOS type

• Nch: Intermediate sink current

type

• Pch: CMOS type

• Nch: Intermediate sink current

type

• Nch: +7-V handling when OD

option selected

• Pch: CMOS type

• Nch: Intermediate sink current

type

• Nch: +7-V handling when OD

option selected

• Pull-up MOS or

Nch OD output

• Output level on

reset

• Pull-up MOS or

Nch OD output

• Output level on

reset

CMOS or Nch OD

output

CMOS or Nch OD

output

State after a Standby mode

reset operation

Hold mode:

High or low

(option)

High or low

(option)

H

H

Output off

Halt mode:

Output

retained

Hold mode:

Output off

Halt mode:

Output

retained

Hold mode:

Output off

Halt mode:

Output

retained

Hold mode:

Output off

Halt mode:

Output

retained

P33/HOLD

P40/INV0I

P41/INV0O

P42/INV1I

P43/INV1O

Hold mode control input

• Hold mode is set up by the HOLD

instruction when HOLD is low.

• In hold mode, the CPU is restarted by

setting HOLD to the high level.

• This pin can be used as input port P33

I

along with P30 to P32.

• When the P33/HOLD pin is at the low

level, the CPU will not be reset by a

low level on the RES pin. Therefore,

applications must not set P33/HOLD

low when power is first applied.

I/O ports P40 to P43

• Input or output in 4-bit or 1-bit units

• Input or output in 8-bit units when used

in conjunction with P50 to P53.

I/O

• Can be used for output of 8-bit ROM

data when used in conjunction with

P50 to P53.

• Dedicated inverter circuit (option)

• Pch: Pull-up MOS type

• CMOS type when the inverter

circuit option is selected

• Nch: Intermediate sink current

type

• Pull-up MOS or

Nch OD output

• Output level on

reset

• Inverter circuit

Hold mode:

Port output

off, inverter

High or low

or inverter

I/O (option)

output off

Halt mode:

Port output

retained,

inverter

output

continues

Continued on next page.

No. 5485-5/26

LC665304A, 665306A, 665308A, 665312A, 665316A

Pin I/O Overview Output driver type Options

I/O ports P50 to P53

• Input or output in 4-bit or 1-bit units

P50

P51

P52

P53/INT2

P60/SI1

P61/SO1

P62/SCK1

P63/PIN1

P80/DS0

P81/DS1

P82

P83

• Input or output in 8-bit units when used

in conjunction with P40 to P43.

• Can be used for output of 8-bit ROM

I/O

data when used in conjunction with

P40 to P43.

• P53 is also used as the INT2 interrupt

request.

I/O ports P60 to P63

• Input or output in 4-bit or 1-bit units

• P60 is also used as the serial input SI1

pin.

• P61 is also used as the serial output

I/O

SO1 pin.

• P62 is also used as the serial clock

SCK1 pin.

• P63 is also used for the event count

input to timer 1.

Dedicated output ports P80 to P83

• Output in 4-bit or 1-bit units

• The contents of the output latch are

input using input instructions.

O

• P80 is a buffer input or a zero-cross

buffer input and P81 is a buffer input

(options).

• Pch: Pull-up MOS type

• Nch: Intermediate sink current

type

• Pch: MOS type

• Nch: Intermediate sink current

type

• Nch: +7-V handling when OD

option selected (P61 and P63

only)

• Pch: CMOS type

• Nch: Intermediate sink current

type

• Pull-up MOS or

Nch OD output

• Output level on

reset

• CMOS or Nch OD

output

• CMOS or Pch OD

output

• Output level at

reset

• Buffer circuit

• Zero-cross

detector buffer

circuit

State after a Standby mode

reset operation

Hold mode:

Output off

High or low

(option)

H

High or low

Buffered I/O

(option)

Halt mode:

Output

retained

Hold mode:

Output off

Halt mode:

Output

retained

Hold mode:

Port output

off, buffer

output off

Halt mode:

Port output

retained,

buffer output

continues

with the

buffer

resistor off.

PC0

PC1

PC2/INV2I

PC3/INV2O

PD0/AN1/

INV3I

PD1/AN2/

INV3O

PD2/AN3

INV4I

PD3/AN4/

INV4O

PE0/XT1

PE1/XT2

I/O ports PC0 to PC3

• Output in 4-bit or 1-bit units

I/O

• Dedicated inverter circuits (option)

Dedicated input ports PD0 to PD3

• Can be switched in software to function

I

as 16-value analog inputs.

• Dedicated inverter circuits (option)

Dedicated input ports and sub-oscillator

I

connections

• Pch: CMOS type

• Nch: Intermediate sink current

type

• Inverter circuits can be

selected as options.

• Pch: CMOS type

• Nch: Intermediate sink current

type

• CMOS or Nch OD

output

• Inverter circuit

Inverter circuit

Sub-oscillator/port

PE selection

H

Normal

input or

inverter I/O

(option)

Selected as

an option

Hold mode:

Port output

off, inverter

output off

Halt mode:

Port output

retained,

inverter

output

continues.

Inverter:

• Hold mode:

Output off

• Halt mode:

Output

continues

Suboscillator:

Hold mode:

Oscillator

stopped

Halt mode:

Oscillator

operates

Continued on next page.

No. 5485-6/26

Continued from preceding page.

LC665304A, 665306A, 665308A, 665312A, 665316A

Pin I/O Overview Output driver type Options

OSC1

OSC2

RES

TEST

V

DD

V

SS

Note: Pull-up MOS type: The output circuit includes a MOS transistor that pulls the pin up to VDD.

CMOS output: Complementary output.

OD output: Open-drain output.

System clock oscillator connections

I

When an external clock is used, leave

OSC2 open and connect the clock signal

O

to OSC1.

System reset input

When the P33/HOLD pin is at the high

I

level, a low level input to the RES pin will

initialize the CPU.

CPU test pin

I

This pin must be connected to V

during normal operation.

Power supply pins

SS

Ceramic oscillator

or external clock

selection

State after a Standby mode

reset operation

Selected as

an option

User Options

1. Port 0, 1, 4, 5, and 8 output level at reset option

The output levels at reset for I/O ports 0, 1, 4, 5, and 8, in independent 4-bit groups, can be selected from the

following two options.

Hold mode:

Oscillator

stopped

Halt mode:

Oscillator

operates

Option Conditions and notes

1. Output high at reset The four bits of ports 0, 1, 4, 5, or 8 are set in a group

2. Output low at reset The four bits of ports 0, 1, 4, 5, or 8 are set in a group

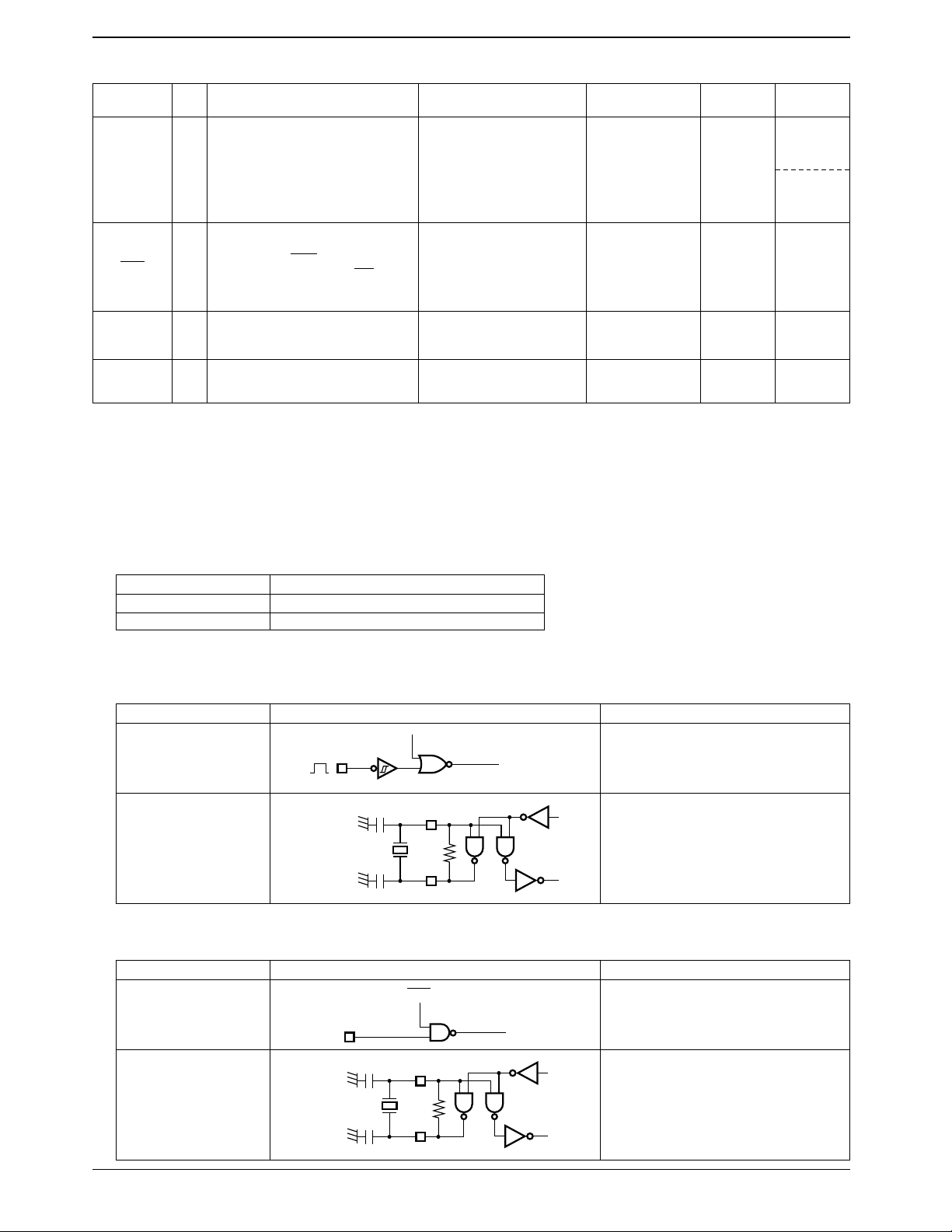

2. Oscillator circuit options

• Main clock

Option Circuit Conditions and notes

1. External clock

2. Ceramic oscillator

Note: There is no RC oscillator option.

OSC1

C1

Ceramic oscillator

C2

OSC1

OSC2

• Sub-clock

Option Circuit Conditions and notes

DSB

1. Ports PE0 and PE1

The input has Schmitt characteristics

Input data

2 Sub-oscillator

(crystal oscillator)

C1

Crystal oscillator

C2

XT1

XT2

No. 5485-7/26

LC665304A, 665306A, 665308A, 665312A, 665316A

3. Watchdog timer option

A runaway detection function (watchdog timer) can be selected as an option.

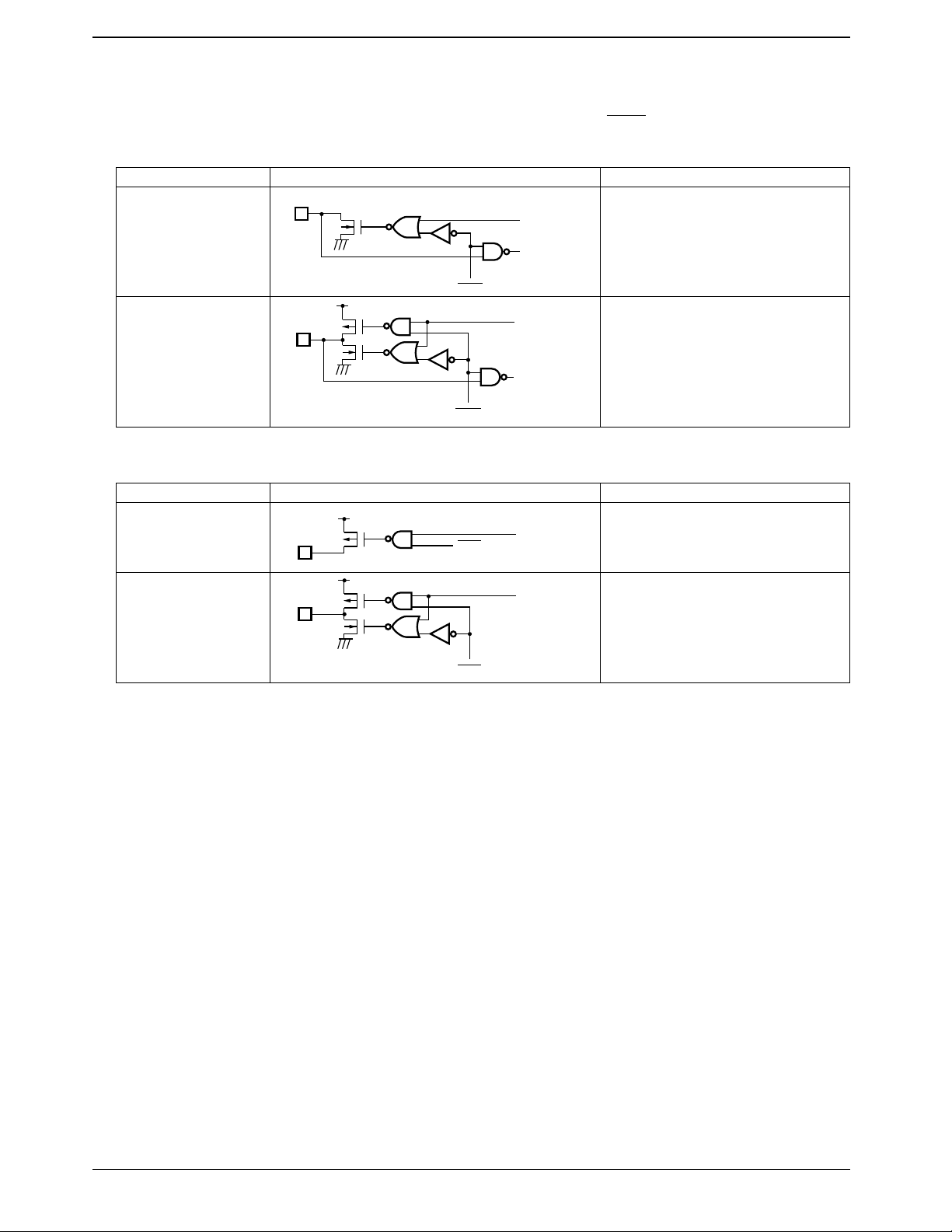

4. Port output type options

• The output type of each bit (pin) in ports P0, P1, P2, P3 (except for the P33/HOLD pin), P4, P5, P6, and PC can be

selected individually from the following two options.

Option Circuit Conditions and notes

Output data

1. Open-drain output

Input data

DSB

Output data

2. Output with built-in pull-up

resistor

Input data

DSB

• One of the following two options can be selected for P8, in bit units.

Option Circuit Conditions and notes

1. Open-drain output

2. Output with built-in pulldown resistor

(CMOS output)

DSB

Output data

Output data

The port P2, P3, P5, and P6 inputs have Schmitt

characteristics.

The port P2, P3, P5, and P6 inputs have Schmitt

characteristics.

The CMOS outputs (ports P2, P3, P6, and PC)

and the pull-up MOS outputs (P0, P1, P4, and

P5) are distinguished by the drive capacity of the

p-channel transistor.

DSB

No. 5485-8/26

Loading...

Loading...