Page 1

现货库存、技术资料、百科信息、热点资讯,精彩尽在鼎好!

S3C72K8/P72K8 PRODUCT OVERVIEW

1 PRODUCT OVERVIEW

OVERVIEW

The S3C72K8 singl-chip CMOS microcontroller has been designed for high performance using Samsung's

newest 4-bit CPU core, SAM48 (Samsung Arrageable Microcontrollers). With a two-channel comparator, up-to320-dot LCD direct drive capability, 8-bit timer/counter, watchdog timer and serial I/O, the S3C72K8 offers an

excellent design solution for a wide variety of applications which require LCD functions.

Up to 27 pins of the 80-pin QFP package can be dedicated to I/O. Seven vectored interrupts provide fast

response to internal and external events. In addition, the S3C72K8's advanced CMOS technology provides for

low power consumption and a wide operating voltage range.

OTP

The S3C72K8 microcontroller is also available is OTP (one time programmable) version, S3P72K8.

S3P72K8 microcontroller has an one-chop 8 Kbyte one time programmable EPROM instead of masked ROM.

The S3P72K8 is comparable to S3C72K8, both in function and in pin configuration.

1-1

Page 2

PRODUCT OVERVIEW S3C72K8/P72K8

FEATURES

Memory

— 8 K × 8-bit RAM

— 1,024 × 4-bit ROM

27 I/O Pins

— Input only: 4 pins

— I/O: 15 pins

— Output: maximum 8 pins for 1-bit level output

(sharing with segment driver outputs)

Comparator

— Two channel mode: internal reference

(4-bit resolution)

— One channel mode: external reference

LCD Controller/Driver

— 40 segments and 8 common terminals

— 3, 4 and 8 common selectable

— Internal resistor circuit for LCD bias

— All dot can be switched on/off

8-Bit Basic Timer

— 4 interval timer functions

— Watchdog timer

8-Bit Timer/Counter

— Programmable 8-bit timer

— External event counter

— Arbitrary clock frequency output

— External clock signal divider

— Serial I/O interface clock generator

8-Bit Serial I/O Interface

— 8-bit transmit/receive mode

Watch Timer

— Timer interval generation:

0.5 s, 3.9 ms at 32,768 Hz

— Four frequency outputs to BUZ pin

— Clock source generation for LCD

Interrupts

— Three internal vectored interrupts:

INTB, INTT0, INTS

— Four external vectored interrupts:

INT0, INT1, INT4, INTK

— Two quasi-interrupts: INT2, INTW

Memory-Mapped I/O Structure

— Data memory bank 15

Two Power-Down Modes

— Idle mode (only CPU clock stops)

— Stop mode (main system oscillation stops)

— Subsystem clock stop mode

Oscillation Sources

— Crystal, ceramic, or External RC for system clock

— Main system clock frequency: 0.4 MHz–6 MHz

— Subsystem clock frequency: 32,768 kHz

— CPU clock divider circuit (by 4, 8, or 64)

Instruction Execution Times

— 0.67 us at 6 MHz (minimum)

— 0.95 µs at 4.19 MHz (minimum)

— 122 µs at 32,768 kHz (minimum)

Operating Temperature

— – 40 °C to 85 °C

— 8-bit receive only mode

— LSB-first or MSB-first transmission selectable

— Internal or external clock source

Bit Sequential Carrier

— Support 16-bit serial data transfer in arbitrary

format

1-2

Operating Voltage Range

— 2.0 V to 5.5 V

Package Type

— 80-pin QFP

Page 3

S3C72K8/P72K8 PRODUCT OVERVIEW

SEG0-SEG31

BLOCK DIAGRAM

IN

OUT

X

X

XT

IN

XT

Clock

OUT

Stack

Pointer

Program

Counter

Program

Status Word

Flags

8 Kbyte

Program

Memory

LCD Driver/

Controller

I/O Port 2

I/O Port 3

I/O Port 4

8-Bit

Timer/

Counter

V

LC1-VLC5

COM0-COM7

P5.0/SEG32-

P5.7/SEG39

P2.0-P2.3

P3.0

P3.1

P3.2/LCDSY

P3.3/CLDCK

P4.0/CLO

P4.1/TCL0

P4.2/TCLO0

Watchdog

Timer

P0.0/SCK/K0

P0.1/SO/K1

P0.2/SI/K2

P0.3/BUZ/K3

P1.0/INT0/CIN0

P1.1/INT1/CIN1

P1.2/INT2

P1.3/INT4

Basic

Timer

Watch

Timer

SIO

I/O Port 0

Comparator

Input Port 1

RESET

Interrupt

Control

Block

Internal

Interrupts

Instruction Decoder

Arithmetic

and

Logic Unit

1024 x 4-Bit

Data Memory

Figure 1-1. S3C72K8 Simplified Block Diagram

1-3

Page 4

PRODUCT OVERVIEW S3C72K8/P72K8

PIN ASSIGNMENTS

SEG32/P5.0

SEG33/P5.1

SEG34/P5.2

SEG35/P5.3

SEG36/P5.4

SEG37/P5.5

SEG22

SEG23

SEG24

SEG25

SEG26

SEG27

SEG28

SEG29

SEG30

SEG31

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

P5.6/SEG38

P5.7/SEG39

VLC1

VLC2

VLC3

VLC4

VLC5

P0.0/SCK/K0

P0.1/SO/K1

P0.2/SI/K2

P0.3/BUZ/K3

VDD

VSS

XOUT

XIN

TEST

XTIN

XTOUT

RESET

P1.0/INT0/CIN0

P1.1/INT1/CIN1

P1.2/INT2

P1.3/INT4

P2.0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

S3C72K8

(80-QFP-1420C)

32

31

30

29

28

27

26

33

34

35

36

37

38

39

40

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

SEG21

SEG20

SEG19

SEG18

SEG17

SEG16

SEG15

SEG14

SEG13

SEG12

SEG11

SEG10

SEG9

SEG8

SEG7

SEG6

SEG5

SEG4

SEG3

SEG2

SEG1

SEG0

COM7

COM6

1-4

COM5

COM4

COM3

COM2

COM1

COM0

TCLO0/P4.2

TCL0/P4.1

CLO/P4.0

LCDCK/P3.3

LCDSY/P3.2

P3.1

P3.0

P2.3

P2.2

P2.1

Figure 1-2. S3C72K8 80-QFP Pin Assignment

Page 5

S3C72K8/P72K8 PRODUCT OVERVIEW

PIN DESCRIPTIONS

Table 1-1. S3C72K8 Pin Descriptions

Pin Name Pin

Type

P0.0

I/O 4-bit I/O port.

P0.1

P0.2

P0.3

1-bit or 4-bit read/write and test is possible.

Individual pins are software configurable as input or

output.

Description Circuit

Type

E–2 8

Pin

Number

9

10

11

Share Pin

K0/SCK

K1/SO

K2/SI

K3/BUZ

Individual pins are software configurable as opendrain or push-pull output.

4-bit pull-up resistors are software assignable; pull-up

resistors are automatically disabled for output pins.

P1.0

P1.1

P1.2

P1.3

I 4-bit input port.

1-bit or 4-bit read and test are possible.

The 1-bit unit pull-up resistors are assigned to input

pins by software.

F–4

F–4

A–3

A–3

20

21

22

23

INT0/CIN0

INT1/CIN1

INT2

INT4

An interrupt is generated by digital input at P1.0,

P1.1.

P2.0–P2.3 I/O Same as port 0 except that 8-bit read/write and test is

E–2 24–27 –

possible.

P3.0

P3.1

P3.2

P3.3

P4.0

I/O Same as port 0 except that port 4 is 3-bit I/O port. E–2 32

P4.1

P4.2

P5.0–P5.7 O Output port for 1-bit data H–11 75–

SCK

I/O Serial I/O interface clock signal E–2 8 P0.0/K0

28

29

30

31

33

34

80,1,2

–

–

LCDSY

LCDCK

CLO

TCL0

TCLO0

SEG32–

SEG39

SO I/O Serial data output E–2 9 P0.1/K1

SI I/O Serial data input E–2 10 P0.2/K2

BUZ I/O 2 KHz, 4 KHz, 8 KHz or 16 KHz frequency output at

E–2 11 P0.3/K3

the watch timer clock frequency of 32.768 kHz.

K0–K3 I/O External interrupt. The triggering edge is selectable. E–2 8–11 P0.0–P0.3

INT0

INT1

INT2 I Quasi-interrupt with detection of rising or falling

I External interrupts. The triggering edge for INT0 and

INT1 is selectable.

F–4 20

21

P1.0/CIN0

P1.1/CIN1

A–3 22 P1.2

edges

INT4 I External interrupts with detection of rising and falling

A–3 23 P1.3

edges

1-5

Page 6

PRODUCT OVERVIEW S3C72K8/P72K8

Table 1-1. S3C72K8 Pin Descriptions (Continued)

Pin Name Pin

Type

CIN0

I 2-channel comparator input.

CIN1

CIN0: comparator input or external reference input

Description Circuit

Type

F–4 20

Pin

Number

21

Share Pin

P1.0/INT0

P1.1/INT1

CIN1: comparator input only.

LCDSY I/O LCD synchronization clock output for display

E–2 30 P3.2

expansion

LCDCK I/O LCD clock output for display expansion E–2 31 P3.3

CLO I/O Clock output E–2 32 P4.0

TCL0 I/O External clock input for timer/counter 0 E–2 33 P4.1

TCLO0 I/O Timer/counter 0 clock output E–2 34 P4.2

SEG32–

SEG39

SEG0–

O LCD segment signal output H–11 75–

P5.0–P5.7

80,1,2

O LCD segment signal output H–6 43–74 –

SEG31

COM0–

O LCD common signal output H–6 35–42 –

COM7

V

LC1–VLC5

– LCD power supply. Voltage dividing resistors are

– 3–7 –

assignable by mask option.

X

X

,

IN

OUT

– Crystal, ceramic or RC oscillator pins for system

– 15, 14 –

clock.

XT

IN

XT

OUT

V

DD

V

SS

RESET

,

– Crystal oscillator pins for subsystem clock. – 17, 18 –

– Main power supply – 12 –

– Ground – 13 –

I Chip reset signal input B 19 –

TEST I Chip test signal input (must be connected to VSS) – 16 –

NOTE: Pull-up resistors for all I/O ports are automatically disabled if they are configured to output mode

1-6

Page 7

S3C72K8/P72K8 PRODUCT OVERVIEW

PIN CIRCUIT DIAGRAMS

VDD

P-Channel

In

N-Channel

Figure 1-3. Pin Circuit Type A

VDD

Pull-Up

Resistor

P-Channel

In

Pull-Up

Resistor

Enable

Data

Output

Disable

VDD

Pull-Up

Resistor

In

Schmitt Trigger

Figure 1-5. Pin Circuit Type B

VDD

P-Channel

Out

N-Channel

Schmitt Trigger

Figure 1-4. Pin Circuit Type A-3

Figure 1-6. Pin Circuit Type 7

1-7

Page 8

PRODUCT OVERVIEW S3C72K8/P72K8

VDD

Data

Output

Disable

PNE

Schmitt Trigger

VDD

Figure 1-7. Pin Circuit Type E-2

Pull-up

Resistor

Resistor

Enable

P-CH

I/O

N-CH

VDD

Resistor Enable

Schmitt Trigger

Digital In

EXT-REF

(P1.0 only)

Analog In

Comparator

Digital or Analog Selectable

by Software (P1MOD)

Figure 1-8. Pin Circuit Type F-4

Pull-up

Resistor

I/O

+

-

INT-REF

1-8

Page 9

S3C72K8/P72K8 PRODUCT OVERVIEW

VDD

VLC1

VLC2

SEG/COM Data

Output Disable

VLC3

VLC4

VLC5

Out

Figure 1-9. Pin Circuit Type H-5

1-9

Page 10

PRODUCT OVERVIEW S3C72K8/P72K8

VDD

VLC1

VLC2

SEG/COM

VLC3

VLC4

VLC5

Figure 1-10. Pin Circuit Type H-6

VDD

P-CH

Data

Out

Out

1-10

Output Disable 1

SEG

Output Disable 2

Figure 1-11. Pin Circuit Type H-11

Circuit

Type H-5

N-CH

N-CH

Page 11

S3C72K8/P72K8 ELECTRICAL DATA

15 ELECTRICAL DATA

OVERVIEW

In this section, information on S3C72K8 electrical characteristics is presented as tables and graphics. The

information is arranged in the following order:

Standard Electrical Characteristics

— Absolute maximum ratings

— D.C. electrical characteristics

— Main system clock oscillator characteristics

— Subsystem clock oscillator characteristics

— I/O capacitance

— Comparator electrical characteristics

— A.C. electrical characteristics

— Operating voltage range

Stop Mode Characteristics and Timing Waveforms

— RAM data retention supply voltage in stop mode

— Stop mode release timing when initiated by RESET

— Stop mode release timing when initiated by an interrupt request

Miscellaneous Timing Waveforms

— A.C timing measurement points

— Clock timing measurement at X

— Clock timing measurement at XT

— TCL timing

— Input timing for RESET signal

— Input timing for external interrupts

— Serial data transfer timing

IN

IN

15-1

Page 12

ELECTRICAL DATA S3C72K8/P72K8

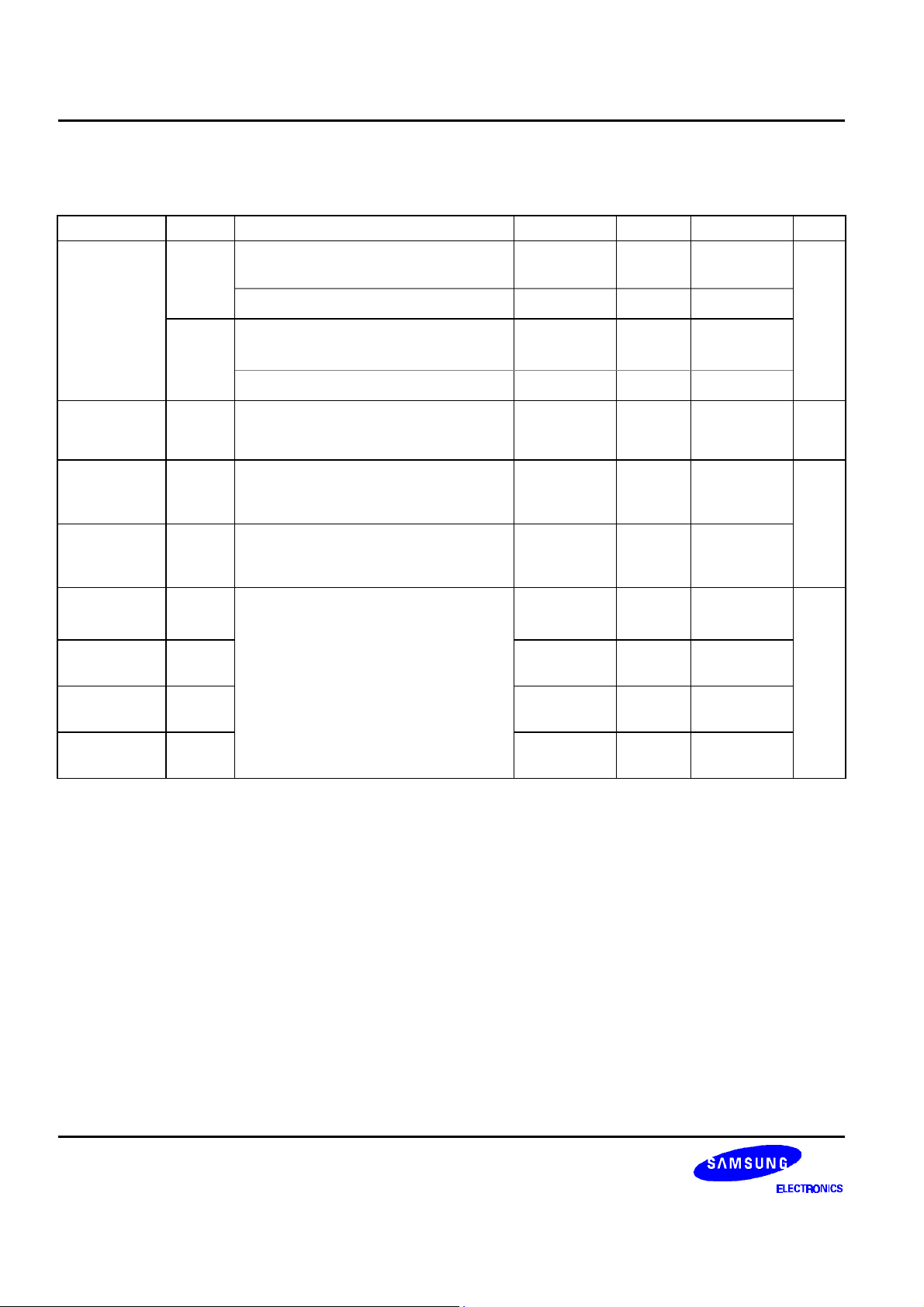

Table 15-1. Absolute Maximum Ratings

(T

= 25 °C)

A

Parameter Symbol Conditions Rating Units

Supply Voltage V

Input Voltage V

Output Voltage V

Output Current High I

DD

I1

O

OH

All I/O pins active – 0.3 to V

One I/O pin active – 15 mA

– – 0.3 to + 6.5 V

+ 0.3 V

DD

– – 0.3 to VDD + 0.3 V

All I/O pins active – 35

Output Current Low I

OL

One I/O pin active + 30 (Peak value) mA

(note)

+ 15

All I/O port, total + 100 (Peak value)

(note)

+ 60

Operating Temperature T

Storage Temperature T

A

stg

– – 40 to + 85 °

– – 65 to + 150 °

C

C

NOTE: The values for Output Current Low ( IOL ) are calculated as Peak Value × Duty .

15-2

Page 13

S3C72K8/P72K8 ELECTRICAL DATA

Table 15-2. D.C. Electrical Characteristics

(T

= – 40 °C to + 85 °C, VDD = 2.0 V to 5.5 V)

A

Parameter Symbol Conditions Min Typ Max Units

Input High

V

Ports 2, 3, P4.0 and P4.2 0.7 V

IH1

DD

– V

DD

V

Voltage

Input Low

V

V

V

Ports 0, 1, P4.1 and RESET

IH2

XIN, X

IH3

Ports 2, 3, P4.0 and P4.2 – – 0.3 V

IL1

OUT

and XT

IN

0.8 V

DD

V

– 0.1 V

DD

V

DD

DD

DD

V

Voltage

Output High

Voltage

V

V

V

IL2

IL3

OH1

Ports 0, 1, P4.1 and RESET

XIN, X

OUT

and XT

IN

VDD = 4.5 V to 5.5 V

IOH = – 3 mA

V

DD

– 2.0 V

– 0.4 – V

DD

0.2 V

0.1

DD

Ports 0, 2, 3 and 4

V

OH2

VDD = 4.5 V to 5.5 V

V

– 2.0 – –

DD

IOH = – 100 µA

Ports 5

Output Low

Voltage

V

OL1

V

= 4.5 V to 5.5 V

DD

IOL = 15 mA

– 0.4 2 V

Input High

Leakage

Current

Input Low

Leakage

Current

Output High

Leakage

Current

Output Low

Leakage

Current

V

I

LIH1

I

LIH2

I

LIL1

I

LIL2

I

LOH

I

LOL

OL2

Ports 0, 2, 3 and 4

VDD = 4.5 V to 5.5 V

IOH = – 100 µA

Ports 5

V

= V

IN

DD

All input pins except those specified

below for I

V

IN

XIN, X

V

= 0 V

IN

All input pins except XIN, X

= V

DD

OUT

LIH2

and XT

IN

, XTIN,

OUT

and RESET

V

= 0 V

IN

XIN, X

V

= V

O

OUT

DD

and XT

IN

All output pins

V

= 0 V

O

All output pins

– – 1

– – 3

20

– – – 3

– 20

– – 3

– – – 3

µA

µA

µA

µA

15-3

Page 14

ELECTRICAL DATA S3C72K8/P72K8

Table 15-2. D.C. Electrical Characteristics (Continued)

(T

= – 40 °C to + 85 °C, VDD = 2.0 V to 5.5 V)

A

Parameter Symbol Conditions Min Typ Max Units

Pull-Up

Resistor

R

V

LI

= 0 V; V

IN

= 5 V ± 10 %

DD

15 40 80

kΩ

Ports 0-4

V

= 3 V ± 10 %

DD

R

L2

V

IN

= 0 V; V

= 5 V ± 10 %

DD

30 80 200

150 220 350

RESET

300 400 800

kΩ

LCD Voltage

R

LCD

V

= 3 V ± 10 %

DD

– 40 60 90

Dividing

Resistor

V

|

-COMi|

DD

Voltage Drop

V

VDD = 2.7 V to 5.5 V

DC

– – 120 mV

– 15 µA per common pin

(i = 0-7)

V

|

-SEGx|

DD

Voltage Drop

V

VDD = 2.7 V to 5.5 V

DS

– – 120

– 15 µA per segment pin

(x = 0-39)

V

Output

LC1

Voltage

V

Output

LC2

V

LC2

V

= 2.0 V to 5.5 V

DD

LCD clock = 0 Hz, V

V

LC3

(1)

LC5

0.8 VDD– 0.2 0.8 V

=

0 V

0.6 VDD– 0.2 0.6 V

0.8 VDD+ 0.2 V

DD

0.6 VDD+ 0.2

DD

Voltage

V

LC3

Output

V

LC4

0.4 VDD– 0.2 0.4 V

0.4 VDD+ 0.2

DD

Voltage

V

LC4

Output

V

LC5

0.2 VDD– 0.2 0.2 V

0.2 VDD+ 0.2

DD

Voltage

15-4

Page 15

S3C72K8/P72K8 ELECTRICAL DATA

Table 15-2. D.C. Electrical Characteristics (Concluded)

(T

= – 40 °C to + 85 °C, VDD = 2.0 V to 5.5 V)

A

Parameter Symbol Conditions Min Typ Max Units

Supply

Current

(1)

I

DD1

(2)

V

DD

Crystal oscillator

= 5 V ± 10%

6.0 MHz

4.19 MHz

– 3.5

2.5

8.0

5.5

mA

C1 = C2 = 22 pF

I

DD2

V

DD

(2)

Idle mode

VDD = 5 V ± 10%

= 3 V ± 10%

6.0 MHz

4.19 MHz

6.0 MHz

4.19 MHz

1.8

1.3

1.3

1.2

4.0

3.0

2.5

1.8

Crystal oscillator

C1 = C2 = 22 pF

I

DD3

(3)

V

= 3 V ± 10%

DD

V

= 3 V ± 10%

DD

6.0 MHz

4.19 MHz

– 15 30

0.5

0.4

1.5

1.0

µΑ

32 kHz crystal oscillator

I

DD4

(3)

Idle mode; V

= 3 V ± 10%

DD

6 15

32 kHz crystal oscillator

I

DD5

Stop mode;

VDD = 5 V ± 10%

SCMOD =

0000B

2.5 5

XTIN = 0V

Stop mode;

0.5 3

VDD = 3 V ± 10%

VDD = 5 V ± 10%

SCMOD =

0.2 3

0100B

VDD = 3 V ± 10%

NOTES:

1. Currents in the following circuits are not included; on-chip pull-up resistors, internal LCD voltage dividing resistors,

output port drive currents, comparator.

2. Data includes power consumption for subsystem clock oscillation.

3. When the system clock control register, SCMOD, is set to 1001B, main system clock oscillation stops and the

subsystem clock is used.

4. Every values in this table is measured when the power control register (PCON) is set to "0011B".

0.1 2

15-5

Page 16

ELECTRICAL DATA S3C72K8/P72K8

Table 15-3. Main System Clock Oscillator Characteristics

(T

= – 40 °C + 85 °C, VDD = 2.0 V to 5.5 V)

A

Oscillator Clock

Parameter Test Condition Min Typ Max Units

Configuration

Ceramic

XIN

XOUT Oscillation frequency

(1)

– 0.4 – 6.0 MHz

Oscillator

C1 C2

Crystal

Oscillator

External

Clock

Stabilization time

XIN

XOUT Oscillation frequency

C1 C2

Stabilization time

XIN XOUT X

input frequency

IN

XIN input high and low

level width (tXH, tXL)

(2)

(2)

Stabilization occurs

– – 4 ms

when VDD is equal to

the minimum

oscillator voltage

range.

(1)

– 0.4 – 6.0 MHz

VDD = 4.5 V to 5.5 V – – 10 ms

VDD = 2.7 V to 4.5 V – – 30

(1)

– 0.4 – 6.0 MHz

– 83.3 – 1250 ns

RC

Oscillator

XIN XOUT

R

Frequency

R = 10 kΩ,

VDD = 5 V

R = 30 kΩ,

– 2 – MHz

– 1 –

VDD = 3 V

NOTES:

1. Oscillation frequency and X

2. Stabilization time is the interval required for oscillating stabilization after a power-on occurs, or when stop mode is

terminated.

15-6

input frequency data are for oscillator characteristics only.

IN

Page 17

S3C72K8/P72K8 ELECTRICAL DATA

Table 15-4. Subsystem Clock Oscillator Characteristics

(T

= – 40 °C + 85 °C, V

A

Oscillator Clock

= 2.0 V to 5.5 V)

DD

Parameter Test Condition Min Typ Max Units

Configuration

Crystal

XTIN

XTOUT Oscillation frequency

(1)

– 32 32.768 35 kHz

Oscillator

C1 C2

Stabilization time

(2)

VDD = 4.5 V to 5.5 V – 1.0 2 s

VDD = 2.0 V to 4.5 V – – 10

External

XTINXT

OUT

XTIN input frequency

(1)

– 32 – 100 kHz

Clock

XTIN input high and low

level width (t

NOTES:

1. Oscillation frequency and XT

2. Stabilization time is the interval required for oscillating stabilization after a power-on occurs.

input frequency data are for oscillator characteristics only.

IN

XTL

, t

XTH

)

– 5 – 15

µs

15-7

Page 18

ELECTRICAL DATA S3C72K8/P72K8

Table 15-5. Input/Output Capacitance

(TA = 25 °C, V

DD

= 0 V )

Parameter Symbol Condition Min Typ Max Units

Input

Capacitance

Output

C

C

OUT

IN

f = 1 MHz; Unmeasured

pins are returned to V

SS

– – 15 pF

– – 15 pF

Capacitance

I/O Capacitance C

IO

– – 15 pF

Table 15-6. Comparator Electrical Characteristics

(T

= – 40 °C + 85 °C, V

A

= 4.0 V to 5.5 V)

DD

Parameter Symbol Condition Min Typ Max Units

Input Voltage Range – – 0 – V

Reference Voltage Range V

Input Voltage Accuracy V

Input Leakage Current I

CIN

REF

CIN

, I

REF

0 V

–

– 3 3

DD

DD

± 150

V

V

mV

µA

15-8

Page 19

S3C72K8/P72K8 ELECTRICAL DATA

Table 15-7. A.C. Electrical Characteristics

(T

= – 40 °C to + 85 °C, V

A

= 2.0 V to 5.5 V)

DD

Parameter Symbol Conditions Min Typ Max Units

Instruction Cycle

(note)

Time

t

CY

V

= 2.7 V to 5.5 V 0.67 – 64

DD

µs

VDD = 2.0 V to 5.5 V 0.95 – 64

With subsystem clock (fxt) 114 122 125

TCL0 Input

f

TI0

, f

TI1

V

= 2.7 V to 5.5 V 0 – 1.5 MHz

DD

Frequency

VDD = 2.0 V to 5.5 V 1

TCL0 Input High,

Low Width

SCK Cycle Time

SCK High, Low

Width

SI Setup Time to

SCK High

SI Hold Time to

SCK High

t

TIH0

t

TIH1

tKH, t

t

KCY

t

SIK

t

KSI

, t

, t

TIL0

TIL1

V

= 2.7 V to 5.5 V 0.48 – –

DD

µs

VDD = 2.0 V to 5.5 V 1.8

V

= 2.7 V to 5.5 V

DD

800 – – ns

External SCK source

Internal SCK source

V

= 2.0 V to 5.5 V

DD

650

3200

External SCK source

Internal SCK source

V

= 2.7 V to 5.5 V

KL

DD

3800

325 – – ns

External SCK source

t

Internal SCK source

VDD = 2.0 V to 5.5 V

KCY

/2 – 50

1600

External SCK source

t

Internal SCK source

V

= 2.7 V to 5.5 V

DD

/2 – 150

KCY

100 – – ns

External SCK source

Internal SCK source

VDD = 2.0 V to 5.5 V

150

150

External SCK source

Internal SCK source

V

= 2.7 V to 5.5 V

DD

500

400 – – ns

External SCK source

Internal SCK source

VDD = 2.0 V to 5.5 V

400

600

External SCK source

Internal SCK source

500

NOTE: Unless otherwise specified, Instruction Cycle Time condition values assume a main system clock ( fx ) source.

15-9

Page 20

ELECTRICAL DATA S3C72K8/P72K8

Table 15-7. A.C. Electrical Characteristics (Continued)

(T

= – 40 °C to + 85 °C, V

A

= 2.0 V to 5.5 V)

DD

Parameter Symbol Conditions Min Typ Max Units

Output Delay for

SCK to SO

t

KSO

V

= 2.7 V to 5.5 V

DD

External SCK source

Internal SCK source

V

= 2.0 V to 5.5 V

DD

– – 300 ns

250

1000

External SCK source

1000

µs

µs

Interrupt Input

High, Low Width

RESET Input Low

t

INTH

t

RSL

, t

Internal SCK source

INT0, INT1, INT2, INT4,

INTL

10 – –

K0–K3

Input 10 – –

Width

CPU Clock

1.5 MHz

1.05 MHz

15.6 kHz

Main Oscillator Frequency

(Divided by 4)

6 MHz

4.2 MHz

1 2 3 4 5 6 7

2.0 V 2.7 V

Supply Voltage (V)

CPU clock = 1/n x oscillator frequency (n = 4, 8 or 64)

Figure 15-1. Standard Operating Voltage Range

15-10

Page 21

S3C72K8/P72K8 ELECTRICAL DATA

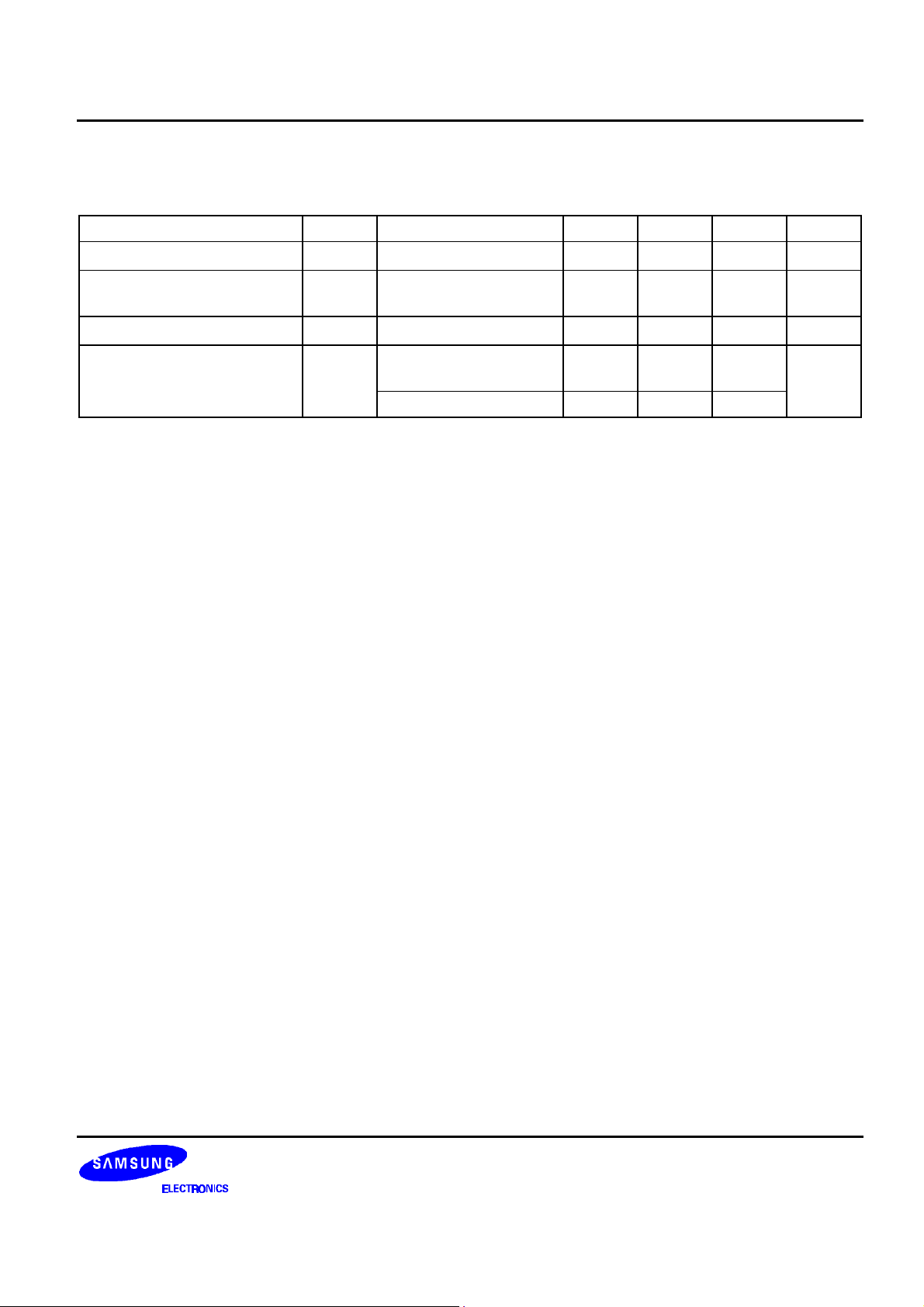

Table 15-8. RAM Data Retention Supply Voltage in Stop Mode

(TA = – 40 °C to + 85 °C)

Parameter Symbol Conditions Min Typ Max Unit

Data retention supply voltage V

Data retention supply current I

DDDR

DDDR

V

DDDR

– 2.0 – 5.5 V

= 2.0 V – 0.1 10

µA

Release signal set time t

Oscillator stabilization wait

(1)

time

SREL

t

WAIT

Released by RESET

Released by interrupt –

NOTES:

1. During oscillator stabilization wait time, all CPU operations must be stopped to avoid instability during oscillator

start-up.

2. Use the basic timer mode register (BMOD) interval timer to delay execution of CPU instructions during the wait time.

– 0 – –

–

17

2

/ fx

(2)

µs

– ms

–

15-11

Page 22

ELECTRICAL DATA S3C72K8/P72K8

TIMING WAVEFORMS

Internal RESET

Operation

~

~

Stop Mode

Idle Mode

VDD

RESET

VDD

~

~

Execution of

STOP Instrction

Data Retention Mode

VDDDR

tWAIT

tSREL

Figure 15-2. Stop Mode Release Timing When Initiated By RESETRESET

Idle Mode

~

~

~

~

Execution of

STOP Instrction

Stop Mode

Data Retention Mode

VDDDR

tSREL

Normal Mode

Normal Mode

15-12

tWAIT

Power-down Mode Terminating Signal

(Interrupt Request)

Figure 15-3. Stop Mode Release Timing When Initiated By Interrupt Request

Page 23

S3C72K8/P72K8 ELECTRICAL DATA

0.8 VDD

Measurement

Points

0.2 VDD

0.8 VDD

0.2 VDD

Figure 15-4. A.C. Timing Measurement Points (Except for XIN and XTIN)

1/fx

tXHtXL

XIN

Figure 15-5. Clock Timing Measurement at X

IN

VDD - 0.1 V

0.1 V

XTIN

1/fxt

tXTHtXTL

Figure 15-6. Clock Timing Measurement at XT

VDD - 0.1 V

0.1 V

IN

15-13

Page 24

ELECTRICAL DATA S3C72K8/P72K8

1/fTI

tTIHtTIL

TCL0

0.8 VDD

0.2 VDD

Figure 15-7. TCL Timing

tRSL

RESET

0.2 VDD

Figure 15-8. Input Timing for RESETRESET Signal

15-14

tINTHtINTL

INT0, 1, 2, 4,

K0 to K3

0.8 VDD

0.2 VDD

Figure 15-9. Input Timing for External Interrupts and Quasi-Interrupts

Page 25

S3C72K8/P72K8 ELECTRICAL DATA

tKCY

SCK

SI

SO

tKSO

tKL

tSIK tKSI

Input Data

Output Data

tKH

Figure 15-10. Serial Data Transfer Timing

0.8 VDD

0.2 VDD

0.8 VDD

0.2 VDD

15-15

Page 26

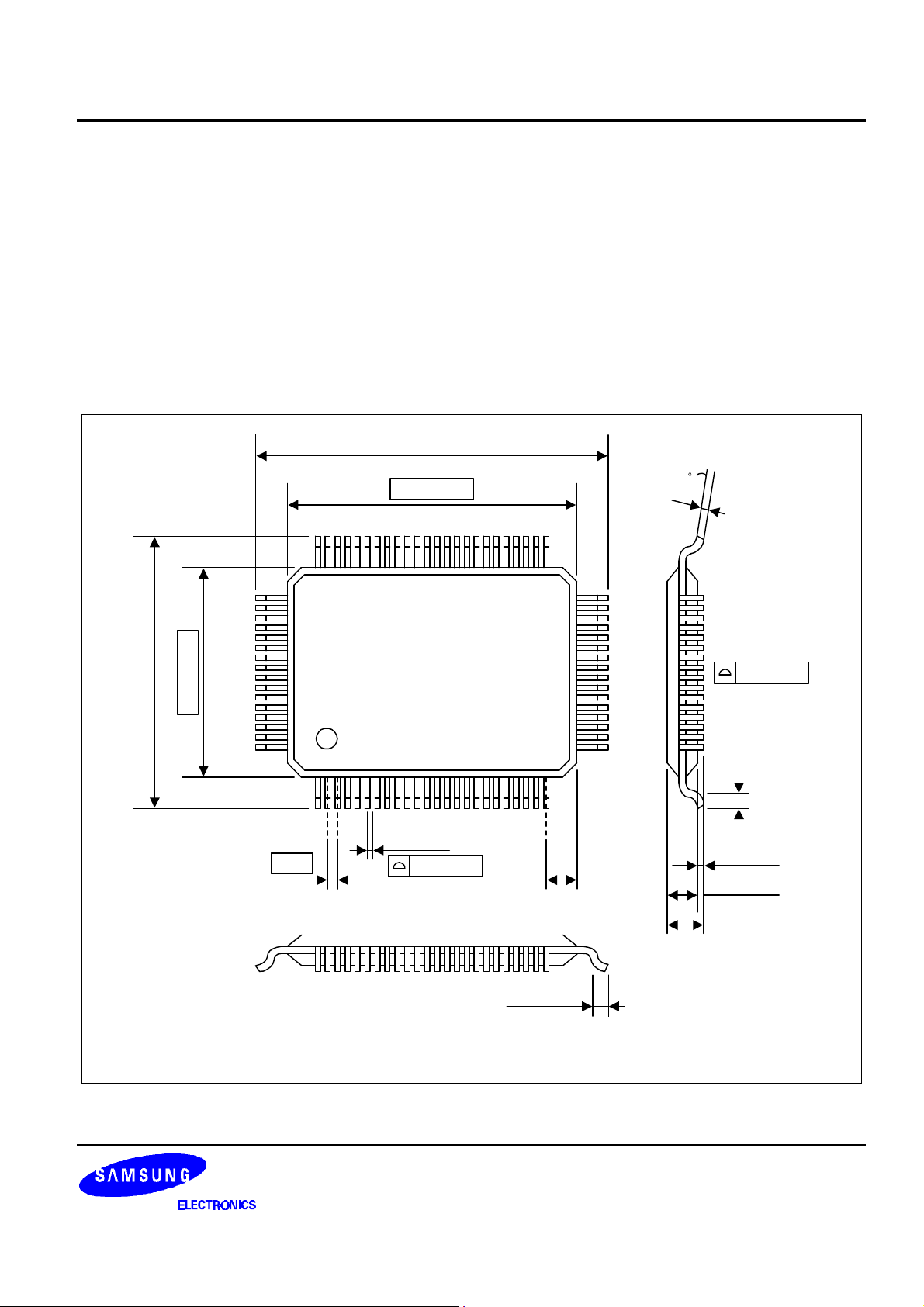

S3C72K8/P72K8 MECHANICAL DATA

16 MECHANICAL DATA

OVERVIEW

The S3C72K8 microcontroller is currently available in a 80-pin QFP package.

23.90 ± 0.30

17.90 ± 0.30

14.00 ± 0.20

#80

0.80

#1

20.00 ± 0.20

80-QFP-1420C

0.35 + 0.10

0.15 MAX

(0.80)

0-8

+ 0.10

- 0.05

0.15

0.10 MAX

0.80 ± 0.20

0.05 MIN

2.65 ± 0.10

3.00 MAX

0.80 ± 0.20

NOTE: Dimensions are in millimeters.

Figure 16-1. 80-QFP-1420C Package Dimensions

16-1

Page 27

S3C72K8/P72K8 S3P72K8 OTP

17 S3P72K8 OTP

OVERVIEW

The S3P72K8 single-chip CMOS microcontroller is the OTP (One Time Programmable) version of the S3C72K8

microcontroller. It has an on-chip OTP ROM instead of masked ROM. The EPROM is accessed by serial data

format.

The S3P72K8 is fully compatible with the S3C72K8, both in function and in pin configuration except ROM size.

Because of its simple programming requirements, the S3P72K8 is ideal for use as an evaluation chip for the

S3C72K8.

17-1

Page 28

S3P72K8 OTP S3C72K8/P72K8

SEG32/P5.0

SEG33/P5.1

SEG34/P5.2

SEG35/P5.3

SEG36/P5.4

SEG37/P5.5

SEG22

SEG23

SEG24

SEG25

SEG26

SEG27

SEG28

SEG29

SEG30

SEG31

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

P5.6/SEG38

P5.7/SEG39

VLC1

VLC2

VLC3

VLC4

VLC5

P0.0/SCK/K0

P0.1/SO/K1

SDAT/P0.2/SI/K2

SCLK/P0.3/BUZ/K3

VDD/VDD

VSS/VSS

XOUT

XIN

VPP/TEST

XTIN

XTOUT

RESETRESET/RESET

P1.0/INT0/CIN0

P1.1/INT1/CIN1

P1.1/INT2

P1.3/INT4

P2.0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

S3P72K8

(80-QFP-1420C)

32

31

30

29

28

27

26

33

34

35

36

37

38

39

40

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

SEG21

SEG20

SEG19

SEG18

SEG17

SEG16

SEG15

SEG14

SEG13

SEG12

SEG11

SEG10

SEG9

SEG8

SEG7

SEG6

SEG5

SEG4

SEG3

SEG2

SEG1

SEG0

COM7

COM6

LCDSY/P3.2

P3.1

P3.0

P2.3

P2.2

P2.1

Figure 17-1. S3P72K8 Pin Assignments (80-QFP Package)

17-2

TCLO0/P4.2

TCL0/P4.1

CLO/P4.0

LCDCK/P3.3

COM1

COM0

COM3

COM2

COM5

COM4

Page 29

S3C72K8/P72K8 S3P72K8 OTP

Table 17-1. Descriptions of Pins Used to Read/Write the EPROM

Main Chip During Programming

Pin Name Pin Name Pin No. I/O Function

P0.2 SDAT 10 I/O Serial data pin. Output port when reading and

input port when writing. Can be assigned as a

Input/push-pull output port.

P0.3 SCLK 11 I Serial clock pin. Input only pin.

TEST V

PP

16 I Power supply pin for EPROM cell writing

(indicates that OTP enters into the writing

mode). When 12.5 V is applied, OTP is in

writing mode and when 5 V is applied, OTP is in

reading mode. (Option)

RESET RESET

VDD/V

SS

VDD/V

SS

19 I Chip Initialization

12/13 I Logic power supply pin. VDD should be tied to +5

V during programming.

Table 17-2. Comparison of S3P72K8 and S3C72K8 Features

Characteristic S3P72K8 S3C72K8

Program Memory 8-Kbyte EPROM 8-Kbyte mask ROM

Operating Voltage (VDD) 2.0 V to 5.5 V 2.0 V to 5.5 V

OTP Programming Mode VDD = 5 V, V

(TEST) = 12.5V

PP

Pin Configuration 80 QFP 80 QFP

EPROM Programmability User Program 1 time Programmed at the factory

OPERATING MODE CHARACTERISTICS

When 12.5 V is supplied to the V

(TEST) pin of the S3P72K8, the EPROM programming mode is entered. The

PP

operating mode (read, write, or read protection) is selected according to the input signals to the pins listed in

Table 17-3 below.

Table 17-3. Operating Mode Selection Criteria

V

DD

V

PP

(TEST)

REG/

MEM

Address

(A15-A0)

R/W Mode

5 V 5 V 0 0000H 1 EPROM read

12.5 V 0 0000H 0 EPROM program

12.5 V 0 0000H 1 EPROM verify

12.5 V 1 0E3FH 0 EPROM read protection

NOTE: "0" means Low level; "1" means High level.

17-3

Page 30

S3P72K8 OTP S3C72K8/P72K8

NOTES

17-4

Loading...

Loading...