Samsung S3CB018, S3FB018 Datasheet

S3CB018/FB018 PRODUCT OVERVIEW

1 PRODUCT OVERVIEW

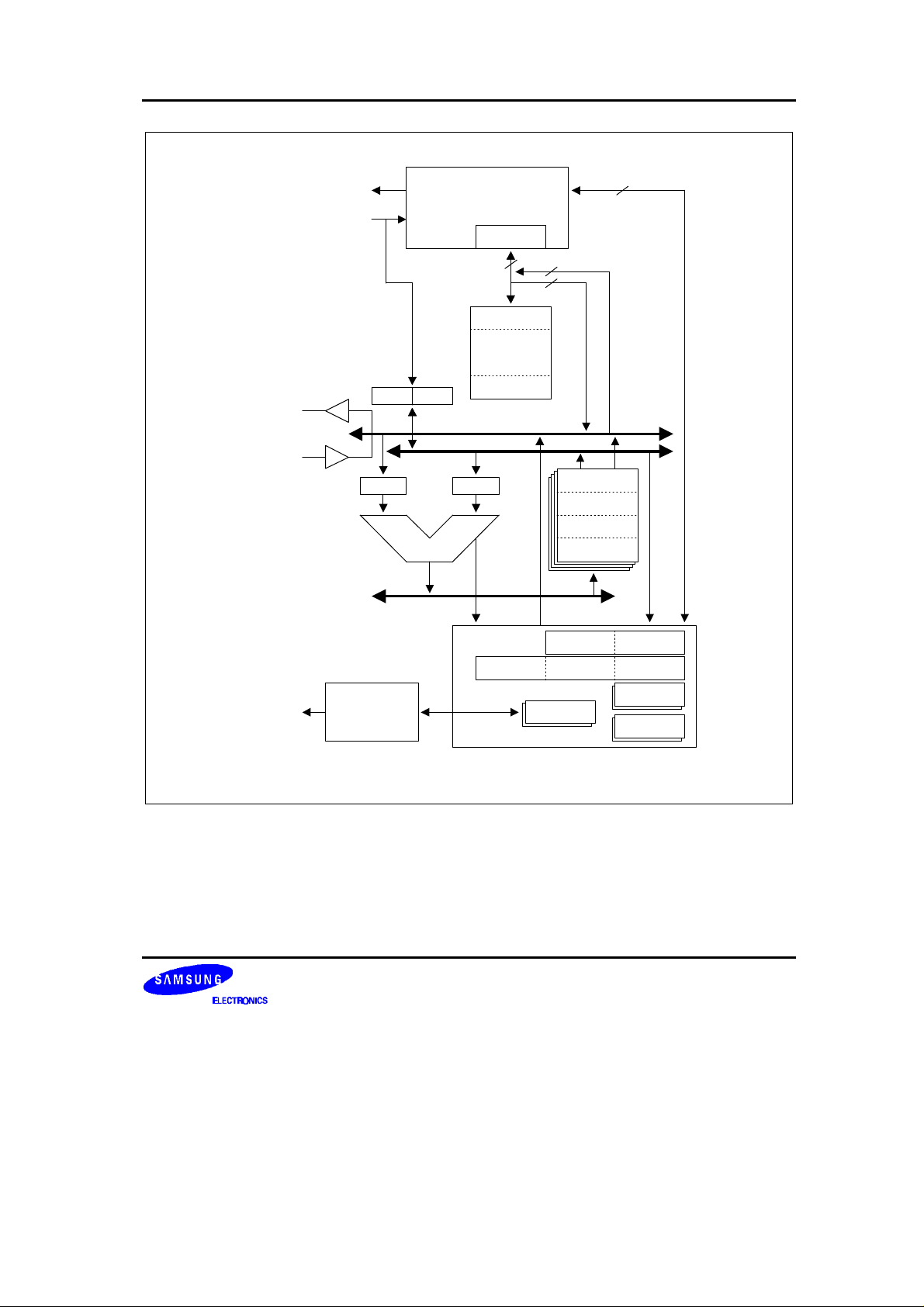

CALMRISC OVERVIEW

The S3CB018/FB018 single-chip CMOS microcontroller is designed for high performance using Samsung’ s

newest 8-bit CPU core, CalmRISC.

CalmRISC is an 8-bit low power RISC microcontroller. Its basic architecture follows Harvard style, that is, it has

separate program memory and data memory. Both instruction and data can be fetched simultaneously without

causing a stall, using separate paths for memory access. Represented below is the top block diagram of the

CalmRISC microcontroller.

1-1

PRODUCT OVERVIEW S3CB018/FB018

S3CB018/FB018 OVERVIEW

FEATURES SUMMARY

CPU

• 8-Bit RISC architecture

Memory

• ROM: 4 Kword (8 K-byte)

• RAM: 3072 (1024+2048) byte

1024 (X-memory) byte

2048 (Y-memory) byte

Stack

• size: maximum 16 (word)-level

26 I/O Pins

• I/O: 26 pins, including 8 S/W open drain pins

8-Bit Basic Timer

• Programmable interval timer

• 8 kinds of clock source

Watchdog Timer

• System reset when 11-bit counter overflows

16-Bit Timer/Counter

• Programmable interval timer

• Two 8-bit timer counter mode and one 16-bit

timer counter mode, selectable by S/W

Watch Timer

• Real time clock or interval time measurement

• Four frequency outputs for buzzer sound

8-Bit Serial I/O Interface

• 8-bit transmit/receive mode

• 8-bit receive mode

• LSB first or MSB first transmission selectable

• Internal and external clock source

16-Bit Serial I/O Interface

• 16-bit transmit/receive mode

• External clock source

Coprocessor

• MAC 816

• 8 x 16, 16 x 16 Multiply and Accumulation

• Arithmetic operation

Two Power-Down Modes

• Idle mode: only CPU clock stop

• Stop mode: selected system clock and CPU

clock stop

Oscillation Sources

• Crystal and Ceramic (0.4-20MHz), RC

Oscillation

• Programmable oscillation source

Instruction Execution Times

• 50ns at 20MHz for 1 cycle instruction

• 100ns at 20MHz for 2 cycle instruction

1-2

S3CB018/FB018 PRODUCT OVERVIEW

DO[7:0]

DI[7:0]

PA[19:0]

PD[15:0]

Program Memory Address

Generation Unit

TBH TBL

ABUS[7:0]

ALUL ALUR

ALU

PC[19:0]

20

HS[0]

Hardware

Stack

HS[15]

BBUS[7:0]

Flag

RBUS

20

8

8

R0

R1

R2

R3

GPR

DA[15:0]

ILHILX ILL

Data Memory

Address

Generation Unit

Bank 0,1

IDH

Figure 1-1. Top Block Diagram of CalmRISC

SR0SR1

IDL0

IDL1

SPR

1-3

PRODUCT OVERVIEW S3CB018/FB018

The CalmRISC building blocks consist of:

— An 8-bit ALU

— 16 general purpose registers (GPR)

— 11 special purpose registers (SPR)

— 16-level hardware stack

— Program memory address generation unit

— Data memory address generation unit

16 GPR’ s are grouped into four banks (Bank0 to Bank3) and each bank has four 8-bit registers (R0, R1, R2, and

R3). SPR’ s, designed for special purposes, include status registers, link registers for branch-link instructions, and

data memory index registers. The data memory address generation unit provides the data memory address

(denoted as DA[15:0] in the top block diagram) for a data memory access instruction. Data memory contents are

accessed through DI[7:0] for read operations and DO[7:0] for write operations. The program memory address

generation unit contains a program counter, PC[19:0], and supplies the program memory address through

PA[19:0] and fetches the corresponding instruction through PD[15:0] as the result of the program memory access.

CalmRISC has a 16-level hardware stack for low power stack operations as well as a temporary storage area.

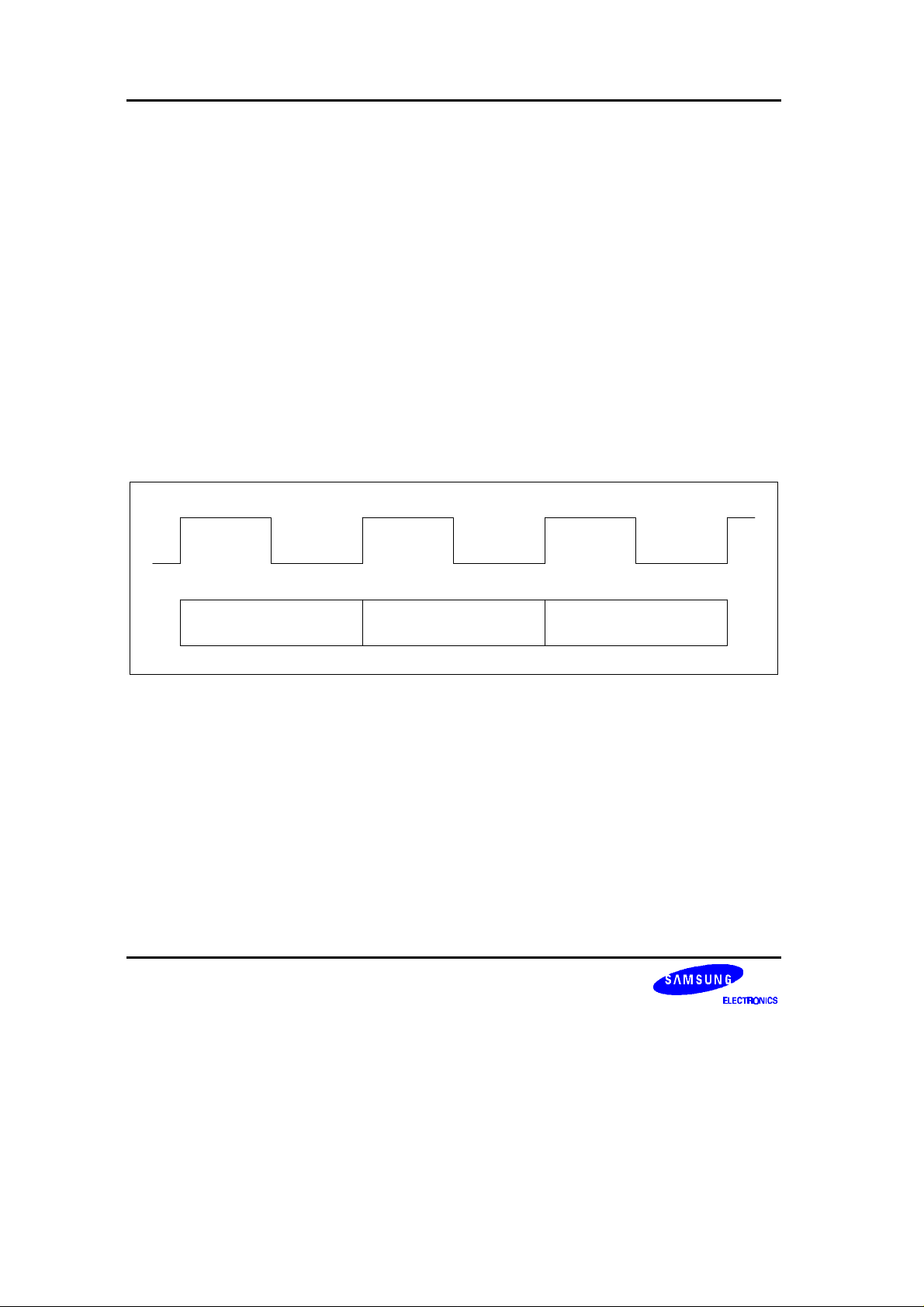

CalmRISC has a 3-stage pipeline as described below:

Instruction Fetch

(IF)

Instruction Decode/

Data Memory Access

(ID/MEM)

Execution/Writeback

(EXE/WB)

Figure 1-2. CalmRISC Pipeline Diagram

As can be seen in the pipeline scheme, CalmRISC adopts a register-memory instruction set. In other words, data

memory where R is a GPR, can be one operand of an ALU instruction as shown below:

The first stage (or cycle) is Instruction Fetch stage (IF for short), where the instruction pointed to by the program

counter, PC[19:0] , is read into the Instruction Register (IR for short). The second stage is Instruction Decode and

Data Memory Access stage (ID/MEM for short), where the fetched instruction (stored in IR) is decoded and data

memory access is performed, if necessary. The final stage is Execute and Write-back stage (EXE/WB), where the

required ALU operation is executed and the result is written back into the destination registers.

Since CalmRISC instructions are pipelined, the next instruction fetch is not postponed until the current instruction

is completely finished, but is performed immediately after the current instruction fetch is done. The pipeline stream

of instructions is illustrated in the following diagram.

1-4

S3CB018/FB018 PRODUCT OVERVIEW

/ 1

ID/MEM

/ 2

EXE/WBIF

IF

ID/MEM

/ 3

IF

/ 4

EXE/WB

ID/MEM

IF IF

EXE/WB

/ 5

ID/MEM

IF

/ 6

EXE/WB

ID/MEM

IF

EXE/WB

ID/MEM

EXE/WB

Figure 1-3. CalmRISC Pipeline Stream Diagram

Most CalmRISC instructions are 1-word instructions, while same branch instructions such as “LCALL” and “LJT”

instructions are 2-word instructions. In Figure 1-3, the instruction, I4, is a long branch instruction and it takes two

clock cycles to fetch the instruction. As indicated in the pipeline stream, the number of clocks per instruction (CPI)

is 1 except for long branches, which take 2 clock cycles per instruction.

1-5

PRODUCT OVERVIEW S3CB018/FB018

P3.0 - P3.1

P2.0 - P2.7

P1.0 - P1.7

P0.0 - P0.7

Port 3

Port 2

Port 1

Port 0

OSC

Control

X-Memory

1024 Byte

MAC

816

WT BT/WDT

CalmRISC

CPU

Y-Memory

2048 Byte

Control Register

128 Byte

(38 Byte)

Figure 1-4. S3CB018/FB018 Block Diagram

SIO

Timer A

Timer B

SIO

SI

S0

SCK

TACLK

TAOUT

TBCLK

TBOUT

ADDA

1-6

S3CB018/FB018 PRODUCT OVERVIEW

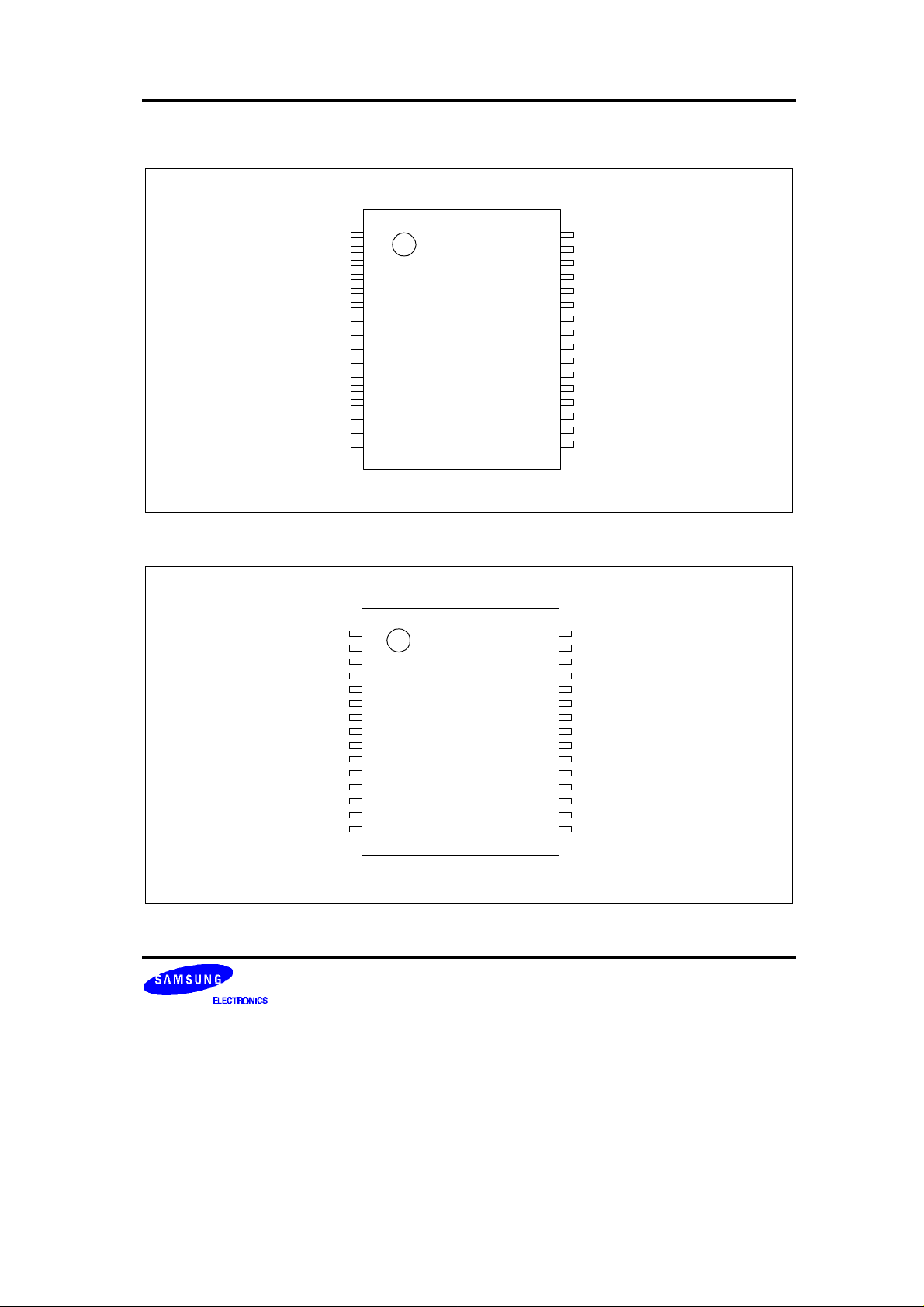

PIN ASSIGNMENTS

VSS

XOUT

X

TEST

SI/P0.0

SO/P0.1

RESET

SCK/P0.2

BUZ/P0.3

CSI/P0.4

CSO/P0.5

CSCK/P0.6

CFSYNC/P0.7

CFSYNC/P0.7

P1.0

P1.1

P1.7

VSS

X

OUT

XIN

TEST

SI/P0.0

SO/P0.1

RESET

SCK/P0.2

BUZ/P0.3

CSI/P0.4

CSO/P0.5

CSCK/P0.6

P1.0

P1.1

1

2

3

IN

4

5

6

7

8

9

10

11

12

13

14

15

16

S3CB018

32-SOP

(Top-View)

Figure 1-5. 32-SOP Pin Assignment

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

S3CB018

30-SDIP

(Top View)

VDD

32

P3.1/SCLK/INT01

31

P3.0/SDAT/INT00

30

P2.7/TACLK

29

P2.6/TBOUT

28

P2.5/TBCLK

27

P2.4/TAOUT

26

P2.3/INT13

25

P2.2/INT12

24

P2.1/INT11

23

P2.0/INT10

22

P1.2

21

P1.3

20

P1.4

19

P1.5

18

P1.6

17

VDD

30

P3.1/SCLK/INT01

29

P3.0/SDAT/INT00

28

P2.7/TACLK

27

P2.6/TBOUT

26

P2.5/TBCLK

25

P2.4/TAOUT

24

P2.3/INT13

23

P2.2/INT12

22

P2.1/INT11

21

P2.0/INT10

20

P1.2

19

P1.3

18

P1.4

17

P1.5

16

Figure 1-6. 30-SDIP Pin Assignment

1-7

PRODUCT OVERVIEW S3CB018/FB018

I/O PIN DESCRIPTION

Table 1-1. S3CB018/FB018 Pin Descriptions (32-SOP)

Pin

Name

Pin

Type

P0.0-P0.7 I/O I/O port with bit programmable pins; Input and output mode are

selectable by software; Software assignable pull-up. P0.4-P0.7

can be used as inputs for comparator input CIN0-CIN3.;

Alternately they can be used as SI, SO, SCK, BUZ, CSI, CSO,

CSCK, CFSYNC.

P1.0-P1.7 O Output port with bit programmable pins; Push-pull output mode

and open-drain output mode are selected by software;

Software assignable pull-up.

P2.0-P2.7 I/O I/O port with bit programmable pins; Input and output mode are

selectable by software; Software assignable pull-up; P2.0-P2.3

can be used as inputs for external interrupts INT10-INT13.

(with noise filter) ; Alternately they can be used as TAOUT,

TACLK or TBOUT, TBCLK.

P3.0-P3.1 I/O I/O port with bit programmable pins; Input or output mode

selected by software; software assignable pull-up; P3.0-P3.1

can be used as inputs for external interrupts INT00-INT01.

(with noise filter and interrupt polarity control)

Pin Description

Circuit

Type

D-2

F-10

Share

Pins

SI, SO, SCK

BUZ, CSI,

CSO, CSCK,

CFSYNC

E-2

D-4

INT10-INT13

D-2

TAOUT

TACLK

TBOUT

TBCLK

D-4 INT00-INT01

Table 1-2. S3CB018/FB018 Pin Descriptions (30-SDIP)

Pin

Name

Pin

Type

Pin Description Circuit

P0.0-P0.7 I/O I/O port with bit programmable pins; Input and output mode are

selectable by software; Software assignable pull-up. P0.4-P0.7

can be used as SI, SO, SCK, BUZ, CSI, CSO, CSCK,

CFSYNC, Alternately.

P1.0-P1.5 O O port with bit programmable pins; Push-pull output mode and

open-drain output mode are selected by software; Software

assignable pull-up.

P2.0-P2.7 I/O I/O port with bit programmable pins; Input and output mode are

selectable by software; Software assignable pull-up; P2.0-P2.3

can be used as inputs for external interrupts INT10-INT13.

(with noise filter); Alternately they can be used as TAOUT,

TACLK or TBOUT, TBCLK.

P3.0-P3.1 I/O I/O port with bit programmable pins; Input or output mode

selected by software; software assignable pull-up; P3.0-P3.1

can be used as inputs for external interrupts INT00-INT01.

(with noise filter and interrupt polarity control)

NOTE: In S3CB018/FB018, the CSI, CSO, CSCK, CFSYNC pins are shared with P0.7-P0.4.

Share

Type

D-2

F-10

Pins

SI, SO, SCK

BUZ, CSI,

CSO, CSCK,

CFSYNC

E-2

D-4

INT10-INT13

D-2

TAOUT

TACLK

TBOUT

TBCLK

D-4 INT00-INT01

1-8

S3CB018/FB018 PRODUCT OVERVIEW

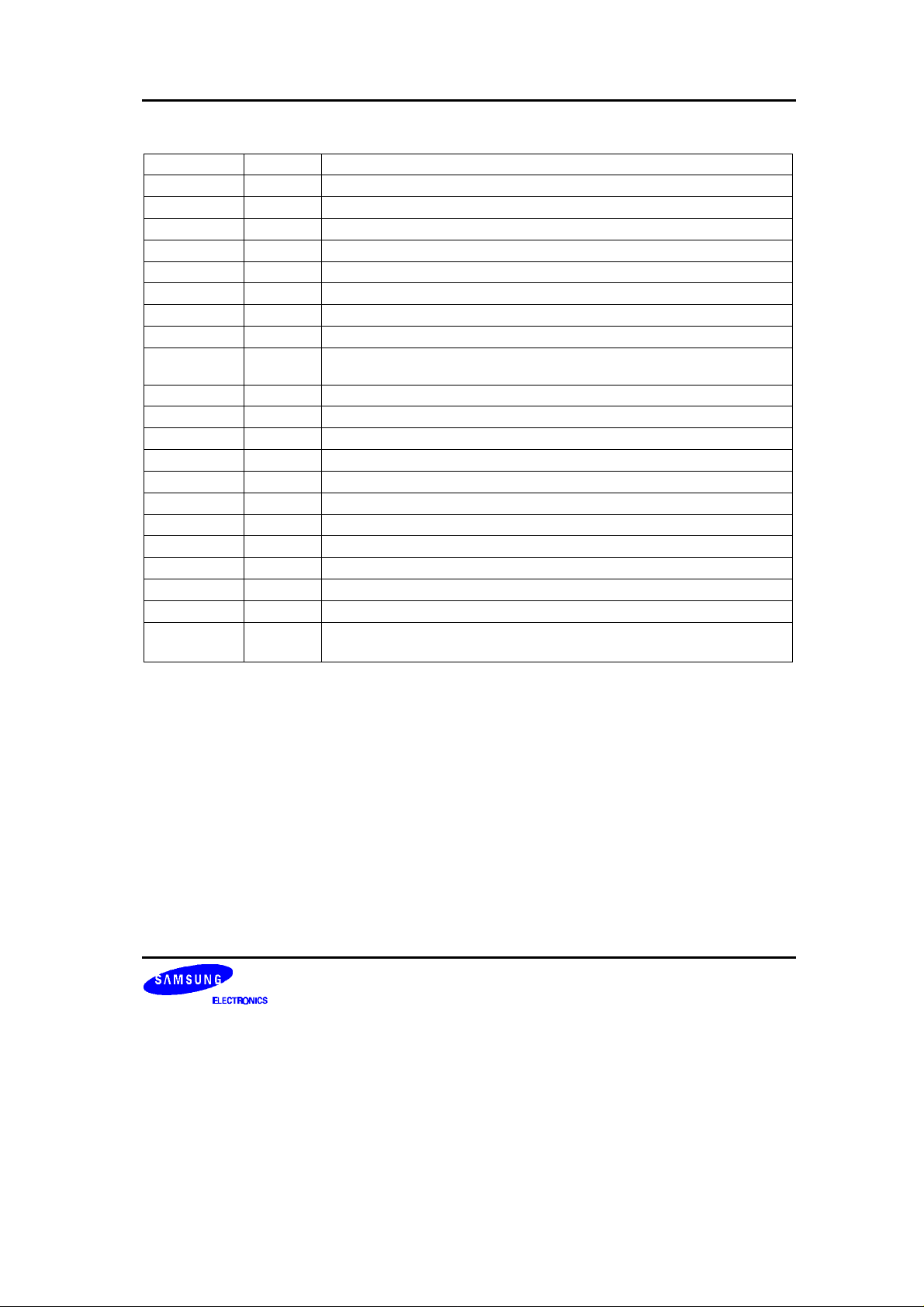

Table 1-3. I/O Pin Description

Pin Name Pin Type Description

CSI I AD/DA Serial Input (from codec)

CSO O AD/DA Serial Output (to codec)

CSCK I AD/DA Serial Clock (from codec)

CFSYNC I AD/DA Sync signal (from codec)

SI I/O Serial data input

SO I/O Serial data output

SCK I/O Serial I/O interface clock signal

BUZ I/O 0.5 kHz, 1 kHz, 2 kHz, or 4 kHz frequency output at 4.19 MHz for buzzer sound

INT10-INT13 I External interrupts. Stop release. Can’ t be masked by S/W individually but

wholly.

TAOUT I/O Timer A interval mode output

TACLK I/O Timer A counter external clock input

TBOUT I/O Timer B interval mode output

TBCLK I/O Timer B counter external clock input

INT00-INT01 I External interrupts. Stop release. Can be masked by S/W individually.

SDAT I Serial data for Programmable memory

SCLK I Serial clock for Programmable memory

VDD – Power supply

VSS – Ground

TEST – Test signal input

RESET I Reset signal

XIN, X

OUT

– Crystal, ceramic and RC oscillator signal for system clock (For external clock

input, use XIN and input XIN's reverse phase to X

OUT

)

1-9

PRODUCT OVERVIEW S3CB018/FB018

PIN ASSIGNMENTS

P0.0

P0.1

P0.2

V

P0.3

P0.4

P0.5

GND

P0.6

P0.7

V

P1.0

P1.1

P1.2

P1.3

GND

P1.4

P1.5

P1.6

P1.7

GND

X

XOUT

V

DDI/VDD

P2.0

P2.1

P2.2

V

P2.3

P2.4

GND

P2.5

P2.6

P2.7

VDD

P3.0

P3.1

GND

TMODE

PIN_RESB

CFSYNC

CSOUT

CSCLK

CSIN

V

DD

156

157

158

159

160

1

2

3

4

DD

5

6

7

8

9

10

11

DD

12

13

14

15

16

17

18

19

20

21

22

IN

23

24

25

26

27

28

DD

29

30

31

32

33

34

35

36

37

38

39

40

45

44

434241

PTMS

PTCK_MCLK

V

PNTRST_STATEINIT

JTAGSEL

DD

/V

DDI

EVENIO

WENIO

OENIO

153

154

155

484746

GND

PTDO_TXD

PTDI_RXD

CSNWIO

CSNBIO

GND

150

151

152

50

49

NPMCS

NPMOE

NPMWE

WENX

OENX

148

149

535251

VDD

RUNST

VDD/VDDI

CSNXH

CSNXL

XD15

144

145

146

147

(Top-View)

57

565554

NP64KW

XDOCNT

DOCNTX

OUTDIS

XD10

XD11

XD12

XD13

XD14

GND

138

139

140

141

142

143

S3EB010

160-QFP

636261

605958

PD12

PD13

VDD/VDDI

PD14

PD15

GND

XD9

137

64

PD11

XD8

136

65

GND

V

DD

135

66

PD10

XD7

134

67

PD9

XD6

133

68

PD8

XD5

132

69

V

DD

/V

DDI

XD4

131

70

PD7

GND

130

71

PD6

XD3

129

72

PD5

XD2

128

73

PD4

XD1

127

GND

XD0

126

PD3

VDD

125

767574

PD2

XDA1

XDA0

123

124

78

77

PD0

PD1

XDA3

XDA2

121

122

80

79

ICLKO

GND

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

XDA4

XDA5

XDA6

GND

XDA7

XDA8

XDA9

VDD/V

DDI

XDA10

XDA11

XDA12

XDA13

GND

TEST

PA0

PA1

PA2

VDD/VDDI

PA3

PA4

PA5

GND

PA6

PA7

V

DD

PA8

PA9

PA10

PA11

GND

PA12

PA13

PA14

PA15

VDD

PA16

PA17

PA18

PA19

BKREQX

1-10

Figure 1-7. S3EB010 Pin Diagram

Loading...

Loading...