Page 1

Samsung Electronics 7-1

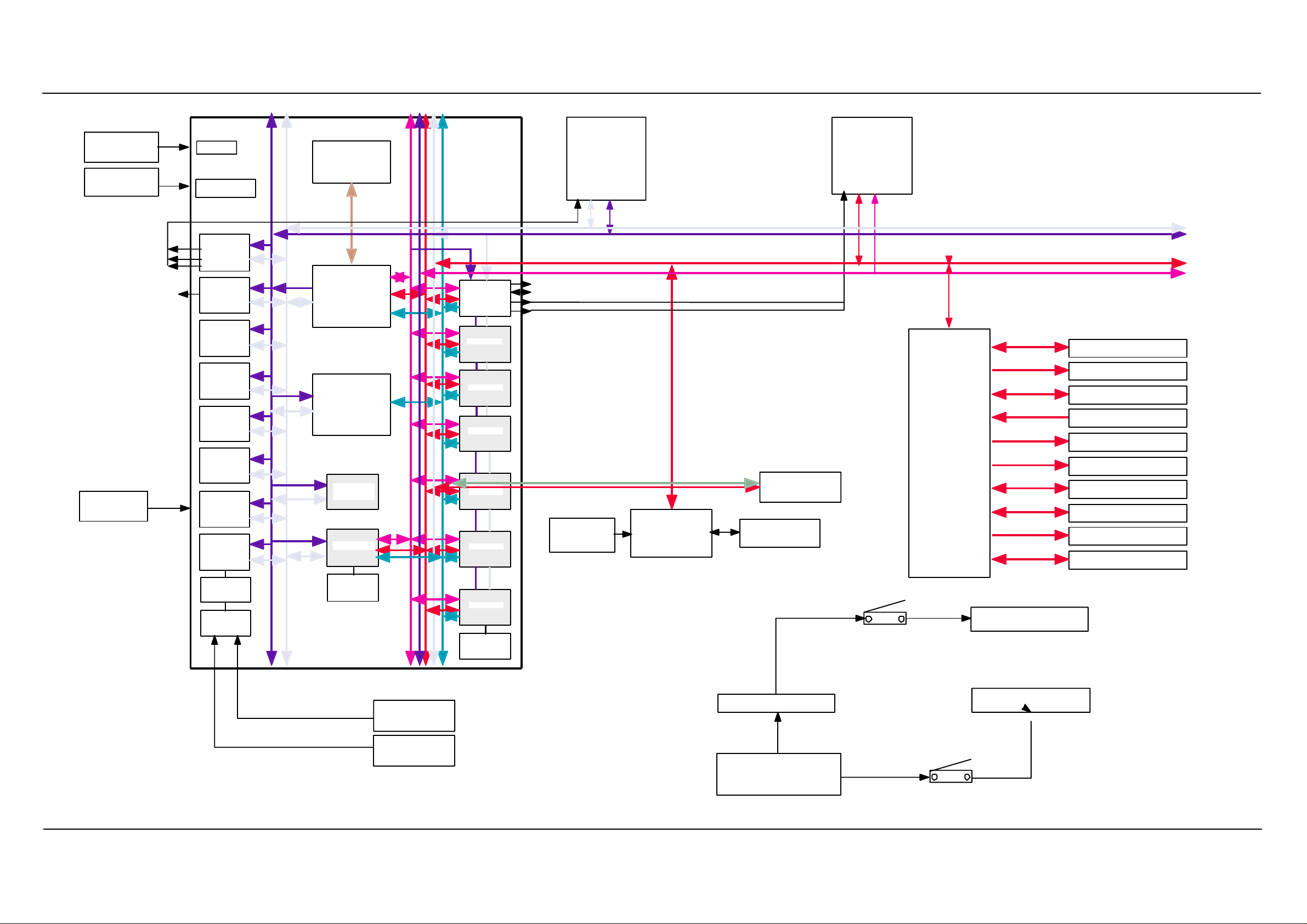

Block Diagram

OSC.

20 MHz

POWER

ON RESET

PARALLEL

INTERFACE

PROGRAM ROM

(FLASHMEMORY)

512K*16b*1ea

DATA RAM

(DRAM)

1M*16b*2ea

USB

INTERFACE

USB

INTERFACE IC

(USBN9602)

OSC.

48 MHz

RAS

CAS

MA

MD

RCS

RD

WR

IOCS

SPGPe

( KS3 2C61200)

PLL

Reset & WDT

Gene ration

ROM/SRAM/

FLASH ROM

Control

(4 Bank)

GPIO

I/O

Contro l

(5 Bank)

Ti me r

(3 CH)

To ne

Generator

Interrupt

Contro l

(4 External)

VIS

Engine

Comm. I/F

CPU Bus

Interfa ce

Block

Systerm Bus

Interface

Block

[Arbiter]

EDO / FPM

D RAM

Control

(4 B an k)

GEU

(2CH)

A/D Bus

C

P

U

D

a

t

a

B

U

S

C

P

U

A

d

d

r

B

U

S

S

y

s

A

d

d

r

B

U

S

S

y

s

C

n

t

l

B

U

S

S

y

s

D

a

t

a

B

U

S

PVC

PPI

HCT

ARM7TDMI

Cache 8KB

ADC

RAM : 512B

UART

(3 C H )

JBIG

LRAM :1296B

CXRAM :256B

HPVC

RA M

512B + 512B

OSC.(Video)

45.03224 MHz

/CS,/RD,/WR

SYSTEM DATA B US

SYSTEM ADDR. BUS

I/O

INTERFACE

74HC245*2EA

74LS273* 3EA

PANEL INTERCACE

MOTOR CONTROL

NV RAM INTERCACE

SENSORS INPUT

SOLENOID CONTROL

FAN/PTL CONTROL

LSU INTERFACE

HVPS CONTROL

FUSER CONTROL

SCF INTERFACE

CPU DATA BUS

CPU A DDR. BUS

THERMISTOR

ADC INPUT

THV READ

ADC INPUT

[COVER OPEN SWITCH]

[LASER DIODE ON/OFF SWITCH]

SM P S

SUPPLY 5V to each ICs

24V

5V

24VS

SUPPLY 24V to

Motor/HVPS/FAN/LSU

Laser Diode Vcc

on LSU

DMAC

7. Block Diagram

Loading...

Loading...