Samsung KS7306 Datasheet

KS7306 DIGITAL CAMERA PROCESSOR

ORDERING INFORMATION

GENERAL DESCRIPTION

100-QFP-1414

KS7306 is a CCD digital signal processor.

The electronic video signal that passed the color

filter array(CFA) pattern of CCD is put to the process

of dual correlation sampling and then converted to

digital video signal by A/D converter.

Taking the digital video signal so processed as an

input, KS7306 performs luminance and chroma

signal process and finally outputs signals encoded to

NTSC/PAL broadcast standards, and generates

detection signals for AE/AF/AWB.

Device Package

KS7306 100-QFP-1414

FEATURES

• Offers 10 bit input digital signal processing.

• Carries built-in 2H line memory.(10bit 1024)

• Performs Y signal processing.

• Performs C signal processing.

• Carries an encorder capable to NTSC/PAL dual form application.

• Carries built-in Y/C 2-channal DA converter.

• Carries built-in AE/AF/AWB detection system.

• Provides micom parallel interface.

• Micom capable to control variable parameters.

• Offers digital effects interfacing

• Suites Hi8/Normal CCD application.

• Suites 470K,520K,570K and 620K CCD controlled EIS system application.

• Supports 16:9 aspect wide TV (full mode) application.

APPLICATIONS

CCD camera ( camcorder, CCTV, digital still camera, etc.).

Operating Temperature

0 ~ 70 °C

VID-97-D004

February 1997

1

KS7306 DIGITAL CAMERA PROCESSOR

VDDPO

VSSPO

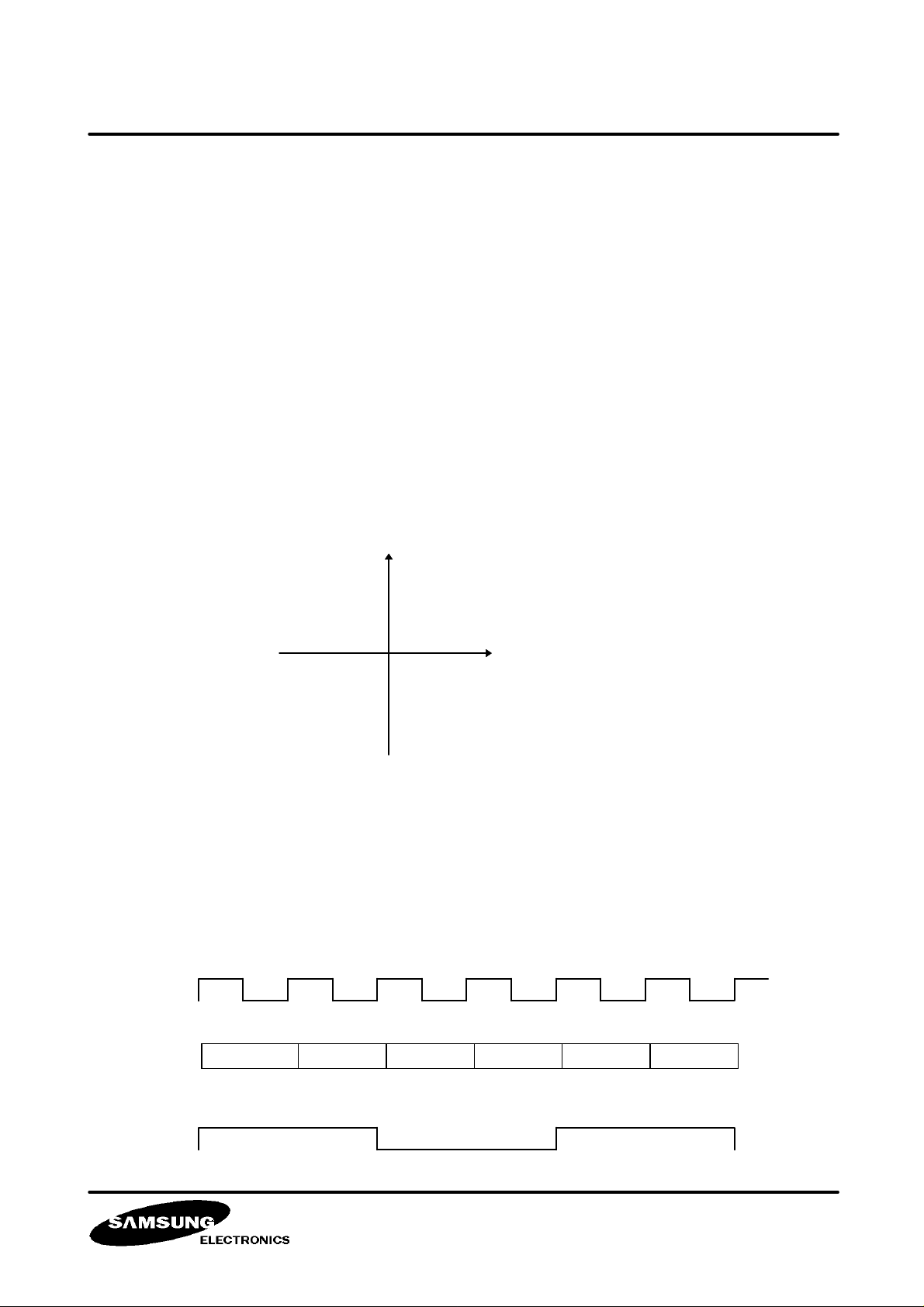

PIN CONFIGURATION

UVIO3

UVIO2

UVIO1

UVIO0

VDDI

UVO3

UVO2

UVO1

UVO0

VSSI

CD9

CD8

CD7

CD6

VDDPO

CD5

CD4

CD3

CD2

VSSPO

CD1

CD0

FSC4

CBLK

CSYNC

YI2

YI1

YI3

YO3

YO1

YO2

YO0

75 74 73 72 71 70 69 68 67 66 65 64 63 62 61 60 59 58 57 56 55 54 53 52 51

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

C-Processor

VSSPO

YO4

YO5

NTSC/PAL Encoder

Line Memory

Pre-Processor

Timing Interface

YO6

YO7

YI0

VDDPO

Y-Processor

TEST

YI4

VSSI

YI5

YI6

YI7

TST2

Interface

Optical

Detector

MICOM

VDDI

DZCSYNCI

D/A

D/A

DZBFII

DZCBLKI

TST1

50

DZCBLKO

49

DZBFO

48

DZCSYNCO

47

UVCK

46

XCK

45

TST4

44

INDIR

43

VSSA

42

VDDA

41

AC

40

VREF

39

IREF

38

BCAP

37

AY

36

VDDA

VSSA

35

34

BFO

33

FSC

32

CSYNCO

31

AFZONE

30

TST3

29

VSYNC

28

HSYNC

27

HCON

26

RSTN

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25

ID

BF

LALT

HD

VDDI

VD

LHLD

PCLK

PBLK

VSSI

NEC

AS

WRN

VSKIP

RDN

MD7

MD6

MD5

MD4

MD3

MD2

MD1

VID-97-D004

February 1997

MD0

2

KS7306 DIGITAL CAMERA PROCESSOR

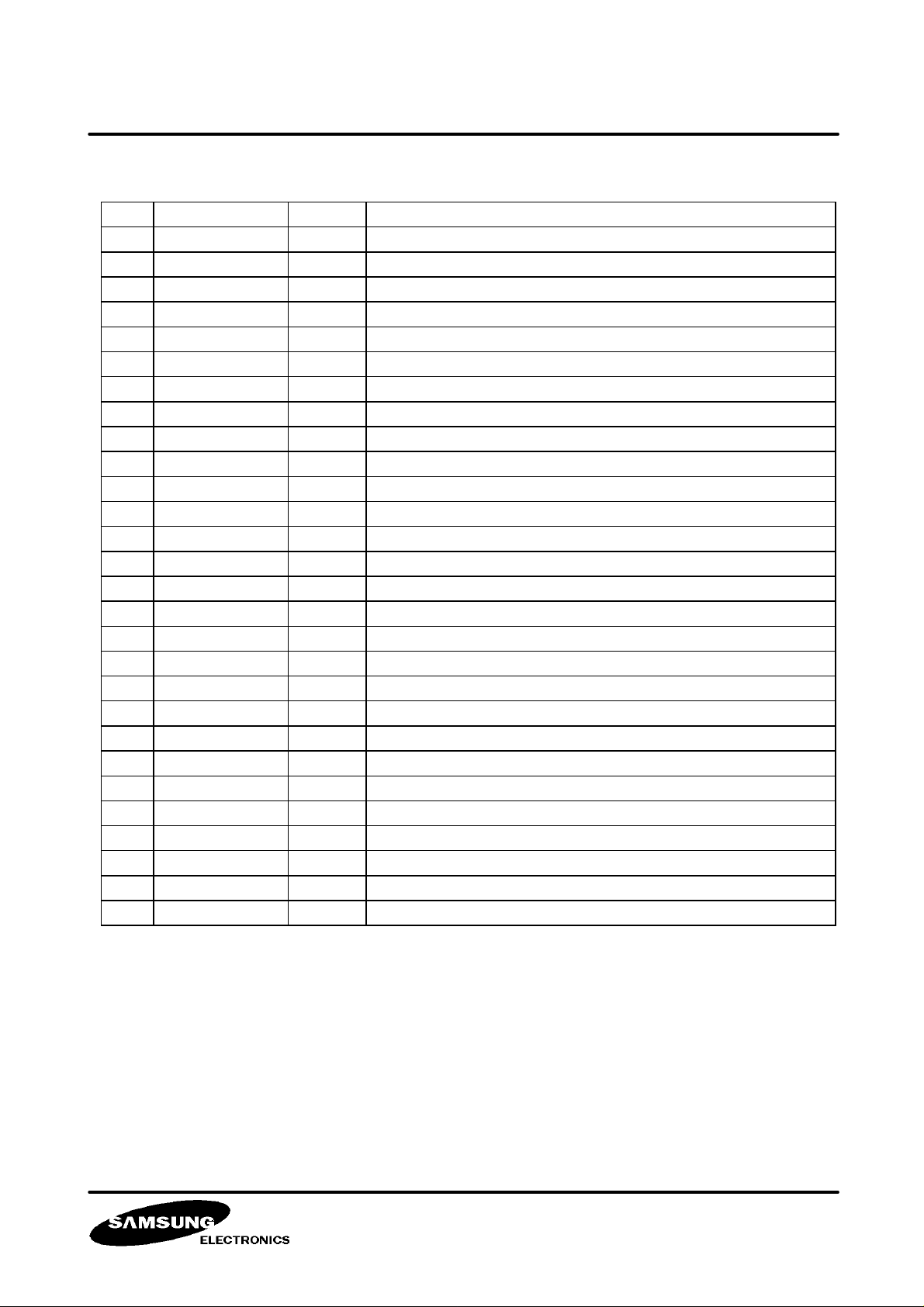

PIN DESCRIPTION

NO. Symbol I/O Description

1 BF I Burst Flag

2 LALT I Line Alternation for PAL System

3 ID I Line Identifer

4 HD I Horizontal Driving Pulse

5 VDDI P Power Supply for Internal Logic

6 VD I Vetical Driving Pulse

7 LHLD I Line Hold Signal

8 PCLK I System Clock

9 PBLK I Pre-Blanking Pulse

10 VSSI G Ground for Internal Logic

11 NEC I Ext. Micom select (NEC/SAM 8*)

12 AS I Address Strobe for Micom I/F

13 VSKIP I Vertical Skip Pulse

14 WRN I Write Enable (Active Low) for Micom I/F

15 VDDPO P Power Supply for Input & Output PAD

16 RDN I Read Enable (Active Low) for Micom I/F

17 MD7 I/O Micom Address & Data Port 7

18 MD6 I/O Micom Address & Data Port 6

19 MD5 I/O Micom Address & Data Port 5

20 VSSPO G Ground for Input & Output Pad

21 MD4 I/O Micom Address & Data Port 4

22 MD3 I/O Micom Address & Data Port 3

23 MD2 I/O Micom Address & Data Port 2

24 MD1 I/O Micom Address & Data Port 1

25 MD0 I/O Micom Address & Data Port 0

26 RSTN I System Reset (Active Low)

27 HCON I Horizontal Sync. Signal (S1,S2 Control)

28 HSYNC O Horizontal Sync. Signal

29 VSYNC O Vertical Sync. Signal

30 TST3 O Test Output 3

31 AFZONE O Auto Focus Window Zone Pulse

32 CSYNCO O Composite Sync. Output (Processor Delay Matched Signal)

33 FSC O Color Subcarrier Signal

34 BFO O Burst Flag Output (Processor Delay Matched Signal)

35 VSSA AG Analog Ground

VID-97-D004

February 1997

3

KS7306 DIGITAL CAMERA PROCESSOR

(Continued)

NO. Symbol I/O Description

36 VDDA AP Analog Power

37 AY O D/A Converted Luminance Signal

38 BCAP I Bypass Capacitor Port for D/A Converter

39 IREF I Current Source Reference Port D/A Converter

40 VREF I Voltage Source Reference Port D/A Converter

41 AC O D/A converted Chroma Signal

42 VDDA AP Analog Power

43 VSSA AG Analog Ground

44 INDIR I Input Mode Select for I/O Bidirectional Pin

45 TST4 O Test Output 4

46 XCK I External Clock for Multimedia PC

47 UVCK O R-Y / B-Y Identifier

48 DZCSYNCO I/O

49 DZBFO I/O

50 DZCBLKO I/O

51 TST1 I/O Test I/O

52 DZCBLKI I/O

53 DZBFI I/O

54 DZCSYNCI I/O

55 VDDI P Power Supply for Internal Logic

56 TST2 I/O Test I/O

57 YI7 I Digital Zoom Processed Luminance Input 7

58 YI6 I Digital Zoom Processed Luminance Input 6

59 YI5 I Digital Zoom Processed Luminance Input 5

60 VSSI G Ground for Internal Logic

61 YI4 I Digital Zoom Processed Luminance Input 4

62 YI3 I Digital Zoom Processed Luminance Input 3

63 YI2 I Digital Zoom Processed Luminance Input 2

64 YI1 I Digital Zoom Processed Luminance Input 1

65 VDDPO P Power Supply for Input / Output Pad

66 YI0 I Digital Zoom Processed Luminance Input 0

67 YO7 O Luminance Output 7 for Digital Zoom

68 YO6 O Luminance Output 6 for Digital Zoom

69 TO5 O Luminance Output 5 for Digital Zoom

70 VSSPO G Ground for Input & Output Pad

71 YO4 O Luminance Output 4 for Digital Zoom

72 YO3 O Luminance Output 3 for Digital Zoom

Delay Matched Composite Sync. Output for Digital Zoom or Test I/O

Delay Matched Burst Flag Output for Digital Zoom or Test I/O

Delay Matched Composite Blank Output for Digital Zoom or Test I/O

Delay Matched Composite Blank input for Digital Zoom or Test I/O

Delay Matched Burst Flag input for Digital Zoom or Test I/O

Delay Matched Composite Sync. input for Digital Zoom or Test I/O

VID-97-D004

February 1997

4

KS7306 DIGITAL CAMERA PROCESSOR

(Continued)

NO. Symbol I/O Description

73 YO2 O Luminance Output 2 for Digital Zoom

74 YO1 O Luminance Output 1 for Digital Zoom

75 YO0 O Luminance Output 0 for Digital Zoom

76 UVIO3 I/O Digital Zoom Processed Chroma Input 3/4:2:2 Chroma Output 7

77 UVIO2 I/O Digital Zoom Processed Chroma Input 2/4:2:2 Chroma Output 6

78 UVIO1 I/O Digital Zoom Processed Chroma Input 1/4:2:2 Chroma Output 5

79 UVIO0 I/O Digital Zoom Processed Chroma Input 0/4:2:2 Chroma Output 4

80 VDDI P Power for Internal Logic

81 UVO3 O Chroma Output 3 for Digital Zoom / 4:2:2 Chroma Output 3

82 UVO2 O Chroma Output 2 for Digital Zoom / 4:2:2 Chroma Output 2

83 UVO1 O Chroma Output 1 for Digital Zoom / 4:2:2 Chroma Output 1

84 UVO0 O Chroma Output 0 for Digital Zoom / 4:2:2 Chroma Output 0

85 VSSI G Ground for Iternal Logic

86 CD9 I CCD Data Input 9 Precessed ADC or FCM

87 CD8 I CCD Data Input 8 Precessed ADC or FCM

88 CD7 I CCD Data Input 7 Precessed ADC or FCM

89 CD6 I CCD Data Input 6 Precessed ADC or FCM

90 VDDPO P Power Supply for Input & Output Pad

91 CD5 I CCD Data Input 5 Precessed ADC or FCM

92 CD4 I CCD Data Input 4 Precessed ADC or FCM

93 CD3 I CCD Data Input 3 Precessed ADC or FCM

94 CD2 I CCD Data Input 2 Precessed ADC or FCM

95 VSSPO G Ground for Input & Output Pad

96 CD1 I CCD Data Input 1 Precessed ADC or FCM

97 CD0 I CCD Data Input 0 Precessed ADC or FCM

98 FSC4 I Color Subcarrier x 4

99 CBLK I Composite Blank Signal

100 CSYNC I Composte Sync. Signal

VID-97-D004

February 1997

5

KS7306 DIGITAL CAMERA PROCESSOR

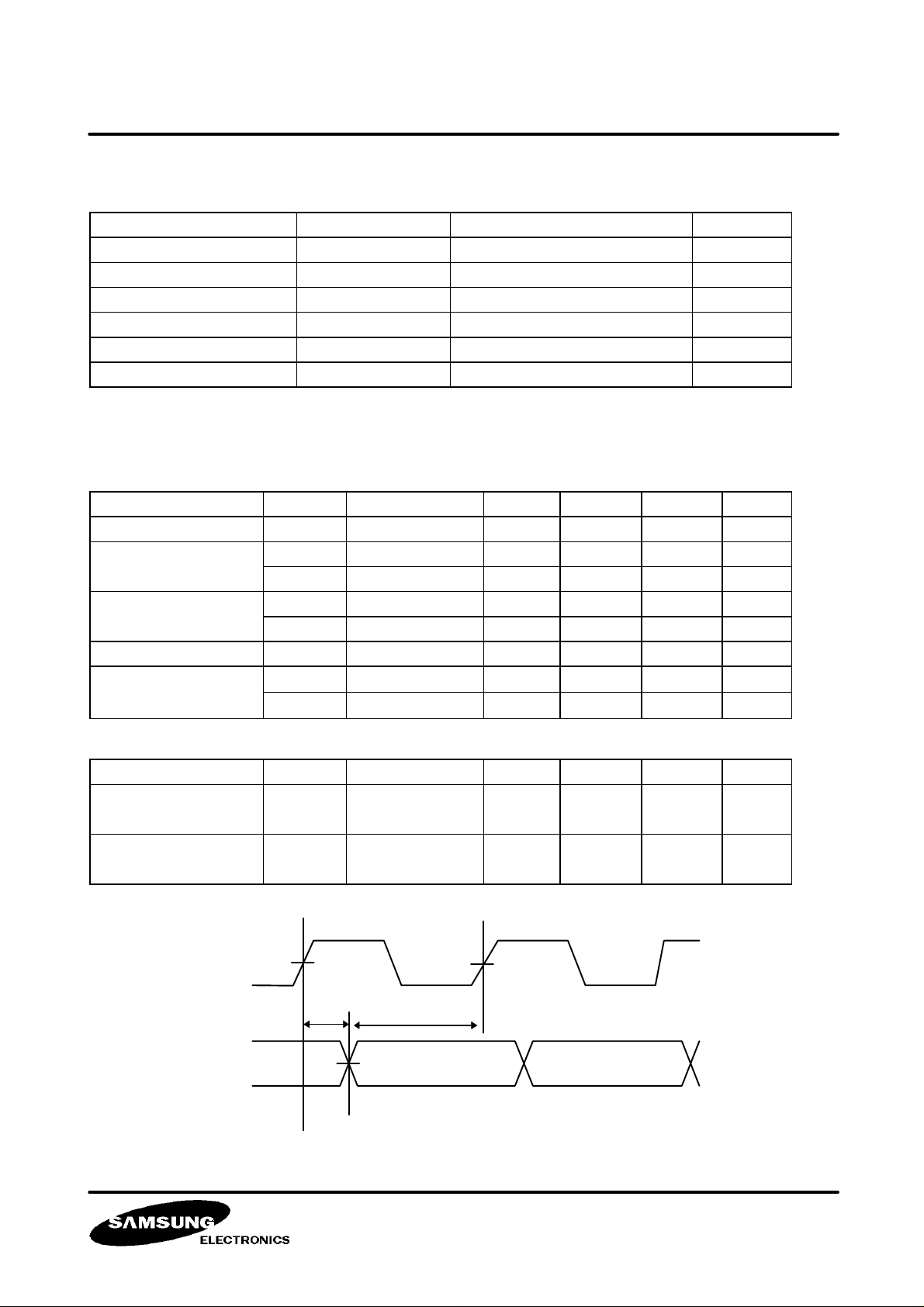

ABSOLUTE MAXIMUM RATINGS

Characteristics Symbol Value Unit

Supply Voltage V

Teminal input Voltage V

Power Dissipation P

DD

I

D

Operating Temperature TORR 0 ~ +70

Storage Temperature T

Latch-Up Current I

STG

LU

ELECTRICAL CHARACTERISTICS

DC

Characteristics Symbol Test Condition Min Typ Max Unit

Operating Voltage V

Input Voltage

output Voltage

Operating Current I

Maximum Input I

Leakage Current I

DD

V

IH

V

IL

V

OH

V

OL

DD

IH

IL

Ta = 25°C 4.75 5.0 5.25 V

Ta = 25°C 0.7V

Ta = 25°C - - 0.3V

IOH = -1mA 2.4 - - V

IOL = 1mA - - 0.4 V

V

= 5V - 140 160 mA

DD

VI = 0~V

VI = 0~V

DD

DD

-0.3 to 7 V

-0.3 to VDD +0.3 V

700 mW

-40 ~ +125

100 mA

DD

- - V

DD

-10 - 10

-10 - 10

°C

°C

V

µA

µA

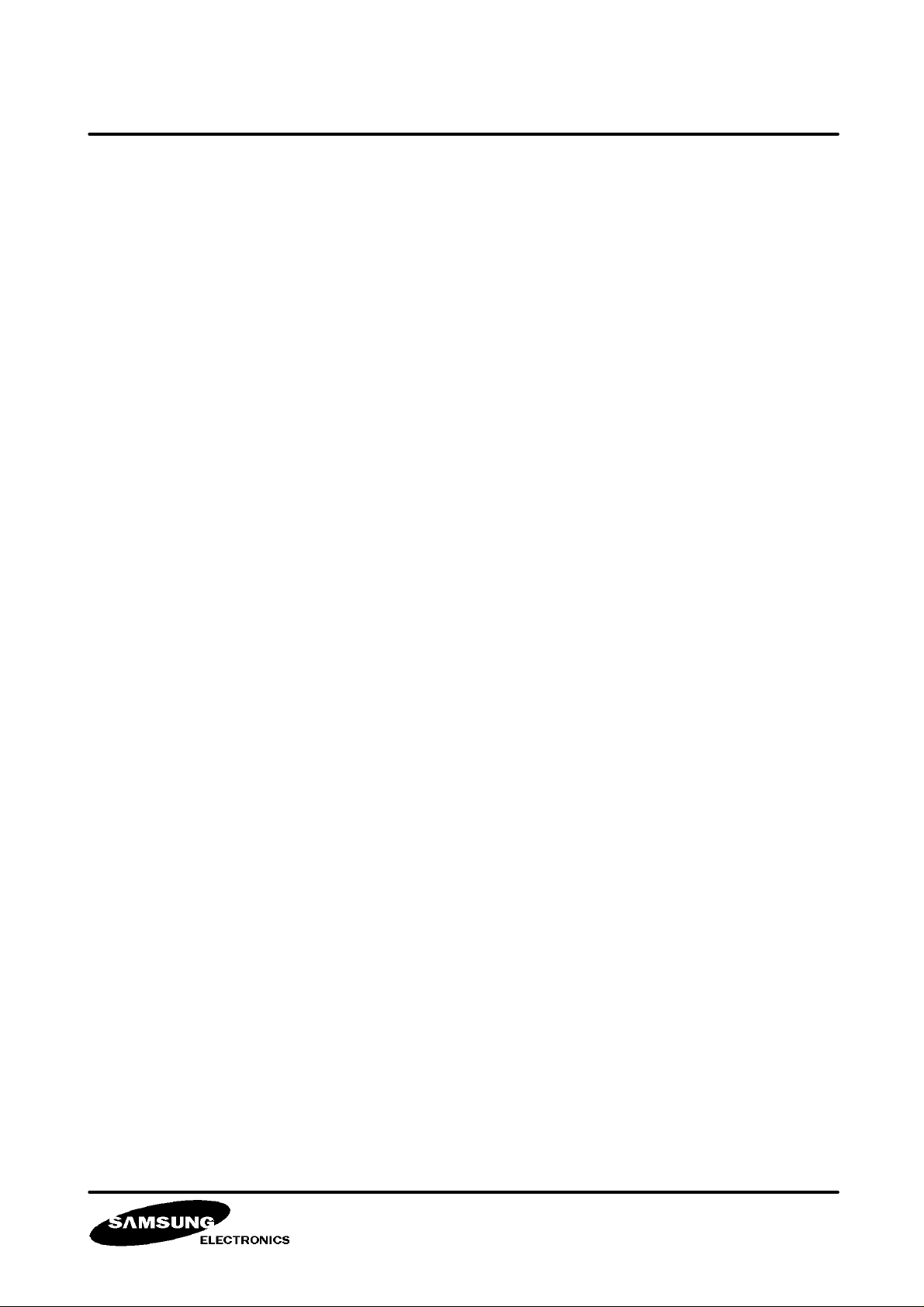

AC

Characteristics Symbol Test Condition Min Typ. Max Unit

Input Data Setup Time

T

SU

VDD = 5±5%,

5

-

-

Ta = 0 ~70°C

Input Data Hold Time

T

HD

VDD = 5±5%,

5

-

50

Ta = 0 ~70°C

PCLK

CD9~0

T

HD

T

SU

nsec

nsec

VID-97-D004

February 1997

6

KS7306 DIGITAL CAMERA PROCESSOR

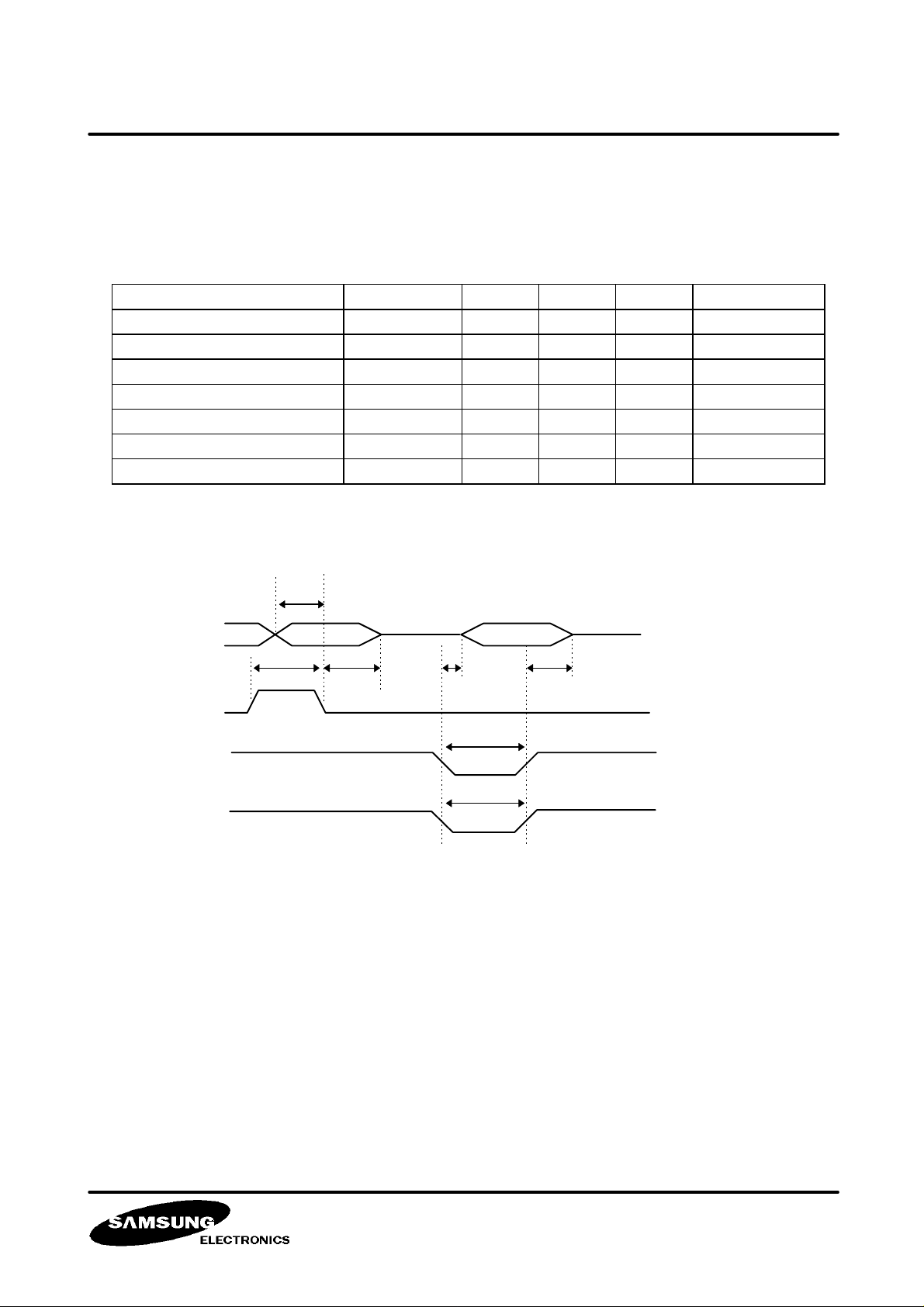

MICOM INTERFACE

1. NEC MICOM INTERFACE

Characteristics Symbol Min Typ Max Unit

Address setup time Tast 15 - - nsec

Address hold time That 35 - - nsec

AS pulse width Tasw 35 - - nsec

RDN pulse width Trdw 400 - - nsec

WRN pulse width Twrw 400 - - nsec

Data delay from RDN,WRN Td - - 100 nsec

Data hold time Tdh 0 - - nsec

MD7~0

AS

RDM

WRN

Tast

ADDR DATA

Tsaw

Taht

Td

Trdw

Twrw

Tdh

READ Mode

( WRN = ″1″)

WRITE Mode

( RDN = ″1″)

VID-97-D004

February 1997

7

KS7306 DIGITAL CAMERA PROCESSOR

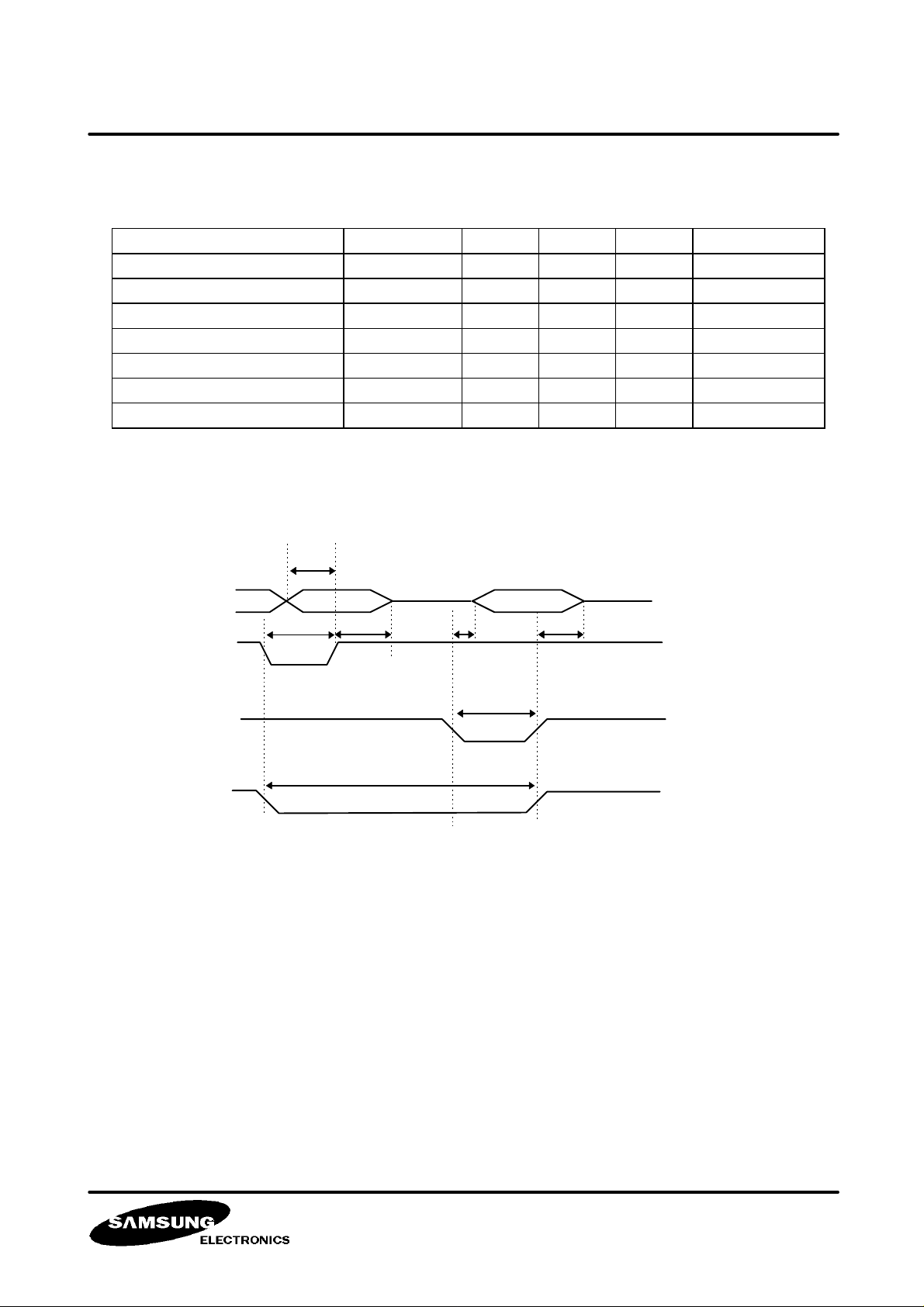

2. SAM8 MICOM INTERFACE

Characteristics Symbol Min Typ Max Unit

Address setup time Tast 15 - - nsec

Address hold time That 35 - - nsec

AS pulse width Tasw 35 - - nsec

RDN pulse width Trdw 400 - - nsec

WRN pulse width Twrw 400 - - nsec

Data delay from RDN,WRN Td - - 100 nsec

Data hold time Tdh 0 - - nsec

Tast

MD7~0

AS

RDM

WRN

ADDR DATA

Tsaw Taht

Twrw

Td Tdh

Trdw

READ Mode

( WRN = ″1″ )

WRITE Mode

( RDN = ″1″ )

VID-97-D004

February 1997

8

KS7306 DIGITAL CAMERA PROCESSOR

SYSTEM DESCRIPTION

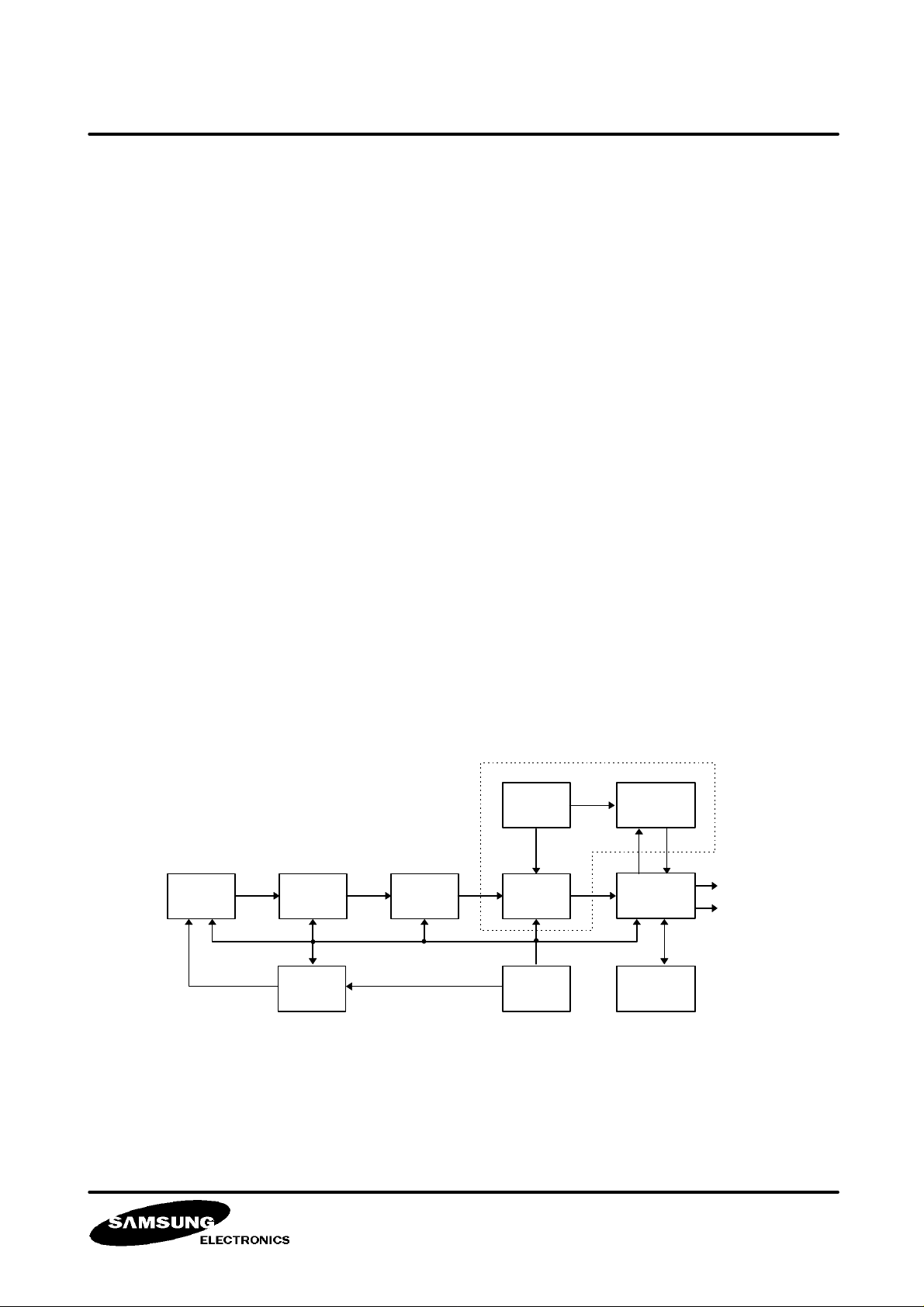

The video data output from CCD go through CDS IC (KA7307) and become quantized by 10 bit ADC.

For hand tremble correction in the CCD controlled gyro sensor method, the quatized video data are fed

to FCM in which effective pixel section of the data gets corrected and extended, then the data are

entered to the signal processor (KS7306) for YC coding so that the data are propely encoded to

conform with NTSC/PAL broadcasting method.

The encoded data is converted to analog signal by the built-in DAC and output Y.C signal finally.

The camera embodies current video status detection function needed for AE/AF/AWB function as an

automatic control provision of the camera system. The function of signal processing and video status

detection is implemented by data communication with the micom through the parallel interfaces to

allow setting of variable parameters, transmisson of detection signals, and reception of control signals

that are necessary in the signal processing. The clock used in IC' s is supplied by a separate IC, the

timining generator (KS7213). For the zooming, the Y,(R-Y)(B-Y) interface to the processing is

provided. And the interface allows interfacing with IC' s for the option of other digital effects.

The timing generator generates time pulse and video syncronizing signal required in all functional

block of the camera system. The clock supports the vertical expansion mode especially required in

CCD controlled gyro sensor and electronic zooming.

Using the clock furnished by the clock generator, the digital zoom (KS7314) performs zooming by

means of vertical interpolation of expanded CCD output and horizontal expansion and interpolation of

the output.

In this camera system, IC' s used for FCM, gyro, microcontroller, and DZ functions respectively are

the ones required only in the system that employs CCD controlled gyro sensor and electronic zooming

for optional funtions while a system pursuing electronic zooming alone requires employment of DZ IC

only to achieve the purpose. The CCDs of 510H (NTSC/PAL) and 760H (NTSC/PAL) allow a range of

system configurations that support 470K, 520K, and 620K (wobble correction CCD) pixels. The figure

below illustrates the camera system.

A/D; Analog to Digital

CCD; Charge Coupled Device

FCM; Frquency Converting Memory

DZ; Digital Camera Process

DCP; Digital Camera Process

CCD

CDS

KA7307

V-Driver

KS7221

A BLOCK DIAGRAM OF CAMERA SYSTEM CONFIGRATION

A/D

10bit

<OPTION>

Gyro

uCOM

FCM

KS7308

TG

KS7213

DZ

KS7314

DCP

KS7306

System

µCOM

Y

C

VID-97-D004

February 1997

9

KS7306 DIGITAL CAMERA PROCESSOR

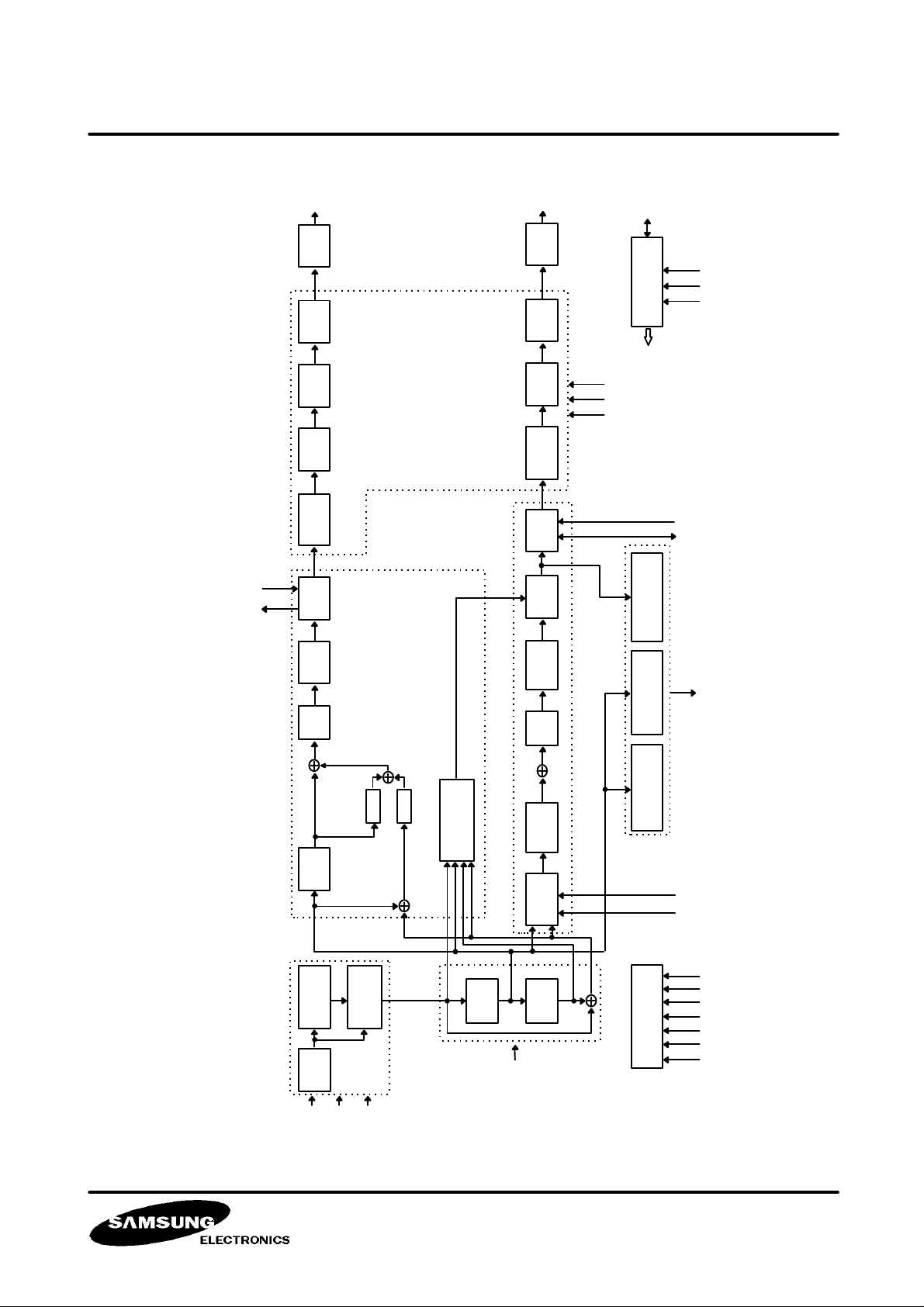

OPD- PROCESSOR

CD9 ~ 0

YI7 ~ 0

YO7 ~ 0

AY

ENCODER

AY

IF EFFECT SFC BM DAC

CSUP

HUE &

MD7 ~ 0

MICOM

INTERFACE

INT. REGISTER

BF

LALT

FSCA

UVO3 ~ 0

UVIO3 ~ 0

AWB

INTEGRATOR

WRN

RDN

AS

LPF γ DLY IF EFFECT BLK SYNC YDL DAC

Y PROCESSOR

DET

DEFECT

PREPROCESSOR

CLAMP

BLOCK DIAGRAM

PBLK

HAP

DEFECT

CORRECT

VSKIP

( - )

VAP

DET

HL / EDGE

LM

CDIFF

MATRIX

γ

W/B

RGB

MATRIX

B

/C

R

/C

LPF

L

Y

C PROCESSOR

LM

LHLD

AF ZONE

AE

INTEGRATOR

AF

INTEGRATOR

ID

HCON

TIMING

INTERFACE

HD

VD

PCLK

CBLK

CSYNC

RSTN

XCK

VID-97-D004

February 1997

10

KS7306 DIGITAL CAMERA PROCESSOR

Y

OMDL

OMDH

OA2W1L

OA1W1L

OA2W1M

OA1W1M

OA1W2L

OA2W2L

OA1W2M

OA2W2M

OAP2W1L

OAP1W2L

OAP1W1L

OWN

OAP2W2L

OWSH

OACCL

16

OACCM

OA2W1H

OA1W1H

24

INTEGRATOR

HPF

2

OA1W2H

OA2W2H

OAP2W1H

OAP1W2H

OAP1W1H

16

Peak & Hold

MUX

OAP2W2H

OPC1A

OPC1B

OPC2B

OPC2A

OWM

OWSV

8

Window Control

OPC1E

OPC1C

OPC1D

OPC2E

OPC2C

OPC2D

OPC1F

OPC1G

OPC2F

OPC2G

OACCH

24

INTEGRATOR

Detection

16

INTEGRATOR

MUX

6

SRAM

Memory

(16b *48w)

OADR

Memory Control

OYL

6

OBYTH

OADR

LPF

8

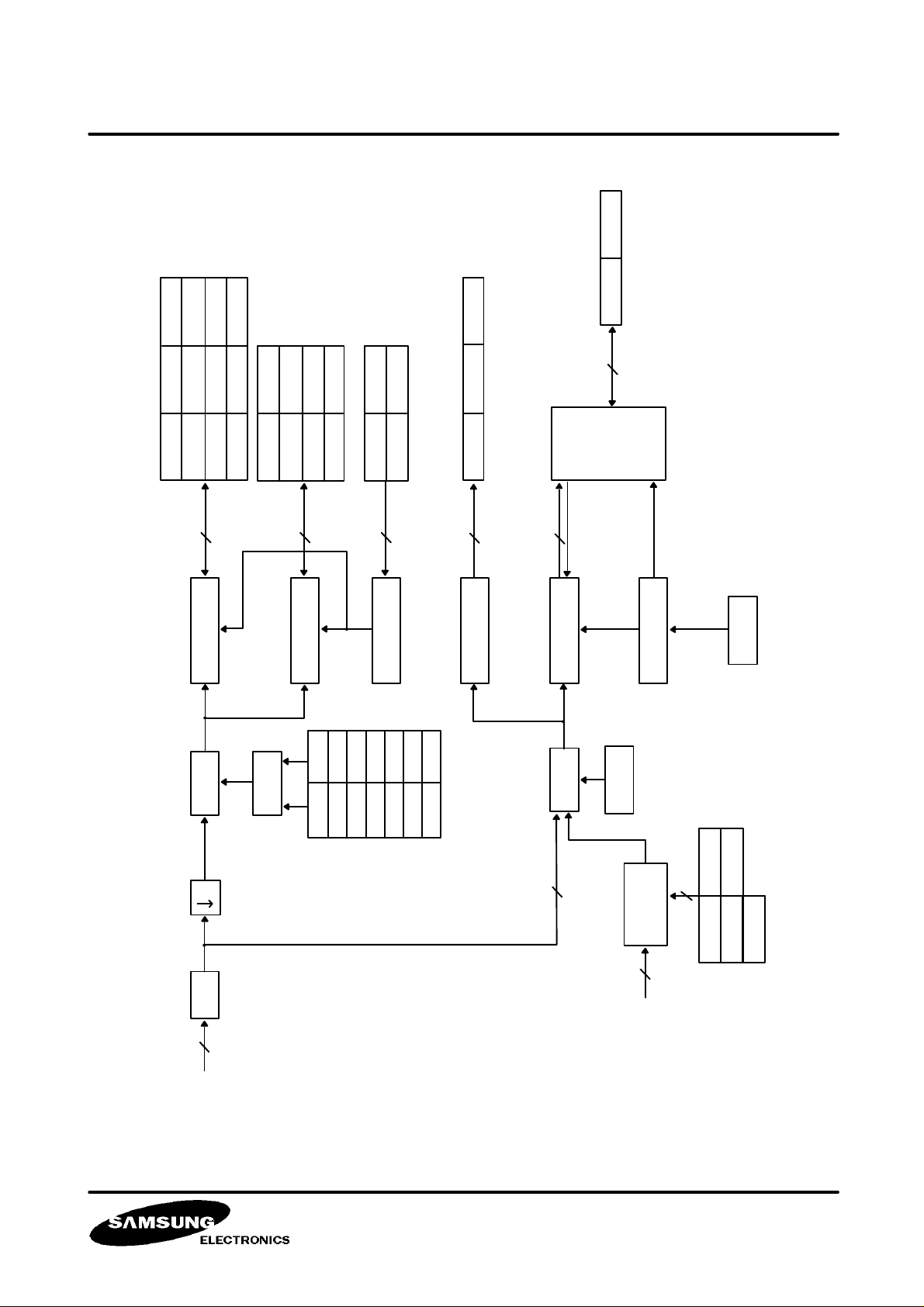

OPD-PROCESSOR BLOCK DIAGRAM

VID-97-D004

February 1997

Comparator

6

(R-Y)/(B-Y)

OYH

OADS

ORYTH

11

KS7306 DIGITAL CAMERA PROCESSOR

OPERATION OF BLOCKS

1. Preprocess

In case of signal processing of a camera with single CCD, before the performance of main processing,

it takes the optical black appearing before the real data among CCD data as the reference value and

the mean figure of it enables correct alignment of the black in the main processing, and in case of

defect found existing in CFA mode, it locates 4 errornous spots in maximum and processes to replace

the errors with two siding data by initial interpolation and then outputs line memory.

2. Line memory

Two built-in 10 bits line memories for 3 line color processing in 2H delay application, enable

simultaneous vision of 3 horizontal video lines, and in the processing of luminance signals, 1H delayed

signal, the H1D is offered, and in the chroma signal processing, HO2D or the luminance signal process

lines interpolated by two siding lines one in front and the other in the back are offered.

The line momory has 1024 depth for safe application to a CCD with 620 pixels, of 16:9 aspect.

For application to gyro sensor based and CCD controlled electronic image stabilizer system, it has the

functional capability to hold previous line at the blank signal line.

This is externally controlled by a LHLD signal.

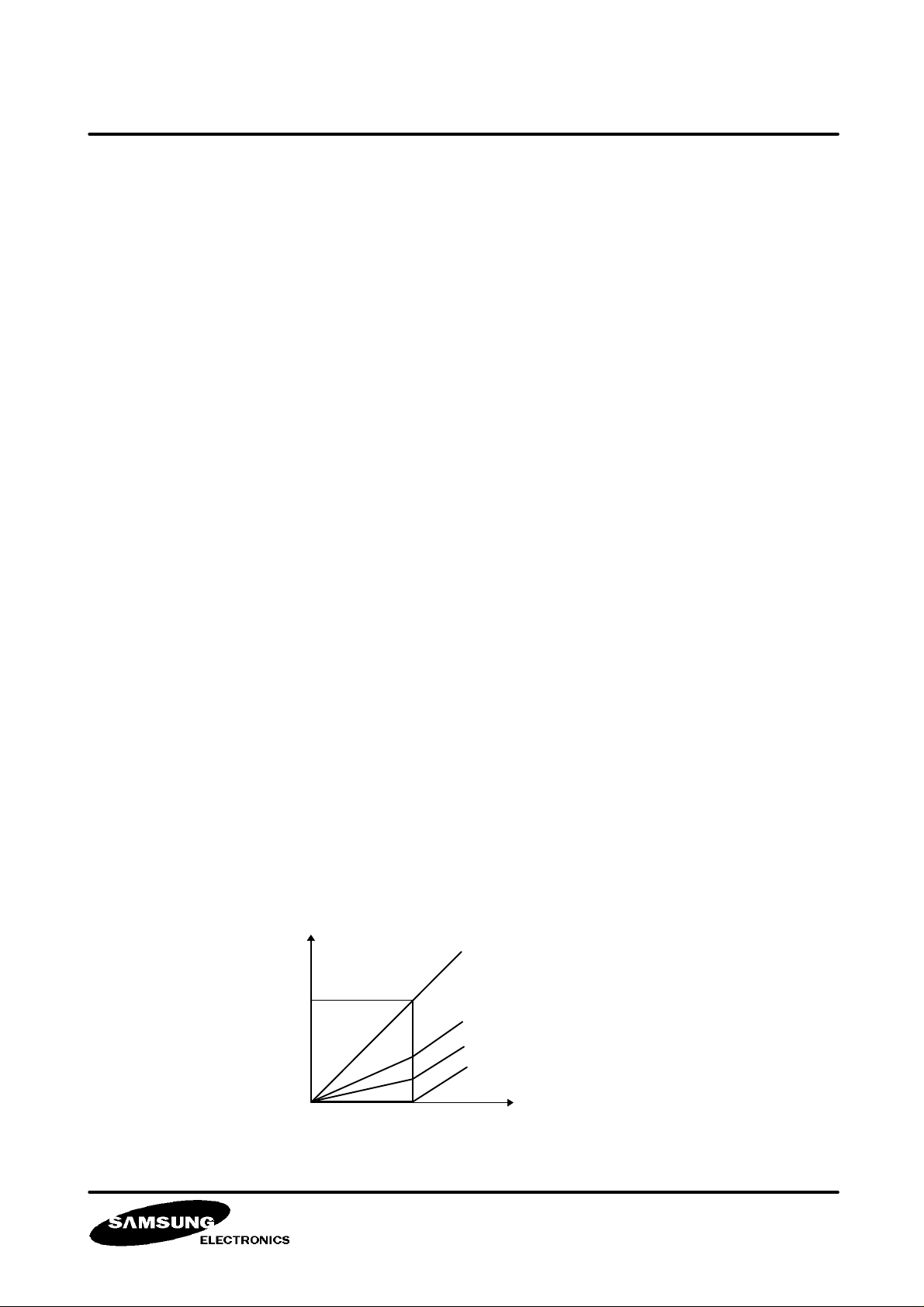

3. Y processor

- LPF

The filter removes recurring pattern noise of single type CCD.

- Non-linear characteristics in H aperture application :

In order to reduce back noise caused by the noise of low luminance when H aperture is emphasized,

low luminance components are compressed before the aperture.

OUTPUT

BKG(X1)

BKG(X1/2)

BKTH

BKG(X1/4)

BKG(X0)

INPUT

VID-97-D004

February 1997

12

KS7306 DIGITAL CAMERA PROCESSOR

- H_Aperture

Horizontal and vertical outline portions are emphasized.

INPUT

HAFS<1:0> = ″00″

HAFS<1:0> = ″01″

HAFS<1:0>= ″10″

HAFS<1:0> = ″11″

- REGISTER

HAPG : Horizontal Aperture Gain Control

5bits (X0 ~ X0.96875)

VAPG : Vertical Aperture Gain Control

5bits (X0 ~ X1.9375)

APSC : Aperture Slice Level

6bits (0~63)

APCLP : Aperture Clip Level

2bits 0 0 OFF

0 1 256

1 0 128

1 1 64

OUT

-APSC

IN

OUT

-APCLP

IN

APSC

< Noise Slice >

VID-97-D004

February 1997

APCLP

< Aperture Clip >

13

KS7306 DIGITAL CAMERA PROCESSOR

- Gamma and knee

Adopting user defined variable gamma and knee in eight step piecewise linear method allows the user

free adjustment of the coefficient.

4. C-Processor

- S/H and interpolation LPF

With the input of HID and H02D signals from the line memory, C-Processor samples and holds S

and S2 for the generation of RGB chroma signals.

The band width of the signals so generated is limited by LPF.

- RGB matrix

Based on Cr, Cb and YC signals being the sum and balance components of S1 and S2, RGB chroma

signals are obtainable from the following matrix.

1

YC = S1 + S2, Cr = S2 - S1, Cb = S1 - S

2

R = Cr + CCOR X YC (or G)

G = YC - (Cr + Cb)

B = Cb + CCOB X G (or YC)

Register :

CCOR : Matrix coefficient for RED generation 6 bits (0-X0.25)

CCOB : Matrix coefficient for BLU generation 6 bits (0-X0.25)

CMATX : 2bits RED BLUE

0 0 Y

C

G

0 1 G G

1 0 G Y

1 1 YC Y

C

C

- White and black balance control :

Through interfacing with the micom, RB signal level is coordinated with G signal level.

Register :

* GWB : GREEN WHITE BALANCE CONTROL

8 bits (0~X4)

* RWB : RED WHITE BALANCE CONTROL

8 bits (0~X8)

* BWB : BLUE WHITE BALANCE CONTROL

8 bits (0~X8)

* GBLK : GREEN BLACK BALANCE CONTROL (2 ′S complement)

8 bits (-128 ~127)

* RBLK : RED BLACK BALANCE CONTROL (2 ′S complement)

8 bits (-128 ~127)

* BBLK : BLUE BLACK BALANCE CONTROL (2 ′S complement)

8 bits (-128 ~127)

VID-97-D004

February 1997

14

KS7306 DIGITAL CAMERA PROCESSOR

- Gamma correction :

The process is indentical to the variable gamma method employed in the process of Y signals.

Register :

CGM1 - CGM8 : C-Gamma Y fraction coefficient

8 bits (0~255)

- Chroma MATRIX

It generates R-Y and B-Y signals of basic color space used as NTSC/PAL broadcast standards.

- HUE and gain control

Micro adjustment can be made to coordinate the balance vector to its complement color vector.

Individual adjustment against +, - on the R-Y and B-Y vector space that color regeneration is enhanced.

Register :

R-Y

RHPN

BHPN

(-1~X1)

RHNP

BHNP

(-1~X1)

RHPP

BHPP

(-1~X1)

B-Y

RHNN

BHNN

(-1~X1)

- Chroma suppress

It supresses false chroma signal by horizontal outline and high luminance signal.

Supress level is adjustable by the mode data.

- Chroma signal interface

PLCK

UVO3 ~ 0

UVCK

..

RY0<7:4> RY0<3:0> BY0<7:4> BY0<3:0> RY1<7:4> RY1<3:0>

VID-97-D004

February 1997

.....

15

KS7306 DIGITAL CAMERA PROCESSOR

5. NTSC/PAL encoder

- Digital effects

It performs various digital effects and Mosaic, Art Freeze, and Posi/Nega inversion.

Register :

. Art 3 bit 000:normal 001:128 rep val* 010:64 rep val* 011:32 rep val*

100:6 rep val* 101:8 rep val* 110:4 rep val* 111:2 rep val*

( *Rep val stands for representative value.)

. Nega 1 bit 0:normal 1:negative

- Fade function

A smooth screen shift is available by Y/C gain control (8bit resolution)

Register :

. Ygain 8bits 0-X1

. Cgain 8bits 0-X1

- Set-up and white clip

It determines the set-up level that conforms to specific broadcast method (NTSC/PAL) and defermins

also adequate white clip level.

Register :

. Set-up 5bits 0-32

. WCLP 8bits 0-256

- BLK/SYNC mix

CBLK/CSYNC are mixed to conform specific broadcast method

- Sampling frequency converter

The chroma signal synchronized to PCLK is converted to 4FSC frequency for chroma modulation.

- Modulation

The chroma data synchronized to 4FSC is put to repeat R-Y,B-Y in 2FSC frequncy,and invert in 4FSC

frequncy and thus modulation of chroma signal is achieved. In this process the level of burst signal

applied by the EUSC/EVSC reg, can be controlled and by the adjustment of EUSC/EVSC, color phase

can

be rotated entirely.

Register :

. EUSC 8bits B-Y burst level

. EVSC 8bits R-Y burst level

- Delay

The delays developed in the signal processing path of luminance and chroma signals are compensated

and other delicate delays resultant from the external applications can also be compensated.

VID-97-D004

February 1997

16

KS7306 DIGITAL CAMERA PROCESSOR

* ORYTH

6. OPD Processor

The OPD Processor detects signals for AE/AF1/AF2/AWB and enters the detected signals to the

micom through the micom interface. The signals for AF1/AF2 can be detected simultaneously in one

filed for both of integral and peak values and the detection field can be set freely set by the user.

The peak value is, however, obtained by means of finding from a line in each field first and then

repeated by lines to fine the peak. The signals for AE/AWB can be detected by means of taking

integrated value of entire image or a sectional value of the image area divided in 48 sections.

Register :

* OCMD

* OA1W1H,OA1W1M,OA1W1L

* OA1W1H,OA1W1M,OA1W1L

* OA1W2H,OA1W2M,OA1W2L

* OA2W2H,OA2W2M,OA2W2L

* OAP1W1H,OAP1W1L

* OAP2W1H,OAP2W1L

* OAP1W2H,OAP1W2L

* OAP2W2H,OAP2W2L

* OACCH,OACCM,OACCL

* OMDH,OMDL

* OWM

* OWN

* OWSV

* OWSH

* OADR

- LPF; 6Tap FIR filter (-3db at 2 MHZ)

Signal band for input is limited for AE/AF.

- HPF; 3 Order IIR filter (HPF1:200KHZ, HPF2:600KHZ)

The filter suppresses low frequency components to enable detection of only the outline signal

selectively for AF1/AF2. Detection of AF1/AF2 is performed simultaneously for each horizontal line

that detection of AF1/AF2 singal in any one field is enabled.

The filter 3 order IIR filter is structured a hardware like, but coefficients are devised programmable

that the performance charactor can be adjusted by the user.

8 bits

8 bits * 3

8 bits * 3

8 bits * 3

8 bits * 3

8 bits * 2

8 bits * 2

8 bits * 2

8 bits * 2

8 bits * 3

8 bits * 2

8 bits

8 bits

8 bits

8 bts

6 bts

Mode settings command register

Integrated data of A area for AF1

Integrated data of A area for AF2

Integrated data of B area for AF1

Integrated data of B area for AF2

Peak data of A area for AF1

Peak data of A area for AF2

Peak data of B area for AF1

Peak data of B area for AF2

Peak data of full area for AE/AWB

Integrated of small image of sectioned area

Pixel number of small image of sectioned area

Line number of small image of sectioned area

Vertical start point of area A for AF

Horizontal start point of area A for AF

RAM start address (Write/Read)

Register :

* OPC2A, OPC2B, OPC2C, OPC2D, OPC2E, OPC2F, OPC2G 8bits AF2 HPF COEFFICIENTS

* OPC1A, OPC1B, OPC1C, OPC1D, OPC1E, OPC1F, OPC1G 8bits AF1 HPF COEFFICIENTS

- Comparator

It removes chroma signal from the high luminance and low luminance components in R-Y and B-Y signals

in order to limit the signal range suitable for input to AWB for the purpose of the signal detections.

Register

* OYH 6bits High luminance threshold level

* OYL 6bits Low luminance threshold level

* ORY? 6bits R-Y chroma signal threshold level

* ORYTH

* ORY? 6bits B-Y chroma signal threshold level

* ORBYTH 6bits (R-Y) + (B-Y) threshold level

VID-97-D004

February 1997

17

Loading...

Loading...