Samsung KS7301B Datasheet

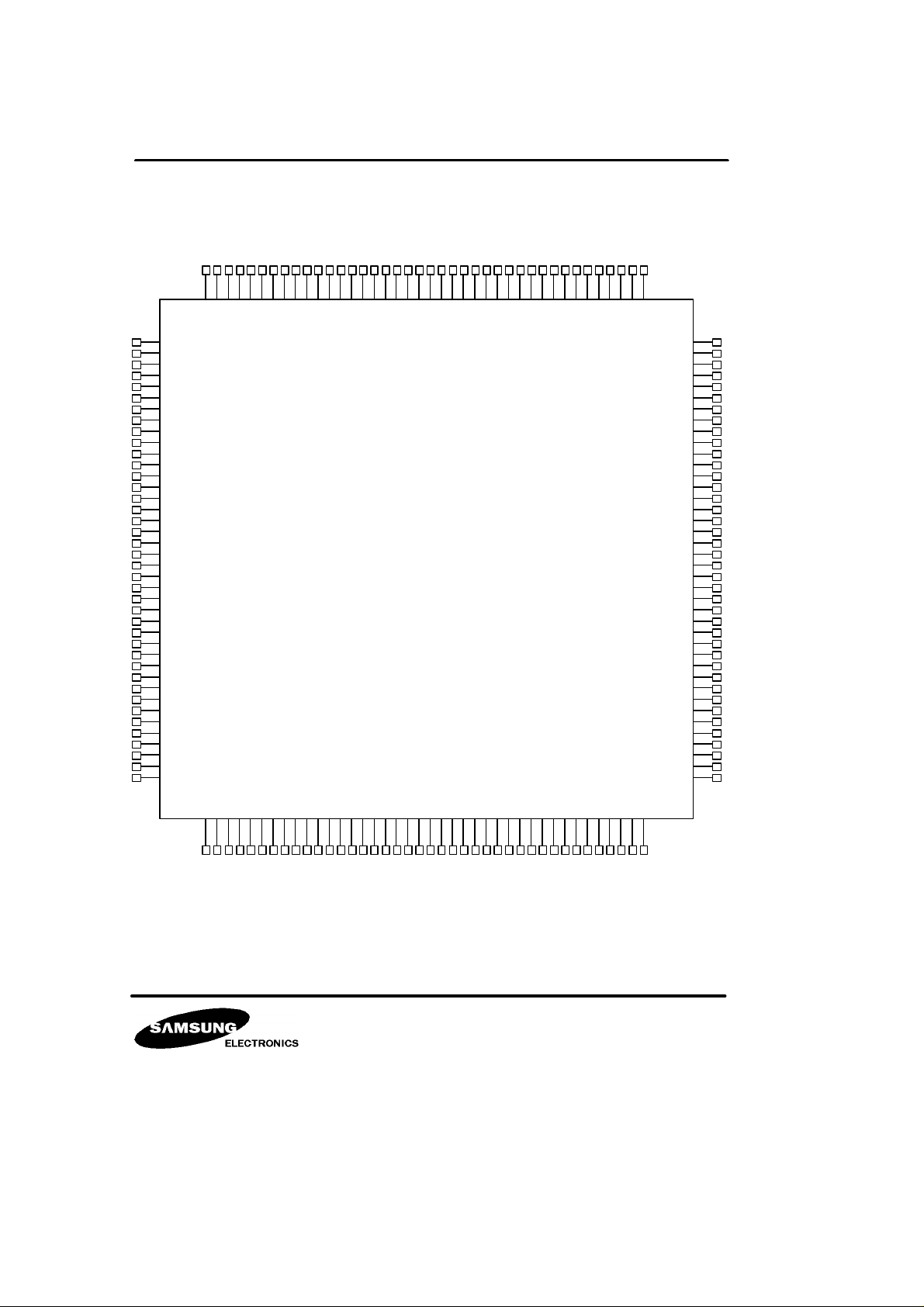

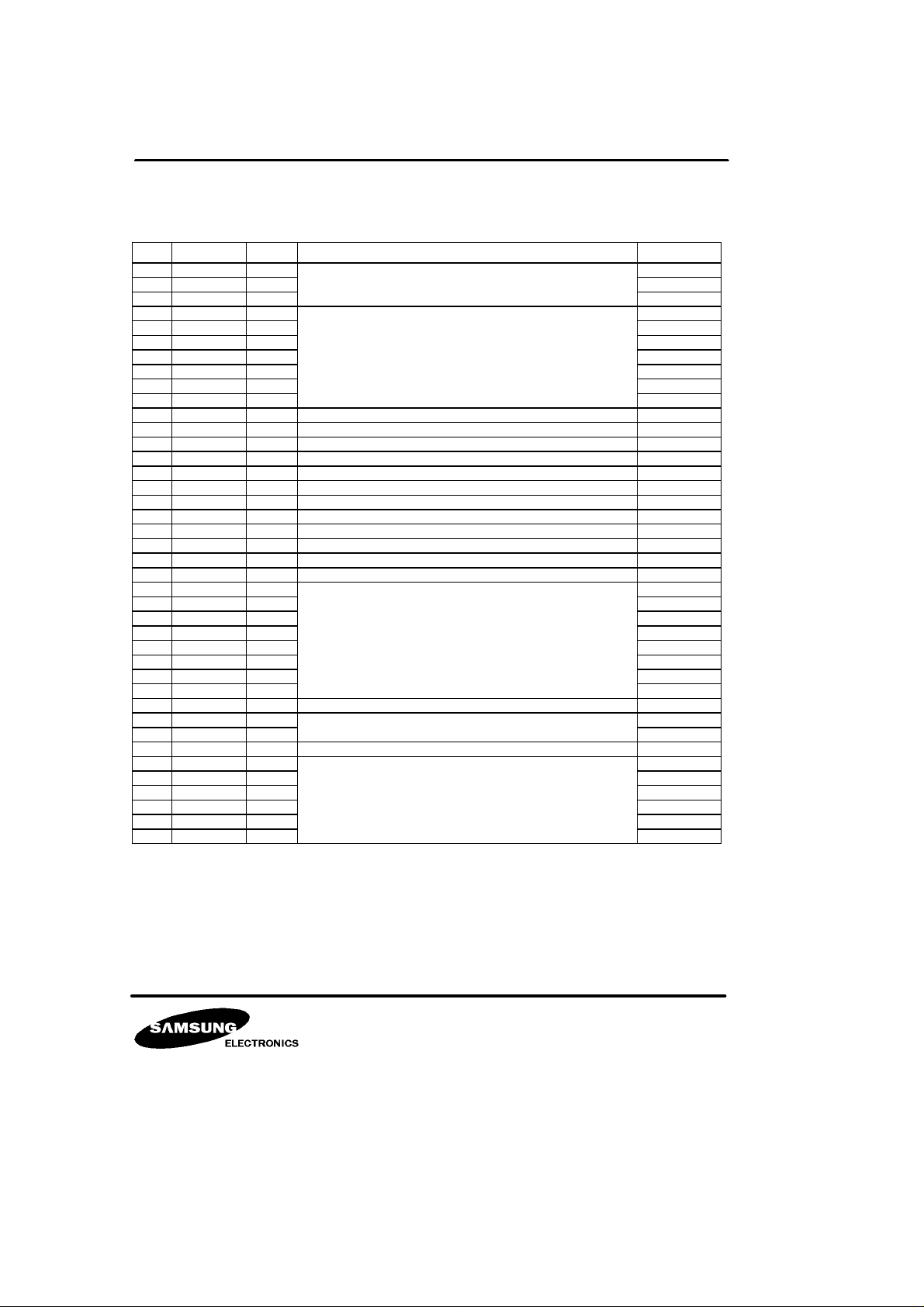

KS7301B DIGITAL CAMERA PROCESSOR

ORDERING INFORMATION

GENERAL DESCRIPTION

KS7301B is a CMOS IC designed for Digital Camcorder

System. This Processor is Compatible for NTSC/PAL & Hiband/Normal Camcorder System.

FEATURES

- Luminance & Chroma Signal Procession

- Built in Timing Generator

- Built in Sync. Generator

- Built in Memory for Detection Part

(16bit* 64 word*2 page)

- Built in 1H delay line (1H *2, 8 bit *910)

- Built in Encoder for PAL/NTSC

- Built in DIS Interface Block

- Built in Super Impose function

- Built in Title Mix Block

- Compatible with NORMAL/Hi - Band System

- Built in Micro controller Interface Block

BLOCK DIAGRAM

DISRSTN

FLD

LSSE

DYD

DHD

LD

SDATA

HEODN

VEODN

DOS <7:0>

DIS <7:0>

DM

(Detection Module)

CPM

(Color Processing

Module)

160-QFP-2424

Device Package Operating Temperature

KS7301B 160-QFP-2424

MATM

(Matrix Module)

(Encoding Module)

TST0

TST1SOEN

EM

-20°C ~ +75°C

Y <7:0>

C <7:0>

SPDAC

SPDAY

FSC

SYNC

LALT

BF

X1

X2

X3

X4

PCK

SCK

H1

H2

XSG1

XSG2

(Timing Generation Module)

ID

SHD

XPG

SHP

XSUB

TGM

CLP1

CLP2

CLP3

CLP4

M - BUS

BIM

(BUS Interface Module)

V2

V1

V3

V4

PC

SPO

PBLK

PALNTN

AD<7.0>

HIB

DCPCSN

ASTB

WRN

RDN

WAITN

RESETN

DCPN

SAM8NECN

SIM

(SuperImpose Module)

VVD

VHD

VBLK

SWEN

VDATA

SCSROMN

SSA <19:0>

SSD <7:0>

VCOL<2:0>

SCSRAMN

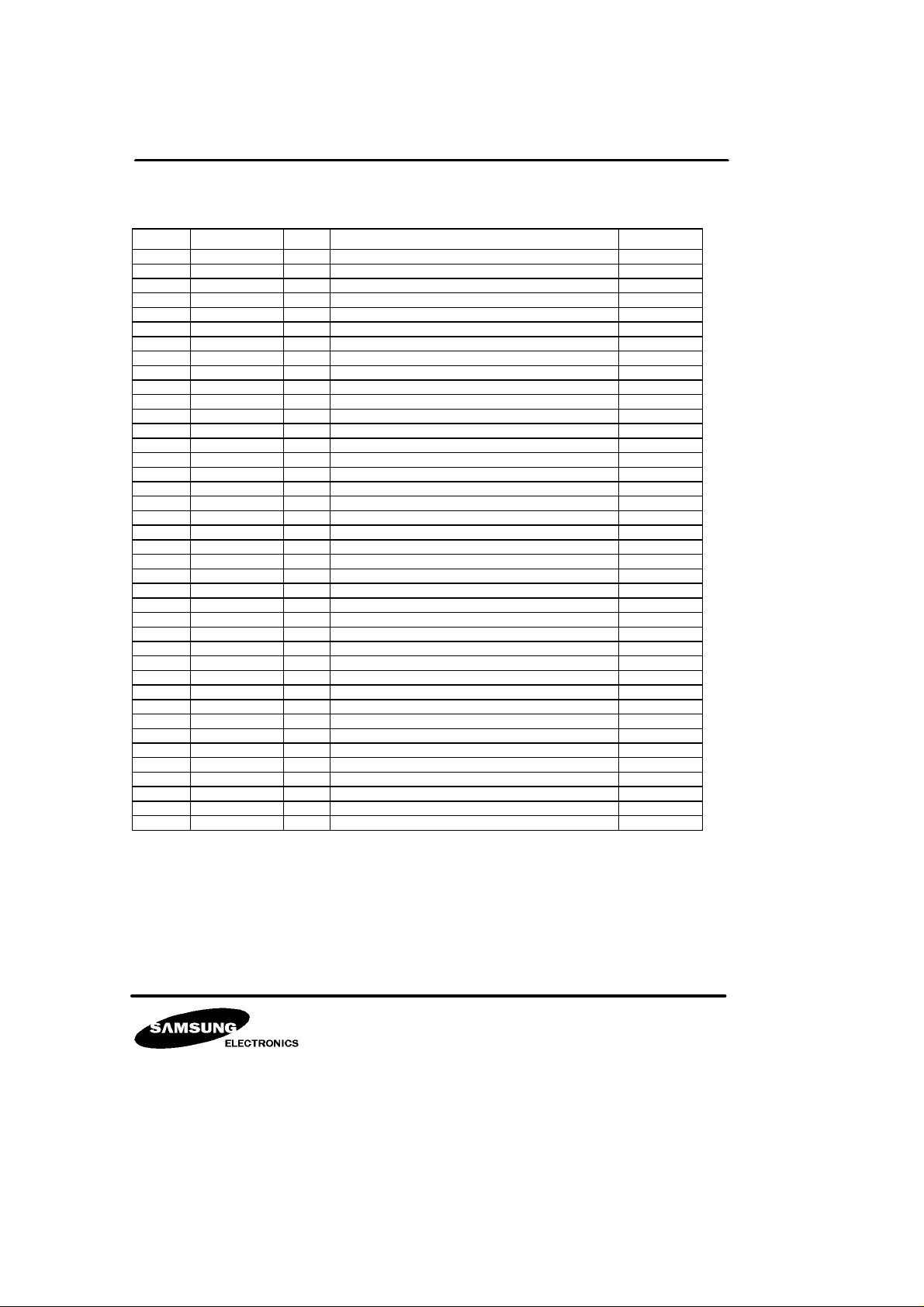

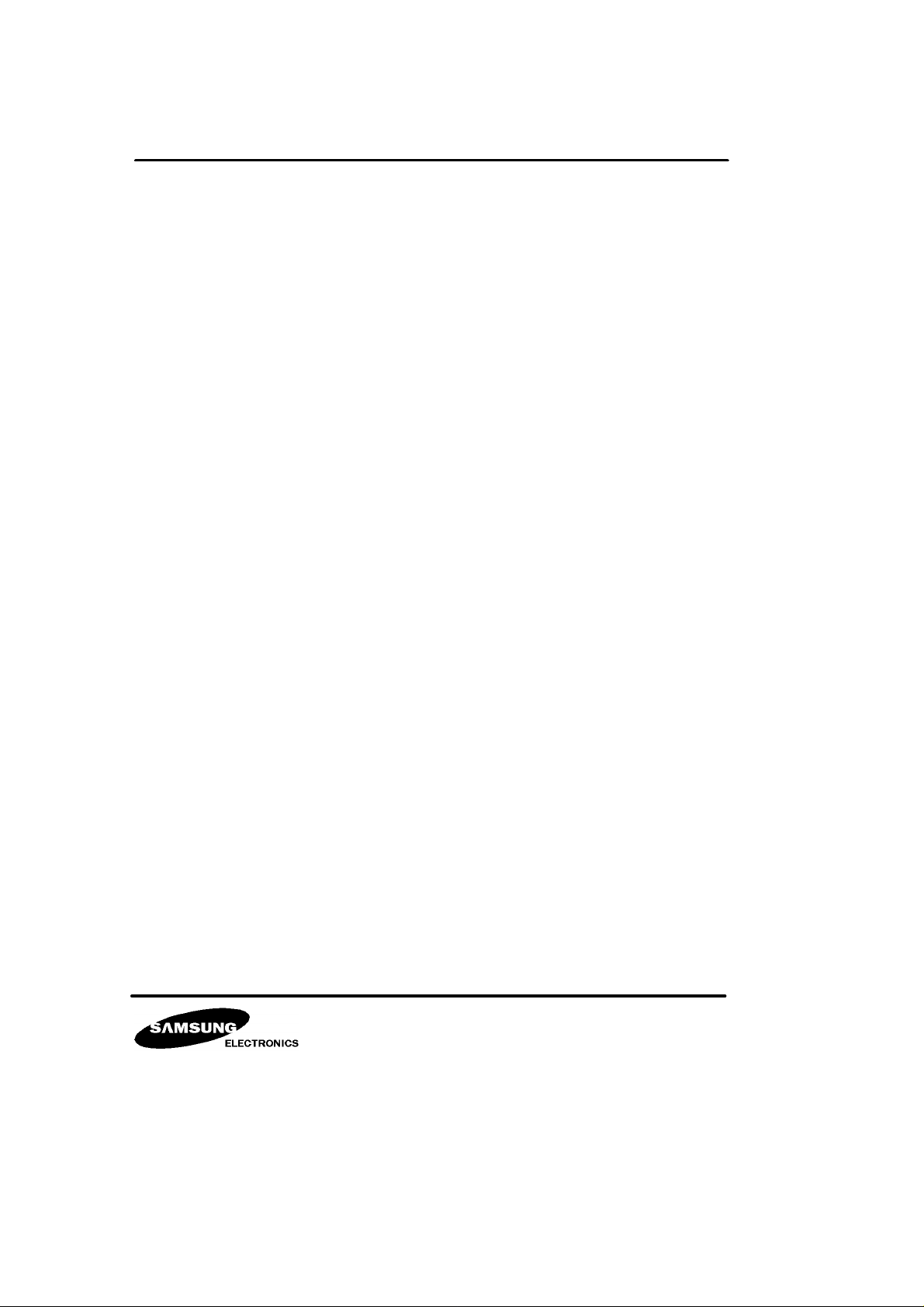

KS7301B DIGITAL CAMERA PROCESSOR

PIN CONFIGURATION

121

126

131

136

141

146

151

156

160

Y<5>

Y<6>

Y<7>

C<0>

C<1>

C<2>

C<3>

C<4>

C<5>

C<6>

VDDIN

C<7>

SDATA

LD

DHD

DVD

VSSIN

VDD

LSSE

FLD

HEODN

VEODN

DIS<0>

DIS<1>

DIS<2>

DIS<3>

DIS<4>

DIS<5>

DIS<6>

DIS<7>

VDDIN

DOS<0>

DOS<1>

VSS

DOS<2>

DOS<3>

DOS<4>

DOS<5>

DOS<6>

DOS<7>

120

VSS

Y<4>

Y<3>

116

Y<2>

Y<1>

Y<0>

LALT

SPDAC

111

SYNC

SSA<11>

SSA<10>

96

SSA<9>

SSA<8>

SSA<7>

106

BF

FSC

SPDAY

SSA<19>

SSA<18>

SSA<17>

SSA<14>

SSA<16>

SSA<15>

101

SSA<13>

SSA<12>

KS7301B

VSS

SSA<6>

SSA<5>

91

SSA<4>

SSA<3>

SSA<2>

SSA<1>

86

SSA<0>

SSD<7>

SSD<6>

SSD<5>

SSD<4>

SSD<3>

81

VDD

SSD<2>

SSD<1>

SSD<2>

SCSRAMN

SCSROMN

VDATA

VCOL<2>

VCOL<1>

VCOL<0>

SAM8NECN

WAITN

DCPCSN

RESETN

PALNTN

SWEN

SOEN

VSSIN

VBLK

WD

VHD

VSS

AD<7>

AD<6>

AD<5>

AD<4>

AD<3>

AD<2>

AD<1>

AD<0>

RWN

ASN

DSN

VSSIN

PC

VDD

H18

VSS

VSS

X4

X3

DCPN

80

76

71

66

61

56

51

46

41

SCK

PCKIDDISRSTNNCNC

1

VDDNCNCNCNCNCNC

6

SP0

CLP1

CLP2

CLP3

CLP4

PBLK

SHD

VSS

SHPH1H2

XPG

XSG1

XSG2

XSUBV1V2V3V4

11

16

21

26

VDD

VSSX1X2

TST0

TST1

VDDIN

VDD

31

36

40

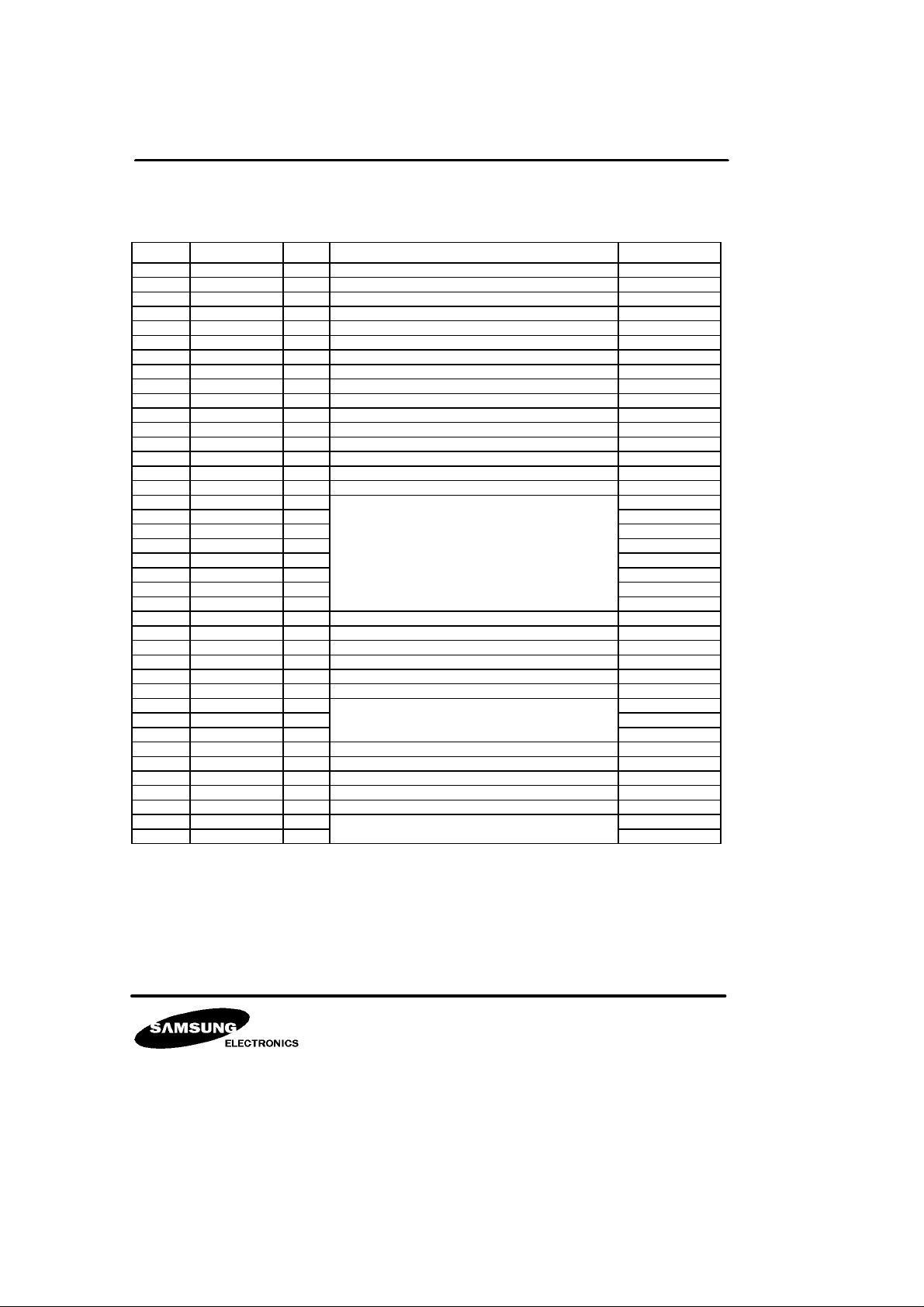

KS7301B DIGITAL CAMERA PROCESSOR

PIN DESCRIPTIONS

No. Symbol I/O Description Remark

1 SCK O Secondary Pipe Line clock ( PCK/2 )

2 PCK O Main Pipe Line Clock * 1

3 ID O CCD Line ID Signal

4 DISRSTN O DZE Reset Signal ( Active Low )

5 NC - No connection

6 NC - No connection

7 VDD - I/O Power supply

8 NC - No connection

9 NC - No connection

10 NC - No connection

11 NC - No connection

12 NC - No connection

13 NC - No connection

14 SP0 O A/D Converter Sampling Clock

15 CLP1 O Clamp Pulse 1

16 CLP2 O Clamp Pulse 2

17 CLP3 O Clamp Pulse 3

18 CLP4 O Clamp Pulse 4

19 PBLK O Video Pre - Blanking Pulse

20 SHD O Data Sampe & Hold Pulse For CDS

21 VSS - Ground

22 SHP O Pre-Charge Sample & Hold Pulse For CDS

23 H1 O Horizontal Driving Pulse 1 For CCD

24 H2 O Horizontal Driving Pulse 2 For CCD

25 XPG O Pre-Charge Gate Pulse For CCD

26 XSG1 O Read Out Pulse 1 For CCD

27 XSG2 O Read Out Pulse 2 For CCD

28 XSUB O Discharge Pulse For CCD

29 V1 O Vertical Driving Pulse 1 For CCD

30 V2 O Vertical Driving Pulse 2 For CCD

31 V3 O Vertical Driving Pulse 3 For CCD

32 V4 - Vertical Driving Pulse 4 For CCD

33 VDD - I/O Power Supply

34 VSS I Ground

35 X1 O Main X-tal Input *2

36 X2 I Main X-tal Output

37 TST0 I IC Test pin *3

38 TST1 - IC Test Output *3

39 VDDIN - Power Supply (INTERNAL)

40 VDD I Power Supply For X - tal

KS7301B DIGITAL CAMERA PROCESSOR

PIN DESCRIPTIONS (Continued)

No. Symbol I/O Description Remark

41 DCPN I IC Test Pin *3

42 X3 I 4Fsc X - tal Input For PAL (17.73447MHz)

43 X4 O 4Fsc X - tal Output For PAL

44 V

45 V

46 PALNTN I PAL/NTSC Mode Select ion Pin

47 HI8 I 760H/510H CCD Mode Selection Pin

48 RESETN I IC Reset Input

49 V

50 PC O Phase Comparator Output Of PAL PLL *4

51 VSSIN - Ground (INTRENAL)

52 DCPCSN I DCP Chip Select Pin (Low Active)

53 WAITN O Wait For Micom Interface (Low Active)

54 DSN(RDN) I *5

55 ASN(AS) I *6

56 RWN I *7

57 AD<0> I/O Micro controller Address / Data Bus I / O

58 AD<1> I/O

59 AD<2> I/O

60 AD<3> I/O

61 AD<4> I/O

62 AD<5> I/O

63 AD<6> I/O

64 AD<7> I/O

65 VSS - Ground

66 VHD I VCR Part HD Pulse (VCR PB Mode Title Mix)

67 VVD I VCR Part VD Pulse (VCR PB Mode Title Mix)

68 SAM8NECH I Microcontroller Type Select Pin (SAM8:High, NEC:Low)

69 VBLK O Title Blank Signal For VCR PB Mode Title Mix

70 VSSIN - Ground (INTERNAL)

71 VCOL<0> O Title Color Signal For VCR PB Mode Title Mix

72 VCOL<1> O

73 VCOL<2> O

74 VDATA O Title Data Enable Signal For VCR PB Mode Title Mix

75 SOEN O ROM Enable For Superimpose ( Low Active )

76 SWEN O RAM Enable For Superimpose ( Low Active )

77 SCSROMN O ROM Chip Select For Superimpose ( Low Active )

78 SCSRAMN O RAM Chip Select For Superimpose ( Low Active )

79 SSD<0> I/O Memory Interface Data I/O For Superimpose

80 SSD<1> I/O

SS

SS

DD

- Ground X - tal

- Ground

- I/O Power Supply

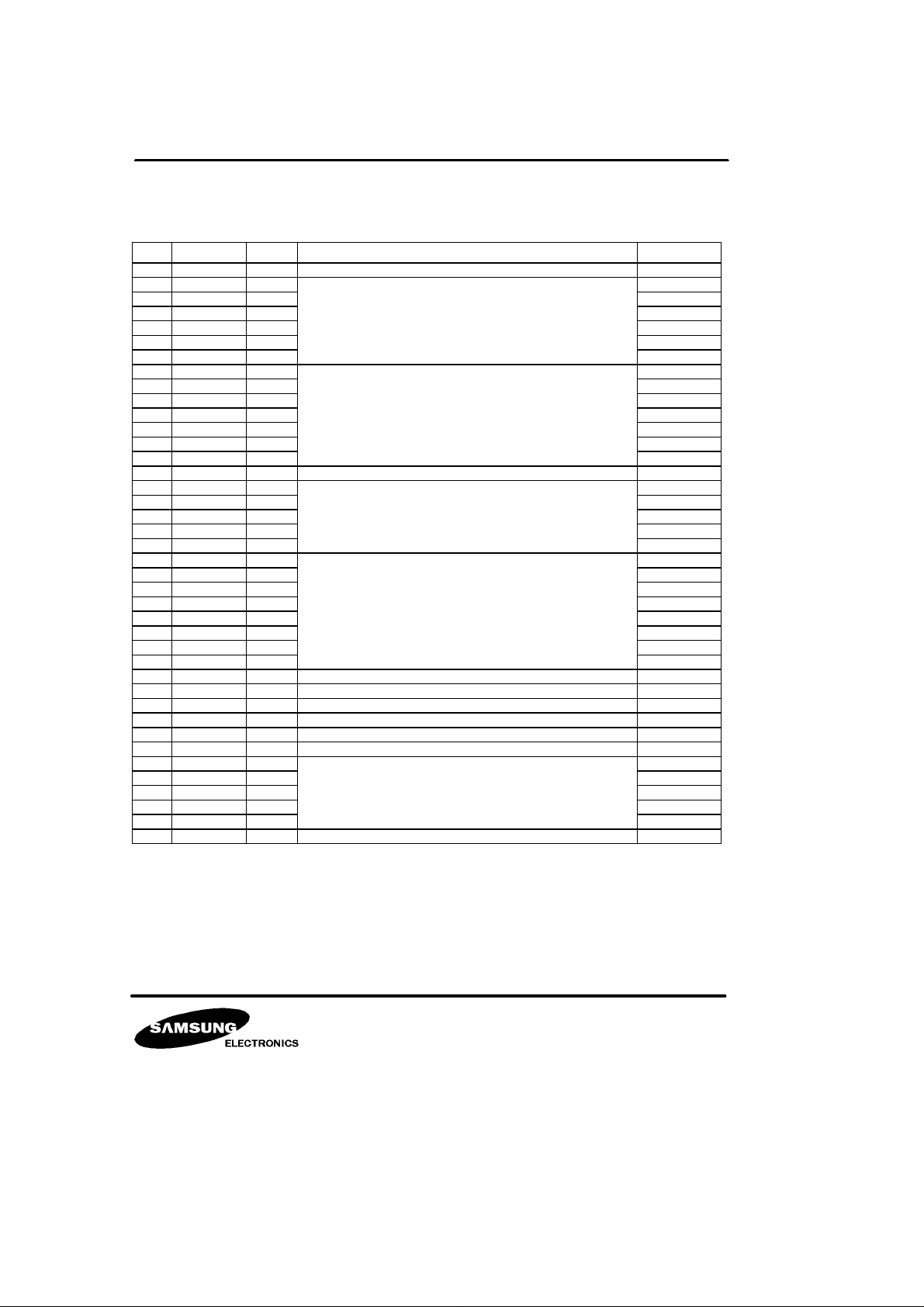

KS7301B DIGITAL CAMERA PROCESSOR

PIN DESCRIPTIONS (Continued)

No. Symbol I/O Description Remark

81 VDD - Power supply For I/O

82 SSD<2> I/O Memory Interface Data I/O For Superimpose

83 SSD<3> I/O

84 SSD<4> I/O

85 SSD<5> I/O

86 SSD<6> I/O

87 SSD<7> I/O

88 SSA<0> O Memory Interface Address Output For Superimpose

89 SSA<1> O

90 SSA<2> O

91 SSA<3> O

92 SSA<4> O

93 SSA<5> O

94 SSA<6> O

95 VSS - Ground

96 SSA<7> O Memory Interface Address Output For Superimpose

97 SSA<8> O

98 SSA<9> O

99 SSA<10> O

100 SSA<11> O

101 SSA<12> O Memory Interface Address Output For Superimpose

102 SSA<13> O

103 SSA<14> O

104 SSA<15> O

105 SSA<16> O

106 SSA<17> O

107 SSA<18> O

108 SSA<19> O

109 SPDAY O D/A Converter Sampling Clock For Y Signal (PCK)

110 FSC O Chroma Subcarrier (NTSC : 3.7595MHz, PAL : 4.4336MHz)

111 BF O Burst Flag Pulse

112 SYNC O Video Composite SYNC signal

113 LALT O Line Atternate Pulse For PAL

114 SPDAC O D/A Converter Sampling Clock for C Signal (4Fsc)

115 Y<0> O Y Video Signal Output

116 Y<1> O

117 Y<2> O

118 Y<3> O

119 Y<4> O

120 VSS - Ground

KS7301B DIGITAL CAMERA PROCESSOR

PIN DESCRIPTIONS (Continued)

No. Symbol I/O Description Remark

121 Y<5> O Y Video Signal Output

122 Y<6> O

123 Y<7> O

124 C<0> O C Video Signal Output

125 C<1> O

126 C<2> O

127 C<3> O

128 C<4> O

129 C<5> O

130 C<6> O

131 VDDIN - Power supply (INTERNAL)

132 C<7> O C Video Signal Output

133 SDATA O DZE Interface Serial Data

134 LD O DZE Interface Load Signal

135 DHD O HD signal for DIS

136 DVD O VD signal for DIS

137 V

138 VDD - Power supply For I/O

139 LSSE O Low Shutter Speed Enable

140 FLD O Video Field Signal

141 HEODN I Chroma S1, S2 Pixel Control (Default : High)

142 VEODN I Chroma 2R-G, G-2B Line Control (Default : High)

143 DIS<0> I/O CCD Video Input Signal

144 DIS<1> I/O

145 DIS<2> I/O

146 DIS<3> I/O

147 DIS<4> I/O

148 DIS<5> I/O

149 DIS<6> I/O

150 DIS<7> I/O

151 V

152 DOS<0> I DZE Video Input Signal

153 DOS<1> I

154 V

155 DOS<2> I DZE Video Input Signal

156 DOS<3> I

157 DOS<4> I

158 DOS<5> I

159 DOS<6> I

160 DOS<7> I

SSSIN

DDIN

SS

- Ground (INTERNAL)

- Power supply (INTERNAL)

- Ground

KS7301B DIGITAL CAMERA PROCESSOR

< REMARK >

*1. Main Pipe Line Clock

510H: NTSC 1820/3fh, PAL 18 6/3fh

760H: NTSC 910fh, PAL 908fh

*2. Main X-tal Input

NTSC:28.63636MHz, PAL:28,375Mhz

*3. IC Test Pin

( TST1, TST0, DCPN)

( 0,0,0 ) : TEST ( CPM )

( 0,0,1 ) : TEST ( MATM )

( 0,1,0 ) : TEST ( TGM )

( 0,1,1 ) : TEST ( SIM )

( 1,0,0 ) : TEST ( DC LOW )

( 1,0,1 ) : TEST ( DC HIGH )

( 1,1,0 ) : NORMAL

( 1,1,1 ) : RESERVED

*4. Phase Comparator Output Of PAL PLL

Include Charge Pump Part

*5. SAM 8 Mode : Data Strobe Signal Input ( Low Active )

NEC Mode : Read Enable ( Low Active )

*6. Address Strobe For Micom Interface

SAM 8 : Low Active, NEC : High Active

*7. SAM 8 Mode : Read / Write Enable Read : High, Write : Low )

NEC Mode : Write Enable ( Low Active )

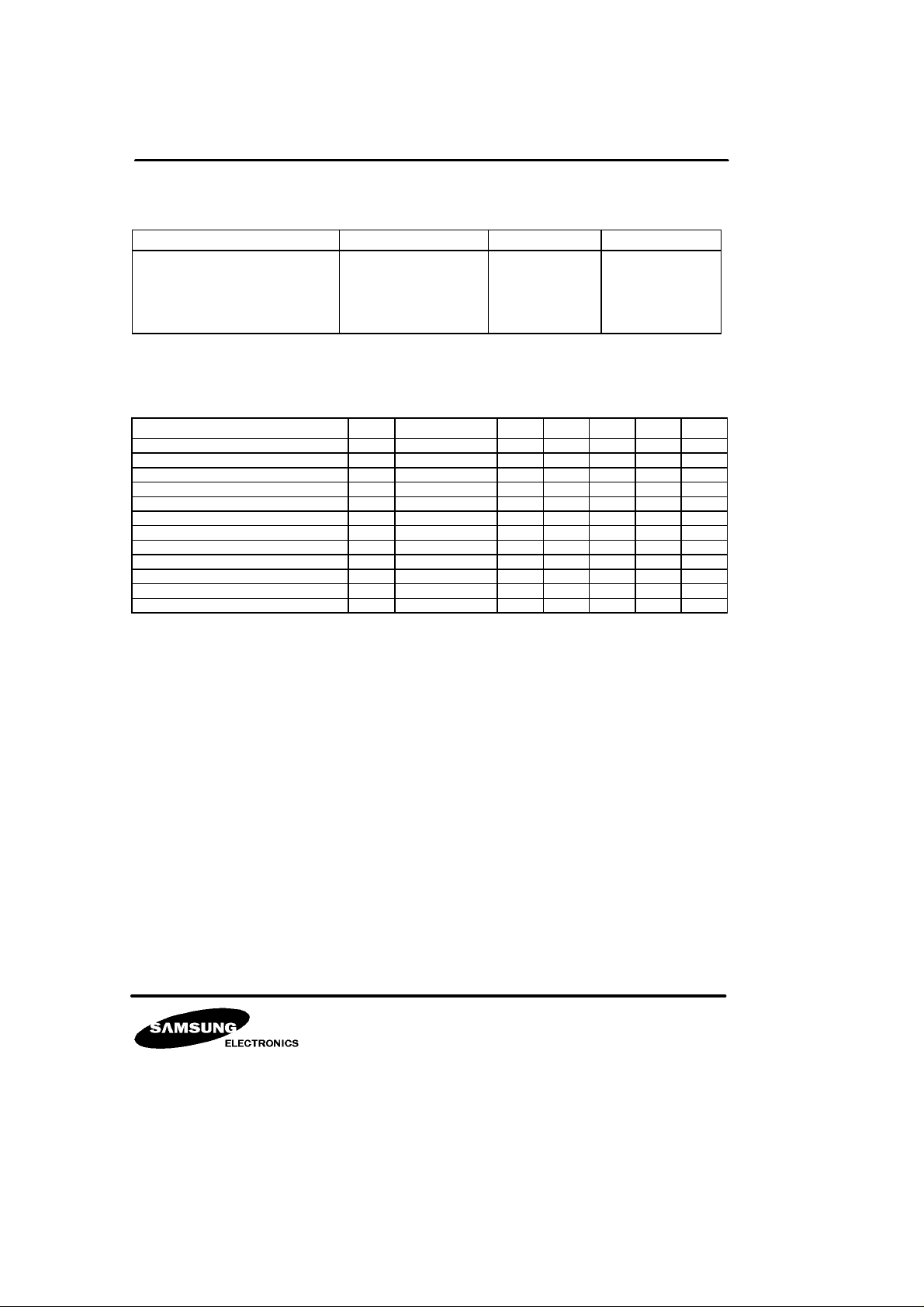

KS7301B DIGITAL CAMERA PROCESSOR

ABSOLUTE MAXIMUMTINGS (Ta=25°C)

Characteristics Symbol Value Unit

Supply Voltage

Input Voltage

Output Voltage

Power Dissipation

Operating Temperature

Storage Temperature

ELECTRICAL CHARACTERISTICS

(VCC=5V, Ta = 25°C, unless otherwise specified )

Characteristics Symbol Test Condition Min Typ Max Unit Remark

Supply Voltage V

Input Leakage Current I

Output Leakage Current I

Operating Current I

High-Level Input Voltage V

Low-Level Input Voltage V

Output High Voltage 1 V

Output Low Voltage 1 V

*Output High Voltage 2 V

*Output Low Voltage 2 V

**Output High Voltage 3 V

**Output Low Voltage 3 V

LO

CC

OH1

OL1

OH2

OL2

OH3

OL3

V

DD

V

IN

V

OUT

P

D

T

OPR

T

STG

DD

U

- 4.5 5.0 5.5 V

- - - 1 uA

-0.5~6.5

-0.5~VDD+0.5

-0.5~VDD+0.5

1

-20~+75

-65~+150

V

V

V

W

°C

°C

- - - 1 uA

VDD=5V - 140 180 mA

IH

IL

- 0.8V

- 0 - 0.2V

- V

DD

V

DD

V

DD

IOH=-2mA VDD-0.5 - - V *1

IOL=4mA - - 0.45 V *1

IOH=-4mA VDD-0.5 - - V *2

IOL=8mA - - 0.45 V *2

IOH=-8mA VDD-0.5 - - V *3

IOL=8mA - - 0.45 V *3

*: XPG, SHP, SHD Pulse

** :H1, H2 Pulse

*1 : IO=2mA

*2 : IO=4mA

*3 : IO=8mA

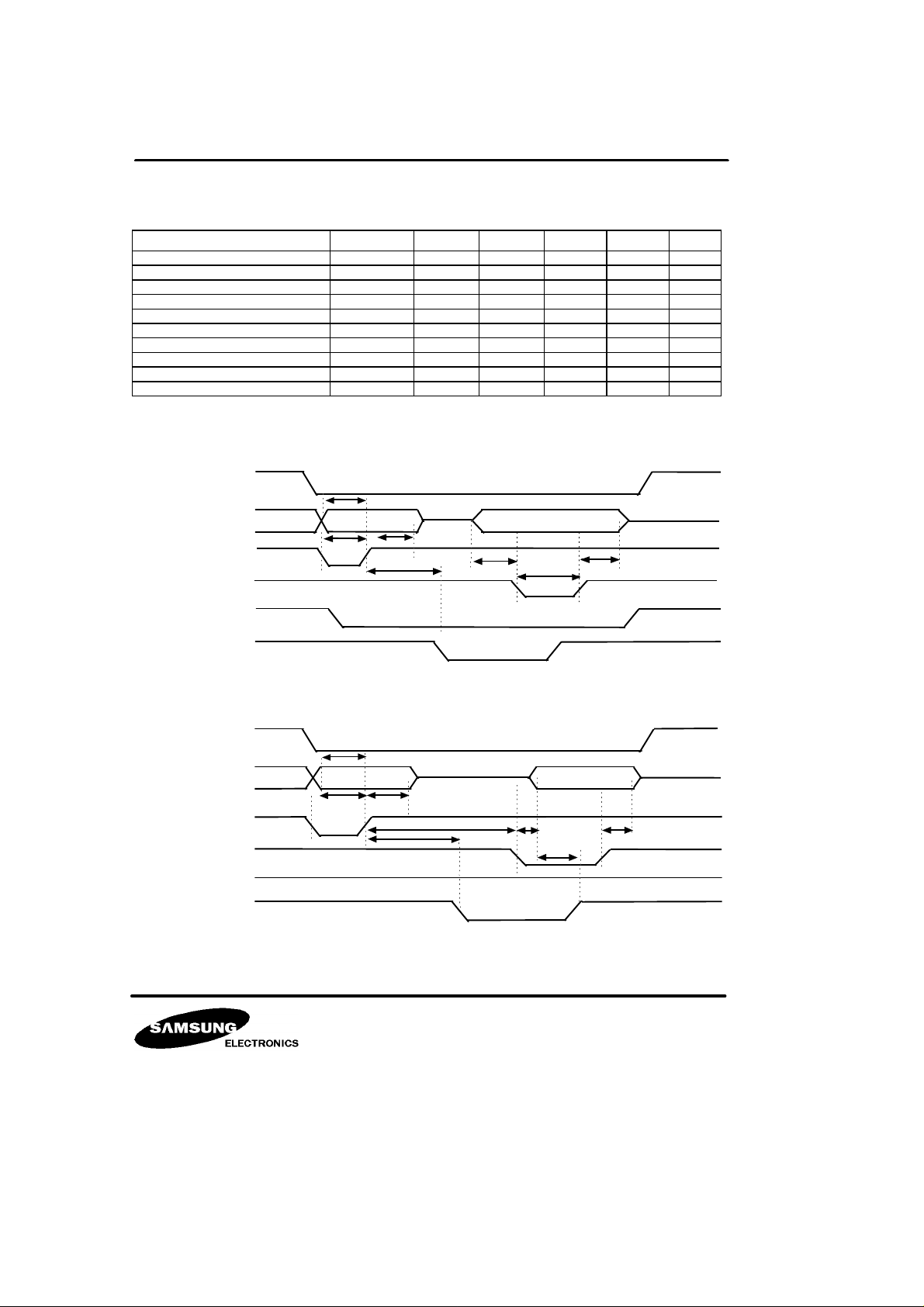

KS7301B DIGITAL CAMERA PROCESSOR

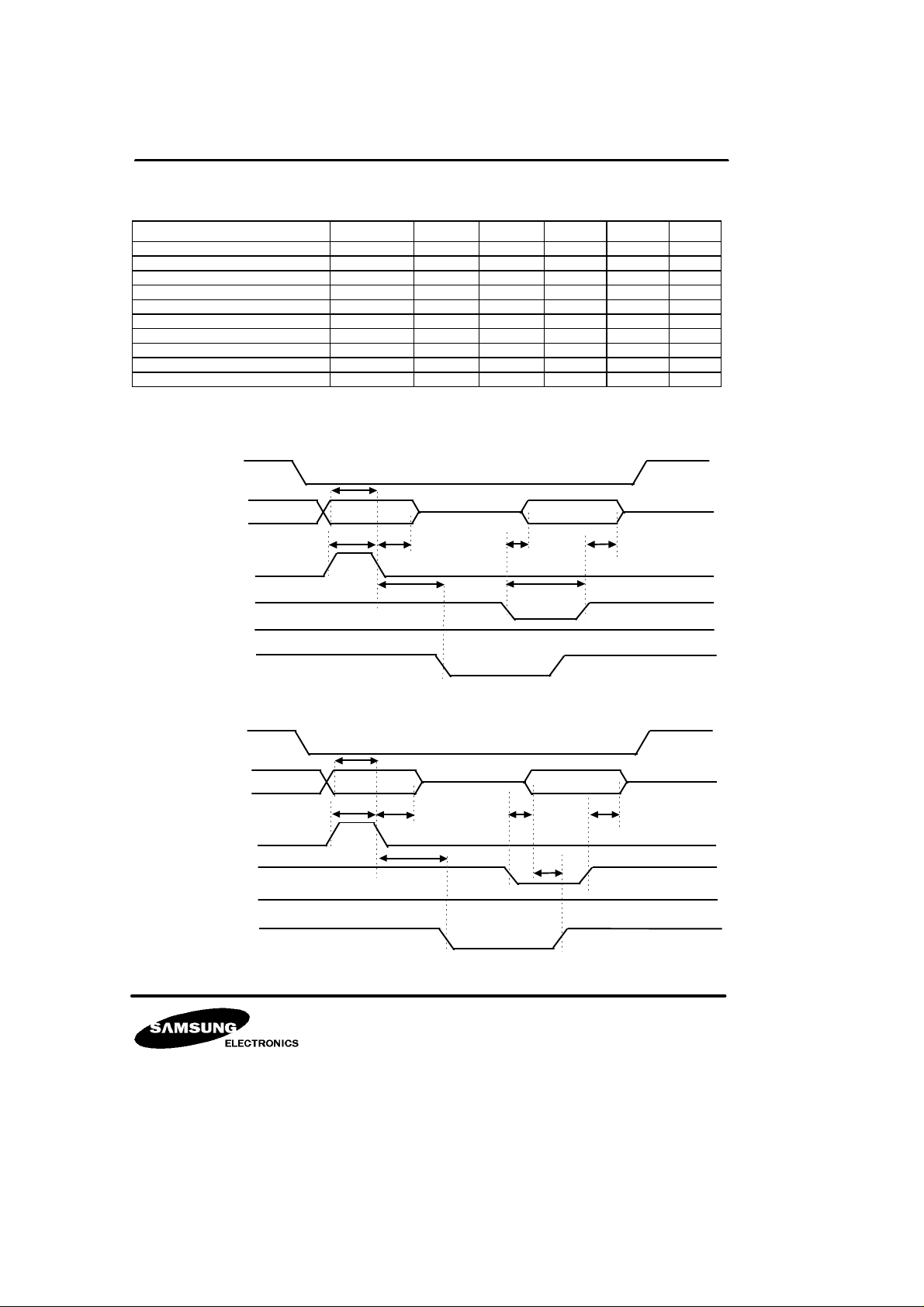

Micro controller Interface Ι : for SAVB ( PIN68A → HIGH )

Characteristics Symbol Min Typ Max Unit Remark

Address setup time Tast 15 - - nsec Address hold time Taht 35 - - nsec ASTB pulse width Tasw 35 - - nsec ASTB, WAITN distance Tawd - - 35 nsec DSN delay from Data Tdsdy 35 - - nsec Write

WRN width Twrw 400 - - nsec Data hold time Tdh 0 - - nsec Data delay from DSN Trdrv - - 270 nsec Read

Data, WAITN distance Tdwd 35 - - nsec ASN, DSN distance Tadd - - 140 nsec Read

Micro controller Interface Ι : for SAM8 (PIN68 → HIGH)

DCPCSN

Tast

AD <7:0>

ASN(AS)

DSN(RDN)

Tasw

Taht

Tdsdv

Tawd

DATAADDR

Tdh

Twrw

RWN (WRN)

WAITN

DCPCSN

AD <7:0>

ASN(AS)

DSN(RDN)

RWN(WRN)

WAITN

Tast

ADDR

Tasw

< WRITE MODE >

Taht

Tadd

Tawd

< READ MODE >

Trddv

DATA

Tdh

Tdwd

KS7301B DIGITAL CAMERA PROCESSOR

Micro controller Interface ΙΙ: for SAVB (PIN68 → LOW)

Characteristics Symbol Min Typ Max Unit Remark

Address setup time Tast 15 - - nsec Address hold time Taht 35 - - nsec ASTB pulse width Tasw 35 - - nsec ASTB, WAITN distance Tawd - - 35 nsec Data delay from DSN Tdsdy 35 - 100 nsec Write

WRN width Twrw 400 - - nsec Data hold time Tdh 0 - - nsec Data delay from RDN Trdrv - - 270 nsec Read

Data, WAITN distance Tdwd 35 - - nsec ASN, DSN distance Tadd - - 140 nsec Read

Micro controller Interface ΙΙ : for NEC (PIN68 → LOW)

DCPCSN

Tast

AD <7:0>

ADDR

Tasw

Taht

Tdsdv Tdh

DATA

ASTB (AS)

WRN (RWN)

RDN (DSN)

WAITN

DCPCSN

AD <7:0>

ASTB (AS)

RDN (DSN)

WRN (RWN)

WAITN

Tast

ADDR

Tasw

Tawd Twrw

< WRITE MODE >

Taht

Tawd

< READ MODE >

DATA

Trddv Tdh

Tdwd

KS7301B DIGITAL CAMERA PROCESSOR

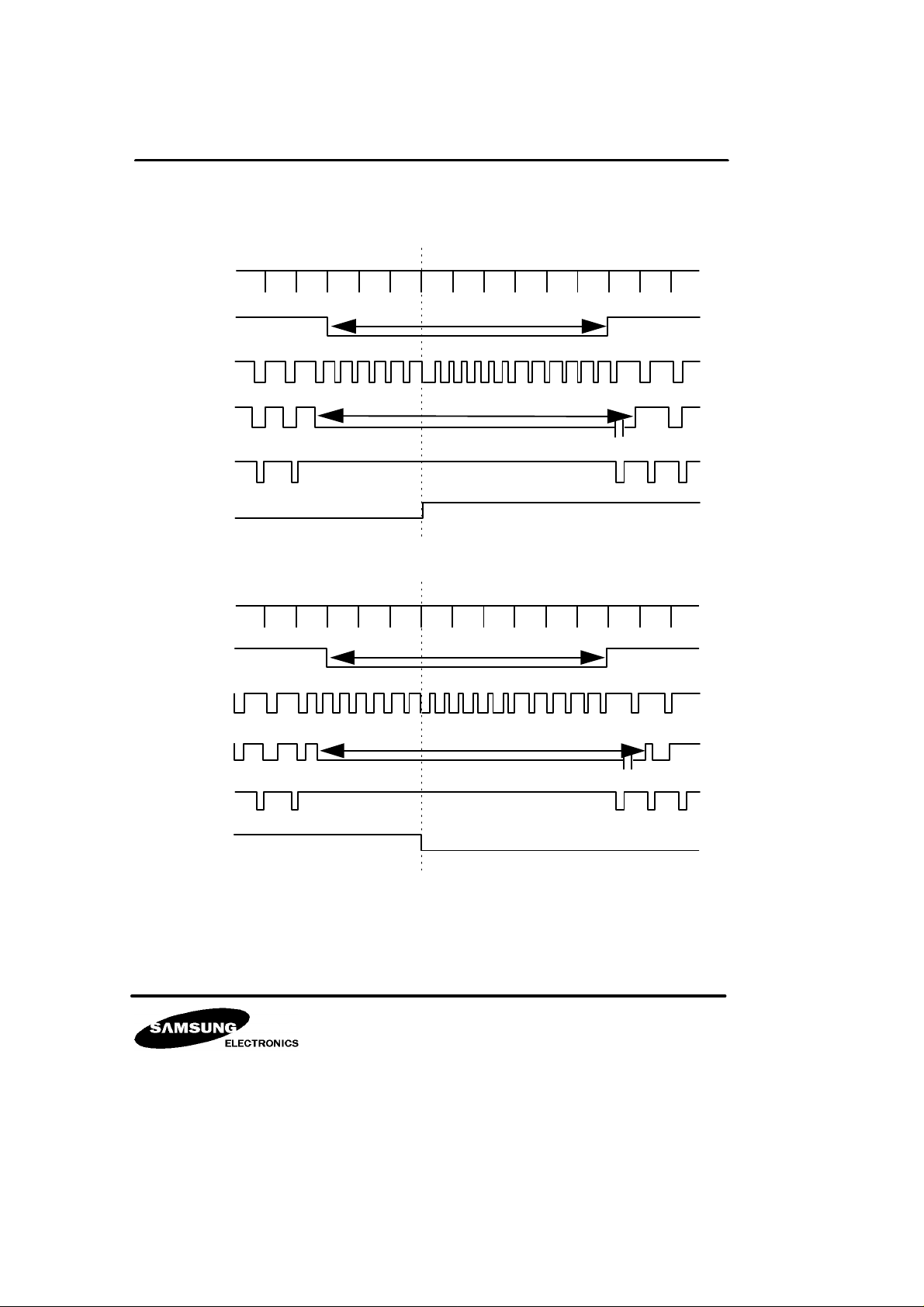

Vertical Timing for SYNC signal

(1) NTSC

VHD

VVD

STNC

VBLK

BF

FLD

VHD

VVD

STNC

FIELD ΙΙ FIELD Ι

9H

20H

ΙΙ

FIELD

FIELD

9H

Ι

VBLK

BF

FLD

20H

Loading...

Loading...