Samsung KS7221D Datasheet

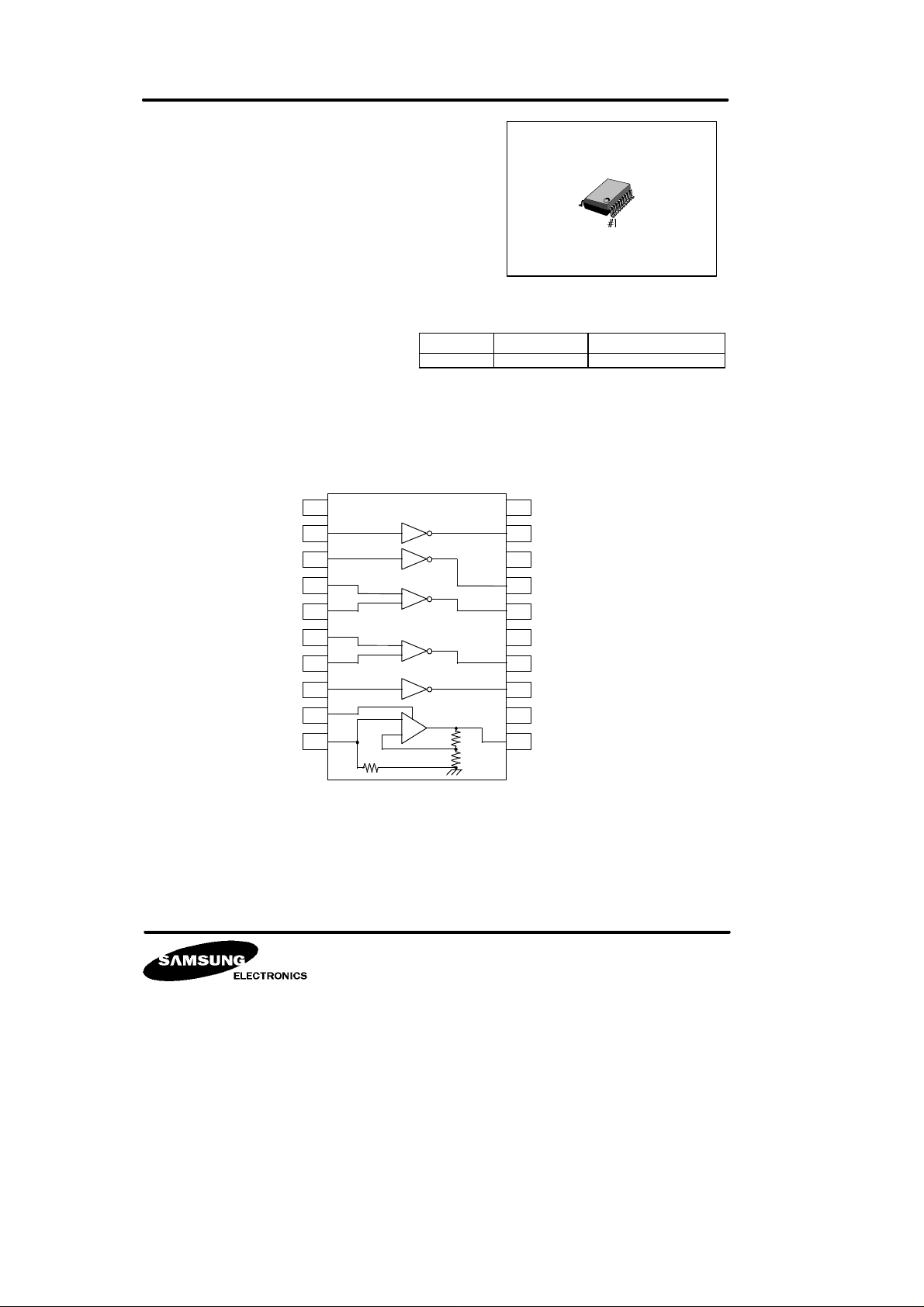

KS7221D VERTICAL DRIVER FOR CCD

GENERAL DESCRIPTION

The KS7221D is a Vertical CCD Driver LSI which is

fabricated by CMOS process for high voltage

20-SSOP-225

FEATURES

⋅ Include voltage source circuit for CCD image sensor.

⋅ Input voltage : 5V / 3.3V

⋅ Package : 20 SSOP

BLOCK DIAGRAM

GND

2

XSUB

3

XV2

4

XV1

5

XSG1

6

XV3

7

XSG3

8

XV4

9

VCP

10

DCIN

ORDERING INFORMATION

Device Package Operating Temperature

KS7221D 20-SSOP-225

+

-

201

VHH

19

VSUB

18

VEE

17

V2

Φ

16

ΦV1

15

VME

14

ΦV3

13

ΦV4

12

VHH

11

DCOUT

-20°C ~ + 85°C

KS7221D VERTICAL DRIVER FOR CCD

OUT

OPR

STG

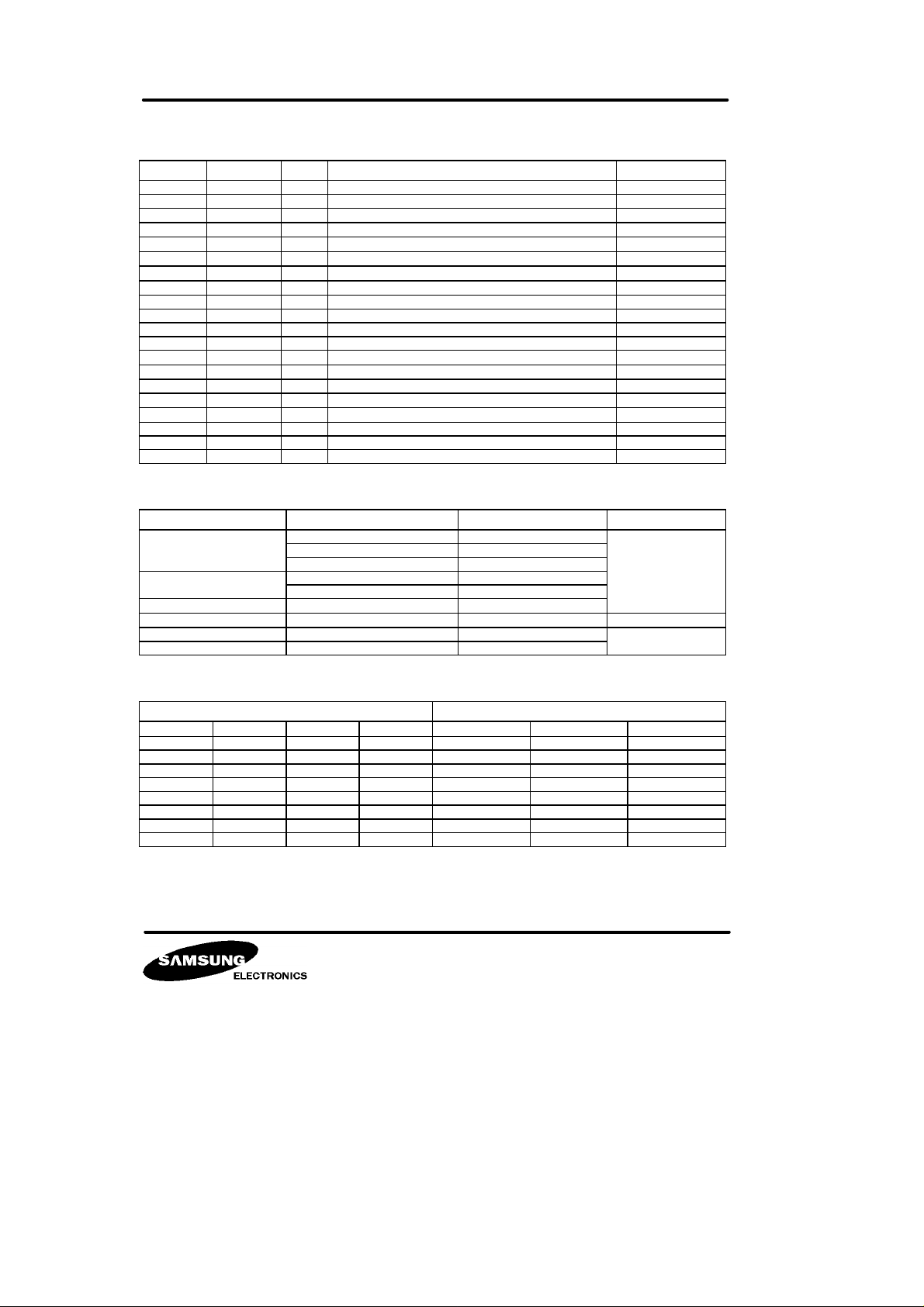

PIN DESCRIPTION

Pin Symbol I/O Description Remark

1 GND - Ground control

2 Xsub I Output Control (Vsub)

3 XV2 I

4 XV1 I

5 XSG1 I

6 XV3 I

7 XSG3 I

8 XV4 I

9 VCP I Power of amp

10 DCIN I OP-Amp input (internal pull-down resistor)

11 DCOUT O OP-Amp output

12 VHH - Power (15V)

13

14

15 VME - Power (0V)

16

17

18 VEE - Power (-8.5V)

19 Vsub O High Voltage Output ( 2 level : VEE, VHH)

20 VHH - Power (15V)

ΦV4

ΦV3

ΦV1

ΦV2

ABSOLUTE MAXIMUM RATINGS ( Ta = 25°C )

Characteristics Symbol Value Unit

Supply Voltage VHH -0.3 ~ VEE +35

Input Voltage

Output Voltage

OP-Amp output Current I

Operating Temperature T

Storage Temperature T

Output Control (ΦV2)

Output Control (ΦV1)

Output Control (ΦV1)

Output Control (ΦV3)

Output Control (ΦV3)

Output Control (ΦV4)

O High Voltage Output (2 level :VME, VEE)

O High Voltage Output ( 3 level : VME, VEE, VHH)

O High Voltage Output (3 level : VME, VEE, VHH)

O High Voltage Output (2 level : VME, VEE)

VEE 0 ~ -10

VME VEE -0.3 ~ 3.0 V

VI -0.3 ~ VHH +0.3

ΦV1, ΦV2, ΦV3, ΦV4, ΦVsub

VCP -0.3 ~ VEE+35

VEE -0.3 ~ VHH +0.3

±5

-25 ~ +85

-45 ~ +120

mA

°C

LOGIC FUNCTION TABLE

INPUT OUTPUT

XV1,3 XSG1,3 XV2,4 XSUB

L L - - VHH - H L - - Z - L H - - VME - H H - - VEE - -

- - L - - VME -

- - H - - VEE -

- - - L - - VHH

- - - H - - VEE

ΦV1, 3 ΦV2, 4

VSUB

KS7221D VERTICAL DRIVER FOR CCD

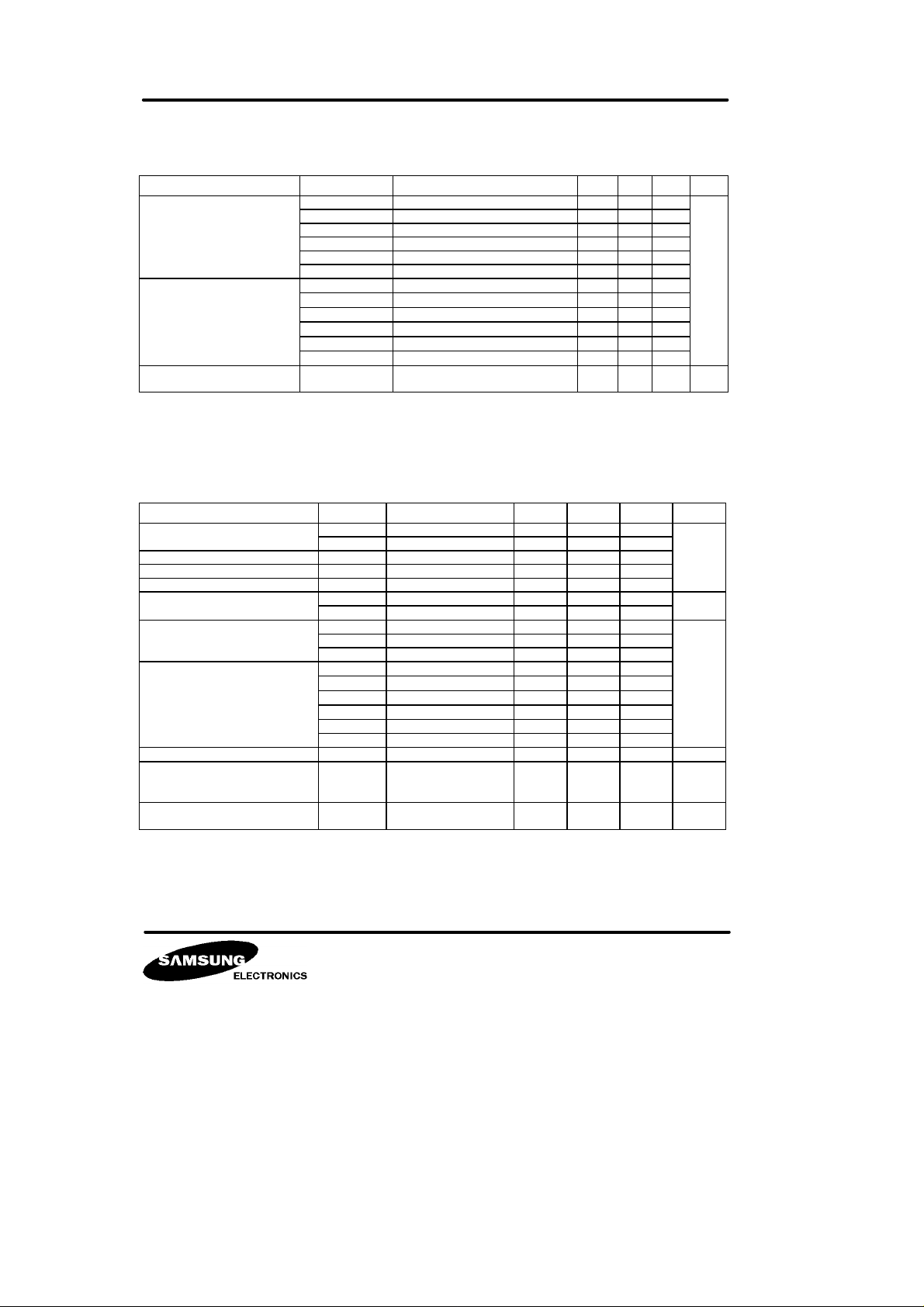

AC CHARACTERISTICS

( VHH = 15V, VME = GND, VEE = - 8.5V ; Ta = 25°C )

Description Symbol Test Condition Min Typ Max Unit

TPLM NO LOAD (*1) 10 40 70

DELAY TIME TPLH NO LOAD (*1) 10 40 100

RISING TIME TTML

OUTPUT NOISE

VOLTAGE

(*1) REFER TIMING DIAGRAM

(*2) REFER NOISE DIAGRAM

DC CHARACTERISTICS

( VHH = 15V, VME = GND, VEE = -8.5, VCP = 22V ; Ta = 25°C )

Description Symbol Test Conditon Min Typ Max Unit

Supply Voltage

Input Voltage VCP When VCP is used VHH 22 23.5 V

High level input voltage VIH (*3) 2.3 - Low level input voltage VIL (*3) - - 1.2

Input Current

Operation Current IME (*1) - 4.5 5.0

Output Current IOM2

Op-Amp Gain G

Gain Variation

Operation Current IVCP

TPMH NO LOAD (*1) 10 30 70

TPML NO LOAD (*1) 10 100 200

TPHM NO LOAD (*1) 10 100 180

TPHL NO LOAD (*1) 10 60 100

TTLM

TTMH

TTLH

TTHM

TTHL

VCLH, VCLL

VCMH, VCML

VHH 14.5 15 15.5

VEE -9.5 -8.5 -7.5

II VIN = 0~5V (*3) -1.0 0.0 1.0

IDCIN VDCIN = 1.0V 80 100 140

IHH (*1) - 2.0 3.5

IEE (*1) -8.5 -6.5 IOL

IOM1

IOH

IOSL VSUB = -8.0V 12 18 IOSH VSUB = 14.5V - -10.5 -7

∆G

VEE → VME (*1)

VME → VHH (*1)

VEE → VHH (*1)

VME → VEE (*1)

VHH → VME (*1)

VHH → VME (*1)

(*2) - - 0.5 V

ΦV1~4 = -8.0V

ΦV1~4 = -0.5V

ΦV1.3 = 0.5V

ΦV1.3 = 14.5V

IOUT = -200µA

Ta=-20 ~ 75°C (*2),

Iout=-200µAVDCIN = 1.0

~ 4.5V

VDCIN = 1.0 ~ 4.5V

IOUT = 0µA

25 37 -

- -15 -10 mA

9 13.5 -

- -18 -12

x 4.0 x 4.2 x 4.7

-3 - +3 %

0.08 - 1.0 mA

400 700 930 ns

400 650 930

10 50 100

200 300 500

400 600 820

10 50 100

µA

( * 1 ) : Refer the test cirect. Shutter speed : 1/100000 SEC

( * 2 ) : Refer the characteristics of OP - AMP

( * 3 ) : XV1 ~ 4, XSG1, XSG3, XSUB PIN

Loading...

Loading...