Samsung Geneva, NP-R700 Schematic

4

B

2

D

1

SAMSUNG PROPRIETARY

COM-22C-015(1996.6.5) REV. 3

C

3

A

D:/tingting/geneva/Geneva_pr_1023

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

Table of Contents

Table of Contents

Table of Contents

Table of Contents

Table of Contents

Table of Contents

Table of Contents

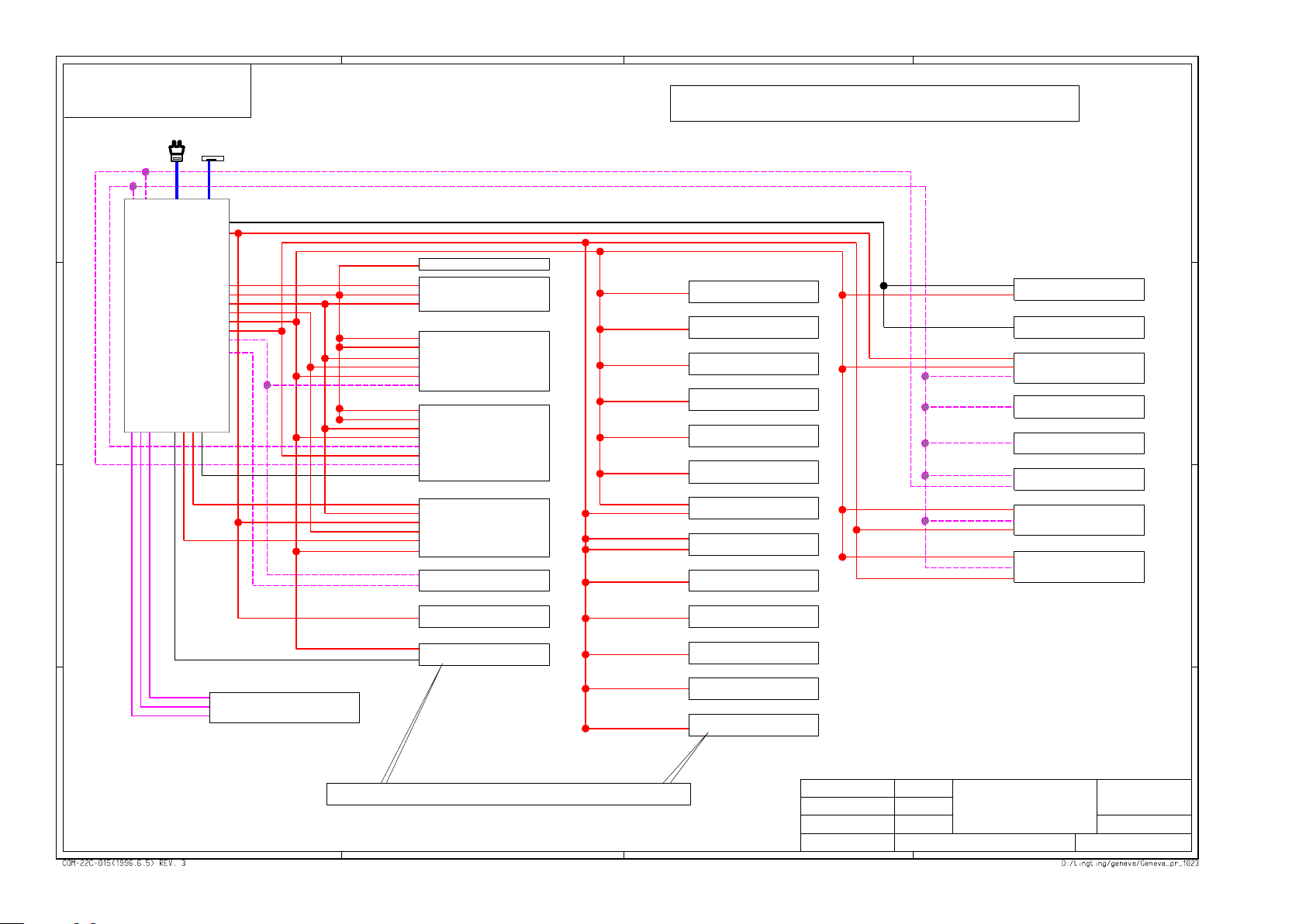

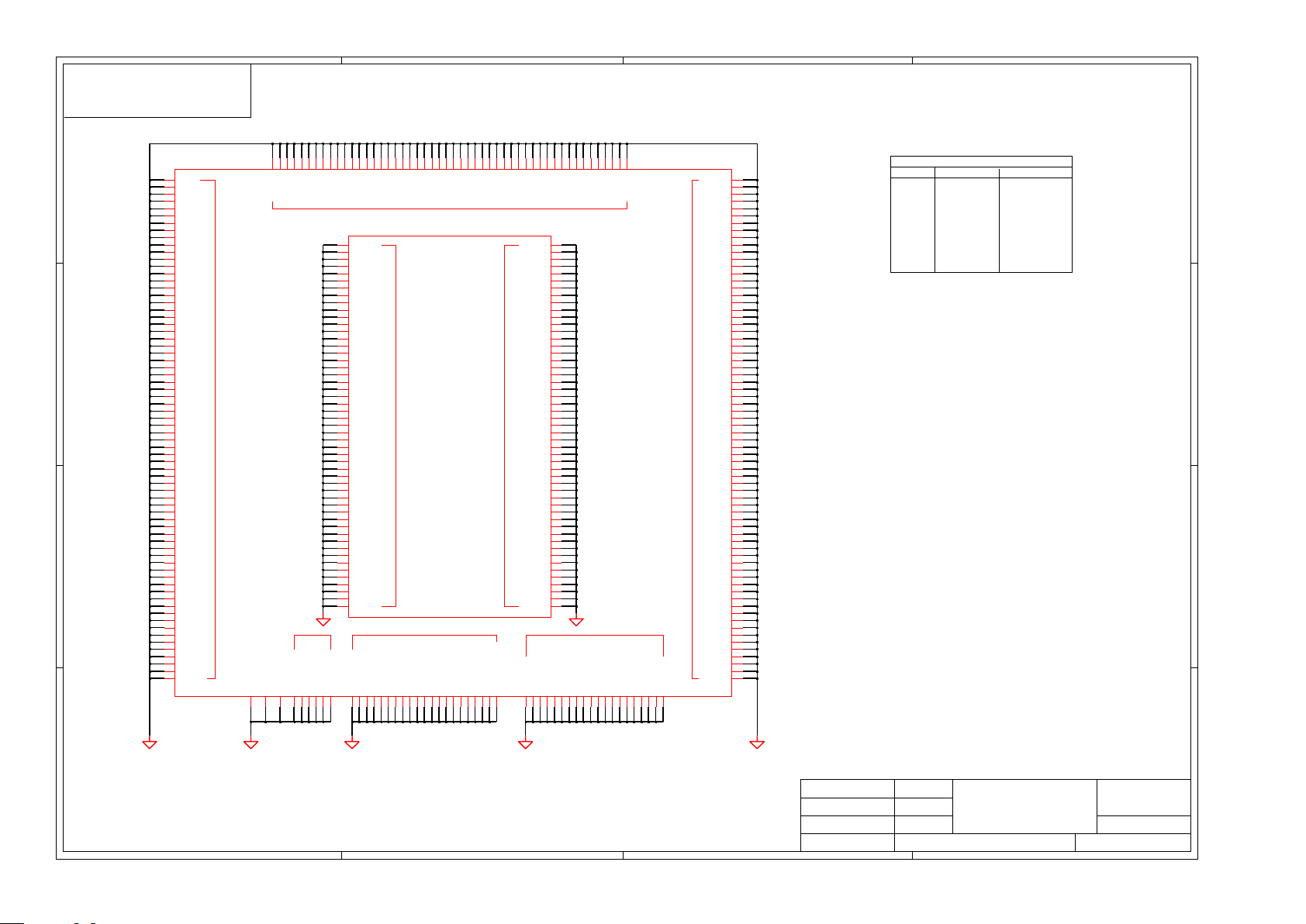

Sheet 1 Cover

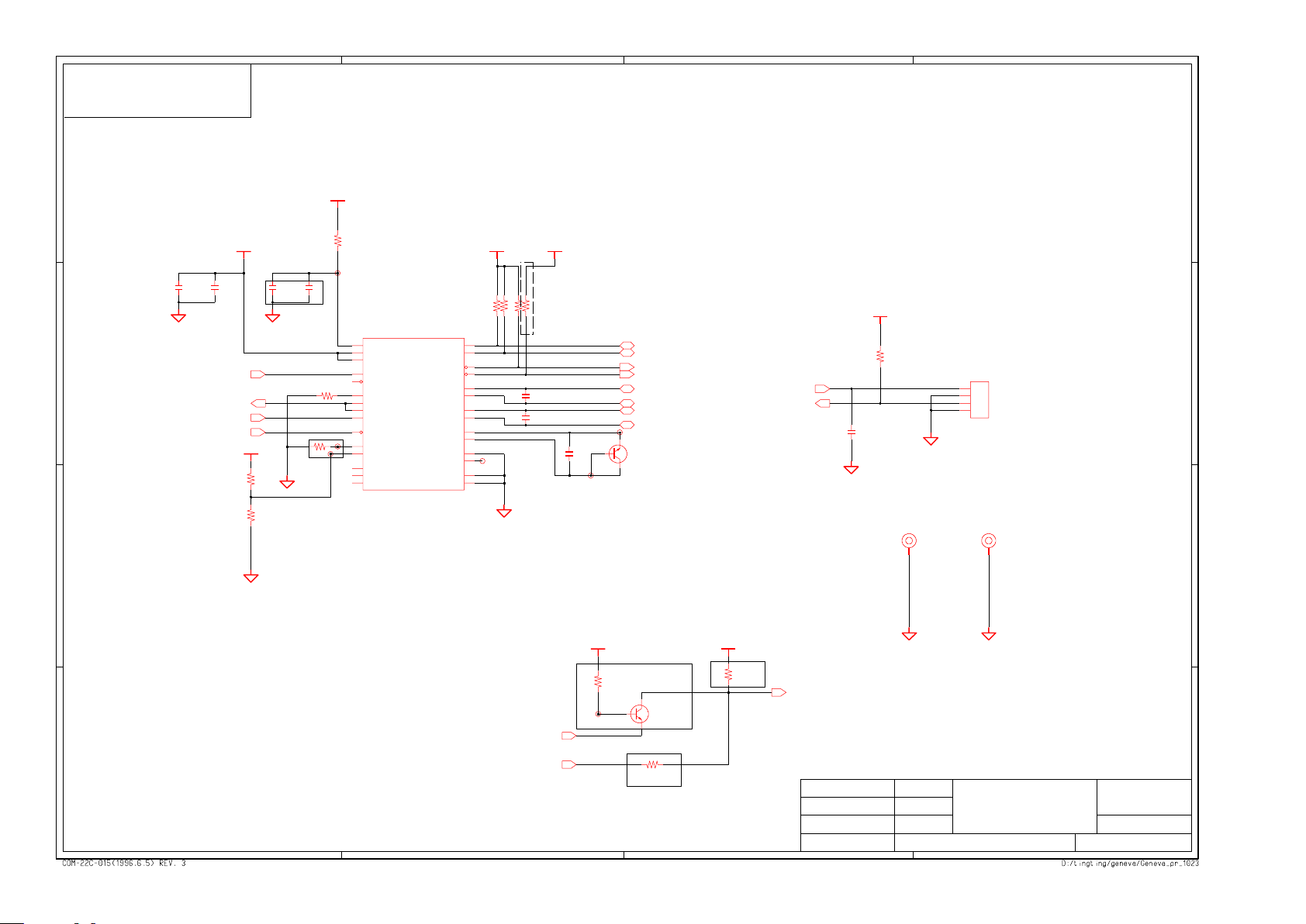

Sheet 2 Diagram (Block/Power) & Annotations

D

Sheet 8 Clock Generator

Sheet 9 Thermal Sensor & FAN

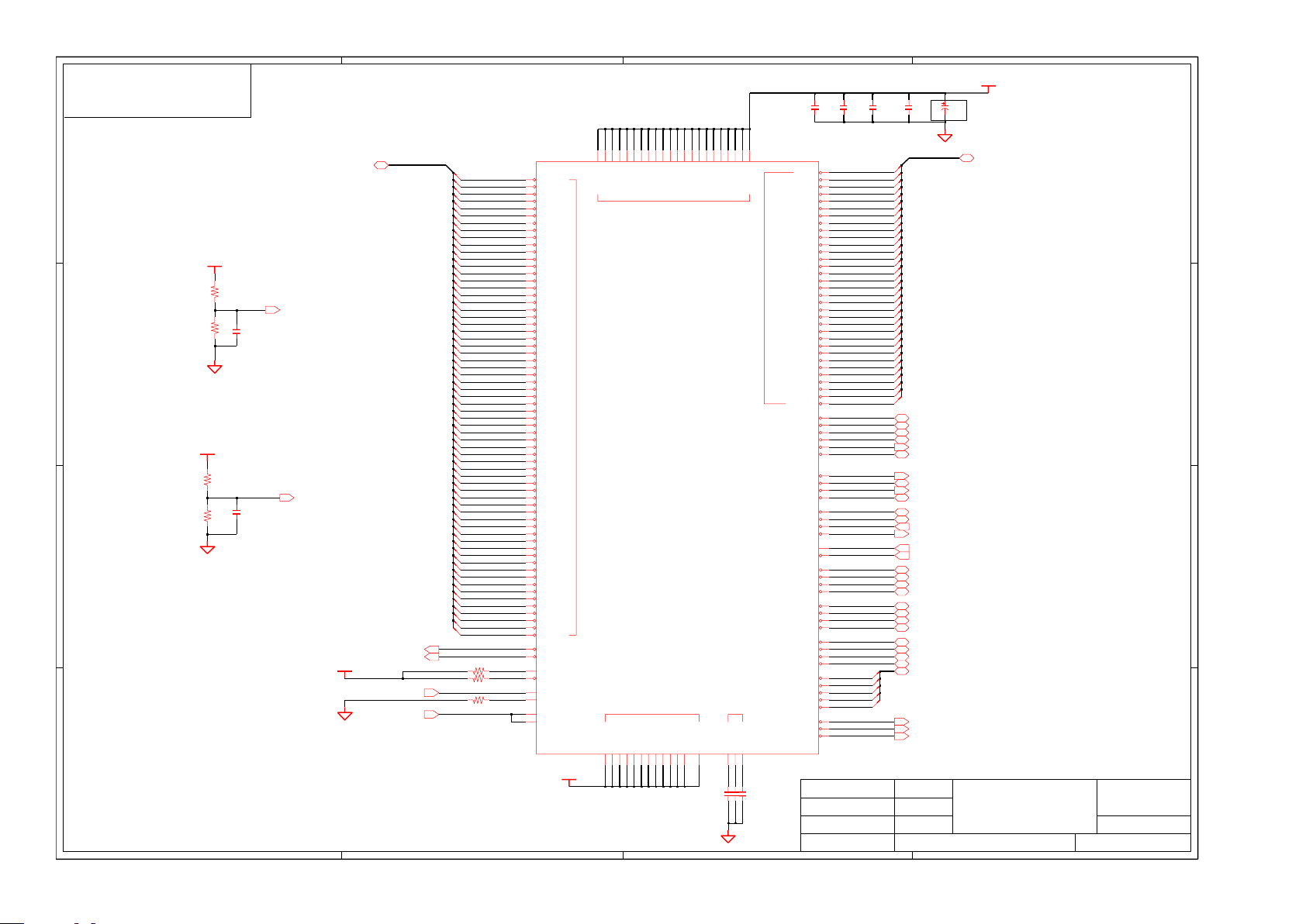

Sheet 10-12 Merom-4M CPU

Sheet 13-17 Crestline-GMCH

Sheet 18 DDR2 SODIMM A

GENEVA

Sheet 19 DDR2 SODIMM B

Sheet 20-23 ICH8-M

Sheet 24 ICH8-M STRAP

Sheet 25-28 NIVIDIA NB8P

Sheet 29 NIVIDIA NB8P STRAP

CPU :

Chip Set :

Remarks :

MEROM

SANTAROSA CHIPSET

Mobility Platform

Sheet 30 Video Memory Channel A

Sheet 31 Video Memory Channel B

Sheet 32 LCD and Camera Connector

Sheet 33 CRT PORT

Sheet 34 SIO CHIP and Connector

Sheet 35 7 IN 1 Card Reader

Sheet 36 MINI CARD AND ROBSON DVB-T

Sheet 37 Express card

C

Sheet 38 AUDIO - ALC262

Model Name :

PBA Name :

PCB Code :

Dev. Step :

Revision :

T.R. Date :

GENEVA

MAIN

BA41-XXXXX

PV2

Samsung

1.0

Sheet 39 AUDIO - AMP

Sheet 40 AUDIO - HEADPHONE & MIC JACK

Sheet 41 AUDIO - POWER

Sheet 42-43 LAN AND CONNECTOR

Sheet 44-45 MICOM AND MICOM POWER LOGIC

Sheet 46 POWER - SWITCH POWER

Sheet 47 POWER - VCCP P1.25V and P1.2V

Sheet 48 POWER - DDR2 POWER

Sheet 49 POWER - CHARGE & POWER MANAGEMENT

Sheet 50 POWER - P3.3V_ALW & P5V_AUX

Sheet 51 POWER - CPU VRM

Sheet 52 POWER - GFX CORE P1.5V

Sheet 53 HDD & ODD Connector

B

Sheet 54 USB/MDC/BLUETOOTH/TOUCHPAD

Sheet 55 KBD/LID SWITCH/80H/ICT/LED IF/USB /IF

DRAW

4

CHECK

APPROVAL

Confidential

3

Sheet 56

Sheet 57

Sheet 58

Sheet 59

Sheet 60

OTHERS

TOUCHPAD AND LED B’D

SIO AND USB B’D

TEST POINT

TEST POINT

DRAW

CHECK

APPROVAL

MODULE CODE

2

SUN XIAO

WUSHIJIANG

KEVIN LEE

DATE

DEV. STEP

REV

LAST EDIT

6/26/2007

TITLE

PV2

1.0

Gevena

MILAN

COVER

October 23, 2007 10:38:02 AM

1

SAMSUNG

ELECTRONICS

PART NO.

BA41-XXXXX

158

PAGE

A

OF

2

SAMSUNG PROPRIETARY

B

A

C

1

4

3

D

COM-22C-015(1996.6.5) REV. 3

D:/tingting/geneva/Geneva_pr_1023

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

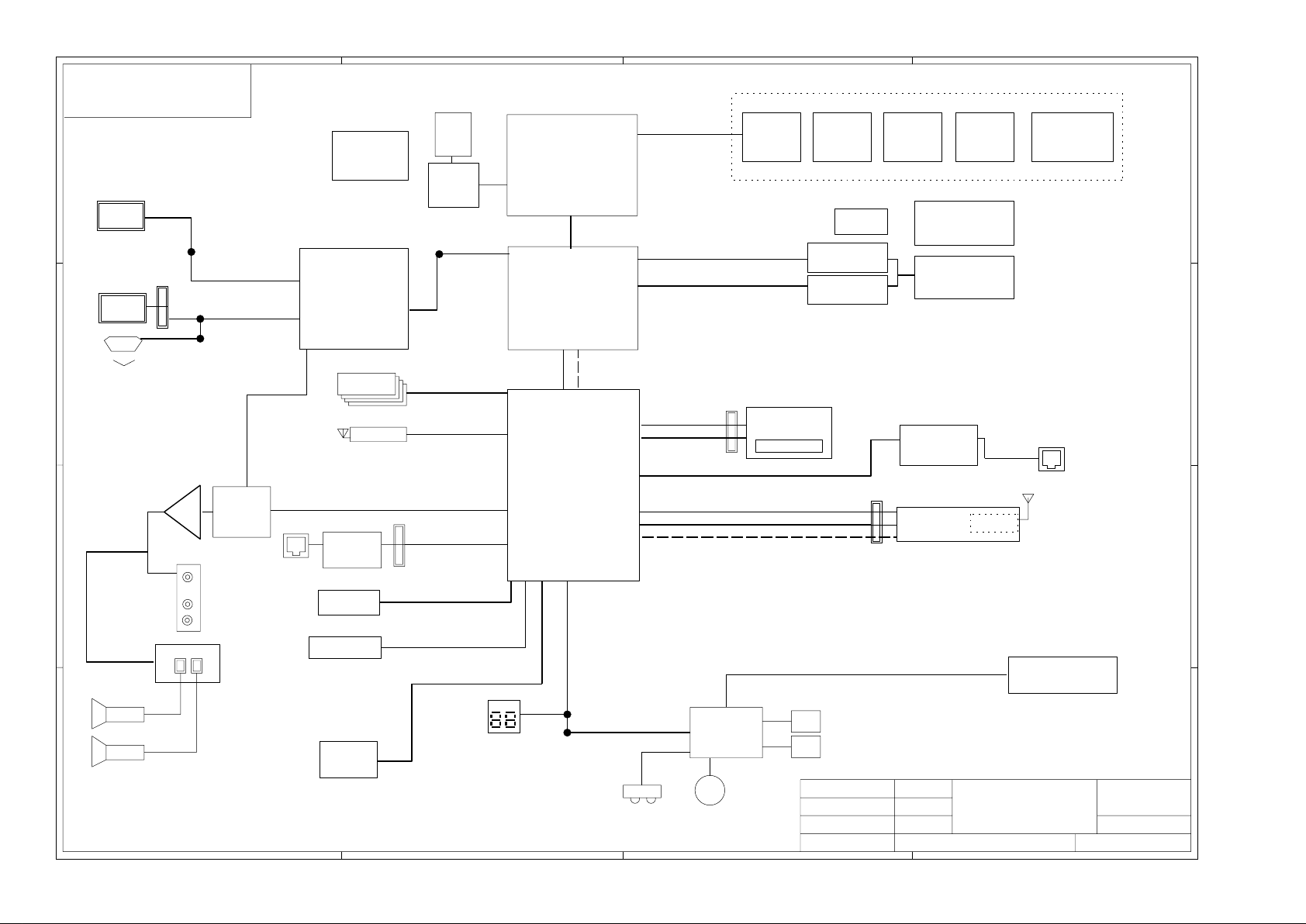

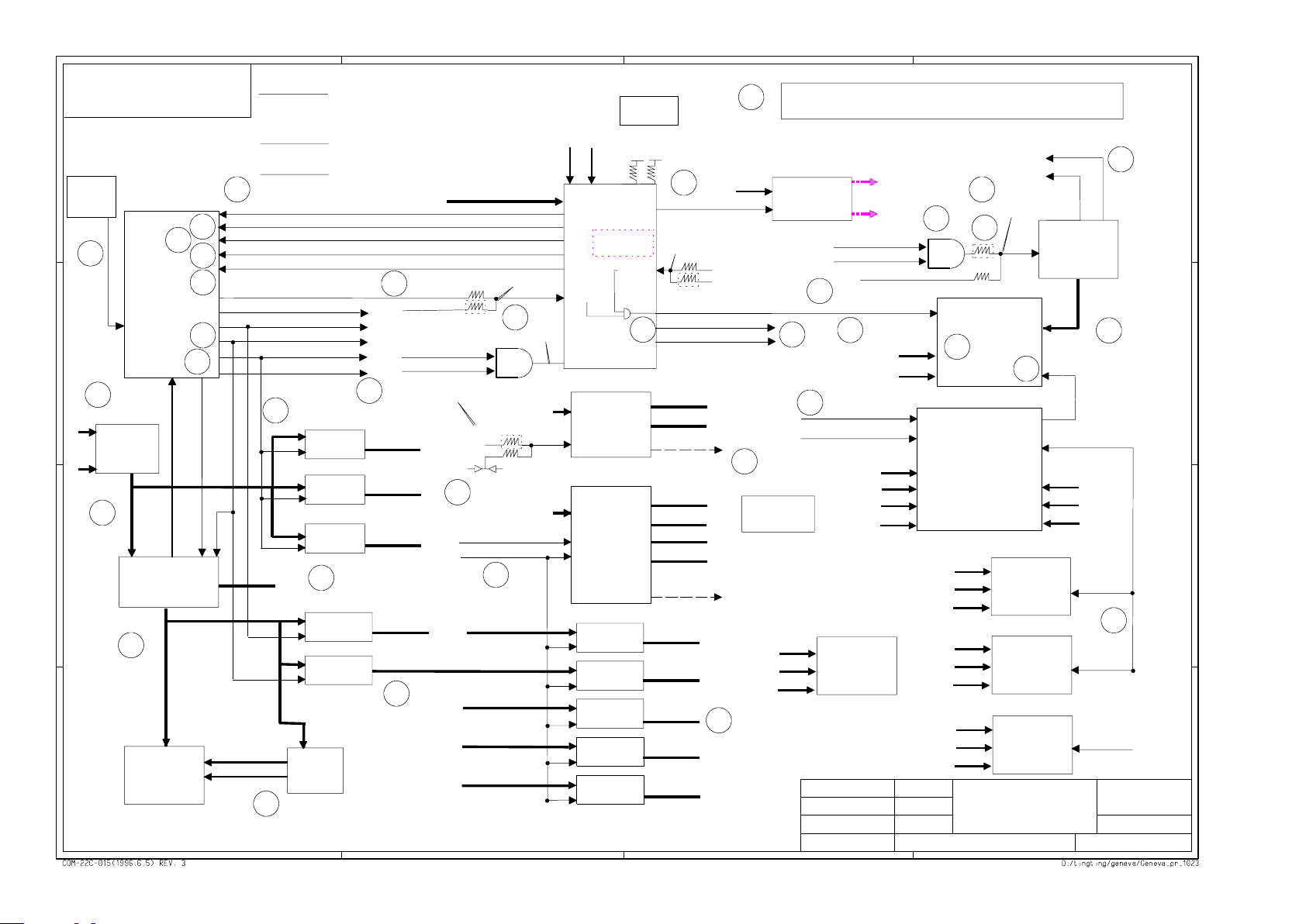

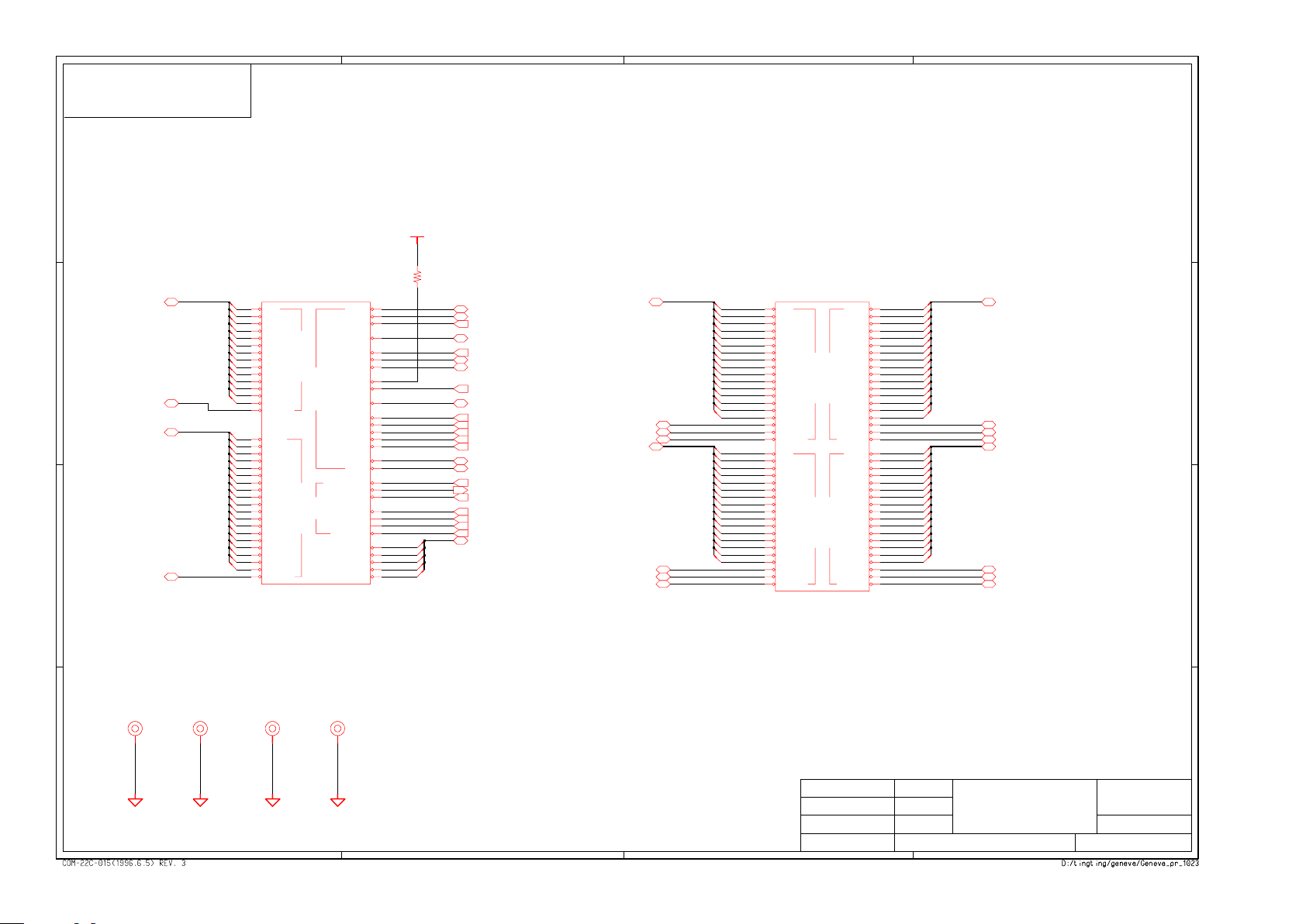

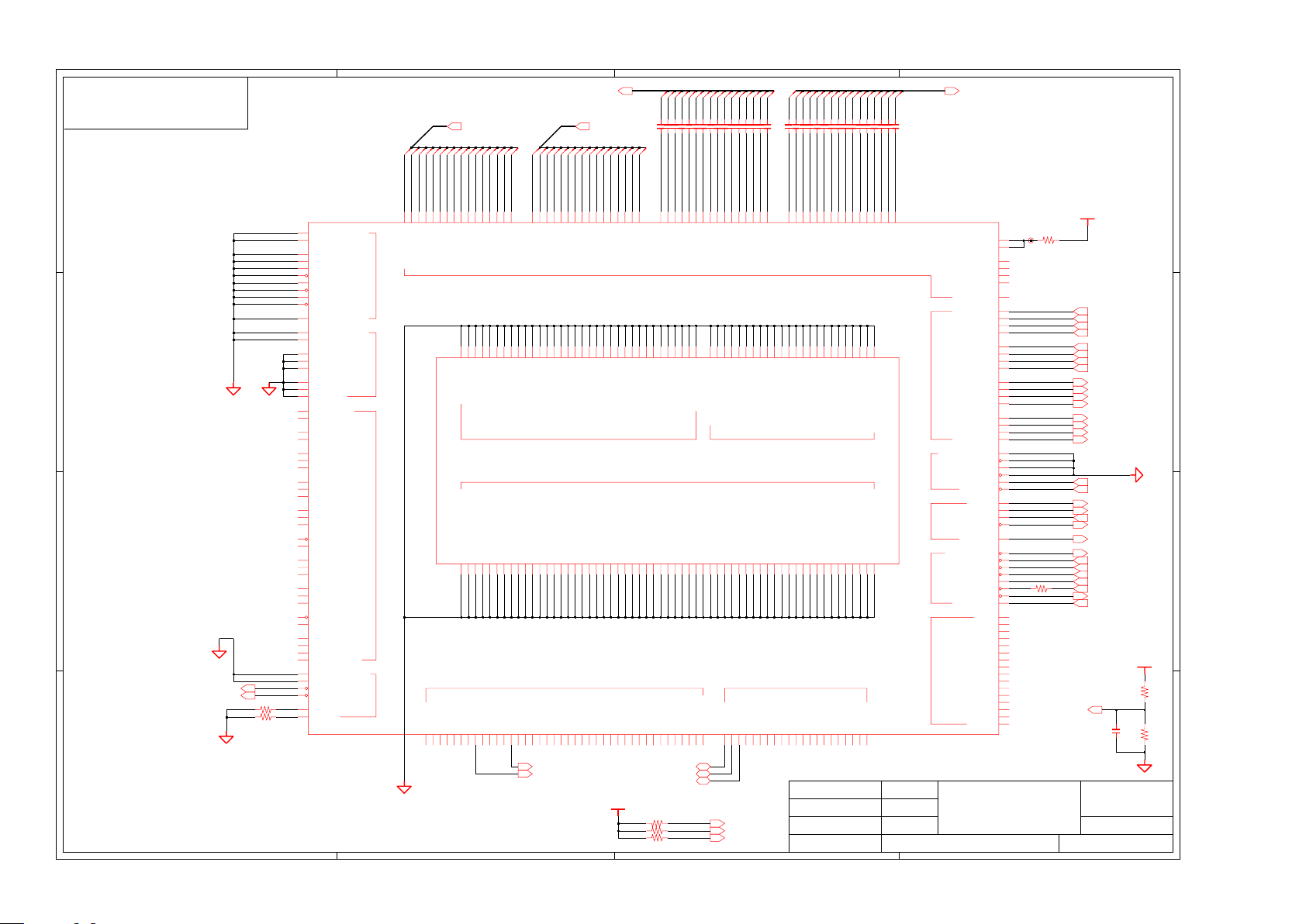

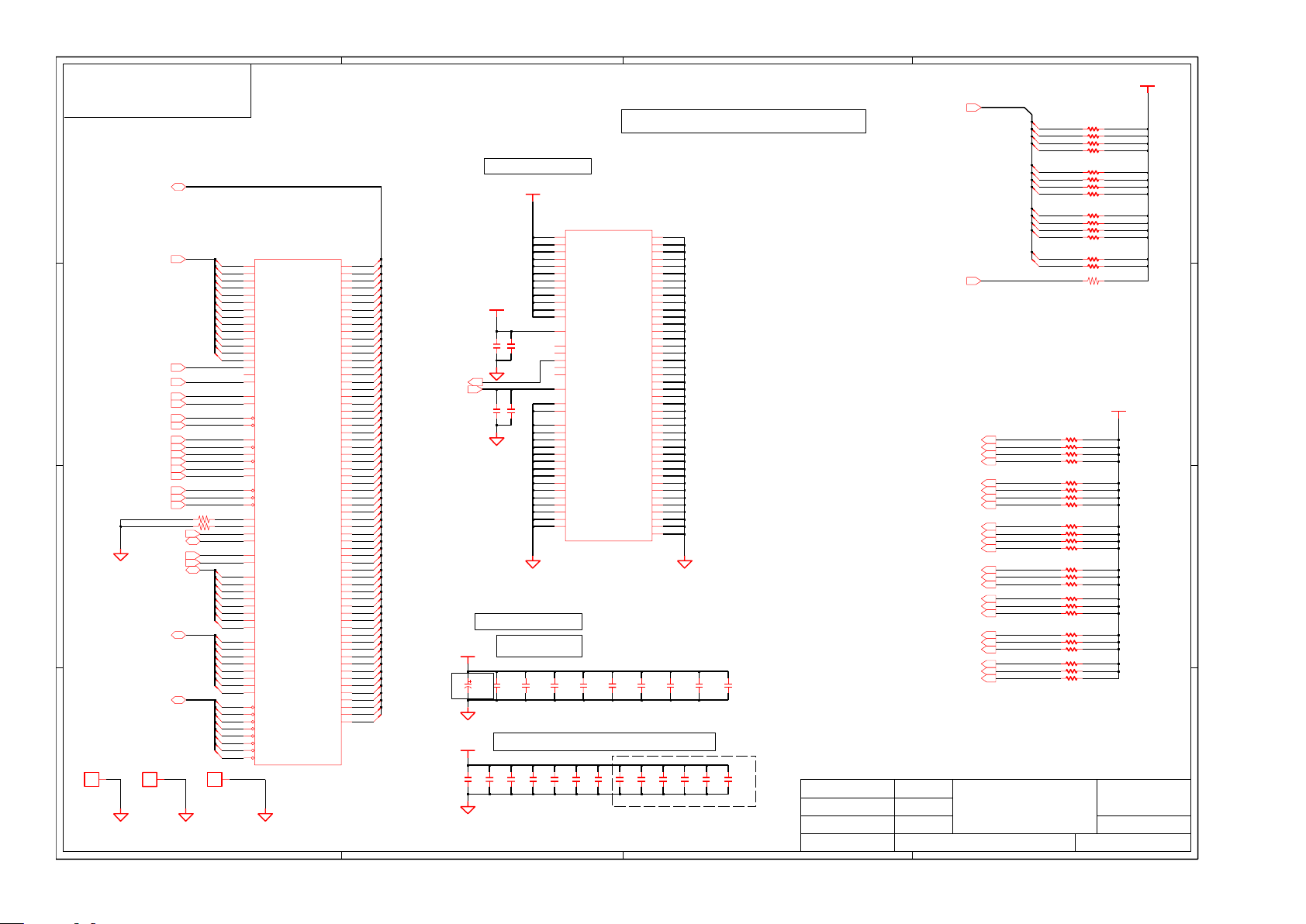

Clocking

CK-505

PG 8

PG 71

HDMI

Thermistor

FAN

PG 9

CPU

(TBD)

PG 9

Mobile Processor

Merom-4M

(800MHz)

478pin

PG 10,11,12

L2 Cache : 4 MB

FSB

800 MT/S

Channel A (Standard)

GMCH-M

NVIDIA

RJ11

PG 43

PG 22

NB8P / M

PG 25-29

PG 54

PG 55

Modem

SPI ROM

SATA

USB 0,1,2,3

ANT

Bluetooth

MDC

PG 54

HDD

Direct Media Interface

USB 0,1,2,3

USB 5

HD Primary

12P

HD Secondary

Samsung

SATA 0

PATA

PG 32

LCD

PG 33

CRT

High Definition Audio

30PIN

SVHS / RCA

Component

Aud.

AMP

PG 39

LCD/CRT/TV

HDAUDIO

Audio

ALC262

PG 38

PG 40

HEADPHONE

MIC-IN

2P

2P

PG 53

Confidential

SPKR R

SPKR L

4

PG 53

CD-ROM

CD / DVD

PG 55

Pri. IDE slave

3

SPI

80 Port

Crestline-GM

(TBD)

1299 FCBGA

PG 13 - 17

x4, 1.5V

CLINK

ICH8-M

676 BGA

PG 20 - 24

LPC

3.3V LPC, 33MHz

Channel B (Reverse)

PCIE x1

GLCI (Lane5)

LCI

PCIE x1

USB 4

CLINK

FIR(CIR)

PG 54

Dual channel

Lane 0

Lane 1

PG 51

ON BOARD

DDR II 667/533,400

DDR II 667/533,400

52P

MICOM

HD64F2169/2160

TMKBC (TBD)

LED

PG 45

CPU

DC/DC

IMVP-6

PG 51

PG 37

MINI CARD

ROBSON

DVB-T OPTION

2

Charging

Circuit

PG 49

Termination

PG 18,19

DDR II

SODIMM 0

DDR II

SODIMM 1

82566Mx (Nineveh)

82562V

Touch

PG 55

PAD

KBD

PG 55

DRAW

CHECK

APPROVAL

MODULE CODE

PG 18

PG 19

52P

SUN XIAO

WUSHIJIANG

KEVIN LEE

Smart

Battery

Module

PG 49

VCCP / DC-DC

DDR II Power

Marvell

8E8055(GLAN)

PG 42

Mini Card

PG 37

DATE

6/26/2007

DEV. STEP

PV2

REV

LAST EDIT

1.0

DC/DC

46

PG 47

PG 48

TITLE

OPTION

ANT

Kedron

MIO_BUTTON

Gevena

BLOCK DIAGRAM

October 23, 2007 10:38:02 AM

IGFX / EGFX

CORE

PG 52

RJ45

PG 43

PAGE

1

SAMSUNG

ELECTRONICS

PART NO.

BA41-XXXXX

OF

D

C

B

A

582

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

4

3

2

1

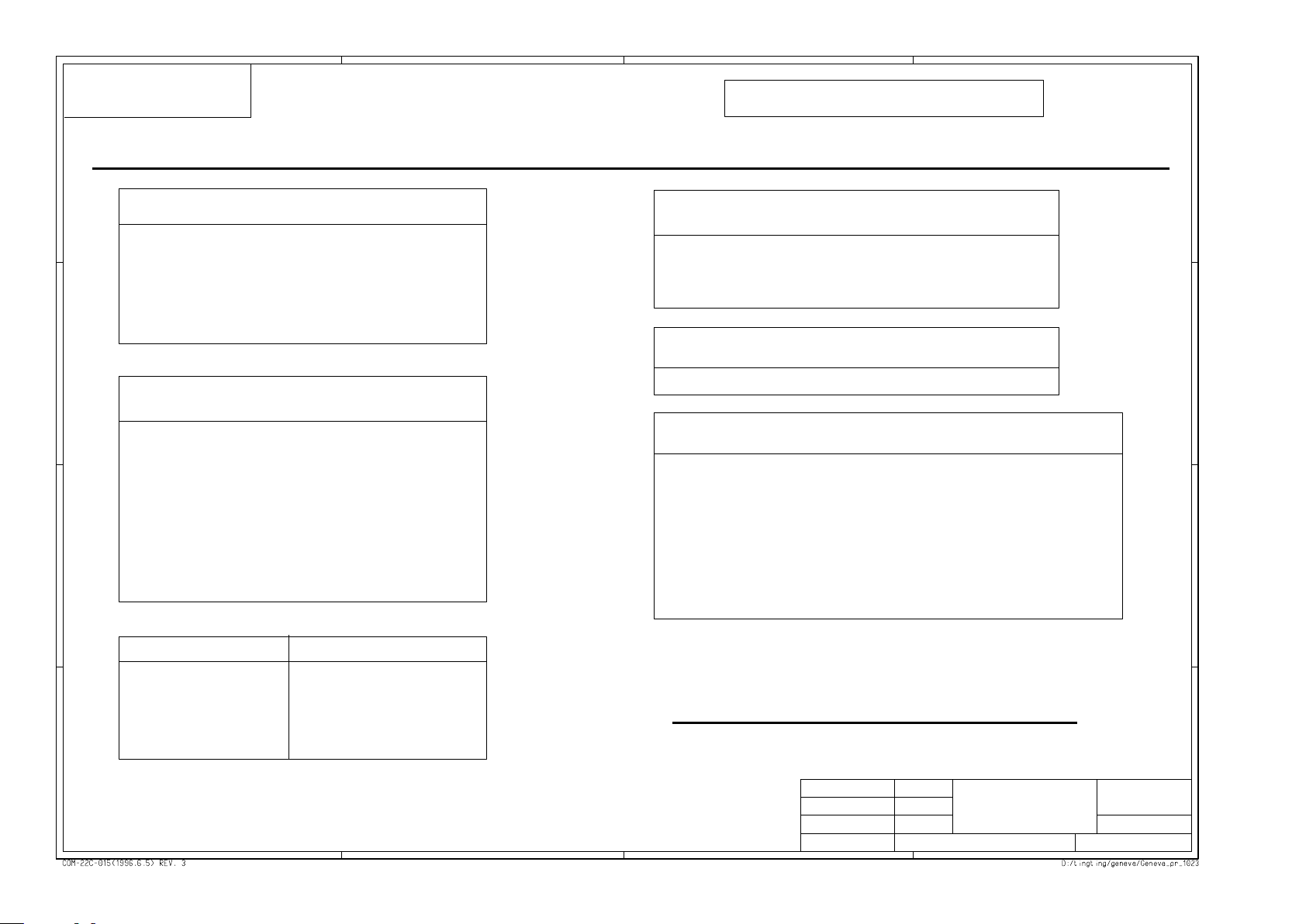

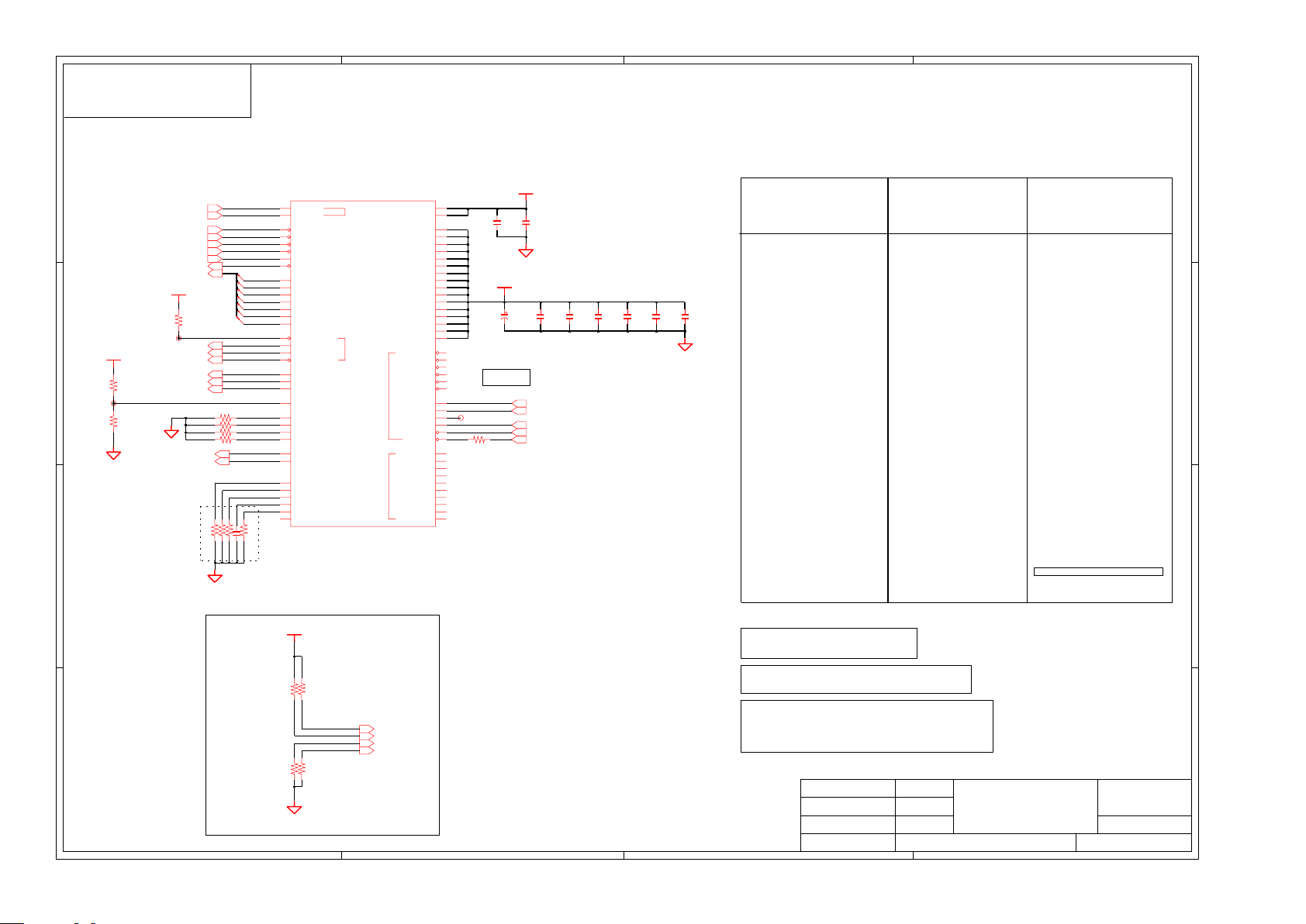

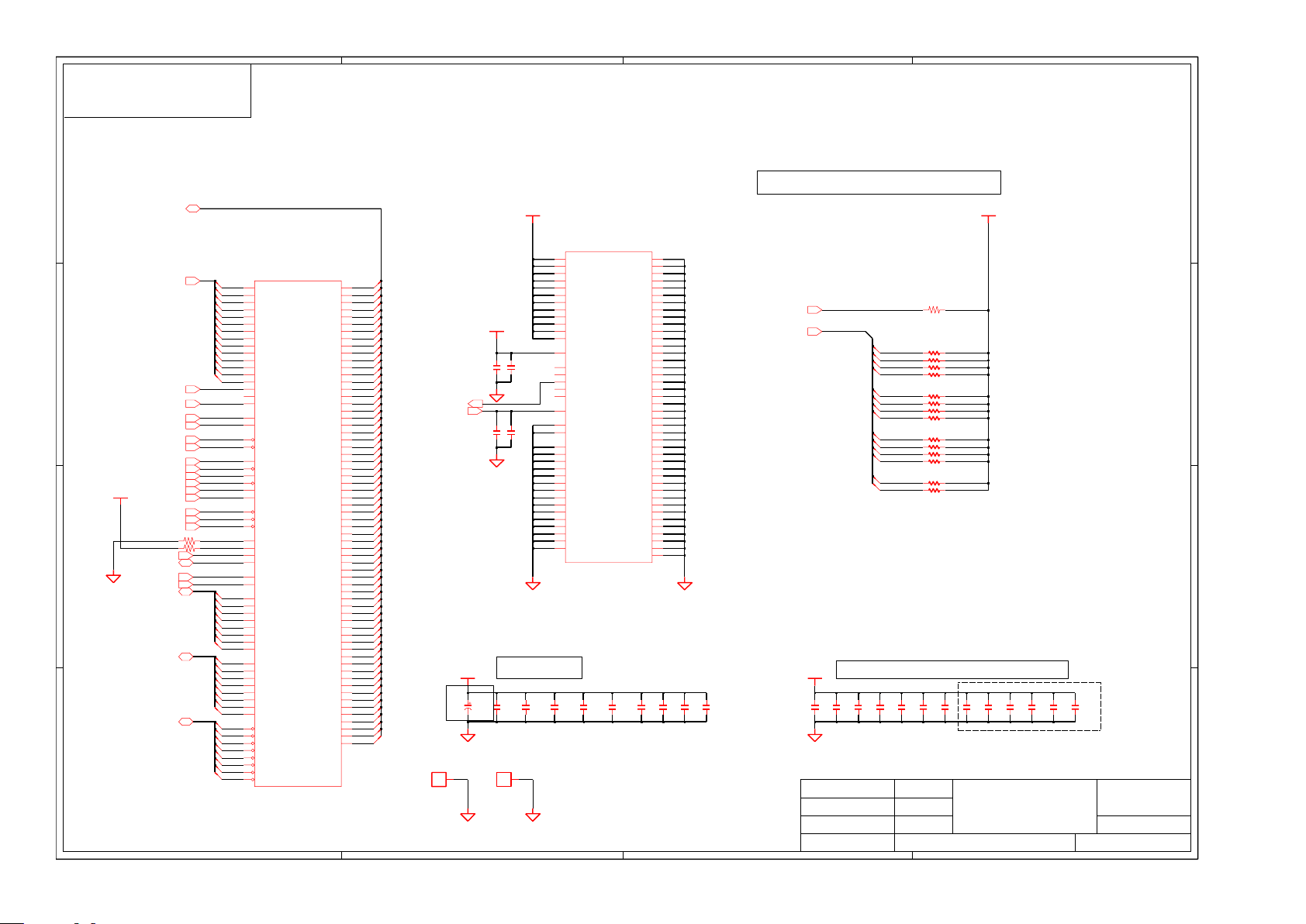

BOARD INFORMATION

SCHEMATIC ANNOTATIONS AND BOARD INFORMATION

D

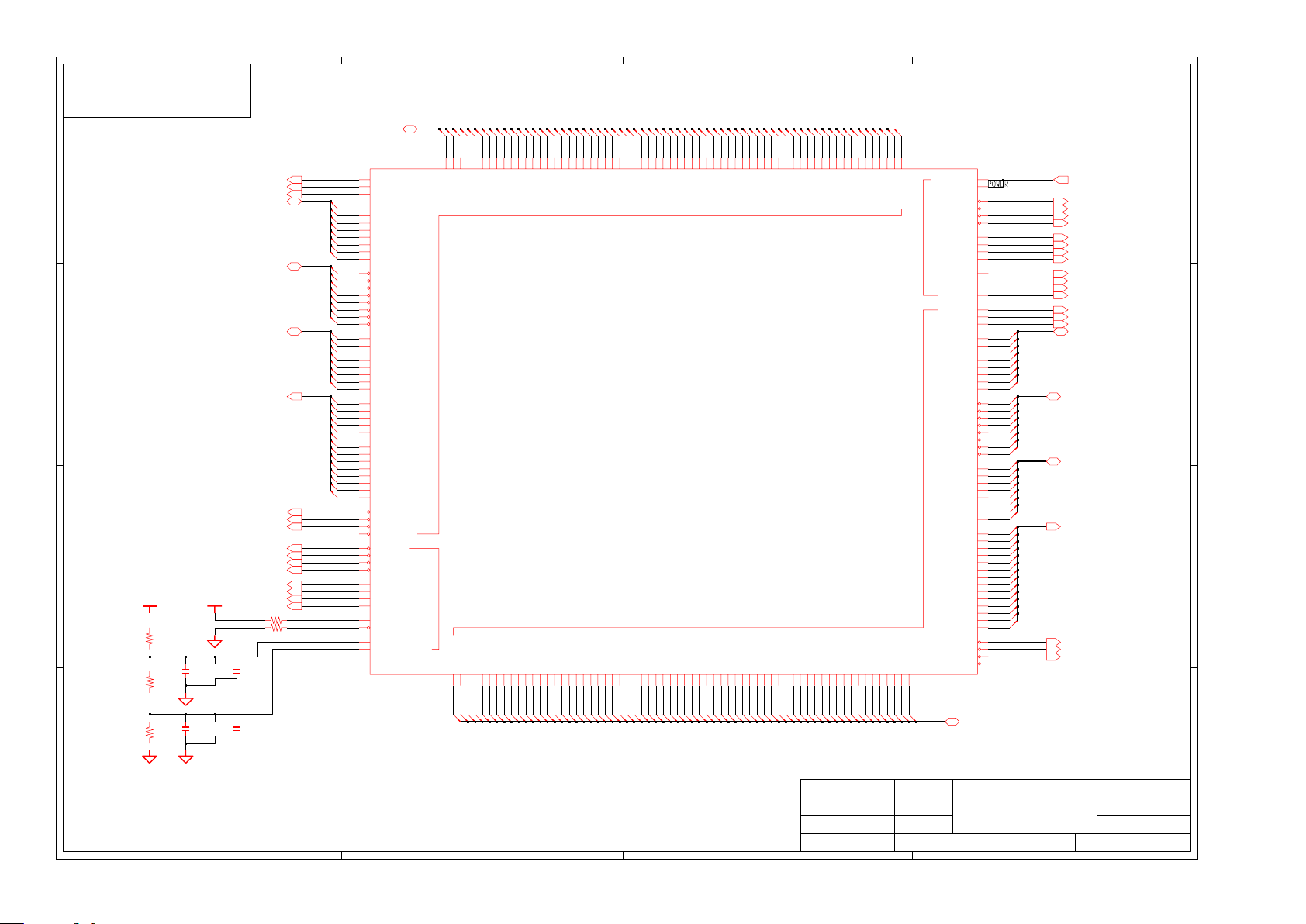

PCI Devices

Devices

Cardbus

MiniPCI SLOT

USB

Hub to PCI

LPC bridge/IDE/AC97/SMBUS

Internal MAC

AC Link

GLAN -

IDSEL#

AD25

AD22DT PCI SLOT

AD23

AD29(internal)

AD30(internal)

AD31(internal)

AD24(internal)

-

-

REQ/GNT#

3

1

2 A,B

-

-

-

-

C

Interrupts

B,C,D

B,C,D,C

USB2.0 #0 (USB0) : A

USB2.0 #1 (USB1) : D

USB2.0 #2 (USB4) : C

USB2.0 #3 (USB5) : E

USB2.0 #4 (EHCI) : H

B

E

BF

Voltage Rails

VDC

VCC_CORE

MCH_CORE Core Voltage for CPU

ICH_CORE

P1.05V (VCCP)

P1.25V_M

P3.3V_M

P3.3V_A

MICOM_P3V

P1.5V

P1.5V_AUX

P2.5V

P1.8V_AUX

P0.9V

B

P3.3V

P3.3V_AUX

P5V

P5V_AUX

Primary DC system power supply (7 to 21V)

Core Voltage for CPU

Core Voltage for CPU

VTT for CPU, Crestline & ICH8-M

1.05V switched power rail for ME (on in M0/M1)P1.05V_M

1.25V switched power rail for ME (on in M0/M1)

3.3V switched power rail for ME (on in M0/M1)

3.3V always power rail (by KBC3_ALWS_ON)

3.3V always power rail (for Micom)

3.3V always power rail (for LAN)LAN_3.3V

1.5V switched off power rail (off in S3-S5)

1.5V switched on power rail

2.5V switched off power rail (off in S3-S5)

1.8V switched off power rail (off in S3-S5)P1.8V

1.8V power rail for DDR

0.9V power rail for DDR

3.3V switched off power rail (off in S3-S5)

3.3V switched on power rail

5.0V switched off power rail (off in S3-S5)

5.0V switched on power rail

Samsung

Crystal / Oscillator

TYPE

Crystal

Crystal

Crystal

Crystal

Crystal

Crystal

Crystal

FREQUENCY

32.768KHz

10MHz HD64F2169/2160

14.318MHz CK-505

24.576MHz 1394

25MHz

27MHz (TBD)

24.576MHz (TBD)

LCD Pannel Detect

Devices

2

I C / SMB Address

Devices

ICH8-m

CPU Thermal Sensor

SODIMM0

SODIMM1

Thermal Sensor on SODIMM0

Thermal Sensor on SODIMM1

CK-505M (Clock Generator) 1101 001x

DB400 (PCI Express Clocks)

TBD

TBD : (ALS)

TBD : (AUX DISPLAY)

LAN

TPM

Resolution

Address

Master

1001 110x

1010 000x

1010 010x

0011 000x

0011 010x

1101 110x

0100 1100 Thermal Sensor

0101 1000

0111 0010

0011 110x

1100 1000 82566

TBD

TBD

(TBD)

DEVICE

ICH8-M

MICOM

CLOCK-Generator

Cardbus Controller

LAN

VIDEO

HD Audio

Hex

9Ch

A0h

A4h

30h

34h

D2h

DCh

4Ch

58h

72h

3Ch

C8h

TBD

TBD

USAGE

Real Time Clock

Intel LAN

PEG

Audio

PANNEL_DETECT_0

Bus

SMBUS Master

Thermal Sensor

-

-

-

Clock, Unused Clock Output Disable

Clock Buffer for PCI Express

-TBD : (LVDS BackLight Inverter)

Ambient Light Sensor

EMA

TBDPCI Express Docking

TBD

D

C

B

USB PORT Assign

PORT # ASSIGNED TO

0

SYSTEM PORT 0

SYSTEM PORT 11

DMB

2

3

Expresas Card

DOCKING PORT 0

4

Bluetooth

5

Mini PCI Express

6

7

Aux Display

8

Test Port (RSVD)

9

WWAN/WIBRO (TBD)

A

4

PCI Express Assign

ASSIGNED TO

PORT #

0

PCIE x1 Slot

Mini Card (Golan)

1

Mini Card (WIBRO : RSVD)

2

Expresas Card

3

DOCKING PORT 0

4

5 GLAN

Confidential

REVISION HISTORY

See rev notes for more information.

DRAW

CHECK

APPROVAL

MODULE CODE

3

2

SUN XIAO

WUSHIJIANG

KEVIN LEE

DATE

DEV. STEP

REV

LAST EDIT

6/26/2007

TITLE

Gevena

PV2

1.0

BOARD INFO

October 23, 2007 10:38:02 AM

1

SAMSUNG

ELECTRONICS

PART NO.

BA41-XXXXX

358

PAGE

A

OF

HDD

M_PCI

FAN CIRCUIT

AUX DISPLAY

VCCA

P1.5V

Thermal Sensor

SODIMM

FWH

PCMCIA

LEDs

Gevena

1

KBC3_VRON

CPU_CORE

R5C843

PEG

MEROM

MICOM

M_PCI

TPM

LCD

ATI (TBD)

nVidia (TBD)

CRESTLINE

PAGE OF

1

MEROM

SAMSUNG

ELECTRONICS

BA41-XXXXX

584

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

D

4

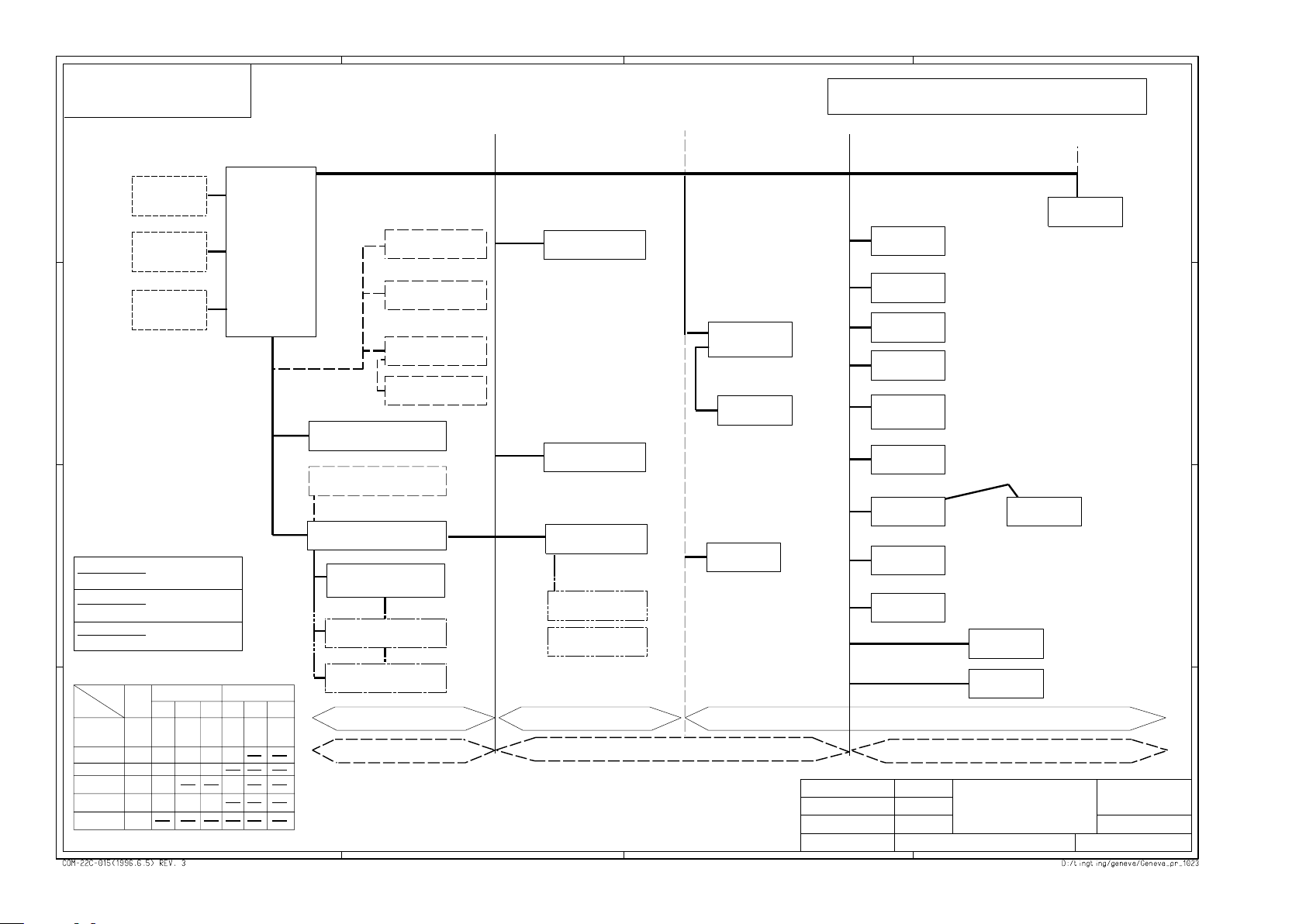

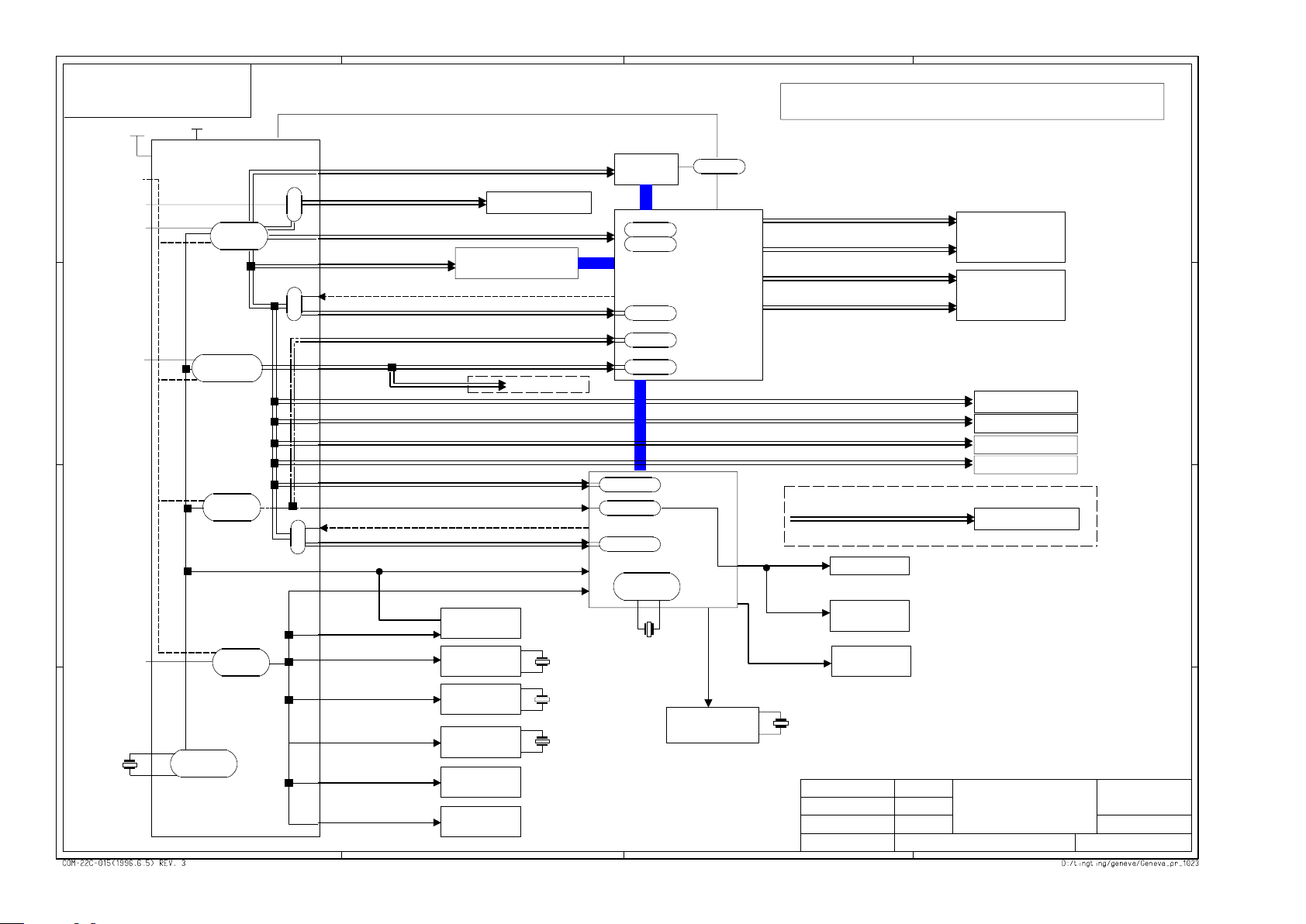

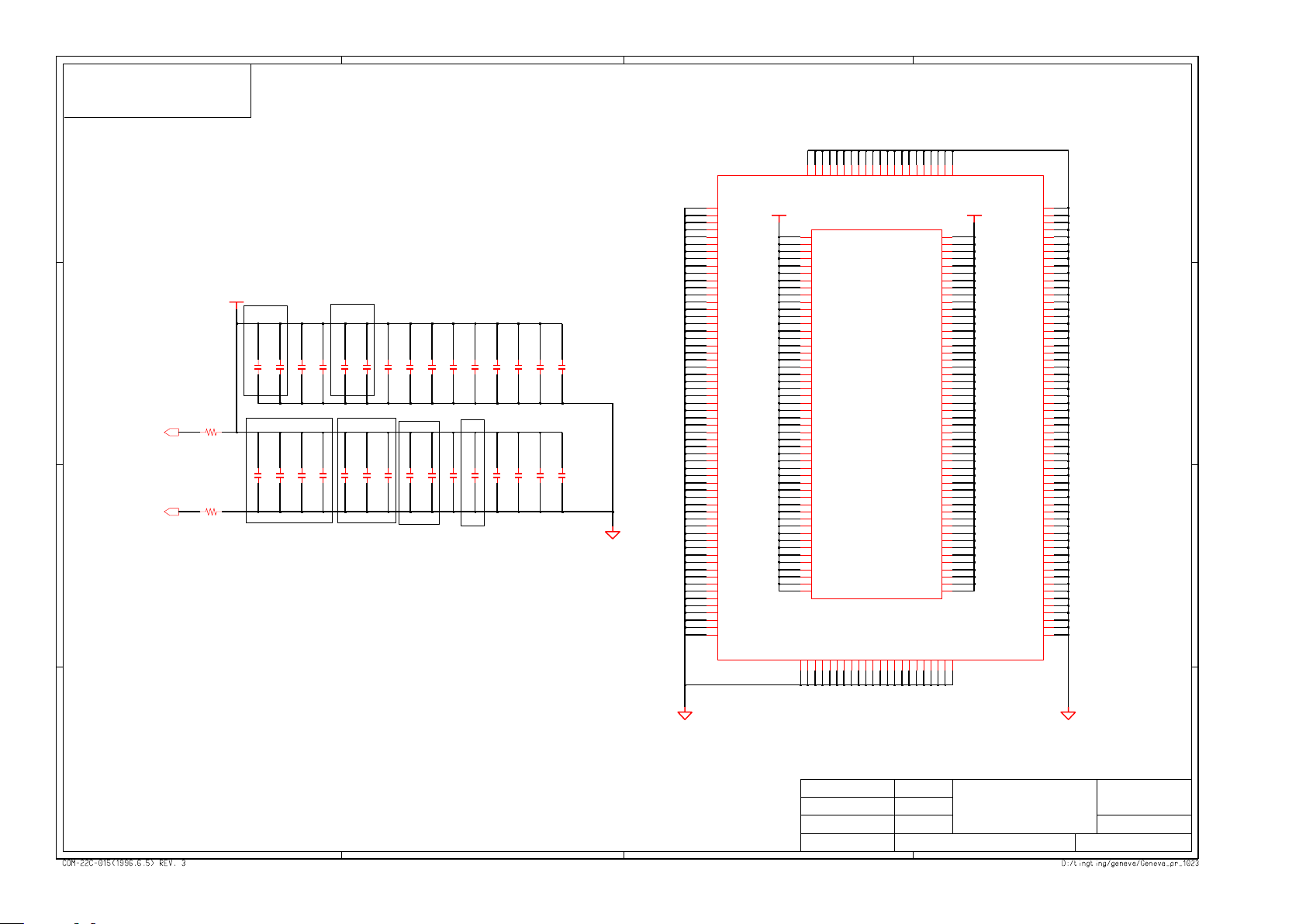

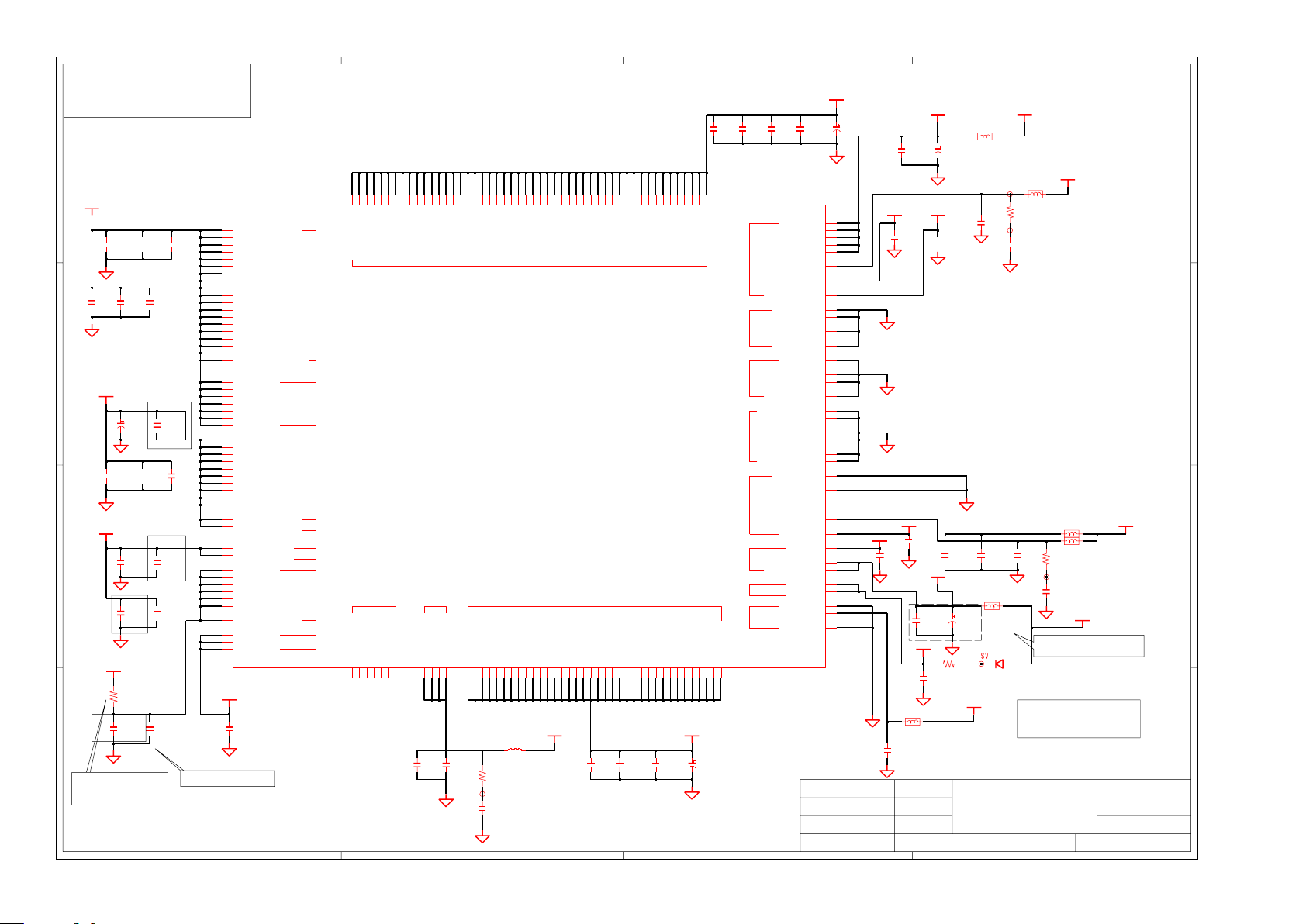

AC Adapter

DOCK DC

VDC

KBC3_ALWS_ON

KBC3_MEPWRON

(CHP3_SLPM*)

ME ENABLE

(CHP3_S4_STATE*) or

: KBC3_DDRPWRON (CHP3_SLPS4*)

(CHP3_SLPM*)

P1.8V_AUX (ME)

3

SODIMM (DDR II)

CRESTLINE

KBC3_SUSPWR

(CHP3_S4_STATE*)

ME OPTION

P1.8V_AUX

SODIMM (DDR II)

CRESTLINE

P0.9 (ME)

Battery DC

C C

DDR II-Termination

DDR II for PEG (TBD)

P1.25V_M

CRESTLINE

P1.05V_M

CRESTLINE

MICOM_P3V

MICOM

P5V_AUX

2

KBC3_MEPWRON

(CHP3_SLPM*)

ME DISABLE

P1.25V_M

CRESTLINE

P1.05V_M

CRESTLINE

POWER DIAGRAM

KBC3_PWRON

(CHP3_SLPS3*)

P1.8V

P0.9V

ME OPTION

P1.25V

P1.2V

P1.05V

(VCCP)

P5V

PEG

GDDR-3 for PEG

DDR II-Termination

DDR II for PEG (TBD)

CRESTLINE

ICH8-M

R5C843

PEG

nVidia

MEROM

CRESTLINE

ICH8-M

PCMCIA

ICH8-M

USB

FDD

HEATSINK

CRT

MDC

MICOM

P3.3V_M

CK505

SPI

ICH

Power Sequence by ME On/Off

B

Host Boot / ME Off

(SLPS4* = S4_STATE*) > (SLPM* = SLPS3*)

Host / ME Boot

(SLPS4* = S4_STATE*) > SLPM* > SLPS3*

Host S5 / ME Boot

(SLPS4* = SLPM*) > S4_STATE* > SLPS3*

Power On/Off Table by S-state

Rail

M0

+0.9V

+V* M

S0

ON

ON

ON ON

ON

ON

ON

State

+V*A(LWS)

+V*LAN

+1.8V_AUX

A A

+V*AUX

+V* (CORE)

M1

S3

S4

ON

ON

ON

ON

ON

ON

ON ON ON

4

M off

S4ONS5

S5

S3

ON

ON

ON

ON

ON

ON

ON

P3.3V_LAN

P3.3V_WLL

P1.8V_LAN

P1.0V_LAN

S5-S3/Moff-M0

Samsung

ICH8-M

ICH8-M

LAN

LAN

LAN

INT_VRM_LAN

Confidential

S5-S3

3

P3.3V_ALW

P3.3V_AUX

P3.3V_M

CRESTLINE

CK505

SPI

P1.05V_AUX

P1.5V_AUX

INT_VR_ICH

ICH8-M

ICH8-M

LAN

MDC

BT

S3- S0 S0

S4-S3/M1-M0

DRAW

CHECK

APPROVAL

MODULE CODE

2

P1.5V

P3.3V

P2.5V

VTT3_PWRGD

MCH3_GFX_VR_EN

DATE

SUN XIAO

DEV. STEP

WUSHIJIANG

REV PART NO.

KEVIN LEE

LAST EDIT

6/26/2007

PV2

1.0

CRESTLINE

ICH8-M

CRESTLINE

ICH8-M

SUPER I/O

PEG

MDC

CRESTLINE

ICH8-M

R5C843

PEG

TITLE

EGFX_CORE

IGFX_CPRE

S0/M0

POWER DIAGRAM

October 23, 2007 10:38:02 AM

D

B

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

4

3

2

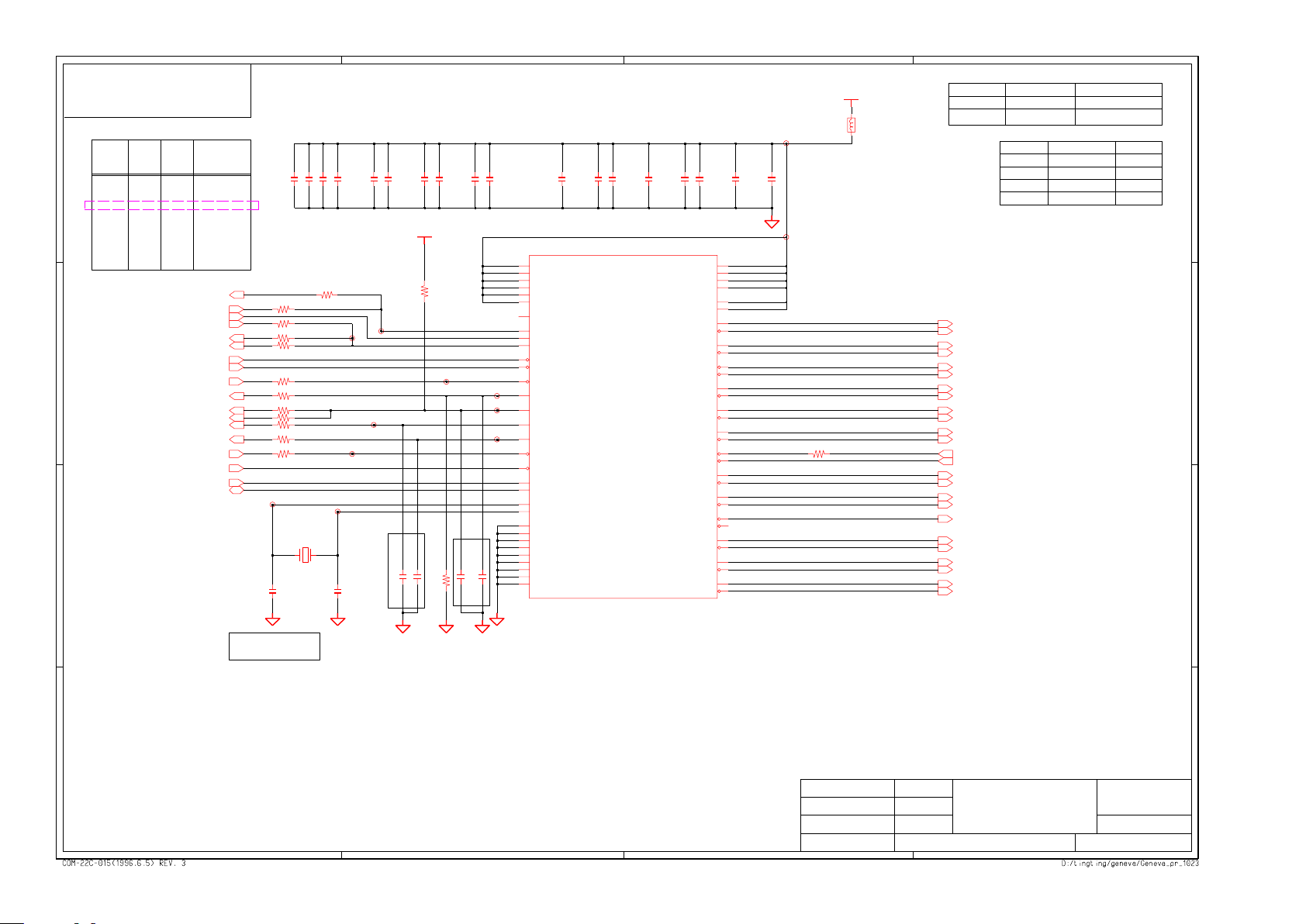

POWER RAILS ANALYSIS

1

Rev. 0.5

D D

C

B

220V

Adapter

MICOM 3V ( TBD A )

1.8V ( TBD A )

5V_AUX ( TBD A )

3.3V_AUX ( TBD A )

CPU CORE ( TBD A )

1.05V ( TBD A )

1.5V ( TBD A )

2.5V ( TBD A )

3.3V ( TBD A )

5V ( TBD A )

1.8V_AUX ( TBD A )

0.9V_AUX ( TBD A )

P1.8V_ALW (TBD A)

P1.0V_ALW (TBD A)

P3.3V_ALW ( TBD A )

VDC INV ( TBD A )

PEX IO (TBD A)

P1.2V_ALW

P2.5V_ALW

P3.3V_ALW

Battery

RTC_Battery

VGA CORE (TBD A)

TBD A (TBD)

TBD A (TBD)

TBD A (TBD)

This sheet should be updated !!!

LAN (82566)

1.05V

CPU CORE

1.05V (VCCP)

1.5V

1.05V (MCH CORE)

1.05V (VCCP)

1.5V

2.5V

3.3V

1.8V_AUX

1.05V (ICH CORE)

1.05V (VCCP)

1.5V

3.3V

3.3V_AUX

5V

5V_AUX

RTC_Battery

1V-1.2V (VGA CORE)

1.5V

1.8V

2.5V

1.2V (PEX IO)

3.3V

1.8V_AUX

0.9V_AUX

1.8V

3.3V (LCD 3V)

19V (VDC INV)

Confidential

0.1 A (TBD)

24.5 A (TBD)

3 A (TBD)

0.3 A (TBD)

4.8 A (TBD)

2.5 A (TBD)

1.3 A (TBD)

0.2 A (TBD)

0.12 A (TBD)

2.7 A (TBD)

1.3 A (TBD)

0.4 A (TBD)

1.3 A (TBD)

0.2 A (TBD)

0.12 A (TBD)

2.7 A (TBD)

2.7 A (TBD)

0.01 A (TBD)

8 A (TBD)

0.035 A (TBD)

1 A (TBD)

0.28 A (TBD)

1.6 A (TBD)

0.01 A (TBD)

Samsung

3.1 A (TBD)

1 A (TBD)

3.1 A (TBD)

0.67 A (TBD)

0.24 A (TBD)

ITP

Merom-4M

( 34 W )

*1.5V : 13.4 A (TBD)

Crestline

GMCH

(8 - 8.5 W )

ICH8-M

( ~ 2.0 W )

PEG

DDR-2

(Dual slots)

( ~ 5.0 W )

GDDR FAN

LCD

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

5V

5V

5V

5V

5V

5V

5V

5V

0.1 A (TBD)

0.02 A (TBD)

0.2 A (TBD)

0.2 A (TBD)

0.01 A (TBD)

0.02 A (TBD)

0.06 A (TBD)

0.07 A (TBD)

1 A (TBD)

1 A (TBD)

0.22 A (TBD)

0.16 A (TBD)

1 A (TBD)

2 A (TBD)

0.2 A (TBD)

Thermal

Sensor

SIO

CLOCK

KeyBoard

KBD LED

FWH

HD Audio

HDD

PATA

ODD

SATA HDD

Audio AMP

USB (x 4)

Touch Pad

MICOM 3V

3.3V

MICOM 3V

1.8V

3.3V

3.3V_AUX

3.3V_AUX

3.3V_AUX

3.3V_AUX

5V_AUX

3.3V

3.3V_AUX

5V

3.3V

3.3V_AUX

5V

0.08 A (TBD)

0.08 A (TBD)

0.1 A (TBD)

0.14 A (TBD)

0.1 A (TBD)

0.1 A (TBD)

0.6 A (TBD)

0.1 A (TBD)

1.2 A (TBD)

1 A (TBD)

0.7 A (TBD)

0.2 A (TBD)

0.4 A (TBD)

0.3 A (TBD)

0.01 A (TBD)

0.3 A (TBD)

KBC

PWR LED

R5C843

LAN (Intel)

SD Card

Card Bus

Mini PCI

MDC

C

B

A A

Value by Datasheet/Application notes

4

3

(Value by measurement)

DRAW

CHECK

APPROVAL

MODULE CODE

2

SUN XIAO

WUSHIJIANG

KEVIN LEE

DATE

DEV. STEP

REV

LAST EDIT

6/26/2007

TITLE

PV2

1.0

Gevena

POWER RAILS

October 23, 2007 10:38:02 AM

1

SAMSUNG

ELECTRONICS

PART NO.

BA41-XXXXX

558

PAGE

OF

30

PEG

Gevena

1

Rev. 0.5

CPU

VRM

DC/DC B’d

9) P1.8V_AUX

16) P1.05V

16) P3.3V

1

26

25) VCC_CORE

25

30) CPU1_CPURST*

29) PLT3_RST*

29

29) PCI3_RST*

SAMSUNG

ELECTRONICS

BA41-XXXXX

658

PAGE OF

KBC

12

4

Host Boot / ME Off

(SLPS4* = S4_STATE*) > (SLPM* = SLPS3*)

M-1) KBC3_DDR_PWRON (TBD) = 8) KBC3_SUSPWR

M-2) KBC3_ME_PWRON = 15) KBC3_PWRON

Host / ME Boot

(SLPS4* = S4_STATE*) > SLPM* > SLPS3*

Host S5 / ME Boot

(SLPS4* = SLPM*) > S4_STATE* > SLPS3*

10

10) CHP3_SLPS5*

11

13

14

8

5

11) CHP3_SLPS4*

12) CHP3_SLPSM*

13) CHP3_S4_STATE*

14) CHP3_SLPS3*

18) KBC3_PWRGD

M-1) KBC3_DDR_PWRON

M-2) KBC3_ME_PWRON

8) KBC3_SUSPWR

15) KBC3_PWRON

(Test Option)

19) KBC3_VRON

18

26) VRM3_CPU_PWRGD

16-PG) VTT3_PWRGD

9-PG) 1.8V_AUX_PWRGD

19

8) KBC3_SUSPWR or M-2) KBC3_ME_PWRON

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

D

POWER

S/W

DC/DC B’d

4

4) POWER_SW*

C C

3

MICOM_P3V

15

B

A

Adapter

Battery

AC_DC / Battery

MAX 8724

2) VDC

2

P3.3V_LAN & P5V_AUX

MAX 1999

6

Nineveh

Sheet 46-47

6) P3.3V_LAN

LOM

8) KBC3_SUSPWR

5) KBC3_ALWS_ON

7) P1.0V_LAN

7) P1.8V_LAN

4

MIC5219

15) KBC3_PWRON

M-2) KBC3_ME_PWRON

LT1930

GFX VR

9) P5V_AUX

9

FDS6680A

Sheet 40

FDS6680A

Sheet 40

BCP69

Sheet 46

7

16) P2.5V

8) KBC3_SUSPWR

16) P12V

16) GFX_CORE

Samsung

9-M) P3.3V_M

9) P3.3V_AUX

9

Confidential

3

TO BE UPDATED!!

6) P3.3V_LAN(A)

16) ICH_CORE (P1.05V)

27) CHP3_PWROK

PWROK

17

17) CHP3_ME_PWROK

2) VDC

M-1) KBC3_DDR_PWRON

(Test Option)

M-2) KBC3_ME_PWRON

ICH8-M

CL_PWROK

MAX8632

8

2) VDC

M-2) KBC3_ME_PWRON

15) KBC3_PWRON

15

9) P5V_AUX

9) P3.3V_AUX

9) P1.8V_AUX

9-M) P1.25V_M

9-M) P1.05V_M

3

Battery

PRTC

9) P3.3V_AUX

7) P1.05V_AUX

7) P1.5V_AUX

VRMPWRGD

Sheet 22-25

DDR2 POWER

Sheet 50

TPS5130

FDS4435

Sheet 40

FDS6680A

Sheet 40

FDS6680A

Sheet 40

FDS6680A

Sheet 40

FDS6680A

Sheet 40

RTC

1) VCC_RTC

CHP3_RTCRST

PRTC

23

23) CLK3_PWRGD

INTVRMEN

LAN100_SLP

CHP3_VRMPWRGD

28) CPU1_PWRGDCPU

29) PLT3_RST*

20

29) PCI3_RST*

9) P1.8V_AUX

9) 0.9V

9-PG) 1.8V_AUX_PWRGD

9-M) P1.05V_M

9-M) P1.25V_M

16) P1.5V

16) P1.2V

16-PG) VTT3_PWRGD

16) P5V

16) P3.3V

16) P1.8V

16) P1.25V

16) P1.05V

2

1

9-M) P3.3V_M

CK-505

Sheet 8

26) VRM3_CPU_PWRGD

22) CLK3_PWRGD*_INV

29

12

Thermal

Monitor

Sheet 14

9) P1.8V_AUX

9) P0.9V

9-M) P3.3V_M

16

2

POWER SEQUENCE

26) VRM3_CPU_PWRGD

9-M) ME Host Clock

24) Clock Running

PG-2) VTT3_PWRGD

18) KBC3_PWRGD

19) KBC3_VRON

22

28) CPU1_PWRGDCPU

28

27

27) CHP3_PWROK

17) CHP3_ME_PWROK

9-M) P1.05V_M

9-M) P1.25V_M

16) MCH_CORE

16) GFX_CORE

DDR2

Memory

Sheet 20-21

DRAW

CHECK

APPROVAL

MODULE CODE

SUN XIAO

WUSHIJIANG

KEVIN LEE

16) P1.5V

16) P1.05V

DATE

DEV. STEP

REV PART NO.

LAST EDIT

24

PWROK

CL_PWROK

16) P3.3V

16) P1.8V

16) P1.5V

16) P1.2V

2) VDC

16) P3.3V

16) P3.3V

16) P1.8V

16) P1.5V

6/26/2007

PV2

16

Sheet 10-12

Sheet 15-19

TITLE

1.0

21) CLK3_PWRGD*

21

20) KBC3_ALL_PWRGD

20

(Test Option)

CPU

GMCH

PCIe

Devices

PCI

Devices

POWER SEQUENCE

October 23, 2007 10:38:02 AM

D

B

A

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

CLK_3.3V_M

4

P0.8V

FS(2:0)

3

2

CLOCK DISTRIBUTION

1

Rev. 0.8

D

CLK3_PWRGD*

ITP_EN

CPU_STP*

C C

SS(96/100) SEL

Main PLL

PLL3

SSC

SSC

48MHz PLL

B B

SLG8SP513

CK-505M (w/ CLKREQ* & SSDC)

14 MHz

OSC

4

33 MHz

Buffer

Page 8

PCI_STP*

A A

14.318 MHz

2801-003730

200 MHz

100 MHz

MUX

200 MHz

100 MHz

100 MHz

MUX

96 MHz

100 MHz

100 MHz

100 MHz

100 MHz

100 MHz

48 MHz

100 MHz

MUX

14.318 MHz

33 MHz

33 MHz

33 MHz CLK3_PCLKMICOM

33 MHz CLK3_PCLKCB

33 MHz

33 MHz CLK3_PCLKPORT80

EXP3_CLKREQ*

CLK1_PEG/PEG*

Option For External GFX

PCI Express Gfx

Samsung

CLK3_SIO14

CLK3_PCLKSIO

CLK3_TPMLPC

Confidential

CLK3_PCLKMIN

SIO

TPM 1.2

KBC

CARDBUS

MINI PCI

PORT 80

3

CLK0_HOST_CPU/CPU*

EXPRESS

CARD

CLK0_HOST_GMCH/GMCH*

MCH3_CLKREQ*

CLK1_MCH3GPLL/3GPLL*

CLK1_DREFCLK/CLK*

CLK1_DREFSSC/SSC*

CLK3_GFX_27M/SSC

CLK1_PCIEICH/ICH*

CLK3_USB48

CHP3_SATACLKREQ*

CLK1_SATA/SATA*

CLK3_ICH14

CLK3_PCLKICH33 MHz

32.768 KHz

10 MHz

1394 Clock

24.576 MHz

2801-003898

PEG

CPU

HPLL

MPLL

PCIE PLL

DPLLA

DPLLB

PCIEPLL

USBPLL

SATAPLL

32.768 KHz

OSC

RTC Clock

32.768 KHz

2801-003856

FSB

DMI

BSEL

Crestline

GMCH

100 MHz

100 MHz

100 MHz

ICH8-M

LAN3_PHYCLK

LCI LAN

(Intel)

333/266/200 MHz

333/266/200 MHz

333/266/200 MHz

333/266/200 MHz

PEX3_CLKREQ* (TBD)

PEX3_CLKREQ* (TBD)

PEX3_CLKREQ* (TBD)

AUD3_BCLK

HD 24 MHz

MDC3_BCLK

17.86 MHz

SPI3_CLK

25 MHz

2801-003892

DRAW

CHECK

APPROVAL

MODULE CODE

2

100 MHz

HD Audio

MDC

CLK1_MCLK0/0*

CLK1_MCLK1/1*

CLK1_MCLK3/3*

CLK1_MCLK4/4*

CLK1_DCKLAN*

CLK1_MINIPCIE/PCIE*

CLK1_WIPCIE*

CLK1_NF*100 MHz

SPI

DATE

SUN XIAO

DEV. STEP

WUSHIJIANG

REV

KEVIN LEE

LAST EDIT

667/533/400 MHz

SODIMM #0

SODIMM #1

DCK LAN

MINI PCIE

HDSPA

ROBSON

LAN (3rd Vender)

TITLE

6/26/2007

PV2

1.0

October 23, 2007 10:38:02 AM

CARD

Gevena

CLOCK DIAGRAM

SAMSUNG

ELECTRONICS

PART NO.

BA41-XXXXX

758

PAGE

1

OF

D

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

FSB

FSA

D

BSEL0

BSEL1

0

0

0

0

1

1

1

1

C

4

FSC

HOST CLK

BSEL2

0

0

0

1

1

0

0

1 166 MHz

1

CHP3_SATACLKREQ#

266 MHz

1

333 MHz

0

200 MHz

400 MHz

1

133 MHz

0

100 MHz

1

0

RSVD

1

CLK3_USB48

CPU1_BSEL0

CPU1_BSEL1

CPU1_BSEL2

CLK3_ICH14

CLK3_SIO14

CHP3_CPUSTP#

CHP3_PCISTP#

CLK3_PWRGD

CLK3_PCLKICH

CLK3_PCLKSIO_DS

CLK3_DBGLPC

CLK3_PCLKSIO

CLK3_PCLKMICOM

MCH3_CLKREQ#

SMB3_CLK

SMB3_DATA

B

R237

R265

R266

R264

R240

R259

R260

R257

R261

R262

R263

VDD_SRC_IO

100nF

C530

R238

2.2K

10K

33

33

100 1%

33

33

33

33

475

14.31818MHz

2

C251

0.033nF

100nF

C528

1%

1%

1%33

1%

1%

Y3

3

100nF

C537

R258

10K

C250

0.033nF

6.3V10000nF

C526

R256

10K

VDD_IO

10000nF 6.3V

100nF

C525

C527

C248 C247

0.047nF

0.033nF

VDD_REF

100nF

C536

U13

SLG8SP513

19

VDD_IO

33

VDD_SRC_IO1

43

VDD_SRC_IO2

52

VDD_SRC_IO3

56

VDD_CPU_IO

27

VDD_PLL3_IO

55

NC

17

USB_FS_A

64

FSB_TESTMODE

5

REF_FS_C_TEST_SEL

44

CPUSTOP#

45

PCISTOP#

63

CLKPWRGD_PWRDN#

14

PCIF_5_ITP_EN

13

PCI_4_SEL_LCDCLK#

12

PCI_3

11

PCI_2

10

PCI_1_CLKREQ_B#

8

PCI_0_CLKREQ_A#

7

SCL

6

SDA

3

XTAL_IN

2

XTAL_OUT

18

VSS_48

59

VSS_CPU

22

VSS_IO

15

VSS_PCI

26

VSS_PLL3

1

VSS_REF

30

VSS_SRC1

36

VSS_SRC2

49

VSS_SRC3

VDD_48

100nF

C540

4700nF 10V

C539

VDD_PCI

100nF

C543

SRC11_CLKREQH#

SRC11#_CLKREQG#

SRC7_CLKREQF#

SRC7#_CLKREQE#

SRC3_CLKREQC#

SRC3#_CLKREQD#

LCDCLK#_27M_SS

SRC0#_DOT96#

VDD_PLL3

100nF

100nF

C534

C541

VDD_REF

VDD_48

VDD_PCI

VDD_PLL3

VDD_SRC

VDD_CPU

CPU0

CPU0#

CPU1_MCH

CPU1_MCH#

SRC10

SRC10#

SRC9

SRC9#

SRC8_ITP

SRC8#_ITP#

SRC6

SRC6#

SRC4

SRC4#

SRC2

SRC2#

LCDCLK_27M

SRC0_DOT96

VDD_CPU_IO

6.3V10000nF

100nF

C531

C529

33

1%

1

C252

0.033nF

NO_STUFF

VDD_PLL3_IO

10000nF 6.3V

100nF

C535

C538

P3.3V

Samsung

C249

0.033nF

VDD_SRC

100nF

C210

4

16

9

23

46

62

61

60

58

57

40

39

41

42

37

38

54

53

51

50

48

47

34

35

31

32

28

29

24

25

20

21

2

VDD_CPU

10V4700nF

C186

R239

P3.3V

B33

BLM18PG181SN1

0

SEL_LCDCLK*

CLK0_HCLK0

CLK0_HCLK0#

CLK0_HCLK1

CLK0_HCLK1#

CLK1_EXPRESSCARD

CLK1_EXPRESSCARD#

CLK1_PCIEICH

CLK1_PCIEICH#

CLK1_ROBSON

CLK1_ROBSON#

CLK1_PCIELAN

CLK1_PCIELAN#

LAN3_CLKREQ#

MIN3_CLKREQ#

CLK1_MINIPCIE

CLK1_MINIPCIE#

CLK1_MCH3GPLL

CLK1_MCH3GPLL#

EXP3_CLKREQ#

CLK1_SATA

CLK1_SATA#

GFX3_27M

GFX3_27M_SS

CLK1_PEG

CLK1_PEG#

LOW

HIGH

DOT_96/DOT_96#

SRC_0/SRC_0#

CLK REQ

CLK REQ A

CLK REQ B

CLK REQ E

CLK REQ F

Pin 20/21

1

LCDCLK/LCDCLK#

DEVICE

SATA

GMCH

MINI CARD

EXPRESS CARD

Pin 24/25

27M & 27M_SS

SRC PORT

SRC2

SRC4

SRC6

SRC8

D

C

B

Place 14.318MHz within

500mils of CK-505

NO_STUFF

Confidential

A

DRAW

CHECK

APPROVAL

MODULE CODE

4

3

2

SUN XIAO

WUSHIJIANG

KEVIN LEE

DATE

DEV. STEP

REV

LAST EDIT

6/26/2007

TITLE

Gevena

PV2

1.0

CLOCK GENERATOR

CK-505

October 23, 2007 10:38:02 AM

1

SAMSUNG

PART NO.

PAGE

ELECTRONICS

BA41-XXXXX

A

588

OF

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

4

3

2

1

D

P5.0V

C620

10000nF

6.3V

C619

100nF

C625

10000nF

6.3V

NO_STUFF

C

KBC3_PWRGD

R576

100K

1%

R577

56.2K

1%

R578

R579

FAN5_VDD

FAN3_FDBACK#

CPU3_THRMTRIP#

P3.3V_AUX

R1

R2

B

THERMAL SENSOR & FAN CONTROL

P3.3V_AUX

R590

C624

100nF

NO_STUFF

49.9

1%

U511

EMC2102

1

VDD_3V

24

VDD_5V_1

27

VDD_5V_2

14

POWER_OK

16

RESET#

10

0

FAN_MODE

25

FAN_1

26

FAN_2

28

TACH

13

THERMTRIP#

9

0

SHDN_SEL

11

TRIP_SET

8

NC_1

15

NC_2

21

NC_3

SMDATA

SMCLK

ALERT#

SYS_SHDN#

CLK_SEL

CLK_IN

THRM_PAD

DN1

DP1

DN2

DP2

DN3

DP3

GND

P3.3V

22

23

19

12

2

3

4

5

6

7

17

18

20

29

1%

10K

R588

1%

10K

R589

1%

10K

R587

1%

10K

R575

P3.3V_AUX

(Selectable : PWR_SHDN)

C622

0.47nF

C623

0.47nF

C621

2.2nF

KBC3_THERM_SMDATA

KBC3_THERM_SMCLK

THM3_ALERT#

THM3_STP#

CPU2_THERMDC

CPU2_THERMDA

GFX3_THRMDN

GFX3_THRMDP

2

MMBT3904

1

Q516

3

FAN3_FDBACK#

Samsung

FAN5_VDD

C9

10000nF

6.3V

P3.3V

R16

10K

Line Width = 20 mil

1%

MT9

RMNT-2.5-7.0-1P

J30

HDR-4P-1R-SMD

1

2

3

4

MT11

RMNT-2.5-7.0-1P

D

C

B

TRIP_SET pin voltage = (T-75)/21

3.3 * [R2/(R1+R2)] = (T-75)/21

Confidential

CPU1_THRMTRIP#

A

4

GFX3_THERM#

3 2

VCCP_CORE

R580

2K

1%

1

R573

3

Q512

MMBT3904

2

NO_STUFF

NO_STUFF

P3.3V

R574

10K

NO_STUFF

1%

0

CPU3_THRMTRIP#

DRAW

CHECK

APPROVAL

MODULE CODE

SUN XIAO

WUSHIJIANG

KEVIN LEE

A

DATE

DEV. STEP

REV

LAST EDIT

6/26/2007

TITLE

PV2

THERMAL & FAN CONTROL

1.0

Gevena

THERMAL BLOCK

October 23, 2007 10:38:02 AM

1

SAMSUNG

PART NO.

PAGE

ELECTRONICS

BA41-XXXXX

589

OF

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

4

3

2

1

D

D

VCCP_CORE

1%56.2

J1-1

MEROM-SOCKET

CPU1_A#(16:3)

13-D1

C

CPU1_ADSTB0#

CPU1_A#(35:17)

B

CPU1_ADSTB1#

13-C2

13-D1

13-C2

1 / 4

3

J4

A3*

4

L5

A4*

5

L4

A5*

6

K5

A6*

7

M3

8

N2

9

10

N3

11

12

13

14

15

16

R1

M1

17

18

U5

19

R3

20

W6

21

U4

22

23

U1

24

R4

26

27

W2

28

W5

30

U2

31

32

W3

33

AA4

34

AB2

35

AA3

J1

P5

P2

L2

P4

P1

Y2

Y5

T5

T3

Y4

V4

V1

A7*

A8*

A9*

A10*

A11*

A12*

A13*

A14*

A15*

A16*

ADSTB0*

A17*

A18*

A19*

A20*

A21*

A22*

A23*

A24*

A25*

A26*

A27*

A28*

A29*

A30*

A31*

A32*

A33*

A34*

A35*

ADSTB1*

0

ADDR GROUP

1

ADDR GROUP

CONTROL

ICH

ADS*

BNR*

BPRI*

BR0*

DEFER*

DRDY*

DBSY*

IERR*

INIT*

LOCK*

RESET*

RS0*

RS1*

RS2*

TRDY*

HIT*

HITM*

A20M*

FERR*

IGNNE*

STPCLK*

LINT0

LINT1

SMI*

REQ0*

REQ1*

REQ2*

REQ3*

REQ4*

R656

H1

E2

G5

F1

H5

F21

E1

D20

B3

H4

C1

F3

F4

G3

G2

G6

E4

A6

A5

C4

D5

C6

B4

A3

0

K3

1

H2

Samsung

2

K2

3

J3

4

L1

13-C2

13-C2

13-C2

13-C2

13-B2

13-B2

13-B2

20-C1

13-B2

13-B3

13-A2

13-A2

13-A2

13-B2

13-B2

13-B2

20-C1

20-C1

20-C1

20-C1

20-C1

20-C1

20-C1

13-A2

CPU1_ADS#

CPU1_BNR#

CPU1_BPRI#

CPU1_BREQ#

CPU1_DEFER#

CPU1_DRDY#

CPU1_DBSY#

CPU1_INIT#

CPU1_LOCK#

CPU1_CPURST#

CPU1_RS0#

CPU1_RS1#

CPU1_RS2#

CPU1_TRDY#

CPU1_HIT#

CPU1_HITM#

CPU1_A20M#

CPU1_FERR#

CPU1_IGNNE#

CPU1_STPCLK#

CPU1_INTR

CPU1_NMI

CPU1_SMI#

CPU1_REQ#(4:0)

CPU1_D#(15:0)

CPU1_DSTBN0#

CPU1_DSTBP0#

CPU1_DBI0#

CPU1_D#(31:16)

CPU1_DSTBN1#

CPU1_DSTBP1#

CPU1_DBI1#

13-D3

13-D3

13-B2

13-B2

13-B2

13-B2

13-B2

13-B2

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

J1-2

MEROM-SOCKET

2 / 4

E22

D0*

F24

D1*

E26

D2*

G22

D3*

F23

D4*

G25

D5*

E25

D6*

E23

D7*

K24

D8*

G24

D9*

J24

D10*

J23

D11*

H22

D12*

F26

D13*

K22

D14*

H23

D15*

J26

DSTBN0*

H26

DSTBP0*

H25

DINV0*

N22

D16*

K25

D17*

P26

D18*

R23

D19*

L23

D20*

M24

D21*

L22

D22*

M23

D23*

P25

D24*

P23

D25*

P22

D26*

T24

D27*

R24

D28*

L25

D29*

T25

D30*

N25

D31*

L26

DSTBN1*

M26

DSTBP1*

N24

DINV1*

DATA GRP 0

DATA GRP 2

DSTBN2*

DSTBP2*

DATA GRP 1

DATA GRP 3

DSTBN3*

DSTBP3*

D32*

D33*

D34*

D35*

D36*

D37*

D38*

D39*

D40*

D41*

D42*

D43*

D44*

D45*

D46*

D47*

DINV2*

D48*

D49*

D50*

D51*

D52*

D53*

D54*

D55*

D56*

D57*

D58*

D59*

D60*

D61*

D62*

D63*

DINV3*

Y22

AB24

V24

V26

V23

T22

U25

U23

Y25

W22

Y23

W24

W25

AA23

AA24

AB25

Y26

AA26

U22

AE24

AD24

AA21

AB22

AB21

AC26

AD20

AE22

AF23

AC25

AE21

AD21

AC22

AD23

AF22

AC23

AE25

AF24

AC20

CPU1_D#(47:32)

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

5425

55

56

57

5829

59

60

61

62

63

13-D3

13-B2

13-B2

13-B2

13-D3

13-B2

13-B2

13-B2

CPU1_DSTBN2#

CPU1_DSTBP2#

CPU1_DBI2#

CPU1_D#(63:48)

CPU1_DSTBN3#

CPU1_DSTBP3#

CPU1_DBI3#

C

B

CPU CONNECTOR PART NUMBER 3704-001153

MT504

MT505

RMNT-38-70-1PRMNT-38-70-1P

MT508 MT509

RMNT-38-70-1P

RMNT-38-70-1P

A

4

Confidential

TITLE

DRAW

DRAW

CHECK

CHECK

APPROVAL

APPROVAL

MODULE CODE

MODULE CODE

3

2

SUN XIAO

SUN XIAO

WUSHIJIANG

WUSHIJIANG

KEVIN LEE

KEVIN LEE

undefined

undefined

DATE

DATE

DEV. STEP

DEV. STEP

REV

REV

LAST EDIT

LAST EDIT

6/26/2007

6/26/2007

TITLE

PV2

PV2

1.0

1.0

Gevena

Gevena

CPU

CPU

MEROM(1/3)

MEROM(1/3)

October 23, 2007 10:38:02 AM

October 23, 2007 10:38:02 AM

1

SAMSUNG

SAMSUNG

PART NO.

PART NO.

10

10

PAGEPAGE

ELECTRONICS

ELECTRONICS

BA41-XXXXX

BA41-XXXXX

58

58

OF

OF

A

SAMSUNG PROPRIETARY

COM-22C-015(1996.6.5) REV. 3

D:/tingting/geneva/Geneva_pr_1023

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

4

3

2

1

D

J1-3

MEROM-SOCKET

A22

60-B412-B4

NO_STUFF

1%

1%27.4

A21

D24

AE6

D21

A24

B25

C21

B23

B22

AD26

AA1

U26

R26

AF7

AE7

C23

D25

C24

AF26

AF1

A26

AE2

AF3

AE3

AF4

AE5

AF5

AD6

D7

B5

E5

D6

C7

Y1

BCLK0

BCLK1

SLP*

DPSLP*

DPRSTP*

DPWR*

PWRGOOD

PSI*

VID_6

VID_5

VID_4

VID_3

VID_2

VID_1

VID_0

PROCHOT*

THRMDA

THRMDC

THERMTRIP*

BSEL2

BSEL1

BSEL0

GTLREF

COMP3

COMP2

COMP1

COMP0

VCCSENSE

VSSSENSE

TEST1

TEST2

TEST3

TEST4

TEST5

TEST6

H CLK

3 / 4

THERMAL

XDP/ITP SIGNALS

RSVD

CLK0_HCLK0

CLK0_HCLK0#

CPU1_SLP#

CPU1_DPSLP#

CPU1_DPRSTP#

CPU1_DPWR#

CPU1_PWRGDCPU

CPU1_PSI#

CPU1_VID(6:0)

VCCP_CORE

CPU2_THERMDA

VCCP_CORE

C

CPU2_THERMDC

CPU1_THRMTRIP#

R660

1K

1%

R661

2K

1%

CPU1_BSEL2

CPU1_BSEL1

CPU1_BSEL0

CPU1_VCCSENSE

CPU1_VSSSENSE

R657

56.2

1%

R591

R592

R659

R658

8-C1

8-C1

13-B3

20-C1

14-B1 20-C1 60-C4

13-B2

20-C1

60-B4

6

60-C4

60-B4

5

4

3

2

1

0

9-B4

9-B4

20-C114-B1

8-C4

11-A4

8-C4 11-A4

11-A48-C4

54.9

27.4 1%

54.9 1%

12-C4 60-B4

1%1K

0

0

1K 1%

C680 100nF

R597

R654

R655

B

R653

B26

VCCA_1

C26

VCCA_2

K6

VCCP_1

J6

VCCP_2

M6

VCCP_3

N6

VCCP_4

T6

VCCP_5

R6

VCCP_6

K21

VCCP_7

J21

VCCP_8

M21

VCCP_9

N21

VCCP_10

T21

VCCP_11

R21

VCCP_12

V21

VCCP_13

W21

VCCP_14

V6

VCCP_15

G21

VCCP_16

AC1

PREQ*

AC2

PRDY*

AC4

BPM3*

AD1

BPM2*

AD3

BPM1*

AD4

BPM0*

AC5

TCK

AA6

TDI

AB3

TDO

AB5

TMS

AB6

TRST*

C20

R652

DBR*

D2

RSVD_1

F6

RSVD_2

D3

RSVD_3

D22

RSVD_4

M4

RSVD_5

N5

RSVD_6

T2

RSVD_7

V3

RSVD_8

B2

RSVD_9

C3

RSVD_10

Samsung

C674

10nF

16V

VCCP_CORE

EC509

330uF

2.5V

AL

OXI Cap

Change to 270uF

11-A3

11-A3

11-A3

11-A3

0

22-D4

P1.5V

C673

10000nF

6.3V

C658

100nF

CPU1_TCK

CPU1_TDI

CPU1_TMS

CPU1_TRST#

ITP3_DBRESET#

C640

100nF

C639

100nF

C661

100nF

C659

100nF

C660

100nF

CPU Core Voltage Table

Active Mode

VID(6:0)

0

0

0

0

0

0

0

0

0

0

0

0

0

00

0

0

0

00

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

1

0

0

0

001

0

1

0

0

0

0

1

00

0

1

0

0

0

1

0

0

0

1

0

0

1

0

0

1

0

0

0

0

1

0

0

1

0

0

0

0

1

0

0

0

1

0

0

1

0

0

0

0

1

1

0

0

0

1

0

1

1

0

0

1

1

0

0

1

0

1

1

0

1

0

0

1

0

1

1

0

1

0

1

0

0

1

1

0

0

1

0

0

1

0

0

0

0

0

0

1

1

0

0

0

0

0

1

0

0

1

0

0

1

0

0

0

0

1

0

1

0

DPRSLPVR

DPRSTP*

PSI2*

Voltage

1.5000 V

0

0

0

1.4875 V

0

0

1

1

0

1.4750 V

0

1

0

1

1.4625 V

1.4500 V

0

1

1

1

1.4375 V

0

1.4250 V1

0

1

1.4125 V

1

1

1

1

1

0 1.4000 V

0

0

1

1.3875 V

0

0

1

0

0

1.3750 V

1

1

0

1.3625 V

0

0

1

1.3500 V

1

0

1.3375 V

1

1

1

1.3250 V

0

1

1

1.3125 V

1

0

0

0

1.3000 V

0

0

1

1.2875 V

1.2750 V

1

0

0

1.2625 V

0

1

1

1.2500 V

0

0

1

1

1.2375 V

1

0

1.2250 V

0

1

1

1

1.2125 V

1

1

1

1

0

0

1.2000 V

0

0

1.1875 V

1

0

1.1750 V

0

0

1

1.1625 V

1

0

1

1.1500 V

0

1

0

0

1.1375 V

1

1

1

1

1.1250 V

0

1

1

1

1.1125 V

0

0

0

1.1000 V

1

0

0

1.0875 V

1

0

0

1.0750 V

0

1

1

1.0625 V

0

0

1

1.0500 V

1

1

0

1.0375 V

0

1

1

1.0250 V

1

1

1

1

1

1.0125 V

Active

0

1

0 or 1

Active/Deeper Sleep

Dual Mode Region

VID(6:0)

0

1

0

0

1

0

0

1

0

0

1

0

0

1

0

0

1

0

0

1

0

0

1

0

0

1

1

0

1

1

0

1

1

0

1

1

0

1

1

0

1

1

0

1

1

0

1

1

0

1

1

0

1

1

0

1

0

1

1

1

0

1

1

0

1

1

0

1

1

0

1

1

1

0

0

1

0

0

1

0

0

0

1

0

0

1

1

0

0

1

0

0

1

0

0

0

0

1

0

0

0

0

1

0

1

0

0

1

0

1

0

0

1

0

0

0

0

1

0

1

10

1

DPRSLPVR

DPRSTP*

PSI2*

IMVP-6

0

1

0 1.0000 V

0

0

1

1

0 0.9750 V

1

1

0

1

1

0

1

1

0

1

1

10

1

1

1

1

1

0

0

0

0

0

0 0.8875 V

0

1

0

0

0

1

0

1

0

1

0

1

0

1 0.8250 V

1

1

0

01

0

1

1

0

0

0

1

1

1

0

1

1

1

0

1

0

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

1

0

0

0

1

10

0

0

0

1

0

0

1

1

1

0

1

0

0

1

0

0

1

1

0

1

0

1

1

1

0

1

1

0

1

1

1

1

1

1

1

1

1

0

0

0

Deeper Slp

1

0

0 or 1

Deeper Sleep/Extended Deeper Sleep

Dual Mode Region

Voltage

VID(6:0)

1

0

1

0.9875 V

0

0.9625 V

1

0.9500 V

0

1

0.9375 V

0.9250 V

1

0.9125 V

1

0

0.9000 V

1

0

0.8750 V

0.8625 V

1

0.8500 V

0

1

0.8375 V

0

1

0.8125 V

0.8000 V

0

1

0.7875 V

0

0.7750 V

0.7625 V

1

0

0.7500 V

1

0.7375 V

0.7250 V

0

1

1

0.7125 V

0.7000 V

0

0.6875 V

1

0

0.6750 V

0.6625 V

1

0

0.6500 V

0.6375 V

1

0

0.6250 V

1

0.6125 V

0

0.6000 V

1

0.5875 V

0.5750 V

0

1

0.5625 V

0

0.5500 V

1

0.5375 V

0.5250 V

0

0.5125 V

1

0

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1 0.0000 V

1

1

1

1

1

1

1

1

1

1

1

1

1

11

*"1111111" : 0V power good asserted.

1

0

0

1

0

0

0

1

0

0

1

1

1

0

1

0

1

1

1

0

1

1

1

0

1

1

0

1

0

1

1

0

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

1

0

0

1

0

0

1

0

0

0

0

1

0

0

1

0

0

1

0

1

0

0

1

11

0

1

1

0

1

1

0

1

1

1

0

0

0

0

1

0

0

1

0

0

1

0

1

1

0

1

1

0

1

1

0

1

1

1

1

0

1

0

1

1

1

0

1

0

1

1

1

1

1

1

1 0.0000 V

1

1

1

1

1

Voltage

0

0.4875 V

1

1

0

0.4750 V

1

0.4625 V

1

00

0.4500 V

0

0.4375 V

1

1

0.4250 V

0

0.4125 V

11

0

0.4000 V

0

0

0

0.3875 V

1

0.3750 V

10

1

0.3625 V

1

0

0.3500 V

0

1

0.3375 V

0

0.3250 V

10

0.3125 V

1

1

0

0.3000 V

0

0.2875 V

0

1

0

1

0.2750 V

1

1

0.2625 V

0 0.2500 V

0

0 0.2375 V

1

1

0

0.2250 V

1

1

0.2125 V

0

1

0

0.2000 V

0

1

0.1875 V

0

0.1750 V

1

0.1625 V

1

1

0.1500 V

0

0

1

0

0.1375 V

0

1 0.1250 V

0.1125 V

1

1

0

0

0.1000 V

0.0875 V

0

1

1

01

0.0750 V

1

1

0.0625 V

0

0

0.0500 V

0

0.0375 V

1

1

0.0250 V

0

0.0125 V

1

1

0

1

0

0.0000 V

10 0 0.5000 V

0

1

0.0000 V

0

1

0.0000 V

1

0

0

0.0000 V

0

1

1

0.0000 V

0

0.0000 V

1

1

D

C

B

ITP DISABLE

VCCP_CORE

40.2 1%

150 1%

Confidential

R593

R595

27.4 1%

R594

475 1%

R596

A

4

11-C3

11-C3

11-C3

11-C3

CPU1_TDI

CPU1_TMS

CPU1_TCK

CPU1_TRST#

NO_STUFF

3

GTLREF : Keep the Voltage divider within 0.5"

of the first GTLREF0 pin with Zo=55ohm trace.

Minimize coupling of any switching signals to this net.

COMP0,2(COMP1,3) should be connected with Zo=27.4ohm(55ohm)

trace shorter than 1/2" to their respective Banias socket pins.

GND test points within 100mil of the VCC/VSSsense at the end of the line.

Route the VCC/VSSsense as a Zo=55ohm traces with equal length.

Observe 3:1 spacing b/w VCC/VSSsense lines and 25mil away

(preferred 50mil) from any other signal. And GND via 100mil away

from each of the VCC/VSS test point vias.

DRAW

CHECK

APPROVAL

MODULE CODE

2

SUN XIAO

WUSHIJIANG

KEVIN LEE

DATE

DEV. STEP

REV

LAST EDIT

6/26/2007

TITLE

PV2

1.0

*Yonah Processor (2.33 GHz / 800 MHz : TBD)

Gevena

CPU

MEROM(2/3)

October 23, 2007 10:38:02 AM

PAGE

1

SAMSUNG

ELECTRONICS

PART NO.

BA41-XXXXX

11 58

OF

A

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

3

24

1

D

A11

VSS_1

A14

A16

A19

A2

A23

A25

A4

A8

AA11

AA14

AA16

CPU_CORE

NO_STUFF

20%

C

22000nF

C633

100 1%

CPU1_VCCSENSE

CPU1_VSSSENSE

R599

R600

100 1%

20%

22000nF

C665

NO_STUFF

B

20%

22000nF

C631

20%

22000nF

C666

NO_STUFF

NO_STUFF NO_STUFF

20%

20%

22000nF

22000nF

C634

C632

20%

20%

22000nF

22000nF

C663

C662

NO_STUFF

NO_STUFF

20%

22000nF

C653

20%

22000nF

C645

NO_STUFF

20%

22000nF

C654

20%

22000nF

C646

NO_STUFF

20%

22000nF

22000nF

22000nF

22000nF

C638

C635

C637

C636

20%

20%

20%

20%

22000nF

22000nF

22000nF

22000nF

C82

C81

C66

C647

NO_STUFF

Samsung

NO_STUFF

NO_STUFF

22000nF

C67

20%

22000nF

C68

NO_STUFF

22000nF

C664

20%

22000nF

C642

20%

22000nF

C657

20%

22000nF

C641

22000nF

C656

20%

22000nF

C644

22000nF

C655

20%

22000nF

C643

20%

20%

20%

20%

20%

20%

20%

6x 330 uF : CPU VR side

Be Caution the placement of decap!!

AA19

AA22

AA25

AB11

AB13

AB16

AB19

AB26

AC11

AC14

AC16

AC19

AC21

AC24

AD11

AD13

AD16

AD19

AD22

AB23

AD25

AE11

AE14

AE16

AE19

AE23

AE26

AF11

AF13

AF16

AF19

AF21

AA2

AA5

AA8

AB1

AB4

AB8

AC3

AC6

AC8

AD2

AD5

AD8

AE1

AE4

AE8

AF2

CPU_CORE CPU_CORE

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

AA10

AA12

AA13

AA15

AA17

AA18

AA20

AB10

AB12

AB14

AB15

AB17

AB18

AB20

AC10

AC12

AC13

AC15

AC17

AC18

AD10

AD12

AD14

AD15

AD17

AD18

AE10

AE12

AE13

AE15

AE17

AE18

AE20

A10

A12

A13

A15

A17

A18

A20

A7

A9

AA7

AA9

AB7

AB9

AC7

AC9

AD7

AD9

VSS_163

Y6

K23

K26

VSS_121

VSS_122

VCC_1

VCC_2

VCC_3

VCC_4

VCC_5

VCC_6

VCC_7

VCC_8

VCC_9

VCC_10

VCC_11

VCC_12

VCC_13

VCC_14

VCC_15

VCC_16

VCC_17

VCC_18

VCC_19

VCC_20

VCC_21

VCC_22

VCC_23

VCC_24

VCC_25

VCC_26

VCC_27

VCC_28

VCC_29

VCC_30

VCC_31

VCC_32

VCC_33

VCC_34

VCC_35

VCC_36

VCC_37

VCC_38

VCC_39

VCC_40

VCC_41

VCC_42

VCC_43

VCC_44

VCC_45

VCC_46

VCC_47

VCC_48

VCC_49

VCC_50

VSS_161

VSS_162

Y3

Y24

L21

L24

L3

VSS_123K4VSS_124

VSS_125

VSS_126

VSS_127L6VSS_128M2VSS_129

MEROM-SOCKET

VSS_160

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

V5

W1

W4

Y21

W23

W26

M22

4 / 4

V25

M25

VSS_130

VSS_131M5VSS_132N1VSS_133

J1-4

VSS_152

VSS_153

VSS_154

V2

V22

N23

VSS_150

VSS_151

U3

U6

N26

VSS_134

VSS_135N4VSS_136

VCC_100

VSS_148

VSS_149

U21

U24

P21

P24

VCC_51

VCC_52

VCC_53

VCC_54

VCC_55

VCC_56

VCC_57

VCC_58

VCC_59

VCC_60

VCC_61

VCC_62

VCC_63

VCC_64

VCC_65

VCC_66

VCC_67

VCC_68

VCC_69

VCC_70

VCC_71

VCC_72

VCC_73

VCC_74

VCC_75

VCC_76

VCC_77

VCC_78

VCC_79

VCC_80

VCC_81

VCC_82

VCC_83

VCC_84

VCC_85

VCC_86

VCC_87

VCC_88

VCC_89

VCC_90

VCC_91

VCC_92

VCC_93

VCC_94

VCC_95

VCC_96

VCC_97

VCC_98

VCC_99

VSS_147

T4

T26

P6

VSS_137

VSS_138P3VSS_139

VSS_144

VSS_145

VSS_146

T1

T23

R22

VSS_140R2VSS_141

AE9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

AF9

B10

B12

B14

B15

B17

B18

B20

B7

B9

C10

C12

C13

C15

C17

C18

C9

D10

D12

D14

D15

D17

D18

D9

E10

E12

E13

E15

E17

E18

E20

E7

E9

F10

F12

F14

F15

F17

F18

F20

F7

F9

VSS_142

VSS_143

R5

R25

VSS_120

VSS_119

VSS_118

VSS_117

VSS_116

VSS_115

VSS_114

VSS_113

VSS_112

VSS_111

VSS_110

VSS_109

VSS_108

VSS_107

VSS_106

VSS_105

VSS_104

VSS_103

VSS_102

VSS_101

VSS_100

VSS_99

VSS_98

VSS_97

VSS_96

VSS_95

VSS_94

VSS_93

VSS_92

VSS_91

VSS_90

VSS_89

VSS_88

VSS_87

VSS_86

VSS_85

VSS_84

VSS_83

VSS_82

VSS_81

VSS_80

VSS_79

VSS_78

VSS_77

VSS_76

VSS_75

VSS_74

VSS_73

VSS_72

VSS_71

VSS_70

VSS_69

VSS_68

VSS_67

VSS_66

VSS_65

VSS_64

VSS_63

VSS_62

VSS_61

K1

J5

J25

J22

J2

H6

H3

H24

H21

G4

G26

G23

G1

F8

F5

F25

F22

F2

F19

F16

F13

F11

E8

E6

E3

E24

E21

E19

E16

E14

E11

D8

D4

D26

D23

D19

D16

D13

D11

D1

C8

C5

C25

C22

C2

C19

C16

C14

C11

B8

B6

B24

B21

B19

B16

B13

B11

AF8

AF6

AF25

D

C

B

Confidential

A

DRAW

CHECK

APPROVAL

MODULE CODE

3

24

SUN XIAO

WUSHIJIANG

KEVIN LEE

DATE

DEV. STEP

REV

LAST EDIT

6/26/2007

TITLE

Gevena

PV2

1.0

CPU

MEROM(3/3)

October 23, 2007 10:38:02 AM

1

SAMSUNG

ELECTRONICS

PART NO.

BA41-XXXXX

12 58

PAGE OF

A

24

C

3

COM-22C-015(1996.6.5) REV. 3

SAMSUNG PROPRIETARY

1

D:/tingting/geneva/Geneva_pr_1023

B

A

D

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

VCCP_CORE

C731

2200nF

C733

4700nF

10V

C730

470nF

16V

C732

4700nF

XC501

330uF

10V

NO_STUFF

2.5V

OXI

U13

U12

CPU1_D#(63:0)

VCCP_CORE

R684

221

1%

13-A3

C728

100nF

MCH1_HXSWING

R685

100

1%

VCCP_CORE

R697

1K

R696

1%

C812

100nF

2K

1%

13-A3

MCH1_HVREF

VCCP_CORE

10-C1 10-C2 10-D1 10-D2

Samsung

CPU1_CPURST#

CPU1_SLP#

MCH1_HXSWING

Confidential

MCH1_HVREF

0 4

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

10-C3

11-D4

R688

R687

13-C4

R686

13-B4

54.9

54.9

24.9 1%

E2

HD*_0

G2

HD*_1

G7

HD*_2

M6

HD*_3

H7

HD*_4

H3

HD*_5

G4

HD*_6

F3

HD*_7

N8

HD*_8

H2

HD*_9

M10

HD*_10

N12

HD*_11

N9

HD*_12

H5

HD*_13

P13

HD*_14

K9

HD*_15

M2

HD*_16

W10

HD*_17

Y8

HD*_18

V4

HD*_19

M3

HD*_20

J1

HD*_21

N5

HD*_22

N3

HD*_23

W6

HD*_24

W9

HD*_25

N2

HD*_26

Y7

HD*_27

Y9

HD*_28

P4

HD*_29

W3

HD*_30

N1

HD*_31

AD12

HD*_32

AE3

HD*_33

AD9

HD*_34

AC9

HD*_35

AC7

HD*_36

AC14

HD*_37

AD11

HD*_38

AC11

HD*_39

AB2

HD*_40

AD7

HD*_41

AB1

HD*_42

Y3

HD*_43

AC6

HD*_44

AE2

HD*_45

AC5

HD*_46

AG3

HD*_47

AJ9

HD*_48

AH8

HD*_49

AJ14

HD*_50

AE9

HD*_51

AE11

HD*_52

AH12

HD*_53

AJ5

HD*_54

AH5

HD*_55

AJ6

HD*_56

AE7

HD*_57

AJ7

HD*_58

AJ2

HD*_59

AE5

HD*_60

AJ3

HD*_61

AH2

HD*_62

AH13

HD*_63

B6

H_CPURST*

E5

H_CPUSLP*

1%

W1

H_SCOMP

1%

W2

H_SCOMP*

B3

H_SWING

C2

H_RCOMP

A9

H_DVREF

B9

H_AVREF

VCCP_CORE

U11

VTT_1

VTT_2

Host Data Bus

VCC_1

AT35

AT34

VTT_3U9VTT_4U8VTT_5U7VTT_6U5VTT_7U3VTT_8U2VTT_9

VCC_2

4 1

3

VCC_3

AH28

VCC_4

AC32

VCC Core

VCC_5

VCC_6

AK32

AC31

U1

T13

T11

T10

VTT_10

VTT_11

VTT_12

VTT_13T9VTT_14T7VTT_15T6VTT_16T5VTT_17T3VTT_18T2VTT_19

VTT

U32-1

LE88CLPM

1 OF 5

VCC_10

VCC_11

VCC_12

VCC_8

VCC_9

AH32

AH31

AH29

AF32

VCC_13

R30

VCC_7

AJ31

AJ28

R3

VTT LF

VTTLF_1

16V470nF

F2

A7

470nF 16V

C729

C727

R1

VTT_20R2VTT_21

VTT_22

VTTLF_2

VTTLF_3

16V470nF

AH1

C734

HA*_3

HA*_4

HA*_5

HA*_6

HA*_7

HA*_8

HA*_9

HA*_10

HA*_11

HA*_12

HA*_13

HA*_14

HA*_15

HA*_16

HA*_17

HA*_18

HA*_19

HA*_20

HA*_21

HA*_22

Host Address Bus

HA*_23

HA*_24

HA*_25

HA*_26

HA*_27

HA*_28

HA*_29

HA*_30

HA*_31

HA*_32

HA*_33

HA*_34

HA*_35

H_ADS*

H_ADSTB*_0

H_ADSTB*_1

H_BNR*

H_BPRI*

H_BREQ*

H_DEFER*

H_DBSY*

H_DPWR*

H_DRDY*

H_HIT*

H_HITM*

H_LOCK*

H_TRDY*

HPLL_CLK

HPLL_CLK*

H_DINV*_0

H_DINV*_1

H_DINV*_2

H_DINV*_3

H_DSTBN*_0

H_DSTBN*_1

H_DSTBN*_2

H_DSTBN*_3

H_DSTBP*0

H_DSTBP*1

H_DSTBP*2

H_DSTBP*3

H_REQ*_0

H_REQ*_1

H_REQ*_2

H_REQ*_3

H_REQ*_4

H_RS*_0

H_RS*_1

H_RS*_2

2

DRAW

CHECK

APPROVAL

MODULE CODE

J13

B11

C11

M11

C15

F16

L13

G17

C14

K16

B13

L16

J17

B14

K19

P15

R17

B16

H20

L19

D17

M17

N16

J19

B18

E19

B17

B15

E17

C18

A19

B19

N19

G12

H17

G20

C8

E8

F12

D6

C10

H8

K7

E4

C6

G10

B7

AM5

AM7

K5

L2

AD13

AE13

M7

K3

AD2

AH11

L7

K2

AC2

AJ10

M14

E13

A11

H13

B12

E12

D7

D8

0

1

2

3

4

SUN XIAO

WUSHIJIANG

KEVIN LEE

10-C3

10-C4

10-B4

10-C3

10-C3

10-C3

10-C3

10-C3

11-D4

10-C3

10-C3

10-C3

10-C3

10-C3

10-C2

10-B2

10-C1

10-B1

10-C2

10-B2

10-C1

10-B1

10-C2

10-B2

10-C1

10-B1

10-B3

10-C3

10-C3

10-C3

3

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

2925

30

31

32

33

34

35

8-C1

8-C1

10-C410-D4

Calero : HA*[35:32] not support

CPU1_ADS#

CPU1_ADSTB0#

CPU1_ADSTB1#

CPU1_BNR#

CPU1_BPRI#

CPU1_BREQ#

CPU1_DEFER#

CPU1_DBSY#

CPU1_DPWR#

CPU1_DRDY#

CPU1_HIT#

CPU1_HITM#

CPU1_LOCK#

CPU1_TRDY#

CLK0_HCLK1

CLK0_HCLK1#

CPU1_DBI0#

CPU1_DBI1#

CPU1_DBI2#

CPU1_DBI3#

CPU1_DSTBN0#

CPU1_DSTBN1#

CPU1_DSTBN2#

CPU1_DSTBN3#

CPU1_DSTBP0#

CPU1_DSTBP1#

CPU1_DSTBP2#

CPU1_DSTBP3#

CPU1_REQ#(4:0)

CPU1_RS0#

CPU1_RS1#

CPU1_RS2#

DATE

6/26/2007

DEV. STEP

PV2

REV

1.0

LAST EDIT

CPU1_A#(35:3)

TITLE

October 23, 2007 10:38:02 AM

Gevena

CMCH

CRESTLINE (1/5)

SAMSUNG

PART NO.

13 58

PAGE

D

C

B

A

ELECTRONICS

BA41-XXXXX

OF

D

B

COM-22C-015(1996.6.5) REV. 3

A

SAMSUNG PROPRIETARY

C

D:/tingting/geneva/Geneva_pr_1023

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

4

3

4

0

32

5

621112

1

72-C4

27-D327-D2

27-C2

27-C3

PM-model

100nFC501

100nFC508

100nFC505

PEG1_RXN(15:0) PEG1_RXP(15:0)

27-C327-D227-D3 27-C272-B4

5

0

1

4

1311

7143

9

10

8

0

12

15

14

72-C4 27-D3 27-D2

27-B327-C2

27-B2

6

2

3

7

11

12

10

8

5

16

13

94

27-C3

100nFC503

C906 100nF

C898 100nF

15

C902 100nF

2

8

13 8

10

14

7

9

100nF

100nF

100nFC513

100nFC515

C511

C911 100nF

C923

C915 100nF

C919 100nF

3

15

0

114

100nFC157

100nFC895

C500 100nF

C926 100nF

C502 100nF

6

47

5

100nF

100nFC904

100nFC900

C507 100nF

C506

100nFC909

92

100nFC914

C510 100nF

10

100nFC918

C512 100nF

12

13

100nFC921

C514 100nF

15

100nFC92511100nFC156

27-C3

72-D4

27-D2

27-C2

27-D3

1

PEG1_TXP(15:0)PEG1_TXN(15:0)

D

24.9 1%

R736

22-D2

22-D2

22-C2

22-C2

22-D2

22-D2

22-C2

22-C2

22-D2

22-D2

22-D2

22-C2

22-D2

22-D2

22-D2

22-C2

22-C2

22-C2

22-B425-C1

22-C2

14-A1

22-D4

60-C4 20-C1 11-D4

34-A4 25-B2

51-C4

22-B4

100

11-C420-C1

22-C460-C4

MCH3_CL_VREF

1

P1.05V_PEG

DMI1_TXN_0

DMI1_TXN_1

DMI1_TXN_2

DMI1_TXN_3

DMI1_TXP_0

DMI1_TXP_1

DMI1_TXP_2

DMI1_TXP_3

DMI1_RXN_0

DMI1_RXN_1

DMI1_RXN_2

DMI1_RXN_3

DMI1_RXP_0

DMI1_RXP_1

DMI1_RXP_2

DMI1_RXP_3

8-B1

CLK1_MCH3GPLL

8-B1

CLK1_MCH3GPLL#

CHP3_CL_CLK_0

CHP3_CL_DATA_0

KBC3_PWRGD

CHP3_CL_RST#_0

MCH3_CL_VREF

MCH3_BMBUSY#

CPU1_DPRSTP#

MCH3_EXTTS0#

MCH3_EXTTS1#

KBC3_PWRGD

1%

PLT3_RST#

CPU1_THRMTRIP#

CHP3_DPRSLPVR

SAMSUNG

PART NO.

PAGE

14-B1

C516

100nF

ELECTRONICS

BA41-XXXXX

C

Connect to GND for PM-model

B

27-C2

28-C3

25-A4

37-A4

38-C2

39-C3

22-B4

21-C1

P1.25V

R502

1K

1%

R501

390

A

5814

OF

M47

U44

T49

J51

L51

N47

MCH3_CLKREQ#

MCH3_ICHSYNC#

R735

R714

22-A4

14-A28-C4

0

20K

K33

CRT_DDC_CLK

G35

CRT_DDC_DATA

F33

CRT_HSYNC

E33

CRT_VSYNC

H32

CRT_BLUE

G32

CRT_BLUE*

K29

CRT_GREEN

J29

CRT_GREEN*

F29

CRT_RED

E29

CRT_RED*

C32

CRT_TVO_IREF

M35

TV_DCONSEL_0

P33

TV_DCONSEL_1

E27

TVA_DAC

G27

TVB_DAC

K27

TVC_DAC

F27

TVA_RTN

J27

TVB_RTN

L27

TVC_RTN

C37

L_DDC_CLK

D35

L_DDC_DATA

E39

L_CTRL_CLK

E40

L_CTRL_DATA

K40

L_VDD_EN

J40

L_BKLT_CTRL

H39

L_BKLT_EN

G51

LVDSA_DATAN_0

E51

LVDSA_DATAN_1

F49

LVDSA_DATAN_2

G50

LVDSA_DATAP_0

E50

LVDSA_DATAP_1

F48

LVDSA_DATAP_2

D46

LVDSA_CLK*

C45

LVDSA_CLK

G44

LVDSB_DATAN_0

B47

LVDSB_DATAN_1

B45

LVDSB_DATAN_2

E44