Page 1

Features

• 80C51 Core

– 12 or 6 Clocks per Instruction (X1 and X2 Modes)

– 256 Bytes Scratchpad RAM

– Dual Data Pointer

– Two 16-bit Timer/Counters: T0 and T1

• T83C5121 with 16 Kbytes Mask ROM

• T85C5121 with 16 Kbytes Code RAM

• T89C5121 with 16 Kbytes Code RAM and 16 Kbytes EEPROM

• On-chip Expanded RAM (XRAM): 256 Bytes

• Versatile Host Serial Interface

– Full-duplex Enhanced UART (EUART) with Dedicated Baud Rate Generator (BRG):

Most Standard Speeds up to 230K bits/ s at 7. 36 MHz

– Output Enable Input

– Multiple Logic Level Shifters Options (1.8V to V

– Automatic Level Shifter Option

• Multi-protocol Smart Card Interface

– Certified with Dedicated Firmware Acc ording to ISO 7816, EMV2000, GIE-CB, GSM

11.12V and WHQL Standards

– Asynchronous Protocol s T = 0 and T = 1 with Direct and Inver se Modes

– Baud Rate Generator Supporting All ISO7816 Speeds up to D = 32/F = 372

– Parity Error Det ection and Indication

– Automatic Character Repetition on Parity Errors

– Programmable Tim eout Detection

– Card Clock Stop High or Low for Card Power-down Mode

– Support Synchronous Card with C4 and C8 Programmabl e Outputs

– Card Detection and Automatic De- activation Sequence

– Step-up/down Conve rte r wit h Programmable V oltage Output: 5V, 3V (± 8% at

60 mA) and 1.8V (±8% at 20 mA)

– Direct Connection to Smart Car d Terminals:

Short Circuit Current Limitation

Logic Level Shif ter s

4 kV ESD Protection (MIL/STD 833 Class 3)

• Alternate Card Support with CLK, I/O and RST According to GSM 1 1.12V Standard

• 2x I/O Ports: 6 I/O Port1 and 8 I/O Port3

• 2x LED Outputs with Programmable Current Sources: 2, 4, or 10 mA

• Hardware Watchdog

• Reset Output Includes

– Hardware Watchdog Reset

– Power-on Reset (POR)

– Power-fail Detector (PFD)

• 4-level Priority Interrupt System with 7 Sources

• 7.36 to 16 MHz On-chip Oscill ator with Clock Prescaler

• Absolute CPU Maxi mal Frequen c y: 16 MHz in X1 mode, 8MHz in X2 mode

• Idle and Power-down Modes

• Voltage Operation: 2.85V to 5.4V

• Low Power Consumption

– 8 mA Operating Current (at 5.4V and 3. 68 MHz )

– 150 mA Maximum Current with Smart Card Power-on (at 16 MHz X1 Mode)

–30 μA Maximum Power-down Current at 3.0V (without Smart Card)

–100 μA Maximum Power-down Current at 5.4V (without Smart Card)

• T em p erature Range

– Commercial: 0 to +70°C Operating Temperature

– Industrial: -4 0 to +85°C Operati ng Temperature

• Packages

– SSOP24

–QFN32

– PLCC52

CC

)

8-bit

Microcontroller

with Multiprotocol Smart

Card Interface

T83C5121

T85C5121

T89C5121

AT83C5121

AT85C5121

AT89C5121

Rev. 4164G–SCR–07/06

Page 2

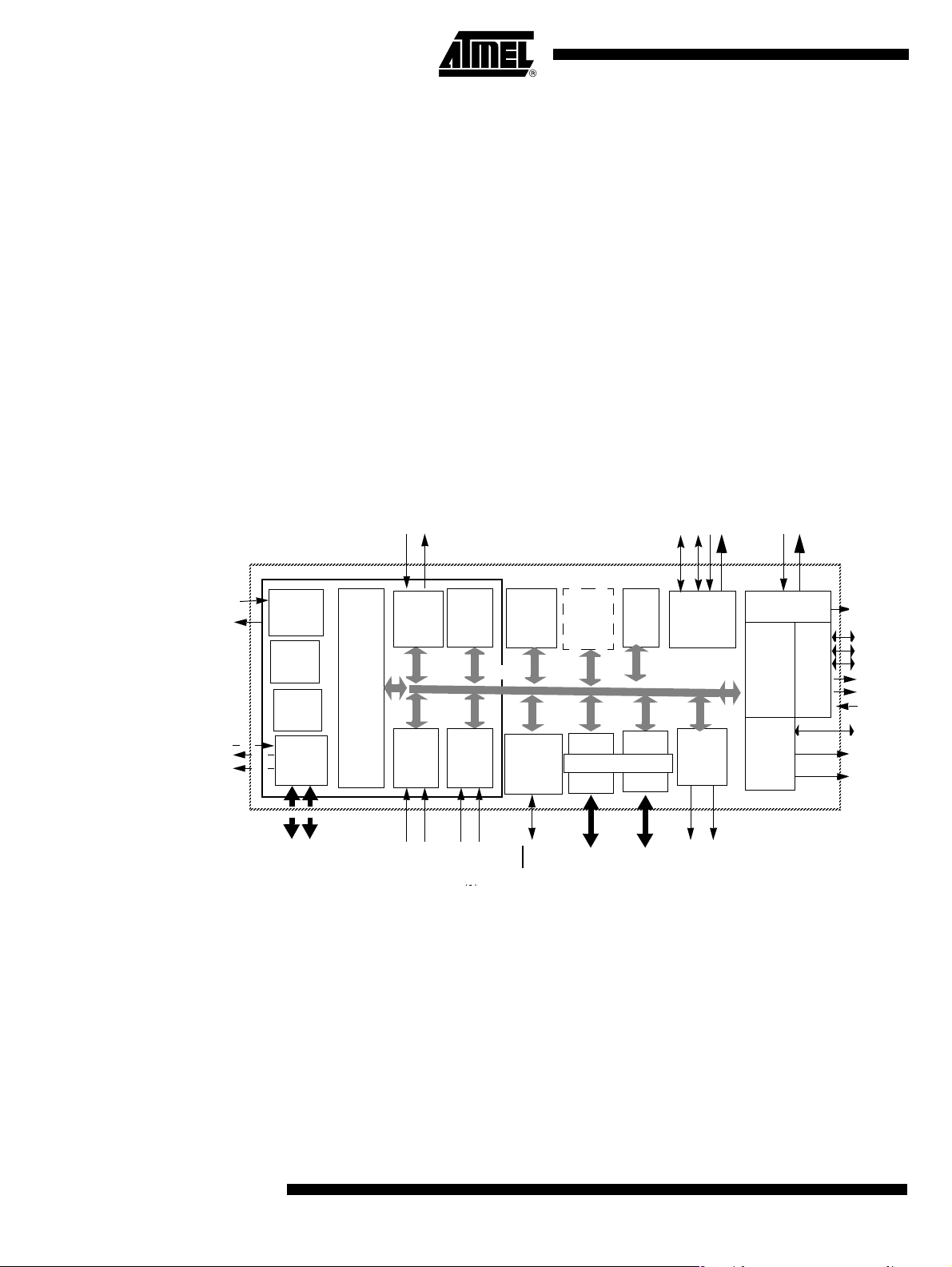

A/T8xC5121

Description T8xC5121 is a high performance CMOS ROM/CRAM derivative of the 80C51 CMOS

single chip 8-bit microcontrollers.

T8xC5121 retains the features of the Atmel 80C51 with extended ROM capacity (16

Kbytes), 512 bytes of internal RAM, a 4-level interrupt system, two 16-bit timer/counters

(T0/T1), a full duplex enhanced UART (EUART) with baud rate generator (BRG) and an

on-chip oscillator.

In addition, the T8xC5 121 have, a Multi protocol Smart Card Interface, a dual data

pointer, 2 programmable LED current sources (2-4-10 mA) and a hardware Watchdog.

T89C5121 Flash RAM vers ion and T85C5121 Cod e RAM version can be loaded by InSystem Programming (ISP) software residing in the on-chip ROM from a low-cost external serial EEPROM or from R232 interface.

T8xC5121 have 2 software-selectable modes of reduced activity for further reduction in

power consumption.

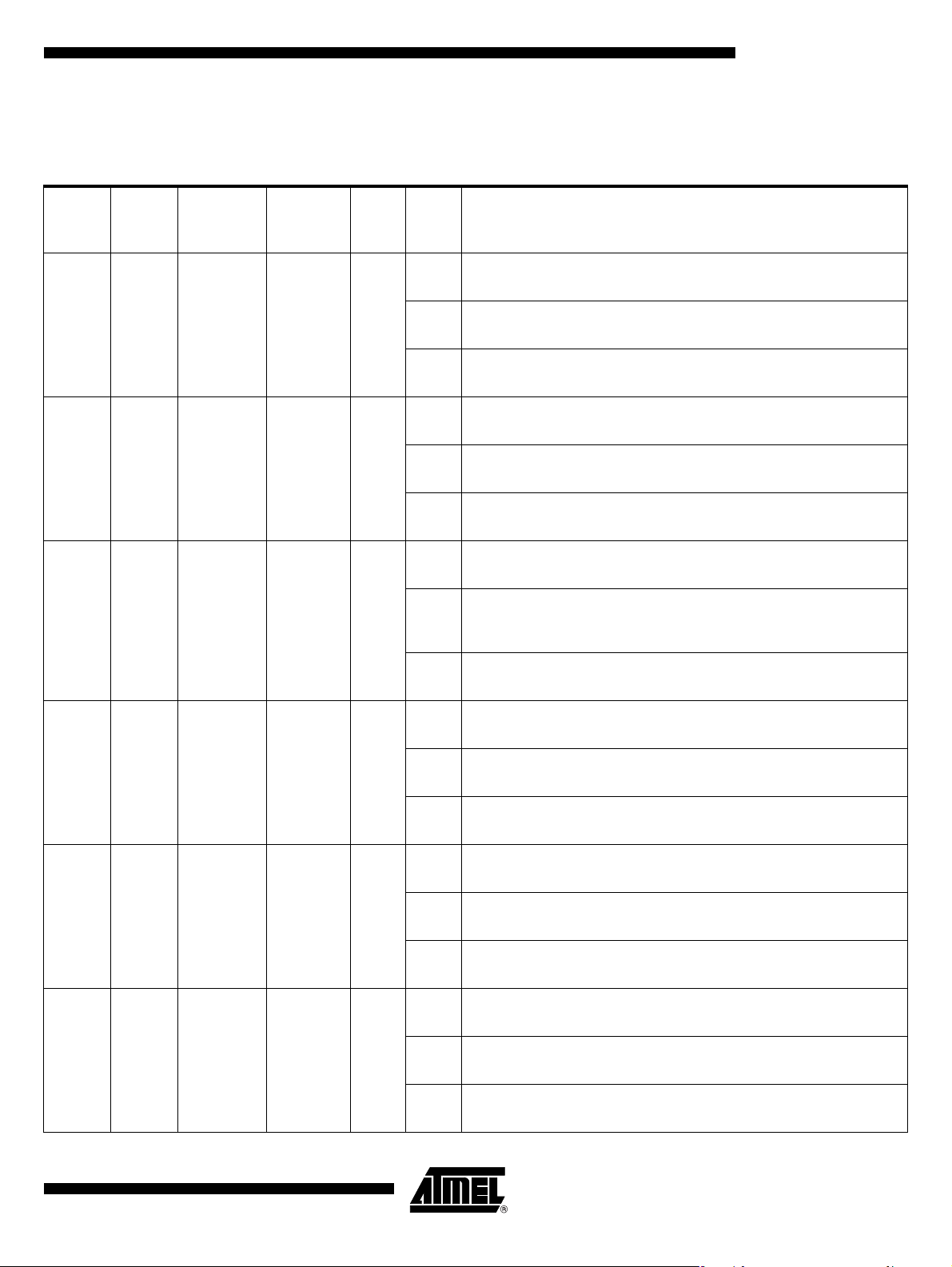

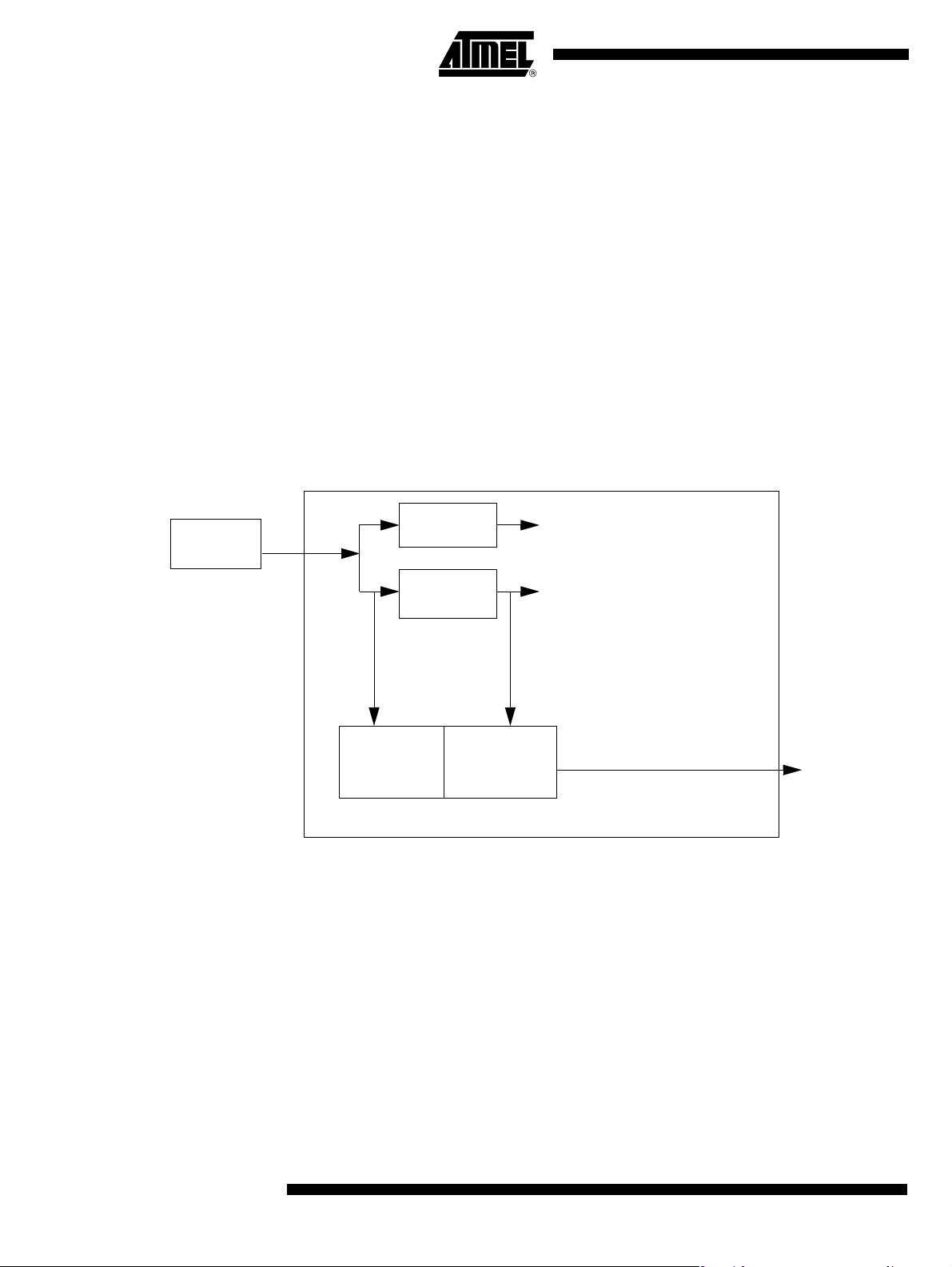

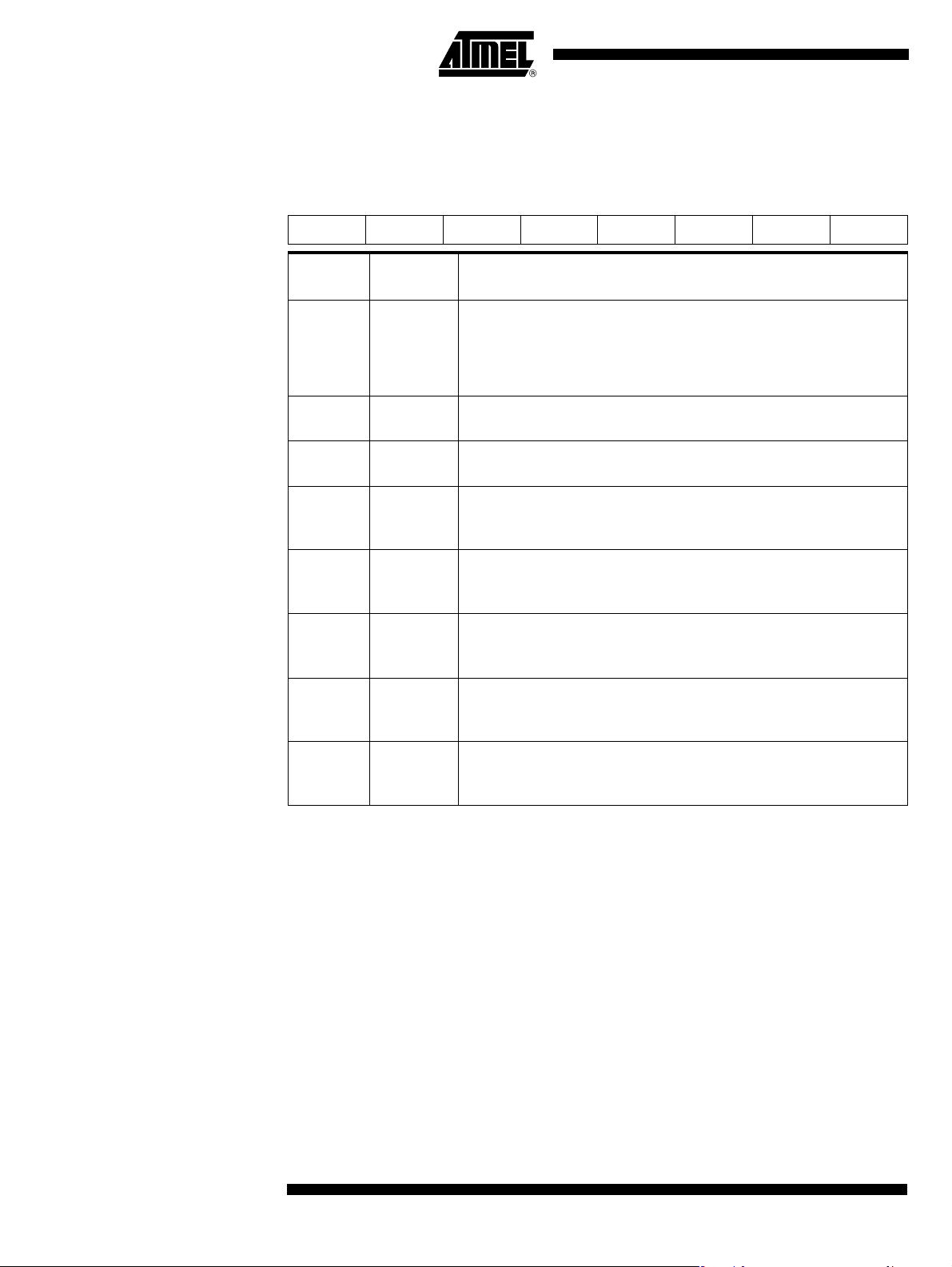

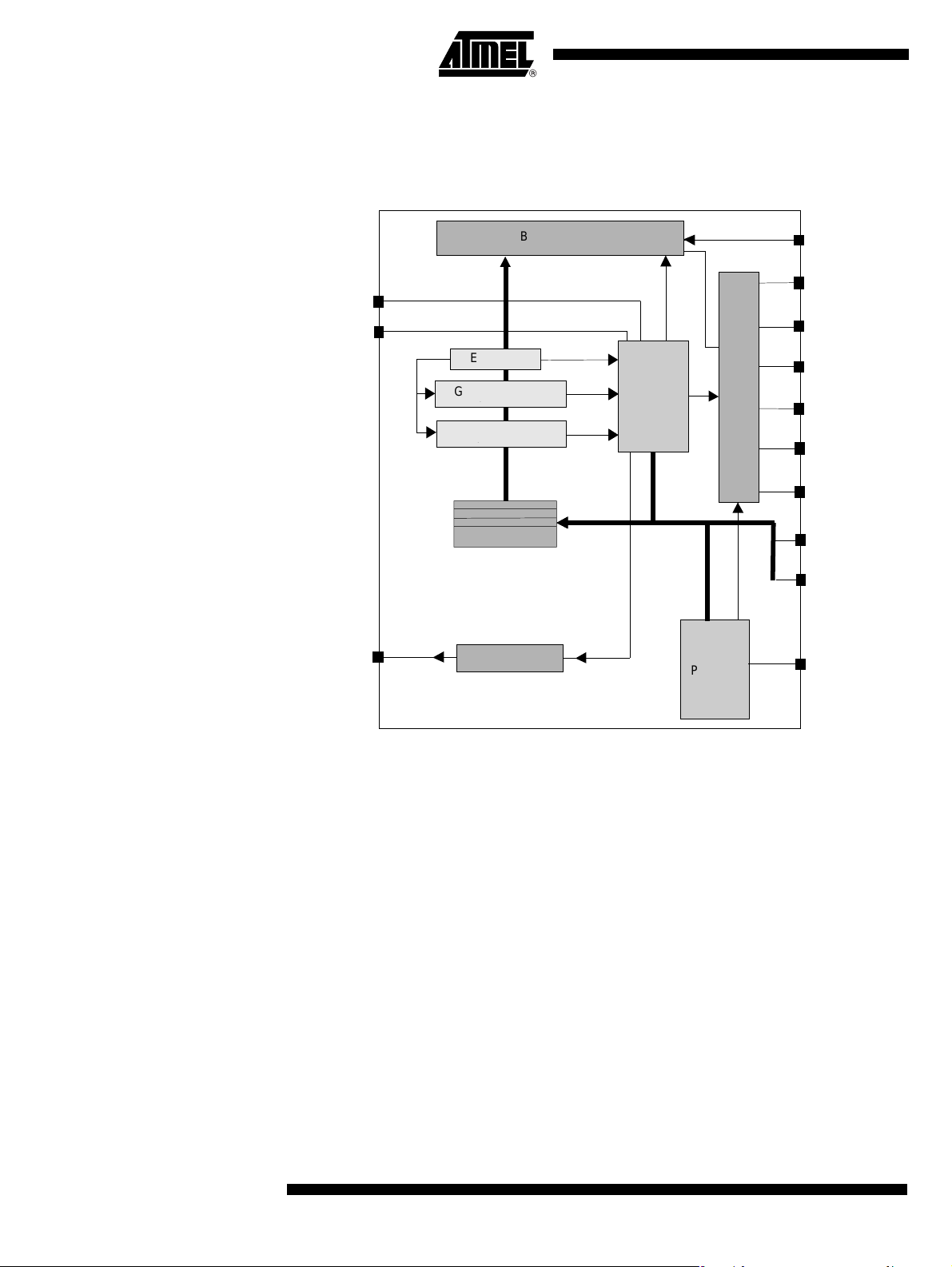

Block Diagram

Figure 1. Block Diagram

CC

CC

CC

V

DV

EV

VSS

LI

CVSS

(2) (2)

RxD

TxD

XTAL1

XTAL2

EA

PSEN

ALE

Xtal

Osc

:1-16

Clock

Prescaler

X2

(4)

P0

P2

CPU

EUART

BRG

Timer 0

Timer 1

(2)(2) (2)(2)

RAM

256 x8

C51

CORE

INT

Ctrl

T0

T1

INT1

INT0

Notes: 1. Alternate function of Port 1

2. Alternate function of Port 3

3. Only for the Code RAM version

4. Only for PLCC52

ROM

16K x8

IB-bus

Watchdog

POR

PFD

RST

(3)

CRAM

16K x8

6 I/Os

XRAM

256

x8

8 I/Os

Parallel I/O Ports

P1

P3

Voltage

Direct

Output

(2)

Reg.

Drive

LED

(2)

LED0

LED1

DC/DC

Converter

SCIB

Alternate

Card

Level

Shifters

(1)

(1)

(1)

(1)

(1)

(1)

CPRES

(2)

(2)

CRST1

(2)

CCLK1

CV

CC4

CC8

CIO

CRST

CCLK

CIO1

CC

2

4164G–SCR–07/06

Page 3

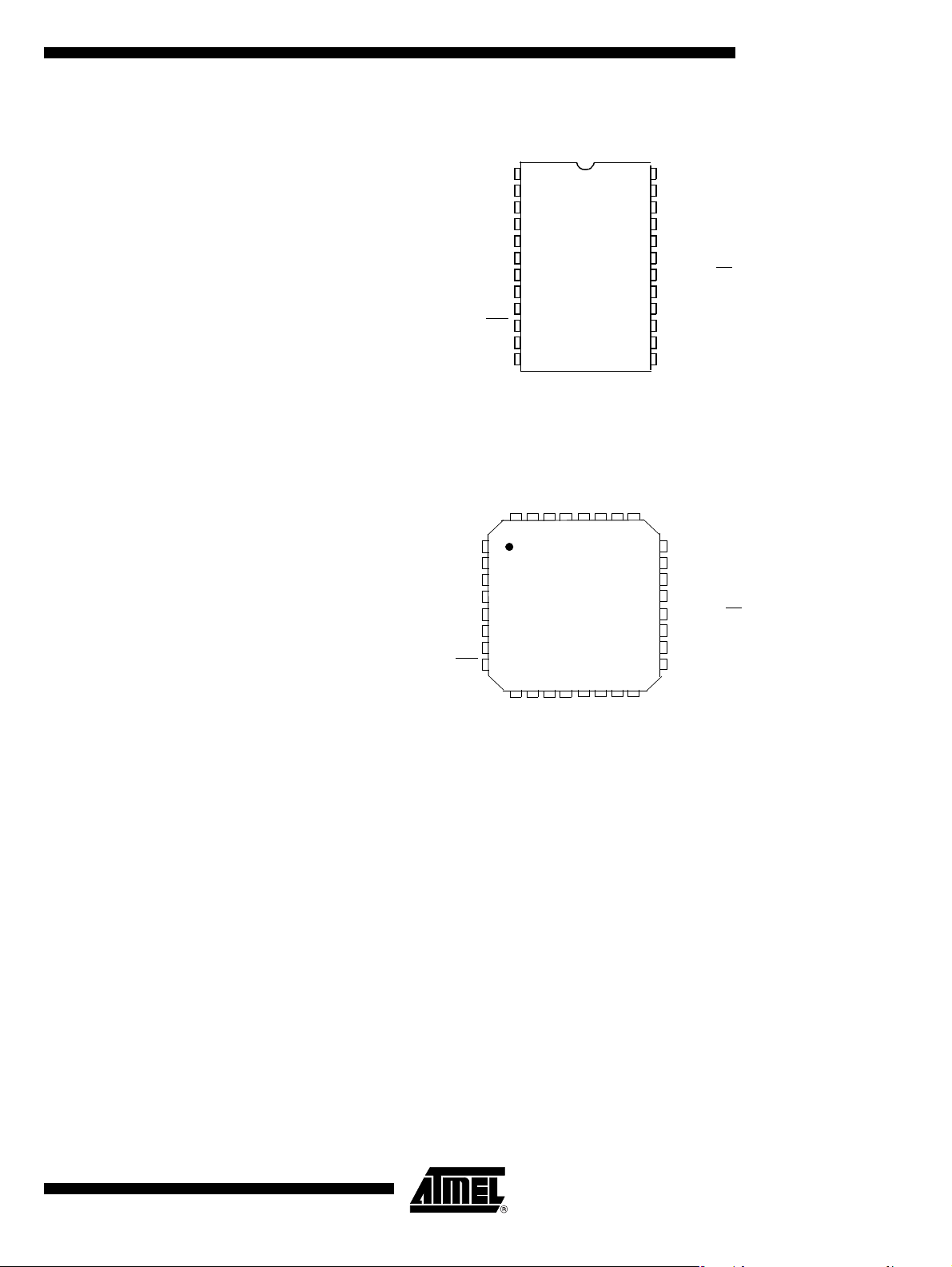

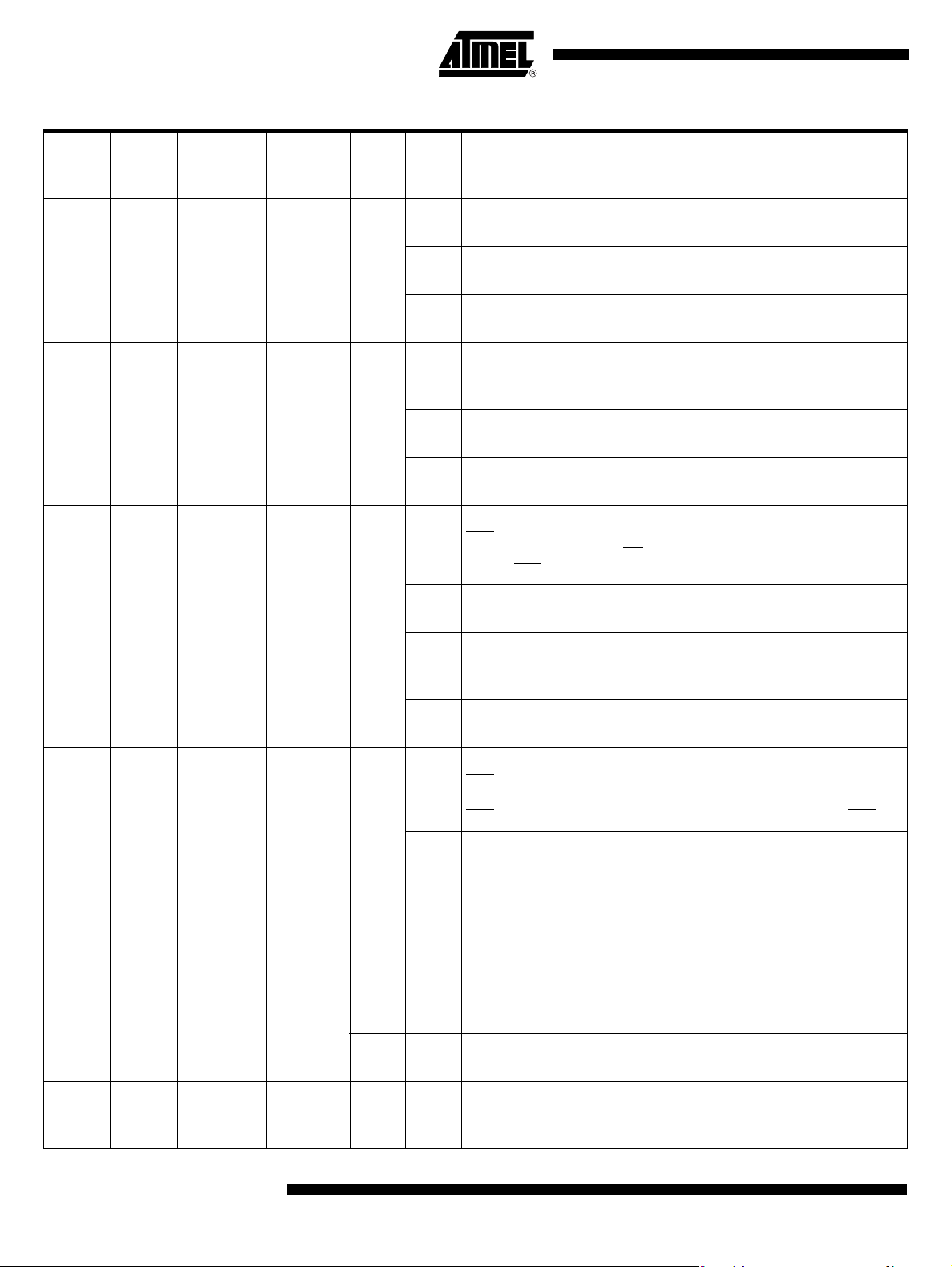

Pin Description Figure 2. 24-pin SSOP Pinout

A/T8xC5121

P1.5/CRST

P1.4/CCLK

P1.2/CPRES

Figure 3. QFN32 Pinout

CVcc

P1.5/CRST

P1.4/CCLK

P1.3/CC4

P1.2/CPRES

P1.1/CC8

P1.0/CIO

CVSS

V

C

P1.3/CC4

P1.1/CC8

P1.0/CIO

RST

XTAL2

XTAL1

RST

1

LI

2

3

CC

4

5

6

7

8

9

10

11

12

N/C

CVss

LI

N/C

28 27 26

1

2

3

4

5

QFN32

6

7

8

1211109131415

24

V

CC

23

EVCC

22

D

V

CC

21

VSS

P3.0/RxD

20

P3.1/TxD

19

P3.3/INT1/OE

18

P3.4/T0

17

P3.2/INT0

16

P3.5/CIO1/T1

15

14

P3.6/CCLK1/LED0

P3.7/CRST1/LED1

13

Vcc

EVcc

N/C

DVcc

2529303132

Vss

24

Vss

23

P3.0/RxD

22

P3.1/TxD

21

P3.3/INT1/OE

20

P3.4/T0

19

P3.2/INT0

18

P3.5/CIO1/T1

17

16

N/C

N/C

N/C

XTAL2

XTAL1

P3.7/CRST1/LED1

N/C

P3.6/CCLK1/LED0

4164G–SCR–07/06

3

Page 4

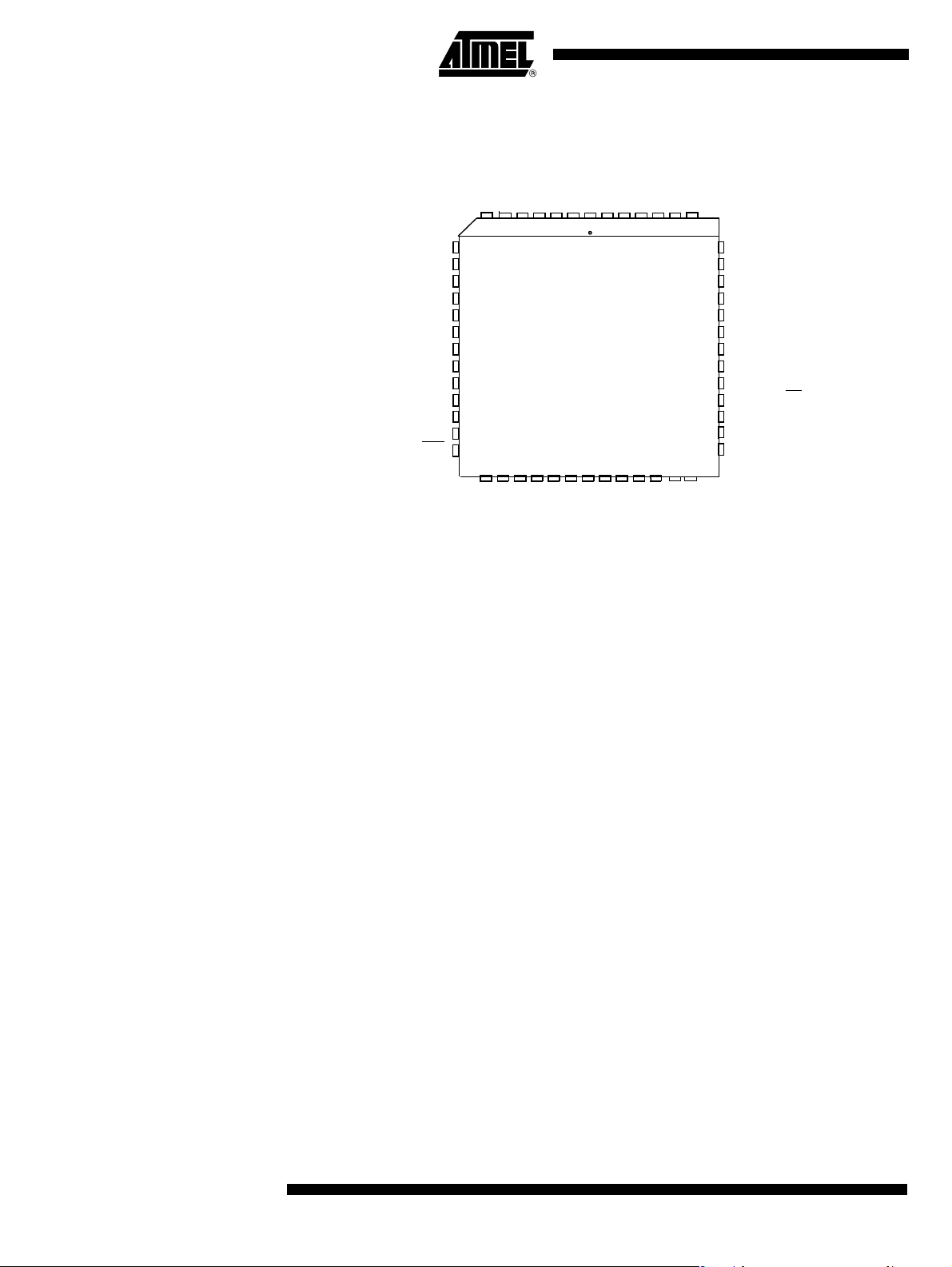

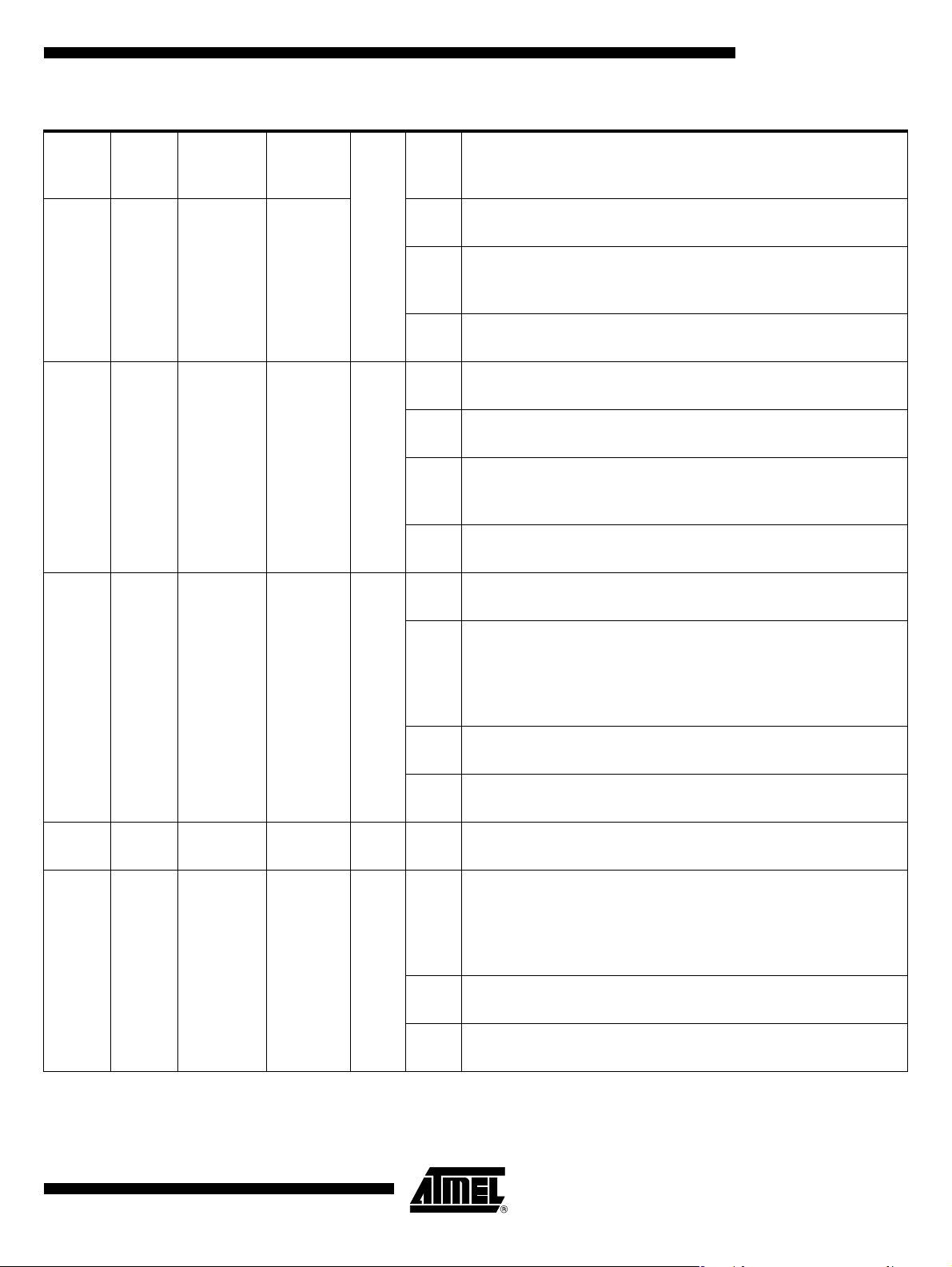

A/T8xC5121

Figure 4. PLCC52 Pinout

P1.4/CCLK

P1.3/CC4

EA

PSEN

ALE

P2.7/A15

P2.6/A14

P2.5/A13

P1.2/CPRES

P1.1/CC8

P1.0/CIO

P2.4/A12

RST

10

11

12

16

17

18

19

20

8

9

13

14

15

CC

V

NC

NC

C

P1.5/CRST

5 4 3 2 1 6

7

CVSS

LI

CC

NC

V

52 51 50 49 48

2122 26252423 292827 30 31

CC

VSS

V

XTAL1

XTAL2

P0.5/AD5

P2.1/A9

P2.3/A11

P2.2/A10

CC

V

E

P2.0/A8

NCNCNC

32 33

P0.7/AD7

P3.7/CRST1/LED1

NC

47

46

D

V

45

44

43

42

41

40

39

38

37

36

35

34

P0.4/AD4

P3.6/CCLK1/LED0

CC

VSS

P3.0/RxD

P3.1/TxD

P0.0/AD0

P0.1/AD1

P0.2/AD2

P0.3/AD3

P0.6/AD6

P3.3/INT1/OE

P3.4/T0

P3.2/INT0

P3.5/CIO1/T1

4

4164G–SCR–07/06

Page 5

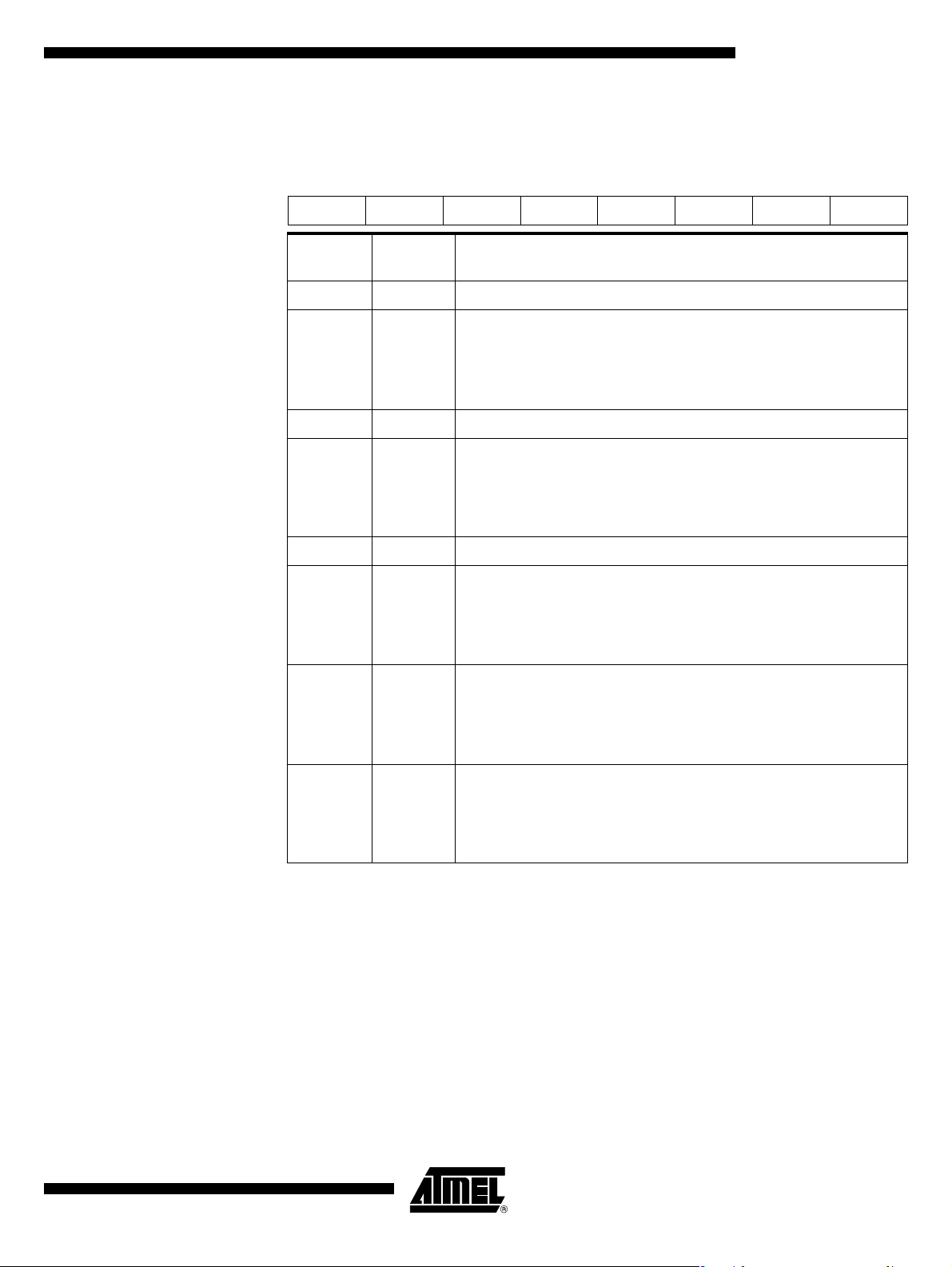

Signals All the T8xC5121 signals are detailed in Table 1.

The port structure is described in Section “Port Structure Description”.

Table 1. Ports Description

Internal

Power

Supply ESD Type Description

Port

Signal

Name Alternate

A/T8xC5121

P1.0 CIO CV

P1.1 CC8 CV

P1.2 CPRES V

P1.3 CC4 CV

CC

CC

CC

CC

4 kV I/O

I/O

4 kV O

O

4 kV I

I/O

4 kV O

Smart ca rd interf ace function

Card I/O.

Input/Out p ut func tion

P1.0 is a bi-directional I/O port .

Reset co nfiguration

I

Input .

Smart ca rd interf ace function

Card contact 8

Output function

P1.1 is a Push-pull port.

Reset co nfiguration

I

Input

Smart ca rd interf ace function

Card presence

Input/Out p ut func tion

P1.2 is a bi-directional I/O port with internal pull-ups- ( External Pull-up

configuration can be selected).

Reset co nfiguration

I

Input (high leve l due to internal pu ll-up)

Smart ca rd interf ace function

Card contact 4

P1.4 CCLK CV

P1.5 CRST CV

4164G–SCR–07/06

CC

CC

4 kV O

I/O

4 kV O

I/O

Output function

O

P1.3 is a Push-pull port.

Reset co nfiguration

I

Input (high leve l due to internal pu ll-up)

Smart ca rd interf ace function

Card clock

Input/Out p ut func tion

P1.4 is a a Push-pull port.

Reset co nfiguration

O

Output at low level

Smart ca rd interf ace function

Card reset

Input/Out p ut func tion

P1.5 is a a Push-pull port.

Reset co nfiguration

O

Output at low level

5

Page 6

A/T8xC5121

Table 1. Ports Description (Continued)

Internal

Power

Supply ESD Type Description

Port

Signal

Name Alternate

P3.0 RxD EV

P3.1 TxD EV

P3.2 INT0 DV

CC

CC

CC

UART function

I

Receive data input

Input/Out p ut func tion

I/O

P3.0 is a bi-directional I/O port with internal pull-ups.

Reset co nfiguration

I

Input ( high level)

UART function

O

Transmit data output

OE active at low or high level depending of PMSO EN bits in SIOCON Reg.

Input/Out p ut func tion

I/O

P3.1 is a bi-directional I/O port with internal pull-ups.

Reset co nfiguration

Z

High impedance due to PMOS switched OFF

External interrupt 0

input set IE0 in the TCON register. If bit IT0 in this register is set, bits IE0

INT0

I

are set by a falling edge on INT

level on INT0

Input/Out p ut func tion

I/O

P3.2 is a bi-directional I/O port with internal pull-ups.

Timer 0: Gate input

I

INT0 serves as external run control for Timer 0 when

select ed in TCON register.

.

0. If bit IT0 is cleared, bits IE0 is set by a low

P3.3 INT1 OE EV

P3.4 T0 EV

Reset co nfiguration

I

Input ( high level)

External Interrupt 1

INT1

CC

CC

I

I

I/O

I

I

O

input set OEIT in ISEL Register, IE1 in the TCON register.

If bit IT1 in this register is set, bits OEIT and IE1 are set by a falling edge on

. If bit IT1 is cleared, bits OEIT and IE1 is set by a low level on INT1

INT1

UART function

Output enable. A low or high level (depending OELEV bit in

ISEL Register) on this pin disables the PMOS transistors of TxD

(P3.1) and T0 (P3.4). This function can be disabled by sof tware

Input/Out p ut func tion

P3.3 is a bi-directional I/O port with internal pull-ups.

Timer 1 function: Gate input

INT1 serves as external run control for Timer 1 when

select ed in TCON register.

Reset co nfiguration

Input ( high level)

UART function

OE active at low or high level depending of PMSOEN

bits in SIOCON Reg.

6

4164G–SCR–07/06

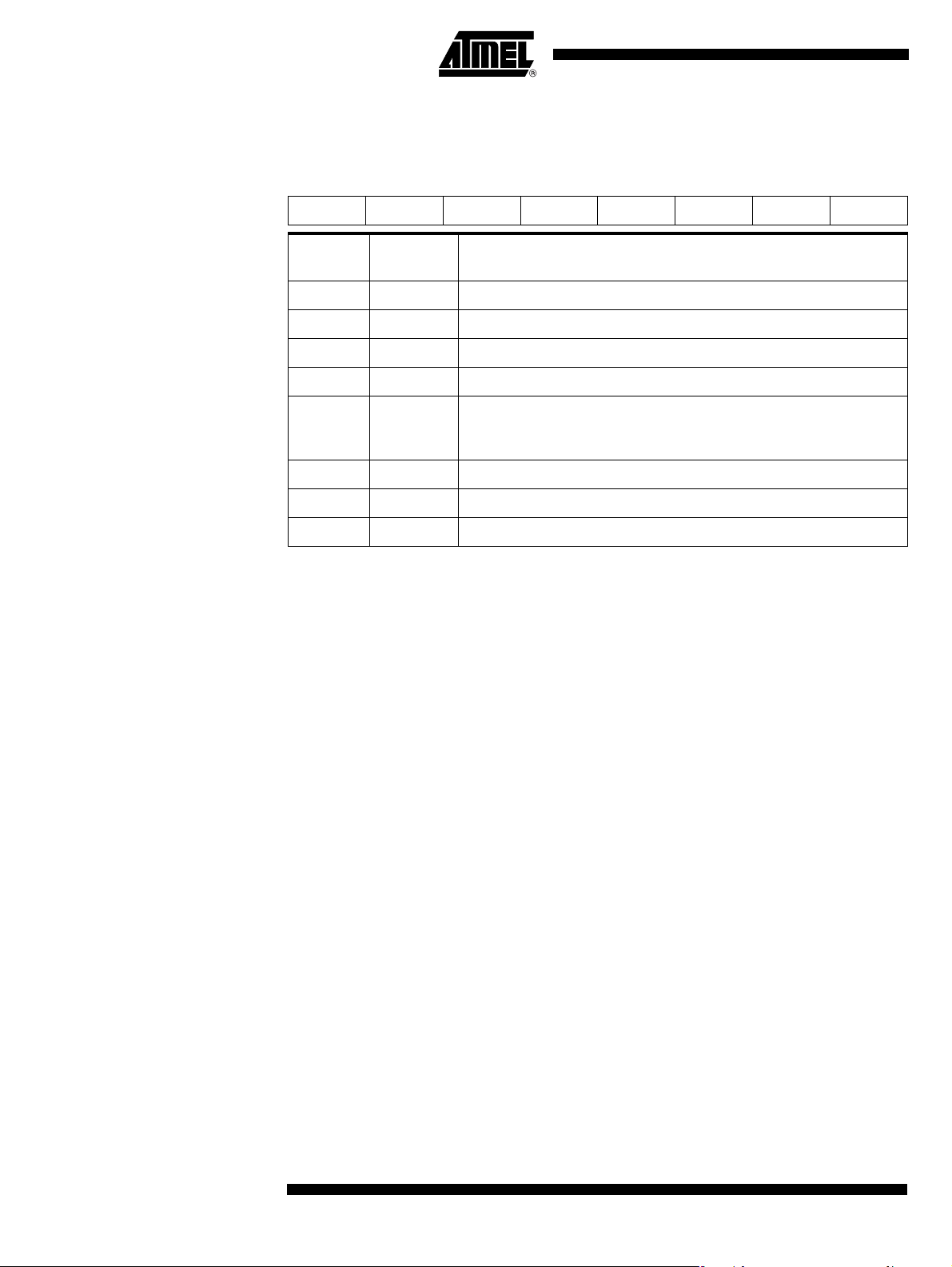

Page 7

Table 1. Ports Description (Continued)

Internal

Signal

Port

P3.5 CIO1 DV

Name Alternate

Power

Supply ESD Type Description

CC

Input/Out p ut func tion

I/O

P3.4 is a bi-directional I/O port with internal pull-ups.

Timer 0 function: External clock input

I

When Timer 0 operates as a counter, a falling edge on the T0 pin

increments the count.

Reset co nfiguration

Z

High impedance due to PMOS switched OFF

Alternate card function

I/O

Card I/O

Input/Out p ut func tion

I/O

P3.5 is a bi-directional I/O port with internal pull-ups.

Timer 1 function: External clock input

I

When Timer 1 operates as a counter, a falling edge on the T1 pin

increments the count.

A/T8xC5121

P3.6 CCLK1 LED0 DV

P3.7 CRST1 DV

P3.7 CRST1 LED1 DV

CC

CC

CC

Reset co nfiguration

I

Input (high leve l due to internal pu ll-up)

Alternate card function

O

Card clock

LED function

Thes e pin s ca n be directly connecte d to t h e cat hode of standa r d

O

LED without external current limitin g resistor s. The typical current

of each output can be programmed by software to 2, 4 or 10 mA

(LEDCON register).

Input/Out p ut func tion

I/O

P3.6 is a LED port.

Reset co nfiguration

I

Input at high level

Alternate card function

O

Card reset

O LED function

Thes e pin s ca n be directly connecte d to t h e cat hode of standa r d

LED without external current limitin g resistor s. The typical current

of each output can be programmed by software to 2, 4 or 10 mA

(LEDCON register).

I/O Input/Out p ut func tion

P3.7 is a a LED port.

4164G–SCR–07/06

I Reset configuration

Input at high level

7

Page 8

A/T8xC5121

Table 1. Ports Description (Continued)

Internal

Power

Supply ESD Type Description

Port

Signal

Name Alternate

RST V

CC

I/O Reset input

Holding this pin low for 64 oscillator periods while the oscillator

is running reset s the device. The Po rt pins are driven to their reset

cond iti on s w he n a vo ltag e lower than V

not the os cillator is running.

This pin has an internal pull-up resistor which allows the device to be reset by

connecting a capacitor between this pin and VSS.This capacitor is optional

thanks to the internal POR which output a Reset as long as Vcc has not

reached the POR threshold level

Asserting RST

return s the chip to normal op eration.

The output is active for at least 12 oscillator periods when an internal

reset occurs.

XTAL1 V

CC

I Input to the on-chip inverting oscillator amplifier

T o use the internal oscillator, a crystal/resonator circuit is connected

to this pin.

If an external oscillator is used, its output is connec ted to this pin.

XTAL2 V

CC

O Output of the on-chip inverting oscillator amplifier

T o use the internal oscillator, a crystal/resonator circuit is connected

to this pin.

If an external oscillator is used, XTAL2 may be lef t unconnected.

V

CC

PWR Supply voltage

is used to power the internal voltage regulators and internal I/O’s.

V

CC

LI PWR DC/DC input

LI must be tied to V

the curr ent for the pump charge of the DC/DC converter.

is applied, whether or

IL

when the chip is in Idle mode or Power-down mode

through an external coil (typically 4, 7 μH) and provi de

CC

CV

CC

PWR Card Sup ply voltage

is the programmable voltage output for the Card interface.

CV

CC

It must be connected to an external decoupling capacitor.

DV

CC

PWR Digital Sup ply voltage

is used to supply the digital core and internal I/Os. It is

DV

CC

interna ll y co nnect e d to the ou tp ut of a 3V re gul a tor and must be co nn ec ted t o

an exte rn a l de co upling capa ci t o r.

EV

CC

V

CC

PWR Extra supply voltage

is used to supply the level shifters of UART interface I/O

EV

CC

pins. It must be connected to an external decoupling capacitor.

This reference voltage is generated internally (automatically or not),

or it can be connected to an external voltage reference.

CVSS GND DC/DC ground

CVSS is used to sink high shunt currents from the external coil.

VSS GND Ground

8

4164G–SCR–07/06

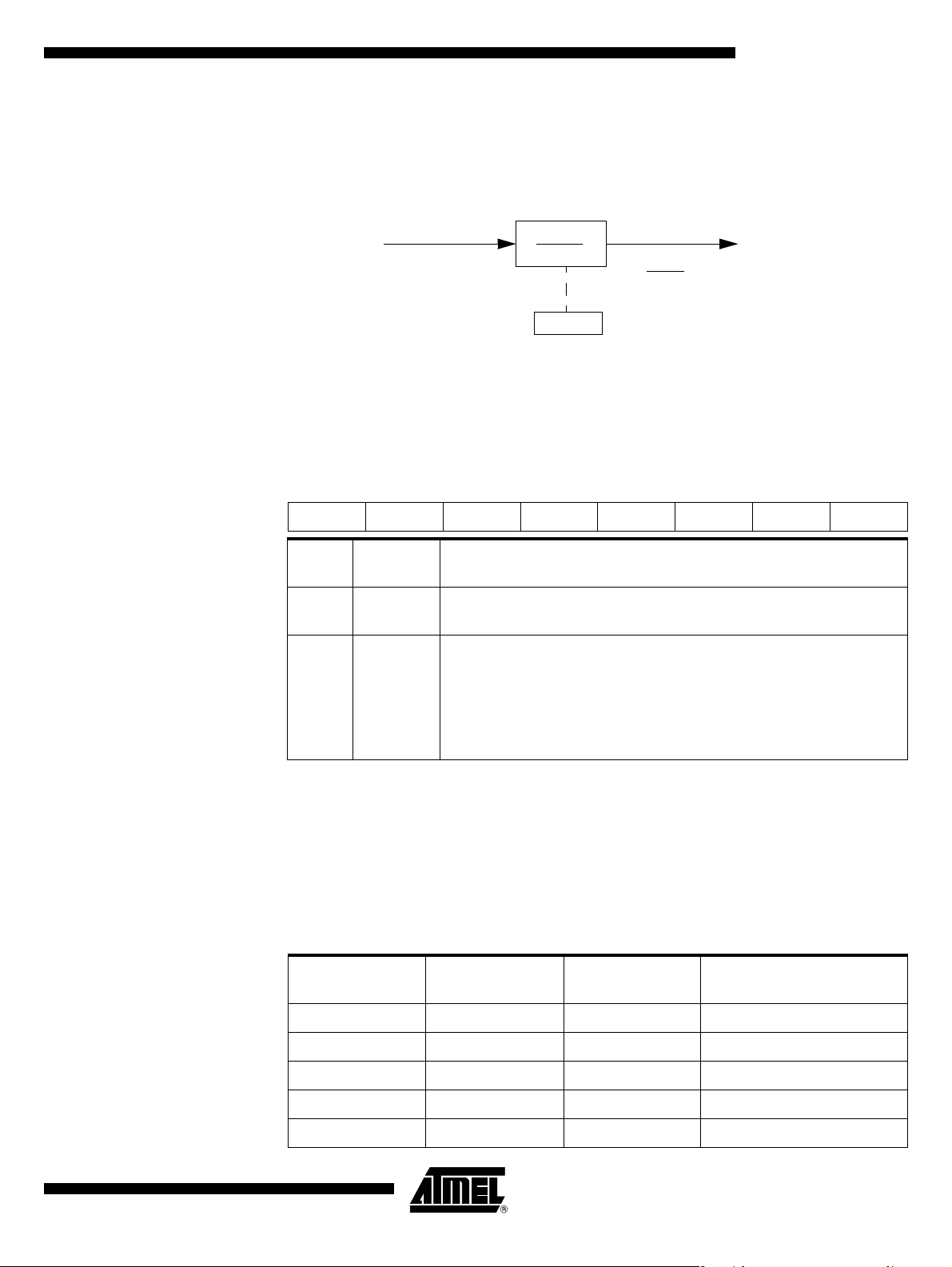

Page 9

Table 1. Ports Description (Continued)

Internal

Signal

Port

Name Alternate

ONLY FOR PLCC52 version

Power

Supply ESD Type Description

A/T8xC5121

P0[7:0] AD[7:0] V

P2[7:0] A[15:8] V

P3.6 WR DV

P3.7 RD DV

ALE V

PSEN PSEN V

EA EA V

CC

CC

CC

CC

CC

CC

CC

I/O Input/Output function Port 0

P0 is an 8-bit open-drain bi-directional I/O port. Port 0 pins that

have 1s written to them float and can be used as high impedance

inputs. T o avoid any parasitic current consumption, Floating P0

inputs must be pulled to V

CC

or VSS.

I/O Address/Data low

Mutiplexed Address/Data LSB for external access

I/O Input/Output function Port 2

P2 is an 8-bit open-drain bi-directional I/O port with internal pull-ups

O Address high

Address Bus MSB for external access

O Write signal

Write signal asserted during external data memory write operation

I Read signal

Read signal asserted during external data memory read operation

O Address latch enable output

The falling edge of ALE strobes the address into e x ternal latch

O Program strobe en ab le

I External access enable

This pin must be held low to force the device to fetch code from

external progra m memory starting at address 0000h. It is la tched

during reset and cannot be dynamicall y changed during operation.

4164G–SCR–07/06

9

Page 10

A/T8xC5121

Port Structure

The different ports structures are described as follows.

Description

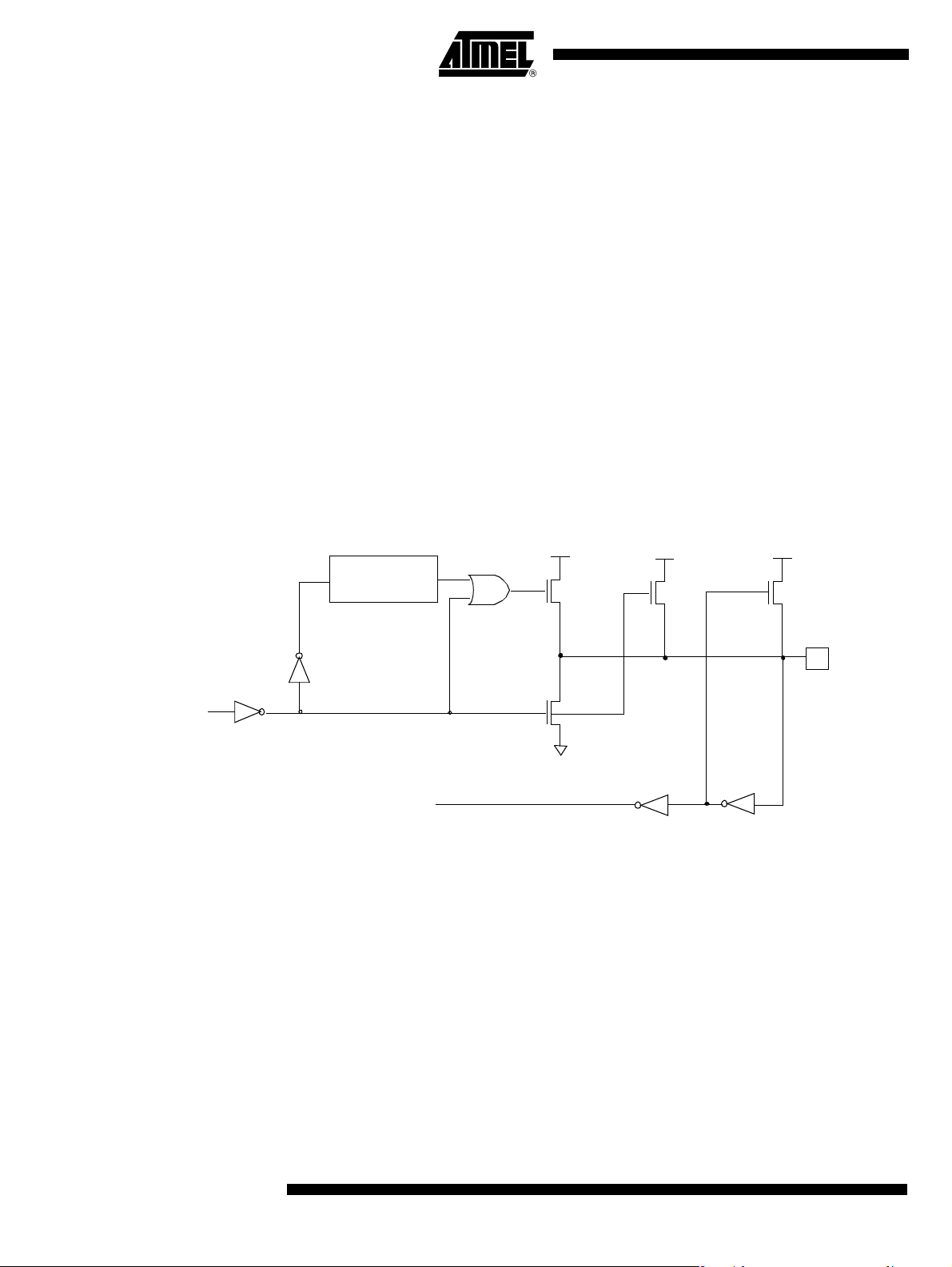

Quasi Bi-directional Output Configuration

Figure 5. Quasi Bi-directional Output Configuration

The default port output configuration for standard I/O ports is the quasi bi-directional output that is comm on on the 80 C5 1 an d mo st o f its de rivati ve s. Thi s o utput ty pe ca n b e

used as both an input and output without the need t o reconfigure the port. This is possible because whe n t he port out puts a l ogic h igh, it i s weak ly driven, al lowing an external

device to p ull th e pi n low . Wh en the po rt o utput s a lo gic l ow s tate , it is driv en s trongl y

and able to sink a fai rly large current . These fe atures are so mewhat sim ilar to an ope n

drain output except that there are three pull-up transistors in the quasi bi-directional output that serve different purposes. One of these pull-ups, called the weak pull-up, is

turned o n wheneve r the po rt latch for the pin contains a logic 1. The weak pull-up

sources a very sm all current th at will pull the pin high if it is left floating . A secon d pullup, called the medium pull-up, is turned on when the port latch for the pin contains a

logic 1 and the pin itself is also at a logic 1 level. This pull-u p provides the primary

source current for a quasi bi-directional pin that is outputting a 1. If a pin that has a logic

1 on it is pull ed low by a n ex ternal d evice , the m edi um pul l-up tu rns off, and only the

weak pull-up remains on. In order to pull the pin low under these conditions, the external

device has to sink enough current to overpower the medium pull-up and take the voltage

on the port pin below its input threshold.

2 CPU

CLOCK DELAY

PMOS

P

Strong

P

Weak

P

Medium

Port latch

Data

Push-pull Out p ut Configuration

Pin

N

NMOS

Input

Data

The Push-pull output configuration has the same pull-down structure as the quasi bidirection al outp ut mod es, bu t prov ide s a cont inuou s strong pull- up w hen the p ort la tch

contains a l ogic 1. The P ush-pull mod e may be use d when more source curre nt is

needed from a port output. The Push-pull port configuration is shown in Figure 5.

10

4164G–SCR–07/06

Page 11

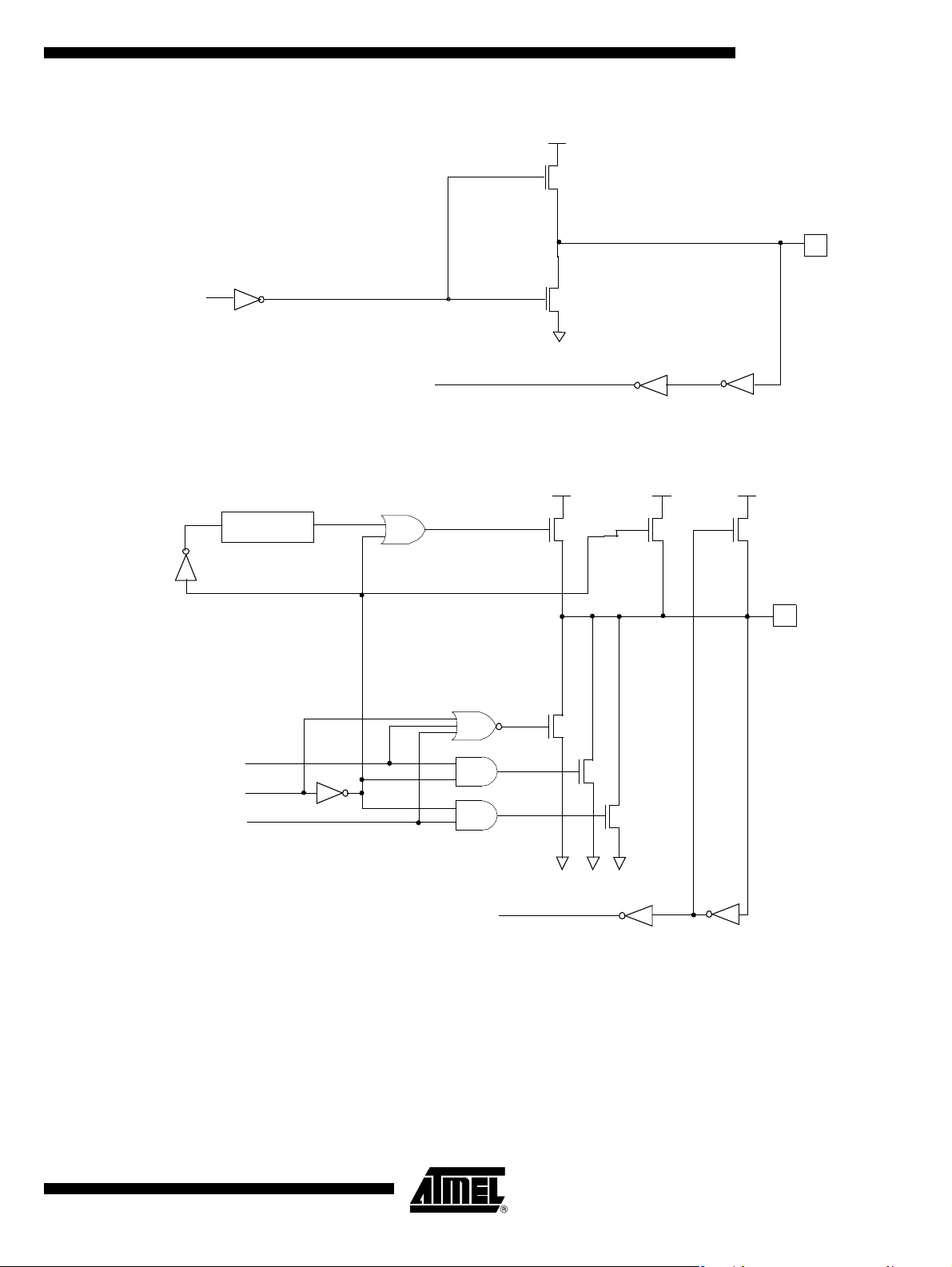

Figure 6. Push-pull Output Configuration

PMOS

A/T8xC5121

P

Strong

Port latch

Data

N

NMOS

Input

Data

LED Output C on f ig urat i on The input only configuration is shown in Figure 7. Figure 7. LED Source Current Configuration

2 CPU

CLOCK DELAY

PMOS

NMOS

P

Strong

N

P

Weak

Pin

P

Medium

Pin

LEDx.0

Port Latch

Data

LEDx.1

Input

Data

Note: The port can be configured in quasi bi-directional mode and the level of current can be programmed by means of LEDCON0

and LEDCON1 registe rs before switching the led on by writing a logical 0 in Port latch.

LED1CTRL

LED2CTRL

N

N

11

4164G–SCR–07/06

Page 12

A/T8xC5121

SFR Mapping The Special Function Registers (SFR) of the T8xC5121 belongs to the following

categories:

• C51 core registers: ACC, B, DPH, DPL, PSW, SP

• I/O port registers: P0, P1, P2, P3

• Timer 0 registers: TCON, TH0, TH1, TMOD, TL0, TL1

• Serial I/O port registers: SADDR, SADEN, SBUF, SCON, BRL, BDRCON

• Power and clock control registers: PCON, CKRL, CKCON0, CKCON1, DCCKPS

• Interrupt system registers: IE0, IPL0, IPH0, IE1,IPL1, IPH1, ISEL

• Watchdog Timer 0: WDTRST, WDTPRG

• Others: AUXR, AUXR1, RCON

• Smart Card Interface: SCSR, SCC O N/ SCETU0, SCISR/SCETU1, SCIER/SCIIR,

SCTBUF/SCRBUF, SCGT0/SCWT0, SCGT1/SCWT1, SCICR/SCWT2

• Port configuration: SIOCON, LEDCON

12

4164G–SCR–07/06

Page 13

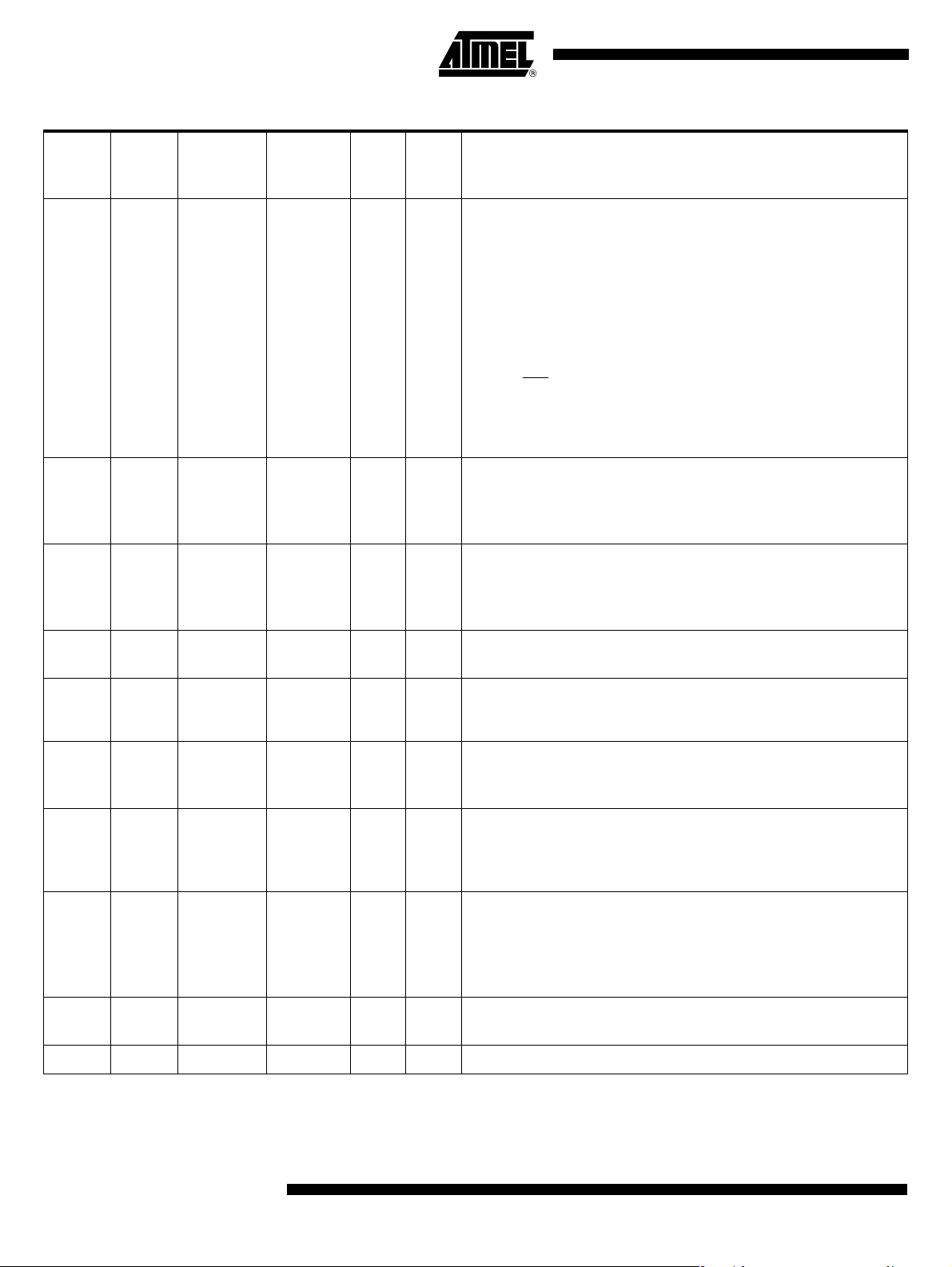

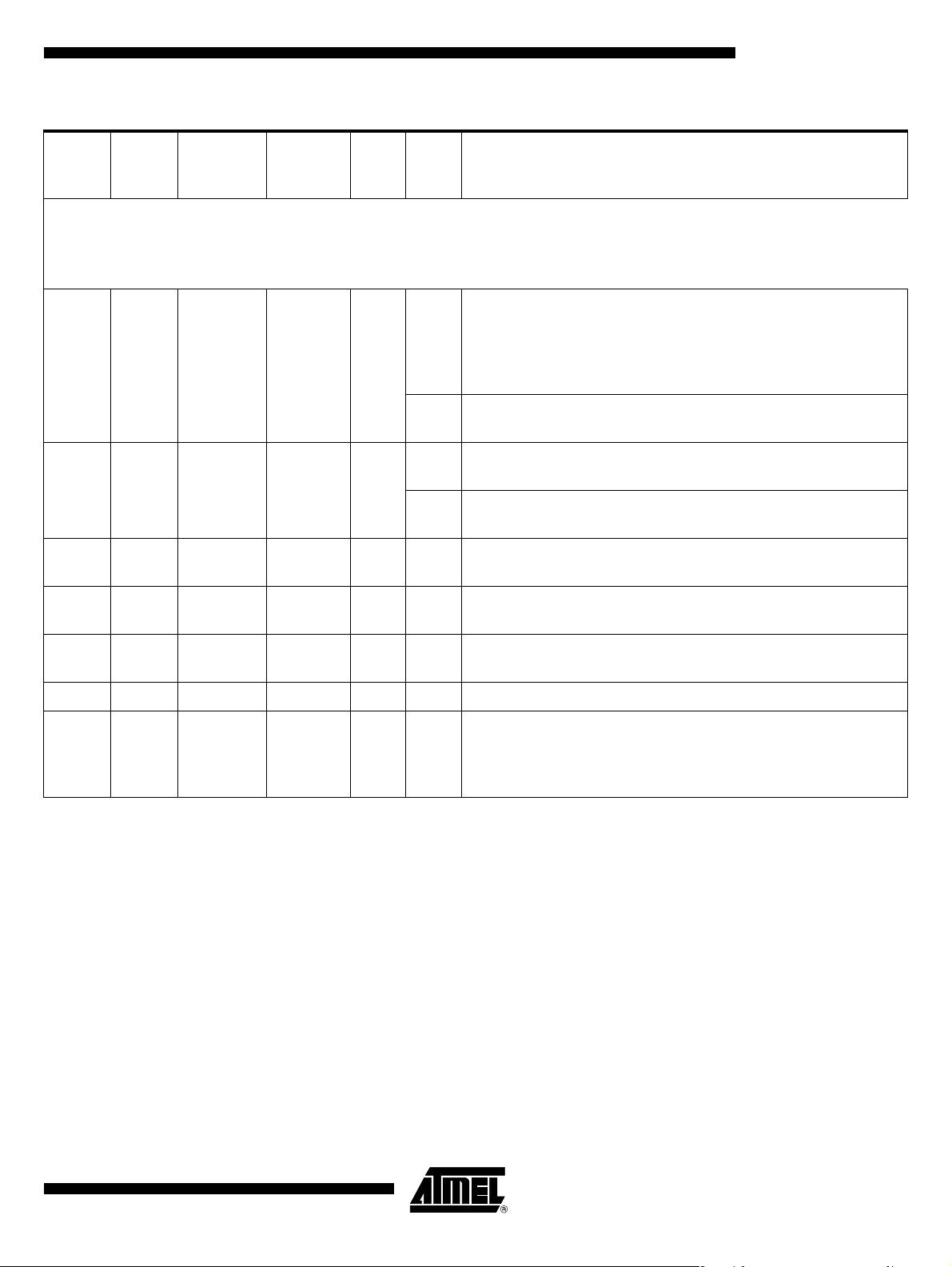

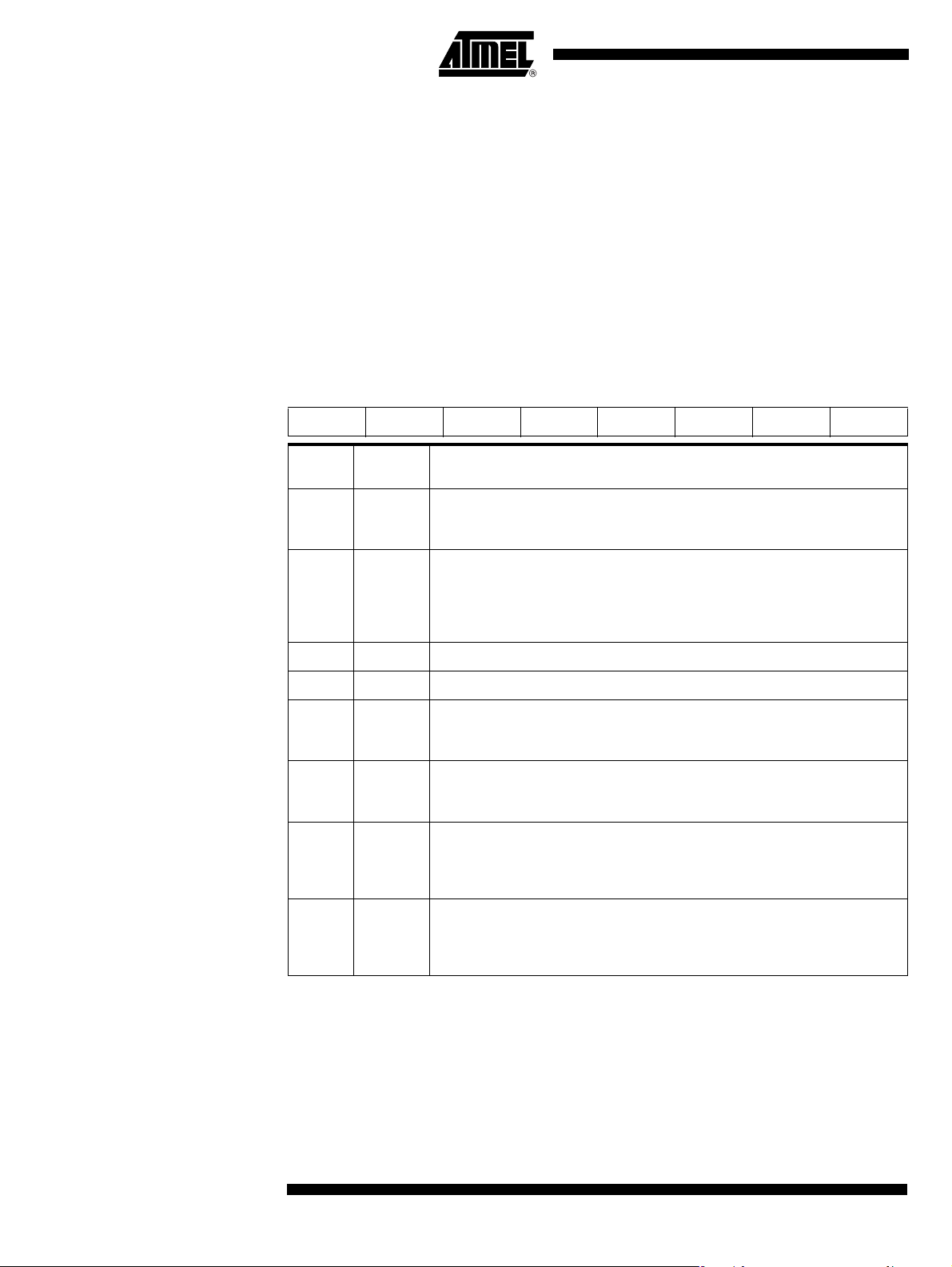

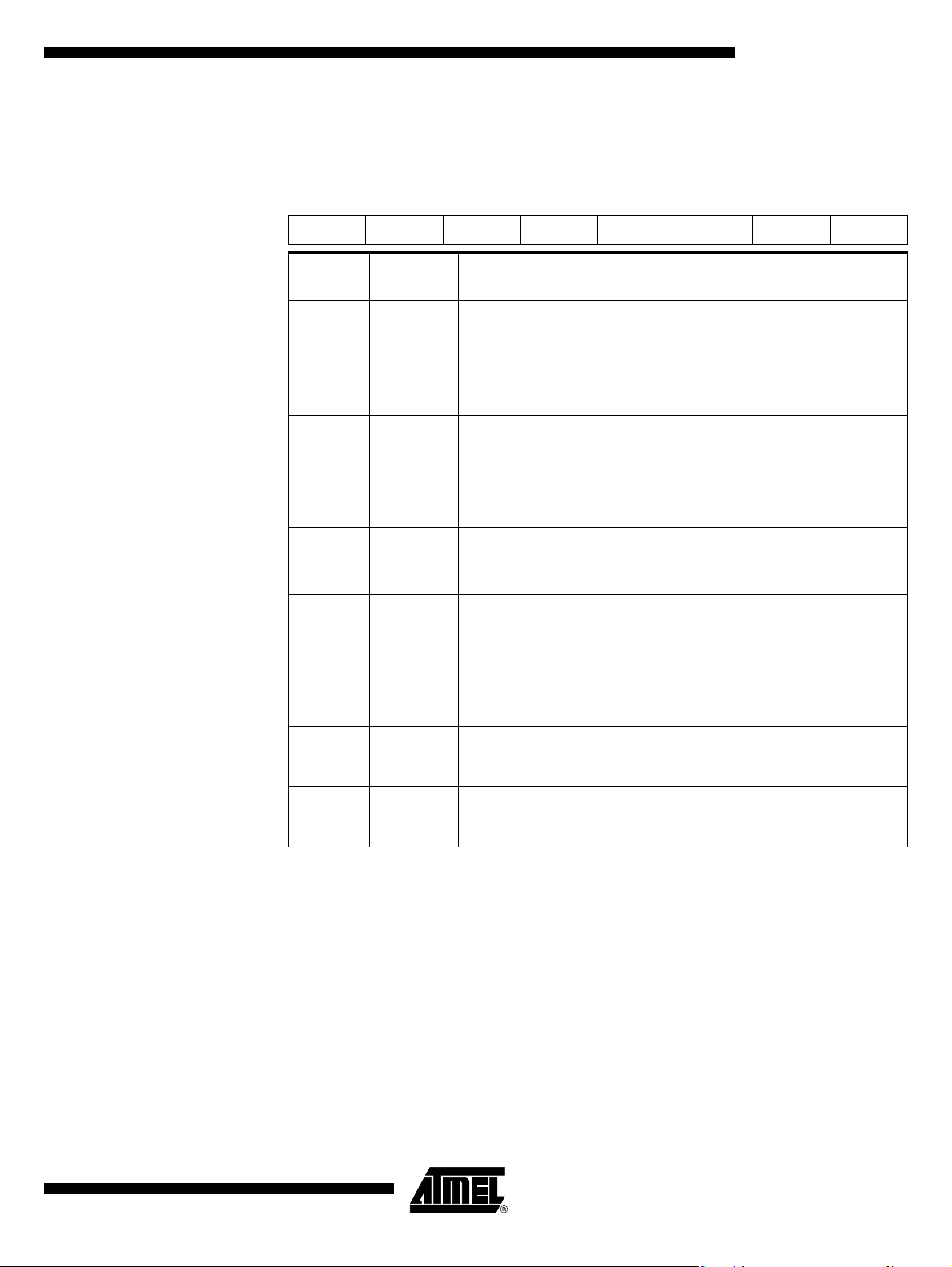

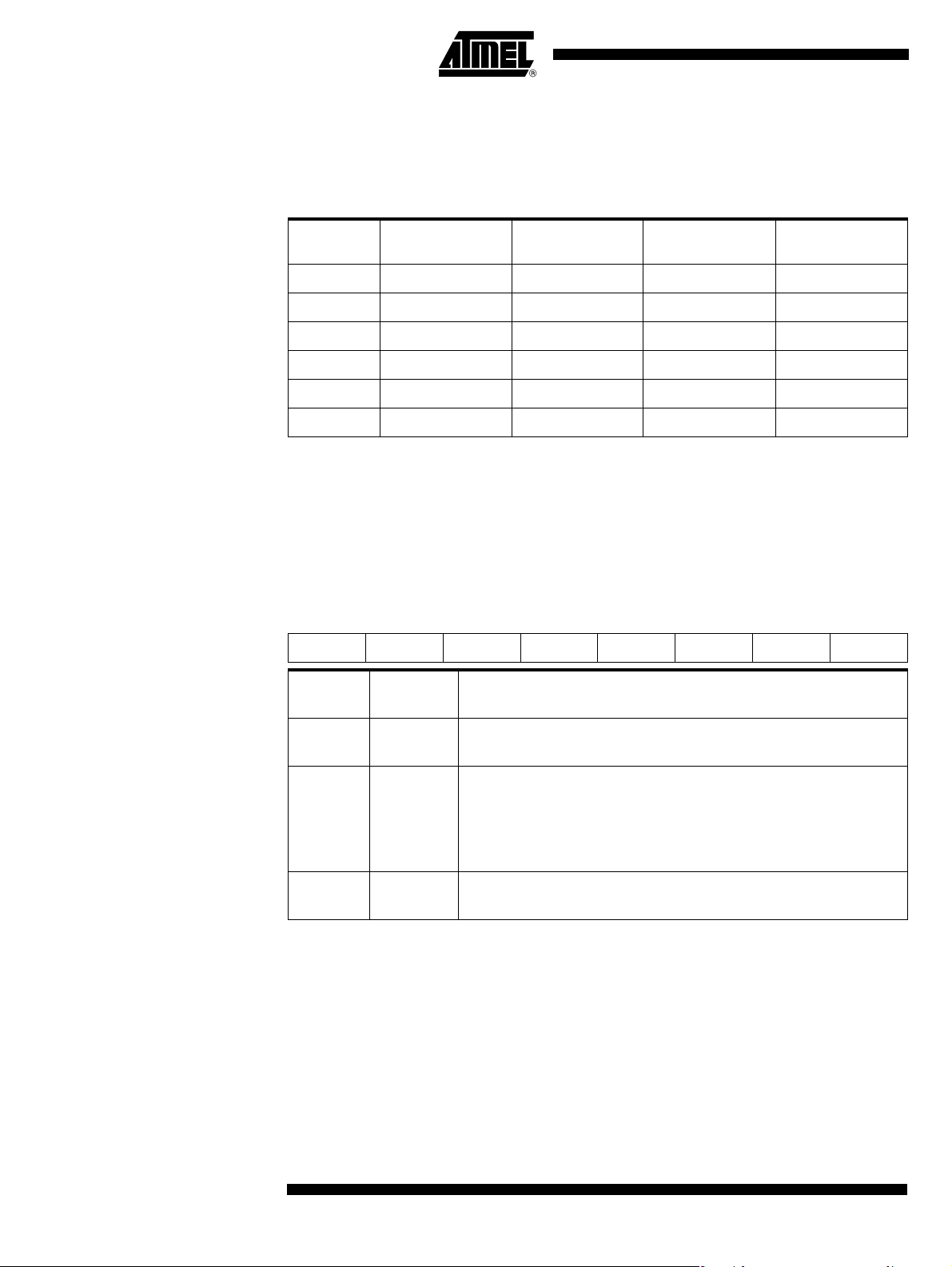

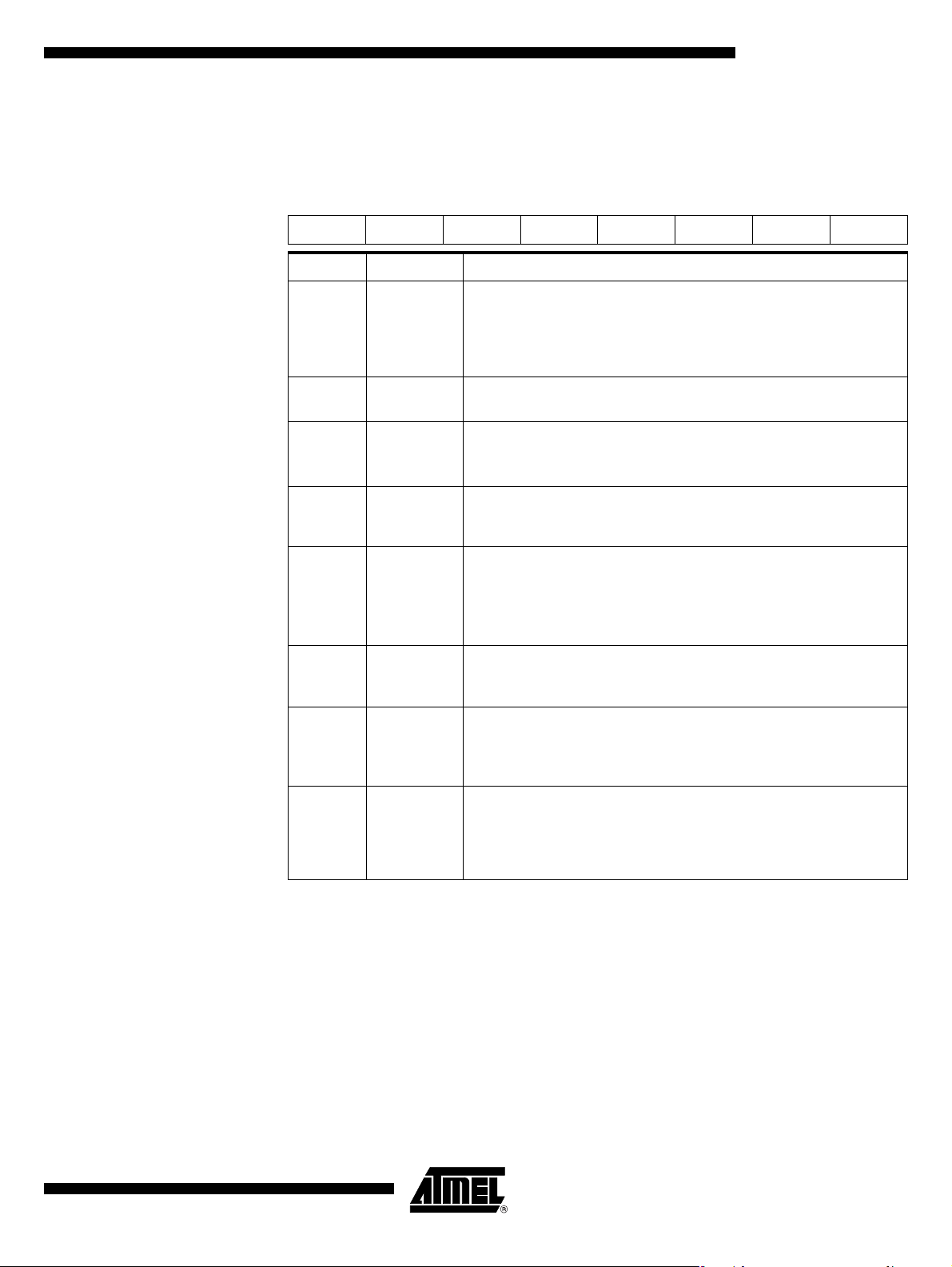

Table 2. SFR Addresses and Reset Values

0/8 1/9 2/A 3/B 4/C 5/D 6/E 7/F

A/T8xC5121

F8h

F0h B

0000 0000

E8h

E0h ACC

0000 0000

D8h

D0h PSW

0000 0000

C8h

C0h

B8h IPL0

XXX0 0000

B0h

A8h

P3

1111 1111

IE0

0XX0 0000

LEDCON

XXXX 0000

RCON

XXXX OXXX

SADEN

0000 0000

IE1

XXXX 0XXX

SADDR

0000 0000

ISEL

0000 0100

IPL1

XXXX 0XXX

SCTBUF*

0000 0000 SCS R

SCRBUF

0000 000

IPH1

XXXX 0XXX

XXX0 1000

0SCWT0 *

1000 0000

1SCGT0 *

0000 1100

0 SCCON *

0X000

1SCETU0

0111 0100

0SCWT1 *

0010 0101

1SCGT1*

0000 0000

0 SCISR*

10X0 0000

1SCETU1

0XXX

0SCWT2 *

0000 0000 IPH0

1 SCICR *

0000 0000

0 SCIIR*

0X00 0000 CKCON1

1SCIER *

0X00 0000

DCCKPS

XXXX XX11

XXX0 0000

XXXX 0XXX

FFh

F7h

EFh

E7h

DFh

D7h

CFh

C7h

BFh

B7h

AFh

A0h P2

1111 1111

98h SCON

XXX0 0000

90h P1

XX11 1111

88h TCON

0000 0000

80h P0

1111 1111SP0000 0111

0/8 1/9 2/A 3/B 4/C 5/D 6/E 7/F

Reserved

4164G–SCR–07/06

SBUF

XXXX XXXX

SIOCON

00XX 0000

TMOD

0000 0000

AUXR1

XXX XXX0

BRL

0000 0000

TL0

0000 0000

DPL

0000 0000

WDTRST

XXXX XXXX

BDRCON

XXX0 0000

TL1

0000 0000

DPH

0000 0000

SCRS Bit (SCSR.0) (*)

0SFR value

1SFR value

TH0

0000 0000

20 PCON

TH1

0000 0000

AUXR

00XX XX00

WDTPRG

XXXX X0000

CKRL

XXXX 111X

CKCON0

X0X0 X000

00XX XX00

A7h

9Fh

97h

8Fh

87h

13

Page 14

A/T8xC5121

PowerMonitor The Powe rMonito r functi on superv ises t he evol ution of the vo ltages f eedin g the mi cro-

controller, and if needed, suspends its activity when the detected value is out of

specification.

It is guaranteed to start up pr operly whe n T8xC512 1 is po wered up and prevents cod e

execution errors when the power supply becomes lower than the functional threshold.

This section describes the functions of the PowerMonitor.

Description In order to start up and to properly maintain the microcontroller operation, V

stabilized in the V

nal amplitude compatible with logic threshold.

This control is carried out during three phases which are the power-up, normal operation

and stop. It complies with the following requirements:

• It guarantees an operational Reset when the microcontroller is powered

• and a protection if the power supply goes out from the functional range of the

Figure 8. PowerMonitor Block Diagram

External

Power Supply

V

DD

microcontroller.

operating range and the oscillator has to be stabilised with a nom i-

DD

DC to DC

3V Regulator

C

V

CC

D

V

CC

has to be

DD

Power-up

Detector

Power-fail

Detector

Internal RESET

PowerMonitor Diagram The target of the PowerMonitor is to survey the power supply in order to detect any volt-

age drops which are not in the target specification. This PowerMonitor block checks two

kind of situations that occur:

• During the power-up condition, when V

• During a steady-state condition, when V

undesirable voltage drops.

Figure 9 shows some configurations that can be met by the PowerMonitor.

14

is reaching the product specification

DD

is stable but disturbed by any

DD

4164G–SCR–07/06

Page 15

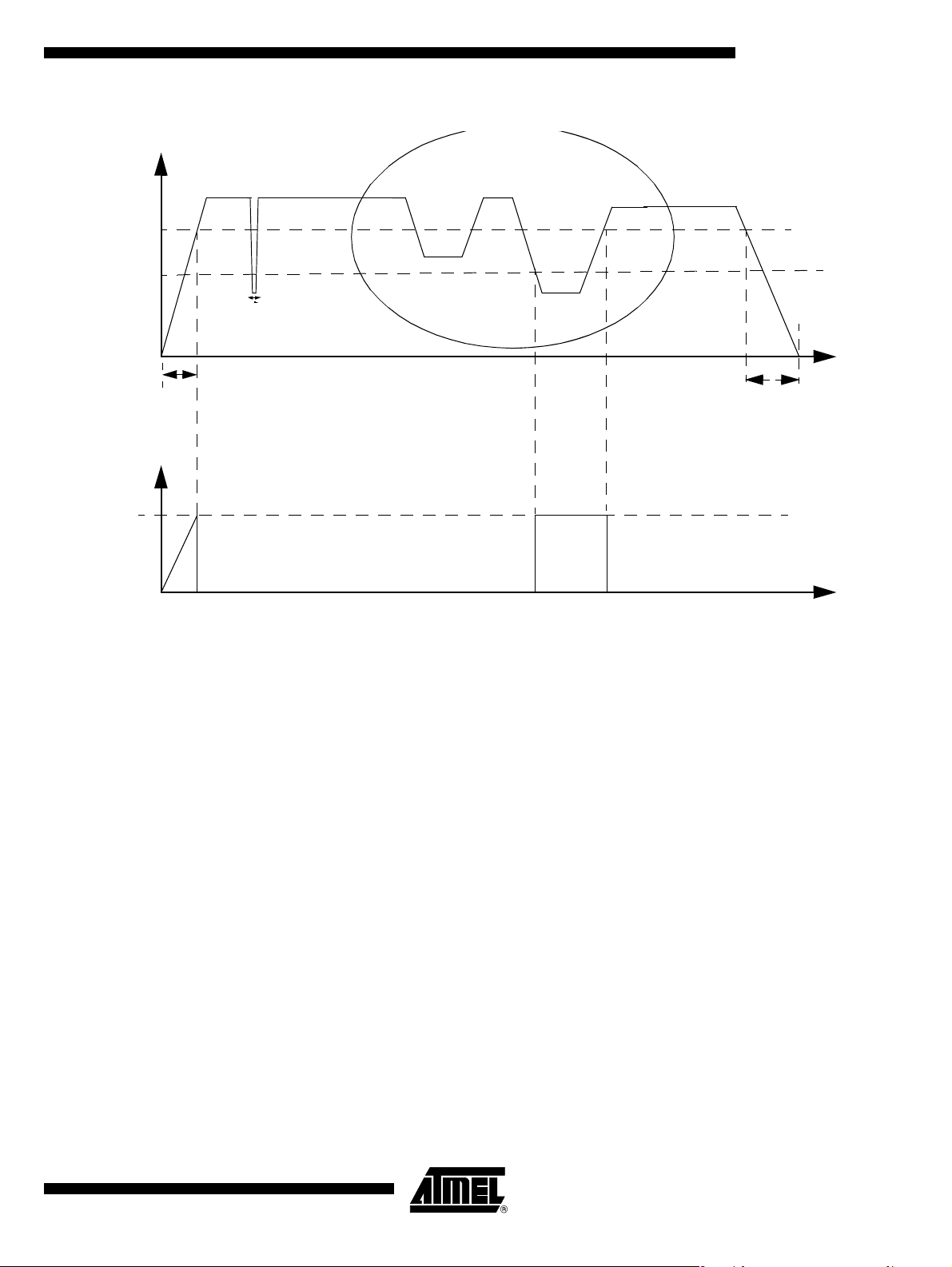

Figure 9. Power-Up and Steady-state Conditions Monitored

DV

CC

VPFDP

VPFDM

A/T8xC5121

Reset

V

CC

t

G

Power-up

t

rise t

Steady-state Condition

Power-down

Such device when it is integrated in a microcontroller, forces the CPU in reset mode

when V

reaches a voltage condition which is out of the specification.

DD

The thresholds and their functions are:

•V

: the output voltage of the regulator has reached a minimum functional value

PFDP

at the power-up . The circuit leaves the RESET mode.

•V

: the output voltage of the regulator has reached a low threshold functional

PFDM

value for the microcontroller. An internal RESET is set.

fall

4164G–SCR–07/06

Glitch fi lt e r ing prevents th e system from R ESET w hen short duration glitches are carried

on V

The ele ctri cal pa ram eter s V

power supply.

DD

PFDP

, V

PFDM

, t

, t

, tG are speci fied i n th e DC para mete rs

rise

fall

section.

15

Page 16

A/T8xC5121

Power Moni toring and Clock Management

For applications where power consumption is a critical factor, three power modes are

provided:

• Idle mode

• Power-down mode

• Clock Management (X2 feature and Clock Prescaler)

• 3V Regulator Modes (pulsed or not pulsed)

Idle Mode An instruction that sets PCON. 0 causes t he last inst ruction to be exec uted bef ore goi ng

into the Idle mode. In the Idle mode, the internal clock signal is gated off to the CPU, but

not to the interrup t, Time r 0, and Serial Port f unction s. The CPU status is prese rved in

its entirety: the Stack Pointer, Program Counter, Program Status Word, Accumulator

and all other registers maintain their data during Idle. The port pins hold the logical

states they had at the time Idle was activated. ALE and PSEN hold at logic high levels.

There are two ways to terminate th e Idle. Activation of any enabl ed interru pt will cause

PCON.0 to be cleared by hardware, terminating the Idle mode. The interrupt will be s erviced, and following RETI the next instruction to be executed will be the one following

the instruction that put the device into idle.

The flag bit GF0 can be used to give an indication if an interrupt occurred during normal

operation or during a n Idle. For exam ple, an i nstructio n that act ivate s Idle can al so set

one or both fl ag bit s. Whe n Idle is term inated by an interrupt, the interrup t serv ice routine can examine the flag bits.

The other way of terminating the Idle mode is with a hardware reset. Since the clock

oscillator is still running, the hardware reset needs to be held active for only two

machine cycles (24 oscillator p er iods) to co mplete the reset.

Power-down Mode

Entering Power-down Mod e To save maximum power, a Power-down mode can be invoked by software (refer to

Table 3, PCON register).

In Power-down mode, the os cillator is stopped a nd the instructi on tha t invoked P ower-

down mode is the last instruction executed. The internal RAM and SFRs retain their

V

value until the Power-down mode is terminated.

power. Eith er a ha rdwa re reset o r an exte rnal interru pt ca n ca use an e xit fro m Powe rdown. To pr operly terminat e Pow er-down, t he reset or ext ernal interr upt sho uld no t be

exec uted befo re

long enough for the oscillator to resta rt and stabi liz e.

Only external interrupts INT0

interrupt must be enabled and configured as level or edge sensitive interrupt input.

Holding the pin low restarts the oscillator but bringing the pi n high com pl etes the exit as

detailed in F igure 10. W hen both interrupt s are ena bled, the oscilla tor restart s as soon

as one of the two inputs is held low and Power-Down exit will be completed when the

first input will be released. In this case the higher priority interrupt service routine is

executed.

Once the in ter rupt is serv iced, the nex t instr uctio n to be e xec uted after RE TI will b e the

one following the instruction that put it into Power-down mode.

Exit from Power-down Mode Exiting from Power-down by external interrupt does not affect the SFRs and the internal

RAM content.

V

is restored to its normal operating level and must be held active

CC

and INT1 are useful to exit from Power-down. For that,

can be lowered to save further

CC

16

4164G–SCR–07/06

Page 17

The ports status under Power-down is the status which was valid before entering this

mode.

The IN T1 int errup t is a m ul tiple xed i nput (s ee Inte rrupt para grap h) w ith CP RES (Car d

detection) and Rxd (U ART Rx) . So these t hree input s can be us ed to exi t from Pow erdown mode. The configurations which must be set are detailed below:

• Rxd input:

• CPRES input:

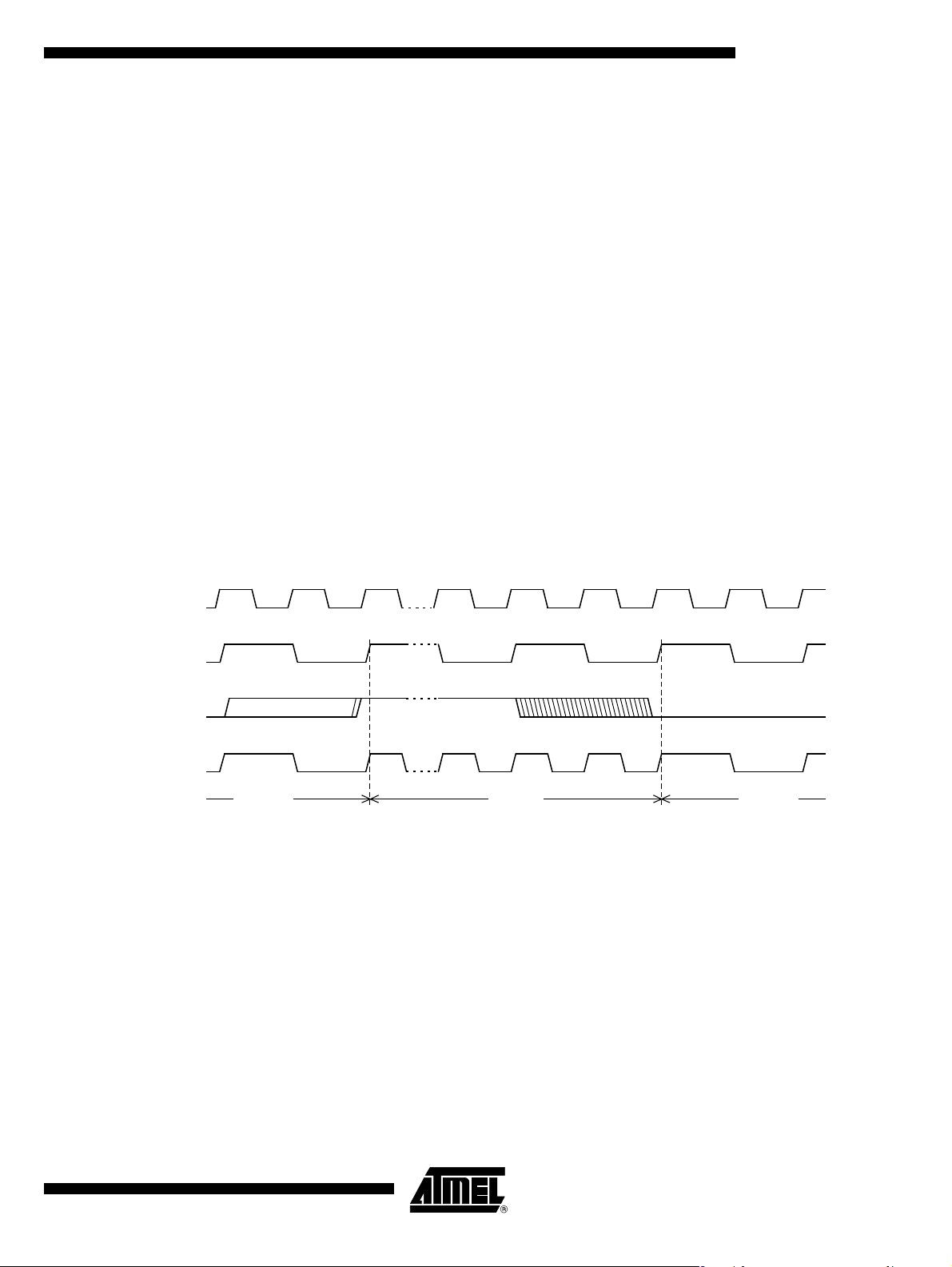

Figure 10. Power-down Exit Waveform

INT0

A/T8xC5121

– RXEN (ISEL.0) must be set

– EX1 (IE0.2) mu st b e set

– A low level detected during more than 100 microseconds exit from Power-

down

– PRSEN (ISEL.1) must be set

– EX1 (IEO.2) must be set

– EA (IE0.7) mu st b e set

– In the INT1 interrupt vector, the CPLEV Bit (ISEL.7) must be inverted

and PRESIT Bit (ISEL.5) must be reset.

INT1

XTAL1

Power-down phase

Oscillator restart phase

Active phaseActive phase

Exiting from Pow er-down by rese t rede fines al l the SF Rs, ex iting from Pow er-down by

external interrupt does no affect the SFRs.

Exiting from Power-down by either reset or external interrupt does not affect the internal

RAM content.

Note: If idle mode is activated wi th Power -down mode (IDL and PD bits set), the exit sequence

is unchanged, when execution is vectored to interrupt, PD and IDL bits are cleared and

idle mode is not entered.

SCI Control Prior to entering Power-down mode, a de-activation of the Smart Card system must be

performed.

LED Control Prior to entering Power-down mode, if the LED mode output is used, the medium pull-up

must be disconnected by setting the LEDPD bit in the PCON Register (PCON 3).

Low Power Mod e Only in Power-down mode, in order to reduce the power consumption, the user can

choose to select this low-power mode.

The activation reference is the following.

• First select the Low-power mode by setting the LP bit in the AUXR Register (AUXR.

6)

• The activation of Power-down can then be done.

4164G–SCR–07/06

17

Page 18

A/T8xC5121

Reduced EMI Mode The ALE signal is used to demultiplex address and data buses on port 0 when used with

external program or data memory. Nevertheless, during internal code execution, ALE

signal is still gene r ated .

Only in case of PLCC52 version, in order to redu ce EMI , ALE s ignal can be disabled by

setting AO bit.

The AO bit is located in AUXR register at b it location 0 (See Table 4). As soon as A O is

set, ALE is no longer output but remains active during MOVX and MOVC instructions

and external fetches. During ALE disabling, ALE pin is weakly pulled high.

Power Modes Control Registers

Table 3. PCON Register

PCON (S:87h)

Power Configuration Register

76543210

SMOD1 SMOD0 - - LEDPD GF0 PD IDL

Bit

Number

7SMOD1

6SMOD0

5 Reserved

4 Reserved

3 LEDPD

2GF0

Bit

Mnemonic Description

Double Baud Rate bit

Set to d ou ble t he Bau d Rat e when Timer 1 i s u sed and mo de 1, 2 o r 3 i s se le cted in

SCON register.

SCON Select bit

When cleared, read/write accesses to SCON.7 are to SM0 bit and rea d/write

accesses to SCON.6 are to SM1 bit.

When set, read/write accesses to SCON.7 are to FE bit and read/write accesses to

SCON.6 are to OVR bit. SCON is Serial Port Control register.

LED Control Power-Down Mode bits

When cleaned the I/O pull-up is the standard C51 pull-up control. When set the

medium pull-up is disconnected.

General-pu r pos e fla g 0

One use is to indi cate wether an interrupt occ urred during normal operation or

during I dl e mo de .

18

Power-down Mode bit

1PD

0IDL

Cleared by hardware when an interrupt or reset occurs.

Set to activate the Power-down mode.

If IDL and PD are both set, PD takes precedence.

Idle Mode bit

Cleared by hardware when an interrupt or reset occurs.

Set to activate the Idle mode.

If IDL and PD are both set, PD takes precedence.

Reset Valu e = X0XX XX 0 0b

4164G–SCR–07/06

Page 19

A/T8xC5121

Table 4. AUXR Register

AUXR (S:8Eh)

Auxiliary Registe r

76543210

- LP - - - - EXTRAM AO

Bit

Number

7-

6LP

5-

4-

3-

2-

1EXTRAM

0AO

Bit

Mnemonic Description

Reserved

The value read from this bit is indeterminate. Do not set this bit.

Low Power mode selection

Clear to select standard mode

Set to select low consumption mode

Reserved

The value read from this bit is indeterminate. Do not set this bit.

Reserved

The value read from this bit is indeterminate. Do not set this bit.

Reserved

The value read from this bit is indeterminate. Do not set this bit.

Reserved

The value read from this bit is indeterminate. Do not set this bit.

EXTRAM select

(ONLY for PLCC52 version)

Clear to map XRAM datas in internal XRAM memory.

Set to map XRAM datas in exter nal XRAM memo ry.

ALE Output bit

(ONLY for PLCC52 version)

Clear to restore ALE operation during internal fetches.

Set to disable ALE operation during internal fetches.

4164G–SCR–07/06

Reset Value = 00XX XX00b

19

Page 20

A/T8xC5121

Table 5. IE0 Register

IE0

Interrupt Enable Register (A8h)

76543210

EA - - ES ET1 EX1 ET0 EX0

Bit

Number

7EA

6-

5-

4ES

3ET1

2EX1

1ET0

Bit

Mnemonic Description

Enable All interrupt bit

Clear to disable all inter rupts.

Set to enab le all in terr u p ts.

If EA = 1, each interrupt source is individually enabled or disabled by setting or

clearing its interrupt enable bit.

Reserved

The value read from this bit is indeterminate. Do not set this bit.

Reserved

The value read from this bit is indeterminate. Do not set this bit.

Serial port Enable bit

Clear to disable serial port interrupt.

Set to enable serial por t int er ru pt.

Timer 1 overflow interrupt Enable bit

Clear to disable Timer 1 overflow interrupt.

Set to enable Timer 1 overflow interrupt.

External interrupt 1 Enable bit

Clear to disable external interrupt 1.

Set to enable external interrupt 1.

Timer 0 overflow interrupt Enable bit

Clear to disable Timer 0 overflow interrupt.

Set to enable Timer 0 overflow interrupt.

20

External interrupt 0 Enable bit

0EX0

Clear to disable external interrupt 0.

Set to enable external interrupt 0.

Reset Value = 0XX0 0000b

4164G–SCR–07/06

Page 21

A/T8xC5121

Table 6. ISEL Register

ISEL (S:BAh)

Interrupt Enable Register

76543210

CPLEV - RXIT PRESIT OELEV OEEN RXEN PRESEN

Bit

Number

7 CPLEV

6-

5 PRESIT

4RXIT

3 OELEV

2OEEN

Bit

Mnemonic Description

Card presence detection level

This bit indicates which CPRES level will bring about an interrupt

Set this bit to indicate that Card Presence IT will appear if CPRES is at high

level.

Clear this bit to indicate that Card Presence IT will appear if CPRES is at low

level.

Reserved

The value read from this bit is indeterminate. Do not set this bit.

Card presence detection interrupt flag

Set by hardware

Must be cleared by software

Received data interrupt flag

Set by hardware

Must be cleared by software

OE/INT1 signal active level

Set this bit to indicate that high level is active.

Clear this bit to indicate that low level is active.

OE/INT1 inte rru pt dis ab le bit

Clear to disable INT1 interrupt

Set to enable INT 1 interr u pt

4164G–SCR–07/06

Card pr es en ce detecti on i nterrupt en able bit

1 PRESEN

0RXEN

Clear to disable the card presence detect ion interrupt comi ng from SCIB.

Set to enable the card pre se nc e detect io n int erru pt com in g from SC IB.

Received data Interrupt enable bit

Clear to disable the RxD interrupt.

Set to enable the RxD in ter r up t

Reset Value = 0X00 0000b

21

Page 22

A/T8xC5121

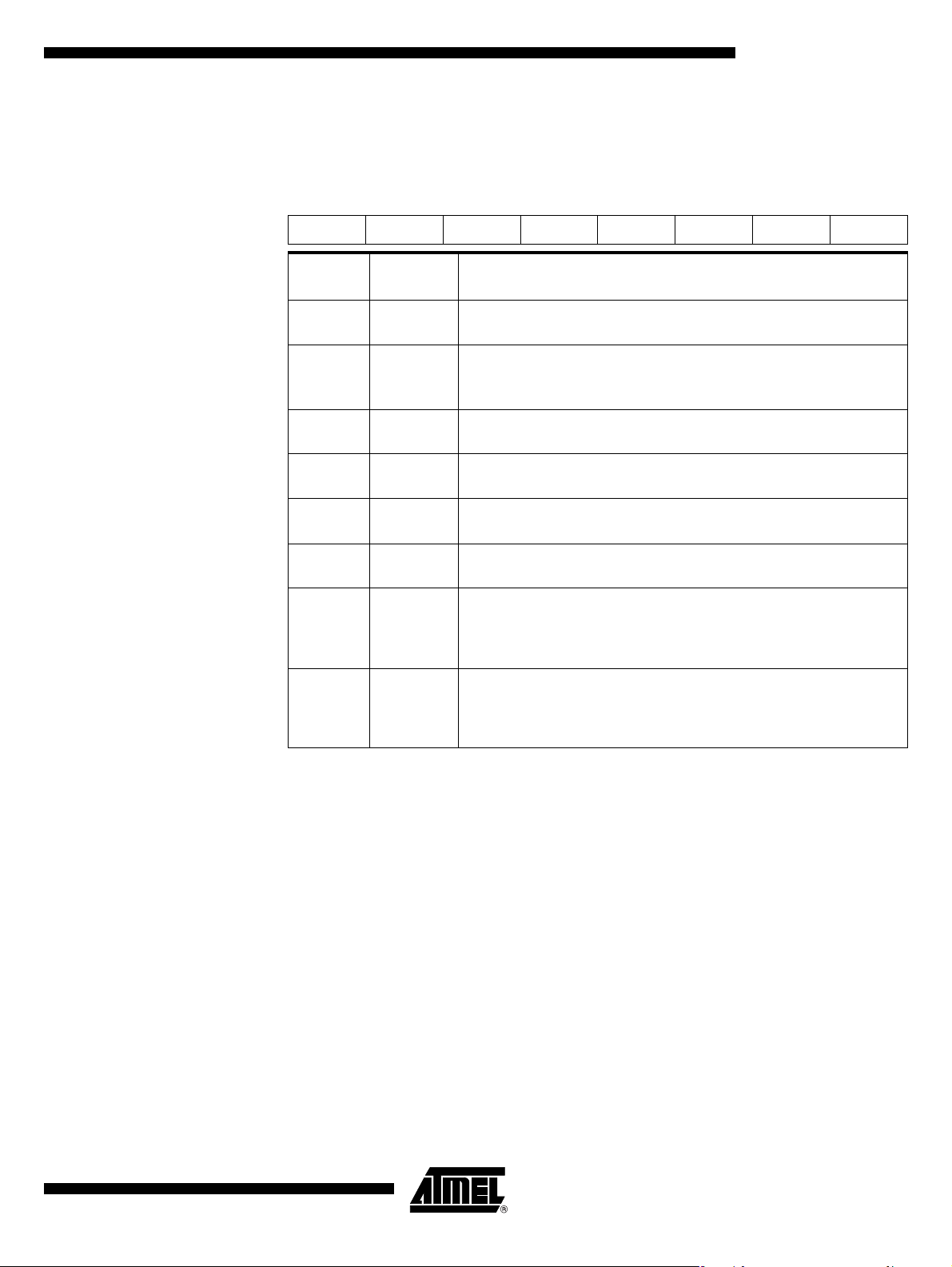

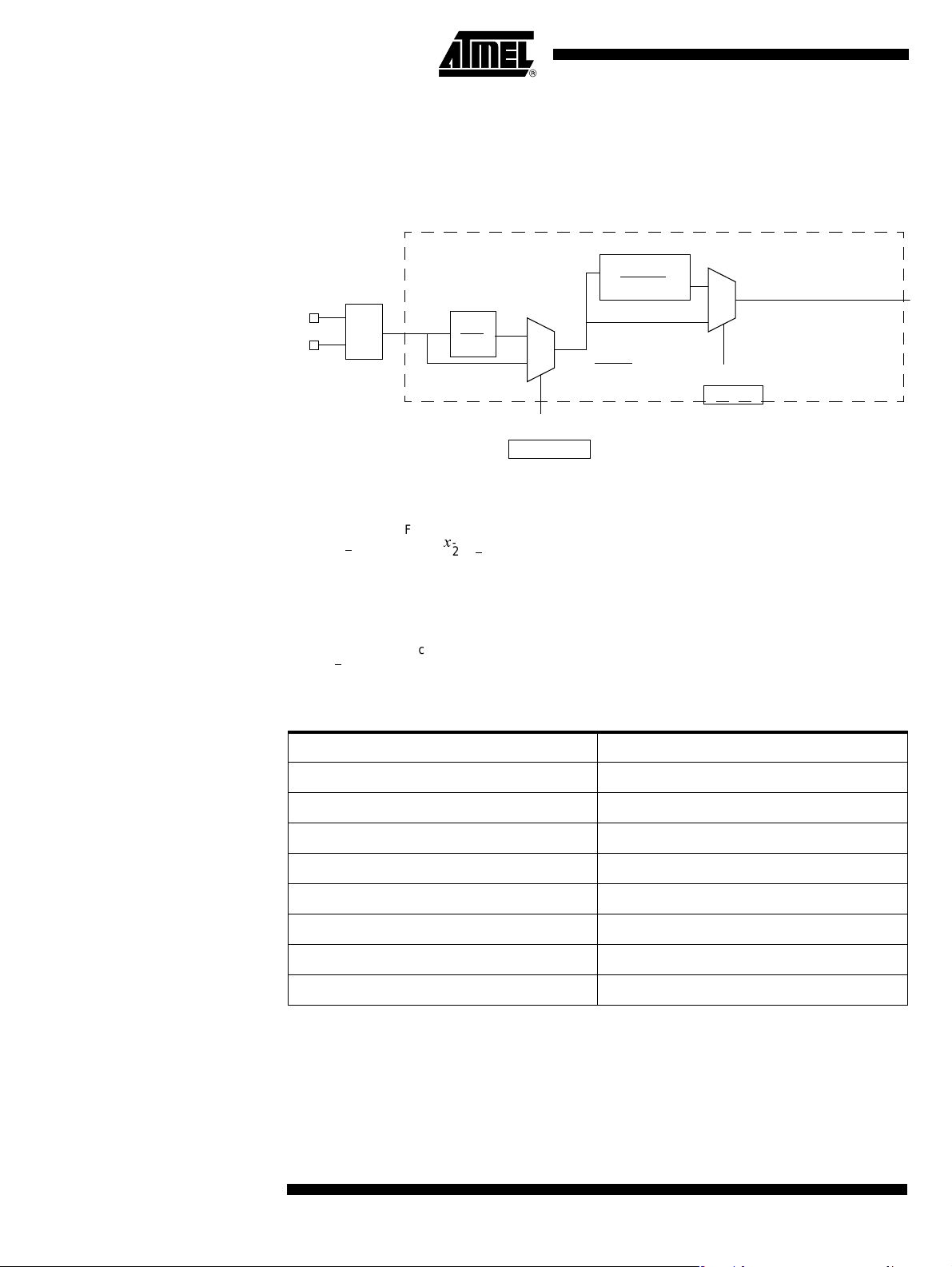

Clock Management In order to optimize the power consumption and the execution time needed for a specific

task, an internal prescaler feature and a X2 feature have been implemented between

the oscillator and the CPU.

Funct ional Bl ock Diagram

Figure 11 . Clock Generation Diagram

XTAL1

XTAL2

Osc.

F

OSC

1

2

0

1

X2

CKCON0

If CKRL<>7 then:

F

–

CLK CPU

OSC

----- ----------- x2()

2

1

----- ----------- ----------- ------- -=

x

2 7 CKRL

–

()

F

If CKRL = 7 then:

F

–

CLK CPU

Fosc

--------------=

x2

2

2(7-CKRL)

F

OSC

x2

2

1

F

0

1

CKRL = 7

CKRL

CLK_CPU

F

CLK_Periph

22

CKRL Prescalor Factor

71

62

54

46

38

210

112

014

4164G–SCR–07/06

Page 23

A/T8xC5121

X2 Feature The T8xC5121 core needs only 6 clock periods per mach ine cycle. This feature called

”X2” provides the following advantages:

• Divides frequency crystals by 2 (cheaper crystals) while keeping same CPU power.

• Saves power consumption while keeping same CPU power (oscillator power

saving).

• Saves power consumption by dynamical ly dividing the operating frequenc y by 2 in

operating and idle modes.

• Increases CPU power by 2 while keeping same crystal frequency.

In order to keep the original C51 compatibility, a divider by 2 is inserted between the

XTAL1 signal and the main clock input of the core (phase generator). This divider m ay

be disabled by software.

Description The clock for the who le circuit and peripheral s is first divided by tw o before being used

by the CPU core and the peripherals.

This allows any cyclic ratio to be accepted on XTAL1 input. In X2 mode, as this divider is

bypassed, the signals on XTAL1 must have a cyclic ratio from 40 to 60%.

As shown in Figure 11, X2 bit is validated on the rising edge of the XTAL1÷2 to avoid

glitches when switching from X2 to standard mode. Figure 12 shows the switching mode

waveforms.

Figure 12. Mode Switching Waveforms

XTAL1

XTAL1:2

X2 bit

CPU clock

The X2 bit in t he CKCON 0 reg ister (se e Table 9) al lows to s witch (if CK RL=7) from 12

clock periods per instruction to 6 clock periods and vice versa.

The T0X2, T1X2, UartX2, and WdX2 bits in the CKCON0 register (see Table 9) and

SCX2 bit in the CK CON1 registe r (see Tab le 10) allow to s witch f rom standa rd perip heral speed (12 clock periods per peripheral clock cycle) to fast peripheral speed (6 clock

periods per peripheral clock cycle). These bits are active only in X2 mode.

More information about the X2 mod e can be f ound in the application note "How to Take

Advantage of the X2 Features in TS80C51 Microcontroller?".

F

OSC

X2 ModeSTD Mode STD Mode

4164G–SCR–07/06

23

Page 24

A/T8xC5121

Clock Prescaler Before supplying the CPU and the peripherals, the main clock is divided by a factor 2 to

30 to reduce the CPU power consumption. This factor is controlled with the CKRL

register.

Table 7. Examples of Factors

F

XTAL (MHz) X2 CPU CKCON0 CKRL Value Prescaler Factor

16 0 (reset mode) 07h 1 8

16 1 (X2 mode) 07h 1 16

16 1 07h 1 16

16 0 07h 1 8

16 0 06h 2 4

16 1 06h 2 8

Clock Control Registers

Clock Prescaler Register This register is used to reload the clock prescaler of the CPU and peripheral clock.

CLK_CPU, FCLK_Periph

(MHz)

Table 8. CKRL Register

CKRL - Clock Reload Register (97h)

76543210

- - - - CKRL CKRL CKRL -

Bit

Number

7 - 4 -

3 - 1 CKRL

0-

Bit

Mnemonic Description

Reserved

The value read from this bit is indeterminate. Do not set this bit.

Clock Reload Register

Prescaler value

XXXX 000Xb: CKRL=7 and Division factor equals 14

XXXX 110Xb: CKRL=6 and factor equals 2

XXXX 111Xb: CKRL=7 and division fa ctor equal s 1

Reserved

The value read from this bit is indeterminate. Do not set this bit.

Reset Value = XXXX 111Xb

24

4164G–SCR–07/06

Page 25

A/T8xC5121

Table 9. CKCON0 Register

CKCON0 - Clock Control Register (8Fh)

76543210

-WDX2- SIX2 - T1X2T0X2X2

Bit

Number

7-Reserved

6WDX2

5-Reserved

4SIX2

3-Reserved

2T1X2

1T0X2

Bit

Mnemonic Description

Watchdog clock

(This control bit is validated when the CPU clock X2 is set; when X2 is low, this

bit has no effect)

Cleared to select 6 clock periods per per ipheral clock cycle.

Set to select 12 clock periods per peripheral clock cycle.

Enhanced UART clock (Mode 0 and 2)

(This control bit is validated when the CPU clock X2 is set; when X2 is low, this

bit has no effect)

Clear to select 6 clock periods per peripheral clock cycle.

Set to select 12 clock periods per peripheral clock cycle.

Timer 1 clock

(This control bit is validated when the CPU clock X2 is set; when X2 is low, this

bit has no effect)

Clear to select 6 clock periods per peripheral clock cycle.

Set to select 12 clock periods per peripheral clock cycle

Timer 0 clock

(This control bit is validated when the CPU clock X2 is set; when X2 is low, this

bit has no effect)

Clear to select 6 clock periods per peripheral clock cycle.

Set to select 12 clock periods per peripheral clock cycle

4164G–SCR–07/06

CPU clock

Clear to select 12 clock periods per machine cycle (Standard mode) for CPU

0X2

and all the peripherals.

Set to select 6 clock periods per machine cycle (X2 mode) and to enable the

indivi dual peripherals "X2" bits.

Reset Value = X0X0 X000b

25

Page 26

A/T8xC5121

Table 10. CKCON1 Register

CKCON1 - Clock Control Register (AFh)

76543210

----SCX2---

Bit

Number

7-Reserved

6-Reserved

5-Reserved

4-Reserved

3SCX2

2-Reserved

1-Reserved

0-Reserved

Bit

Mnemonic Description

SCIB clock

Clear to select 6 clock periods per peripheral clock cycle.

Set to select 12 clock periods per perip heral clock cycle.

Reset Value = XXXX 0XXXb

26

4164G–SCR–07/06

Page 27

A/T8xC5121

DC/DC Clock The DC/DC block needs a clock with a 50% duty cycle. The frequency must also respect

a value between 3.68 MHz and 4 MHz. The first requirement imposes a divider in the

clock path and the second constraint is solved with the use of a prescaler.

Figure 13. Functional Block Diagram

F

OSC

1

(2 to 5)

DCCKPS

Address BFh

F

OSC

2 to 5

F

CLK_DC/DC

Clock Control Register This register is used to reload the clock prescaler of the DC/DC converter clock.

Table 11. DCCKPS Register

DCCKPS - DC/DC converter Reload Register (BFh)

76543210

- - - - - - DCCKPS DCCKPS

Bit

Number

7:2 -

1:0 DCCKPS

Bit

Mnemonic Description

Reserved

Do not use write those bits

Clock Reload Register

Pres caler value

00b: Divi sion factor equals 2

01b: division factor equals 3

10b: division factor equals 4

1 1b: division factor equals 5 (reset value which minimize the consumption)

Reset Value = XXXX XX11b

Clock Prescaler Before supplying the DC/DC block, the oscillator clock is divided by a factor 2 to 5 to

adapt th e cloc k needed by the DC/DC co nverte r. This factor i s contro lled with t he

DCCKPS register.

The prescaler factor must be chosen to match the requirement range which is 4MHz.

Table 12. Examples of Factors

Prescaler

XTAL (MHz) DCCKPS Value

800h2 4

12 01h 3 4

14.756 02h 4 3.689

16 02h 4 4

20 03h 5 4

4164G–SCR–07/06

Factor DC/DC Converter CLK (MHz)

27

Page 28

A/T8xC5121

28

4164G–SCR–07/06

Page 29

A/T8xC5121

Smart Card Interface Block (SCIB)

Introduction The SCIB provides all signals to directly interface a smart card. Compliance with the

ISO7816, EMV’2000, GSM and WHQL standards has been certified.

Both synchronous (e.g. memory card) and asynchronous smart cards (e.g. micropro-

cessor card) are supported. The component supplies the different voltages requested by

the smart card. The power-off sequence is directly managed by the SCIB.

The card presence switch of the smart card connector is used to detect card insertion or

card removal. In case of card removal, the SCIB de-activates the smart card using the

de-activation sequence. An interrupt can be generated when a card is inserted or

removed.

Any malfunction is reported to the microcontroller (interrupt + control register).

The different operating modes are configured by internal registers.

Main Features • Su pport of ISO/IEC781 6

• Character mode

• 1 transmit buffer + 1 receive buffer

• 11 bits ETU counter

• 9 bits guard time counter

• 24 bits waiting time counter

• Auto-character repetition on error signal detection in transmit mode

• Auto-error signal generation on parity error detection in receive mode

• Power-on and power-off sequence generation

• Manual mode to directly drive the card I/O

4164G–SCR–07/06

29

Page 30

A/T8xC5121

Block Diagram The Smart Card Interface Block diagram is shown in Figure 14.

Figure 14. SCIB Block Diagram

Clk_iso

Clk_cpu

INT

Ba r r e l s h if ter

Etu counter

Guard time

Wa iting t im e

SCI Registers

Interrupt generator

Scart

fsm

I/O

mux

Power on

Power off

fsm

IO (in)

IO (ou t)

CLK

RST

C4 (out)

C8 (out)

CLK1

C4 (in)

C8 (in)

VCARD

Functional Description The architecture of the Smart Card Interface Block is detailed below.

Barrel Shifter It allows the translation between 1 bit serial data and 8 bits parallel data.

The barrel function is useful for character repetition since the character is still present in

the shifter at the end of the character transmission.

This shifter is able to shift the data in both directions and to invert the input or output

value in order to manage both direct and inverse ISO7816-3 convention.

Coupled with the barrel shifter there is a parity checker and generator.

There are 2 regist ers conn ected to this barre l shifter, one for the trans mission and on e

for the reception.

They act as buffers to relieve the CPU of timing constraints.

SCART FSM (Smart Card Asynchronous Receiver Transmitter Finite State Machine)

This is th e c ore of the de sign. I ts pu rpo se is to co ntro l the barre l s hifter. To sequ enc e

correctly the barrel shifter for a reception or a transmission, it uses the signals issued by

30

4164G–SCR–07/06

Page 31

A/T8xC5121

the different counters. One of the most important counters is the guard time counter that

gives time slots corresponding to the character frame.

It is enabled only in UART mode.

The transition from the receipt mode to the transmit mode is done automatically. Priority

is given to the transmission.

ETU Counter The ETU (Elementary Timing Unit) counter controls the working frequency of the barrel

shifter, in fact, it generates the enable signal of the barrel shifter.

It is 11 bits wide and t here i s a special compensation mode activ ated with t he m ost s ig-

nificant bit that allows non integer ETU value with a working clock equal to the card

clock .

But the decimal va lue is limit ed t o a hal f clock cycle. I n fa ct the bit dura ti o n is not fixed. It

takes turns in n clock cycles and n-1 clock cycles. The character duration (10 bits) is

also equal to 10*(n+1/2) clock cycles.

This allows to reach the required precision of the character duration specified by the

ISO7816 standard.

example: F = 372 D = 32 = > ETU = 11.625 clock cycles.

ETU = (ETU[10-0] -0.5 * COMP)*f with ETU[10-0] = 12, COMP = 1 (bit 7 of SCETU1)

To achieve this clock rate we activated the compensation mode and we programmed

the ETU duration to 12 clock cycles.

The result will be a full character duration (10 bits) equal to 11.5 clock cycles.

Guard Time Co unt er The minimum time between the leading edge of the start bit of a character and the lead-

ing edge of the start bit of the following character transmitted (Guard time) is controlled

by one counter.

It is 9 bits wide and is incremented at the ETU rate.

Figure 15. Guard Time Counter

ETU Counter

Guard Time Counter

GT[8:0]

SCGT1 SCGT0

Timeout

4164G–SCR–07/06

31

Page 32

A/T8xC5121

Waiting Time Counter (WT) The WT counter is a 24 bits down counter which can be loaded with the value contained

in the SCW T2, SCW T1, S CWT 0 re gisters . Its m ain p urpos e is tim e ou t sig nal ge neration. It is 24 b its wide an d is decrem ent ed at the ETU rate. The ETU co unter acts as a

prescaler (See Figure 16).

When the WT co unter timeout, an interrupt is gener ated and the SC IB function is

locked: reception and emission are disabled. It can be enabled by resetting the macro or

reloading the counter.

Figure 16. Waiting Time Counter

ETU Counter

WTEN

Write_SCWT2

UART

Start bit

WT Counter

Load

Timeout

WT[23:0]

SCWT2

SCWT1

SCWT0

The counter is loaded, if WTEN = 0, during the write of SCWT2 register.

This counter is available in both UART and m anual mode s. But the behaviour depe nds

on the selected mode.

In manual mode, the WTEN signal controls the start of the counter (rising edge) and the

stop of the count er (falling edge). After a time out of the co unter, a falling edge on

WTEN, a reload of SCWT 2 and a risin g edge of WT EN are neces sary to start aga in the

counter and to release the SCIB macro. The reload of SCWT2 transfers all SCWT0,

SCWT1 and SCWT2 registers to the WT counter.

In UART mode there is an aut oma tic load on the start bit detection. This automatic load

is very useful for changing on-the-fly t he Timeout value since there is a registe r to hold

the load value. This is the case, for example, when in T = 1 a launch is performed on the

BWT Timeout on the start bit of th e last transmitted charac ter. But on the receipt of the

first character an other time out value (CWT) must be used . For this, the new load value

of the waiting time counter must be loaded with CWT before the transmission of the last

character. The reload of SCWT[2-0] with the new value occurs with WTEN = 1.

32

After a time out of the counter in UART mode, the restart is done as in manual mode.

The maximum interv al be tween th e s tart leading edge of a character and the start lead-

ing edge of the next character is loaded in the SCWT2, SCWT1, SCWT0 registers.

In T = 1 mode, the CWT (character waiting time) or the BWT (block waiting time) are

loaded in the same registers.

The maximum time between two consecutive start bit is WT[23:0] * ETU.

When used to check BWT according to ISO 7816, WT can be set between 971 and

15728651.

4164G–SCR–07/06

Page 33

Figure 17. T = 0 Mode

Figure 18. T = 1 Mode

CHAR 1

A/T8xC5121

> GT

CHAR 2

< WT

Reception

BLOC 2

CHAR n+2 CHAR n+3

CHAR 1

< CWT

Transmission

BLOC 1

CHAR 2

CHAR n

< BWT

CHAR n+1

< CWT

Power-on and Power-off FSM In this state, the machine appli es the signals on the smart card in accorda nce with

ISO7816 standard.

To be able to power-on the SCIB, the card presence is mandatory.

Removal of the smart card will automatically start the power-off sequence as described

in Figure 19.

Figure 19. SCI Deactivation Sequence after a Card Extraction

V

CC

RST

4164G–SCR–07/06

CLK

IO

8 Clock Cycles

33

Page 34

A/T8xC5121

Interrupt Gen erator There are several sources of interrup tion but the SCIB m ac ro-cell issues onl y one inter-

rupt signal: SCIB IT.

Figure 20. SCIB Interrupt Sources

Transmit buffer

copied to shift register

Output current

out of range

Output voltage

out of range

Timeout on WT

counter

Complete

transmission

Complete

reception

Parity error

detected

This signal is high l evel ac tive. One of the sources is a ble to set up the interru pt signal

and this is the read of the Smart Card Interrupt register by the CPU that clears this

signal.

ESCTBI

CIccER

ECVccER

SCIB IT

ESCWTI

ESCTI

ESCRI

ESCPI

If during the read of the Smart Card Interrupt register an interrupt occurs, the set of the

corresponding bit into the Smart Card Interrupt register and the set of the interrupt signal

will be delayed after the read access.

Registers There are fourteen registers to control the SCIB macro-cell. They will be described in

the Section “DC/DC Converter”.

Some of the register widths are greater than a byte. Despite the 8 bits access provided

by the BIU, the address mapping of this kind of register respects the following rule:

• The Lowest significant byte register is implemented at the higher address.

This implementation makes access to these registers easier when using high level pro-

gramming language (C,C++).

34

4164G–SCR–07/06

Page 35

A/T8xC5121

Other Features

Clock The Ck-ISO input must be in the range 1 - 5 MHz according to ISO7816.

The ISO Clock diagram and the configuration examples are shown in Figure 20.

Figure 21. Clock Diagram of the SCIB Block

FCLK_CPU

FCLK_Periph

Clk_cpu

SCIB

1

2

SCX2

CKCON 1.3

Reset value = 1

1

Clk_iso

0

F4_8MHz

Table 13. Examples of Settings for Clocks

FCLK Cpu

+ FCL K Periph

Xtal ( MHz) X2 CKCON0

40 2 0 2

4 1 (mode X2) 4 0 4

81 8 1 4

11.05905.529512.7648

( MHz) SCX2

Clk_ iso

(1 to 5 MHz)

14.7456 0 7.3728 1 3.6864

160814

20 0 10 1 5

Alternate Card A second card named "Alternate card" can be controlled.

The Clock signal CCLK1 can be adapted to the XTAL frequency. Thanks to the clock

prescaler which can divide the frequency by 1, 2, 4 or 8. The bits ALTKPS0 and

ALTKPS1 in SCSR Register are used to set this factor.

4164G–SCR–07/06

35

Page 36

A/T8xC5121

Figure 22. Alternate Card

F

CK_IDLE

PR3

1, 2, 4 or 8

F

CK_IDLE

P3.6

V

C

CC

CRST

CIO

CCLK

CPRES

1

0

CCLK1

SIM,SAM

CARD

Main

card

Alternate

card

ALTKPS0,1 SCCLK1

SCSR Reg.

SCSR Reg.

Card Presence Input The internal pull-up on Card Presenc e in put can be disconnected in order to reduce the

consumption (CPRESRES, bit 3 in PMOD0).

V

In this case, an external resistor (typically 1 MΩ) must be externally tied to

CC

.

CPRES input can generate an interrupt (see Interrupt system section).

The detection level can be selected.

SCIB Reset The SCICR register contains a reset bit. If set, this bit generates a reset of the SCI and

its registers. Table 15 shows the SCIB registers that are reseted and their reset values.

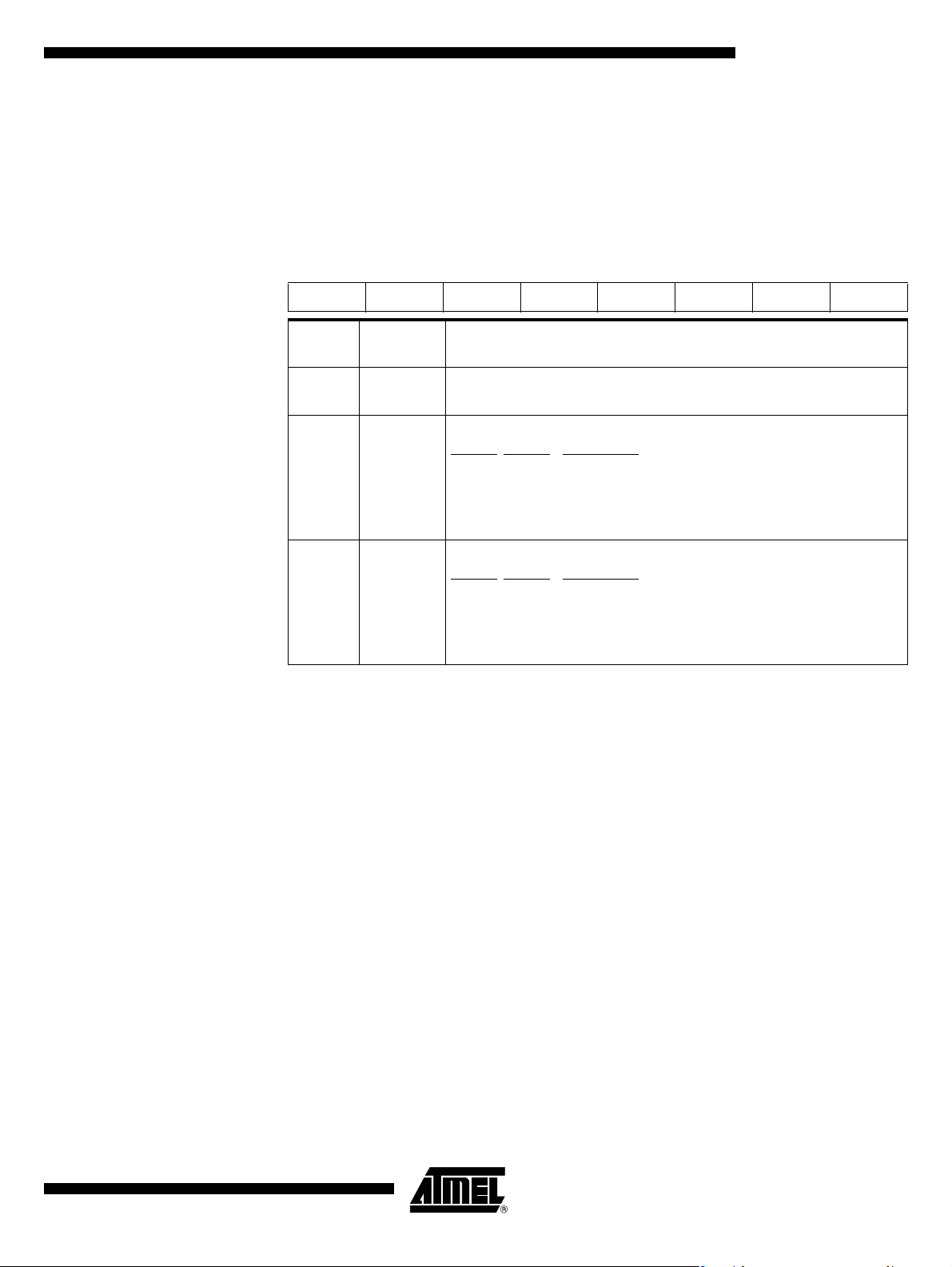

Table 14. Reset Values for SCI Registers

Register Name SCIB Reset Value (Binary)

SCICR 0000 0000b

SCCON 0X00 0000b

SCISR 1000 0000b

SCIIR 0X00 0000b

SCIER 0X00 0000b

36

SCSR XXX0 1000b

SCTBUF 0000 0000b

SCRBUF 0000 0000b

SCETU1, SCETU0 XXX X001b, 0111 0100b (372)

SCGT1, SCGT0 XXXX XXX0b, 0000 1100b (12)

SCWT2, SCWT1, SCWT0 0000 0000b, 0010 0101b, 1000 0000b (9600)

4164G–SCR–07/06

Page 37

A/T8xC5121

DC/DC Converter T he Smart Card supply voltage (CV

It is controlled by several registers:

• The register described in Section “SCICR Register” controls the CVCC voltage with

bits CVcc0, CVcc1

• The register described in Section “SCCON Register”, switches ON/OFF the DC/DC

converter with bit CARDV

• After the selection of the card voltage (CVcc[1:0]), the CARVCC bit is used to switch

on the DC\DC converter. The CVccOK bit indicates that the card voltage is within

the voltage range.

• It is mandatory to switch off the CV

CC

) is generated by the integrated DC/DC converter.

CC

before entering in power-down mode.

CC

4164G–SCR–07/06

37

Page 38

A/T8xC5121

Registers Descr ipt ion Table 15. SCICR Register

SCICR (S:B6h, SCRS = 1)

Smart Card Interface Control Register

76543210

RESET CARDDET CVcc1 CVcc0 UART WTEN CREP CONV

Bit Number Bit Mnemonic Description

7 RESET

6CARDDET

5 - 4 CVcc[1:0]

3UART

2WTEN

Reset

Set this bit to reset the SCIB and its configuration

Card presence detector sense

Clear thi s bi t t o i nd icat e t he ca r d pr es en ce det e ctor i s o pened w hen n o c ard

is inserted (CPRES is high).

Set this bit to indicate the card presence detector is closed when no card is

inserted (CPRES is low).

Card Voltage Selection:

CVcc[1] CVcc[0] CVcc

Card UART selection

Clear this bit to use the Card I/O bit to drive the Card I/O pin.

Set this bit to use the Smart Card UART to drive the Card I/O pin.

Also controls the Wait Time Counter as described in Section “Waiting Time

Counter (WT)”

Wa it time counter enab le

Clear this bit t o stop the counter and enable th e load of the Wait Time

counter hold registers.

The hold reg is t e rs ar e load ed with SCWT0, SCWT1 an d S CWT 2 v a lu es

when SCWT2 is written.

Set this bit to start the Wait Time counter. The counters stop when it

reaches the timeout value.

If the UART bit is set, the Wait Time counter automatically reloads with the

hold registers whenever a start bit is sent or received.

000V

0 1 1.8V

10 3V

11 5V

38

1 CREP

0CONV

Reset Value = 0000 0000b

Character repetition

Clear this bit to disable parity error dete ction an d indication on the Card I/O

pin in receive mode and to disable character repetition in transmit mode.

Set this bit to enable parity error indication on the Card I/O pin in receive

mode and to set automatic character repetition when a parity error is

indicated in transmit mode. In receive mode, three times error indication is

performed and the parity error flag is set after four times parity error

detection. In transmit mode, up to three times character repetition is

allowed and the parity error flag is set after five times (reset configuration,

can be set at 4 using CREPSET bit in SCSR Register) consecutive parity

error indication.

ISO convention

Clear this bit to use the direct convention: b0 bit (LSB) is sent first, the

parity bit is added after b7 bit and a low level on the Card I/O pin represents

a “0”.

Set this bit to use the inverse convention: b7 bit (LSB) is sent first, the parity

bit is added after b0 bit and a low level on the Card I/O pin represents a “1”.

4164G–SCR–07/06

Page 39

A/T8xC5121

Table 16. SCCON Register

SCCON (S:ACh, SCRS = 0)

Smart Card Contacts Register

76543210

CLK - CARDC8 CARDC4 CARDIO CARDCLK CARDRST CARDVCC

Bit Number Bit Mnemonic Description

Card Clock Selection

Clear this bit to use the CardClk bit (CARDCLK) to drive Card CLK pin.

7CLK

Set this bit to use XTAL signal to drive the Card CLK pin.

Note: internal synchr onizati on avoids any glitch on the CLK pi n when

switching this bit.

6-

5 CARDC8

4 CARDC4

3 CARDIO

2CARDCLK

1 CARDRST

0 CARDV

Reserved

The value read from this bit is indeterminate. Do not change this bit or write 0.

Card C8

Clear this bit to drive a low level on the Card C8 pin.

Set this bit to set a high level on the Card C8 pin.

Card C4

Clear this bit to drive a low level on the Card C4 pin.

Set this bit to set a high level on the Card C4 pin.

Card I/O

When the UART bit is cleare d in SCICR Reg is te r, the valu e of thi s bit is

driven to the Card I/O pin.

Then this pin can be used as a p s eudo bi-directional I/O when this b it is set.

T o be used as an input, this bit must contain a 1.

Card CLK

When the CLK bit is cleared in SCCON Register, the value of this bit is driven

to the Card CLK pin.

Card RST

Clear this bit to drive a low level on the Card RST pin.

Set this bit to set a high level on the Card RST pin.

Read is not allowed if VCARDOK=0

Card VCC Control

Clear this bit to desactivate the Card interface and set its power-off. The other

bits of SCC regi ster have no effect while this bit is clea red.

CC

Set this bit to power-on the Card interface. The activation sequence shall be

handled by software.

4164G–SCR–07/06

Reset Value = 0X00 0000b

39

Page 40

A/T8xC5121

Table 17. SCISR Register

SCISR (S:ADh, SCRS = 0)

Smart Card UART Interface Status Register

76543210

SCTBE CARDIN CIccOVF CVccOK SCWTO SCTC SCRC SCPE

Bit

Number

7SCTBE

6 CARDIN

5CIccOVF

4CVccOK

3SCWTO

2SCTC

Bit

Mnemonic Description

SCIB transmit buffer empty

This bit is set by hardware when the Transmit Buffer is copied to the transmit shift

register of the S m art Card UA RT.

It is cleared by hardware when SCTBUF is written to.

Card presence status

This bit is set when a card is detected (debouncing filter has to be done in

software).

It is cleared otherwise.

ICC overflow on card

This bit is set when the current on card is above the limit

It shall be cleared by the hardware .

Card voltage status

This bit is set when the output voltage is within the voltage range specified by

CVcc fi eld.

It is cleared otherwise.

Smart card wait Timeout

This bit is set by hardware when the Smart card wait time counter times out.

It shall be cleared by the rel oad of the counter or by the reset of the SCIB.

Smart card transmitted character

This bit is set by hardware when the Smart Card UART has transmitted a

character.

It shall be cleared by software after this register has been read.

40

1SCRC

0SCPE

Smart card received character

This bit is set by hardware when the Smart Card UART has received a character

It is cleared by hardware when SCBUF is read.

Smart card parity error

This bit is set at the same time as SCTI or SCRI if a parity error is detected.

It shall be cleared by software after this register has been read.

Reset Value = 1000 0000b

4164G–SCR–07/06

Page 41

A/T8xC5121

Table 18. SCIIR Register

SCIIR (S:AEh, SCRS = 0)

Smart Card UART Interrupt

Identification Register (read only)

76543210

SCTBI - CIccERR CVccERR SCWTI SCTI SCRI SCPI

Bit

Number Bit Mnemonic Description

SCIB t ransmit buffer interrupt

7SCTBI

This bit is set by hardware when the Transmit Buffer is copied to the transmit

shift register of the Smart Card UART.

It is cleared by hardware when this register is read.

6-

5CIccERR

4 CVccERR

3SCWTI

2SCTI

1SCRI

0SCPI

Reset Value = 0X00 0000b

Reserved

The value read from this bit is indeterminate. Do not change this bit or write 0.

Card current status

This bit is set when the output current goes out of the current range.

It is cleared by hardware when this register is read.

Card v oltage statu s

This b it is set whe n t he o utpu t vol tag e g oe s ou t of t he v olt a ge ra ng e sp eci fie d

by CVcc fi el d.

It is cleared by hardware when this register is read.

Smart card wait Timeout interrupt

This bit is set by hardware when the Smart Card Timer 0 times out.

It is cleared by hardware when this register is read.

Smart card transmit interrupt

This bit is set by hardware when the Smart Card UART completes a

character transmission.

It is cleared by hardware when this register is read.

Smart card receive interrupt

This bit is set by hardware when the Smart Card UART completes a

character recept ion.

It is cleared by hardware when this register is read.

Smart card parity error interrupt

This bit is set at the same time as SCTI or SCRI if a parity error is detected.

It is cleared by hardware when this register is read.

4164G–SCR–07/06

41

Page 42

A/T8xC5121

Table 19. SCIER Register

SCIER (S:AEh, SCRS = 1)

Smart Card UART Interrupt Enable Register

765 4 3210

ESCTBI - CIccER ECVccER ESCWTI ESCTI ESCRI ESCPI

Bit Number

7 ESCTBI

6-

5CIccER

4 ECVccER

3 ESCWTI

2 ESCTI

1 ESCRI

0 ESCPI

Bit

Mnemonic Description

Smart Card UART Transmit Buffer Empty Interrupt Enable

Clear this bit to disable the Smart Card UART Transmit Buffer Empty interrupt.

Set this bit to enable the Smart Card UART Transmit Buffer Empty interrupt.

Reserved

The val ue read from this bi t is indet erminate . Do not change this bit .

Card Current Error Interrupt Enable

Clear this bit to disable the Card Current Error interrupt.

Set this bit to enable the Card Current Error interrupt.

Card Voltage Error Interrupt Enable

Clear this bit to disable the Card Voltage Error interrupt.

Set this bit to enable the Card Voltage Error interrupt.

Smart Card Wait Timeout Interrupt Enable

Clear t his bit to disable th e Smart Card Wait timeout interrupt .

Set this bit to enable the Smart Card Wait timeout interrupt.

Smart Card Transmit Interrupt Enable

Clear this bit to disable the Smart Card UART Transmit interrupt.

Set this bit to enable the Smart Card UART Transmit interrupt.

Smart Card Receive Interrupt Enable

Clear this bit to disable the Smart Card UART Receive interrupt.

Set this bit to enable the Smart Card UART Receive interrupt.

Smart Card Parity Error Interrupt Enable

Clear this bit to disable the Smart Card UART Parity Error interrupt.

Set this bit to enable the Smart Card UART Parity Error interrupt.

42

Reset Value = 0X00 0000b

4164G–SCR–07/06

Page 43

A/T8xC5121

Table 20. SCSR Register

SCSR (S:ABh) Smart Card Selection Register

76543210

- - - CREPSEL ALTKPS1 ALTKPS0 SCCLK1 SCRS

Bit

Number

7-Reserved

6-Reserved

5-Reserved

4 CREPSEL

3-2

1 SCCLK1

0 SCRS

Bit

Mnemonic Description

Character repetition selection

Clear this bit to select 5 times repetition before parity error indication

Set this bit to select 4 times repetition before parity error indication

Alternate Card Clock prescaler factor

ALTKPS1

ALTKPS0

00ALTKPS = 0: prescaler factor equals 1

01ALTKPS = 1: prescaler factor equals 2

10ALTKPS = 2: prescaler factor equals 4 (reset value)

11ALTKPS = 3: prescaler factor equals 8

Alternate card clock selecti o n

Set to select the prescaled clock (CCLK1)

Clear to select the standa rd port configuration (P3.6)

Smart ca r d reg is t e r sel e ction

The SCRS bit selects which set of the SCIB registers is accessed.

Reset Value = XXX0 1000b

Table 21. SCTBUF Register

SCTBUF (S:AA, write-only, SCRS = 0) Smart Card Transmit Buffer Register

76543210

Bit Number Bit Mnemonic Description

––

Can store a new byte to be transmitted on the I/O pin when SCTBE is set.

Bit ordering on the I/O pin depends on the Convention (see SCICR

Register).

Reset Value = 0000 0000b

4164G–SCR–07/06

43

Page 44

A/T8xC5121

Table 22. SCRBUF Register

SCRBUF (S:AA read-only, SCRS = 1)

Smart Card Receive Buffer Register

76543210

––––––––

Bit

Number

––

Bit

Mnemonic Description

Provides the byte received from the I/O pin when SCRI is set.

Bit ord ering on the I/O pin depends on the Convention (see SCICR Regist er).

Reset Value = 0000 0000b

Table 23. SCETU1 Register

SCETU1 (S:ADh, SCRS = 1)

Smart Card ETU Register 1

76543210

COMP

Bit

Number

7COMP

6-3 –

––––ETU10 ETU9 ETU8

Bit

Mnemonic Description

Compensation

Clear this bit when no time compensation is needed (i.e. when the ETU to Card

CLK period ratio is close to an intege r with an error less than 1/4 of Card CLK

period).

Set this bit otherwise and reduce the ETU period by 1 Card CLK cycle for even

bits.

Reserved

The val ue read from these bi ts is indeterminate. Do not change these bits .

44

2-0 ETU[10:8]

ETU MSB

Used together with the ETU LSB (see SCETU0 Register).

Reset Value = 0XXX X001b

4164G–SCR–07/06

Page 45

A/T8xC5121

Table 24. SCETU0 Register

SCETU0 (S:ACh, SCRS = 1)

Smart Card ETU Register 0

76543210

ETU7 ETU6 ETU5 ETU4 ETU3 ETU2 ETU1 ETU0

Bit

Number

7-0 ETU[7:0]

Bit

Mnemonic Description

ETU LSB

The Elementary Time Unit is (ETU[10:0] - 0.5*COMP)/f, where f is the Card CLK

frequency.

According to ISO7816, ETU[10:0] can be set between 11 and 2047.

The default res et value of ETU[10: 0] is 372 (F = 372, D = 1).

Reset Value = 0111 0100b

Table 25. SCGT1 Register

SCGT1 (S:B5h, SCRS = 1)

Smart Card Transmit Guard Time Register 1

76543210

–––––––GT8

Bit

Number

7-1 –

0GT8

Bit

Mnemonic Description

Reserved

The val ue read from these bi ts is indeterminate. Do not change these bits .

T ransmit Gu ard Time MSB

Used together with the Transmit Guard Time LSB (see SCGT0 Register).

4164G–SCR–07/06

Reset Value = XXXX XXX0b

Table 26. SCGT0 Register

SCGT0 (S:B4h, SCRS = 1)

Smart Card Transmit Guard Time Register 0

76543210

GT7GT6GT5GT4GT3GT2GT1GT0

Bit

Number

7-0 GT[7:0]

Bit

Mnemonic Description

T ransmit Guard Time LSB

The minimum time between two consecutive start bits in transmit mode is

GT[8:0] * ETU.

According to ISO 7816, GT can be set between 11 and 266 (11 to 254+12 ETU).

Reset Value = 0000 1100b

45

Page 46

A/T8xC5121

Table 27. SCWT2 Register

SCWT2 (S:B6h, SCRS = 0)

Smart Card Character/Block Wait Time Register 2

76543210

WT23 WT22 WT21 WT20 WT19 WT18 WT17 WT16

Bit

Number

7-0 WT[23:16]

Bit

Mnemonic Description

Wait Time Byte 2

Used together with WT[15:0] (see SCWT0 Register).

Reset Value = 0000 0000b

Table 28. SCWT1 Register

SCWT1 (S:B5h, SCRS = 0) Smart Card Character/Block Wait Time Register 1

76543210

WT15 WT14 WT13 WT12 WT11 WT10 WT9 WT8

Bit

Number

7-0 WT[15:8]

Bit

Mnemonic Description

Wait Time Byte 1

Used together with WT[23:16] and WT[7:0] (see SCWT0 Register).

Reset Value = 0010 0101b

Table 29. SCWT0 Register

SCWT0 (S:B4h, SCRS = 0)

Smart Card Character/Block Wait Time Register 0

46

76543210

WT7 WT6 WT5 WT4 WT3 WT2 WT1 WT0

Bit

Number

7-0 WT[7:0]

Bit

Mnemonic Description

Wait Time Byte 0

WT[23:0] is the reload value of the Wait Time counter WTC.

The WTC is a general-purpose Timer 0. It is using the ETU clock and is

controlled by the WTEN bit (see Section “Waiting Time Counter (WT)”).

When UART bit of SCICR Register is set, the WTC is automatically reloaded at

each start bit of the UART. It is used to check the maximum time between to

consecu tive sta rt bits.

Reset Value = 1000 0000b

4164G–SCR–07/06

Page 47

A/T8xC5121

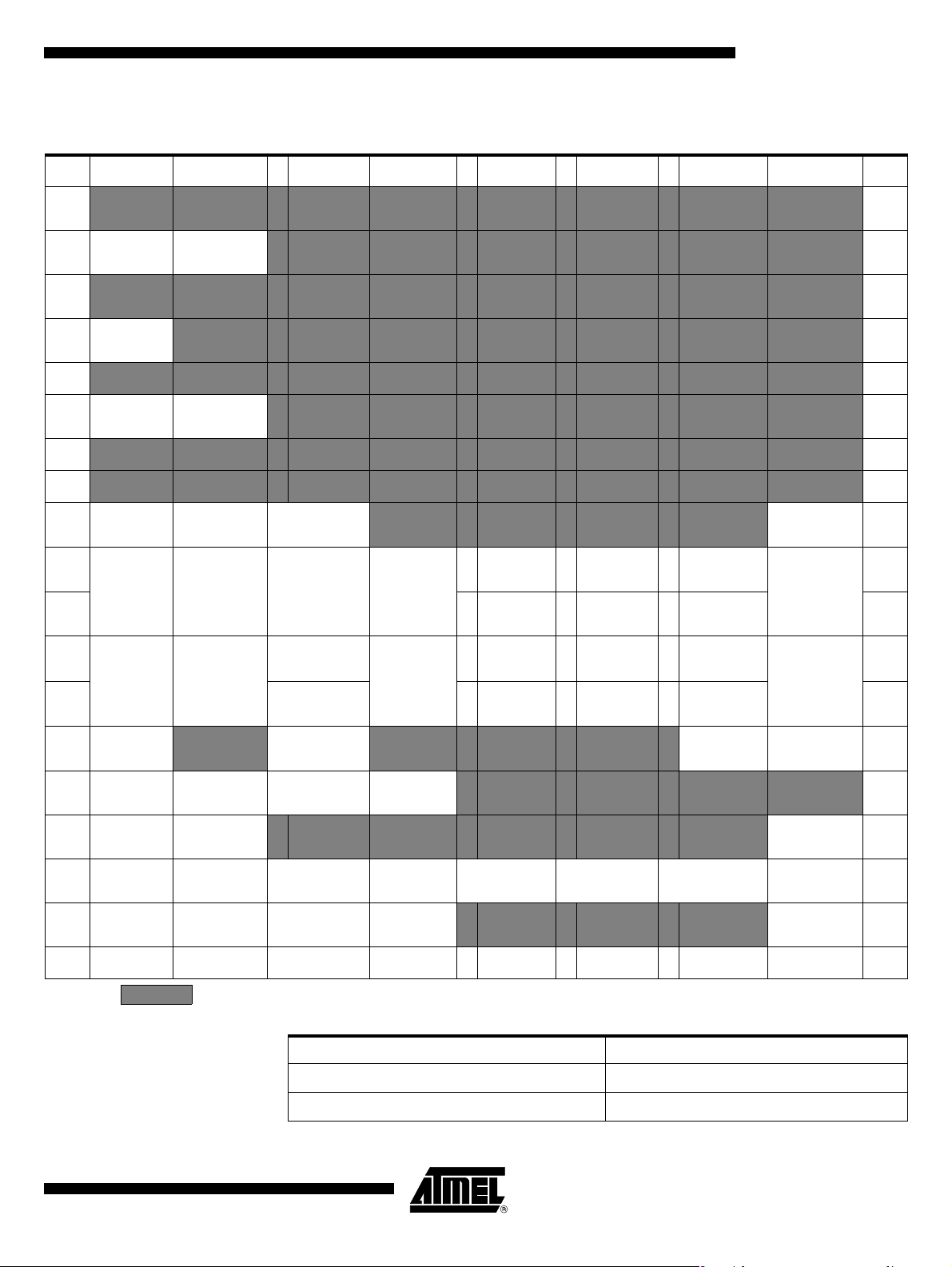

Interrupt S yst em The T8xC5121 has a total of 6 interrupt vectors: four external interrupts (INT0, INT1/OE,

CPRES, RxD), two Timer 0 interrupts (Timer 0s 0 and 1), serial port interrupt and Smart

Card Interface interrupt. These interrupts are shown in Figure 23.

Figure 23. Interrupt Control System

IPH0, IPL0

High Priority

Interrupt

INT0

0

1

IE0

EX0

3

0

TF0

Rxd

INT1/OE

CPRES

TF1

RI

TI

SCI

1

0

OELEV

0