Page 1

Features

• 80C51 Core Architecture

• 256 Bytes of On-chip RAM

• 256 Bytes of On-chip ERAM

– 16-KB of On-chip Flash Memory

– Data Retention: 10 Years at 85°C

– Read/Write Cycle: 10K

• 2K Bytes of On-chip Flash for Bootloader

• 2K Bytes of On-chip EEPROM

– Read/Write Cycle: 100k

• 14-sources 4-level Interrupts

• Three 16-bit Timers/Counters

• Full Duplex UART Compatible 80C51

• Maximum Crystal Frequency 40 MHz

–InX2Mode,20MHz(CPUcore,40MHz)

• Three or Four Ports: 16 or 20 Di gital I/O Lines

• Two-channel 16-bit PCA with:

– PWM (8-bit)

– High-speed Output

– Timer and Edge Capture

• Double Data Pointer

• 21-bit WatchDog Timer (7 Programmable Bits)

• A 10-bit Resolution Analog to Digital Converter (ADC) with 8 Multiplexed Inputs

• Power Saving Modes:

– Idle Mode

– Power-down Mode

• Power Supply: 5V ± 10% (or 3V

• Temperature Range: Industrial (-40° to +85°C)

• Packages: SOIC28, PLCC28, VQFP32

Note: 1. Ask for availability

(1)

± 10%)

Low Pin Count

8-bit MCU with

A/D Converter

and 16-Kbytes of

Flash Memory

T89C5115

Description

The T89C5115 is a high performance Flash version of the 80C51 single chip 8-bit

microcontrollers. It contains a 16-KB Flash m emory block for program and data.

The 16-KB Flash memory can be programmed either in parallel mode or in s erial

mode with the I SP capability or with software. The programming voltage is int ernally

generated from the standard V C C pin.

The T89C5115 retains all features of t he 80C52 with 256 bytes of int ernal RAM, a 7source 4-level interrupt controller and three t imer/counters. In addition, the T89C5115

has a 10-bit A/D converter, a 2-KB Boot Flash m emory, 2-KB EEPROM for data, a

Programmable Counter Array, an ERAM of 256 bytes, a Hardware WatchD og Timer

and a more versatile serial c hannel that facilitates mul tiprocessor communication

(EUART). The fully static design of the T89C5115 reduces system power consumption

by bringing the clock frequency down to any value, even DC, without loss of data.

The T89C5115 has two software-selectable modes of reduced activity and an 8 bit

clock prescaler for further reduction in power consumption. In the idle mode the CPU

is frozen w hile the peripherals and the i nterrupt system are still o perating. In the

power-down mode the RAM is saved and all other functions are inoperative.

The added features of the T89C5115 m ak e it more powerful for applications that need

A/D con version, pulse width m odula tion, high speed I/O and counting capabilities

such as industria l control, cons umer goods, alarms, motor control, etc. While remaining fully compatible with the 80C52 it offers a superset of this standard microcontroller.

Rev. 4128A–8051–04/02

1

Page 2

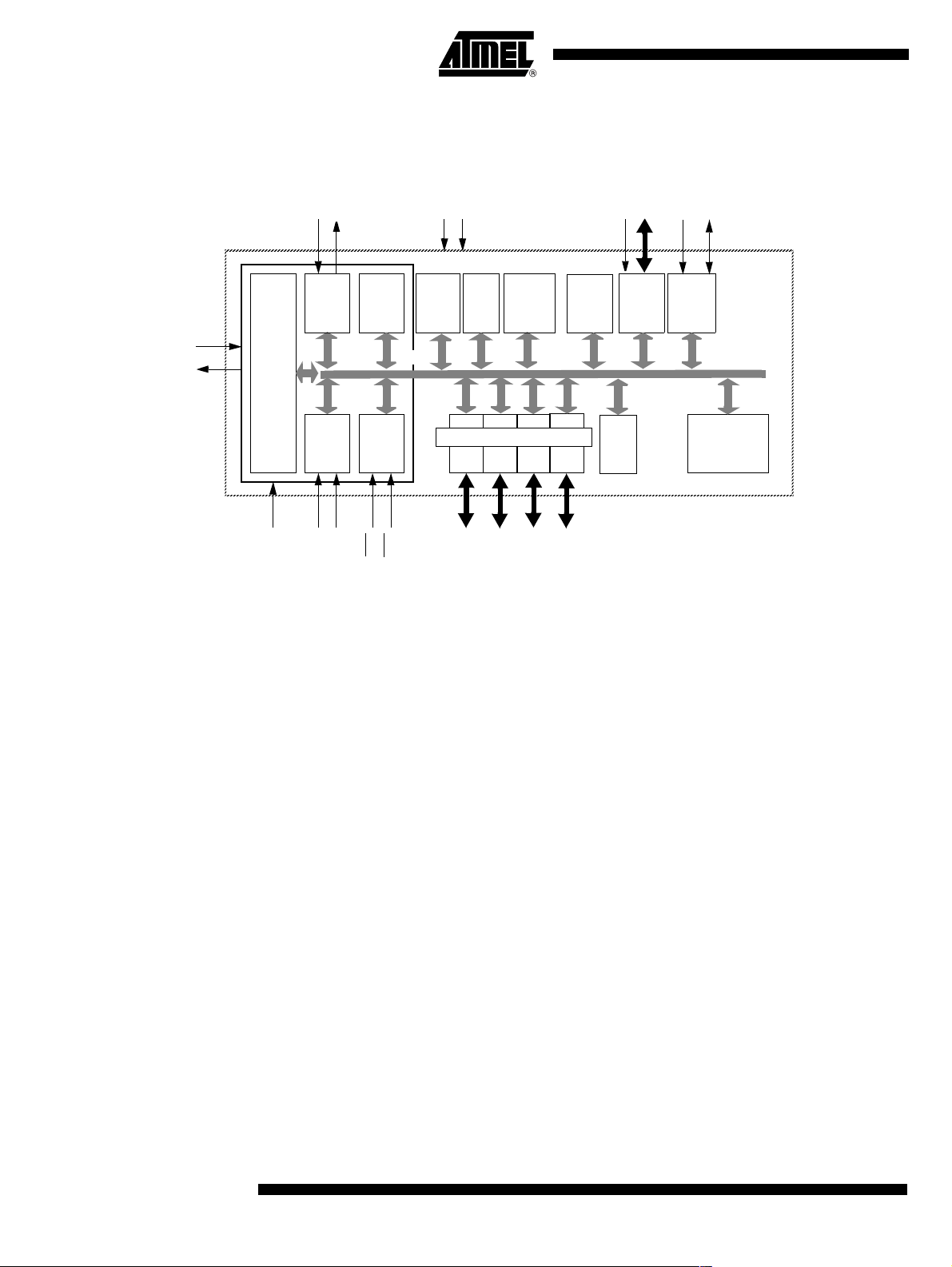

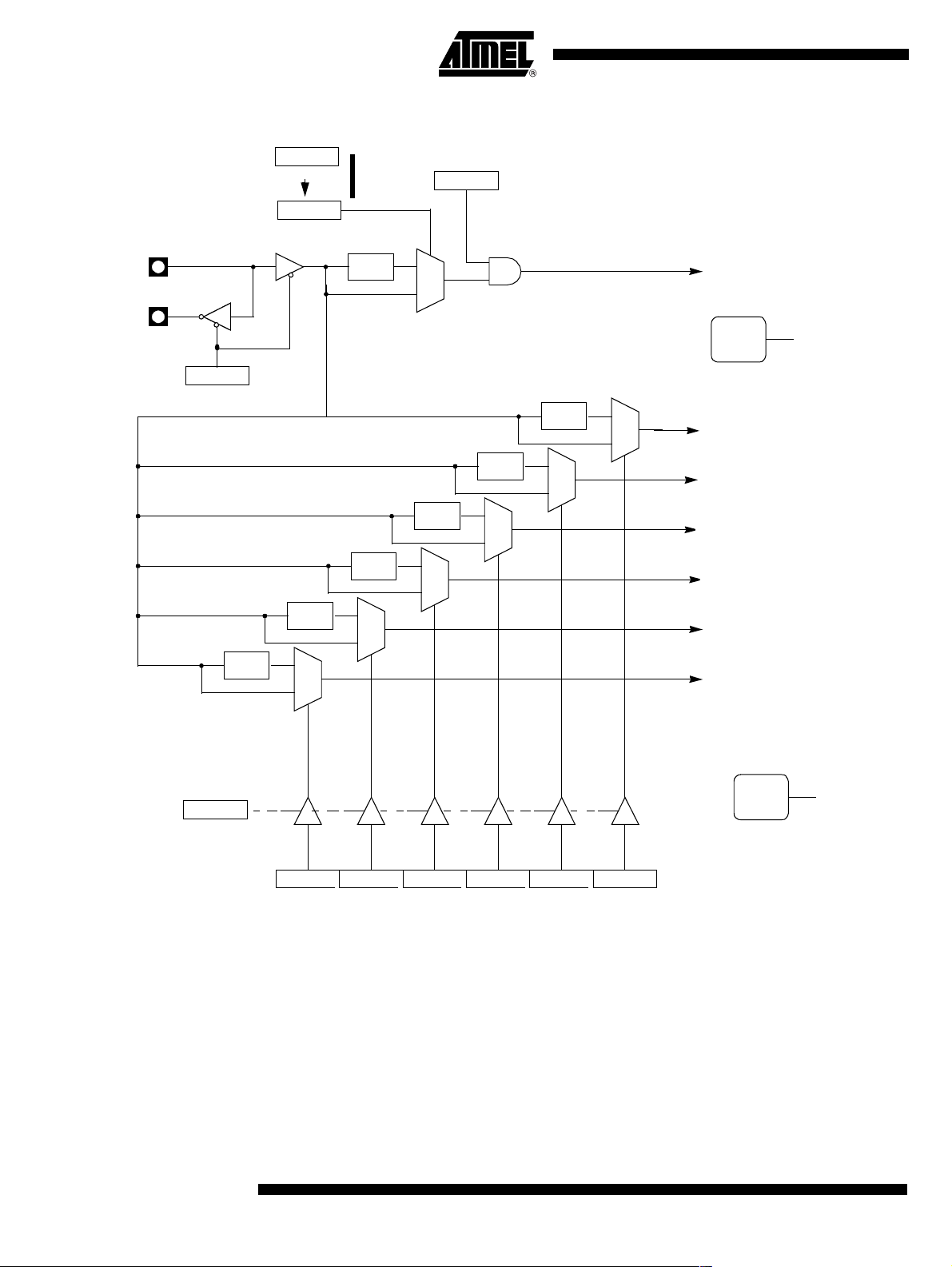

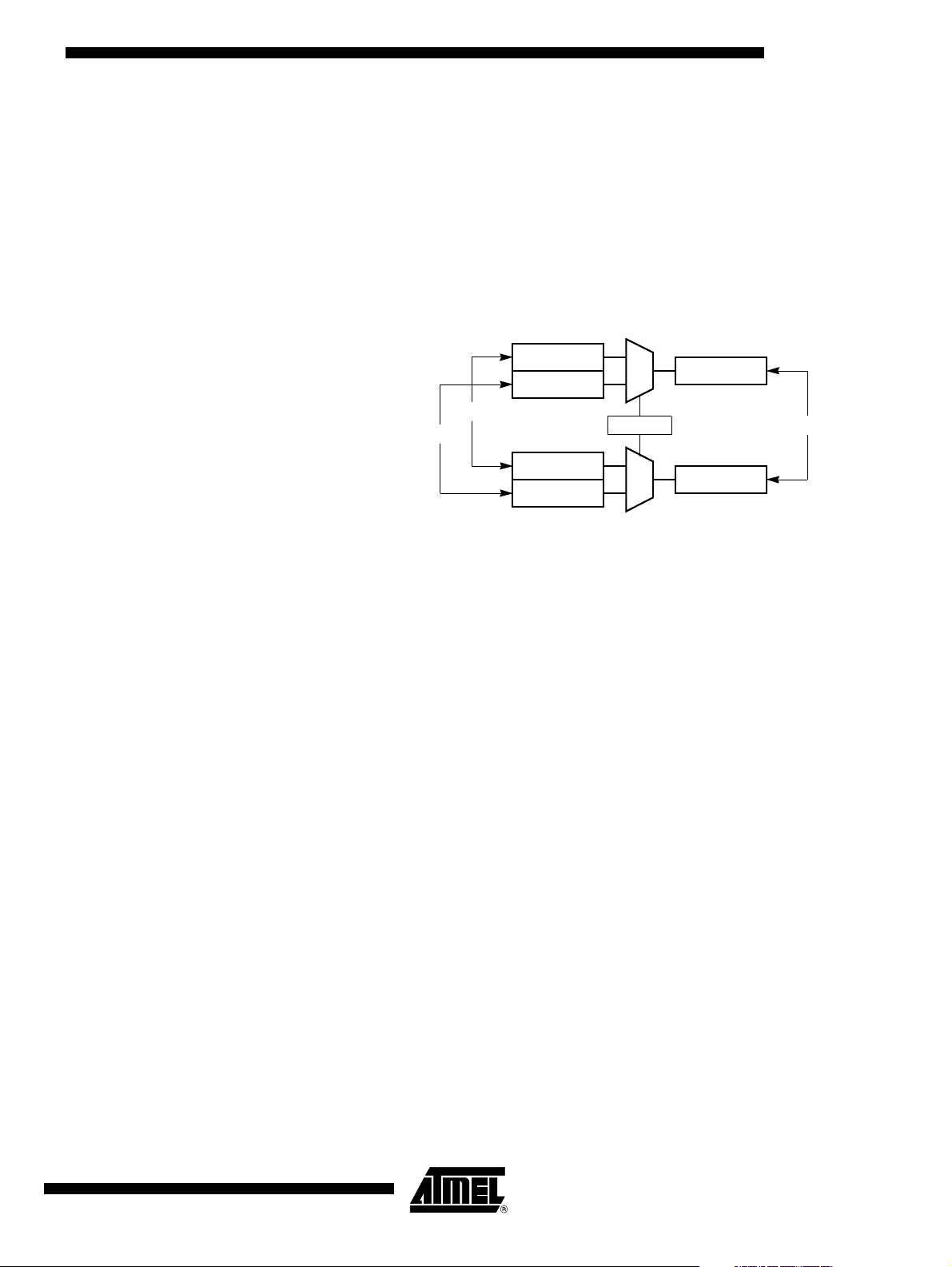

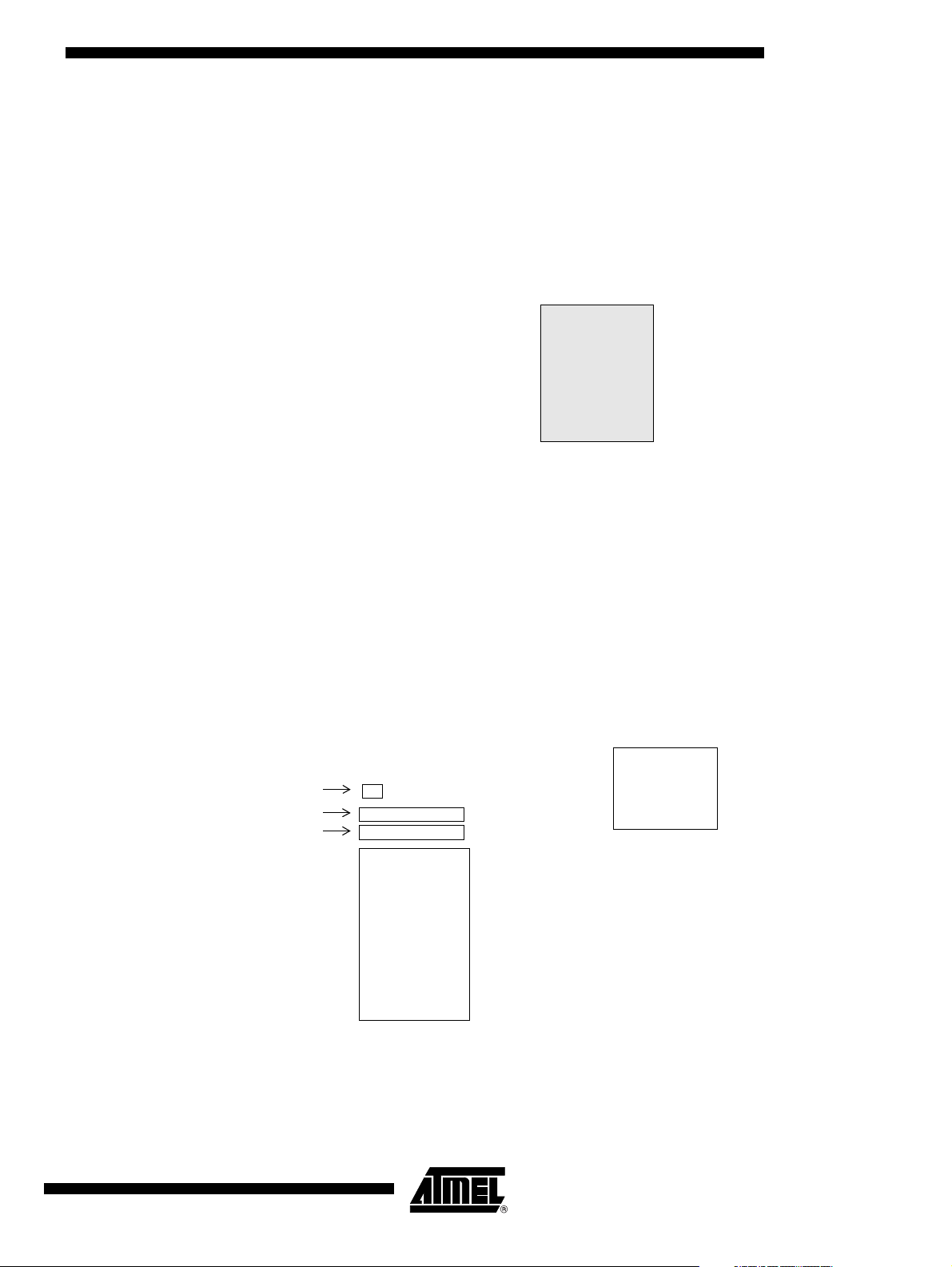

Block Diagram

In X2 mode a m aximum external clock rate of 20 MHz reaches a 300 ns cycle time.

PCA

Vss

RxD

TxD

Vcc

ECI

T2EX

T2

XTAL1

XTAL2

CPU

RESET

Notes: 1. 8 analog Inputs/8 Digital I/O

2. 2-Bit I/O Port

UART

Timer 0

Timer 1

T0

C51

CORE

T1

RAM

256x8

INT

Ctrl

INT0

INT1

Flash

Boot

16kx8

loader

2kx8

IB-bus

Parallel I/O Ports & Ext. Bus

Port 1

Port 2

(2)

(1)

P1

P2

EEPROM

2kx8

Port 3

P3

Port 4

ERAM

256x8

P4(2)

Watch

Dog

PCA

Timer2

10-bit

ADC

2

T89C5115

4128A–8051–04/02

Page 3

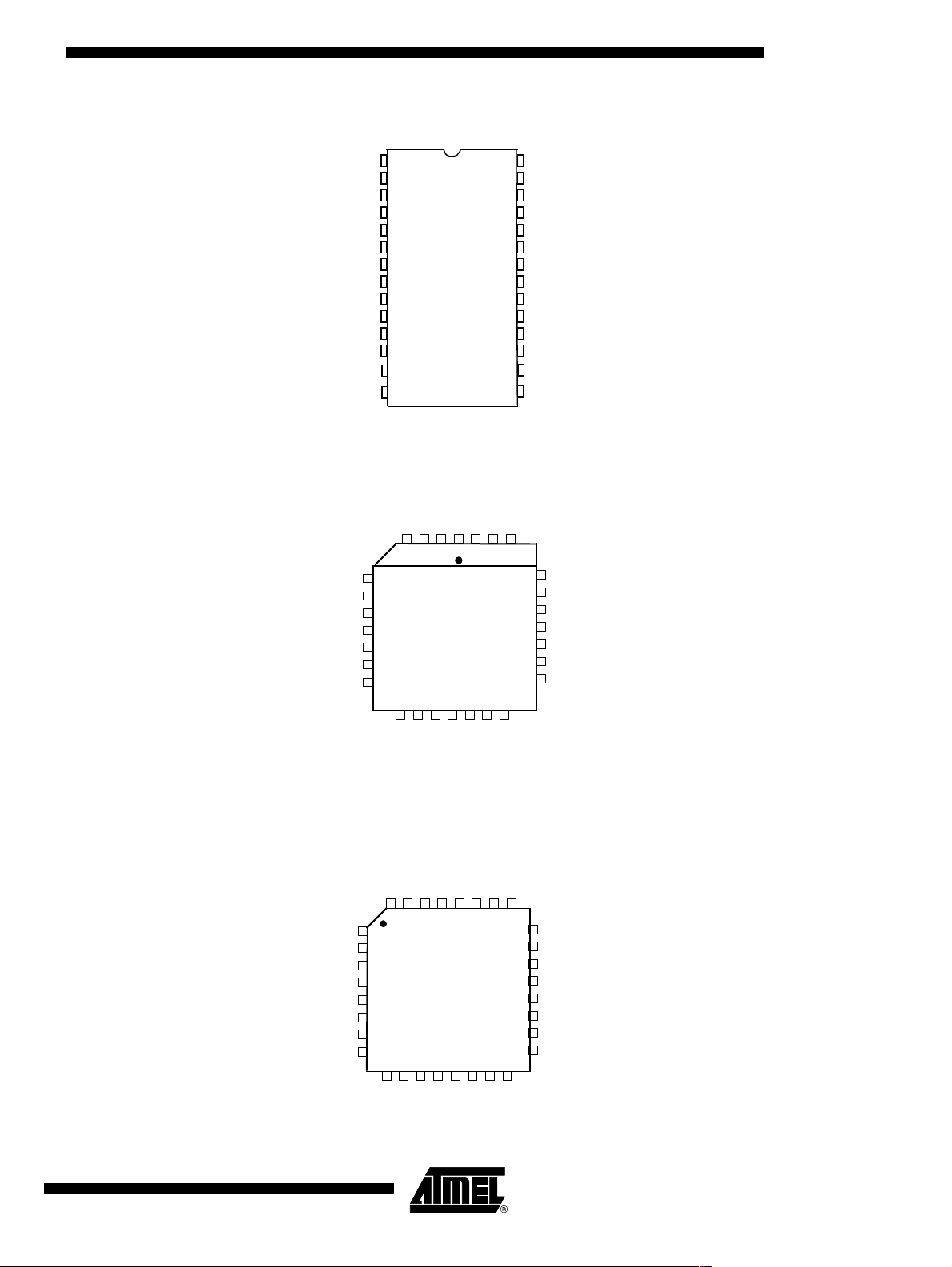

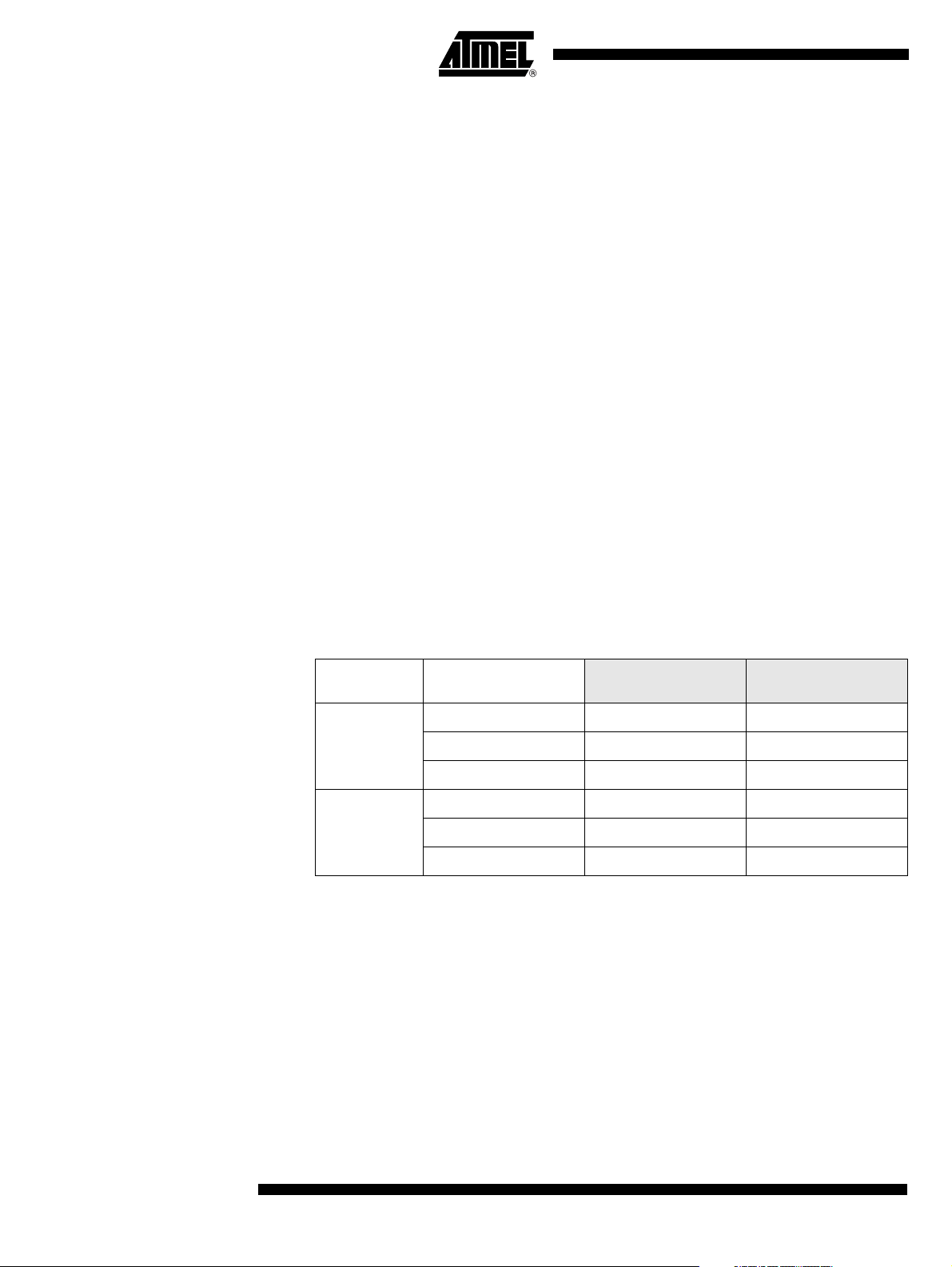

Pin Configuration

T89C5115

VAREF

VAGND

VAVCC

P3.5/T1

P3.4/T0

P3.3/INT1

P3.2/INT0

P3.1/TxD

P3.0/RxD

P4.0

P2.1

P3.7

P3.6

P3.5/T1

P3.4/T0

P3.3/INT1

P4.1

P4.0

P2.1

P3.7

P3.6

1

2

3

4

5

6

7

SO28

8

9

10

11

12

13

14

VAGND

VAVCC

P4.1

432

5

6

7

PLCC-28

8

9

10

11

12131415161718

P1.0 /AN0/T2

VAREF

1

282726

28

P1.0/

27

P1.1/AN1/T2EX

26

P1.2/AN2/ECI

25

P1.3/AN3/CEX0

P1.4/AN4/CE X1

24

P1.5/AN5

23

P1.6/AN6

22

P1.7/AN7

21

P2.0

20

RESE

19

18

VSS

VCC

17

XT AL1

16

XTAL2

15

P1.2 /AN2/ECI

P1.1 /AN1/T2E X

25

24

23

22

21

20

19

AN0/T2

T

P1.3/AN3/CEX0

P1.4/AN4/CEX1

P1.5/AN5

P1.6/AN6

P1.7/AN7

P2.0

RESET

4128A–8051–04/02

P4.0

P2.1

P3.7

P3.6

P3.5/T1

P3.4/T0

NC

P3.3/INT1

VSS

VCC

XTAL1

XTAL2

P3.1/TxD

P3.0/RxD

P3.2/INT0

P4.1

NC

VAREF

VAGND

VAVCC

30

31

32

1

2

3

4

5

6

7

8

9

101112

P3.1/TxD

P3.2/INT0

28

29

QFP-32

131415

NC

XTAL2

P3.0/RxD

P1.0/AN 0/T2

27

XTAL1

P1.2/AN2/ECI

P1.1/AN1/T2EX

25

26

P1.3/AN3/CEX0

24

P1.4/AN4/CEX1

23

P1.5/AN5/CEX2

22

P1.6/AN6/CEX3

21

P1.7/AN7/CEX4

20

P2.0

19

NC

18

RESET

17

16

VSS

VCC

3

Page 4

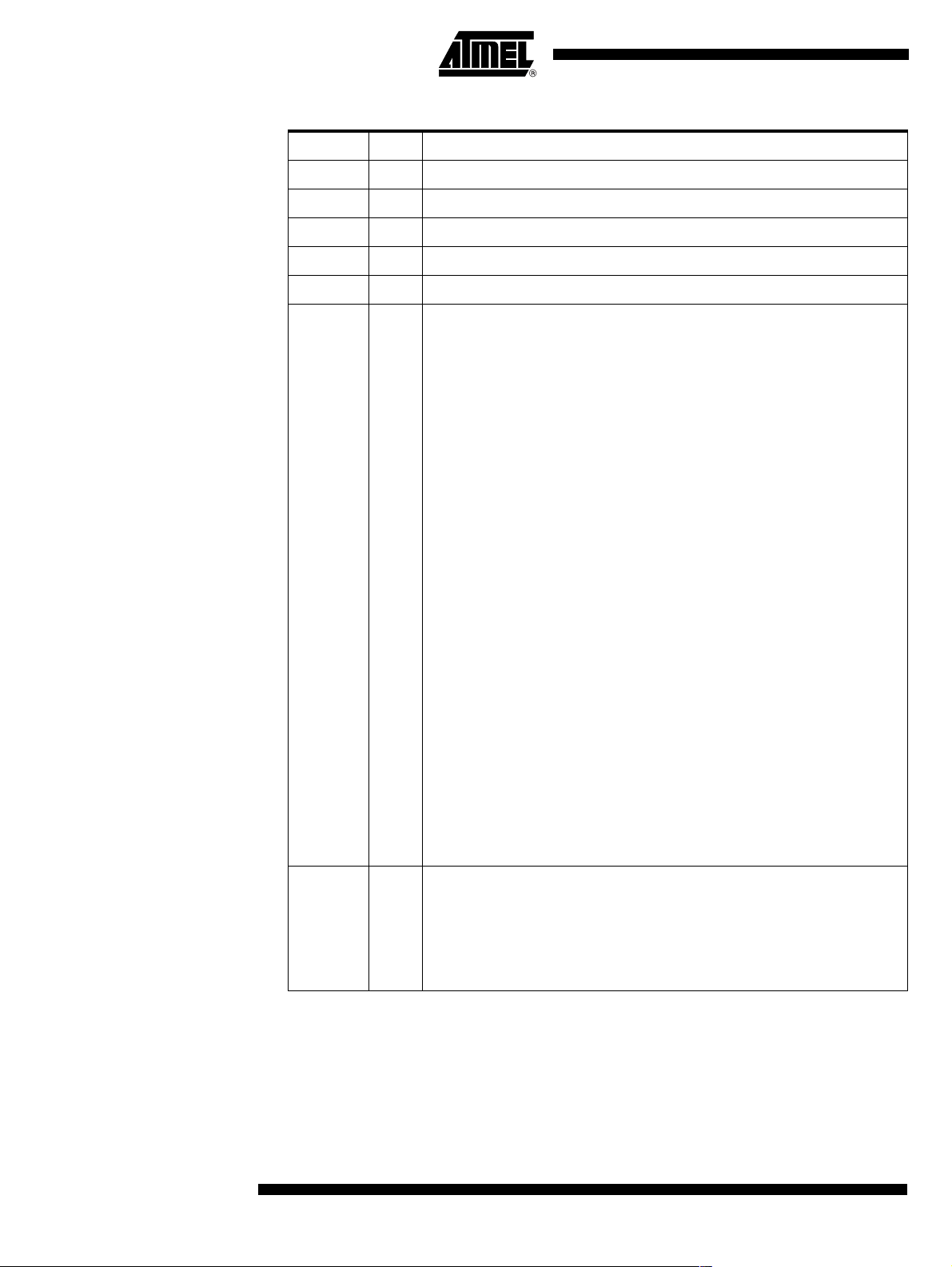

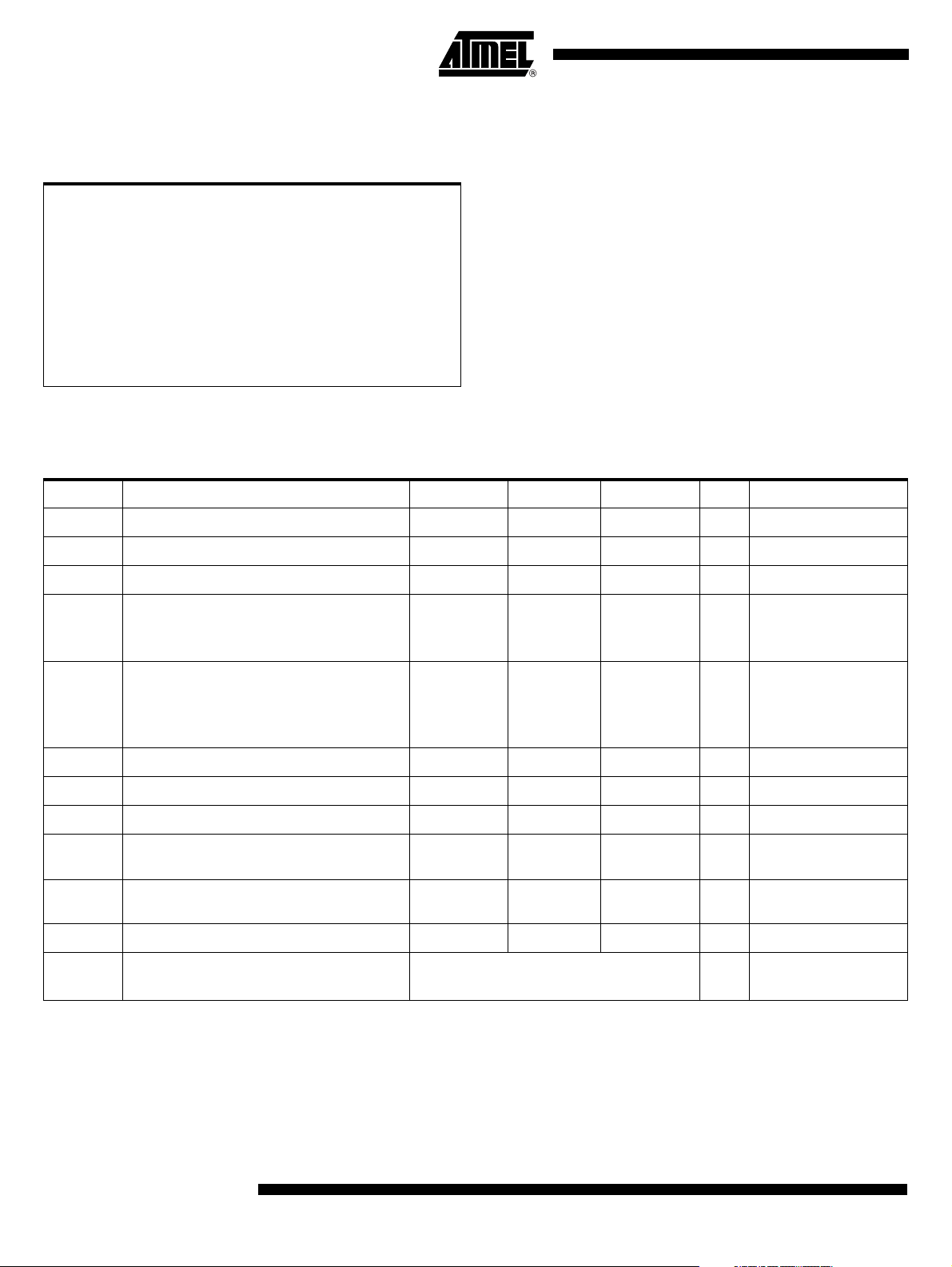

Table 1. Pin Description

Pin Name Type Description

VSS GND Circuit ground

VCC Supply Voltage

VAREF Reference Voltage for ADC

VAVCC Supply Voltage for ADC

VAGND Reference Ground for ADC

P1.0:7 I/O Port 1:

Is an 8-bit bi-directional I/O port with internalpull-ups. Port 1 pins can be used for

digital input/output or as analoginputs for the AnalogDigital Converter(ADC). Port 1

pins that have 1’s written to them are pulled high by the internal pull-up transistors

and can be used as inputs in this state. As inputs, Port 1 pins that are being pulled

lowexternallywillbethesourceof current(I

becauseof the internal pull-ups.Port 1 pins are assigned to be used as analog

inputs via the ADCCF register (in this case the internal pull-ups are disconnected).

As a secondary digitalfunction, port 1 containsthe Timer2 externalt rigger and clock

input; the PCA external clock input and the PCA module I/O.

P1.0/AN0/T2

Analoginput channel 0,

External clock input for Timer/counter2.

P1.1/AN1/T2EX

Analoginput channel 1,

Trigger input f or Timer/counter2.

P1.2/AN2/ECI

Analoginput channel 2,

PCA external clock input.

P1.3/AN3/CEX0

Analoginput channel 3,

PCA module 0 Entry of input/PWM output.

P1.4/AN4/CEX1

Analoginput channel 4,

PCA module 1 Entry of input/PWM output.

P1.5/AN5

Analoginput channel 5,

P1.6/AN6

Analoginput channel 6,

P1.7/AN7

Analoginput channel 7,

It can drive CMOS inputs without external pull-ups.

, see section"Electrical Characteristic")

IL

Port 2:

Is an 2-bit bi-directional I/O port with internalpull-ups. Port2 pins that have 1’s

writtento them are pulled high by the internalpull-ups andcan be used as inputsin

P2.0:7 I/O

4

T89C5115

this state. As inputs, Port 2 pins that are being pulled low externally will be a source

of current (IIL, on the datasheet) because of the internal pull-ups.

IntheT89C51CC02Port2cansinkorsource5mA.ItcandriveCMOSinputs

without external pull-ups.

4128A–8051–04/02

Page 5

Table 1. Pin Description (Continued)

Pin Name Type Description

P3.0:7 I/O Port 3:

Is an 8-bit bi-directional I/O port with internalpull-ups. Port3 pins that have 1’s

writtento them are pulledhigh by the internalpull-uptransistorsand can be used as

inputs in thisstate.As inputs, Port 3 pinsthatare beingpulledlowexternally will be a

sourceof current(I

pull-ups.

The outputlatchcorrespondingto a secondaryfunction must be programmedto one

for that function to operate (except for TxD ). The secondary functions are assigned

to the pins of port 3 as follows:

P3.0/RxD:

Receiver data input (asynchronous) or data input/output (synchronous) of the serial

interface

P3.1/TxD:

Transmitter data output (asynchronous) or clock output (synchronous) of the serial

interface

P3.2/INT0

External interrupt 0 input/timer 0 gate control input

P3.3/INT1

External interrupt 1 input/timer 1 gate control input

P3.4/T0:

Timer 0 counter input

P3.5/T1:

Timer 1 counter input

It can drive CMOS inputs without external pull-ups.

:

:

, see section "Electrical Characteristic") becauseof the internal

IL

T89C5115

P4.0:1 I/O

RESET I/O

XTAL1 I

XTAL2 O

Port 4:

Is an 2-bit bi-directional I/O port with internalpull-ups. Port4 pins that have 1’s

writtento them are pulled high by the internalpull-upsand can be used as inputsin

this state. As inputs, Port 4 pins that are being pulled low externally will be a source

of current (IIL, on the datasheet) because of the internal pull-up transistor.

It can drive CMOS inputs without external pull-ups.

Reset:

A high level on this pin during two machine cycles while the oscillator is running

resetsthe device. An internal pull-downresistorto VSS permitspower-onreset

using only an external capacitor to VCC.

XTAL1:

Input of the invertingoscillator amplifier and input of the internalclock generator

circuits. To drive the device from an external clock source, XTAL1 should be driven,

while XTAL2 is left unconnected. To operate above a frequency of 16 MHz, a duty

cycle of 50% should be maintained.

XTAL2:

Output from the inverting oscillator amplifier.

4128A–8051–04/02

5

Page 6

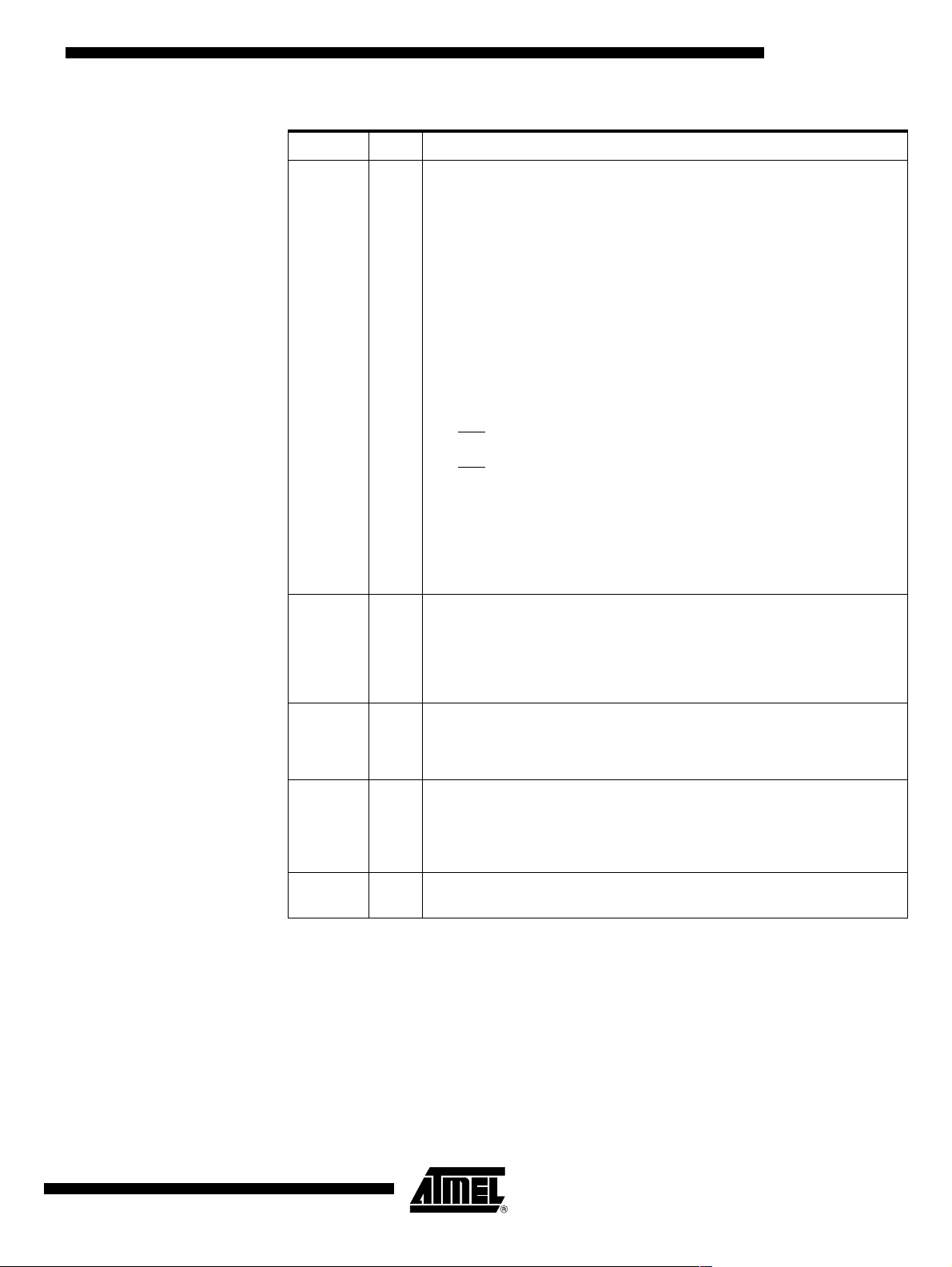

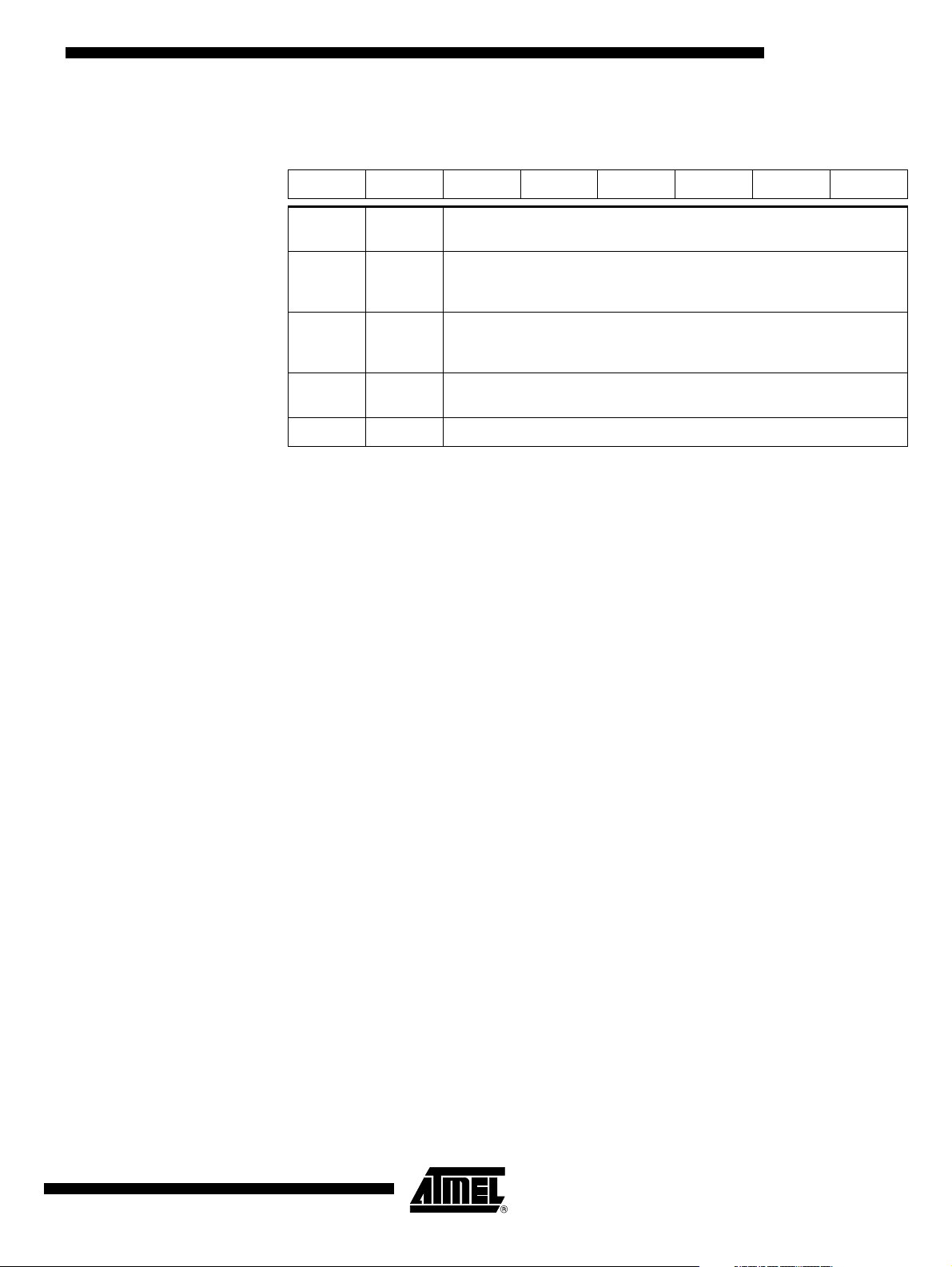

I/O Configurations Each Port SFR operates v ia type-D latches, as illustrated in Figure 1 f or Ports 3 and 4. A

CPU "write to latch" signal initiates transfer of internal bus data into t he type-D latch. A

CPU "read latch" signal transfers the latched Q output on to the internal b us. Sim ilarly, a

"read pin" signal transfers the logical level of the Port pin. Some Port data instructio ns

activate the "read latch" signal while others activate the "read pin" signal. Latch instructions are referre d to as R ead -Modif y-Writ e instructio ns. Each I/O line may be

independently programmed as input or output.

Port Structure Figure 1 shows the st ruc t ure of Ports, which have internal pull-ups. An external source

can pull the pin low. Each Port pin can be configured e ither for general-purpose I/O or

for its alternate input output function.

To use a pin for general-purpose output, set or clear the corresponding bit in the Px register (x = 1 to 4). T o use a pin for general-purpose input, se t the bit in the Px register.

This turns off the output FET drive.

To configure a pin for its alternate function, set the bit in the Px register. When the latch

is set, the "alternate output f unc tion" signal controls the outp ut level (see Figure 1). The

operation of Ports is discussed further in "quasi-Bidirectional Port Operation" p aragraph.

Figure 1. Ports Structure

VCC

READ

LATCH

INTERNAL

BUS

WRITE

TO

LATCH

READ

PIN

D

CL

LATCH

ALTERNATE

OUTPUT

FUNCTION

Q

ALTERNATE

INPUT

FUNCTION

INTERNAL

PULL-UP (1)

Note: The internal pull-up can be disabled on P1 when analog function is selected.

P1.x

P2.x

P3.x

P4.x

6

T89C5115

4128A–8051–04/02

Page 7

T89C5115

Read-Modify-Write Instructions

Some instruction s read the latch da ta rather than the pin data. The latch based instructions read the data, modify the data and then rewrite the latch. These are called "ReadModify-Write" instructions. B elow is a complete list of these special instructions (see

Table ). When the destination operand is a Port or a Port bit, t hes e instructions read the

latch rather than the pin:

Table 2. Read-Modify-Write Instructions

Instruction Description Example

ANL logical A ND ANL P1, A

ORL logical OR ORL P2, A

XRL logical E X-OR XRL P3, A

JBC jump if bit = 1 and clear bit JBC P1.1, LABEL

CPL complement bit CPL P3.0

INC increment INC P2

DEC decrement DEC P2

DJNZ decrement and jump if not zero DJNZ P3, LABEL

MOV Px.y, C move carry bit to bit y of Port x MOV P1.5, C

CLR Px.y clear bit y of Port x CLR P2.4

SET Px.y set bit y of Port x SET P3.3

Quasi-bidirectional Port Operation

It is not obvious the last three instructions in this l ist are Read-Modify-Write instructions.

These instructions read the port (all 8 bits), modify the specifically addressed bit and

write the new byte back to the la tch. These Read-Modify-Write inst ruc tions are directed

to the latch rather than the pin in order to av oid possible misinterpretation of voltage

(and therefore, logic) levels at the pin. For example, a Port bit used to drive the base of

an external bipolar transistor can not rise above the transistor’s base-emitter junction

voltage (a value lower than VIL). With a lo gic one written to the bit, attempts by the CPU

to read the Port at the pin are misinterpreted as logic zero. A read of the latch rather

than the pins r eturns the correct logic-one v alue.

Port 1, Port 3 and Port 4 have fixed internal pull-ups and are referred to as "quasi-bidirectional" Ports. When c onfigured as an input, the pin impedance appears as logic one

and sources current in response to an external logic zero condition. Resets write logic

one to all Port latches. If logical zero is subsequently written to a Port latch, it can be

returned to input conditions by a logical one written to the latch.

Note: Port latch values change near the end of Read-Modify-Write insruction cycles. Output

buffers (and therefore t he pin state) update early in the instruction after Read-ModifyWrite instruction cycle.

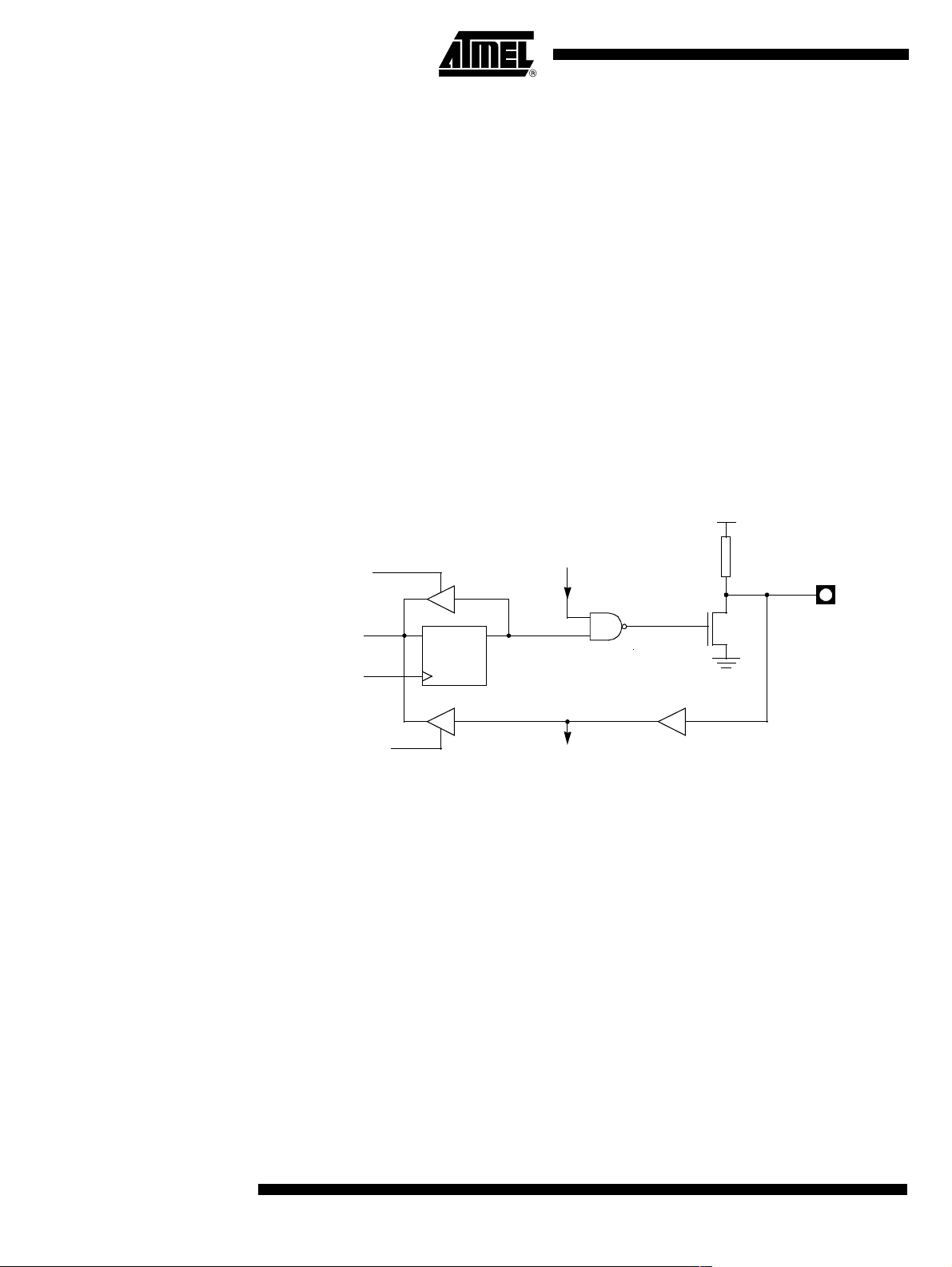

Logical zero-to-one transitions in Port 1, Port 3 and Port 4 use an additional pull-up (p1)

to aid this logic transition see Figure 2. This increases s witch speed. This extra pull-up

sources 100 times normal internal ci rc uit cu rrent du ring 2 oscillator clo c k periods. The

internal pull-ups are fi eld-effect tr ans istors rather than linear resistors. Pull-ups consist

of t hree p-channel FET (pFET) devices. A pFET is on when the gate senses logical zero

and off when the gat e senses logical one. pFET #1 is turned on for two oscillator periods

immediately after a z ero-to-one transition in the Port l atch. A logic al one at the Port pin

turns on pFET #3 (a weak pull-up) through the inverter. This inverter and pFET pair form

a latch to drive logical one. pFET #2 is a very weak pull-up switched on whene ver the

4128A–8051–04/02

7

Page 8

associated nFET is switched off. This is traditional CMOS switch convention. Current

strengths are 1/10 that of pFET #3

Figure 2. Internal Pull-Up Configurations

2 Osc. PERIODS

VCCVCCVCC

OUTPUT DATA

INPUTDATA

READ PIN

p1(1)

n

p2

p3

P1.x

P2.x

P3.x

P4.x

8

T89C5115

4128A–8051–04/02

Page 9

T89C5115

SFR Mapping The Special Function Registers (SFRs) o f the T8 9C5115 fall into t he following

categories:

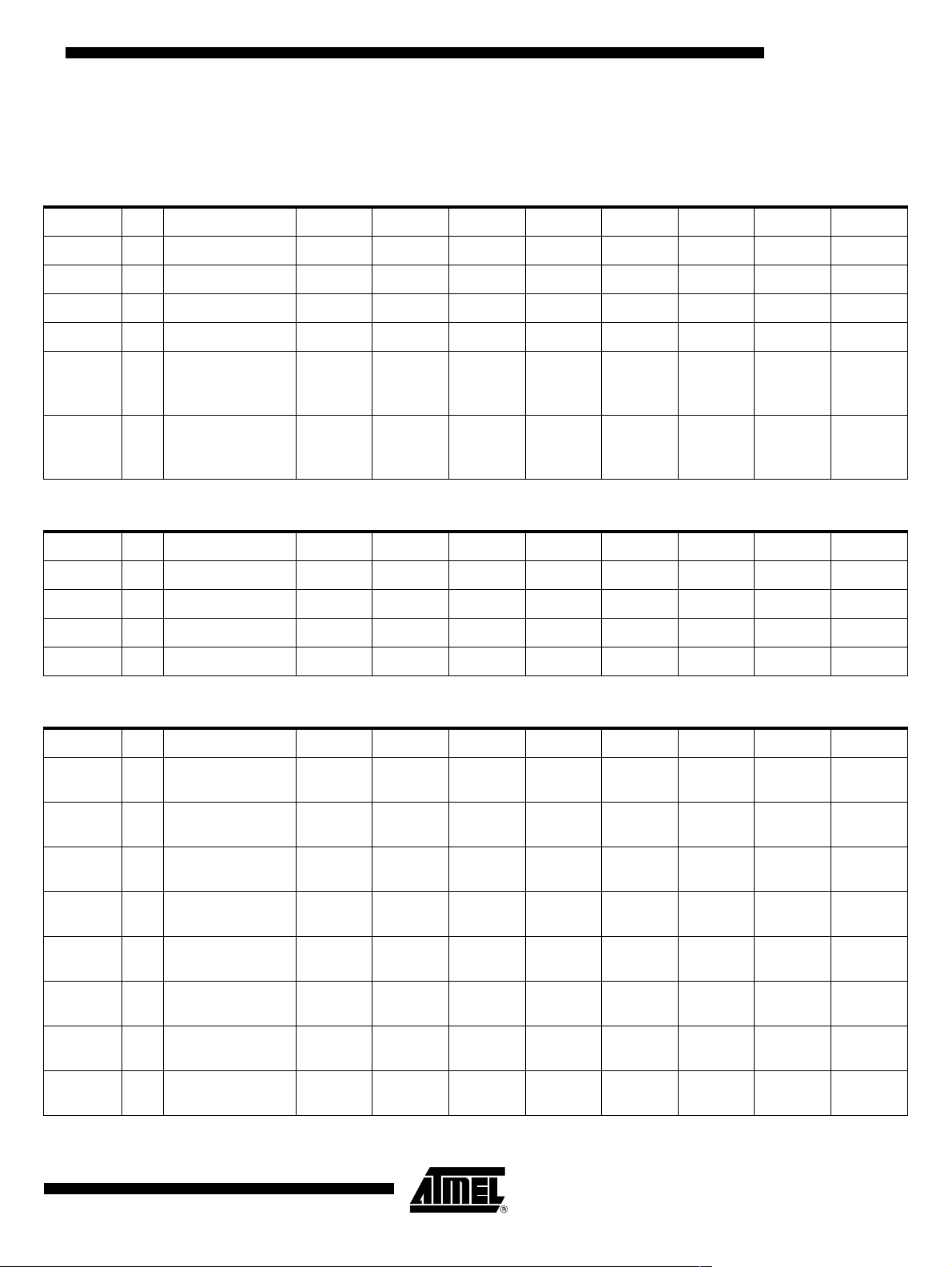

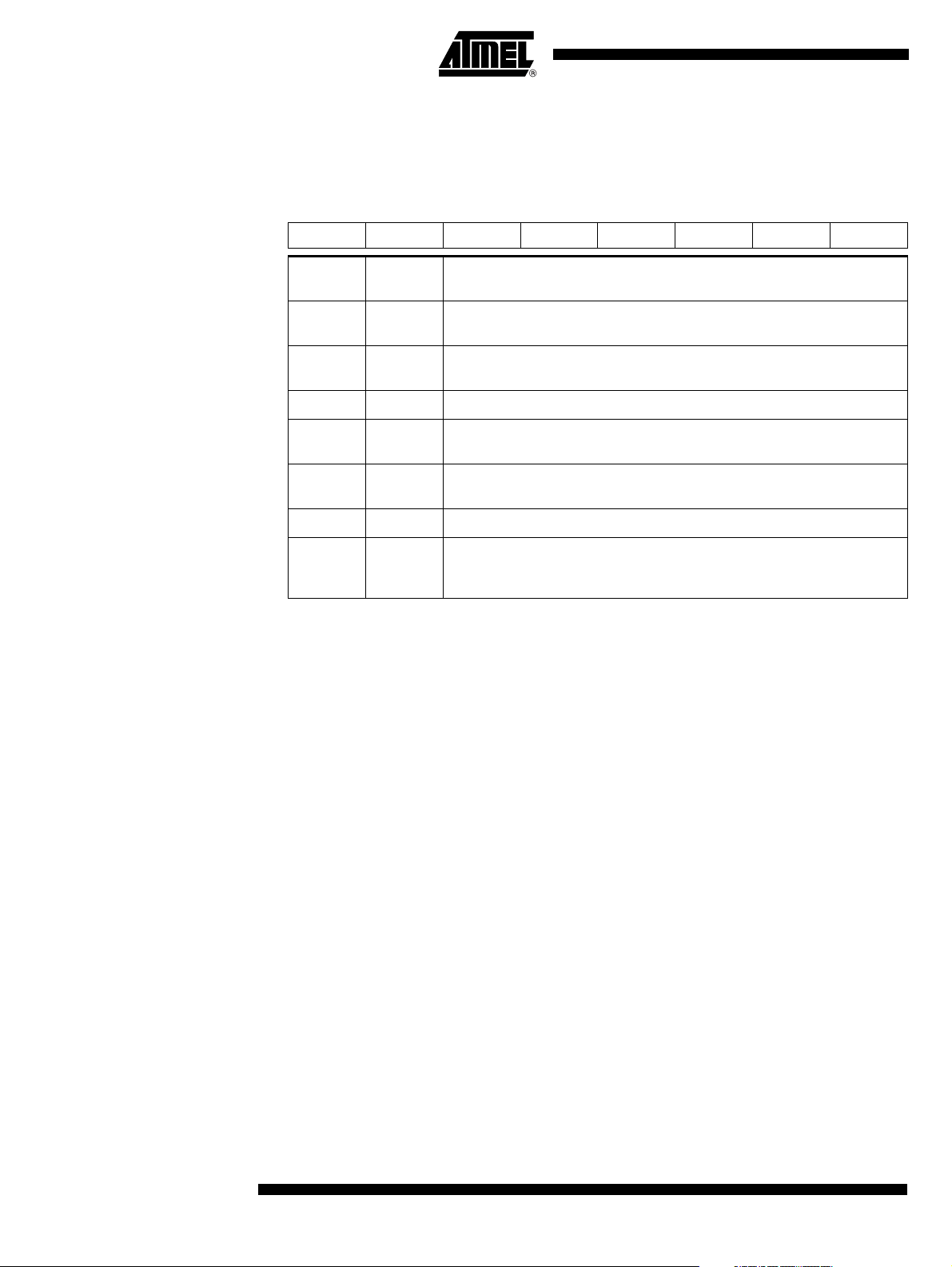

Table 3. C51CoreSFRs

MnemonicAddName 76543210

ACCE0hAccumulator ––––––––

B F0hBRegister ––––––––

PSW D0h Program Status Word CY AC F0 RS1 RS0 OV F1 P

SP81hStackPointer ––––––––

Data Po inter Low

DPL 82h

DPH 83h

byte

LSB of DPTR

Data Pointer High

byte

MSB of DPTR

––––––––

––––––––

Table 4. I/O Port SFRs

MnemonicAddName 76543210

P190hPort1 ––––––––

P2A0hPort2(x2) ––––––––

P3B0hPort3 ––––––––

P4C0hPort4(x2) ––––––––

Table 5. Timers SFRs

MnemonicAddName 76543210

TH0 8Ch

TL0 8Ah

TH1 8Dh

TL1 8Bh

TH2 CDh

Timer/Counter0High

byte

Timer/Counter 0 Low

byte

Timer/Counter1High

byte

Timer/Counter 1 Low

byte

Timer/Counter2High

byte

––––––––

––––––––

––––––––

––––––––

––––––––

TL2 CCh

TCON 88h

TMOD 89h

4128A–8051–04/02

Timer/Counter 2 Low

byte

Timer/Counter 0 and

1 control

Timer/Counter 0 and

1 Modes

––––––––

TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0

GATE1 C/T1# M11 M01 GATE0 C/T0# M10 M00

9

Page 10

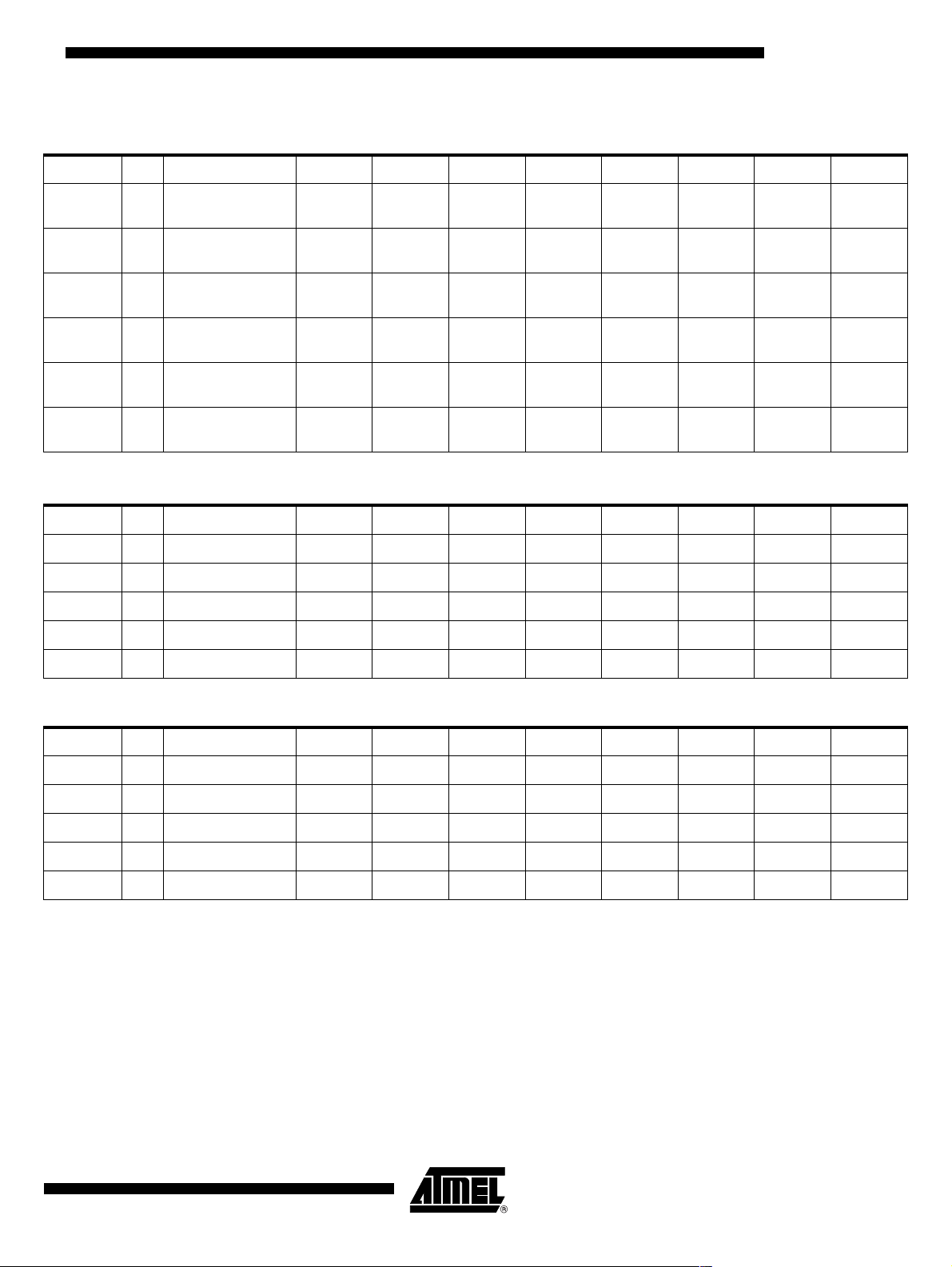

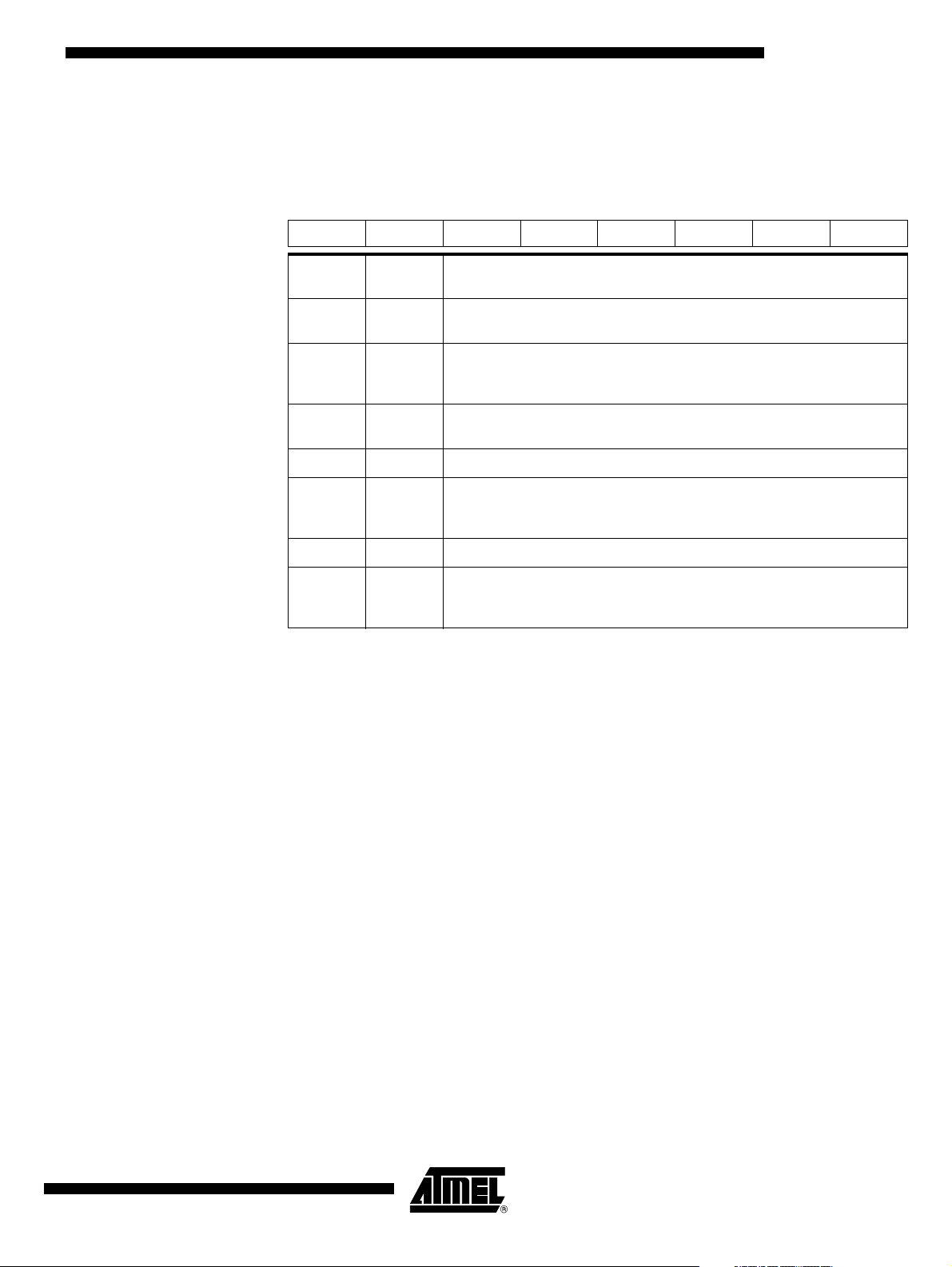

Table 5. Timers SFRs (Continued)

MnemonicAddName 76543210

T2CON C8h

T2MOD C9h

RCAP2H CBh

RCAP2L CAh

WDTRST A6h

WDTPRG A7h

Timer/Counter 2

control

Timer/Counter 2

Mode

Timer/Counter 2

Reload/Capture High

byte

Timer/Counter 2

Reload/Capture Low

byte

WatchDog Timer

Reset

WatchDog Timer

Program

TF2 EXF2 RCLK TCLK EXEN2 TR2 C/T2# CP/RL2#

––––––T2OEDCEN

––––––––

––––––––

––––––––

–––––S2S1S0

Table 6. Serial I/O Port SFRs

MnemonicAddName 76543210

SCON 98h Serial Control FE/SM0 SM1 SM2 REN TB8 RB8 TI RI

SBUF99hSerialDataBuffer––––––––

SADENB9hSlaveAddressMask––––––––

SADDRA9hSlaveAddress ––––––––

Table 7. PCA SFRs

Mnemo

-nicAddName 76543210

CCON D8h PCA Timer/Counter Control CF CR – CCF4 CCF3 CCF2 CCF1 CCF0

CMOD D9h PCA Timer/Counter Mode CIDL WDTE – – – CPS1 CPS0 ECF

CLE9hPCATimer/CounterLowbyte ––––––––

CH F9h PCA Timer/Counter High byte – – – – – – – –

CCAPM0

CCAPM1

CCAP0H

CCAP1H

CCAP0L

CCAP1L

DAh

PCA Timer/Counter Mode 0

DBh

PCA Timer/Counter Mode 1

FAh

PCA Compare Capture Module 0 H

FBh

PCA Compare Capture Module 1 H

EAh

PCA Compare Capture Module 0 L

EBh

PCA Compare Capture Module 1 L

–

CCAP0H7

CCAP1H7

CCAP0L7

CCAP1L7

ECOM0

ECOM1

CCAP0H6

CCAP1H6

CCAP0L6

CCAP1L6

CAPP0

CAPP1

CCAP0H5

CCAP1H5

CCAP0L5

CCAP1L5

CAPN0

CAPN1

CCAP0H4

CCAP1H4

CCAP0L4

CCAP1L4

MAT0

MAT1

CCAP0H3

CCAP1H3

CCAP0L3

CCAP1L3

TOG0

TOG1

CCAP0H2

CCAP1H2

CCAP0L2

CCAP1L2

PWM0

PWM1

CCAP0H1

CCAP1H1

CCAP0L1

CCAP1L1

ECCF0

ECCF1

CCAP0H0

CCAP1H0

CCAP0L0

CCAP1L0

10

T89C5115

4128A–8051–04/02

Page 11

T89C5115

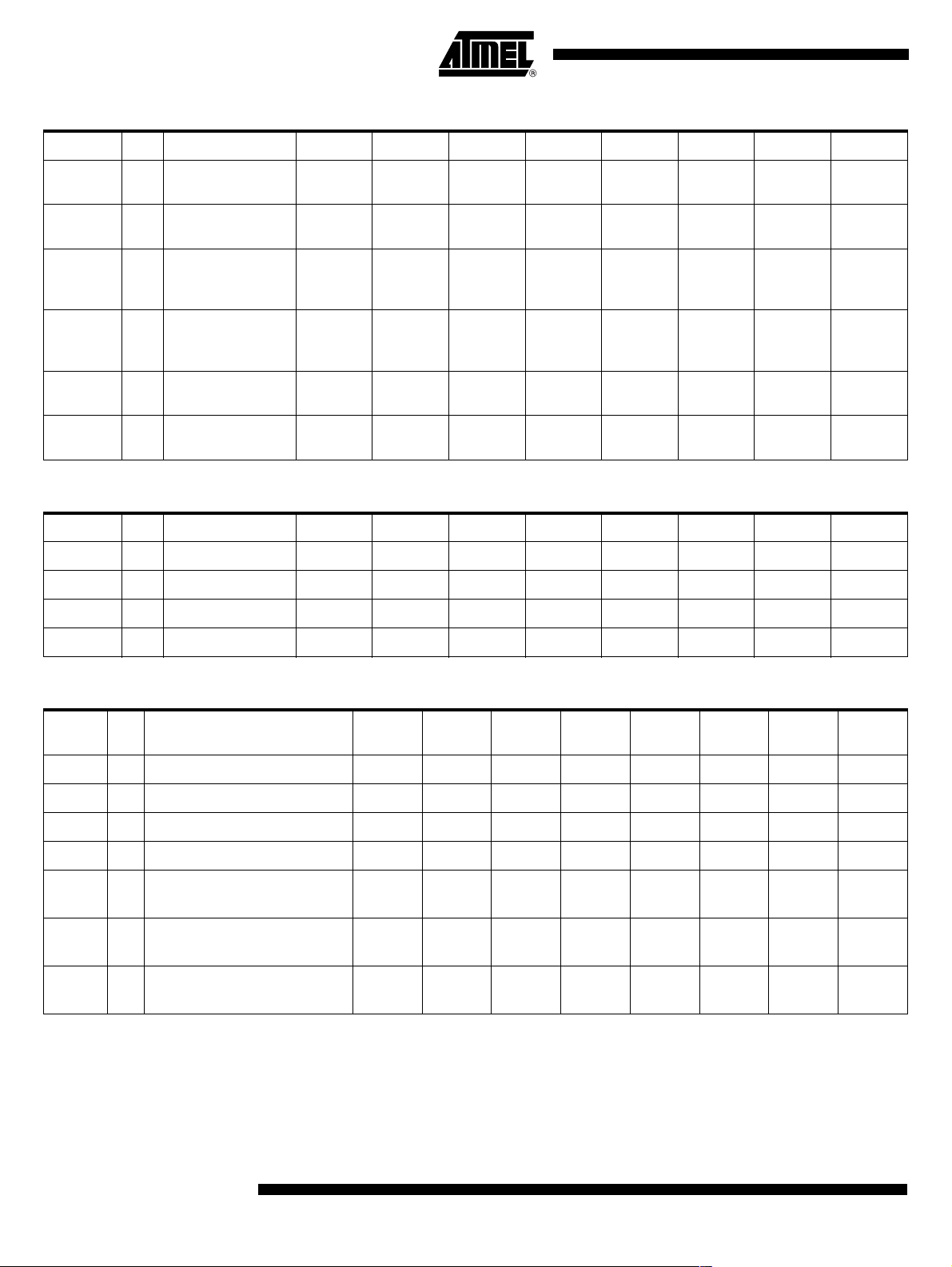

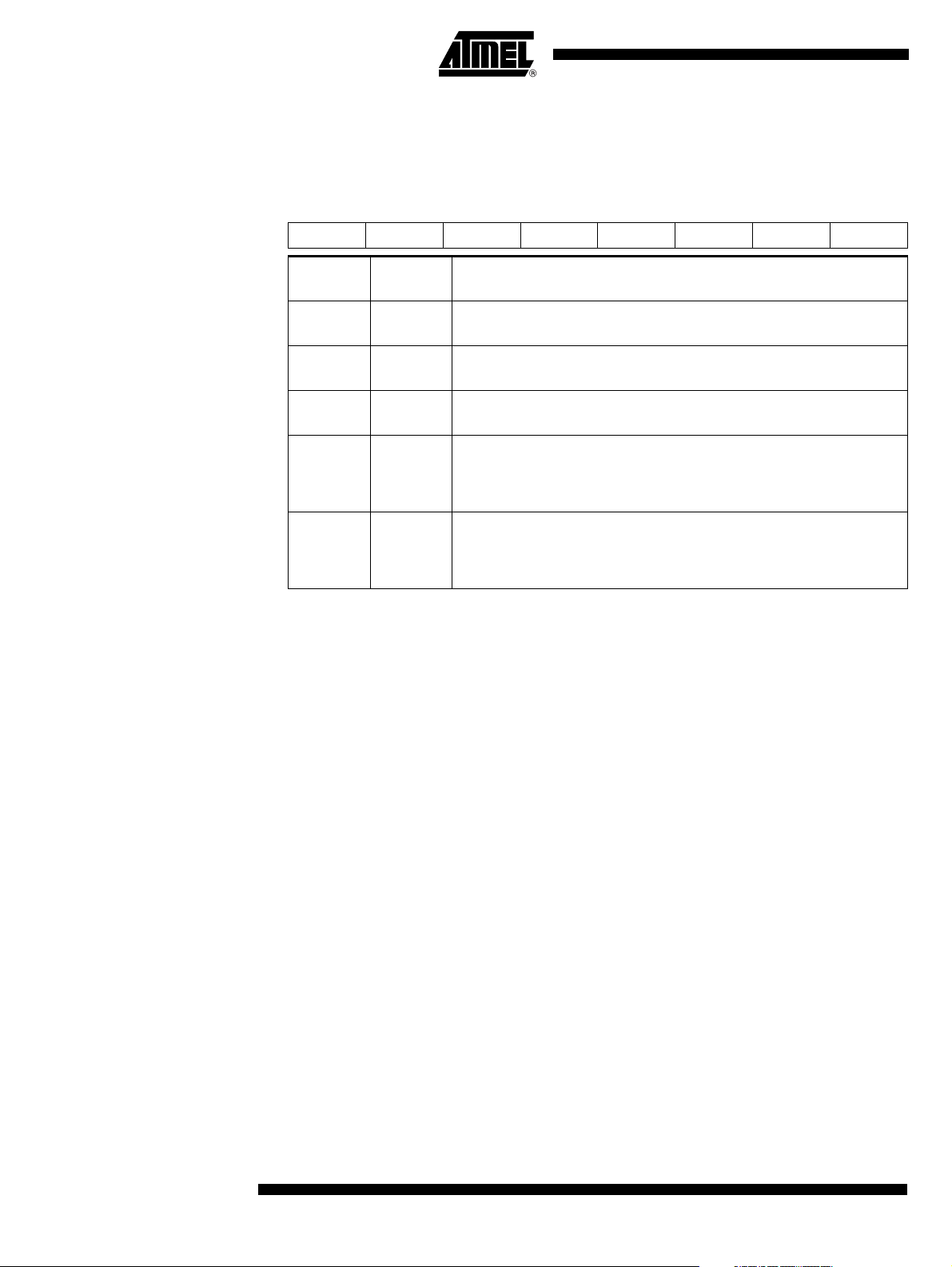

Table 8. Interrupt SFRs

MnemonicAddName 76543210

IEN0 A8h

IEN1 E8h

IPL0 B8h

IPH0 B7h

IPL1 F8h

IPH1 F7h

Interrupt Enable

Control 0

Interrupt Enable

Control 1

Interrupt Priority

Control Low 0

Interrupt Priority

Control High 0

Interrupt Priority

Control Low 1

Interrupt Priority

Control High1

EA EC ET2 ES ET1 EX1 ET0 EX0

––––––EADC–

– PPC PT2 PS PT1 PX1 PT0 PX0

– PPCH PT2H PSH PT1H PX1H PT0H PX0H

––––––PADCL–

––––––PADCH–

Table 9. ADC SFRs

MnemonicAddName 76543210

ADCON F3h ADC Control – PSIDLE ADEN ADEOC ADSST SCH2 SCH1 SCH0

ADCF F6h ADC Configuration CH7 CH6 CH5 CH4 CH3 CH2 CH1 CH0

ADCLK F2h ADC Clock – – – PRS4 PRS3 PRS2 PRS1 PRS0

ADDH F5h ADC Data High byte ADAT9 ADAT8 ADAT7 ADAT6 ADAT5 ADAT4 ADAT3 ADAT2

ADDLF4hADCDataLowbyte––––––ADAT1ADAT0

Table 10. Other SFRs

MnemonicAddName 76543210

PCON 87h PowerControl SMOD1 SMOD0 – POF GF1 GF0 PD IDL

AUXR1 A2h Auxiliary Register 1 – – ENBOOT – GF3 0 – DPS

CKCON 8Fh Clock Control – WDX2 PCAX2 SIX2 T2X2 T1X 2 T0X2 X2

FCON D1h Flash Control FPL3 FPL2 FPL1 FPL0 FPS FMOD1 FMOD0 FBUSY

EECON D2h EEPROM Contol EEPL3 EEPL2 EEPL1 EEPL0 – – EEE EEBUSY

4128A–8051–04/02

11

Page 12

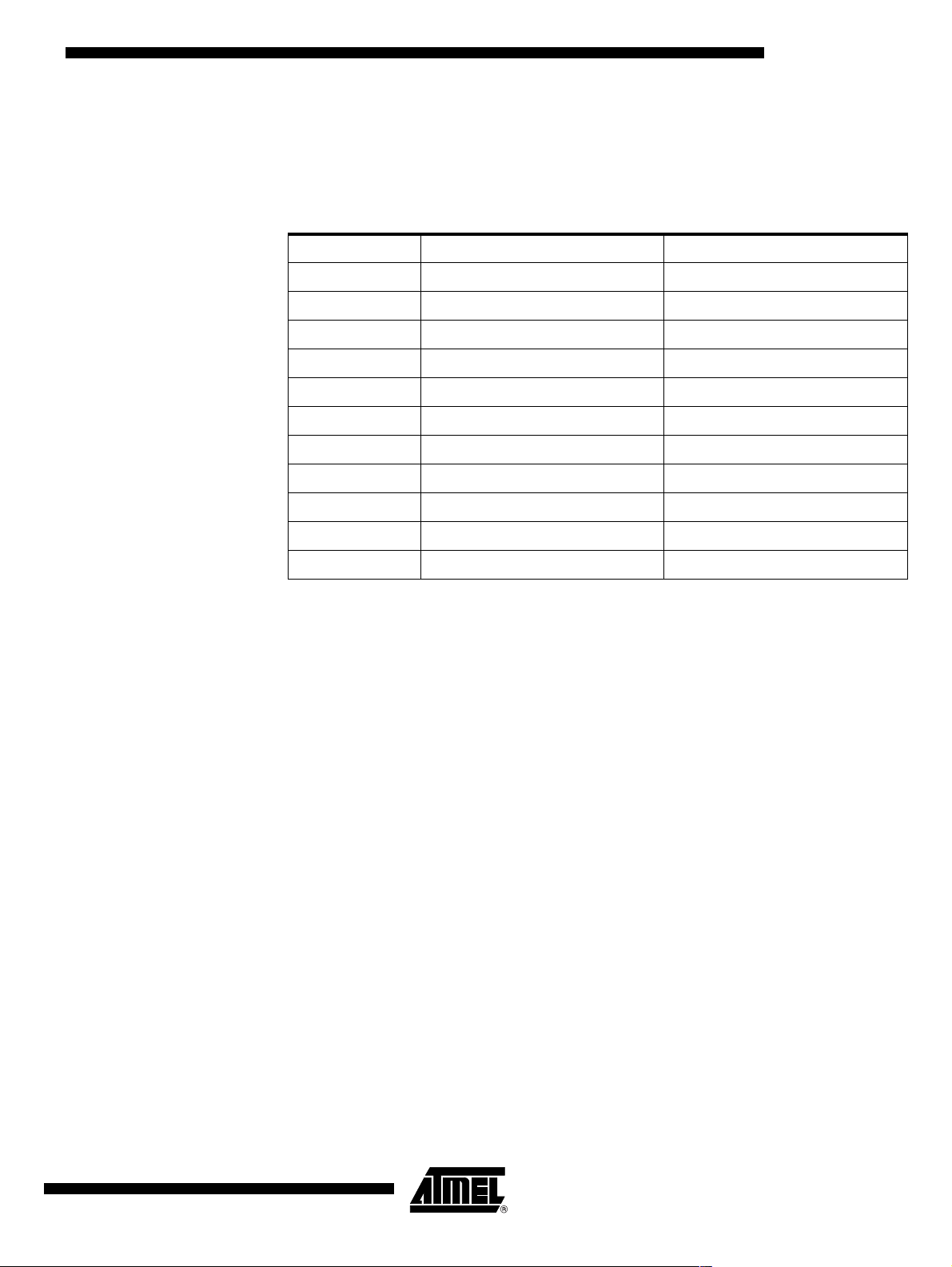

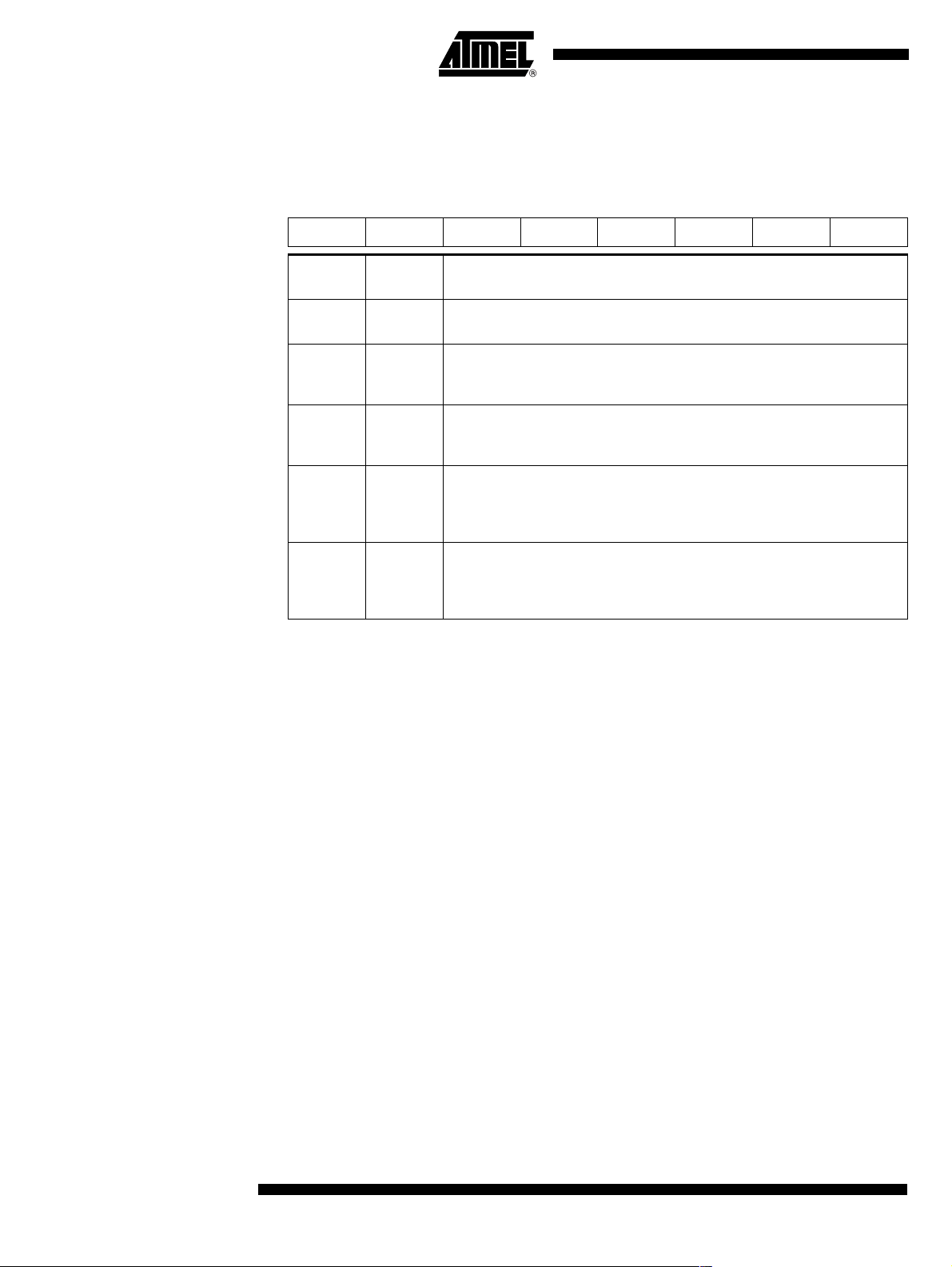

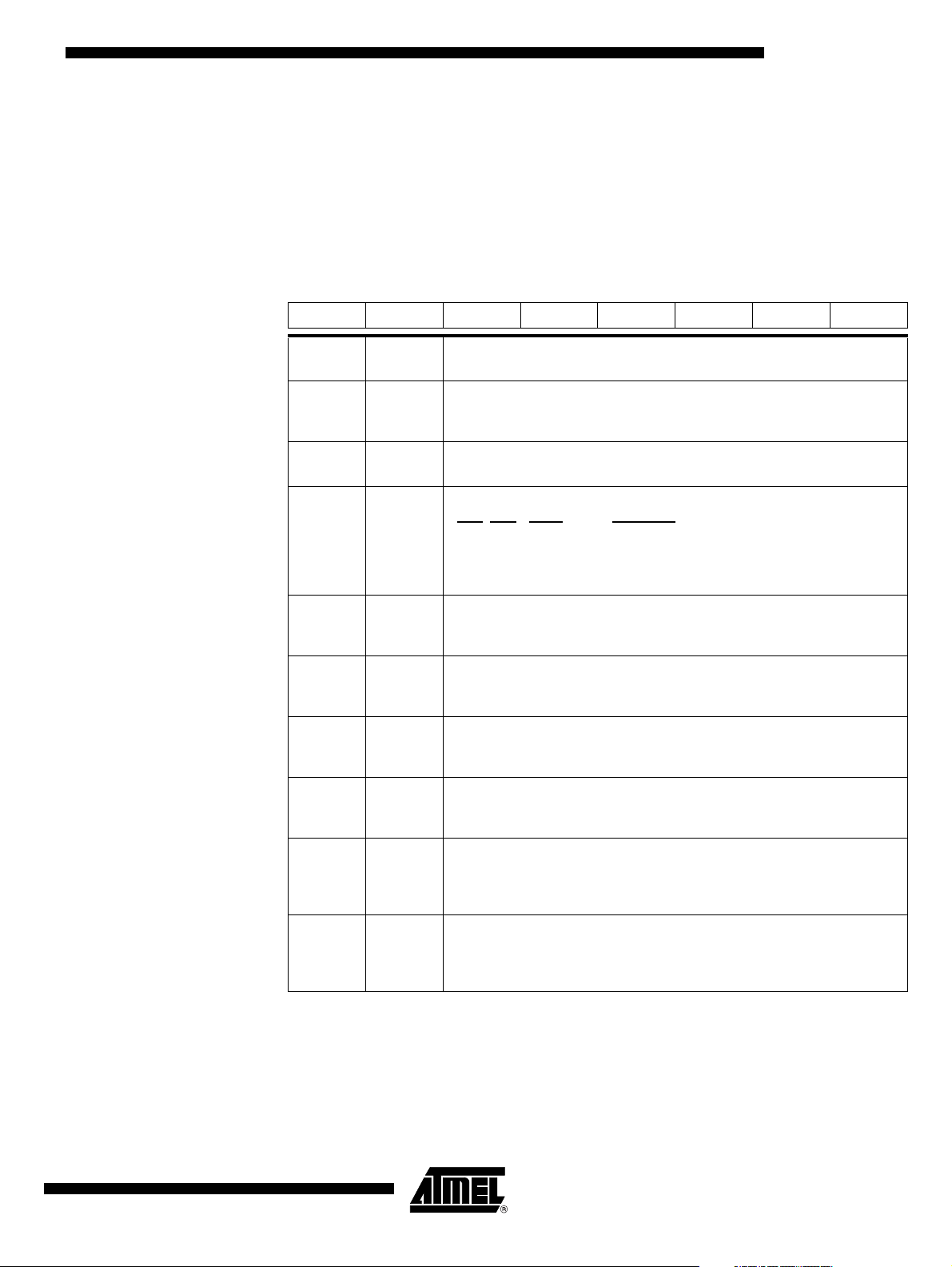

Table 11. SFR Mapping

(1)

0/8

1/9 2/A 3/B 4/C 5/D 6/E 7/F

F8h

F0h

E8h

E0h

D8h

D0h

C8h

C0h

B8h

B0h

A8h

IPL1

xxxx x000

B

0000 0000

IEN1

xxxx x000

ACC

0000 0000

CCON

0000 0000

PSW

0000 0000

T2CON

0000 0000

P4

xxxx xx11

IPL0

x000 0000

P3

1111 1111

IEN0

0000 0000

CH

0000 0000

CL

0000 0000

CMOD

00xx x000

FCON

0000 0000

T2MOD

xxxx xx00

SADEN

0000 0000

SADDR

0000 0000

CCAP0H

0000 0000

ADCLK

xxx0 0000

CCAP0L

0000 0000

CCAPM0

x000 0000

EECON

xxxx xx00

RCAP2L

0000 0000

CCAP1H

0000 0000

ADCON

x000 0000

CCAP1L

0000 0000

CCAPM1

x000 0000

RCAP2H

0000 0000

ADDL

0000 0000

TL2

0000 0000

ADDH

0000 0000

TH2

0000 0000

ADCF

0000 0000

IPH1

xxxx x000

IPH0

x000 0000

FFh

F7h

EFh

E7h

DF

h

D7h

CF

h

C7h

BFh

B7h

AFh

A0h

98h

90h

88h

80h

P2

1111 1111

SCON

0000 0000

P1

1111 1111

TCON

0000 0000

P0

1111 1111

(1)

0/8

SBUF

0000 0000

TMOD

0000 0000

SP

0000 0111

1/9 2/A 3/B 4/C 5/D 6/E 7/F

AUXR1

xxxx 00x0

TL0

0000 0000

DPL

0000 0000

Reserved

Note: 1. These registers are bit-addressable.

Sixteen addresses in the SFR space are both byte-addressable and bit-addressable. The bit-addressable SFR’s are those

whose address ends in 0 and 8. The bit addresses, in this area, are 0x80 through to 0xFF.

TL1

0000 0000

DPH

0000 0000

TH0

0000 0000

TH1

0000 0000

WDTRST

1111 1111

WDTPRG

xxxx x000

CKCON

0000 0000

PCON

00x1 0000

A7h

9Fh

97h

8Fh

87h

12

T89C5115

4128A–8051–04/02

Page 13

T89C5115

Clock The T89C5115 core needs only 6 clock periods per machine cycle. This feature, called

‘X2’, provides the following advantages:

• Divides frequency crystals by 2 (cheaper crystals) while keeping the same CPU

power.

• Saves power consumption while keepi ng the same CPU power (os cillator power

saving).

• Saves power consumption by dividing dynam ic operat ing frequenc y by 2 in

operating and idle modes.

• Increases CPU power by 2 while keeping the same crystal frequency.

In order to keep the original C51 compatibility, a divider-by-2 is inserted between the

XTAL1 signal and the main cloc k input of the core (phase generator). This divider may

be disabled by the software.

An extra feature is available to start after Reset in the X2 mode. This feature can be

enabled by a bit X2B in the Hardware Security Byte. This bit is desc ribed in the section

"In-System Programming".

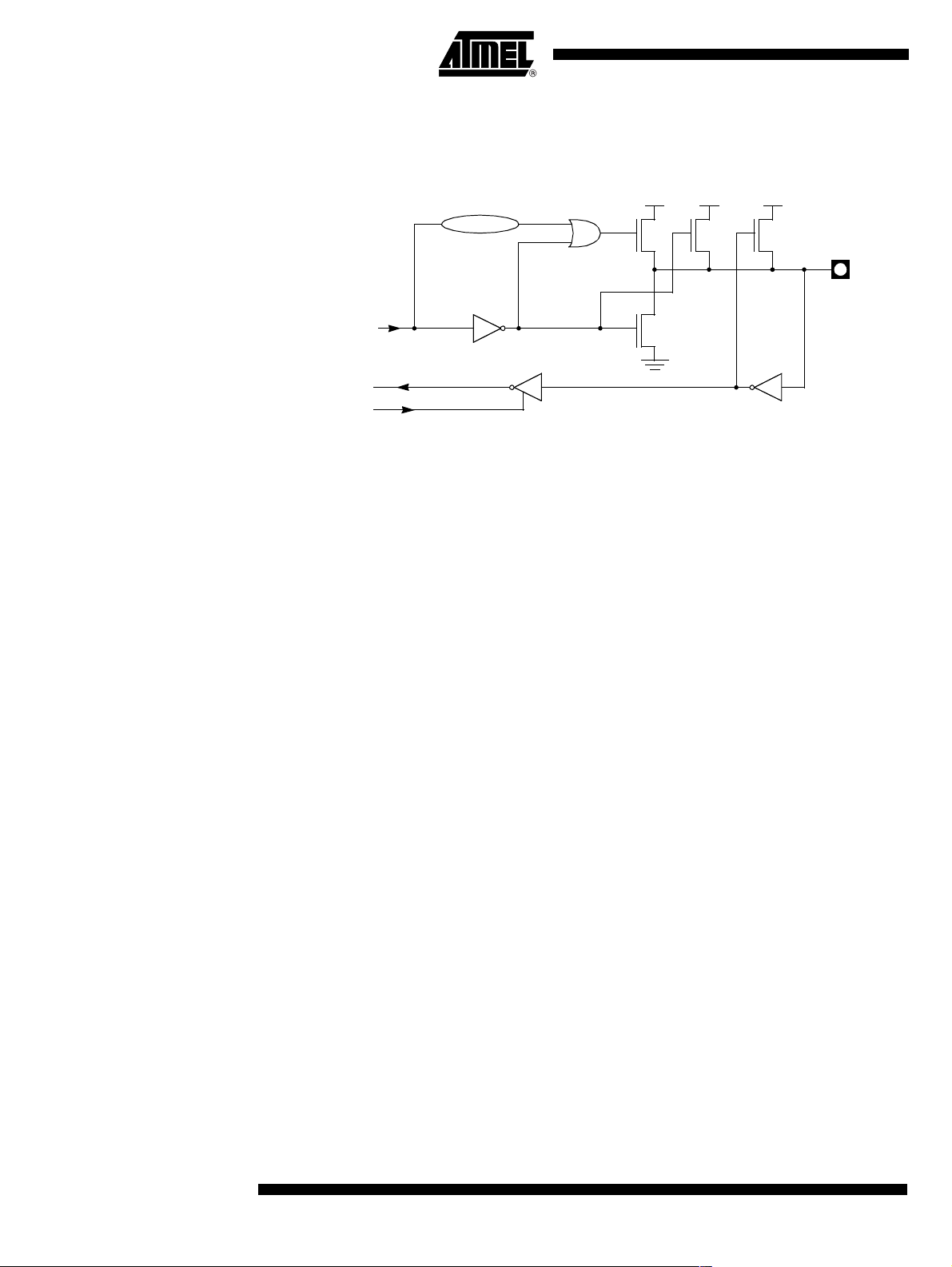

Description The X2 bit in the CKCON register (see Table 12) allows switching from 12 clock cycles

per i ns truct ion to 6 clock cycles and vice vers a. At reset, the stan dard speed is activated

(STD mode).

Setting this bit activates the X2 feature (X2 mode) for the C PU Clock only (see Figure

3.).

The Timers 0, 1 and 2, Uart, PCA or WatchDog switch in X2 mode only if the corresponding bit is cleared in the CKCON register.

The clock for the whole circuit and peripheral is f irst divided by two bef ore being used by

the CPU core and peripherals. This allows any cyclic ratio to be accepted on the XTAL1

input. In X2 mode, as this divider is bypassed, the signals on XTAL1 must have a cyclic

ratio b et ween 40 to 60%. Fi gure 3. shows the cloc k generation block diagram. The X2

bit is validated on the XTAL1÷2 rising edge to avoid glitches when switching from the X2

to the S TD m ode. Figure 4 shows the mode switching waveforms.

4128A–8051–04/02

13

Page 14

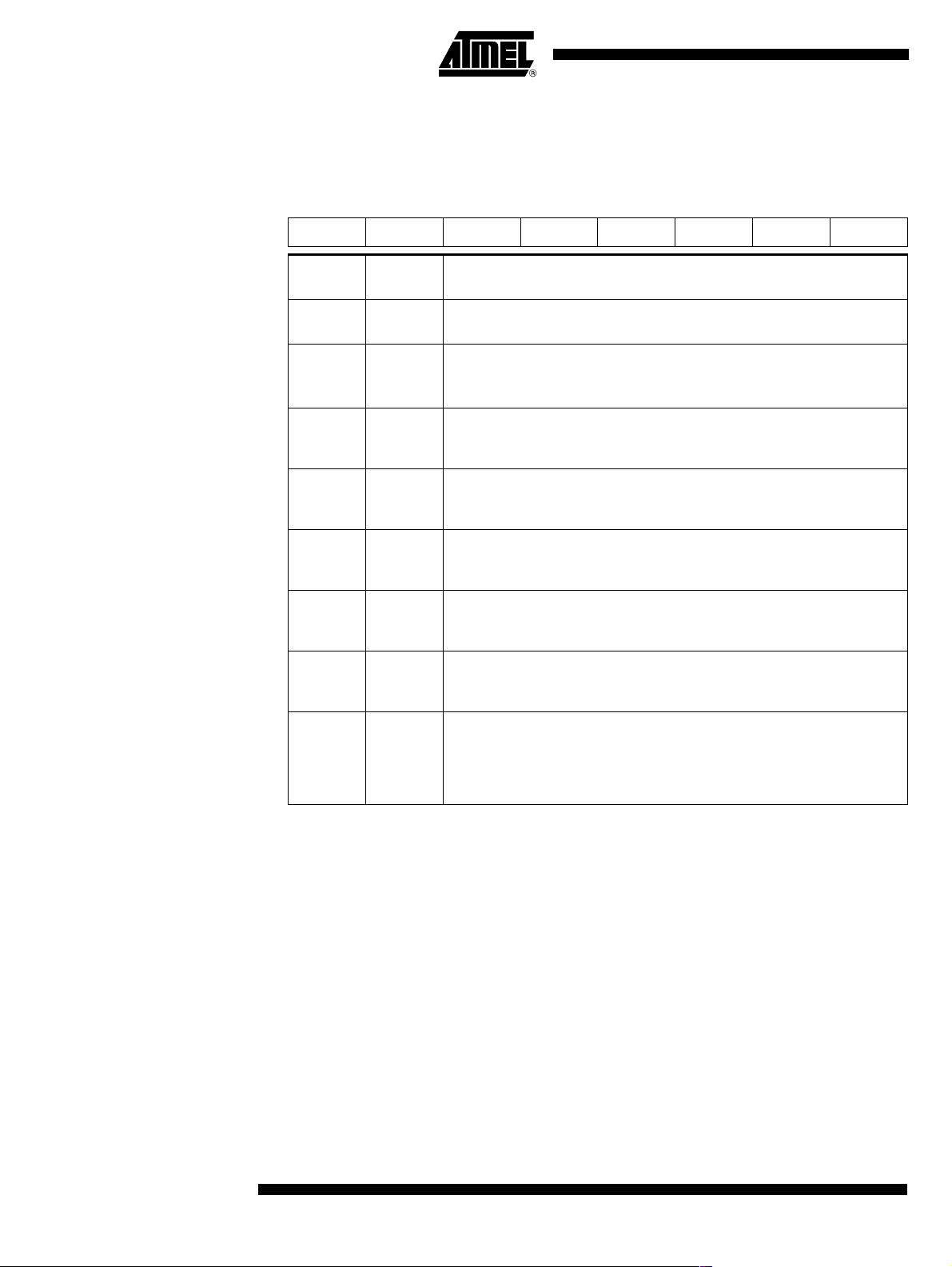

Figure 3. Clock CPU Generation Diagram

XTAL1

XTAL2

PD

PCON.1

÷ 2

X2B

Hardware byte

X2

CKCON.0

÷ 2

1

0

On RESET

÷ 2

÷ 2

1

0

0

1

÷ 2

1

0

PCON.0

IDL

÷ 2

1

0

÷ 2

1

0

CPU Core

Clock

CLOCK

CPU Core Clock Symbol

and ADC

1

0

FT0 Clock

FT1 Clock

FT2 Clock

FUart Clock

FPca Clock

FWd Clock

CPU

14

X2

CKCON.0

T89C5115

WDX2

CKCON.6

PCAX2

CKCON.5

SIX2

CKCON.4

T2X2

CKCON.3

T1X2

CKCON.2

PERIPH

CLOCK

Peripheral Clock Symbol

T0X2

CKCON.1

4128A–8051–04/02

Page 15

T89C5115

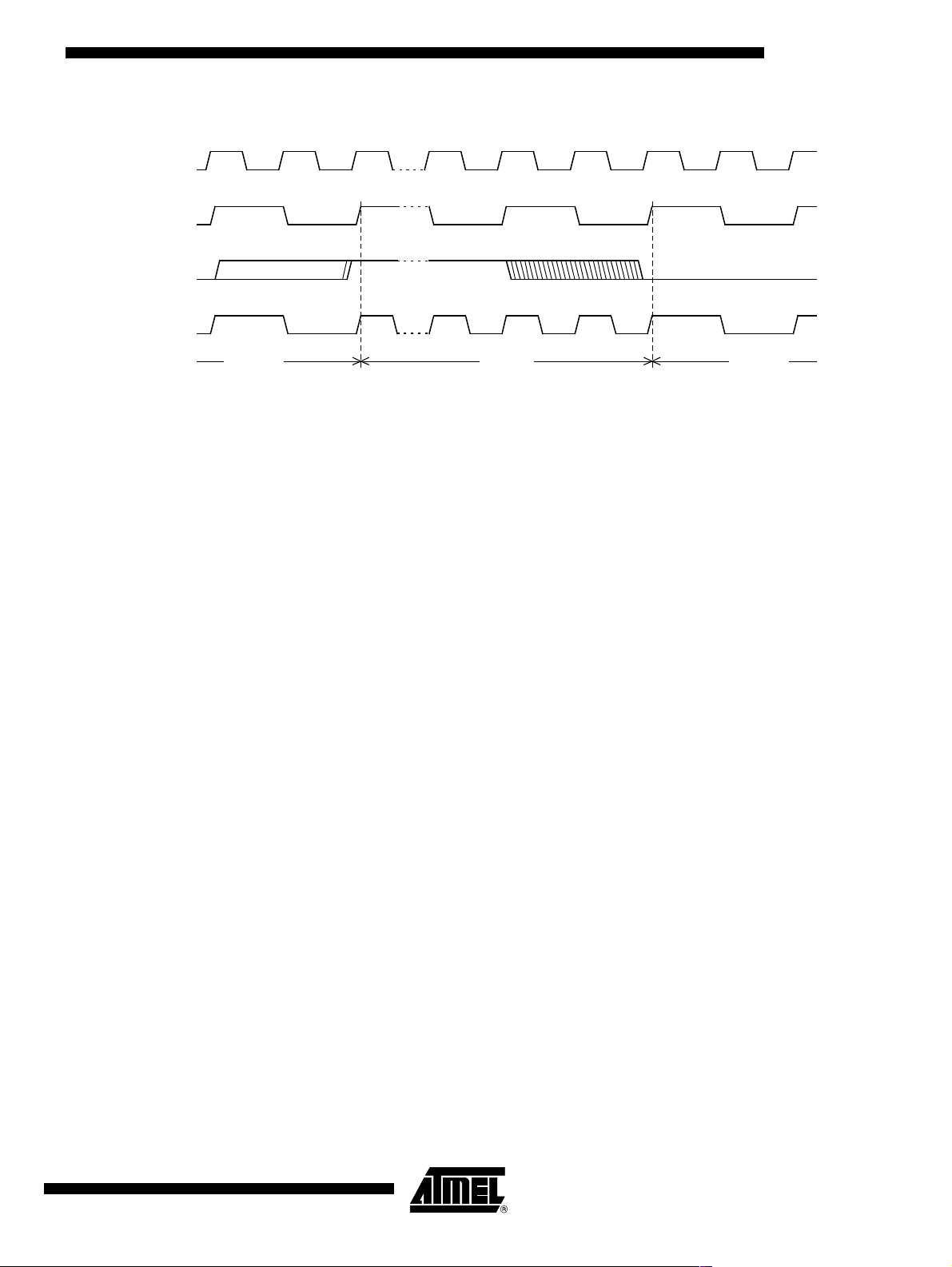

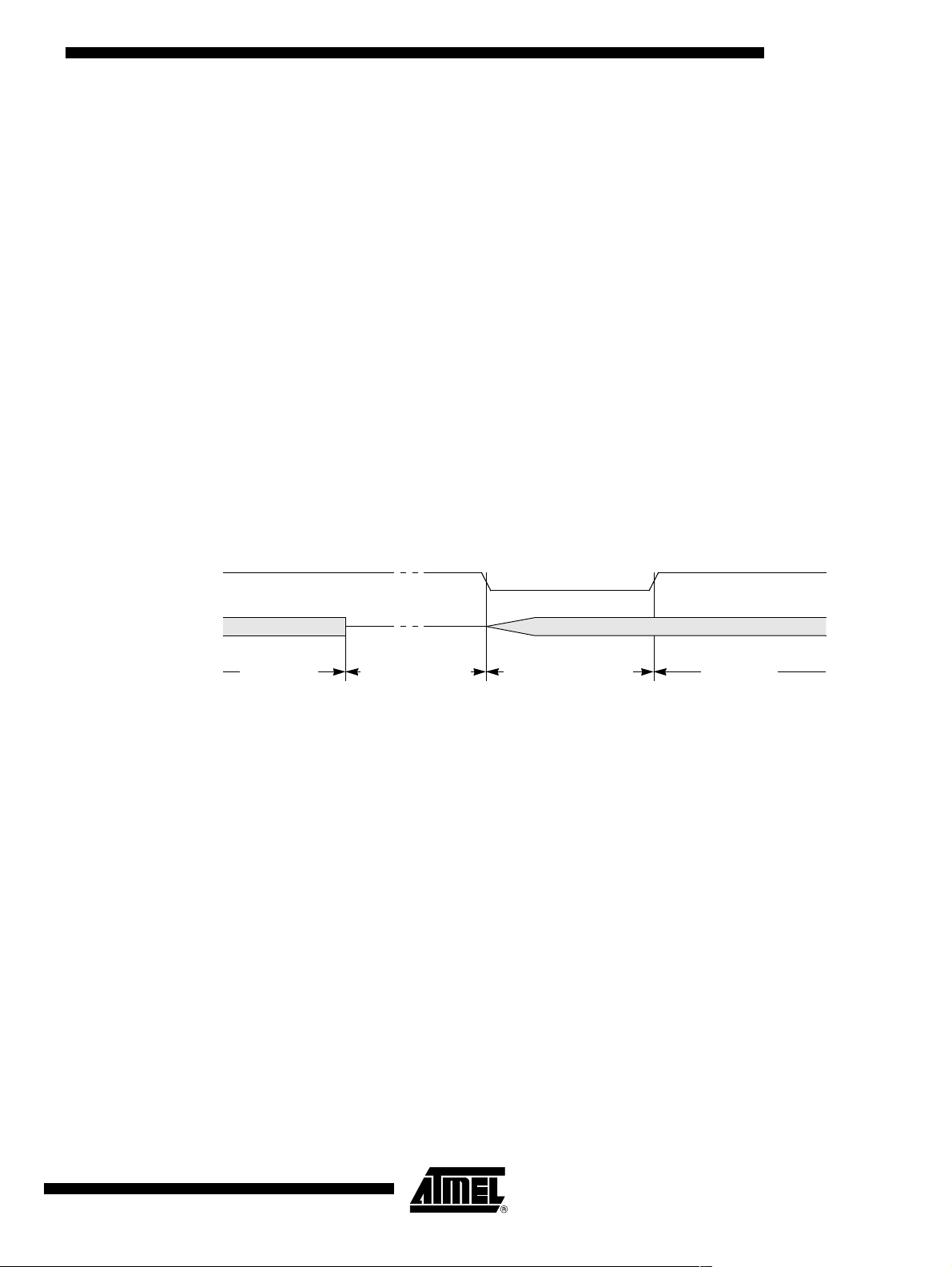

Figure 4. Mode Switching Waveforms

XTAL1

XTAL2

X2 bit

CPU

clock

STD

Mode

Note: In order to prevent any incorrect operation while operating in the X2 mode, users must be aware that all peripherals using the

clock frequency as a time reference (UART, timers...) will have their time reference divided by two. For example a free running

timer generating an interrupt every 20 ms will then generate an i nterrupt every 10 ms. A UART with a 4800 baud rate will have

a 9600 baud rate.

X2

Mode

STD

Mode

4128A–8051–04/02

15

Page 16

Register Table 12. CKCON Register

CKCON (S:8Fh)

Clock Control Register

76543210

– WDX2 PCAX2 SIX2 T2X2 T1X2 T0X2 X2

Bit

Number

7-

6WDX2

5 PCAX2

4SIX2

3T2X2

2T1X2

1T0X2

0X2

Bit

Mnemonic Description

Reserved

The value readfrom this bit is indeterminate. Do not set this bit.

WatchDog clock

Clear to select6 clock periods per peripheral clock cycle.

Set to select 12 clock periods per peripheral clock cycle.

Programmable Counter Array clock

Clear to select6 clock periods per peripheral clock cycle.

Set to select 12 clock periods per peripheral clock cycle.

Enhanced UART clock (MODE 0 an d 2 )

Clear to select6 clock periods per peripheral clock cycle.

Set to select 12 clock periods per peripheral clock cycle.

Timer2 clock

Clear to select6 clock periods per peripheral clock cycle.

Set to select 12 clock periods per peripheral clock cycle.

Timer1 clock

Clear to select6 clock periods per peripheral clock cycle.

Set to select 12 clock periods per peripheral clock cycle.

Timer0 clock

Clear to select6 clock periods per peripheral clock cycle.

Set to select 12 clock periods per peripheral clock cycle.

CPU clock

Clear to select 12 clock periods per machine cycle (STD mode) for CPU and all

the peripherals.

Set to select 6 clock periods per machine cycle(X2 mode) and to enable the

individual peripherals "X2"bits.

(1)

(1)

(1)

(1)

(1)

(1)

16

Notes: 1. This control bit is validated when the CPU clock bit X2 is set; when X2 is l ow, this bit

has no effect.

Reset Value = x000 0000b

T89C5115

4128A–8051–04/02

Page 17

T89C5115

Power Management

Introduction Two po w er reduction modes are implemented in the T89C5115: the Idle mode an d the

Power-down mode. T hese modes are detailed in the following sections. In addition to

these power reduction modes, t he clocks of the core and peripherals can be dynamically

divided by 2 using the X2 mode detailed in Section “Clock”.

Reset A reset i s required after app lying power at turn-on. T o achieve a valid reset, the reset

signal mus t be maintained for a t least 2 m achine cycles (24 o scillat or clock periods)

while the oscillator is running and stabilized and VCC established within the specified

operating ranges. A device reset initializes the T89C5115 and vectors the CPU to

address 0000h. RST input has a pull-down resistor allowing power-on reset by simply

connecting an external capacitor to V

characteristics are discussed in the Section “DC Characteristics” of the T89C5115

datasheet. The status of the Port pins during res et is detailed in Table 13.

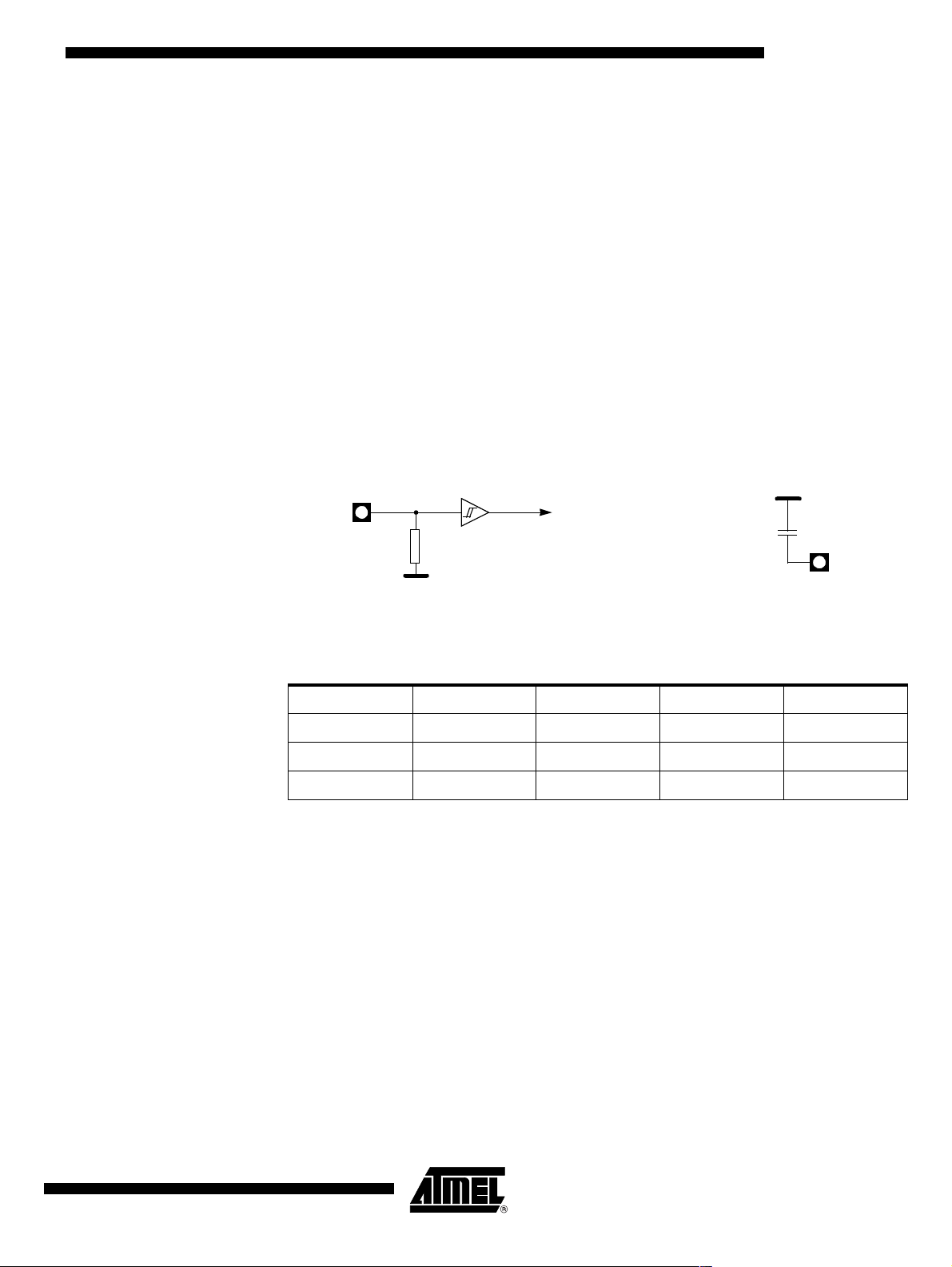

Figure 5. Reset Circuitry and Power-On Reset

as shown in Figure 5. Resistor value and input

DD

Reset Recommendation to Prevent Flash Corruption

VDD

+

RST

b. Power-on Reseta. RST i nput circuitry

RST

VSS

To CPU core

and peripherals

RST

R

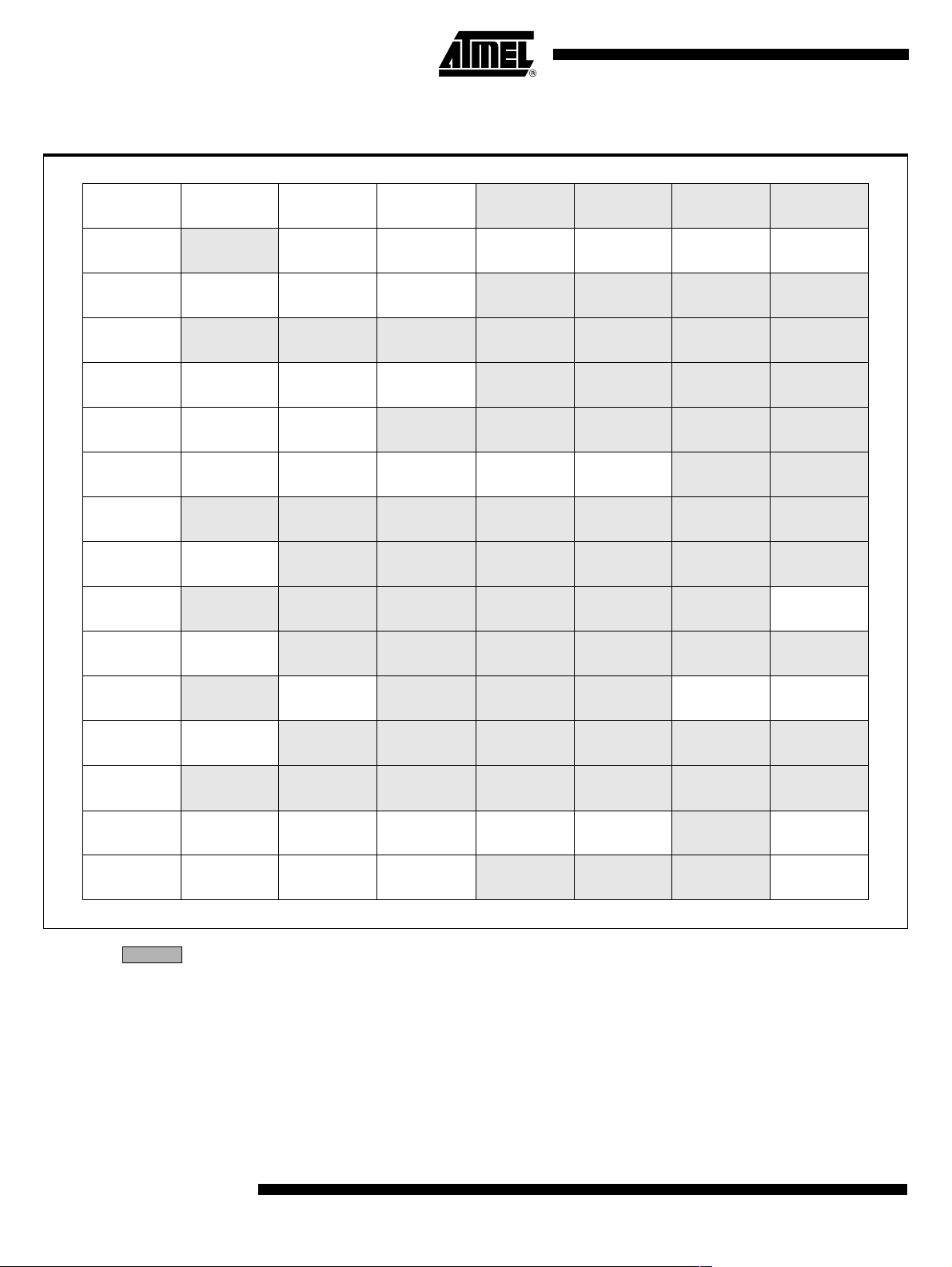

Table 13. Pi n Co nditions in Sp ec ial Operating Modes

Mode Port 1 Port 2 Port 3 Port 4

Reset High High High High

Idle Data Data Data Data

Power-downDataDataDataData

A bad reset sequence will lead to bad micr oco ntrol ler initialization and system registers

like SFR’s, Pr ogram Counter, etc. will not be correctly initialized. A bad initialization may

lead to unpredictable behaviour of the C51 microcontroller.

An example of this s ituat ion m ay occur in an instance where the bit ENBOOT in AUXR1

register is initialized fr om the hardware bit BLJB upon reset. Since this bit allow s mapping of the bootloader in the code area, a r es et fail ure can be critical.

4128A–8051–04/02

If one wants the ENBOOT cleared inorder to unmap the boot from the code area (yet

due to a bad reset) the bit ENBOOT in SFR’s may be set. If the value of Program

Counter is accidently in the range of the boot memory addresses then a flash access

(write or erase) m ay corrupt the Flash on-chip memory .

It is recommended to use an external reset circuitry featuring power sup ply monitoring to

prevent system malfunction during periods of insufficient power supply voltage(power

supply failure, power supply switched off).

17

Page 18

Idle Mode Idle mode is a power reduction mode that reduces the power consumption. In this mode,

program execution halts. Idle mode freezes the clock to the CPU at known states while

the peripherals continue to be clocked. The CPU status before entering Idle mode is

preserved, i.e., the program counter and program status word regis t er retain their data

for the duration of Idle mode. The contents of the

status of the Port pins during I dle mo de is detailed in Table 13.

Entering Idle Mode To enter Idle mode, s et the IDL bit in PCON register (see Table 14). The T89C5115

enters Idle mode upon execution of the instruction that sets IDL bit. The in struction that

sets IDL bit is the l as t instruction executed.

Note: If IDL bit and PD bit are set simultaneously, the T89C5115 enters Power-down mode.

Then it does not go in Idle mode when exitingPower-down mode.

Exiting Idle Mode There are two ways to exit Idle mode:

1. Generate an enabled interrupt.

– Hardware clears IDL bit in PCON register which restores the clock to the

CPU. Execution resumes with the interrupt service routine. Upo n completion

of t he interrupt service routine, program execution resum es with the

instruction immediately following the instruction that activated Idle mode.

The gene ral-purpose flags (GF1 and GF0 in PCON register) may be used to

indicate whether an interrupt occurred during normal operation or during Idle

mode. When Idle mode is exited by an interrupt, the interrupt service routine

may examine GF1 and GF0.

2. Generate a reset.

– A logic high on the RST pin clears IDL bit in P CON r egister directly and

asynchronously. This restores the clock to the CPU. Program execution

momentarily resumes with the instruction im mediately following the

instruction that ac tivated the Idle m ode and may continue for a number of

clock cycles before the internal reset algorithm takes control. Reset

initializes the T89C5115 and vectors t he CPU t o addres s C:0000h.

SFRs and RA M are also retained. The

Note: During the time that execution resumes, the internal RAM cannot be accessed; however,

it is possible for the Port pins to be accessed. To avoid unexpected outputs at the Port

pins, the instruction immediately following the instruction that activatedIdle m ode should

notwritetoaPortpinortotheexternalRAM.

Power-down Mode The Power-down mode places the T89C5115 in a very low power state. Power-down

mode stops the os cillator, freezes all clock at known states. The CPU status pr ior t o

entering Power-down mode is preserv ed, i.e., the program counter, program status

word register retain their data for the duration of Power-down mode. In addition, the

SFRs and RAM contents are preserved. The status of the Port pins during Power-down

mode is detailed in Table 13.

Note: VDDmaybereducedtoaslowasV

power dissipation. Take care, however, that VDD is not reduced until Power-down mode

is invoked.

Entering Power-down Mo de To enter Power-down mode, set PD bit in PCON register. The T89C5115 enters the

Power-down mode upon execution of the instruction that sets PD bit. The instruction

that sets PD bit is the last instruction executed.

18

T89C5115

during Power-down mode to further reduce

RET

4128A–8051–04/02

Page 19

T89C5115

Exiting Power-down Mode Note: If VDD was reduced during the Power-down mode, do not exit Power-down mode until

VDD is r estored to the normal operating level.

There are t w o way s to exit the Power-down mode:

1. Generate an enabled external interrupt.

– The T89C5115 provides capability to exit from Power-down using INT0#,

INT1#.

Hardware clears PD bit in PCON register which starts the os c il lator and

restores the clocks to the CPU and peripherals. Usin g

resumes when the input is released (s ee Fi gure 6). Execution resumes with

the interrupt service routine. Upon completion of the interrupt service

routine, program execution resumes with the instruction immedia tely

following the instruction that activated Power-do w n mode.

Notes: 1. The external interrupt used to exit Power-down mode m ust be configured as level

sensitive (INT0# and INT1#) and m ust be assigned the highest priority. In addition,

the duration of the interrupt must be long enough to allow the oscillator to stabilize.

The execution will only resume when the interrupt is deasserted.

2. Exit from power-down by external interrupt does not affect t he

RAM content.

INTx# input, execution

SFRs nor the internal

Figure 6. Power-down Exit Waveform Using INT1:0#

INT1:0#

OSC

Power-down phase Oscillatorrestartphase Active phaseActive phase

2. Generate a reset.

– A logic hi gh on the RST pin clears PD bit in PCON register directly and

asynchronously. This starts the oscillator and restores the clock to the CPU

and peripherals. Program execution momentarily resumes with the

instruction im mediately following the instruction that ac t ivate d Powe r-do wn

mode and may continue for a number of clock cycles before the internal

reset algorithm takes control. Reset initializes the T89C5115and vectors the

CPU to address 0000h.

Notes: 1. During t he time that execution resumes, the internal RAM cannot be accessed; how-

ever, it is possible for the Port pins to be accessed. To avoid unexpected outputs at

the Port pins, the instruction immediately following the instruction that activated the

Power-down mode should not write to a Port pin or t o the external RAM.

2. Exit from power-down by reset redefines all the

RAM content.

SFRs, but does not affect t he internal

4128A–8051–04/02

19

Page 20

Registers PCON (S:87h)

Table 14. PCON Register

Power Configuration Register

76543210

––––GF1GF0PDIDL

Bit

Number

7-4

3GF1

2GF0

1PD

0IDL

Bit

Mnemonic Description

Reserved

–

The value readfrom these bits is indeterminate.Do not set these bits.

General-purpose flag 1

One use is t o indicate whetheran interrupt occurred duringnormal operation or

during Idle mode.

General-purpose flag 0

One use is t o indicate whetheran interrupt occurred duringnormal operation or

during Idle mode.

Power-down Mode bit

Cleared by hardware when an interrupt or reset occurs.

Set to activate the Power-down mode.

If IDL and PD are both set, PD takes precedence.

Idle Mode bit

Cleared by hardware when an interrupt or reset occurs.

Set to activate the Idle mode.

If IDL and PD are both set, PD takes precedence.

Reset Value = XXXX 0000b

20

T89C5115

4128A–8051–04/02

Page 21

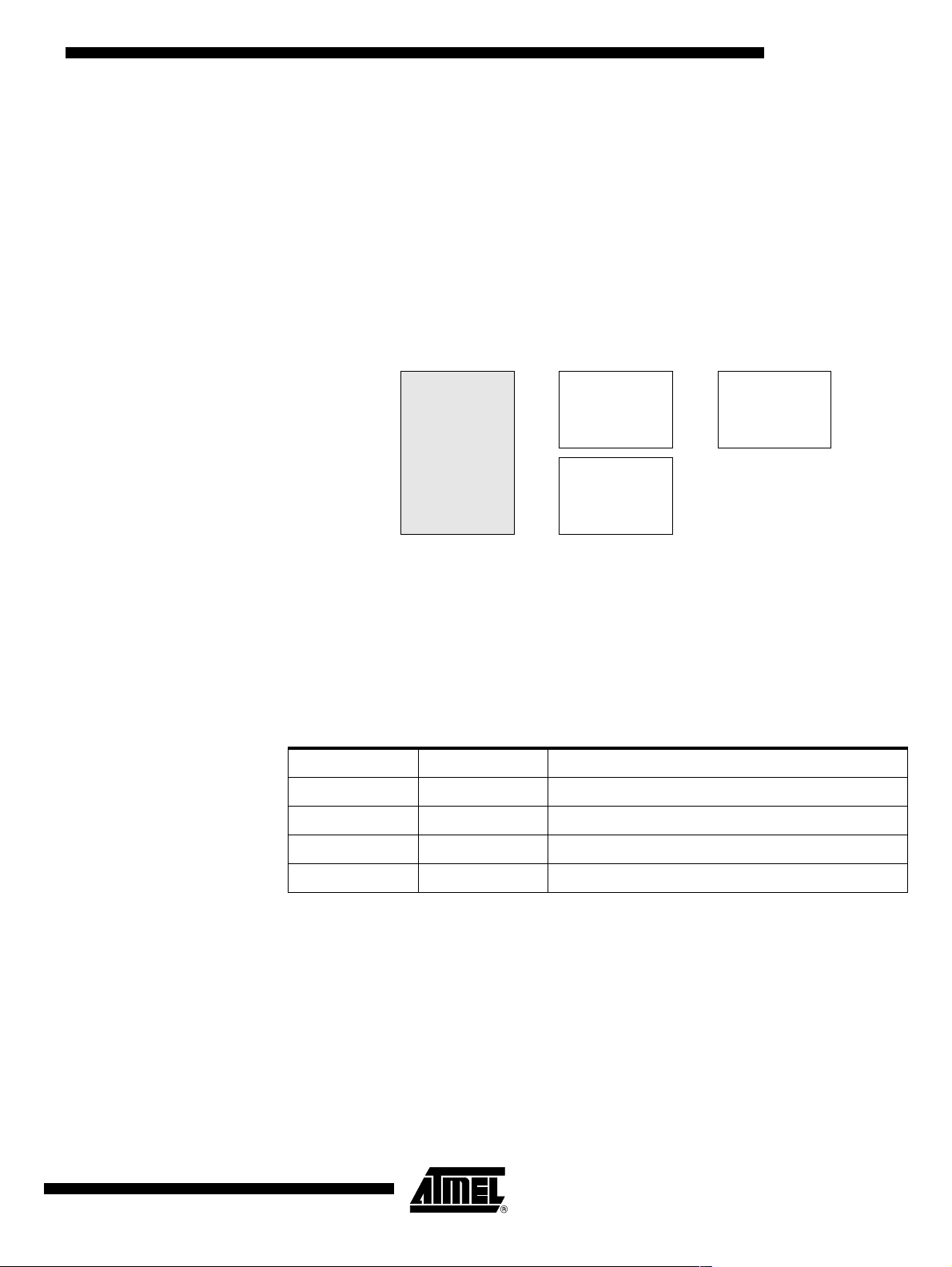

Data Memory The T89C5115 provides data memory access in two different spaces:

The internal space mapped in three separate segments:

• the lower 128 bytes RAM segment.

• the upper 128 bytes RAM segmen t.

• the expanded 256 bytes RAM segment (ERAM) .

A f ourth internal seg ment is availabl e but dedicated to Speci al Function Regi sters,

SFRs, (addresses 80h to FFh) ac c es sible by direct addressing mode.

Figure 7 shows the internal data memory spaces organization.

Figure 7. Internal Memory – RAM

T89C5115

FFh

00h

256 bytes

Internal ERAM

FFh

80h 80h

7Fh

00h

Upper

128 bytes

Internal RAM

indirect addressing

Lower

128 bytes

Internal RAM

director indirect

addressing

FFh

directaddressing

Special

Function

Registers

Internal Space

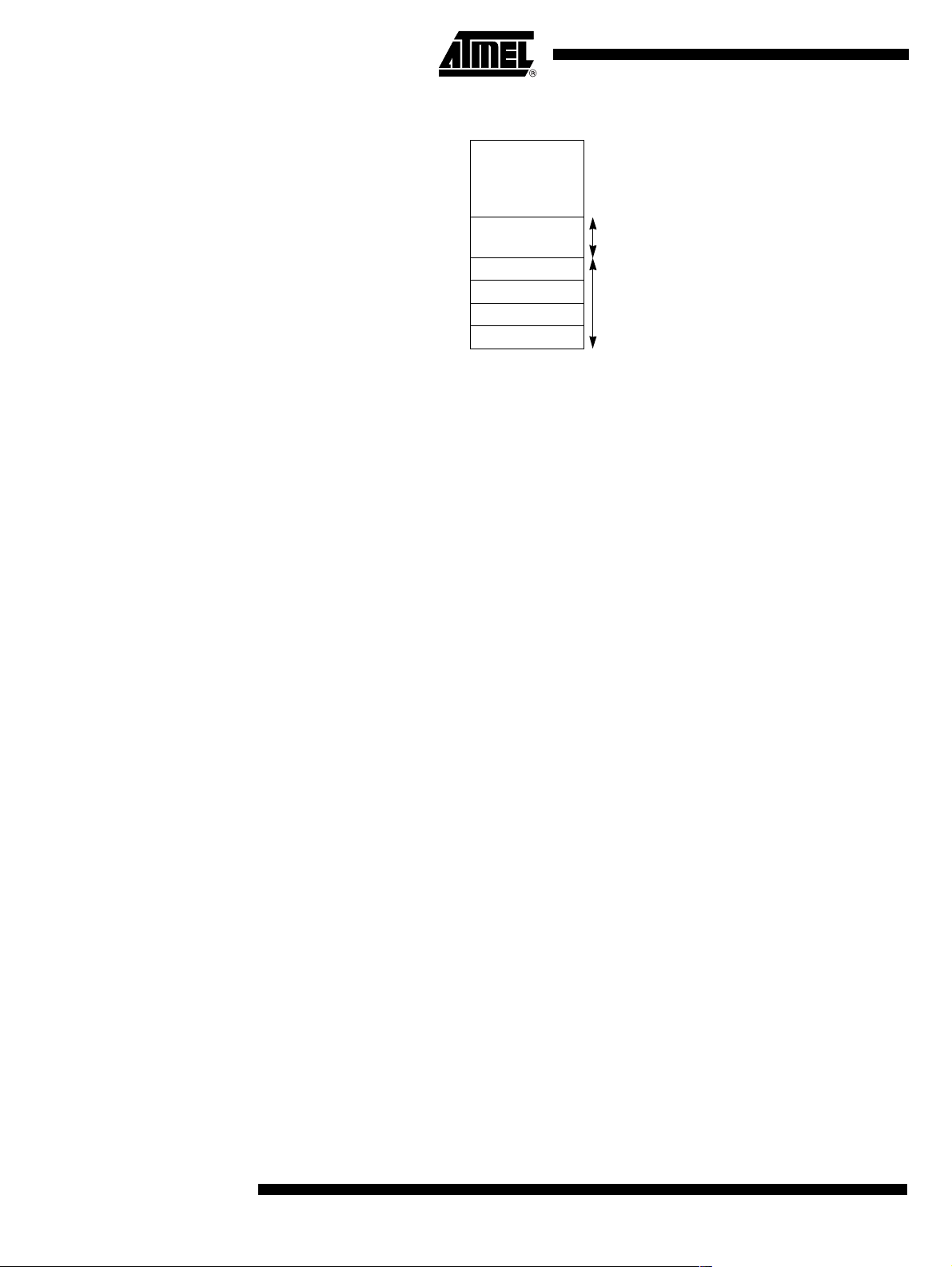

Lower 128 Bytes RAM The lower 128 bytes of RAM (see Figure 7) are accessible from address 00h to 7Fh

using direct or indirect addressing modes . The lowest 32 bytes are grouped into 4 banks

of 8 registers (R0 to R7). Two bits RS0 and RS1 in PSW register (see Figure 16) select

which bank is in use according to T able . This allows more ef fic ient use of code space,

since register instructions are shorter t han inst r uc tions that use direct addressing, and

can be used for c ont ex t switching in interrupt service routines.

Table 15. Register B ank Selection

RS1 RS0 De scription

0 0 Register bank 0 from 00h to 07h

0 1 Register bank 0 from 08h to 0Fh

4128A–8051–04/02

1 0 Register bank 0 from 10h to 17h

1 1 Register bank 0 from 18h to 1Fh

The next 16 bytes above the register banks form a block of bit-addressable memory

space. The C51 instruction set includes a wide s election of single-bit instructions , and

the 128 bits in this area can be directly addressed by these instructions. The bit

addresses in this area are 00h to 7Fh.

21

Page 22

Figure 8. Lower 128 bytes Internal RAM Organization

7Fh

30h

20h

18h

10h

08h

00h

2Fh

Bit-Addressable Space

(Bit Addresses 0-7Fh)

1Fh

17h

4Banksof

8Registers

0Fh

R0-R7

07h

Upper 128 Bytes RAM The upper 128 bytes of RAM are accessible from address 80h to FFh using only indirect

addressing mode.

Expanded RAM The on-chip 256 bytes of expanded RAM (E R AM) are accessible from address 0000h to

00FFh using indirect addressing mode thro ugh MOVX instructions. In this addres s

range.

Note: Lower 128 bytes RAM, Upper 128 bytes RAM, and expanded RAM are made of volatile

memory cells. This m eans that the RAM content is indeterminate after power-up and

must then be i nitialized properly.

22

T89C5115

4128A–8051–04/02

Page 23

T89C5115

Dual Data Pointer

Description The T89 C5115 implements a second data pointer for s peeding up code execution and

reducing code size in case of intensive usage of external memory accesses.

DPTR0 and DPTR1 are seen by the CPU as DPTR and are accessed using the SFR

addresses 83h and 84h that are t he DPH and DPL addresses. The DPS bit i n AUXR1

register (see Figure 17) is used to select whether DPTR is the data pointer 0 or the data

pointer 1 (see Figure 9).

Figure 9. Dual Data Pointer Implementation

DPL0

DPL1

DPTR0

DPTR1

DPH0

DPH1

0

1

DPS

0

1

DPL

AUXR1.0

DPH

DPTR

Application Software can take advant age of the additional data pointers to both increase speed and

reduce code size, for example, block operations (cop y , compare…) are well served by

using one data pointer as a “source” pointer and the other one as a “destination” pointer.

Hereafter is an example of block mov e implementation using t he two pointers and coded

in assem bler. The latest C compiler tak es also adv antage of this feature by providin g

enhanced algorithm libraries.

The INC instruction is a short (2 bytes) an d fast (6 machine cycle) way to manipulate t he

DPS bit in the AUXR1 register. However, note that the INC instruction does not directly

force the DPS bit to a particular state, but simply toggles it. In simple routines, such as

the block move example, only the fact that DPS is toggled in the proper sequence matters, not its actual value. In other words, the block move rout ine works the same whether

DPS is '0' or '1' on entry.

4128A–8051–04/02

; ASCII block move using dual data pointers

; Modifies DPTR0, DPTR1, A and PSW

; Ends when encountering NULL character

; Note: DPS exits opposite to the entry state unless an extra INC AUXR1 is

added

AUXR1EQU0A2h

move:movDPTR,#SOURCE ; address of SOURCE

incAUXR1 ; switch data pointers

movDPTR,#DEST ; address of DEST

mv_loop:incAUXR1; switch data pointers

movxA,@DPTR; get a byte from SOURCE

incDPTR; increment SOURCE address

incAUXR1; switch data pointers

movx@DPTR,A; write the byte to DEST

incDPTR; increment DEST address

jnzmv_loop; check for NULL terminator

end_move:

23

Page 24

Registers Table 16. PSW Register

PSW (S:8Eh)

Program Status Word Register

76543210

CY AC F0 RS1 RS0 OV F1 P

Bit

Number

7CY

6AC

5F0User De finable Flag 0

4-3 RS1:0

2OV

1F1User De finable Flag 1

0P

Bit

Mnemonic Description

Carry Flag

Carry out from bit 1 of ALU operands.

Auxiliary Carry Flag

Carry out from bit 1 of addition operands.

Register Bank Select Bits

Refer to Table for bits description.

Overflow Flag

Overflow set by arithmetic operations.

Parity Bit

Set when ACC contains an odd numberof 1’s.

Cleared when ACC contains an even number of 1’s.

Reset Value = 0000 0000b

24

T89C5115

4128A–8051–04/02

Page 25

T89C5115

Table 17. AUX R 1 R egister

AUXR1 (S:A2h)

Auxiliary Control Register 1

76543210

– – ENBOOT – GF3 0 – DPS

Bit

Number

7-6

5 ENBOOT

4

3GF3General-purpose Flag 3.

20

1 – Reserved for Data Pointer Extension.

0DPS

Bit

Mnemonic Description

Reserved

–

The value readfrom these bits is indeterminate.Do not set these bits.

Enable Boot Flash

Set this bit for map the boot flash between F800h -FFFFh

Clearthis bit for disable boot flash.

Reserved

–

The value readfrom this bit is indeterminate. Do not set this bit.

Always Zero

This bit is stuck to logic 0 to allow INC AUXR1 instruction without affecting GF3

flag.

Data Pointer Select Bit

Set to select second dual data pointer: DPTR1.

Clear to selectfirst dual data pointer:DPTR0.

Reset Value = xxxx 00x0b

4128A–8051–04/02

25

Page 26

EEPROM Data Memory

The 2-kbyte on-c hip EEPROM memory block is located at addres se s 0000h to 07FFh of

the XRAM /ERAM memory space and is selected by setting control bits i n the EECON

register. A read in the EE PRO M m emory is done with a MOVX ins truction.

A physical write in the EEPROM memory i s done in two steps: write data in the column

latches and transfer of all data latches into an EEPROM memory row (programming).

The number of data written on the page may vary from 1 up to 128 bytes (the page

size). When programming, only the data writt en in the column latch is programmed and

a ninth bit is used to obtain t his feature. This provides the capability to program the

whole memory by bytes, by pa ge or by a number of bytes in a page. Indeed, each ninth

bit is set when the writing the corresponding byte in a row and all these ninth bits are

reset after t he w riting of the complete EEPROM row.

Write Data in the Column Latches

Data i s written by byte to the column latches as for an external RAM memory. Out of the

11 address bits of the data pointer, the 4 MSBs are used for page selection (row) and 7

are used for byte selection. Between two EEPROM programming sessions, all the

addresses in the column latches must stay on the same page , meaning th at the 4 MSB

must no be changed.

The following procedure is used to write to the column latches:

• Save and disable interrupt.

• Set bit EEE of EECON register

• Load DPTR with the address to write

• Store A register with the data to be written

• Execute a MOVX @DPTR, A

• If needed loop the three last instructions until the end of a 128 byt es page

• Restore interrupt.

Note: The last page address used when loading the column latch is the one used to select the

page programming address.

Programming The EEPROM programming co ns ists of the following actions:

• writing one or more bytes of one page in the column latc hes . Norm ally, all bytes

must belong to the same page; if not, th e first page address will be latched and the

others disc arded.

• launching programming by writing the control seque nc e (50h followed by A0h) to the

EECON register.

• EEBUSY flag in EECON is then set by hardware to indicate that programming is in

progress and that t he EEPROM segment is not available for reading.

• The end of programming is indicated by a hardware clear of the E EBUSY flag.

Note: The sequence 5xh and Axh must be executed without instructions between them, other-

wise the programming is aborted.

Read Data The following procedure is used to read t he data stored in the EEPROM m emory:

• Save and disable interrupt

• Set bit EEE of EECON register

• Load DPTR with the address to read

• Execute a MOVX A, @DPTR

• Restore interrupt

26

T89C5115

4128A–8051–04/02

Page 27

T89C5115

Examples ;*F*************************************************************************

;* NAME: api_rd_eeprom_byte

;* DPTR contain address to read.

;* Acc contain the reading value

;* NOTE: before execute this function, be sure the EEPROM is not BUSY

;***************************************************************************

api_rd_eeprom_byte:

MOV EECON, #02h; map EEPROM in XRAM space

MOVX A, @DPTR

MOV EECON, #00h; unmap EEPROM

ret

;*F*************************************************************************

;* NAME: api_ld_eeprom_cl

;* DPTR contain address to load

;* Acc contain value to load

;* NOTE: in this example we load only 1 byte, but it is possible upto

;* 128 bytes.

;* before execute this function, be sure the EEPROM is not BUSY

;***************************************************************************

api_ld_eeprom_cl:

MOV EECON, #02h ; map EEPROM in XRAM space

MOVX @DPTR, A

MOVEECON, #00h; unmap EEPROM

ret

;*F*************************************************************************

;* NAME: api_wr_eeprom

;* NOTE: before execute this function, be sure the EEPROM is not BUSY

;***************************************************************************

api_wr_eeprom:

MOV EECON, #050h

MOV EECON, #0A0h

ret

4128A–8051–04/02

27

Page 28

Registers Table 18. EECON Register

EECON (S:0D2h)

EEPROM Control Register

76543210

EEPL3 EEPL2 EEPL1 EEPL0 - - EEE EEBUSY

Bit

Bit Number

Mnemonic Description

7-4 EEPL3-0

3-

2-

1 EEE

0 EEBUSY

Programming Launch Command bits

Write 5Xh followed by AXh to EEPL to launch the programming.

Reserved

The value read from this bit is indeterminate. Do not set this bit.

Reserved

The value read from this bit is indeterminate. Do not set this bit.

Enable EEPROM Space bit

SettomaptheEEPROMspaceduringMOVXinstructions(Writeinthecolumn

latches).

Clear to map the XRAM space during MOVX.

Programming Busy flag

Set by hardware when programming is in progress.

Cleared by hardware when programming is done.

Can not be set or cleared by software.

Reset Value = XXXX XX00b

Not bit addressable

28

T89C5115

4128A–8051–04/02

Page 29

T89C5115

Program/Code Memory

Flash Memory Architecture

The T89C5115 implement 16-KB of on-chip program/code memory .

The Flash memory increases EPROM and ROM functionality by in-circuit electrical era-

sure and programming. Thanks to t he internal charge pump, the high voltage needed for

programming or erasing Flash cells is generated on-chi p using the s tandard VDD voltage. Thus, the Flash Memory can be programmed using only one voltage and allows InSystem Programming c ommonly known as ISP. Hardware programming mode is also

available using specific programming tool.

Figure 10. Program/Code Memory Organization

3FFFh

16-KB

internal

Flash

0000h

T89C5115 features two on-chip flash memories:

• Flash memory FM0:

containing 1 6-KB of program me mory (use r space) organized into pages 128 bytes

• Flash memory FM1:

2K B y tes for boot loader and Application Programming Interfaces (API).

The FM0 can b e program by bot h parallel programming and S erial In-System Program ming (ISP) whereas FM1 supports only parallel programmi ng by p rogramm ers . The ISP

mode is detailed in the "In-System Programming" section.

All Read/Write access operations on Fl as h Memo ry by user application are managed by

a set of AP I described in t he "In-Sy s tem Programming" section.

Figure 11. Flash Memory Architecture

Hardware Security (1 byte)

Extra Row (128 bytes)

Column Latches (128 bytes)

3FFFh

0000h

16-KB

Flash memory

user space

FM0

2K Bytes

Flash memory

boot space

FM1

FM1 mapped between FFFFh and

F800h when bit ENBOOT is set in

AUXR1 register

FFFFh

F800h

4128A–8051–04/02

29

Page 30

FM0 Memory Architecture The Flash memory is made up of 4 blocks (see Figure 11):

1. The memory array (user space) 16-KB.

2. The Extra Row.

3. The Hardware security bits.

4. The column latch registers.

User S pac e This space is composed of a 16-KB Flash memory organized in 128 pages of 128 bytes.

It contains the user’s application c ode.

Extra Row (XROW) This row is a part of FM0 and has a size of 128 bytes. The extra row may contain infor-

mation for boot loader usage.

Hardware security Byte The Hardware Security Byte space is a part of FM0 an d has a size of 1 byte.

The 4 MSB can be read/written by softw are, the 4 LSB can only be read by software and

written by hardware in parallel m ode.

Column Latches The column latches, also part of FM0, have a size of f ull page (128 bytes).

The column latches are the entrance buffers of the three previous memory locations

(user array, XROW and Hardware security byte).

Cross Flash Memory Access

Description

The FM0 memory can be program only from FM1. Programm ing FM0 from FM0 or from

external memory is impossible.

The FM1 memory can be program only by parallel programming.

The Table 19 show all software flash access allowed.

Table 19. Cross Flash Memory Access

Codeexecutingfrom

FM0

(user Flash)

FM1

(boot flash)

Action

Read ok -

Load column latch ok -

Write - Read ok ok

Load column latch ok -

Write ok -

FM0

(user Flash)

FM1

(boot Flash)

30

T89C5115

4128A–8051–04/02

Page 31

T89C5115

Overview of FM0 Operations

The CPU interfaces to the Flash memory through the FCON register and AUXR1

register.

These registers are used to:

• Map the memory spaces in the adressable space

• Launch the programming of the memo ry spaces

• Get the status of the flash memory (busy/not busy)

Mapping of the Memory Space By default, the user space is accessed by MO VC instruction for read only. The colum n

latches space is m ade accessible by setting the FPS bit in FCON register. W riting is

possible from 0000h to 3FFFh, address bits 6 to 0 are used to s elect an address w ithin a

page while bits 14 t o 7 are used to select the programming address of the page.

Setting FPS bit takes precedence on the EEE bit in EECON register.

The oth er memory spaces (user, extra row, hardware security) are made acces s ible in

the code segment by programming bits FMOD0 and F MOD1 in FCON register in accordance with Table 20. A MOVC instruction is then used for reading these spaces.

Table 20. FM0 B locks Select Bits

FMOD1 FMOD0 FM0 Adressable space

0 0 User (0000h-3FFFh)

0 1 Extra Row(FF80h-FFFFh)

1 0 Hardware Security Byte (0000h)

11reserved

Launching Programming FPL3:0 bits in F CON register are used to secure the launch of programming. A specific

sequence must be written in these bits to unlock the write protection and to launch the

programming. This s equence is 5xh followed by Axh. Table 21 summarizes the memory

spaces to program according to FMOD1:0 bits.

Table 21. Programming Spaces

Write to FCON

OperationFPL3:0 FPS FMOD1 FMOD0

5 X 0 0 No action

User

Extra Row

Hardware

Security

Byte

Reserved

AX00

5 X 0 1 No action

AX01

5 X 1 0 No action

A X 1 0 Write the fuse bits space

5 X 1 1 No action

A X 1 1 No action

Write the column latches in user

space

Write the column latches in extra row

space

4128A–8051–04/02

Note: The sequence 5xh and Axh must be executing without instructions between them other-

wise the programming is aborted.

31

Page 32

Interrupts that may occur during programming time must be disabled to avoid any spurious exit of the programming mode.

Status of the Flash Memory T he bit FBUSY in FCON register is used to indicate the status of programming.

FBUSY is set when programming is in progres s .

Selecting FM1 The bit ENBOOT in AUXR1 register is used to map FM1 from F800h to FFFFh.

Loading the Column Latches Any number of data from 1 byte to 128 bytes can be loaded in the c olumn latches. This

provides the capability to program the whole memory by byte, by page or by any num ber

of bytes in a page.

When programming is launched, an automatic erase of the locations loaded in the column latches is fi rs t performed, then programming is effectively d one. Thus no page or

block erase is needed and only the loa ded data are programmed in the corresponding

page.

The following proced ur e is us ed to load th e column latches and is sum ma ri zed in

Figure 12:

• Disable interrupt and map the column latch space by setting FPS bit.

• Load the DPTR with the address to load.

• Load Accumulator register with the data to load.

• Execute the MOVX @DPTR, A instruction.

• If needed loop the three last instructions until the page is completely loaded.

• unmap the column latch and Enable Interrupt

32

T89C5115

4128A–8051–04/02

Page 33

Figure 12. Column Latches Loading Procedu re

Column Latches

Loading

Save & Disable IT

EA= 0

Column Latches Mapping

FCON = 08h (FPS=1)

Data Load

DPTR= Address

ACC= Data

Exec:MOVX@DPTR,A

Last Byte

to load?

T89C5115

Data memory Mapping

FCON = 00h (FPS = 0)

Restore IT

Note: The last page address used when loading the column latch is the one used to select the

page programming address.

Programming the Flash Spaces

User The following procedure is used to program the User space a nd is sum mar ize d in

Figure 13:

• Load up to one page of data in the column latches from address 0000h to 3FFFh.

• Disable the interrupts.

• Launch the programming by writing the data sequence 50h followed by A0h in

FCON register (only f rom F M1).

The end of the program ming indicated by the FBUSY flag cleared.

• Enable the interrupts.

Extra Row The following procedure is used to program the Extra Row space and is summ arized i n

Figure 13:

• Load data in the column latches from address FF80h to FFFFh.

• Disable the interrupts.

• Launch the programming by writing the data sequence 52h followed by A2h in

FCON register (only f rom F M1).

The end of the program ming indicated by the FBUSY flag cleared.

• Enable the interrupts.

4128A–8051–04/02

33

Page 34

Figure 13. Flash and Extra row Programming Procedure

Flash Spaces

Programming

Column Latches Loading

see Figure 12

Save & Disable IT

EA= 0

Launch Programming

FCON= 5xh

FCON= Axh

FBusy

Cleared?

Clear Mode

FCON = 00h

Hardware Security Byte

End Programming

Restore IT

The following procedure is used to program the Hardware Secur ity Byte space

and is summarized in Figure 14:

• Set FPS and map Hardware byte (FCON = 0x0C)

• Save and disable the interrupts.

• Load DPTR at address 0000h.

• Load Accumulator register with the data to load.

• Execute the MOVX @DPTR, A instruction.

• Launch the programming by writing the data sequence 54h followed by A4h in

FCON register (only f rom F M1).

The end of the programming indicated by the FBusy flag cleared.

• Restore the interrupts

34

T89C5115

4128A–8051–04/02

Page 35

Figure 14. Hardware Programming Procedure

Flash Spaces

Programming

Save & Disable IT

EA= 0

FCON = 0Ch

T89C5115

Save & Disable IT

EA= 0

Launch Programming

FCON= 54h

FCON= A4h

Data Load

DPTR= 00h

ACC= Data

Exec:MOVX@DPTR,A

End Loading

Restore IT

FBusy

Cleared?

Clear Mode

FCON = 00h

End Programming

RestoreIT

Reading the Flash Spaces

User The following procedure is used to r ead t he U se r space:

• Read one byte in Accumulator by executing MOVC A,@A+DPTR with

A+DPTR=read@.

Note: FCON is s upposed to be reset when not needed.

Extra Row The following procedure is used to read the Extra Row space and is summarized in

Figure 15:

• Map the Extra Row space by writing 02h in FCO N reg ister.

• Read one byte in Accumulator by executing MOVC A,@A+DPTR with A= 0 &

DPTR= F F80h to FFFFh.

• Clear FCON to unmap the Extra Row.

Hardware Security Byte

4128A–8051–04/02

The following proc ed ur e is used to re ad the Hardwar e Security space and is

summarized in Figure 15:

• Map the Hardware Security space by writing 04h in FCON register.

• Read the byte i n Accumulator by executing MOVC A,@A+DPTR with A= 0 &

DPTR= 0000h.

• Clear FCON to unmap the Hardware Security Byte.

35

Page 36

Figure 15. Reading Procedure

FlashSpaces Reading

Flash Spaces Mapping

FCON= 00000xx0b

Data Read

DPTR= Address

ACC= 0

Exec:MOVCA,@A+DPTR

Clear Mode

FCON = 00h

Flash Protection from P arallel

Programming

The t hree lock bits in Hardware Security Byte (see "In-System Programming" section)

are programmed according to Tabl e 22 provide different level of protection for the o nchip code and data located in FM0 and FM1.

The only way to write this bits are the parallel mode. They are set by default to level 3.

Table 22. Program Lock bit

Program Lock Bits

Security

level

1UUU

2 P U U Parallelprogramming of the Flash is disabled.

3UPU

LB0 LB1 LB2

Protection Description

No program lock features enabled. MOVC instruction executed from

external program memory returns non encrypted data.

Same as 2, also verify through parallel programminginterface is

disabled.

Program Lock bits

U: unprogrammed

P: programmed

WARNING: Security level 2 and 3 should only be programmed after F lash and Core

verification.

Preventing Flash Corruption See paragraph in the "Power Management" section, page 17.

36

T89C5115

4128A–8051–04/02

Page 37

Registers FCON Register

FCON (S:D1h)

Flash Control Register

76543210

FPL3 FPL2 FPL1 FPL0 FPS FMOD1 FMOD0 FBUSY

T89C5115

Bit

Number

7-4 FPL3:0

3FPS

2-1 FMOD1:0

0 FBUSY

Bit

Mnemonic Description

Programming Launch Command Bits

Write 5Xh followed by AXh to launch the programming according to FMOD1:0.

(see Table 21.)

FlashMap Program Space

Set to map the column latch space in the data memory space.

Clear to re-map the data memory space.

Flash Mode

See Table 20 or Table 21.

Flash Busy

Set by hardware when programming is in progress.

Clearby hardwarewhen programming is done.

Can not be changedby software.

Reset Value = 0000 0000b

4128A–8051–04/02

37

Page 38

In-System Programming (ISP)

With the implementation of the User Space (FM0) and the Boot Space (FM1) in Flash

technology the T89C5115 allows the system engineer the development of applications

with a very high level of flexibility. This flexibility is based on the possibility to alter the

customer program at any stages of a product’s life:

• Before assembly the 1st personalization of the product by programming in the FM0

and if needed also a customized Boot loader in the FM1.

Atmel provide also a standard Boot loader by default UART

• After assembling on the PCB in its final embedded position by serial mode via the

UART.

This In-System Programming (ISP) allows code modification over the total lifetime of the

product.

Besides the default Boot loader Atmel provide to the customer also all the needed Application-Programming-Interfaces (API) which are needed for the ISP. The API are located

also in the Boot memory.

This allow the c us tomer to have a f ull use of the 16-Kbyte user memory.

Flash Programming and Erasure

There are three methods of programming the Flash memory:

• The Atmel bootloader located in FM1 is activated by the application. Low level API

routines (located in FM1)wil l be used to program FM0. The interface used for serial

downloading to FM0 is the UA RT. API can be called also by user’s bootloader

locatedin FM0 at [SBV]00h.

• A further method exist in activating the Atmel boot loader by hardware activation.

• The FM0 can be programmed also by the parallel mode using a programmer.

Figure 16. Flash Memory Mapping

FFFFh

2K Bytes IAP

bootloader

F800h

3FFFh

Custom

Boot Loader

[SBV]00h

16-KB

FM1

FM1 mapped between F800h and FFFFh

when API called

38

Flash memory

FM0

0000h

T89C5115

4128A–8051–04/02

Page 39

Boot Process

T89C5115

Software Boot P rocess

Example

Many algorithms can be used for the software boot process. Before describing them,

The description of the different flags and bytes is given below:

Boot Loader Jump Bit (BLJB):

- This bit indicates if on RESET the user wants to jump to this application at address

@0000h on FM0 or execute the boot loader at address @F800h on FM1.

- BLJB = 0 on p arts delivered with bootloade r programm ed.

- To read or m odify this bit, the APIs are used.

Boot Vector Address (SBV):

- This byte c ontains the MSB of the user boot loader address in FM0.

- The default value of SBV is FFh (no user boot loader in FM0).

- To read or m odify this byte, the APIs are used.

Extra Byte (EB) & Boot Status Byte (BSB):

- These bytes are res erv ed for customer use.

- To read or m odify these bytes, the APIs are used.

Figure 17. Hardware Boot Process Algorithm

RESET

bit ENB OOT in AUXR1 register

is initialized with BLJB.

Hardware

ENBOOT = 0

PC = 0000h

BLJB == 0

?

ENBOOT = 1

PC = F800h

Application

Software

in FM0

Boot Loader

in FM1

4128A–8051–04/02

39

Page 40

Application Programming Interface

Several Application Program Interface (API) calls are av ailable for use by an application

program to permit selective erasing and programming of Flash pages . All calls are made

by functions.

All APIs are descr ibe in: "In-System Programing: Flash Library for T89C5115", available

on the Atmel web site at www.atmel.com.

Table 23. List of API

API Call Description

PROGRAM DATABYTE Write a byte in flash memory

PROGRAM DATA PAGE Write a page (128 bytes) in flash memory

PROGRAM EEPROM BYTE Write a byte in Eeprom memory

ERASE BLOCK Erase all flash memory

ERASE BOOT VECTOR (SBV) Erase the boot vector

PROGRAM BOOT VECTOR (SBV) Write the boot vector

PROGRAM EXTRA BYTE (EB) Write the extra byte

READ DATA BYTE –

READ EEPROM BYTE –

READ FAMILY CODE –

READ MANUFACTURER CODE –

READ PRODUCT NAME –

READ REVISION NUMBER –

READ STATUS BIT (BSB) Read the status bit

READ BOOT VECTOR (SBV) Read the boot vector

READ EXTRA BYTE (EB) Read the extra byte

PROGRAM X2 Write the hardware flag for X2 mode

READ X2 Read the hardware flag for X2 mode

START BOOTLOADER T o start the bootloader from the application

XROW Bytes Table 24. XROW Mapping

Mnemonic Description Defaultvalue Address

– Copy of the Manufacturer Code 58h 30h

– Copy of the Device ID#1: Family code D7h 31h

– Copy of the Device ID#2: Memoriessize and type BBh 60h

– Copy of the Device ID#3: Name and Revision FFh 61h

40

T89C5115

4128A–8051–04/02

Page 41

Hardware Security Byte Table 25. Hardware Security byte

76543210

X2B BLJB - - - LB2 LB1 LB0

T89C5115

Bit

Number

7X2B

6BLJB

5-3 -

2-0 LB2:0 Lock Bits

Bit

Mnemonic Description

X2 Bit

Set this bit to start in standard mode

Clearthis bit to start in X2 mode.

Boot Loader Jump Bit

- 1: To start the user’s application on next RESET (@0000h) located in FM0,

- 0: Tostartthe boot loader(@F800h) located in FM1.

Reserved

The value readfrom these bits are indeterminate.

Default value after erasing chip: FFh

Notes: 1. Onlythe 4 MSB bits can be accessed by software.

2. The 4 LSB bits can only be accessed by parallel mode.

4128A–8051–04/02

41

Page 42

Serial I/O Port The T89C5115 I/O serial port is compatible with the I/O serial port in the 80C52.

It provid es both synchronous and asynchronous communication modes. It operates as a

Universal Asynchronous Receiver and Transmitter (UART) in three full-duplex modes

(Modes 1, 2 and 3). Asynchronous transmission and recept ion can oc c ur simultaneously

and at different baud rates

Serial I/O port includes the following enhancements:

• Framing error detection

• Automatic address recognition

Figure 18. Serial I/O Port Block Diagram

IB Bus

TXD

RXD

SBUF

Transmitter

Write SBUF

Mode 0 Transmit

RI

TI

SBUF

Receiver

Receive

Shift register

Read SBUF

Load SBUF

Serial Port

Interrupt Request

Framing Error Detection Framing bit error detection is provided for the three asynchronous modes. To enable t he

framing bit error detection feature, s et SM OD0 bit in PCON register.

Figure 19. Framing Error Block Diagram

RITIRB8TB8RENSM2SM1SM0/FE

Set FE bit if stop bit is 0 (framing error)

42

SM0toUARTmodecontrol

IDLPDGF0GF1POF-SMOD0SMOD1

To UARTframingerror control

When this feature is enabled, the receiver checks each incoming data frame for a valid

stop bit. An invalid stop bit may result from noise on the serial lines or from simultaneous

transmission by t wo CPUs. If a valid stop bit is not found, the Framing Error bit (FE) in

SCON register bit is set.

The software may examine the F E bit af ter each reception to check for data errors.

Once set, only software or a reset clears the F E bit. Subsequently received f rames with

T89C5115

4128A–8051–04/02

Page 43

T89C5115

valid stop bits cannot clear the FE bit. Wh en the FE feature is enabled, RI rises on the

stop bit instead of t he last data bit (See Figure 20 and Figure 21).

Figure 20. UART Timing in Mode 1

Automatic Address Recognition

RXD

RI

SMOD0=X

FE

SMOD0=1

Start

bit

Data byte

D7D6D5D4D3D2D1D0

Stop

bit

Figure 21. UART Timing in Modes 2 and 3

RXD

RI

SMOD0=0

RI

SMOD0=1

FE

SMOD0=1

Start

bit

Data byte Ninth

D8D7D6D5D4D3D2D1D0

Stop

bit

bit

The automatic address recognition feature is enabled when the mul tipro ce ssor communication feature is enabled (SM2 bit in SCO N register is set).

Implemented in t he hardw are, automatic address recognition enhances the multiprocessor c ommunication feature by allowing the serial port to examine the address of each

incoming command frame. Only when the serial port rec ognizes its own address will t he

receiver set the RI bit in the SCON register to generate an interrupt. This ensures that

the CPU is not interrupted by command frames addressed to other devices.

4128A–8051–04/02

If necessary, you can enable the automatic address recognition feature in mode 1. In

this configurati on, the stop bit takes the place of the ninth dat a bit. Bit RI is set only when

the received command frame address matches the device’s address and is terminated

by a valid stop bit.

To support automatic address recognition, a device is identified b y a given address and

a broadcast address.

Note: The multiprocessor communication and automatic address recognition features cannot

be enabled in mode 0 (i.e. setting SM2 bit in SCON register in mode 0 has no effect).

43

Page 44

Given Address Each d evice has a n individual address that is specified in the SADD R register; the

SADEN register is a mask byte that contains don’t-care bits (defined by zeros) to form

the device’s given address . The don’t-care bits provide the flexibility to address one or

more slaves at a t im e. T he following example illustrates how a given addres s is formed.

To address a device by its individual address, the SADEN mask by te must be 1111

1111b.

For example:

SADDR0101 0110b

SADEN

1111 1100b

Given0101 01XXb

Here is an example of how to use given addresses to address different slaves:

Slave A:SADDR1111 0001b

SADEN

1111 1010b

Given1111 0X0Xb

Slave B:SADDR1111 0011b

SADEN

1111 1001b

Given1111 0XX1b

Slave C:SADDR1111 0010b

SADEN

1111 1101b

Given1111 00X1b

The SADEN byte is selected so that each slave may be addressed separately.

For slave A, bit 0 (the LSB) is a don’t-care bit; for slaves B and C, bit 0 is a 1. To c om-

municate with slave A only, the mastermust send an address where bit 0 is clear (e.g.

1111 0000b).

For slav e A, bit 1 is a 0; for slaves B and C, bit 1 is a don’t care bit. To communicate with

slaves A and B, but not slave C, the master m us t send an address with bits 0 and 1 both

set (e.g. 1111 0011b).

To communicate with slaves A, B and C, the master must send an address with bit 0 s et,

bit 1 clear, and bit 2 clear (e.g. 1111 0001b).

Broadcast Address A broadcast address is formed from the logical OR of the SADDR an d SADE N registers

with zeros defined as don’t-care bits, e.g.:

SADDR 0101 0110b

SADEN 1111 1100b

SADDR OR SADEN1111 111Xb

The use of don’t-care bits provides flexibility in defining the broadcast address, however

in most applications, a broadcast address is FFh. The following is an example of using

broadcast addresses:

Slave A:SADDR1111 0001b

SADEN

1111 1010b

Given1111 1X11b,

Slave B:SADDR1111 0011b

SADEN

1111 1001b

Given1111 1X11B,

44

T89C5115

Slave C:SADDR=1111 0010b

SADEN

1111 1101b

Given1111 1111b

4128A–8051–04/02

Page 45

For slaves A and B, bit 2 is a don’t care bit; for slave C, bit 2 is set. T o communicate with

all of the slaves, the master must send an address FFh. To c ommunicate with slaves A

and B, but not slave C, the master can send and address FBh.

Registers Table 26. SCON Register

SCON (S:98h)

Serial Control Register

76543210

FE/SM0 SM1 SM2 REN TB8 RB8 TI RI

T89C5115

Bit

Number

7FE

–SM0

6SM1

5SM2

4REN

3TB8

2RB8

Bit

Mnemonic Description

Framing Error bit (SMOD0 = 1)

Cleartoresettheerrorstate,notclearedbyavalidstopbit.

Set by hardware when an invalid stop bit is detected.

Serial port Mode bit 0 (SMOD0 = 0)

Refer to SM1 for serial port mode selection.

Serial port Mode bit 1

SM0

SM1 Mode Baud Rate

0 0 ShiftRegister F

0 1 8-bit UART Variable

1 0 9-bit UART F

1 1 9-bit UART Variable

Serial port Mode 2 bit/Multiprocessor Communication Enable bit

Clearto disablemultiprocessorcommunication feature.

Set to enable multiprocessor communication feature in mode 2 and 3.

Reception Enablebit

Clearto disable serial reception.

Set to enable serial reception.

Transmitter Bit 8/Ninth bit to transmit in modes 2 and 3

Clearto transmit a logic0 in the 9th bit.

Set to transmit a logic 1 in the 9th bit.

Receiver Bit 8/Ninth bit received in modes 2 and 3

Cleared by hardware if 9th bit received is a logic 0.

Set by hardware if 9th bit receivedis a logic 1.

XTAL

XTAL

/12 (or F

/64 or F

/6 in mode X2)

XTAL

/32

XTAL

4128A–8051–04/02

Transmit Interrupt flag

1TI

0RI

Clear to acknowledge interrupt.

Set by hardware at the end of the 8th bit time in mode 0 or at the beginning of the

stop bit in the other modes.