Page 1

PIONEER CORPORATION 4-1, Meguro 1-Chome, Meguro-ku, Tokyo 153-8654, Japan

PIONEER ELECTRONICS SERVICE INC. P.O.Box 1760, Long Beach, CA 90801-1760 U.S.A.

PIONEER EUROPE NV Haven 1087 Keetberglaan 1, 9120 Melsele, Belgium

PIONEER ELECTRONICS ASIACENTRE PTE.LTD. 253 Alexandra Road, #04-01, Singapore 159936

C PIONEER CORPORATION 2001

K-ZZU. MAR. 2001 Printed in Japan

ORDER NO.

CRT2653

MD MECHANISM MODULE

CX-1020

NOTE:

- This Service Manual describes the operations of the MD mechanism module being used for the models

listed in the Table indicated below.

- Be sure to reference this service manual as well as the service manual prepared for respective models

must be referenced before implementing the repair work.

CONTENTS

1. CIRCUIT DESCRIPTIONS ...........................................2

2. MECHANISM DESCRIPTIONS.................................12

3. DISASSEMBLY .........................................................15

MODEL SERVICE MANUAL MD MECHANISM MODULE

MEH-P7300R/EW CRT2660 CXK3320

MEH-P7350/ES CRT2660 CXK3320

MEH-P5350/ES CRT2654 CXK3310

Page 2

1. CIRCUIT DESCRIPTIONS

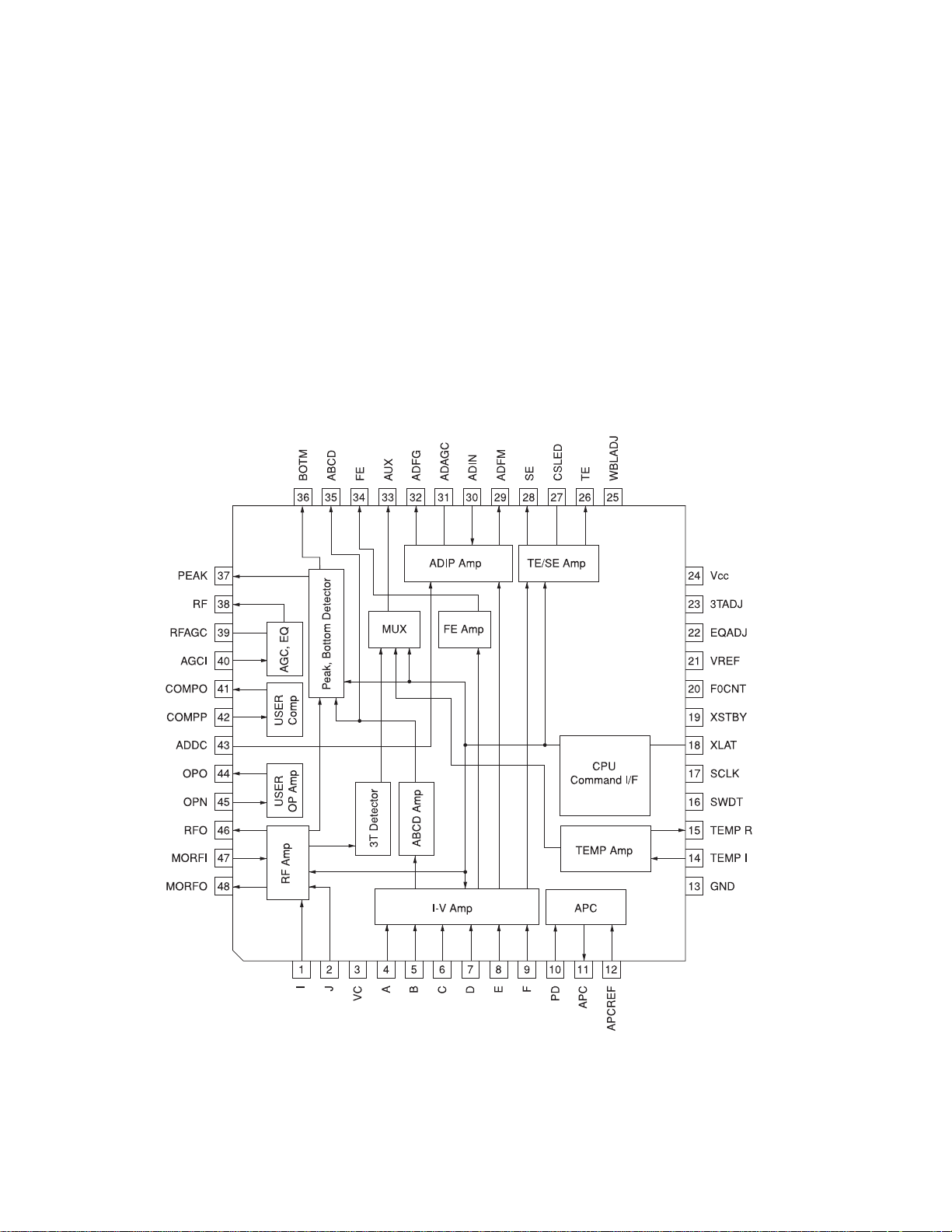

1.1 RF AMPLIFIER BLOCK (CXA2523AR : IC101)

This section works to process the output signals from the MD pickup to generate signals to be transferred to the next

stage, namely, the DSP section (IC201).

Respective photo-detector output signals A, B, C, D, E and F are I-V converted and processed inside the RF amplifier to

become FE, TE and ADIP signals.

Also, I and J outputs which have been I-V converted by the amplifier incorporating the photo-detector inside the

pickup are processed to become the RF signals and the PEAK and BOTM signals.

Meanwhile, since this system is of the single power (+3.3V) specification, the reference voltage for the servo-signals is

Vc (1.65V).

Vc is being output from this RF amplifier (IC101, 3pin).

(Note) Do not short the Vc and GND while making measurements.

2

CX-1020

Fig. 1 : CXA2523AR BLOCK DIAGRAM

Page 3

3

CX-1020

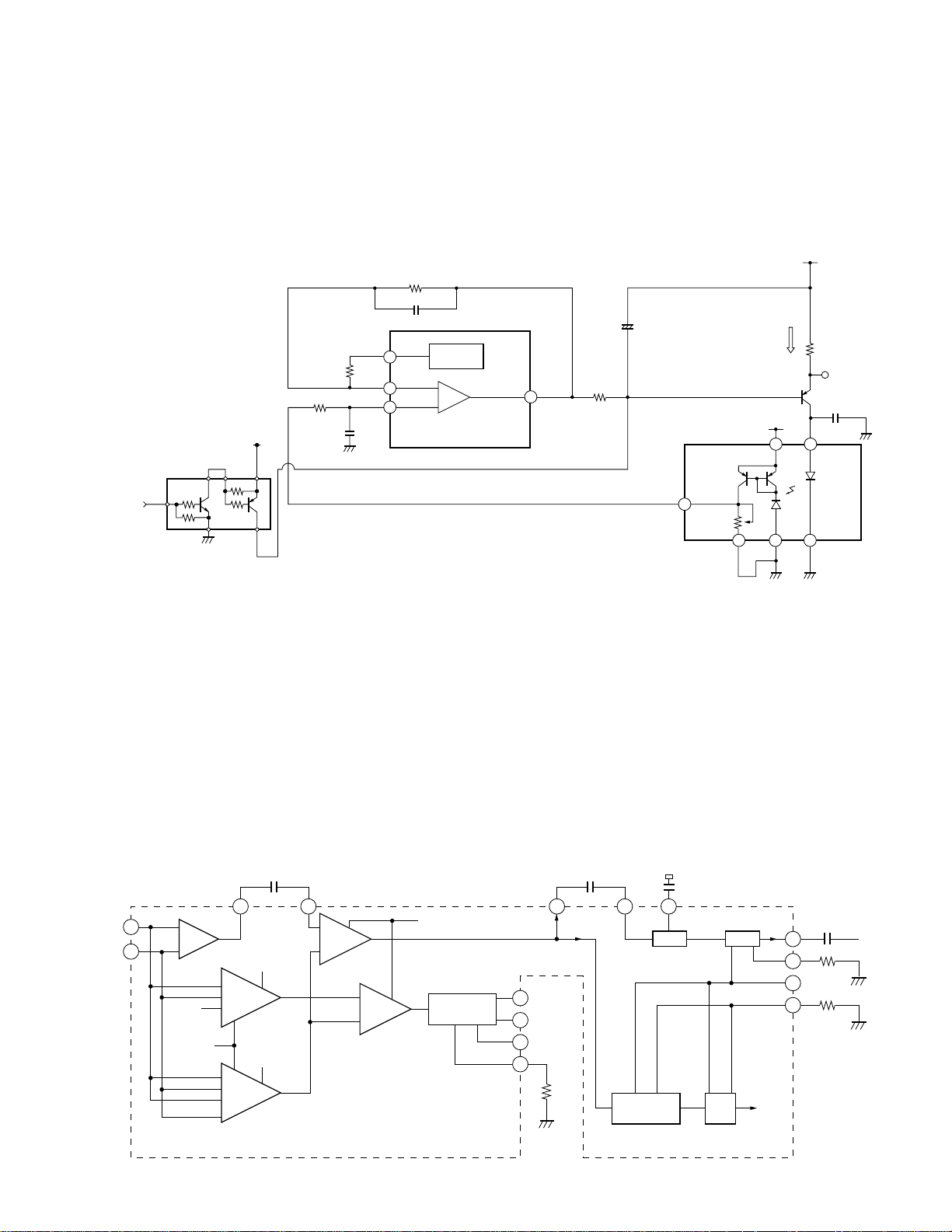

2) RF Amplifier

I and J signals being I-J converted in the pickup are entered to 1 and 2 pins. Then, their difference signal (group

signal) and sum signal (bit signal) are generated on RFA1 and RFA2, respectively.

RFA2 and RFA3 are switching operational amplifiers. The amplifiers detect high reflection (Premastered) and low

reflection (Recordable) using the disc detector switch (S404) to switch to the gain selected by the serial command

HLPT or PTGR.

RF signal (46 pin) is operated and conducted to the AGC circuit and equalizer via C112 to generate RF signal (36 pin).

RF signal is maintained essentially at a constant level (approximately at 1.1 Vpp) by the AGC circuit.

This signal is entered to the signal processing LSI (IC201: 102 pins) for the data processing as well as control of the

Premastered Disc playing spindle.

1) APC (Automatic Power Control) Circuit

Since laser diode (LD) has temperature characteristics, the APC circuit is provided to control current flow using the

monitor diode so that the output may be kept at a constant level.

LD current is determined by measuring voltage across V1 and 3VD.

The current value should be approximately 40 mA (0.4V/10Ω).

19

20 6

10

12

11

–

+

21

12 14

13

VREF

Q102

UMD2N

LDCNT

R101

PD

APC REF

CXA2523AR

MON

Vr

MD

LD

3VD

C105

R1

LD+

3VD

R103 10

VI

100/6R3

R104

APC

C108 R001

R105 470K

R106

6R8K

1.25V

680

C106

+

GNDGND LD –

PU unit

47K

C107

3VD

22P

1

3

4

5

6

2

1

2

38

–

+

–2

–1

–1

–2

–1

–2

–1

–1

–1

–2

–2

48 47

22

20

23

46 40 39

25

20

36

37

Peak/Bottom

Hold

BPF

fo=720kHz

Peak

Hold

BPF3T PEAK3T

PBH1

J

MORFO MORFI RFO

I

RFA1

OFST

ABCD

RFA3

PEAK

BOTM

F0CNT

WBLADJ

PBSW

GRVA

HLPT

GRV

RFA2

PTGR

AGC EQA

3TADJ

F0CNT

I3

EQADJ

RFAGCAGCI

<To IC201>

RF

C112

R022

C111

R047

Page 4

4

CX-1020

3) I-V, ADIP, ABCD and FE Amplifier Blocks

They are used for I-V conversion of photo-detector signals (A to F pins) from the pickup.

ADIP, FE and full quantity of light signals are generated from A to D signals, and TE signal is generated from E and F

signals.

The ABCD amplifier generates the full quantity of light signal for the main spot. This signal is sum of A to D signals

after I-V conversion. According to the level of the full quantity of light signal, resistance value of I-V is automatically

adjusted so that ADIP, FE and TE signals may be maintained at the specified level.

FE and TE signals output from both the Recordable and Premastered Discs are adjusted to approximately 1 Vpp and

1.7 Vpp, respectively. This adjustment is executed whenever a disc is inserted.

ABCD signal entered to the signal processing LSI (IC201: 82 pins) is also used for generating FOK and defect detect

signals.

The ADIP amplifier is used for generating ADIP signal that is present only on the Recordable Disc.

Addresses are already recorded on the Recordable Disc by wobbling FM signal that uses 22.05 KHz as the carrier. In

order to detect wobble elements, noise elements of the signal are eliminated on the BPF, then the signal is output to

the ADFM via the AGC. The signal is then sent to C119 for DC cut and binary converted on the comparator to generate

ADFG signal. ADFG signal is entered to the signal processing LSI (IC201: 67 pins) to control the address and spindle

when the Recordable Disc is played.

–

–

+

+

4

+

–

5

+

–

6

+

–

7

25

+

–

–

–

+

+

–

–

–

–

35

82

34

29

30

32

83

67

20

43 31

Focus err amplifier

IVR0-IVR4

FE

R207

100

AIV

A

AA BB

CC

AA

DD

AA

CC

BB

DD

AA

BB

CC

DD

IVR0-IVR4

BIV

B

ABCD

BB

IVR0-IVR4

CIV

C

CC

IVR0-IVR4

DIV

ABCDA

FEA

ATA

D

DD

ADAGC

ADFM

ADIN

WBLADJ

F0CNT

ADFG

ADDC

C119

4700P

<To IC201 pins>

BPF

fo=22.05kHz

BPF22

ADIPAGC

<To IC201 pins>

<To IC201 pins>

AGC

BPFC

COMP

ABCD amplifier

I-V amplifier ADIP amplifier

Page 5

5

CX-1020

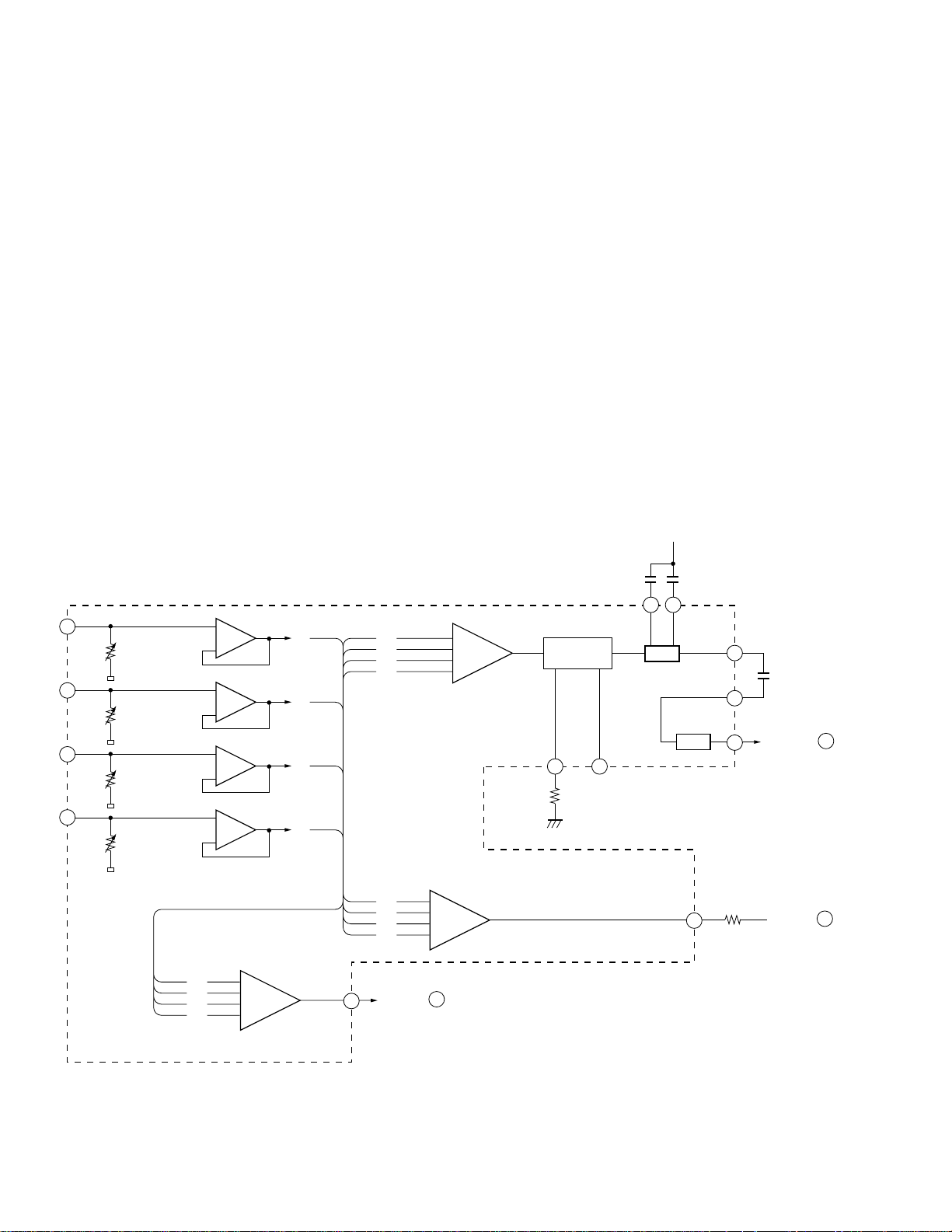

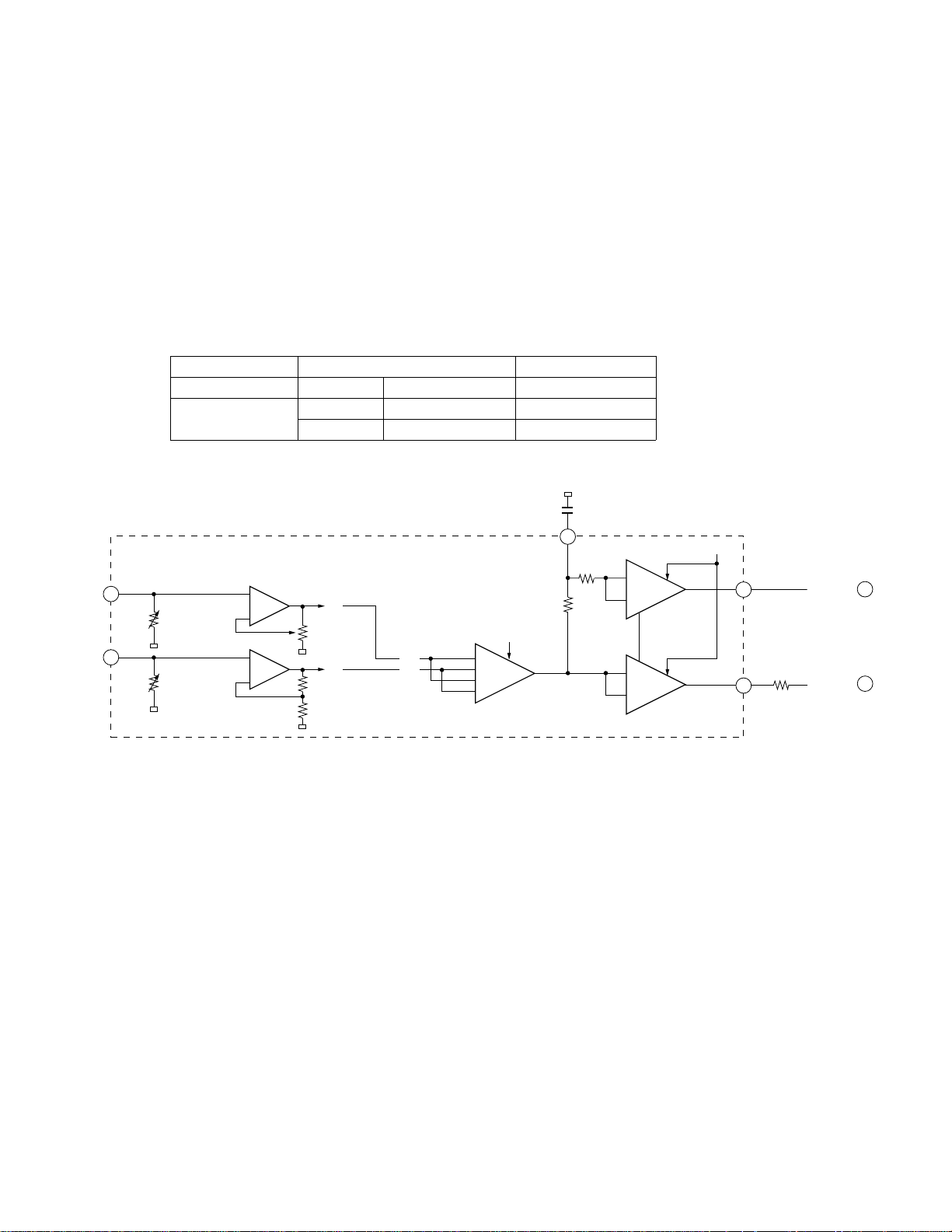

4) TE and SE Amplifiers

Side spot E and F signals are I-V converted, then entered to the EF balance adjusting amplifier. Then, after polarity of

the tracking error signal is switched by the TE differential amplifier (TESW), the signal is conducted to the gain

amplifier to generate TE signal.

Select PTGR = 1 for the Pit play and PTGR = 2 for the group play.

The EF balance adjusting amplifier automatically adjusts an EF balance resistance value so that level of SE signal

becomes the same as the reference voltage Vc when the TRKG made is open.

The SE amplifier generates TE signal from the LPF, then enters it into the signal processing LSI (IC201: 91 pins) for

digital equalizing.

Condition PTGR HLPT

PremasterdDisc Pit High reflection 1 2

RecordableDisc Pit Low reflection 1 1

Groove Low reflection 2 1

—1

+1

+2

—2

8

+

—

9

+

—

26

27

—2

—1

92

28

—2

—1

91

IVR0-IVR4

EFB0-EFB4

EIV

E

EE

EE

FF

IVR0-IVR4

FIV

F

FF

CSLED

TG

TEA

TESW

PTGR

TE

<To IC201 pins>

R208

SEA

SE

<To IC201 pins>

100

C120

R1

Pit / GR Select

Pit

GR

Page 6

1.2 SIGNAL PROCESSOR BLOCK (CXD2667R IC201)

1.2.1 SERVO BLOCK

1) Servo Block

This block offers servo control over the focus, tracking, spindle and carriage.

FE, TE and SE signals from the amplifier are A/D converted, equalized on D.F (digital filer) block, and then output to

PWM.

The spindle servo detects phase and frequency of input signal (from 102 pin RFI terminal for Pre_disc and 67 pin ADFG

terminal for Rec_disc), then outputs it to PWM via the filter.

These signals are power amplified on the driver IC401 to drive the actuator and motor.

Focus Servo System

In order to close the focus, the actuator is driven up near to the Disc once, then moved down.

As soon as up-move is started, the spindle is kicked for 320 ms, then ofst drive is turned on.

Focus close is carried out when the following conditions are met:

1) The actuator, after having approached the Disc once, is now moving away from it.

2) FOK = H (Can be monitored on the mnt0 terminal when the mnt selector is set to 00.)

3) FZC =

↑

After the focus close has been started, the microcomputer judges the operation is complete if FOK = H continues for 32 ms.

6

CX-1020

A/DFE

FIN (For monitoring control signal)

FOP

FOM

A, B, C, D

RF

amplifier

Driver

Pick up

IC201IC101

IC401

BIAS

EQ PWM

FFDR 64pin

FRDR 65pin

close_point

Close operation is judged to have

successfully ended when FOK

remains at "H" for 32 ms.

FE

FOK

FZC

Page 7

Tracking Servo System

The system causes the microcomputer to issue the tracking close instruction to the IC, then switches the spindle

control from the ofst drive to the CLV control.

The close operation completes when the Disc address has been read after the spindle LOCK signal went high

(Can be monitored on the mnt0 terminal when the mnt selector is set to 00).

Carriage Servo System

When the microcomputor judges that the direct current in the tracking direction is above the normal, carriage motor

will drive automatically.

7

CX-1020

A/DTE

TIN (For monitoring control signal)

TOP

TOM

E

F

RF

amplifier

Driver

Pick up

IC201IC101

IC401

OFST

EQ PWM

TFDR 77pin

TRDR 76pin

A/DSE

CIN (For monitoring control signal)

COP

COM

E

F

RF

amplifier

Driver

Carriage Motor

Pick up

IC201IC101

IC401

PWM

SFDR 112pin

SRDR 111pin

M

MD

microcomputer

IC301

Timing Control

Timing Control

RF

ADFG

SIN (For monitoring control signal)

SOP

SOM

RF

amplifier

Driver

Spindle Motor

Pick up

IC201IC101

IC401

FM Demodulation

EQ

Pre_disc

Rec_disc

PWM

SPFD 114pin

SPRD 113pin

M

Spindle Servo

As for Pre_disc, the spindle servo implements CLV control utilizing EFM signal(RF).

As for Rec_disc, the servo implements CLV control utilizing ADIP signal(ADFG) generated for respective disc groups.

The locking status of the spindle servo can be monitored on the MNT3 terminal by setting the monitor selector to 00.

Page 8

Track Jump

Track jumps of 1T, 10T, 16T, 32T and fine search are available thanks to the auto sequence function of LSI.

8

CX-1020

kick

1TRK_rew jump (fwd is reversed-inversion.)

brake

TIN

TE

kick

Multiple TRK_rew jump (fwd is reversed-inversion.)

brake

TIN

TE

CIN

2) Automatic Adjustment Function

This mechanical module implements the following automatic adjustments using the RF amplifier, servo IC and

microcomputer. This function is intended at ensuring stable play by eliminating variations in sounds that can result

from conditions of given environment or discs as well as aged deterioration of the module.

Whenever a disc is inserted, this adjustment is carried out in the following sequence.

1) Offset adjustment

* Electric offset being output from the RF amplifier is adjusted to 0V seen from the reference voltage:VC .

* This adjustment is automatically executed in the IC according to VC, FE and ABCD instructions from the microcomputer.

2) IV adjustment

* Gain of the RF amplifier’s current/voltage converter AD is adjusted to approximately 500 mV for Pre_disc and

approximately 800 mV for Rec_disc using the ABCD (full quantity of light) signal (82 pin) at LD_off as the reference.

* This adjustment is automatically carried out when the IC sends the command to the RF amplifier in response to the

instruction from the microcomputer.

3) Tracking balance (EF.B) adjustment

* In this adjustment, gain of E signal on the RF amplifier is varied so that TE signal may become evenly balanced

against VC (reference voltage, 85 pin) in terms of both plus and minus.

* This adjustment is automatically carried out when the IC sends the command to the RF amplifier in response to the

instruction from the microcomputer.

4) Focus AGC (F.AGC)

* This adjustment is done to maintain loop gain of the focus servo at a constant level so that stable focus servo

function may be ensured.

* Gain adjustment is done by injecting disturbance generated in the IC to the focus servo loop.

* This adjustment is automatically implemented by the IC according to the instruction from the microcomputer.

5) Focus bias adjustment (F.BIAS)

* This function is used for adjusting jitter of EFM signal(RF) to an optimum level by optimizing the focus point during

play.

The microcomputer performs this adjustment by detecting phase and level of I3 signal from the RF amplifier and that

of FE signal.

6) Tracking AGC (T.AGC)

* This function maintains loop gain of the tracking servo at a constant level to ensure its stable function.

* Gain of the tracking servo is adjusted to a constant level by injecting disturbance generated in the IC to the tracking

servo loop.

* The IC automatically implements this adjustment according to the instruction from the microcomputer.

Page 9

**** You can display and check results of the adjustment from the Test Mode(display in hexadecimal, 2’s complement)

"7F~0,FF~80" Conversion from hex to decimal

Hexadecimal ↓

"127~0,-1~-128" Decimal

1) OFST adjustment

Reference 00 (h)

Example 02 = VC ⇒ 2 x 13mV = +26mV

Result of the VC offset adjustment is +26mV, thus the circuit offset must be -26mV.

* Offset adjustment of FE and ABCD is implemented based on result of the adjustment done on the VC.

2) IV adjustment

Reference Pre_disc: 16 (h) Rec_disc: 08 (h)

Example 06 = 1V (with Rec_disc) ⇒ 1 (dB) x (08 - 06) = +2dB

Gain is varied by +2dB against the reference value.

Gain is adjusted approximately by 1dB according to difference of steps from the reference. The smaller the value

represents higher gain.

3) EF.B adjustment

Reference 0F (h)

Variable gain volume can be computed based on difference from the reference.

Example 0A = EFB ⇒ 0.15 (dB) x (0A - 0F) = 0.75dB.

Gain of E signal is varied by -0.75dB against F signal.

(4) AGC adjustment

Reference 30(h)

Variable gain volume can be computed based on difference from the reference.

Example 27 = FACC ⇒ 20log (27 (h)/30 (h)) = -1.8dB.

Variable gain volume is -1.8dB. * The same applies to the tracking, too.

(5) Focus bias adjustment

Reference: 00(h)

Variable bias volume can be computed based on difference from the reference.

Example FA = BIAS ⇒ FA(h) - 100(h) = -6.

Volume of bias applied = -6 x 13mV = -78mV.

1.2.2 Signal Processor Block

Data read from disc is conducted to RF amp, then entered to this IC as EFM signal(RF).

The signal is subjected to EFM demodulation and ACIRC (error correction), then stored in DRAM once. As needed, the

signal is transferred from DRAM, and ATRAC3/ATRAC expanded and then converted to audio data.

This data is output from the built-in DAC as analog audio data.

Incorporates a 20-bit DAC with an 8-times over-sampling filter and a secondary analog LPF (fc = 97 kHz).

9

CX-1020

comp

RF

I

J

RF

amplifier

Pickup

amplifier

IC201

IC101

ATRAC3/

ATRAC

DAC LPF

EFM

Demodulation

ACIRC

Demodulation

DRAM

Memory

Demodulation

audio output

Page 10

1.3 POWER SUPPLY AND DRIVER BLOCK (BA5985FM: IC401)

1) Power supply

Switched system power supplies MDVD and PVD (8.3V) from the mother board and backup system power supply VDD

(5V) are used for this system (see the power supply system diagram).

3.3V for driving MD/LSI system and LD is generated from MDVD. In order to drive large current, only PVD (3.3V) is

used as the driver power.

Pro-test is prepared to detect voltage error in MDVD.

As soon as overvoltage beyond 9.9V or undervoltage below 3.5V is detected, MD microcomputer turns off the start

control signal (VDON) from VD to stop supply of VD from the mother PCB.

In this case, ERR A0 indicating a power supply system error is displayed on the product.

2) Driver block

It is a linear driver used for driving 5 channels consisted of 1 channel on Load/EJ system and 4 channels on

actuator/SPDL/CRG system.

Forward/reverse drive (approximately 7.5V) of the Load/EJ system is implemented by the control signals (MLOAD AND

MEJCT) from the MD microcomputer.

4-channel system conducts binary PWM signal to the differential L.P.F, then supplies it driver.

You can monitor respective signals as analog signals (FIN, TIN, SIN and CIN).

10

CX-1020

M

M

M

MEJCT

C+

C–

CIN

S+

S–

SIN

GND

LOP

LOM

SOM

SOP

COM

COP

MLOAD

T+

T–

TIN

F+

F–

FIN

GND

PVC

CONT

GND

FOM

FOP

TOM

TOP

CRG

SYSTEM

RC

LADDER

RC

LADDER

FOCUS

SYSTEM

RC

LADDER

SPDL

SYSTEM

RC

LADDER

PVD

LOAD/ET

Motor

SPDL

Motor

CRG

Motor

FOCUS

actuator

TRKG

actuator

CN401

LO+

LO–

SO+

SO–

CN101

F–

F+

T–

T+

SFDR

SRDR

SPRD

SPFD

< IC201 >

< IC201 >

< IC301 >

MD microcomputer

TRKG SYSTEM

TRDR

TFDR

< IC201 >

FFDR

FRDR

< IC201 >

Page 11

11

CX-1020

VD system

8.3V

VDD system

5V

3.3V

REG.

BA033FP

BA5985FM

LD

RFÆAmp

ATRAC3

ÆDSP

2.5vreg

Focus/TR

KG ACT

CRG/SPDL

MOT

MD microcomputer

LogicBuffer

/mute

Load/EJ

MOT

* typ36mA

*max55mA/

High tempera

CXA2523AR

CXD2667R

PD5655A

TC7WH125FU x 2

SlaveP-Bus

MDVD

system

PVD system DRIVER

VDsense

High : 8.3 + 1.6V

Low : 5.0 - 1.5V

* 80mAavr/play

*660mApeak/inside and outside search

TEMP sense

+82 ± 3°C

R314 : 10kΩ 82°C

*CXK3330 : +85 ± 3°C

R314 : 9.1kΩ

*90mAavr/play

1.3A with built-in excess

current protector

Output voltage 3.3 ± 0.17V

Software protecting operation

2.5Vsense

more than 1.0V

min operation

*typ48mA(RF+

min operation

max140mA/F

*150mAavr/

inside and ou

*350mApeak/

*150mAavr

*520mApeak/

30mAavr

5µAstby

mAavr

mAmax

1.4 SCHEMATIC FLOW DIAGRAM FOR THE MODULE POWER

(TEMPERATURE DETECTION)

Page 12

12

CX-1020

2. MECHANISM DESCRIPTIONS

2.1 CARTRIDGE LOADING OPERATION

The load switch is provided in front of the cartridge transfer rubber roller.

The load switch is turned on after the cartridge is inserted. Turning this switch on will start rotation of the loading

motor-driven rubber roller and, as the result, transfer of the cartridge is initiated.

A view from the insertion port.

Load switch

(Normally off. It is turned on only when the

cartridge is inserted.).

A view from the insertion port

(when the cartridge is inserted).

Arm.=It starts rotating when the cartridge is

inserted.

An internal view of the machine.

When the cartridge is inserted.

Loading motor

Rubber roller

Eject switch (for positioning of the cartridge before ejection).

Cartridge insertion.

Page 13

13

CX-1020

2.2 CLAMPING OPERATION

The cartridge being transferred by the rubber roller pushes the resin lever shown in the figure. When pushed, the

spur gear on the resin lever (they are molded integral) is engaged with the rotating gear, thereby moving the

sheet metal lever fitted to the resin gear.

When the sheet metal lever is moved, the cartridge holder fitted to the groove on the sheet metal lever is driven

to the clamping position.

Cartridge being transferred.

Resin lever (being pushed by transferring force of the rubber roller).

Cartridge starts pushing the resin lever.

Sheet metal lever.

Resin lever (spur gear) after engagement.

Resin lever (spur gear) before engagement.

Page 14

14

CX-1020

Cartridge holder is driven to the clamping position by move of the sheet metal lever.

Left side fitting pin of the cartridge holder.

An internal view of the machine in the clamping operation.

2.3 EJECT OPERATION

The cartridge is ejected basically in the reverse order of loading.

Eject position is decided by the eject switch. As this switch is turned off, the loading motor is stopped and thus

the cartridge eject operation is completed.

Left side sheet metal lever.

Shutter is opened or closed by the shutter spring and shutter lever

that is screw-fixed to the cartridge holder.

Right side sheet metal lever.

Arm for synchronizing the move of the left and right side sheet metal levers.

Page 15

15

CX-1020

3. DISASSEMBLY

- Removing the PU Unit

1. Provide short solder in section A, then remove the

connector.

2. Remove the two screws, then erect the board in the

direction indicated by the white arrow head.

3. Remove the two screws and two springs.

4. Drive out the PU Unit through the direction indicated

by the white arrow head.

- Carriage Motor and Spindle Motor

Removing the Loading Motor (1/2)

1. Provide short solder in section A, then remove the

connector.

2. Peel off solder in section B, then remove the lead

wire.

3. Remove the two screws, then dismount the MD Unit.

4. Remove the connector situated in section C.

Note: Before removing the Loading Motor, insert the

finished MD Unit, then clamp it.

Page 16

CX-1020

- Removing the Carriage Motor (2/2)

1. Remove the screw, then remove the Holder.

2. Remove the screw, drive out the Carriage Motor

through the direction indicated by the white arrow

head.

- Removing the Spindle Motor (2/2)

1. Peel off solder provided in the circled position, then

remove the lead wire.

2. Remove the three screws, then drive out the Spindle

Motor through the direction indicated by the white

arrow head.

Note: When the PU Unit is installed, it must be

moved along the outer perimeter.

- Removing the Loading Motor (2/2)

1. Peel off solder in the circled position, then remove

the Flexible PCB.

2. Remove the four screws, then dismount

the Bracket.

3. Remove the four springs.

4. Remove the two screws, then dismount

the Motor Bracket.

5. Remove the two screws, then dismount

the Loading Motor.

When replacement of the Loading Motor is

complete, apply 7V to the new Loading

Motor with the chassis being assembled

(without the MD Unit, though). Then, insert

the disk and clamp.

- Why clamping is required

It is difficult to dismount the Chassis Assy

from the Upper Case because its move can

be blocked by section A in the figure. As

long as the machine is in the clamp mode,

section A is pulled inside the chassis,

thereby allowing you to remove the chassis

easier.

Loading...

Loading...