Philips UDA1309H-N1 Datasheet

DATA SH EET

Product specification

Supersedes data of 1996 Jul 18

File under Integrated Circuits, IC01

1998 Jan 06

INTEGRATED CIRCUITS

UDA1309H

Low-power stereo bitstream

ADC/DAC

1998 Jan 06 2

Philips Semiconductors Product specification

Low-power stereo bitstream ADC/DAC UDA1309H

FEATURES

• Low power

• Integrated high-pass filter to cancel DC offset (ADC)

• Analog loop-through function

• Multiple digital input/output formats possible

• 256fs system clock frequency

• Several power-down modes

• Digital de-emphasis (DAC)

• Overload detector to enable automatic recording level

adjustment (ADC)

• High dynamic range

• DAC requires only one capacitor for post-filtering

• Small 44-pin quad flat pack with 0.8 mm pitch

• 256fs system clock frequency in Analog-to-Digital (AD)

and Digital-to-Analog (DA) mode

• Choice of three system clock frequencies

(192fs, 256fs or 384fs) in DA mode.

APPLICATION

• Portable digital audio equipment.

GENERAL DESCRIPTION

The UDA1309H is a single chip stereo analog-to-digital

and digital-to-analog converter employing bitstream

conversion techniques. The device is eminently suitable

for use in low-power portable digital audio equipment

which incorporates recording and playback functions.

ORDERING INFORMATION

TYPE

NUMBER

PACKAGE

NAME DESCRIPTION VERSION

UDA1309H QFP44 plastic quad flat package; 44 leads (lead length 1.3mm); body 10× 10 × 1.75 mm SOT307-2

1998 Jan 06 3

Philips Semiconductors Product specification

Low-power stereo bitstream ADC/DAC UDA1309H

QUICK REFERENCE DATA

V

DDD=VDDA=VDDO=VDDD(F)

=5V; V

SSD=VSSA=VSSO=VSSD(F)

=0V; T

amb

=25°C; full scale sine wave input;

mode 1; fi= 1 kHz; 16-bit input data; conversion rate = 44.1 kHz; measurement bandwidth = 10 Hz to 20 kHz; unless

otherwise specified.

Notes

1. VI for full scale digital output is a function of V

DDA(AD)

[1.0 V (RMS) at V

DDA(AD)

= 5.0 V is equivalent to −1.0 dB in the

digital domain].

2. At full scale digital input; no de-emphasis; V

O(rms)

is a function of V

DDA(DA)

.

3. 18-bit input data.

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Supply

V

DDA(AD)

ADC analog supply voltage (pin 8) 4.5 5.0 5.5 V

V

DDA(DA)

DAC analog supply voltage (pin 25) 4.5 5.0 5.5 V

V

DDO

operational amplifiers supply voltage

(pin 19)

4.5 5.0 5.5 V

V

DDD

ADC and DAC digital supply voltage

(pin 28)

4.5 5.0 5.5 V

V

DDD(F)

digital filters supply voltage (pin 34) 4.5 5.0 5.5 V

I

DDA(AD)

ADC analog supply current (pin 8) − 9 13.5 mA

I

DDA(DA)

DAC analog supply current (pin 25) − 4.5 6.8 mA

I

DDO

operational amplifiers supply current

(pin 19)

− 14 21 mA

I

DDD

ADC and DAC digital supply current

(pin 28)

− 0.2 0.5 mA

I

DDD(F)

digital filters supply current (pin 34) − 24 36 mA

T

amb

operating ambient temperature −20 − +75 °C

Analog-to-digital converter

V

I(rms)

input voltage (RMS value) note 1 0.9 1.0 1.1 V

(THD + N)/S total harmonic distortion plus

noise-to-signal ratio

at 0 dB −−85 tbf dB

at −60 dB; A-weighted −−35 −30 dB

S/N idle channel signal-to-noise ratio V

I

= 0 V; A-weighted tbf 95 − dB

α

cs

channel separation − 90 − dB

Digital-to-analog converter

V

O(rms)

output voltage (RMS value) note 2 0.9 1.0 1.1 V

(THD + N)/S total harmonic distortion plus

noise-to-signal ratio

at 0 dB −−90 −82 dB

at −60 dB; A-weighted −−38 −34 dB

at −60 dB; A-weighted; note 3 −−44 − dB

S/N idle channel signal-to-noise ratio code 0000H; A-weighted − 104 − dB

α

cs

channel separation 90 100 − dB

1998 Jan 06 4

Philips Semiconductors Product specification

Low-power stereo bitstream ADC/DAC UDA1309H

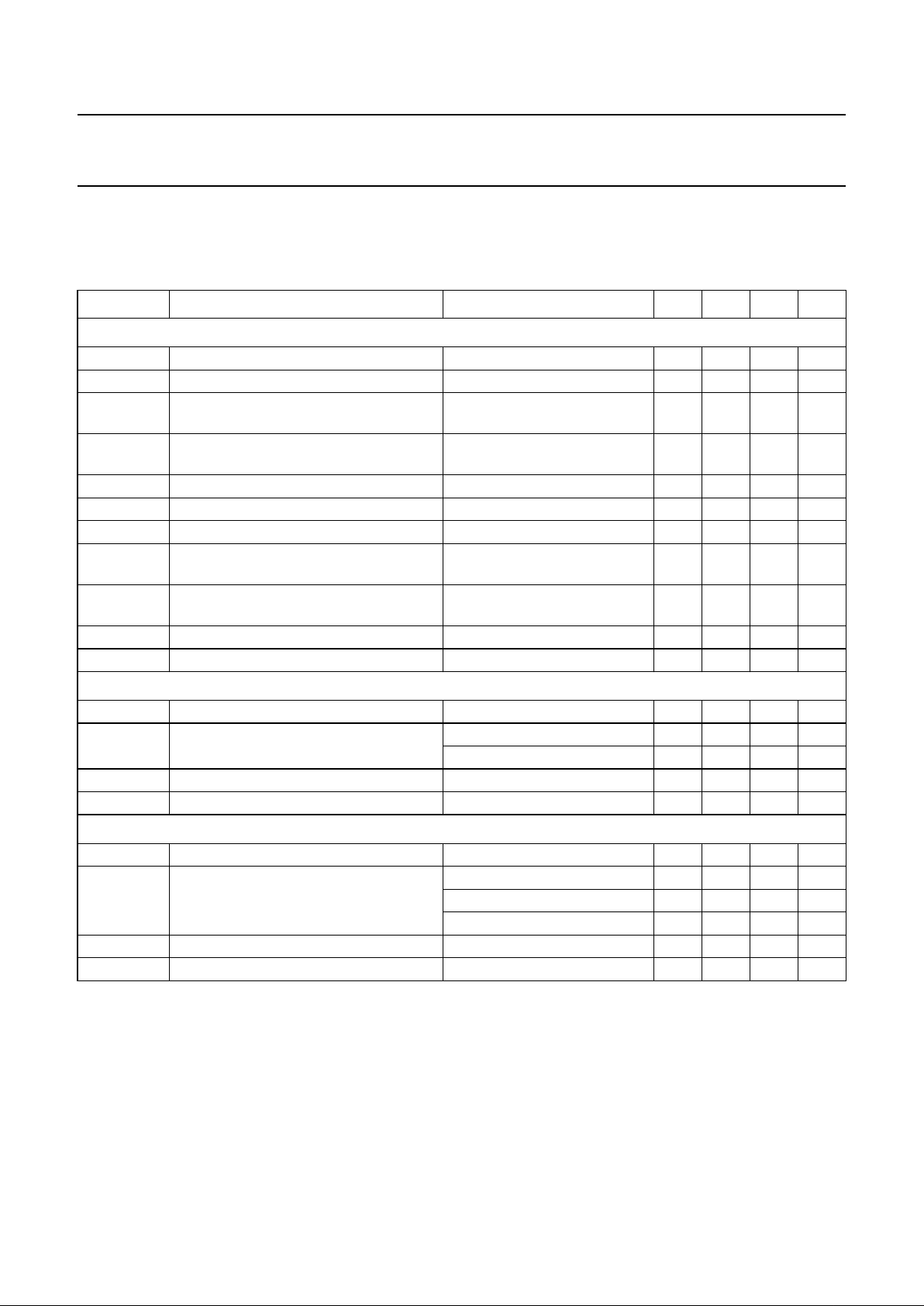

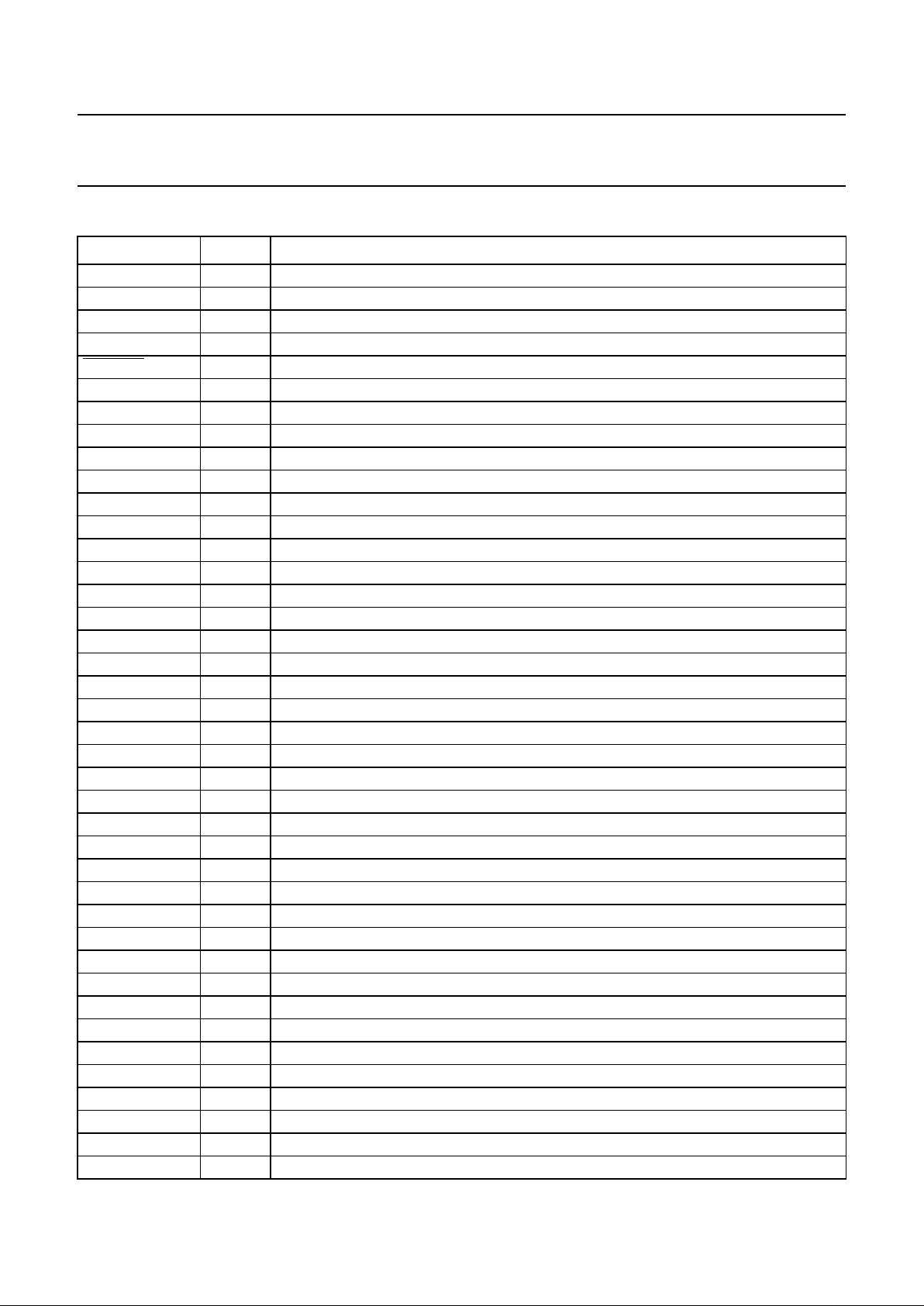

BLOCK DIAGRAM

ok, full pagewidth

MBH527

4.7 kΩ

4.7 kΩ

4.7 kΩ

4.7 kΩ

1.6 kΩ

1.6 kΩ

47 µF

0.22 µF

0.22 µF

47 µF

0.22 µF

1 nF

1 nF

330 pF

330 pF

47

kΩ

10

µF

0.22

µF

Vm

Vm

DAC

DIGITAL

FILTER

DIGITAL

FILTER

DAC

DIGITAL

INTERFACE

DIGITAL

INTERFACE

MODE SELECT

ADC

ADC

CURRENT

REFERENCE

14

15

42

1

41

6

36

32

31

35 29

5

39

28

27

23

24

18

22

21

19

20

26

25

33

34

30

3

42

43

44373840

9

1112

13

10

16

7

8

17

AD

ref

BAIR

BAOR

OVLOAD

ADENB

ADWS

ADBCK

ADSDA

ADPON

ANLPTR

DAWS

DABCK

DASDA

DAPON

V

SS(I/O)

V

DDD

V

SSD

DACR

V

OR

analog output

V

OR

DA

ref

analog input

V

IR

V

OLDACL

analog output

V

OL

V

SSO

V

DDO

V

SSA(DA)

V

DDA(DA)

V

SSD(F)

V

DDD(F)

DADEM

MODE0

MODE1

MODE2

CLKEDGE

TEST0

TEST1

SYSCLK

V

ref(neg)

V

ref(pos)

BAOL

BAIL

V

ref

V

DDA(AD)

analog input

V

IL

V

SSA(AD)

V

DDA(AD)

I

ref

I

DAC

UDA1309H

Supply decoupling on pins 19, 25, 28 and 34; 0.22 µF (ceramic), 47 µF (electrolytic).

Capacitance at pin 11 should be close to pins 11 and 9.

Fig.1 Block diagram.

1998 Jan 06 5

Philips Semiconductors Product specification

Low-power stereo bitstream ADC/DAC UDA1309H

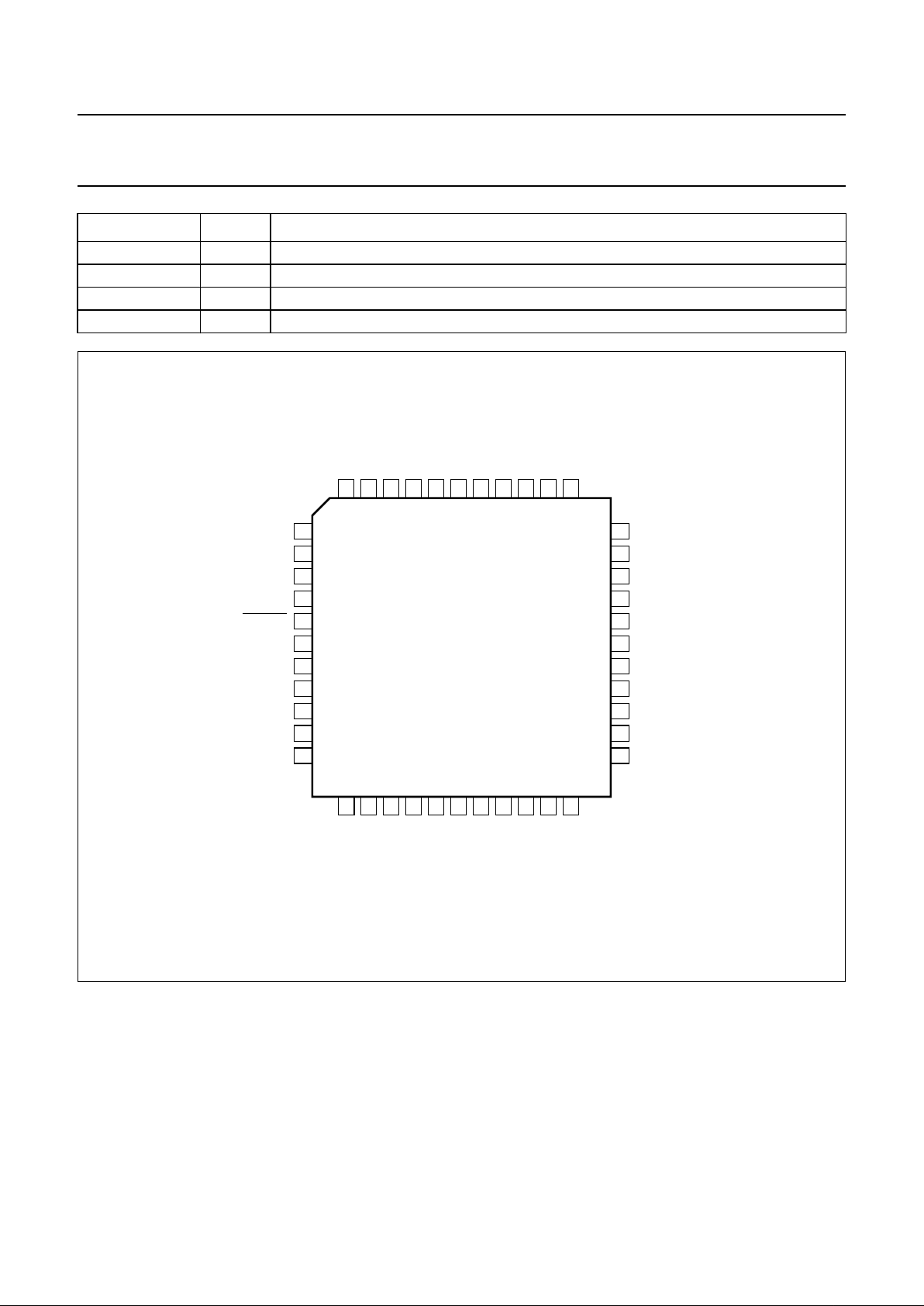

PINNING

SYMBOL PIN DESCRIPTION

ADBCK 1 ADC input bit clock; 32f

s

or 64f

s

ADWS 2 ADC word select input at f

s

MODE0 3 ADC/DAC mode select input

ADENB 4 ADC serial data enable input (active HIGH)

OVLOAD 5 ADC output overload flag (active LOW)

ADPON 6 ADC power-on-mode input (active HIGH)

V

SSA(AD)

7 ADC analog ground supply voltage

V

DDA(AD)

8 ADC analog supply voltage

V

ref(neg)

9 ADC negative reference voltage input (ground)

V

ref

10 ADC decoupling capacitor

V

ref(pos)

11 ADC positive reference voltage decoupling capacitor

BAOL 12 ADC input amplifier output left

BAIL 13 ADC input amplifier virtual ground left

BAIR 14 ADC input amplifier virtual ground right

BAOR 15 ADC input amplifier output right

AD

ref

16 ADC decoupling capacitor

I

ref

17 ADC/DAC reference current resistor input

DA

ref

18 DAC decoupling capacitor

V

DDO

19 ADC/DAC operational amplifier supply voltage

V

SSO

20 ADC/DAC operational amplifier ground supply voltage

V

OL

21 DAC output voltage left

DACL 22 DAC output current left

DACR 23 DAC output current right

V

OR

24 DAC output voltage right

V

DDA(DA)

25 DAC analog supply voltage

V

SSA(DA)

26 DAC analog ground supply voltage

V

SSD

27 ADC/DAC digital ground supply voltage

V

DDD

28 ADC/DAC digital supply voltage

DAPON 29 DAC power-on-mode input (active HIGH)

DADEM 30 DAC digital de-emphasis input (active HIGH)

DABCK 31 DAC input bit clock; 32f

s

, 48fs or 64f

s

DAWS 32 DAC word select input at f

s

V

SSD(F)

33 ADC/DAC digital filters ground supply voltage

V

DDD(F)

34 ADC/DAC digital filters supply voltage

DASDA 35 DAC serial data input

ANLPTR 36 ADC/DAC analog loop-through input (active HIGH)

TEST0 37 ADC/DAC enable test mode 0 input (LOW is normal mode)

TEST1 38 ADC/DAC enable test mode 1 input (LOW is normal mode)

V

SS(I/O)

39 ADC/DAC digital input/output ground supply voltage

SYSCLK 40 ADC/DAC system clock input (f

sys

= 256fs; DAC also 192fs and 384fs)

1998 Jan 06 6

Philips Semiconductors Product specification

Low-power stereo bitstream ADC/DAC UDA1309H

ADSDA 41 ADC serial data output

MODE1 42 ADC/DAC mode 1 select input

MODE2 43 ADC/DAC mode 2 select input

CLKEDGE 44 ADC/DAC input bit clock rising/falling edge

SYMBOL PIN DESCRIPTION

Fig.2 Pin configuration.

handbook, full pagewidth

1

2

3

4

5

6

7

8

9

10

11

33

32

31

30

29

28

27

26

25

24

23

12

13

14

15

16

17

18

19

20

21

22

44

43

42

41

40

39

38

37

36

35

34

UDA1309H

MBH526

V

SSD(F)

DAWS

DABCK

DADEM

V

DDD

V

SSD

V

SSA(DA)

V

DDA(DA)

V

OR

DACR

ADBCK

ADWS

MODE0

ADENB

OVLOAD

ADPON

V

DDA(AD)

V

ref(neg)

V

ref(pos)

DAPON

MODE2

MODE1

ADSDA

SYSCLK

V

SS(I/O)

TEST1

ANLPTR

DASDA

V

DDD(F)

CLKEDGE

TEST0

BAIL

BAIR

BAOR

AD

ref

I

ref

DA

ref

V

SSO

V

OL

DACL

BAOL

V

DDO

V

SSA(AD)

V

ref

1998 Jan 06 7

Philips Semiconductors Product specification

Low-power stereo bitstream ADC/DAC UDA1309H

FUNCTIONAL DESCRIPTION

Figure 1 illustrates the various components of the

UDA1309H.

The analog-to-digital converter is a bitstream type

converter, both channels are sampled simultaneously.

The digital-to-analog converter is a BCC (Bitstream

Continuous Calibration) type converter. The digital filter for

the ADC is a bit serial IIR filter that produces a fairly linear

phase response up to 15 kHz. A high-pass filter is

incorporated in the down-sampling path to remove DC

offsets. An overload detection circuit is incorporated to

facilitate automatic recording level adjustment.

The digital up-sample filter for the DAC is partly IIR, with

virtual linear phase response up to 15 kHz, and partly FIR.

A switchable digital de-emphasis circuit is also

incorporated. Due to the BCC principle used, the DAC

needs only single pole post-filtering (one external

capacitor) to meet the out-of-band suppression

requirement.

The ADC and DAC channels have separate power-down

modes, to reduce power if one of them is not in use.

An analog loop-through function enables analog-input

analog-output mode without using the ADC and DAC

converters or filters, thereby switching them off to reduce

power consumption.

The digital interfaces accommodates, 16 and 18-bit,

I

2

S-bus and LSB justified formats. The ADC digital output

can be made 3-state by means of the ADENB signal, this

enables the use of a digital bus.

The UDA1309H interface accommodates slave mode

only, therefore, the system ICs must provide the system

clock, bit clock and word clock signals. For the DAC, the

UDA1309H accepts the data together with these clocks,

for the ADC it delivers the data in response to these clocks.

Within one stereo frame, the first sample always

represents the left channel. When sending data the

unused bit positions are set to zero, when receiving data

these bit positions are don't cares.

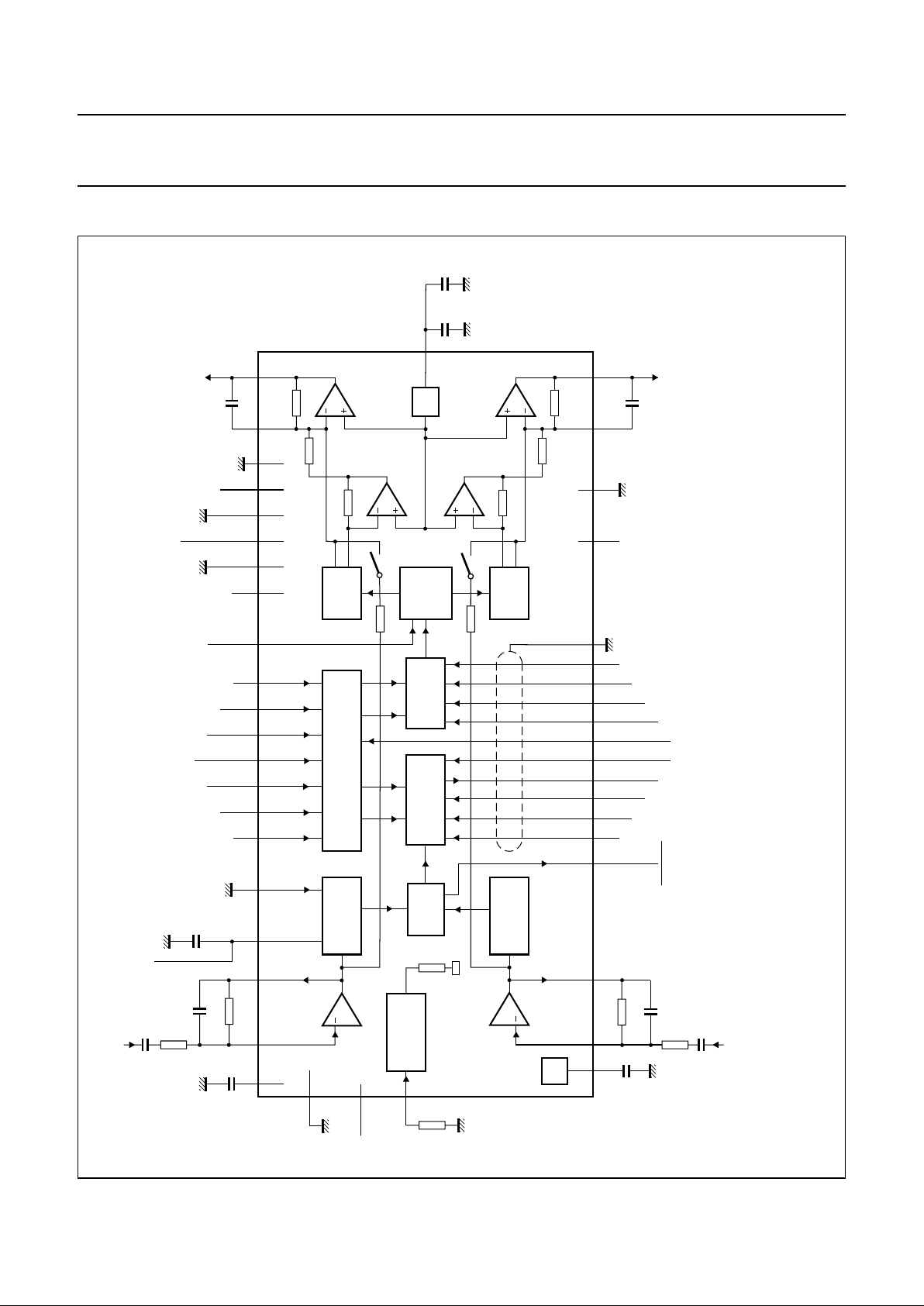

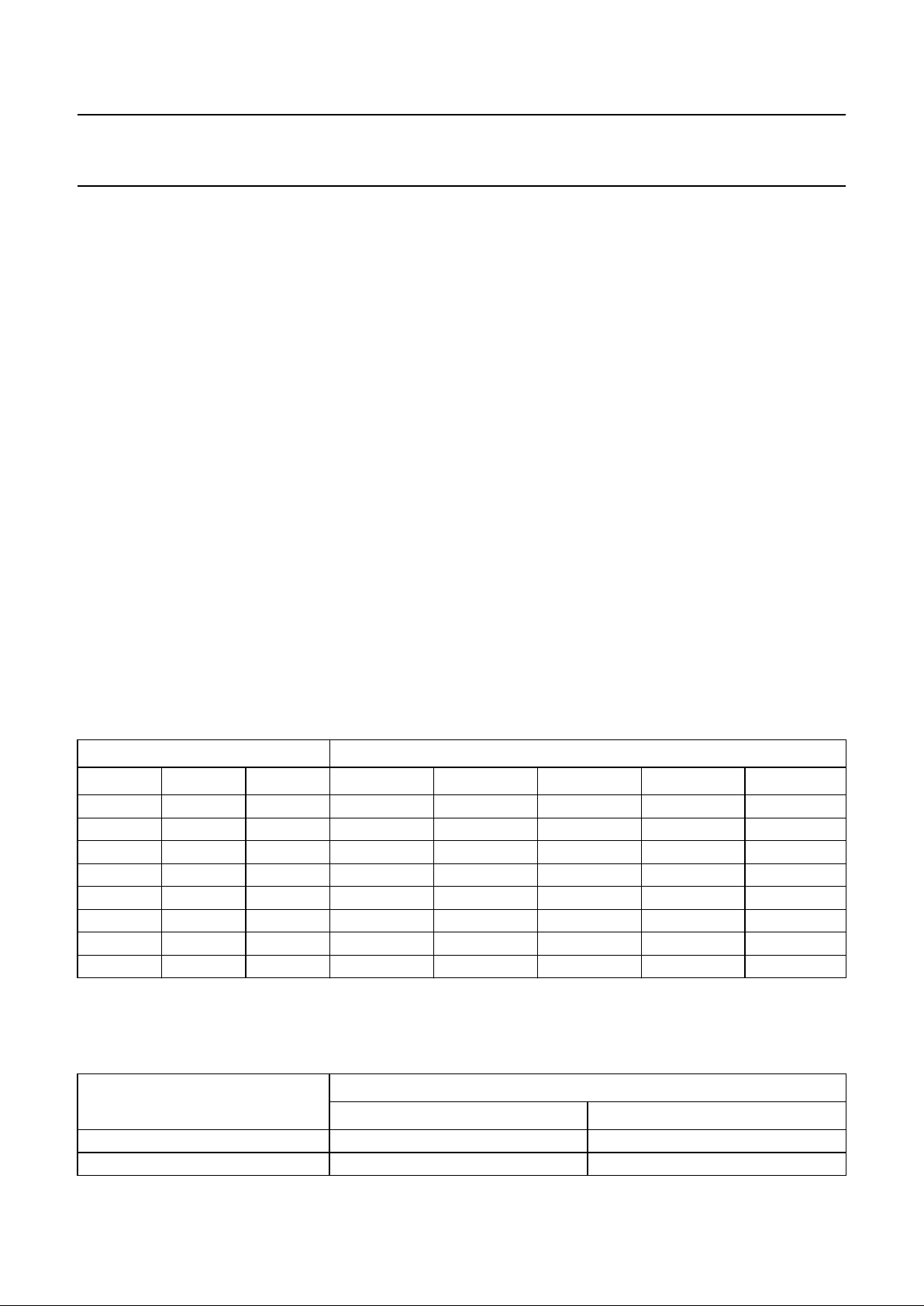

To accommodate the various interface formats and

system clock frequencies four control pins are provided,

MODE0 to MODE2 for mode selection and CLKEDGE

which selects the active edge of the BCK signal. Table 1

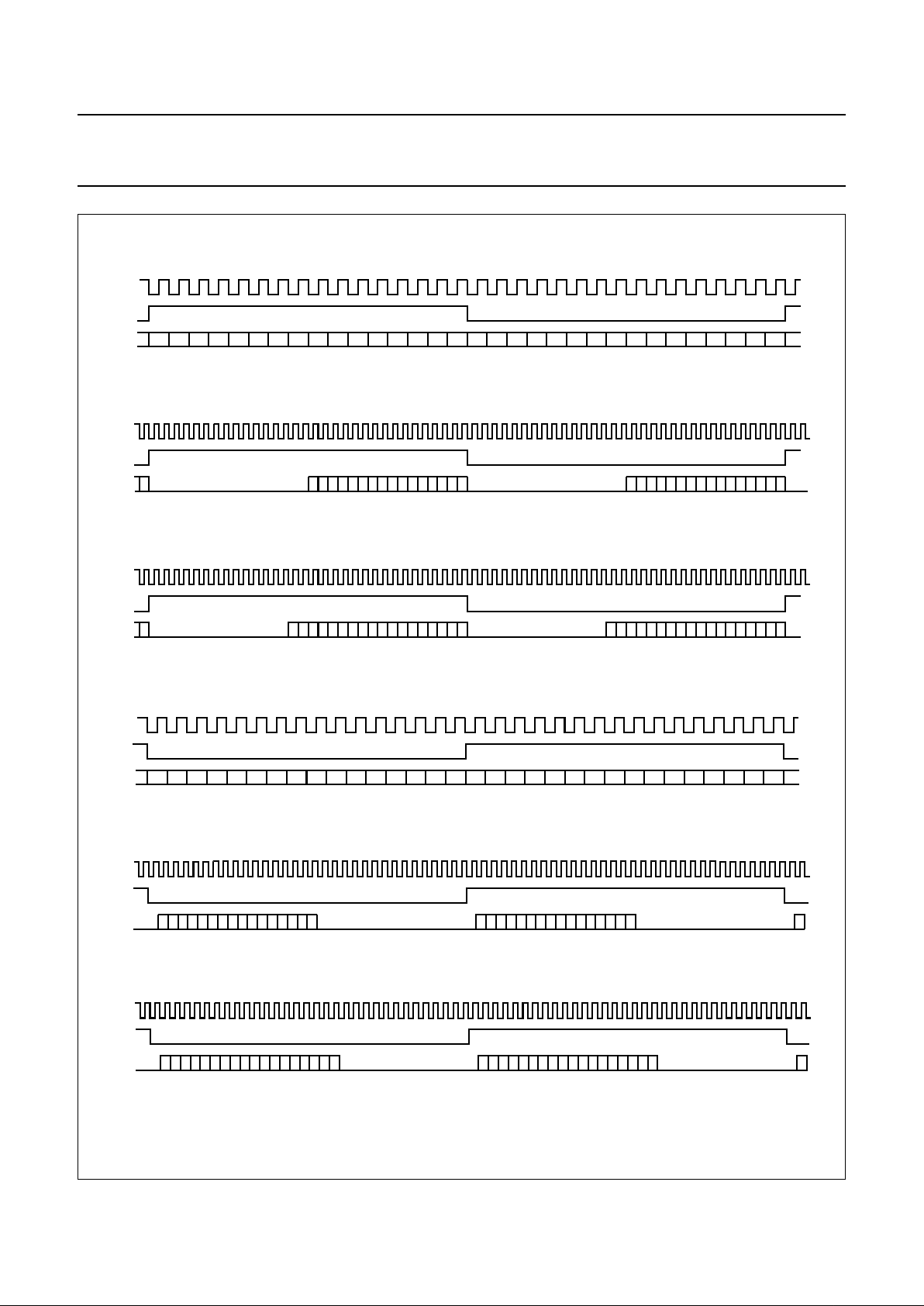

gives the interface mode selection, Fig.3 illustrates the

ADC/DAC data formats and Fig.5 the operating modes.

The section of the UDA1309H is designed to

accommodate two main modes:

1. The 256fs mode in which analog-to-digital and

digital-to-analog can be used.

2. The 192fs or 384fs mode (digital-to-analog only).

Table 1 Interface mode selection

Note

1. Only digital-to-analog.

Table 2 Clock edge mode

DEVICE PIN ADC/DAC FORMATS

MODE 2 MODE 1 MODE 0 TYPE BITS BCK SYS; f

sys

FIGURE

0 0 0 LSB justified 16 32f

s

256f

s

3(a)

0 0 1 LSB justified 16 64f

s

256f

s

3(b)

0 1 0 LSB justified 16 48f

s

192f

s

(1)

4(a)

0 1 1 LSB justified 18 64f

s

256f

s

3(c)

100I

2

S-bus 16 32f

s

256f

s

3(d)

101I

2

S-bus 16 64f

s

256f

s

3(e)

110I

2

S-bus 16 48f

s

384f

s

(1)

4(b)

111I

2

S-bus 18 64f

s

256f

s

3(f)

CLKEDGE

VALID EDGE OF BCK

ADC DAC

0 falling rising

1 rising falling

1998 Jan 06 8

Philips Semiconductors Product specification

Low-power stereo bitstream ADC/DAC UDA1309H

Fig.3 DAC and ADC data formats (continued in Fig.4).

handbook, full pagewidth

MGE767

BCK

WS

SDA

BCK

WS

SDA

BCK

WS

SDA

BCK

WS

SDA

BCK

WS

SDA

BCK

WS

SDA

LSB MSB

LEFT

LSB MSB

RIGHT

LEFT

RIGHT

LEFT

RIGHT

LEFT

RIGHT

LEFT

RIGHT

LEFT

RIGHT

LSB

MSB

LSB MSB

LSB

MSB

LSB MSB

LSB

MSB

LSB

LSB

MSB

LSB

MSB LSB MSB

MSB LSB

MSB

LSB MSB

LSB

MSB

LSB

MSB LSB

I

2

S 64fs 18-BIT

I

2

S 64fs 16-BIT

I

2

S 32fs 16-BIT

LSB JUSTIFIED 64fs 18-BIT

LSB JUSTIFIED 64fs 16-BIT

LSB JUSTIFIED 32fs 16-BIT

(a)

(b)

(c)

(d)

(e)

(f)

Loading...

Loading...