Philips TEA6320T-V1 Datasheet

DATA SH EET

Preliminary specification

Supersedes data of September 1992

File under Integrated Circuits, IC01

1995 Dec 19

INTEGRATED CIRCUITS

TEA6320

Sound fader control circuit

1995 Dec 19 2

Philips Semiconductors Preliminary specification

Sound fader control circuit TEA6320

FEATURES

• Source selector for four stereo and one mono inputs

• Interface for noise reduction circuits

• Interface for external equalizer

• Volume, balance and fader control

• Special loudness characteristic automatically controlled

in combination with volume setting

• Bass and treble control

• Mute control at audio signal zero crossing

• Fast mute control via I2C-bus

• Fast mute control via pin

• I

2

C-bus control for all functions

• Power supply with internal power-on reset.

GENERAL DESCRIPTION

The sound fader control circuit TEA6320 is an I

2

C-bus

controlled stereo preamplifier for car radio hi-fi sound

applications.

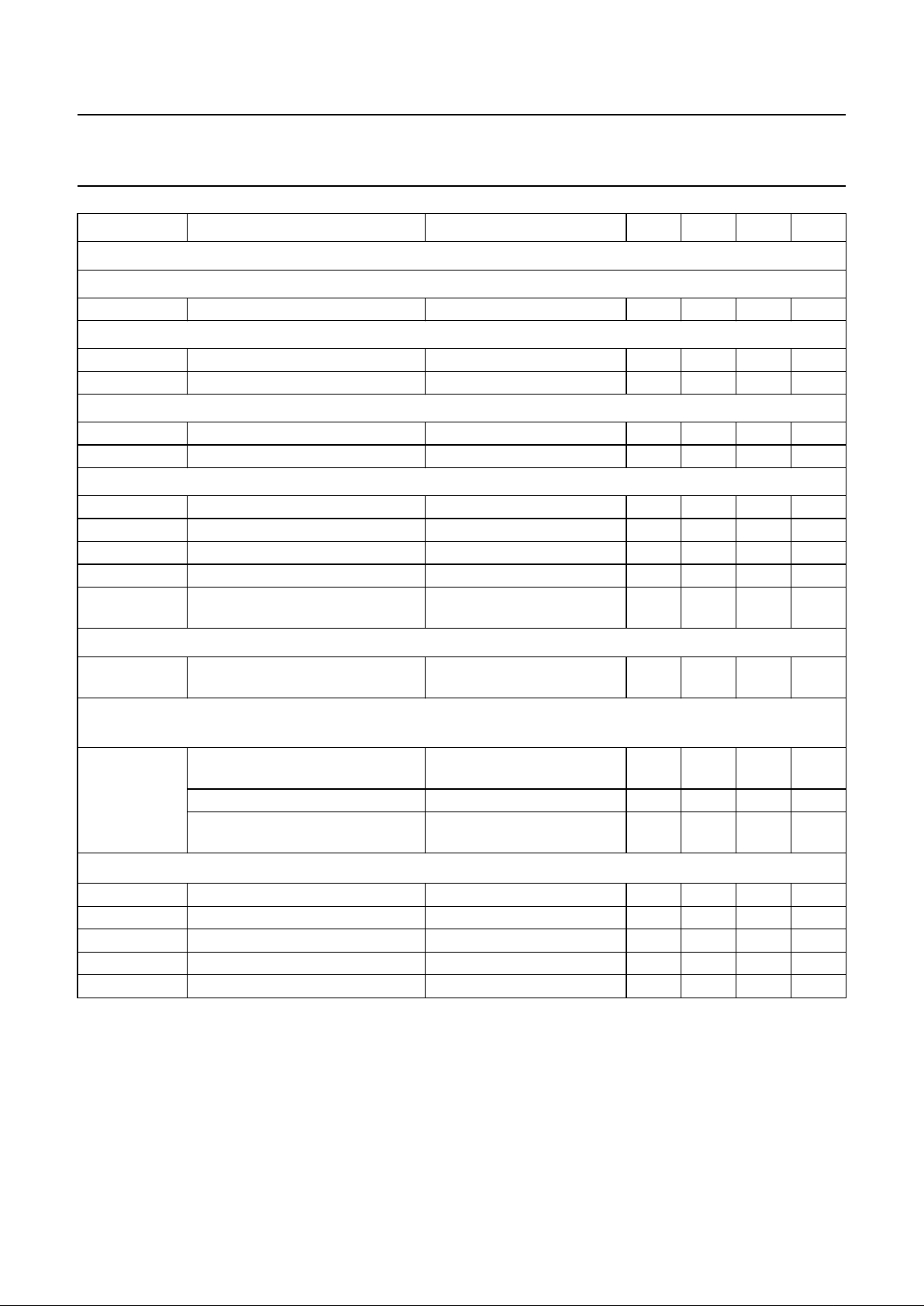

QUICK REFERENCE DATA

ORDERING INFORMATION

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V

CC

supply voltage 7.5 8.5 9.5 V

I

CC

supply current VCC= 8.5 V − 26 − mA

V

o(rms)

maximum output voltage level VCC= 8.5 V; THD ≤ 0.1% − 2000 − mV

G

v

voltage gain −86 − +20 dB

G

step(vol)

step resolution (volume) − 1 − dB

G

bass

bass control −15 − +15 dB

G

treble

treble control −12 − +12 dB

G

step(treble)

step resolution (bass, treble) − 1.5 − dB

(S+N)/N signal-plus-noise to noise ratio V

O

= 2.0 V; Gv= 0 dB;

unweighted

− 105 − dB

RR

100

ripple rejection V

r(rms)

< 200 mV; f = 100 Hz;

Gv=0dB

− 76 − dB

α

cs

channel separation 250 Hz ≤ f ≤ 10 kHz; Gv= 0 dB 90 96 − dB

TYPE

NUMBER

PACKAGE

NAME DESCRIPTION VERSION

TEA6320 SDIP32 plastic shrink dual in-line package; 32 leads (400 mil) SOT232-1

TEA6320T SO32 plastic small outline package; 32 leads; body width 7.5 mm SOT287-1

1995 Dec 19 3

Philips Semiconductors Preliminary specification

Sound fader control circuit TEA6320

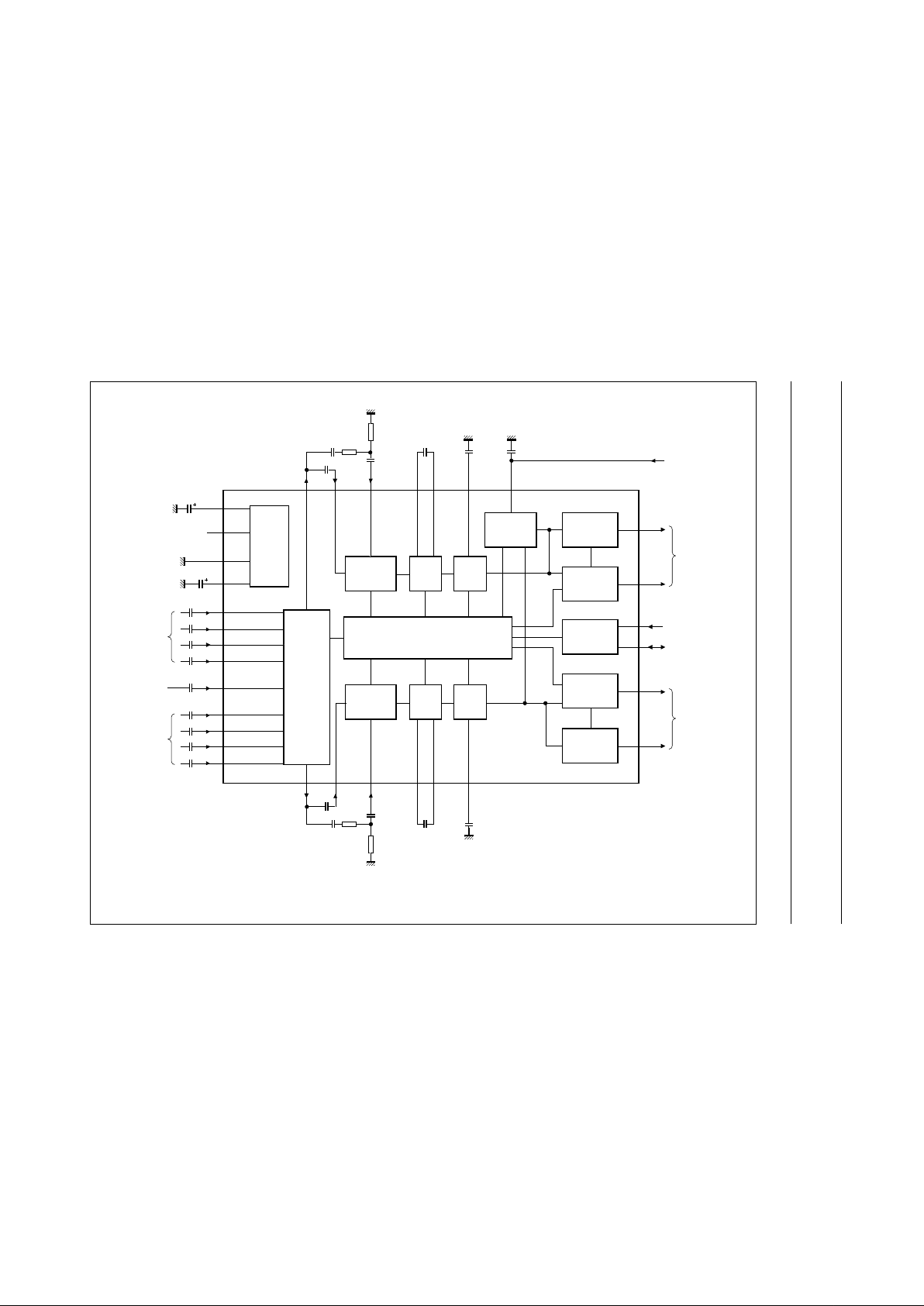

BLOCK DIAGRAM

Fig.1 Block diagram.

handbook, full pagewidth

POWER

SUPPLY

SOURCE

SELECTOR

VOLUME I

+20 to −31 dB

LOUDNESS

LEFT

BASS

LEFT

±15 dB

TREBLE

LEFT

±12 dB

VOLUME II

0 to −55 dB

BALANCE

FADER FRONT

VOLUME II

0 to −55 dB

BALANCE

FADER REAR

MUTE

FUNCTION

ZERO CROSS

DETECTOR

LOGIC

VOLUME I

+20 to −31 dB

LOUDNESS

RIGHT

BASS

RIGHT

±15 dB

TREBLE

RIGHT

±12 dB

VOLUME II

0 to −55 dB

BALANCE

FADER REAR

VOLUME II

0 to −55 dB

BALANCE

FADER FRONT

I2C-BUS

RECEIVER

21

31

2

19

16

15

11

14

22

20

18

17

13

100 µF

V

CC

GND

47 µF

9 x 220 nF

C

KIN

23 25

24

26 27

C

KVL

220 nF

8.2 nF

20 kΩ

150 nF

2.2 kΩ

33 nF

28

5.6 nF

TEA6320

30

29

1

32

SDA

SCL

MUTE

3

4

10 8

9

7

6

512

C

KVL

220 nF

8.2 nF

20 kΩ

2.2 kΩ

150 nF

33 nF

5.6 nF 10 nF

C

m

MED421

V

ref

input

right

source

input

left

source

input

mono

source

output

right

output

left

1995 Dec 19 4

Philips Semiconductors Preliminary specification

Sound fader control circuit TEA6320

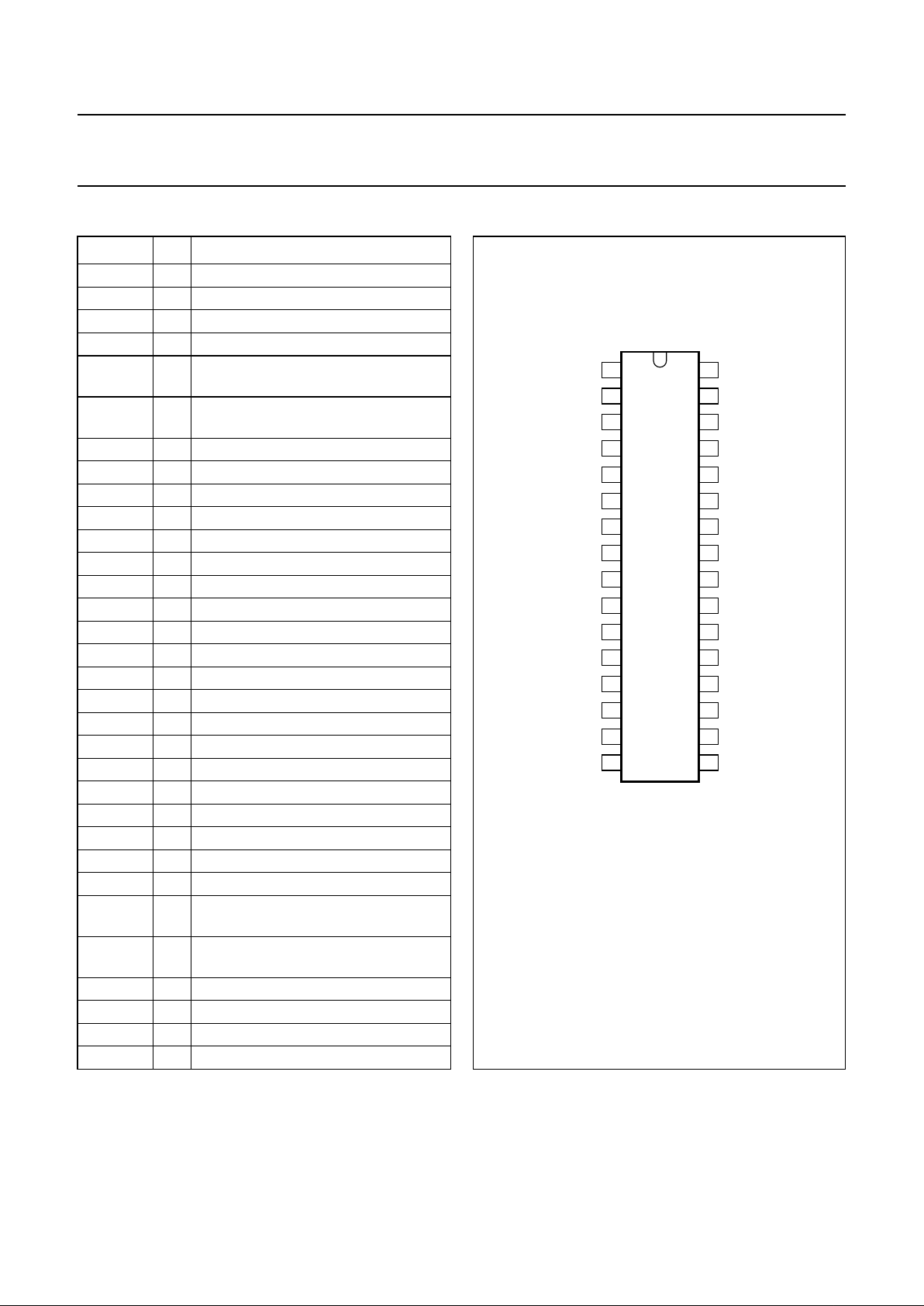

PINNING

SYMBOL PIN DESCRIPTION

SDA 1 serial data input/output

GND 2 ground

OUTLR 3 output left rear

OUTLF 4 output left front

TL 5 treble control capacitor left channel or

input from an external equalizer

B2L 6 bass control capacitor left channel or

output to an external equalizer

B1L 7 bass control capacitor, left channel

IVL 8 input volume I, left control part

ILL 9 input loudness, left control part

QSL 10 output source selector, left channel

IDL 11 input D left source

MUTE 12 mute control

ICL 13 input C left source

IMO 14 input mono source

IBL 15 input B left source

IAL 16 input A left source

IAR 17 input A right source

IBR 18 input B right source

CAP 19 electronic filtering for supply

ICR 20 input C right source

V

ref

21 reference voltage (0.5VCC)

IDR 22 input D right source

QSR 23 output source selector right channel

ILR 24 input loudness right channel

IVR 25 input volume I, right control part

B1R 26 bass control capacitor right channel

B2R 27 bass control capacitor right channel or

output to an external equalizer

TR 28 treble control capacitor right channel

or input from an external equalizer

OUTRF 29 output right front

OUTRR 30 output right rear

V

CC

31 supply voltage

SCL 32 serial clock input

Fig.2 Pin configuration.

handbook, halfpage

TEA6320

MED422

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

B1L

B2L

TL

OUTLF

OUTLR

IAL

IBL

IMO

ICL

IDL

MUTE

QSL

ILL

IVL

ICR

IDR

V

ref

IAR

IBR

CAP

QSR

ILR

IVR

B1R

B2R

TR

OUTRF

OUTRR

V

CC

SCL

GND

SDA

1995 Dec 19 5

Philips Semiconductors Preliminary specification

Sound fader control circuit TEA6320

FUNCTIONAL DESCRIPTION

The source selector selects one of 4 stereo inputs or the

mono input. The maximum input signal voltage is

V

i(rms)

= 2 V. The outputs of the source selector and the

inputs of the following volume control parts are available at

pins 8 and 10 for the left channel and pins 23 and 25 for

the right channel. This offers the possibility of interfacing a

noise reduction system.

The volume control function is split into two sections:

volume I control block and volume II control block.

The control range of volume I is between +20 dB and

−31 dB in steps of 1 dB. The volume II control range is

between 0 dB and −55 dB in steps of 1 dB. Although the

theoretical possible control range is 106 dB

(+20 to −86 dB), in practice a range of 86 dB (+20 to

−66 dB) is recommended. The gain/attenuation setting of

the volume I control block is common for both channels.

The volume I control block operates in combination with

the loudness control. The filter is linear when the maximum

gain for the volume I control (+20 dB) is selected. The filter

characteristic increases automatically over a range of

32 dB down to a setting of −12 dB. That means the

maximum filter characteristic is obtained at −12 dB setting

of volume I. Further reduction of the volume does not

further influence the filter characteristic (see Fig.5). The

maximum selected filter characteristic is determined by

external components. The proposed application gives a

maximum boost of 17 dB for bass and 4.5 dB for treble.

The loudness may be switched on or off via I

2

C-bus control

(see Table 7).

The volume I control block is followed by the bass control

block. A single external capacitor of 33 nF for each

channel in combination with internal resistors, provides the

frequency response of the bass control (see Fig.3). The

adjustable range is between −15 and +15 dB at 40 Hz.

Both loudness and bass control result in a maximum bass

boost of 32 dB for low volume settings.

The treble control block offers a control range between

−12 and +12 dB in steps of 1.5 dB at 15 kHz. The filter

characteristic is determined by a single capacitor of 5.6 nF

for each channel in combination with internal resistors

(see Fig.4).

The basic step width of bass and treble control is 3 dB. The

intermediate steps are obtained by switching 1.5 dB boost

and 1.5 dB attenuation steps.

The bass and treble control functions can be switched off

via I2C-bus. In this event the internal signal flow is

disconnected. The connections B2L and B2R are outputs

and TL and TR are inputs for inserting an external

equalizer.

The last section of the circuit is the volume II block. The

balance and fader functions are performed using the same

control blocks. This is realized by 4 independently

controllable attenuators, one for each output. The control

range of these attenuators is 55 dB in steps of 1 dB with an

additional mute step.

The circuit provides 3 mute modes:

1. Zero crossing mode mute via I

2

C-bus using

2 independent zero crossing detectors (ZCM,

see Tables 2 and 9 and Fig.16).

2. Fast mute via MUTE pin (see Fig.10).

3. Fast mute via I2C-bus either by general mute (GMU,

see Tables 2 and 9) or volume II block setting

(see Table 4).

The mute function is performed immediately if ZCM is

cleared (ZCM = 0). If the bit is set (ZCM = 1) the mute is

activated after changing the GMU bit. The actual mute

switching is delayed until the next zero crossing of the

audio frequency signal. As the two audio channels (left and

right) are independent, two comparators are built-in to

control independent mute switches.

To avoid a large delay of mute switching when very low

frequencies are processed, the maximum delay time is

limited to typically 100 ms by an integrated timing circuit

and an external capacitor (Cm= 10 nF, see Fig.10). This

timing circuit is triggered by reception of a new data word

for the switch function which includes the GMU bit. After a

discharge and charge period of an external capacitor the

muting switch follows the GMU bit if no zero crossing was

detected during that time.

The mute function can also be controlled externally. If the

mute pin is switched to ground all outputs are muted

immediately (hardware mute). This mute request

overwrites all mute controls via the I2C-bus for the time the

pin is held LOW. The hardware mute position is not stored

in the TEA6320.

For the turn on/off behaviour the following explanation is

generally valid. To avoid AF output caused by the input

signal coming from preceding stages, which produces

output during drop of VCC, the mute has to be set, before

the VCC will drop. This can be achieved by I2C-bus control

or by grounding the MUTE pin.

For use where is no mute in the application before turn off,

a supply voltage drop of more than 1 × VBE will result in a

mute during the voltage drop.

1995 Dec 19 6

Philips Semiconductors Preliminary specification

Sound fader control circuit TEA6320

The power supply should include a VCC buffer capacitor,

which provides a discharging time constant. If the input

signal does not disappear after turn off the input will

become audible after certain time. A 4.7 kΩ resistor

discharges the VCC buffer capacitor, because the internal

current of the IC does not discharge it completely.

The hardware mute function is favourable for use in Radio

Data System (RDS) applications. The zero crossing mute

avoids modulation plops. This feature is an advantage for

mute during changing presets and/or sources (e.g. traffic

announcement during cassette playback).

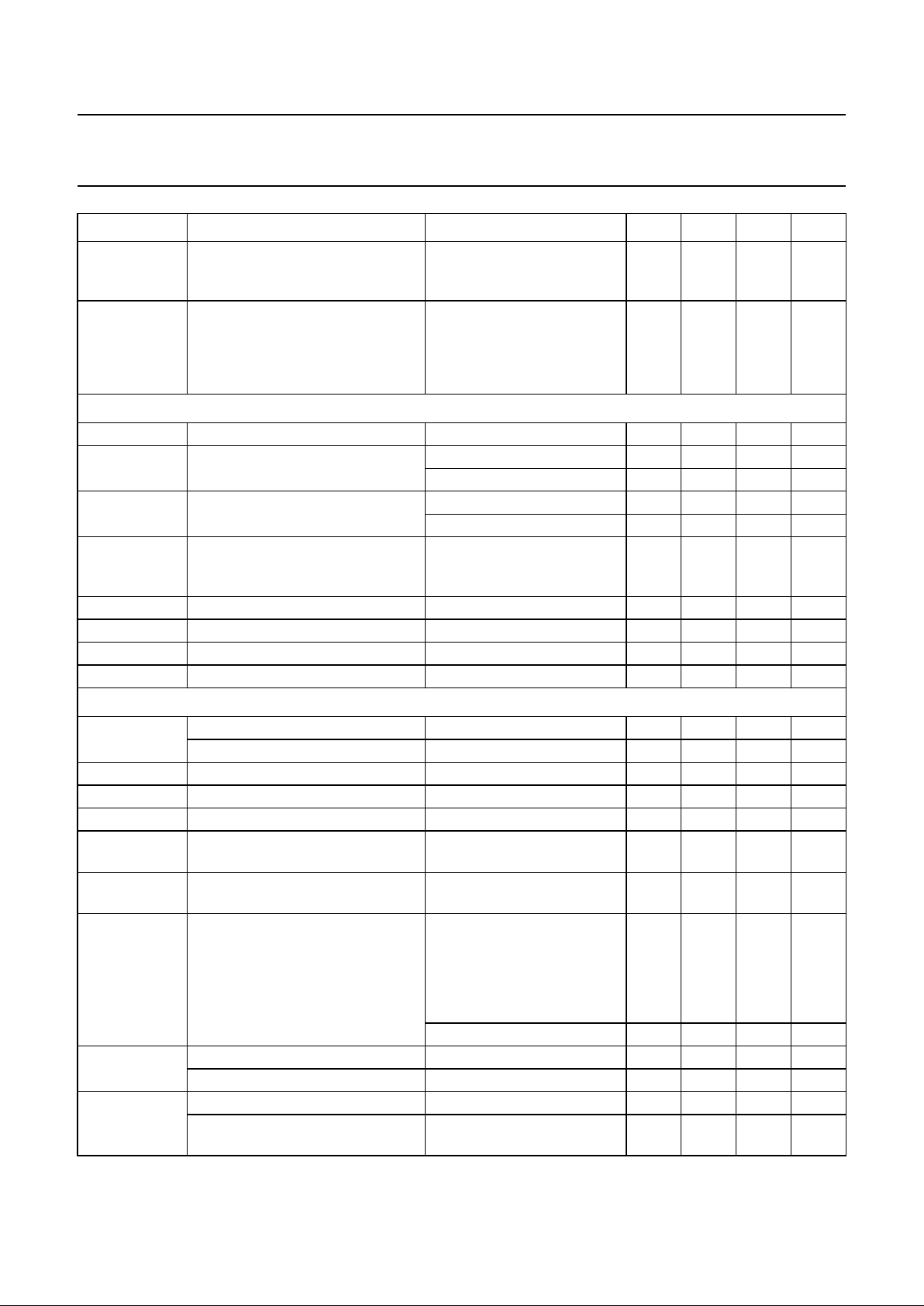

LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134).

Note

1. Human body model: C = 100 pF; R = 1.5 kΩ; V ≥ 2 kV. Charge device model: C = 200 pF; R = 0 Ω; V ≥ 500 V.

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

V

CC

supply voltage 0 10 V

V

n

voltage at all pins except pin 2

referenced to GND (pin 2)

0VCCV

T

amb

operating ambient temperature −40 +85 °C

T

stg

storage temperature −65 +150 °C

V

es

electrostatic handling note 1

1995 Dec 19 7

Philips Semiconductors Preliminary specification

Sound fader control circuit TEA6320

CHARACTERISTICS

VCC= 8.5 V; RS= 600 Ω; RL=10kΩ; CL= 2.5 nF; AC coupled; f = 1 kHz; T

amb

=25°C; gain control Gv= 0 dB; bass

linear; treble linear; fader off; balance in mid position; loudness off; unless otherwise specified.

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V

CC

supply voltage 7.5 8.5 9.5 V

I

CC

supply current − 26 33 mA

V

DC

internal DC voltage at inputs and

outputs

3.83 4.25 4.68 V

V

ref

internal reference voltage at pin 21 − 4.25 − V

G

v(max)

maximum voltage gain RS=0Ω; RL= ∞ 19 20 21 dB

V

o(rms)

output voltage level for

P

max

at the power output stage THD ≤ 0.5%; see Fig.11 − 2000 − mV

start of clipping THD = 1% 2300 −−mV

R

L

=2kΩ; CL= 10 nF;

THD=1%

2000 −−mV

V

i(rms)

input sensitivity Vo= 2000 mV; Gv=20dB − 200 − mV

f

ro

roll-off frequency C

KIN

= 220 nF;

C

KVL

= 220 nF; Zi=Z

i(min)

low frequency (−1 dB) 60 −−Hz

low frequency (−3 dB) 30 −−Hz

high frequency (−1 dB) 20000 −−Hz

C

KIN

= 470 nF;

C

KVL

= 100 nF; Zi=Z

i(typ)

low frequency (−3 dB)

17 −−Hz

α

cs

channel separation Vi= 2 V; frequency range

250 Hz to 10 kHz

90 96 − dB

THD total harmonic distortion frequency range

20 Hz to 12.5 kHz

Vi= 100 mV; Gv=20dB − 0.1 − %

V

i

= 1 V; Gv=0dB − 0.05 0.15 %

V

i

= 2 V; Gv=0dB − 0.1 − %

V

i

= 2 V; Gv= −10 dB − 0.1 − %

RR ripple rejection V

r(rms)

< 200 mV

f = 100 Hz 70 76 − dB

f = 40 Hz to 12.5 kHz − 66 − dB

(S+N)/N signal-plus-noise to noise ratio unweighted;

20 Hz to 20 kHz (RMS);

V

o

= 2.0 V; see Figs 6 and 7

− 105 − dB

CCIR468-2 weighted; quasi

peak; V

o

= 2.0 V

G

v

=0dB − 95 − dB

G

v

=12dB − 88 − dB

G

v

=20dB − 81 − dB

1995 Dec 19 8

Philips Semiconductors Preliminary specification

Sound fader control circuit TEA6320

P

no(rms)

noise output power (RMS value)

only contribution of TEA6320;

power amplifier for 6 W

mute position; note 1 −−10 nW

α

ct

crosstalk

between bus

inputs and signal outputs

note 2 − 110 − dB

Source selector

Z

i

input impedance 25 35 45 kΩ

α

S

input isolation of one selected

source to any other input

f = 1 kHz − 105 − dB

f = 12.5 kHz − 95 − dB

V

i(rms)

maximum input voltage

(RMS value)

THD < 0.5%; VCC= 8.5 V − 2.15 − V

THD < 0.5%; V

CC

= 7.5 V − 1.8 − V

V

offset

DC offset voltage at source

selector output by selection of any

inputs

−−10 mV

Z

o

output impedance − 80 120 Ω

R

L

output load resistance 10 −−kΩ

C

L

output load capacity 0 − 2500 pF

G

v

voltage gain, source selector − 0 − dB

Control part (source selector disconnected; source resistance 600 Ω)

Z

i

input impedance volume input 100 150 200 kΩ

input impedance loudness input 25 33 40 kΩ

Z

o

output impedance − 80 120 Ω

R

L

output load resistance 2 −−kΩ

C

L

output load capacity 0 − 10 nF

R

DCL

DC load resistance at output to

ground

4.7 −−kΩ

V

i(rms)

maximum input voltage

(RMS value)

THD < 0.5% − 2.15 − V

V

no

noise output voltage CCIR468-2 weighted; quasi

peak

G

v

=20dB − 110 220 µV

G

v

=0dB − 33 50 µV

G

v

= −66 dB − 13 22 µV

mute position − 10 −µV

CR

tot

total continuous control range − 106 − dB

recommended control range − 86 − dB

G

step

step resolution − 1 − dB

step error between any adjoining

step

−−0.5 dB

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

20

V

bus p p–()

V

o rms()

-------------------------- -log

1995 Dec 19 9

Philips Semiconductors Preliminary specification

Sound fader control circuit TEA6320

∆G

a

attenuator set error Gv= +20 to −50 dB −−2dB

G

v

=−51 to −66 dB −−3dB

∆G

t

gain tracking error Gv= +20 to −50 dB −−2dB

MUTE

att

mute attenuation see Fig.10 100 110 − dB

V

offset

DC step offset between any

adjoining step

Gv=0to−66 dB − 0.2 10 mV

G

v

=20to0dB − 215mV

DC step offset between any step to

mute

G

v

=0to−66 dB −−10 mV

Volume I control and loudness

CR

vol

continuous volume control range − 51 − dB

G

v

voltage gain −31 − +20 dB

G

step

step resolution − 1 − dB

L

Bmax

maximum loudness boost loudness on; referred to

loudness off; boost is

determined by external

components

f = 40 Hz − 17 − dB

f = 10 kHz − 4.5 − dB

Bass control

G

bass

bass control, maximum boost f = 40 Hz 14 15 16 dB

maximum attenuation f = 40 Hz 14 15 16 dB

G

step

step resolution (toggle switching) f = 40 Hz − 1.5 − dB

step error between any adjoining

step

f = 40 Hz −−0.5 dB

V

offset

DC step offset in any bass position −−20 mV

Treble control

G

treble

treble control, maximum boost f = 15 kHz 11 12 13 dB

maximum attenuation f = 15 kHz 11 12 13 dB

maximum boost f > 15 kHz −−15 dB

G

step

step resolution (toggle switching) f = 15 kHz − 1.5 − dB

step error between any adjoining

step

f = 15 kHz −−0.5 dB

V

offset

DC step offset in any treble

position

−−10 mV

Volume II, balance and fader control

CR continuous attenuation fader and

volume control range

53.5 55 56.5 dB

G

step

step resolution − 12dB

attenuation set error −−1.5 dB

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

1995 Dec 19 10

Philips Semiconductors Preliminary specification

Sound fader control circuit TEA6320

Notes to the characteristics

1. The indicated values for output power assume a 6 W power amplifier at 4 Ω with 20 dB gain and a fixed attenuator

of 12 dB in front of it. Signal-to-noise ratios exclude noise contribution of the power amplifier.

2. The transmission contains: total initialization with MAD and subaddress for volume and 8 data words, see also

definition of characteristics, clock frequency = 50 kHz, repetition burst rate = 400 Hz, maximum bus signal

amplitude = 5 V (p-p).

3. The AC characteristics are in accordance with the I2C-bus specification. This specification,

“The I2C-bus and how to

use it

”, can be ordered using the code 9398 393 40011.

Mute function (see Fig.10)

H

ARDWARE MUTE

V

sw

mute switch level (2 × VBE) − 1.45 − V

mute active

V

swLOW

input level −−1.0 V

I

i

input current V

swLOW

=1V −300 −−µA

mute passive: level internally defined

V

swHIGH

saturation voltage −−VCCV

t

d(mute)

delay until mute passive −−0.5 ms

ZERO CROSSING MUTE

I

d

discharge current 0.3 0.6 1.2 µA

I

ch

charge current −300 −150 −µA

V

swDEL

delay switch level (3 × VBE) − 2.2 − V

t

d

delay time Cm=10nF − 100 − ms

V

wind

window for audio signal zero

crossing detection

− 30 40 mV

Muting at power supply drop

V

CCdrop

supply drop for mute active − V19−

0.7

− V

Power-on reset (when reset is active the GMU-bit (general mute) is set and the I

2

C-bus receiver is in

reset position)

V

CC

increasing supply voltage start of

reset

−−2.5 V

end of reset 5.2 6.5 7.2 V

decreasing supply voltage start of

reset

4.2 5.5 6.2 V

Digital part (I

2

C-bus pins); note 3

V

iH

HIGH level input voltage 3 − 9.5 V

V

iL

LOW level input voltage −0.3 − +1.5 V

I

iH

HIGH level input current −10 − +10 µA

I

iL

LOW level input current −10 − +10 µA

V

oL

LOW level output voltage IL=3mA −−0.4 V

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

1995 Dec 19 11

Philips Semiconductors Preliminary specification

Sound fader control circuit TEA6320

I2C-BUS PROTOCOL

I

2

C-bus format

Notes

1. S = START condition.

2. SLAVE ADDRESS (MAD) = 1000 0000.

3. A = acknowledge, generated by the slave.

4. SUBADDRESS (SAD), see Table 1.

5. DATA, see Table 1; if more than 1 byte of DATA is transmitted, then auto-increment of the significant subaddress is

performed.

6. P = STOP condition.

Table 1 Second byte after MAD

Note

1. Significant subaddress.

S

(1)

SLAVE ADDRESS

(2)

A

(3)

SUBADDRESS

(4)

A

(3)

DATA

(5)

A

(3)

P

(6)

FUNCTION BIT

MSB LSB

765432

(1)

1

(1)

0

(1)

Volume/loudness V 00000000

Fader front right FFR 00000001

Fader front left FFL 00000010

Fader rear right FRR 00000011

Fader rear left FRL 00000100

Bass BA 00000101

Treble TR 00000110

Switch S 00000111

1995 Dec 19 12

Philips Semiconductors Preliminary specification

Sound fader control circuit TEA6320

Table 2 Definition of third byte after MAD and SAD

Notes

1. Zero crossing mode.

2. Switch loudness on/off.

3. Volume control.

4. Don’t care bits (logic 1 during testing).

5. Fader control front right.

6. Fader control front left.

7. Fader control rear right.

8. Fader control rear left.

9. Bass control.

10. Treble control.

11. Mute control for all outputs (general mute).

12. Source selector control.

FUNCTION BIT

MSB LSB

76543210

Volume/loudness V ZCM

(1)

LOFF

(2)

V5

(3)

V4

(3)

V3

(3)

V2

(3)

V1

(3)

V0

(3)

Fader front right FFR X

(4)

X

(4)

FFR5

(5)

FFR4

(5)

FFR3

(5)

FFR2

(5)

FFR1

(5)

FFR0

(5)

Fader front left FFL X

(4)

X

(4)

FFL5

(6)

FFL4

(6)

FFL3

(6)

FFL2

(6)

FFL1

(6)

FFL0

(6)

Fader rear right FRR X

(4)

X

(4)

FRR5

(7)

FRR4

(7)

FRR3

(7)

FRR2

(7)

FRR1

(7)

FRR0

(7)

Fader rear left FRL X

(4)

X

(4)

FRL5

(8)

FRL4

(8)

FRL3

(8)

FRL2

(8)

FRL1

(8)

FRL0

(8)

Bass BA X

(4)

X

(4)

X

(4)

BA4

(9)

BA3

(9)

BA2

(9)

BA1

(9)

BA0

(9)

Treble TR X

(4)

X

(4)

X

(4)

TR4

(10)

TR3

(10)

TR2

(10)

TR1

(10)

TR0

(10)

Switch S GMU

(11)

X

(4)

X

(4)

X

(4)

X

(4)

SC2

(12)

SC1

(12)

SC0

(12)

Loading...

Loading...